# **Durham E-Theses**

# The development of a distributed interfacing system

Gray, Peter

#### How to cite:

Gray, Peter (1986) The development of a distributed interfacing system, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/7028/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- $\bullet\,$  the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# The Development of a Distributed Interfacing System

bу

Peter Gray, BSc.

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

A Thesis submitted in accordance with the regulation for the degree of Master of Science in the Department of Applied Physics and Electronics at the University of Durham.

May 1986

#### ABSTRACT

The Thesis submitted describes the origins and development of an industrial distributed interfacing system. The component modules of the system are described individually and sample flowcharts and software listings are provided.

#### ACKNOWLEDGEMENTS

The author would like to acknowledge the assistance and support for this project given by the staff of the University of Durham, especially Professor G.R. Roberts (now at Oxford University) and Professor T. Spracklen (now at Aberdeen University), and also by the management and staff of Glaxo Pharmaceuticals (referred to herein as 'the Company'). Special thanks are due to Messrs W.H. Presley and R.A. Pearson of the Company's Management Services Department for approving the project development and granting permission to submit this Thesis, to my immediate superiors Messrs J. Howe and J. Prytherick, to Messrs H.G. Myatt and L.Rodrigues for checking production drawings, and to Mr R.W. Atkinson, who developed professional working systems from the test software described in this document. My thanks are also due to Messrs J.M. Wood and S.M. Wood of Labcon Ltd. (referred to herein as 'the Contractors') and to Messrs I. Robertson and J. Williams for prototype layout and much stimulating discussion, and also to Mr R.J. Hickson (now with R.J. Designs, Shildon) for producing the CAD artworks for production boards.

# CONTENTS

| Chapter    | 1          | Introduction                          | 1   |

|------------|------------|---------------------------------------|-----|

| 11         | 2          | The Pilot Scheme                      | 6   |

| Ħ          | 3          | The Expanded System                   | 23  |

| R          | 4          | Memory Expansion                      | 53  |

| 11         | 5          | Communications Interfaces             | 63  |

| tt         | 6          | Serial Port Interfaces                | 86  |

| 11         | 7          | The Analogue Board                    | 104 |

| 11         | 8          | Running MCS BASIC-52 On the System    | 114 |

| 11         | 9          | Project Review                        | 127 |

| References |            |                                       | 132 |

| Appendix   | <b>x</b> 1 | Crystals/Oscillator Components        | 134 |

| 11         | 2          | Pilot Scheme Data                     | 147 |

| n          | 3          | The 8751 Serial Port                  | 158 |

| 11         | 4          | HPIB Overview                         | 163 |

| 11         | 5          | Features of the 8748                  | 168 |

| 11         | 6          | BCD Board (Testing/Firmware)          | 169 |

| 11         | 7          | A Sample HPIB-RS232 Converter         | 173 |

| 11         | 8          | The 8052-BASIC CPU                    | 176 |

| 11         | 9          | Serial/UART Board Functions & Options | 182 |

| 11         | 10         | Power Supplies                        | 187 |

| 11         | 11         | Details of RAM Memory Devices         | 189 |

# LIST OF PLATES AND ILLUSTRATIONS

| Figure | 2.1 | Pilot Scheme - Schematic                   | 7   |

|--------|-----|--------------------------------------------|-----|

| 11     | 2.2 | Power Supplies                             | 10  |

| II     | 2.3 | Schematic Diagram of a Node                | 11  |

| 11     | 2.4 | The NE567 Configured as a PLL              | 14  |

| 11     | 2.5 | " " " VCO                                  | 17  |

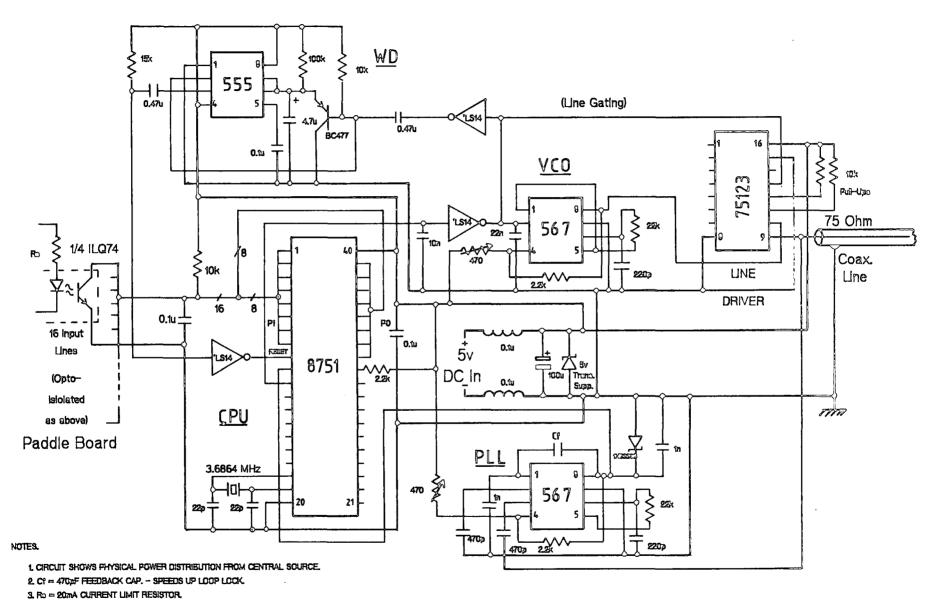

| 11     | 2.6 | Circuit Diagram of a Node                  | 18  |

| 11     | 3.1 | Backplane Connector Pin-out                | 26  |

| 11     | 3.2 | 8751 Pin-out                               | 28  |

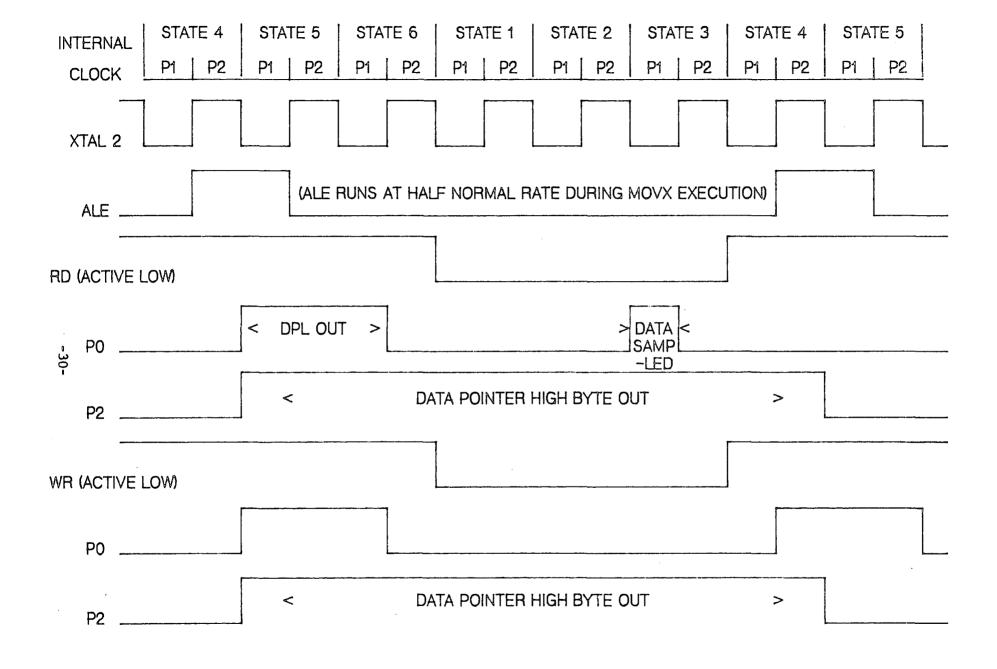

| ŧŧ     | 3.3 | Timing Diagram for External Memory Access  | 30  |

| 11     | 3.4 | CPU Board Circuit Diagram                  | 32  |

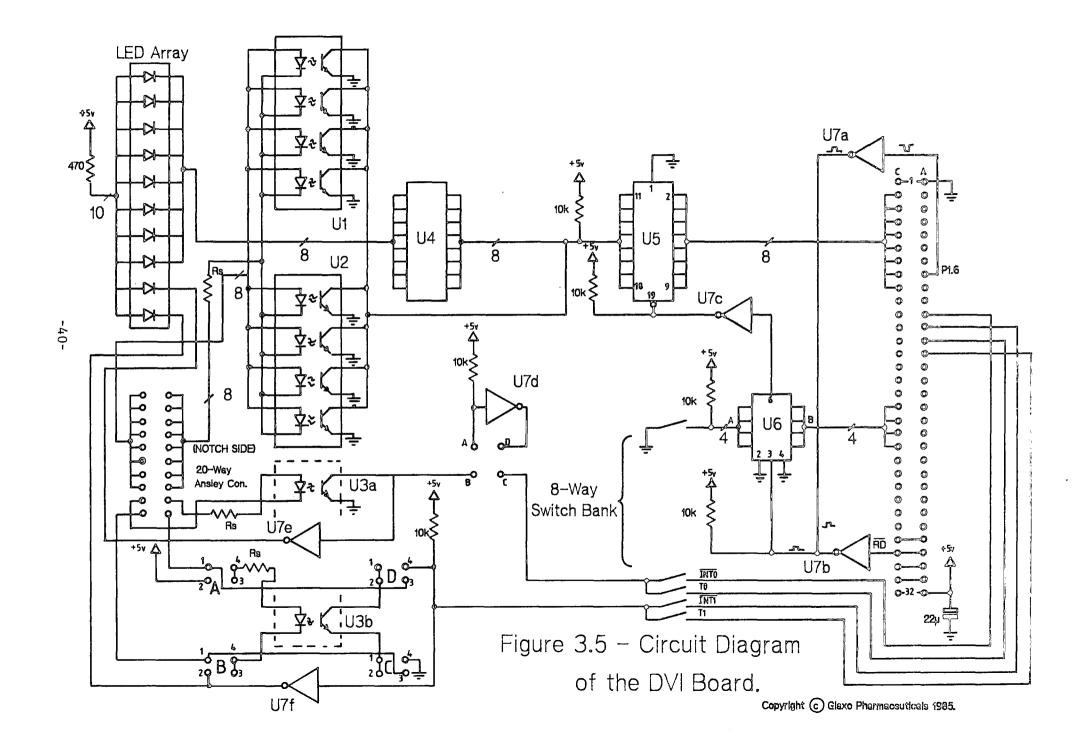

| **     | 3.5 | DVI Board Circuit Diagram                  | 40  |

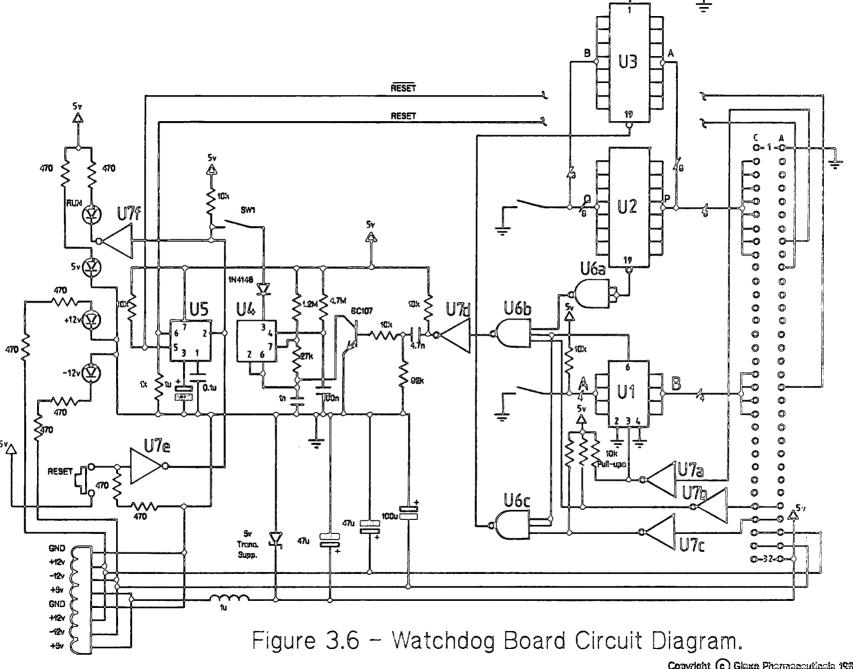

| 11     | 3.6 | Watchdog Board Circuit Diagram             | 45  |

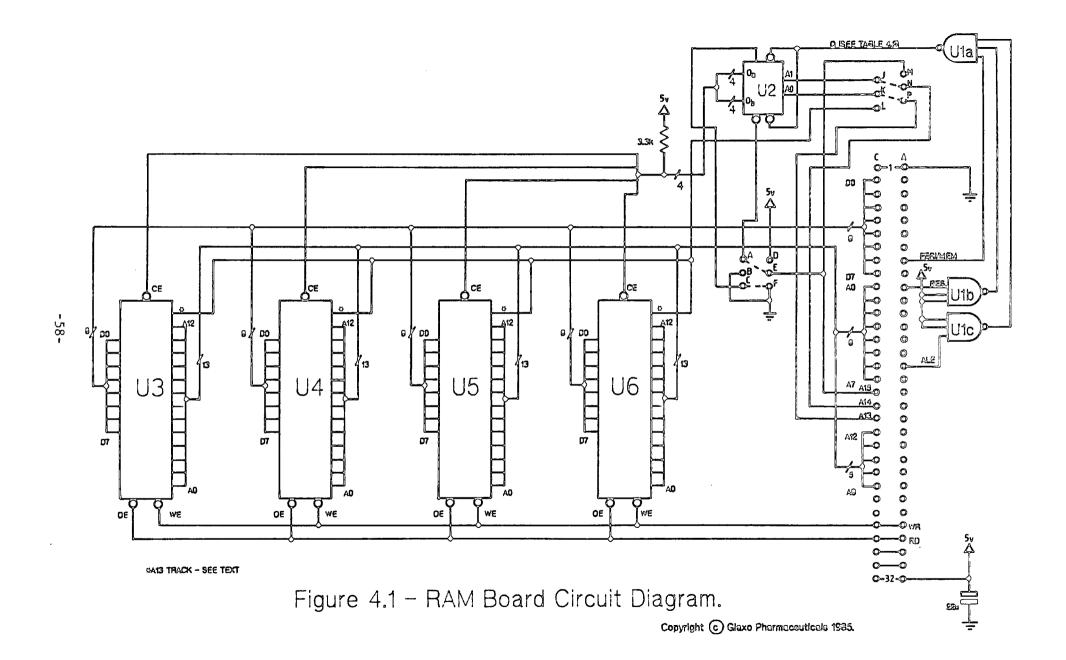

| 11     | 4.1 | RAM Board Circuit Diagram                  | 58  |

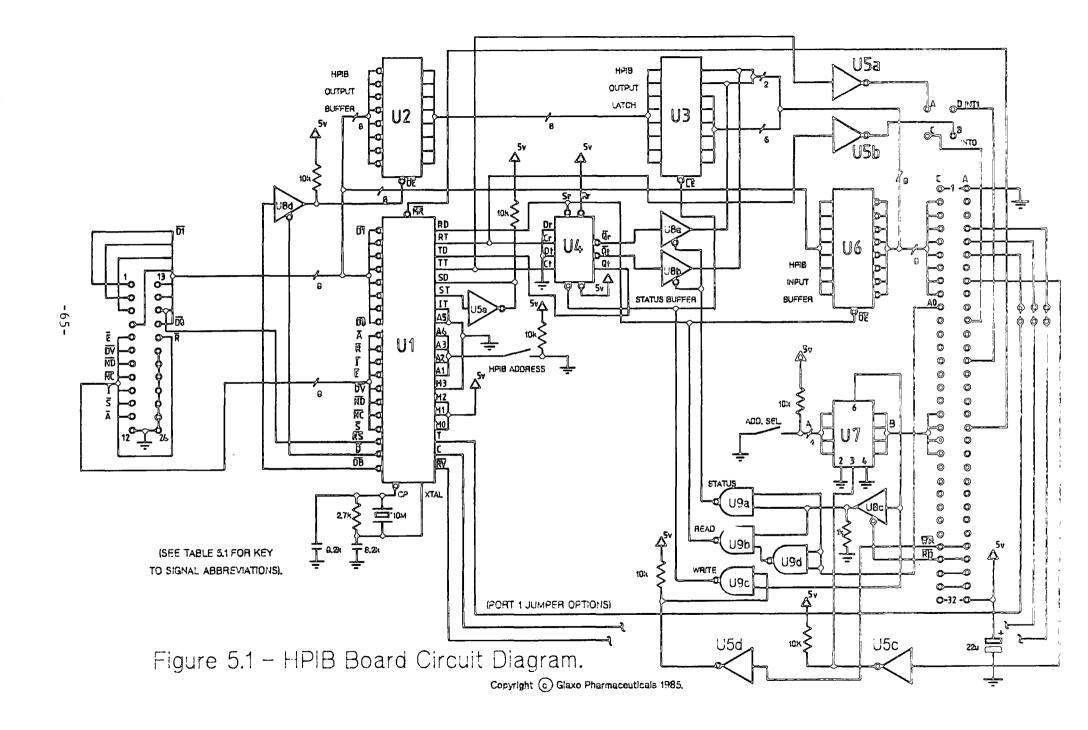

| 11     | 5.1 | HPIB Board Circuit Diagram                 | 65  |

| 11     | 5.2 | BCD Board Circuit Diagram                  | 72  |

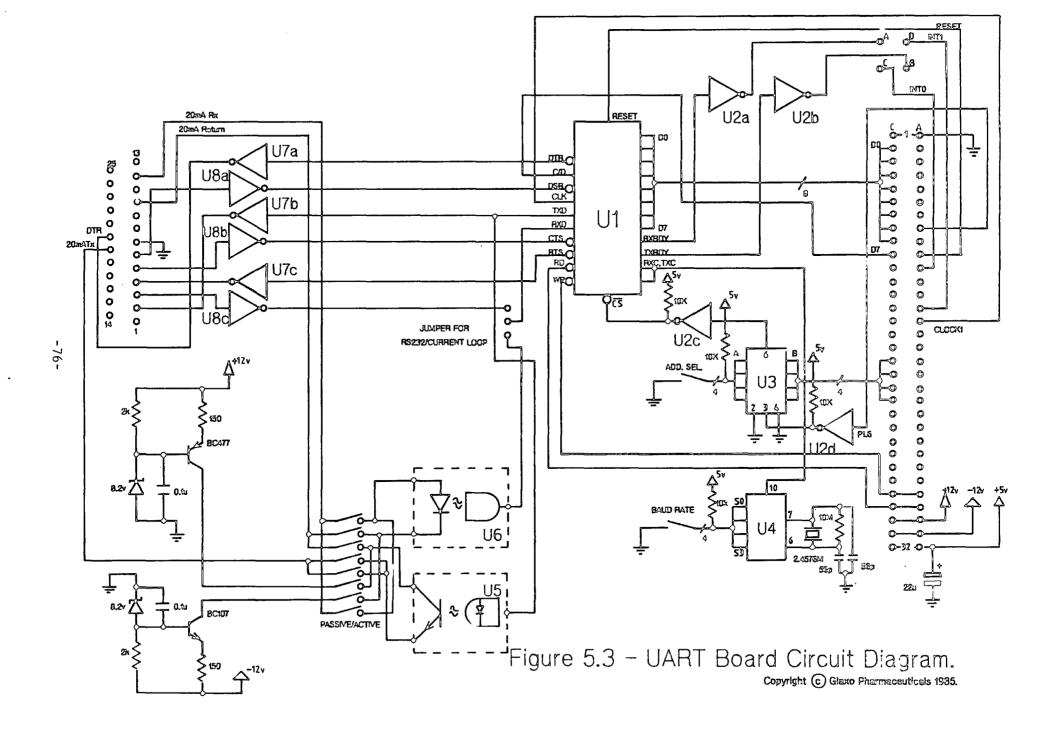

| 11     | 5.3 | UART Board Circuit Diagram                 | 76  |

| 11     | 5.4 | Schematic Diag. Showing HPIB Board Testing | 80  |

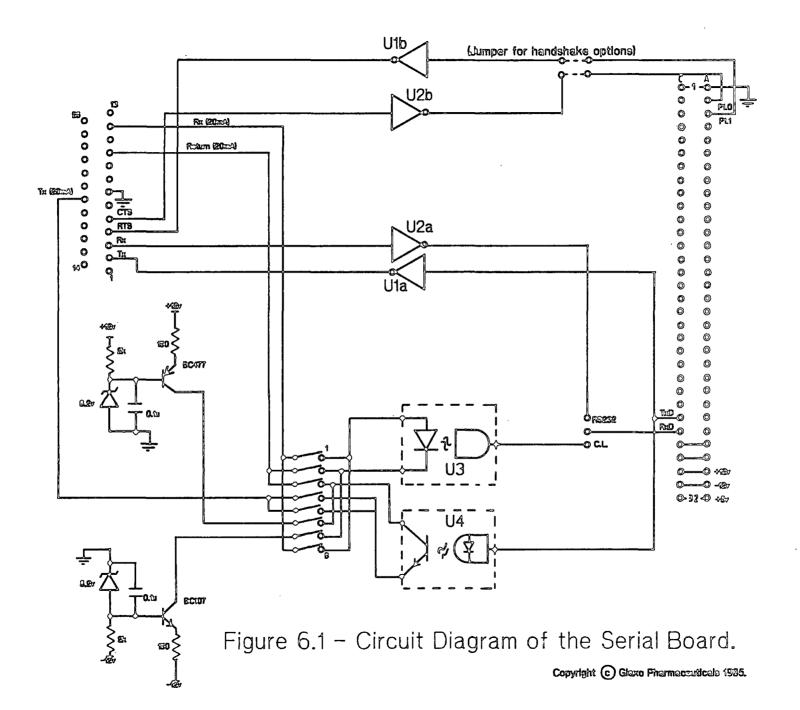

| TT.    | 6.1 | Serial Board Circuit Diagram               | 90  |

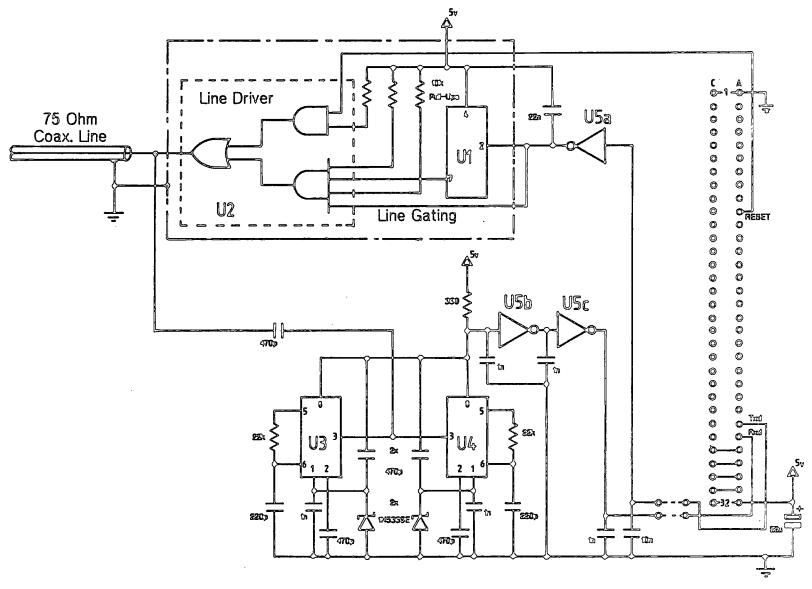

| 11     | 6.2 | R.F. Board Circuit Diagram                 | 95  |

| 11     | 6.3 | Schematic Diag. Showing R.F. Board Testing | 101 |

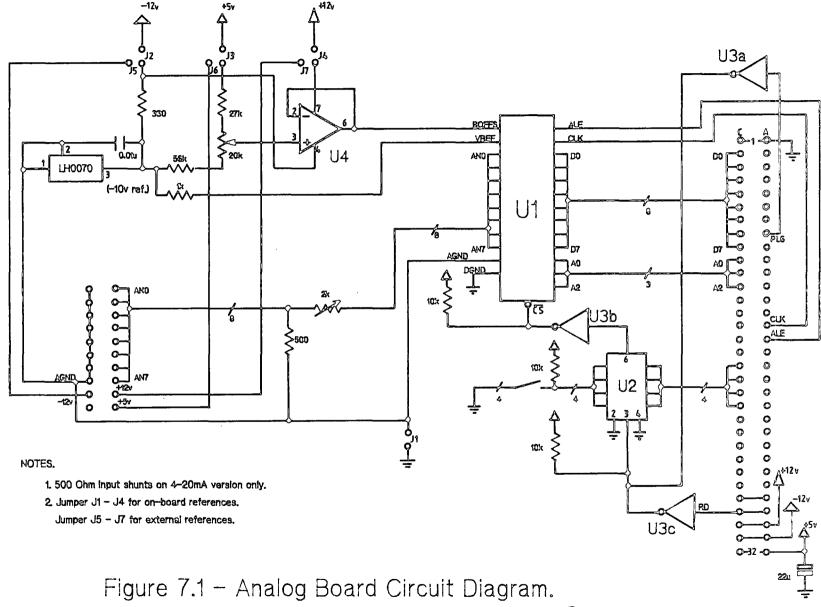

| 11     | 7.1 | Analogue Board Circuit Diagram             | 109 |

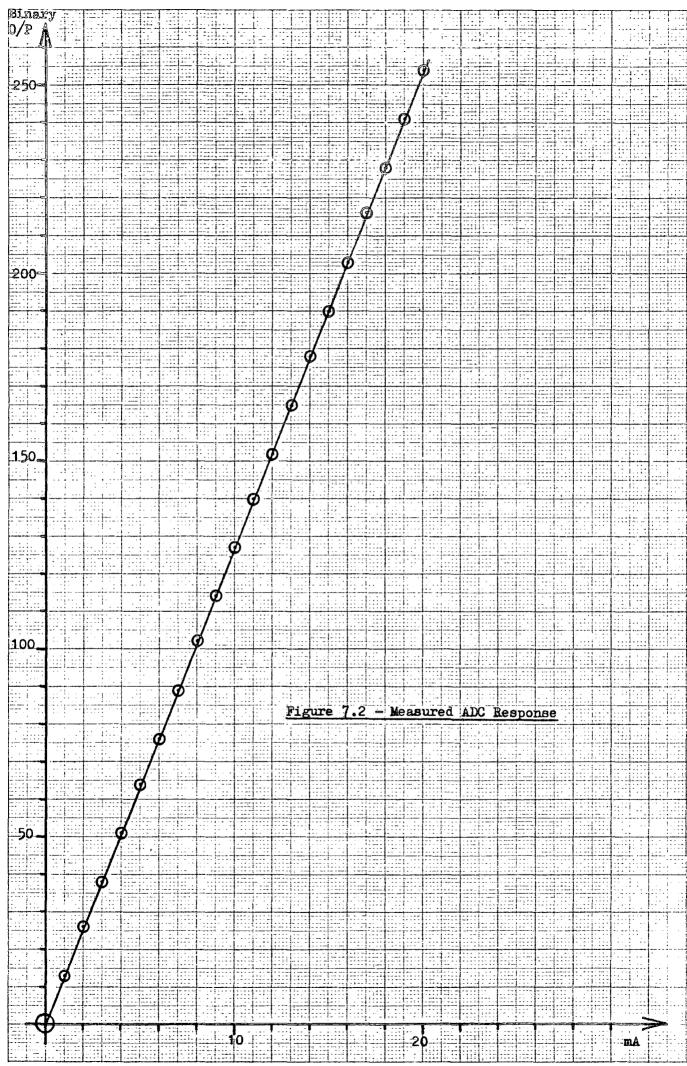

| 11     | 7.2 | Measured ADC Response                      | 110 |

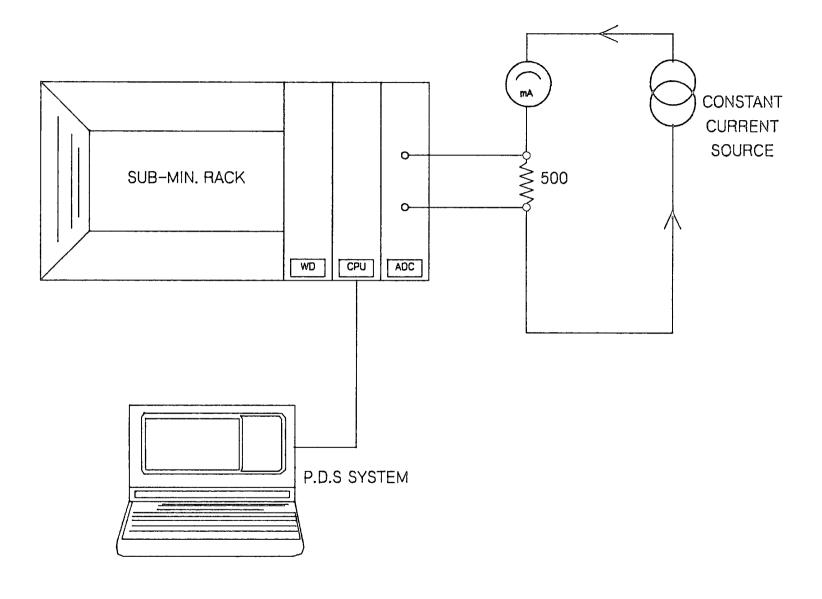

| It     | 7.3 | Test Rig for ADC Evaluation                | 111 |

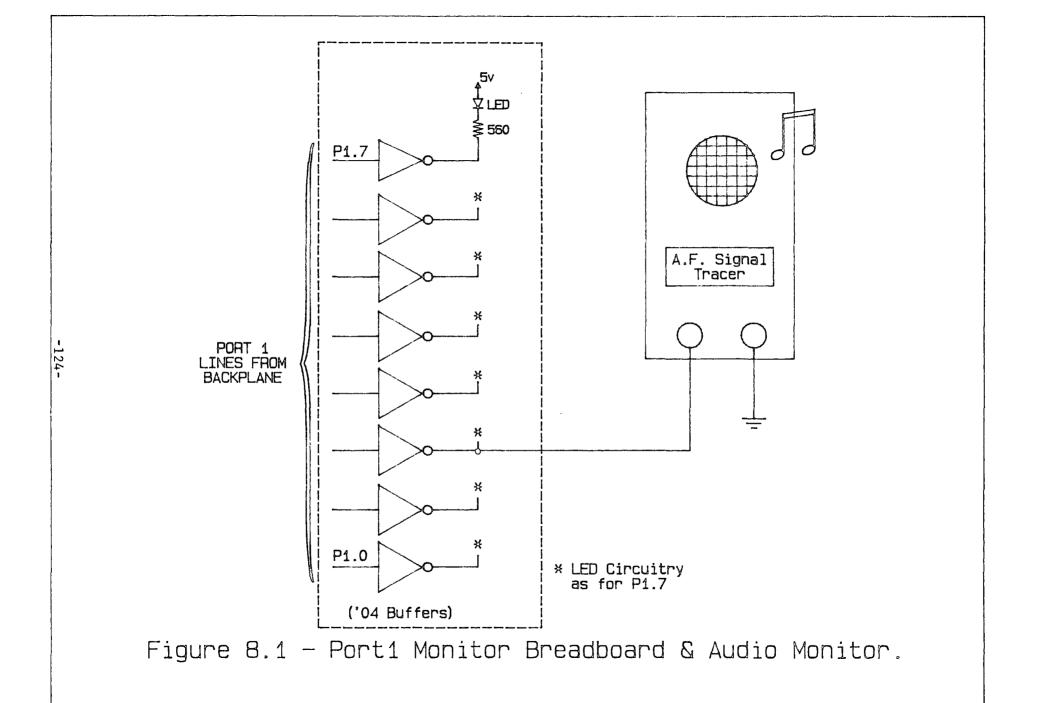

| 11     | Ω 1 | Port 1 Monitor Breadhoard & Audio Monitor  | 12/ |

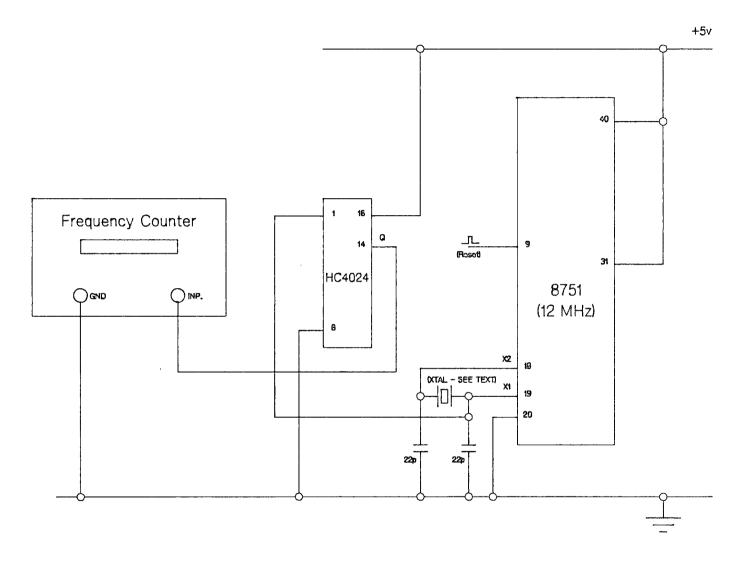

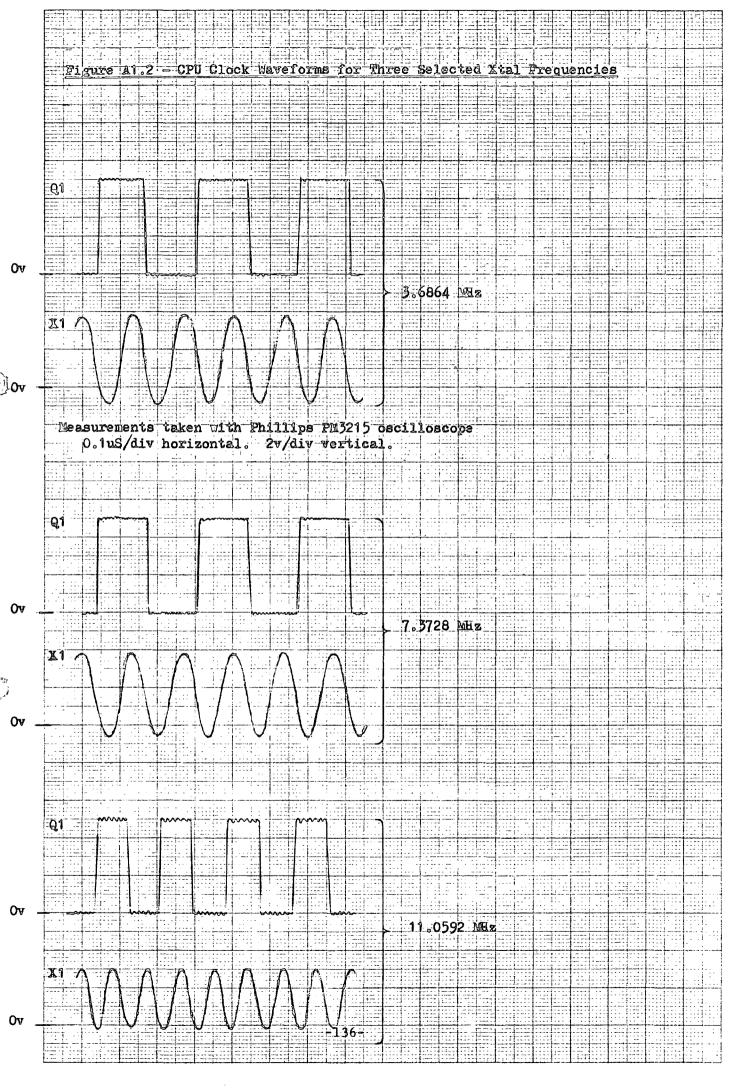

| Figure A | 1.1  | CPU Oscillator Tests                     | 135  |

|----------|------|------------------------------------------|------|

| " A      | 1.2  | CPU Clock Waveforms for 3 Selected Xtals | 136  |

| " A      | 2.1  | VCO Freq. Variation with Mod. Voltage    | 148  |

| " A      | 2.2  | Serial Data Waveforms                    | 150  |

| " A      | 2.3  | Flowchart of Polling Firmware            | 154  |

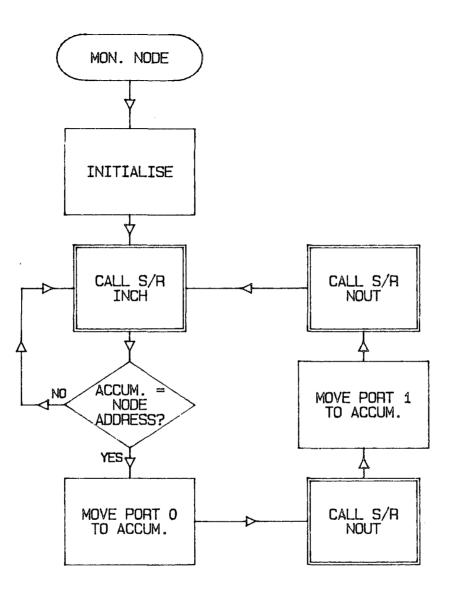

| " A      | 12.4 | " Monitoring Node Firmware               | 155  |

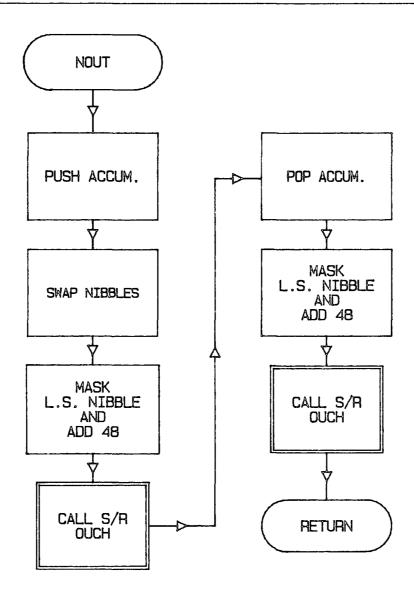

| " A      | 2.5  | " " Subroutine "NOUT"                    | 156  |

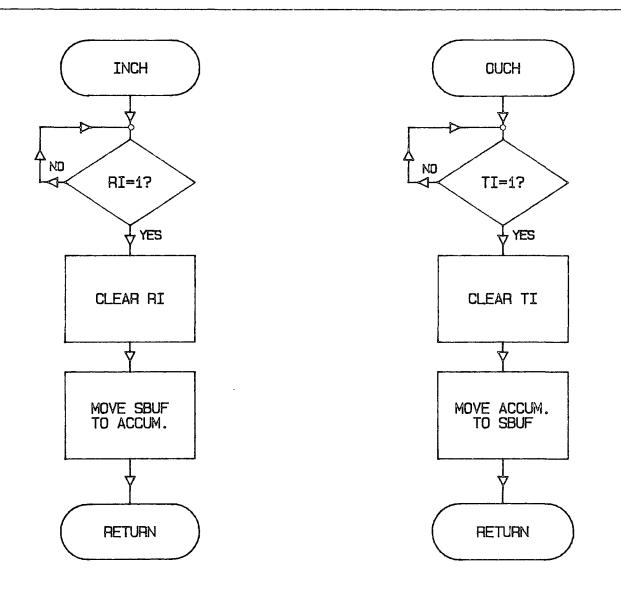

| " A      | .2.6 | " " Subroutines "INCH" & "OUCH"          | 157  |

| " A      | 4.1  | HPIB Schematic                           | 164  |

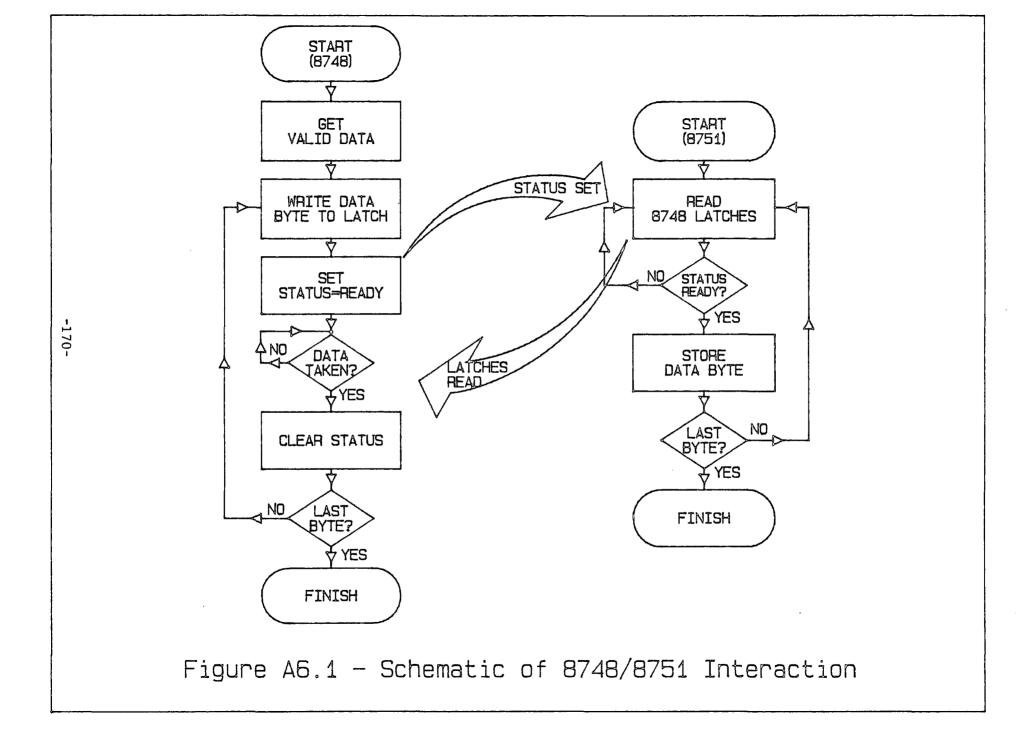

| " А      | 16.1 | Schematic of 8748/8751 Interaction       | 170  |

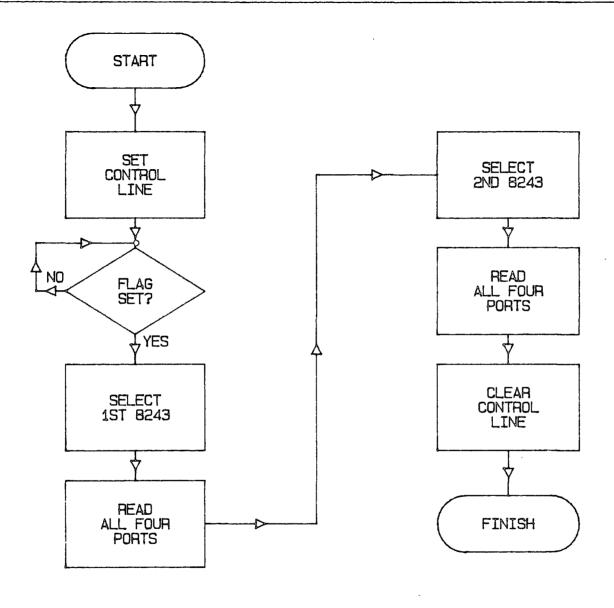

| " A      | 16.2 | "                                        | 171  |

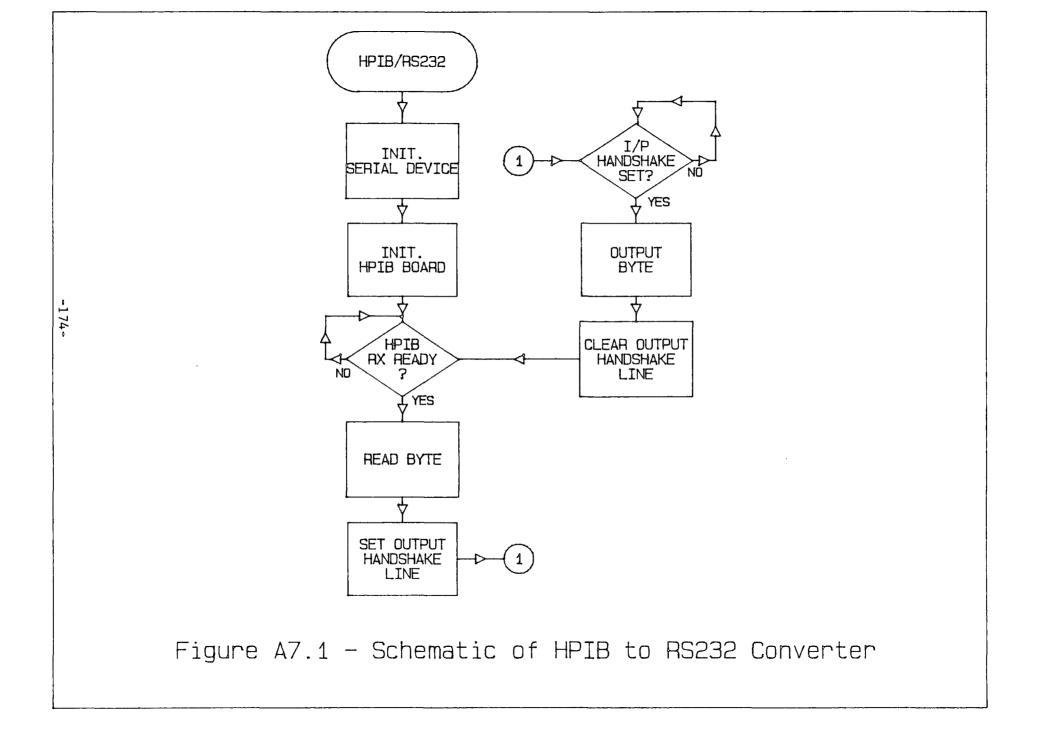

| " A      | 7.1  | " " HPIB to RS232 Converter              | 174  |

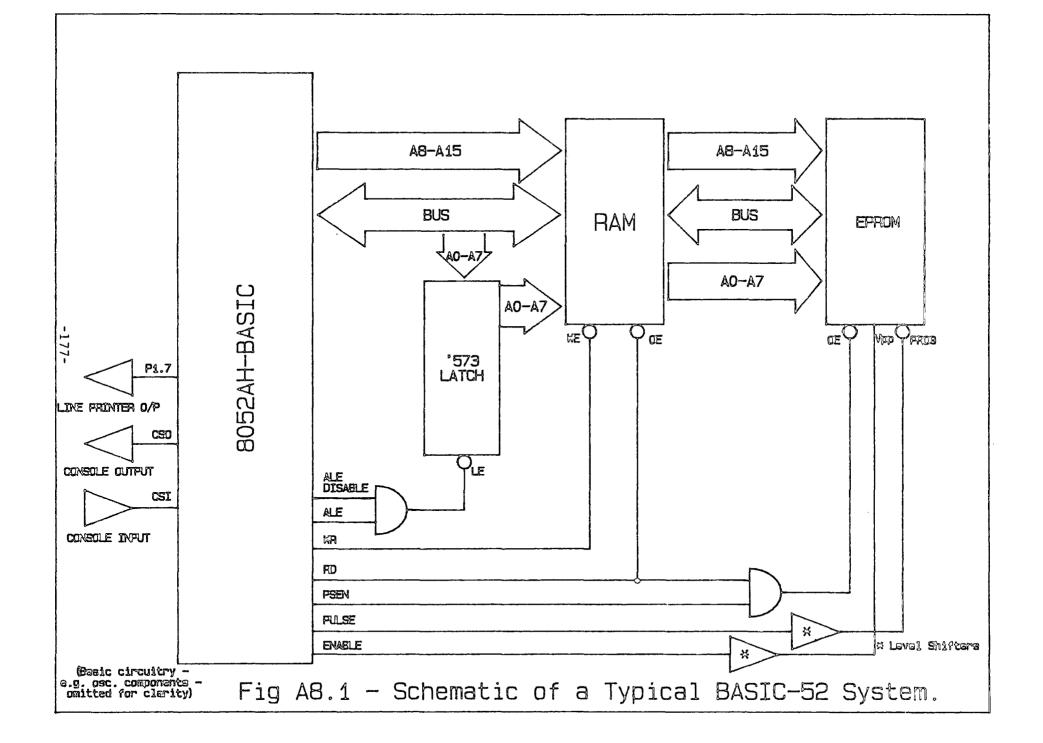

| " A      | 8.1  | " a Typical BASIC-52 System              | 177  |

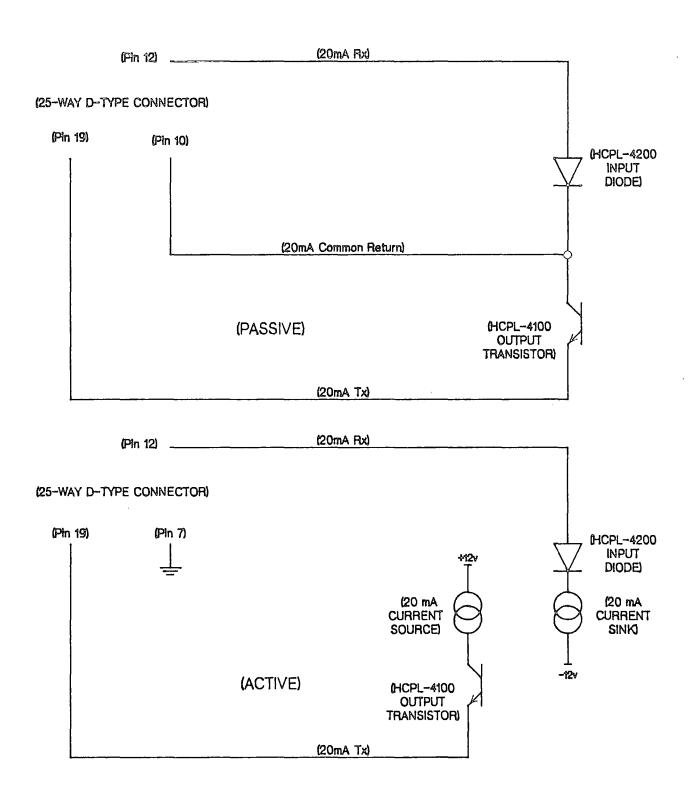

| " A      | 9.1  | Current Loop Configurations              | 183  |

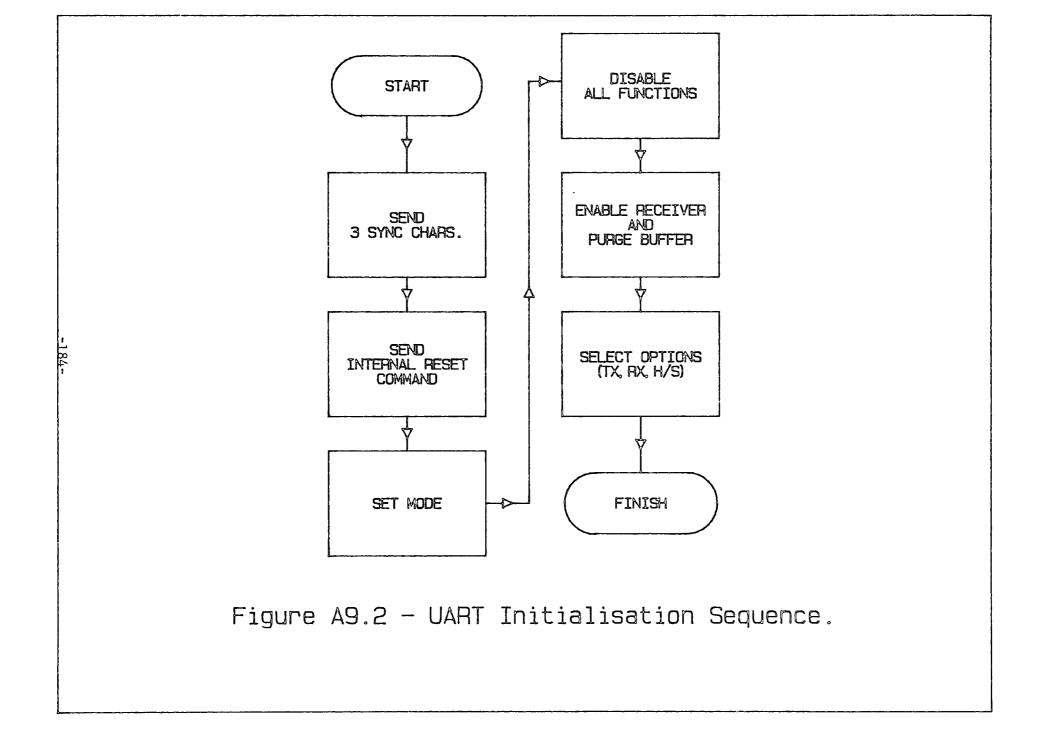

| " A      | 9.2  | UART Initialization Sequence             | 184  |

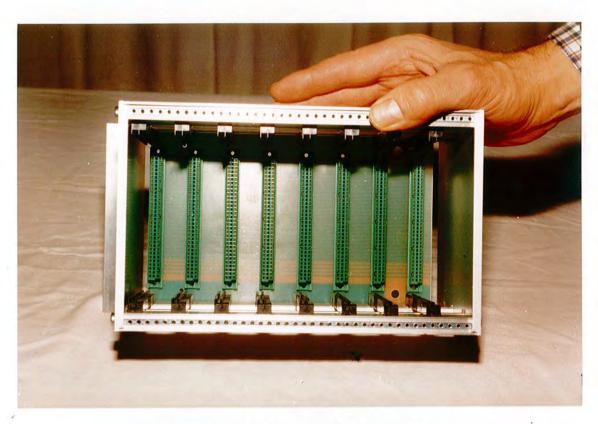

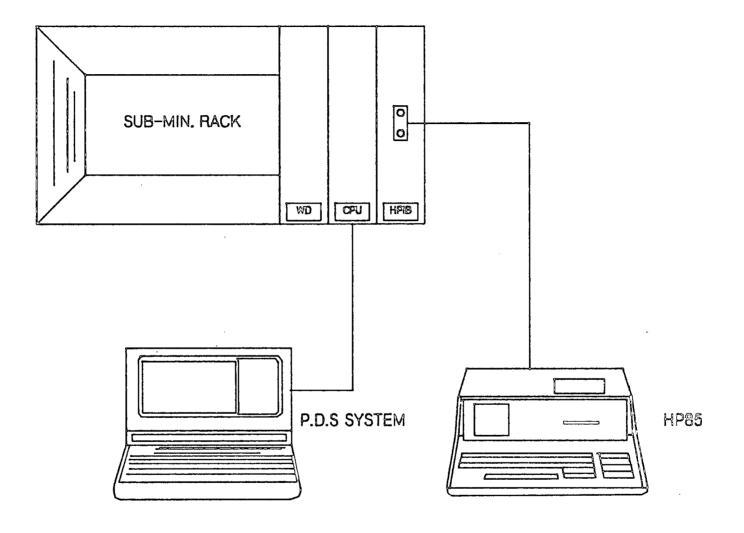

| Plate 3  | 3.1  | The Sub-Miniature Rack                   | 24   |

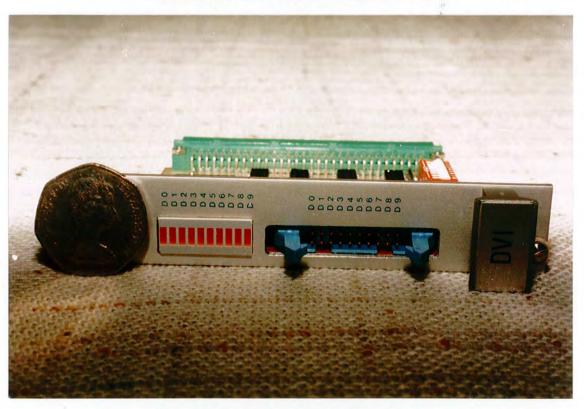

| " 3      | 3.2  | The DVI Board                            | 24   |

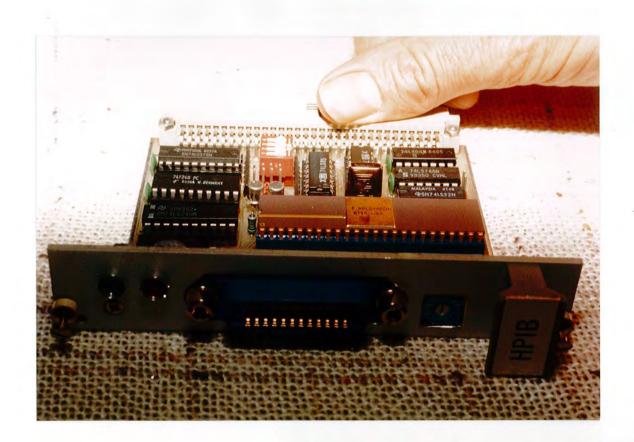

| " 5      | 5.1  | The HPIB "                               | 70   |

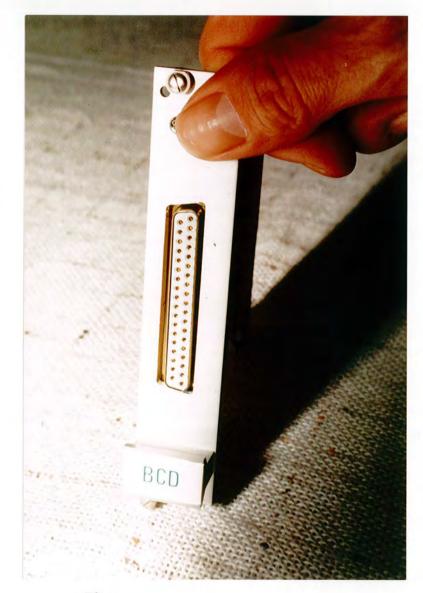

| " 5      | 5.2  | The BCD "                                | 70   |

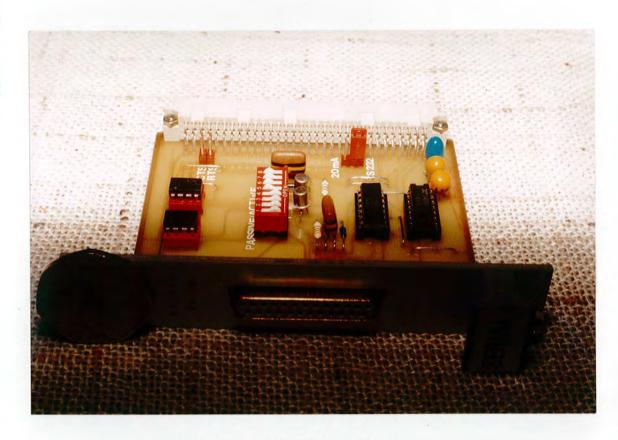

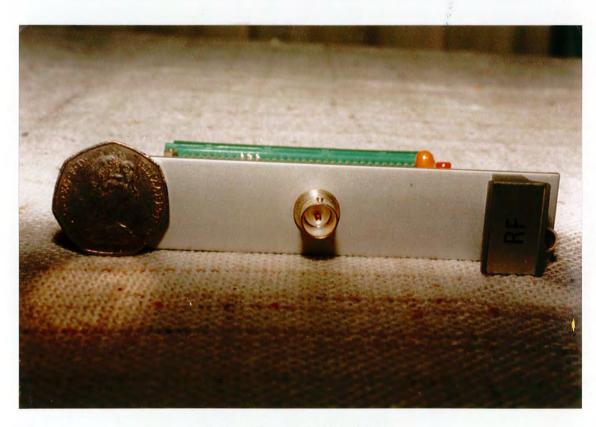

| " 6      | 5.1  | The Serial Board                         | 87   |

| " 6      | .2   | The R.F. Board                           | 87   |

| " 7      | .1   | The Analogue Board                       | 107  |

| " 8      | .1   | Alternative CPU Chips                    | 116  |

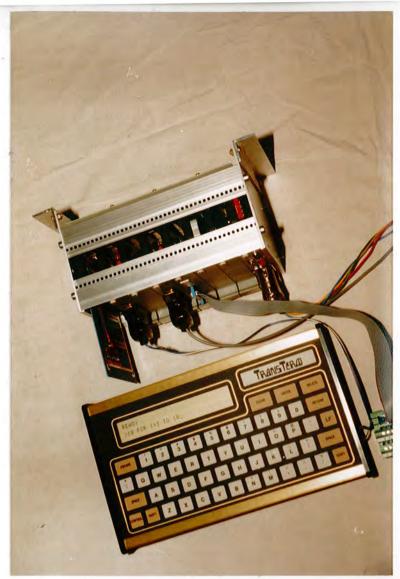

| " 8      | 3.2  | The 'BASIC' System Configuration         | 1.16 |

| " 8      | 3.3  | MCS BASIC-52 Running On the System       | 119  |

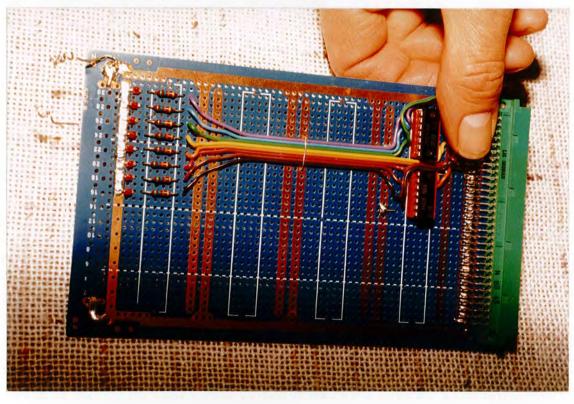

| " 8      | 3.4  | The Port 1 Monitor Breadboard            | 119  |

#### CHAPTER 1 - INTRODUCTION

As the world's population becomes increasingly dependent on manufactured goods, so the trend towards industrial automation in manufacturing industry becomes more dominant, and the demand for plant monitoring and control equipment increases. The introduction in the 1960's of minicomputers such as the D.E.C. PDP-8 into industrial applications greatly extended the scope for monitoring and control of industrial plant. For the first time a flexible controller, for example, could be realized; the hard-wired dedicated machines, often based on wired core storage technology, rapidly fell into disfavour. Purpose-built electronic devices began to be displaced by general purpose computer based units; traditional analog equipment was often superseded by digital hardware. The introduction of microprocessors in the 1970's, with the corresponding increase in the performance/cost figure, increased this trend towards computer-based line monitoring/control equipment.

The author, who has worked since the 1960's on monitoring/control projects, currently works for a large international company, dealing with problems relating to the various hardware/software aspects of the monitoring and control of industrial plant in the Company's U.K. sites. The Company, which has a heavy financial investment in both "mainframe" and microcomputers, has a logical policy of single source supply from a major American manufacturer. This policy, as well as being financially sensible as regards bulk purchase discounts etc., also has the advantage of avoiding familiar pitfalls of the multi-vendor situation. Thus, considering purchasing monitoring/control equipment to link, for example, sensors on a production line to a microcomputer, the natural first choice of supply was the approved computer manufacturer mentioned above, who is also a major manufacturer of laboratory instrumentation equipment.

As an aid to this general discussion on line monitoring, (for brevity we will adopt the term "line monitoring" as a convenient - though rather glib - phrase to reference all areas of the fields of monitoring and control of industrial mechanization) it is perhaps useful at this stage to catalogue the various factors relating to the choice of monitoring equipment. These are as follows:-

- \* Cost

- \* Single supply source

- \* Software/firmware programmable

- \* Versatile range of input/output options

- \* Good noise immunity

- \* Networkable

- \* Easily interfaced to computers

- \* Compact, rugged construction

- \* Ease of maintenance

Cost, of course, is often the overriding factor that governs the choice of any equipment to be purchased. If, as in this case, the equipment may be duplicated many times in different sites, the total capital expenditure over a period of time may be very large. Conversely, for small projects with tight budgets, the price/performance ratio for the equipment to be purchased will frequently determine the scope of the project, and may tip the balance between success or failure. Another factor which determines the successful outcome is the maintainability of the equipment - which can become a major problem in multi-vendor situations, as indicated earlier.

Digital or analogue signals that the monitoring equipment may need to process can be of many different types. For example, analogue signals may take the form of either currents in the range 4-20 milliamps or voltages in the range 0-10 volts. These are two commonly used conventions, although the analogue signals may not conform to either - e.g. thermocouple outputs. A similar situation also arises when digital signals are considered.

A common method of digital signalling (for example, the output of an industrial optical sensor) is to interrupt a closed current loop system; switching devices commonly encountered may be new technology solid-state devices, such as Hall Effect switches, or more traditional electrical hardware - e.g. relays or reed switches. Ideally, as well as supporting digital switching signals conforming to the standard industrial protocols, equipment should also have the ability to communicate with (possibly) remote computers or microprocessors. To achieve this communication, the equipment should be capable of supporting a number of interface protocols, such as RS232C, IEEE488 (HPIB), 20mA current loop and (preferably) a networking protocol - which would allow a number of monitoring "nodes" to be networked with a host computer.

For maximum versatility of application, monitoring systems should be software or "firmware" based (the latter term is generally used in connection with EPROM - as opposed to RAM - storage). This allows, possibly, the internal program to be replaced by another program, allowing the equipment to perform a different task. Another possibility is that the user may wish to vary program parameters, while keeping the basic program task the same. Such an occasion arises when a device is required to scan a different (or extra) channel or sequence of channels.

Perhaps the greatest single source of problems concerning purchased equipment is the possibility of error due to it's lack of resilience to the stresses imposed on it by the working environment - the major sources of stress frequently being mechanical vibration and electrical noise. "Noise" invariably takes the form of large mains born "spikes" (often, say, 40dB in excess of the signal levels inside the equipment), although electromagnetic induction can also cause problems. Manufacturers equipment, often demonstrated by sales staff in an office environment, can sometimes prove

disastrous in performance when sited on an industrial production line, next to heavy electrical machines. Mechanical stress can take the form of prolonged vibration, or sudden, perhaps violent, jolts. Thus equipment must be rugged, compact and generally mechanically sound. Additionally, it should preferably be constructed in a modular easily maintained manner (such as the standard Eurocard system - which also has the advantage of allowing incorporation into other manufacturers racking systems). A modular approach further extends the range of applications, as discussed later in this introduction, and it also means that spare modules can be held on-site, whilst a complete integrated unit may be prohibitively expensive to hold in stock.

Having considered all these factors outlined above, the Company examined the market for potential suppliers, the first choice being the approved manufacturer, mentioned earlier. A limited range of equipment was available, but it was prohibitively expensive, and required an external controller in the form of a desk-top type microprocessor. A networking system was available, but this was again very expensive, and failed to work when demonstrated. Thus the Company began to look elsewhere for sources of supply.

Several companies were able to offer systems that partly fulfilled the requirements outlined above - a considerable number of companies are in the process control/industrial automation market, offering expensive and inflexible "turnkey" systems. The products of a smaller number of firms who manufacture rack based interface systems (typically "Eurocard" based) offering a (limited) range of plug-in options were examined, but the systems offered were either biased towards "low noise" environments or lacked the required networking capability. A possible hybrid system was considered - that is to say that it was envisaged that the total equipment could originate from two independent suppliers, the interface equipment

being supplied from one source and the networking equipment from another. However, apart from defaulting on the single-source requirements, it did not prove to be a viable alternative economically. Those networking systems that possessed good noise immunity were, inevitably, amongst the most expensive available.

Faced with the possibility of having to purchase multi-sourced expensive equipment lacking some of the features required, the Company then considered the possibility of developing it's own; although the Company lacked the facilities to manufacturer in quantity it's own equipment, it was felt that if a prototype design could be developed and proven in a pilot scheme, then the equipment could then be manufactured by an external contractor. The author was approached to develop the prototype equipment for the pilot scheme, which is described in the next chapter. The thesis proceeds, in further chapters, to narrate how the full Distributed Interfacing System was developed from this successful initial scheme.

#### CHAPTER 2 - THE PILOT SCHEME

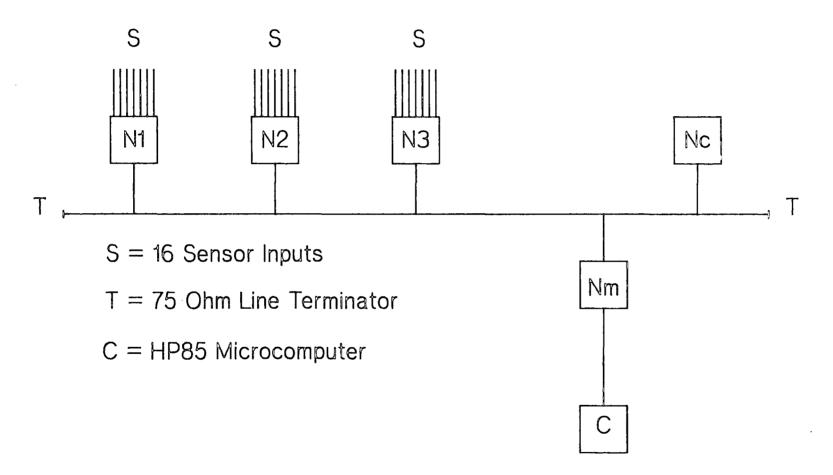

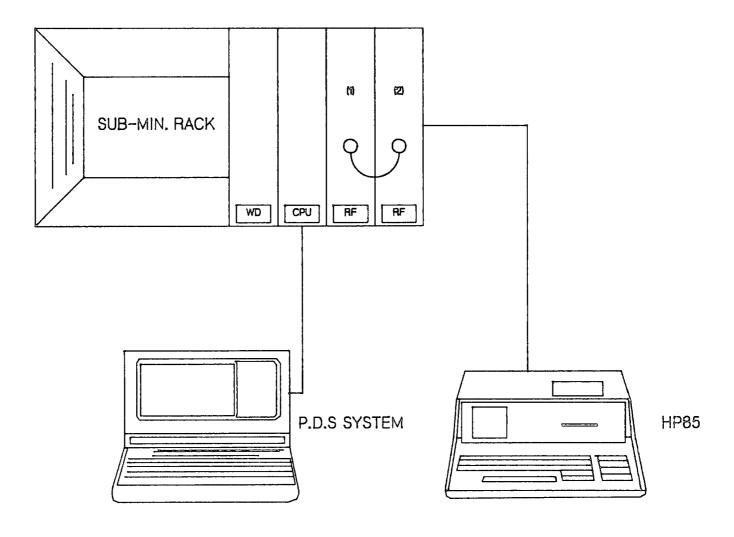

The initial scheme chosen to test the viability of a subset of the proposed hardware was a three 'node' system used to monitor an ageing production line in one of the Company's North of England sites, the aim of the scheme being to pin-point troublesome areas within the line by recording fault indications. A distributed system was preferred to a centralized system, in order to minimize cabling to sensors, thus saving installation effort, and reducing the risk of noise pick-up. A schematic diagram is shown in Figure 2.1. The three nodes are represented N1 - N3, a fourth node (Nc) is also shown - this being the 'controller', as explained later; a microprocessor node (Nm) connects an HP-85 (Hewlett-Packard desk-top computer) to the system. Standard M-70 75 Ohm coaxial cable was used as the interconnecting medium, for economy.

### 2.1. The 8751 Single Chip Microprocessor

To minimize size and to keep printed circuit board (PCB) layouts simple, a decision was taken to base the circuit design of the node hardware around a 'single chip' microprocessor. Such a device contains the central processing unit (CPU), memory - typically erasable programmable read only memory (EPROM) and some random access memory (RAM) - and input/output hardware, in a single package. Several such devices were at that time available, but the chip selected, the Intel 8751, was unique in that it featured an on-board full duplex UART (Universal Asynchronous Receiver Transmitter). Table 2.1. below lists the major features of the device. Reference 1 contains a full description of the MCS-51 family, of which the 8751 is a member.

Figure 2.1 Pilot Scheme - Schematic

- \* Eight-Bit CPU with hardware mult./div

- \* Four Eight-Bit I/O ports

- \* 4K Bytes of EPROM

- \* 128 Bytes of RAM

- \* Full Duplex UART

- \* Boolean processor

- \* Two Sixteen-bit Timers

- \* Multiplexed Sixteen-bit Address/Data Bus

# TABLE 2.1. - The Major Features of the Intel 8751 Microprocessor

For the pilot scheme, the full capability of the chip was not exploited. The eight-bit internal architecture was considered adequate, as was the number of input/output ports; indeed only two of the ports were used for data transfer, as we shall see later in the chapter. (Chapter 3 gives details of the 8751 facilities not relevant to this chapter, and also provides a pin-out diagram - Figure 3.1.).

The UART was of immeasurable value to the author in the early 'breadboard' stages of the design work, as it allowed the connection of serial devices (e.g. computers, printers, visual display units [VDU's]) as test units. However, the fact that the UART is an integral part of the 8751 does have its disadvantages - mainly because the UART is timed from the microprocessor's on-board oscillator (master clock), which is referenced to an external crystal. Appendix 1 discusses in detail aspects of the oscillator circuitry and lists the baud rates available from the 3.6864 MHz and 7.3728 MHz crystals. Early versions of the 8751 were available with a maximum clock frequency of 8 MHz, effectively limiting the clock frequency to a maximum value of 7.3728 MHz.

The author had some in-depth discussions with the Intel support staff as regards the preference of oscillator components (discussed more fully in Appendix 1). The accuracy of the serial data timing is wholly dependent on the stability of the clock circuitry; Intel's recommendation of the use of the on-chip Pierce oscillator with the minimum of external circuits led to the requirement of purchasing crystals quoted for parallel resonance. These were obtainable 'off the shelf' from component suppliers for the 3.6864 Mhz frequency, and therefore this was selected as the operating frequency for the hardware described in this chapter. The need for special clock frequencies (and non-standard crystals) is a disadvantage the 8751 incurs by supporting the on-board serial facilities. Another disadvantage is the implied inability to 'hesitate' the CPU clock - a matter discussed in Chapter 3.

Other features of the 8751 listed in Table 1, although of great value in pursuing development work (described in the later chapters of this thesis), were not exploited in the preliminary work.

# 2.2. <u>Design Criteria (node units)</u>

Having thus selected a suitable intelligent device around which to base the design, the author then turned to the problem of isolating the total design requirements, i.e. determining the design 'goals'. These are summarized in Table 2.2. below:

- \* Sixteen opto-isolated inputs per node

- \* Single 5v supply

- \* High noise immunity

- \* Serial half-duplex data transmission

- \* Minimal cost

- \* Minimal software/firmware

- \* Simple PCB artworks

- \* Watchdog on-board

- \* Rapid development

### TABLE 2.2. - Design goals for initial development work

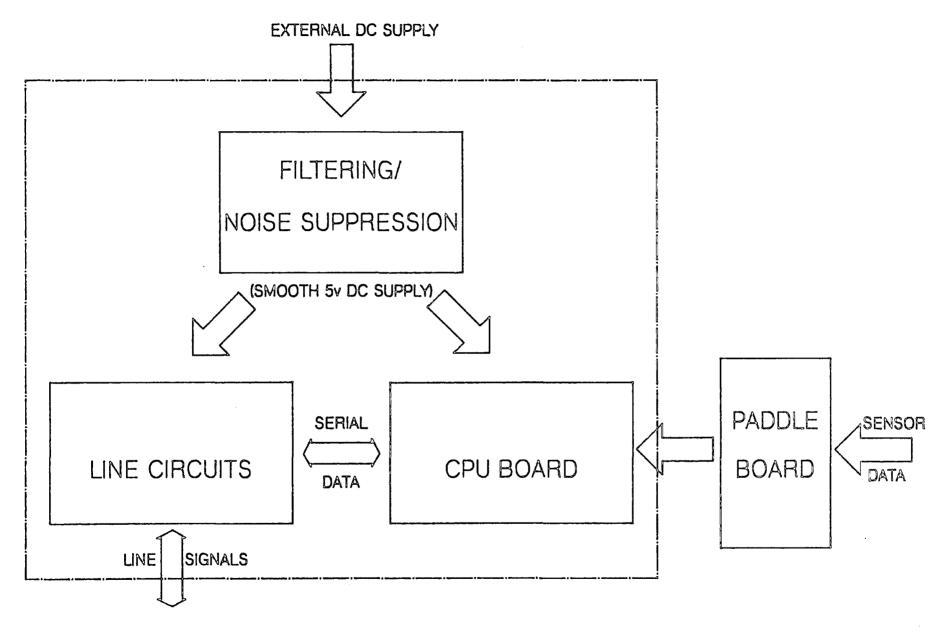

Figure 2.2 - Power Supplies.

Figure 2.3 - Schematic Diagram of a Node.

The rest of this chapter narrates the author's attempts to meet these design goals for the trial system, and summarizes the achievements and the lessons learnt. The Thesis continues, in the subsequent chapters, to outline the development of the complete Distributed Interfacing System.

# 2.3. Power supplies

Great attention was paid from the early stages onwards, to the elimination of noise 'spikes' from the electronics. As stated earlier, the transients may be either induced or mains-born - in the latter case most of the transients may be eliminated by a conventional commercial mains filter, although such a filter may prove to be incapable of eliminating completely the largest spikes.

The technique adopted in this prototype system was to filter the mains supply as described, using a Belling-Lee (model L2140/2L) mains filter, before converting to 5v DC using an inexpensive (Farnell D5-05A) sub-miniature power supply (see Figure 2.2.) - and then to attenuate the remaining transients to an acceptable level. Figure 2.3. shows the schematic diagram for each (nl, n2, n3) node; the power (5v supply) arrives on the board at a central location, where it is further smoothed by series RF chokes, a large (100 micro-Farad) reservoir capacitor, and finally a solid-state transient suppressor. It is then fed from this central point to the various circuits in the node. Most of the circuitry of the prototype nodes was located on the main printed circuit board (PCB), with the 8751 CPU and its associated oscillator and reset circuits located on a small 'Piggy-back' PCB.

### 2.4. Line circuits

The need to transmit a serial data stream over long distances (several hundred metres) in an electrically hostile environment requires more than a simple amplitude modulation system such as, say, RS232 or TTL with line drivers. The commercially available option that springs immediately to mind is the modem; the essence of this device is to generate one of two basic frequencies according to the logic state of the incoming (TTL) signal - i.e., two-state frequency modulation (FM). At the receiving end of the transmission line the signal is demodulated (hence the name, MODulator-DEModulator), typically by a phase-locked-loop (PLL), to recover the original TTL signal.

To design a miniature modem is not a difficult task, as several suitable PLL's are available, the most commonly used being the Signetics NE565. This chip has two disadvantages, firstly it requires a dual voltage power supply, and, secondly, it is inefficiently packaged. A suitable alternative is the NE567, an 8-pin device requiring only a single 5-volt supply. This chip is frequently used as a tone decoder, but has sufficient bandwidth to decode serial data transmitted at rates of the order of 10 kilobaud.

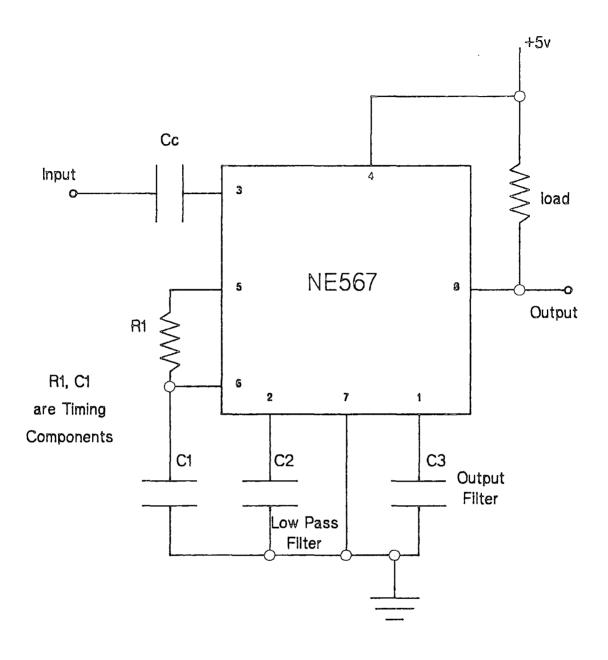

The 567 has an open collector output; the output transistor is driven into saturation whenever a tone of the correct frequency is present at the input. Figure 2.4. shows the 567 in its usual use as a PLL; the resistor-capacitor combination

Figure 2.4 - The NE567 configured

As a Phase Locked Loop.

determines the centre frequency, while external capacitors adjust the loop capture range and the output filter response. With a suitable pull-up, the output is TTL compatible. The output is then at logic '1' state when the loop is idle, and at logic '0' when locked onto a tone of the correct frequency. Thus if we consider a transmission system that 'tone-bursts' on logic '0's only, then clearly a '567 can decode the incoming signal into a form immediately presentable to the serial input of an 8751 microprocessor. This is the basis of the transmission system implemented.

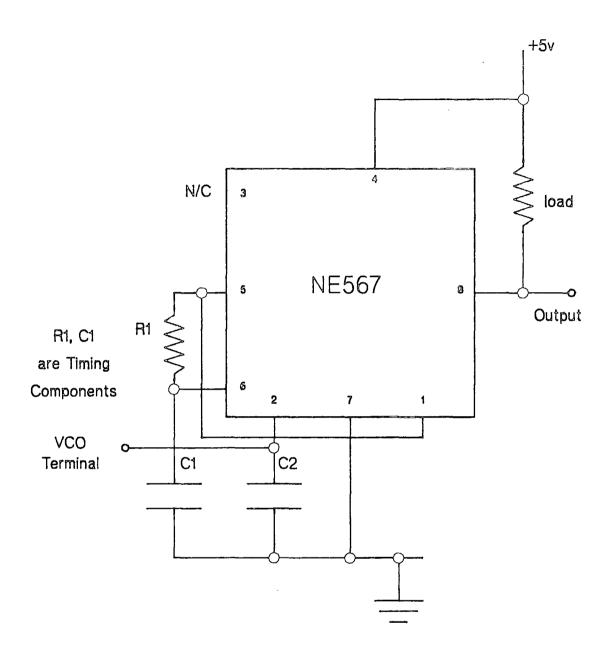

The 567 is a versatile chip enabling, for example, the independent use of the on-board voltage controlled oscillator (VCO) for other purposes. This versatility permitted the use of the VCO as an inexpensive tone burst generator, thus allowing the same type of chip to be used as both the encoder and decoder of the line signals. Figure 2.5. shows the basic VCO circuit, which together with the PLL circuit originates from the Signetics application notes (Ref. 2). These circuits configured for a centre frequency of approximately 200 KHz (See Appendix 2) are incorporated unmodified (excepting the addition of supply trimming potentiometers) into the circuit shown in Figure 2.6. The buffered serial data stream is used to pulse the oscillator and generate the logic 'O' tone bursts.

The output of the VCO is a pulsed 200KHz square wave, which is TTL compatible, and can be buffered by a conventional TTL line driver, in this case the Texas 75123. The 75123 is used to drive a 750hm coaxial line, terminated at the characteristic impedance. The serial data stream is also used to gate the

line driver, floating it's open-emitter output on logic '1's the normal state for an idle transmitter - and allowing other

nodes to transmit.

The line receiver circuit is the 567 configured as a PLL, as already described. The minimum values for the two external capacitors (input/output filters) were calculated from the formulae supplied with the Signetics application notes, and were found to give the best performance for noise rejection. Note that the PLL is used to detect tone bursts that occur during the periods corresponding to logic zeros in the original TTL signal; when the '567 detects a tone burst its output is driven LOW. The external pull-up guarantees the logic one state during the absence of the tone-bursts, which of course includes the line idle condition.

#### 2.5. CPU sub-board

The 8751 CPU and its associated reset and oscillator circuitry, together with connectors etc., were mounted on a miniature pre-prepared PCB sub-board, which the author designed for earlier 'breadboard' tests on the 8751. The use of this item as a circuit component eased the development task. sub-board was mounted on the main PCB by means of short 'stand-offs', both boards being enclosed within a small die-cast box. The sub-board's 20-way connector allowed a ribbon cable connection to an external 'D' socket mounted on the lid of the box. This enabled data input from the opto-isolating 'paddle board' (see below) to be routed to the microprocessor input ports. Only two of the three general purpose ports were used on these prototype nodes as input

Figure 2.5 - The NE567 configured As a Voltage Controlled Oscillator.

Figure 2.6 - Circuit Diagram of a Node.

ports, the sixteen input lines offered by each node being more than adequate for the pilot scheme.

#### 2.6. Watchdog

Also featured in Figure 2.6. is a 'watchdog' circuit, a retriggerable monostable circuit as found in standard References (Ref. 24). The watchdog is retriggered by pulses from the 8751's serial port; it has a decay time of 500 milliseconds before expiring and pulsing the reset line. Thus, provided the node responds to 'polling' (see below), the watchdog remains in a quiescent state. A watchdog circuit is applications, essential in industrial to recover situations where the internal registers (e.g. the program counter) within the CPU have been corrupted. Such a situation can occur, for example, as the result of a mains 'brown-out'.

#### 2.7. Opto-input board

This small externally mounted 'paddle board' was used to isolate the sensor input signals (0/20mA) from the CPU input ports, for noise rejection and CPU protection purposes. Four Litronix quad opto-isolator packages were used for compactness. The paddle board PCB featured a row of rigid wire posts, which allowed mechanical connection to a row of DIN rail mounted Klippon connectors. These screw-type block terminals were used to terminate input sensor signal lines.

### 2.8. Node firmware

Descriptions of the firmware for the various nodes are included in Appendix 2. A brief outline only is given here.

#### 2.8.1. Sensor node firmware

A sensor node consists of the complete circuit of Figure 2.3. above. The firmware (that is, the program held in EPROM) is identical for each node (n1, n2, n3) with the exception of one byte of EPROM containing the node number - 1,2 or 3. Each node compares this node number with the controlling node's current polling character, and if a match is found it then transmits four ASCII bytes, the least significant four bits of each byte corresponding to the nibble present at the input to each quad isolator on the paddle board. Because the characters transmitted are ASCII printing characters, and the polling characters are pure binary non-printing characters, the two types of transmission are easily distinguished.

### 2.8.2. Controlling node firmware

The controlling or polling node is simply a device for continuously transmitting the node polling sequence; although it does not require the receiver circuits of the sensor nodes, it was constructed using the same PCB, with the PLL chip omitted. The firmware consists of a loop of code which outputs the binary sequence 8,7,..2,1 (a maximum of eight sensor nodes were allowed for, three being used initially), with a delay between each transmitted character of sufficient duration to allow the polled node to respond with the four ASCII characters described above. Thus the system is seen to be simple T.D.M. (Time Division Multiplexing).

#### 2.8.3. Monitoring node software

The monitoring node uses the PLL receiver part of node hardware shown in Figure 2.6. The CPU (and paddle board) are not required, the serial data stream being fed directly to an HP85 serial interface, configured for TTL. A transmission rate of 9600 baud was utilized. The simple software written for the HP85 by the author was sufficient to prove the system. It consisted of a small program written in BASIC, which displayed the state of the sensors connected to system as three rows of sixteen noughts or ones on the screen of the HP85.

# 2.9. Noise tests

During the development the system was tested for noise immunity by deliberately injecting noise signals into the power lines and saturating the boards with EM radiation. The most sensitive parts of the circuitry were found to be the TTL serial data lines. Excellent results were obtained simply by decoupling the lines with optimum value capacitors. Not surprisingly, the die cast box eliminated the pickup of EM radiation. The box, paddle board and power supply were all mounted in a standard (earthed) metal industrial enclosure when installed on site.

#### 2.10. Review

Several useful lessons were learnt from the pilot scheme. The RF (radio frequency) transmission system worked well. The site engineers were able to run the coaxial cable (the HP85 was sited remote from the line being monitored) through the same ducting used for the fluorescent lighting circuits without

problems occurring with data transmission. It was found necessary to trim the VCO frequency, using the supply trim potentiometer, to the mid-range of the PLL pass-band, to allow for drift due to temperature variations. Clearly a stable crystal oscillator to replace the 567 VCO would be an improvement. The die cast box was not considered a convenient enclosure, as it made access to the boards difficult. The unit was not sufficiently versatile - it could not process commonly encountered analog signals, nor interface standard communications devices such as hand-held terminals.

Despite the criticisms above, the system has performed a useful function for two years with only one malfunction - a dry joint on a PCB. The author's simple demonstration software has been replaced by an elegant software package written by software specialists within the Company's Computer Services Department, which provides statistical printouts and logging facilities on disc files.

After completing the pilot scheme, the author was asked to continue the development of the system into a versatile interfacing system. How this was progressed is discussed in the following chapters.

#### CHAPTER 3 - THE EXPANDED SYSTEM

The dilemma the author encountered in attempting to expand the system is known in Literature (Ref. 4) as Parkinson's Third Law, and is stated formally thus: 'Expansion means complexity, and complexity decay'. The inevitable increase in size and complexity is the price to be paid for increased flexibility. It was decided to aim at keeping the total unit size as small as possible whilst still retaining flexibility as a major requirement - though these two conflicting requirements, compactness and versatility, created problems from the outset. How, for instance, could the system have the versatility and power of a typical modular Eurocard system yet be compact enough to be accommodated in a standard wall mounting industrial enclosure? - the most common type in use on the Company's sites has an internal depth of only fourteen centimetres.

A decision was taken to split the existing design into four separate small boards; the average chip-count per board would then for the most part dictate the final board size. The principal board in this initial set was of course the CPU board, the other boards being the Watchdog/power input board, the RF board, and DVI board (digital voltage input). All these boards are described in detail below - with the exception of the RF board, which is covered in Chapter 6. We will examine first the choice of the mechanical components for the system - the racking system, the backplane, the connectors and other related components.

#### 3.1. The Eurocard Sub-rack

A local contractor with past associations with the Company was selected to produce the emerging prototype system in small quantities for evaluation. The major function of the Contractor (see Acknowledgements), was to perform assembly work - both electrical and mechanical. As the Contractor already

Plate 3.1. - The Sub-miniature Rack

Plate 3.2. - The DVI Board

held stock items of components for other customer's systems, it was pertinent to consult with the Contractor's staff throughout the design exercise as regards circuit components, to aim for a design that would take full advantage of bulk purchase. The Schroff Eurocard racking system (Ref. 29) is a particularly well-designed versatile and compact system, with a professional appearance and low cost. This was one of the rack systems stocked by the Contractor.

Another racking system held in stock and also considered was the ISEP system, and in fact, trial assemblies of sub-racks were made using both the ISEP and Schroff parts comparison), but the Schroff system was found to adapt easiest to the shallow depth required. Moreover, the ISEP system was heavier and less elegant in appearance. The Schroff system was therefore selected for the implementation of the sub-rack hardware. Plate 3.1. shows a photograph of an assembled sub-rack. Although most Eurocard racking systems use a standard nineteen inch card frame, the Schroff system allows the user to assemble an eight-inch frame, which is ample for most purposes. Again, although the normal depth for a Eurocard is 160 centimetres, the side plate pressings allow for the long Eurocard, or in our case the half-depth Eurocard (80 mm.). As the card fronts fitted are one inch wide, the sub-rack capacity is eight cards (using an eight-inch rack), as can be seen from the photograph.

The backplane used in the prototypes was again a stock part from the sub-contractors, a simple printed circuit board designed to accept standard Eurocard DIN connectors with rows

'A' and 'C' fully pinned (32 pins each rows) and row 'B' omitted.

Figure 3.1. shows the signal names assigned to the pins.

```

С

Α

o--1-o GROUND

port 0.0 o 2 o port 1.0

B port 0.1 o 3 o port 1.1

port 0.2 o 4 o port 1.2

U port 0.3 o 5 o port 1.3

port 0.4 o 6 o port 1.4

S port 0.5 o 7 o port 1.5

port 0.6 o 8 o port 1.6 Peri*/memory

port 0.7 o 9 o port 1.7

Address 0 o 10 o RESET

Address 1 o 11 o INTERRUPT 0*

Address 2 o 12 o Timer 1

Address 3 o 13 o Timer 0

Address 4 o 14 o INTERRUPT 1*

Address 5 o 15 o Clock 1

Address 6 o 16 o Address Latch Enable (ALE)

Address 7 o 17 o Prog. Store Enable (PSEN)*

ADD. 15 Port 3.7 o 18 o Relinquish Control (REL)

14 Port 3.6 o 19 o RESET*

13 Port 3.5 o 20 o Clock 2

12 Port 3.4 o 21 o Spare

11 Port 3.3 o 22 o Spare

10 Port 3.2 o 23 o Spare

9 Port 3.1 o 24 o Spare

8 Port 3.0 o 25 o Spare

Serial TX o 26 o Spare

Serial RX o 27 o Spare

o-28-o WRITE*

o-29-o READ*

o-30-o +12v

o-31-o -12v

o-32-o +5v

```

\*Active LOW

Figure 3.1. Backplane Connector Pin-out

The backplane tracking consists of a series of parallel lines interconnecting like-named pins on the eight DIN connector sockets. Each signal track is 0.5 millimetre thick, with heavier tracking provided for power lines (and the read/write lines - assigned, for utility, to spare power lines). The backplane, as explained, was a part 'borrowed' from another system; it did not feature intertrack ground

lines, a desirable feature if the system should enter mass production at some future time, especially if the CPU clock rate should be increased. However, during the development work there was no evidence of backplane crosstalk, possibly attributed to both the low CPU clock rate and the wide track spacing on the simple PCB.

# 3.2. CPU board

The signals present on the backplane connector pins are for the most part determined by the structure and design of the CPU Board; this in turn reflects the facilities afforded by the 8751 - which are fully exploited in this system. The development system (Ref. 18) used for developing test firmware was the Intel PDS (Personal Development System), which the author used to assemble, edit and run programs. Although not as convenient or as powerful as a standard Intel (MDS) microcomputer development system, this cheap portable system proved to be adequate. The emulation vehicle used was the Intel EMV51 (Ref. 19), which is a plug-in option for the PDS. EMV51 is essentially a device that replaces the 8751 on the CPU board with an electronic 'umbilical chord' linking it to the PDS; this allows the user to monitor the internal registers of the processor during the debug stage. Although this thesis repeatedly refers to the 8751, the author used exclusively for firmware debugging; for final testing of debugged firmware the 8751 was used and some work was also done with the 8052-BASIC device (see Appendix 8).

The author opted for a 'memory mapped' I/O (input/output) scheme to realize the desired flexibility in interfacing to external systems (Ref. 5). This system is described below in

sub-section 3.2.1. Subsequent sub-sections cover the remaining features of the board.

# 3.2.1. The Bus and Memory Mapped I/O

The Bus system of the 8751 is derived from the Intel 8085, the successor to the still-popular Intel 8080, whose most famous descendant is the ubiquitous (Zilog) Z80. The latter processors use separate address and data lines, while 8085-type addressing structures multiplex the lower 8 bits of the (16-bit) address lines with the 8 data lines on one 'bus' port usually referred to simply as 'the Bus'. The Bus on the 8751 is assigned to the port 0 lines, whilst the upper eight address lines are mapped to port 2. Figure 3.2. below shows the 8751 pin-out.

```

port 1.0 :1

40: Vdd(5v)

port 1.1 :2

39: port 0.0

port 1.2 :3

38: port 0.1

port 1.3 :4

37: port 0.2

port 1.4 :5

36: port 0.3

port 1.5 :6

35: port 0.4

port 1.6 :7

34: port 0.5

port 1.7 :8

33: port 0.6

RESET:9

32: port 0.7

RxD :10

31: EA/VDD

P

30: ALE

TxD :11

INTO* :12

29: PSEN*

0

INT1* :13

R

28: port 2.7 (Add 15)

T

TO:14

27: port 2.6 (Add 14)

T1:15

26: port 2.5 (Add 13)

3

WR* :16

25: port 2.4 (Add 12)

RD* :17

24: port 2.3 (Add 11)

XTAL 1 :18

23: port 2.2 (Add 10)

XTAL 2 :19

22: port 2.1 (Add 9)

Vss (GROUND) :20

21: port 2.0 (Add 8)

. . . . . . . . . . . . .

```

\*Active LOW

Figure 3.2. - 8751 Pin-out

Although nominally designated 'ports', ports PO and P2 implement the address/data Bus, while P3 provides eight special one-line functions, described later. The remaining port (P1) is reserved for use as eight individual I/O lines (e.g. Pl.6 is used as a peripheral memory control line - see below), although it could also be employed as a port during firmware testing, as an aid to diagnostics. During a write to external data memory (see Figure 3.3) the 8751 generates signals on several pins. For example, the signal ALE (address latch enable) is emitted on pin 30; because of the way the 8751 fetches program memory bytes internally (in pairs), ALE is clocked at half the normal rate when external data memory is accessed. This issue is dealt with in more depth in Chapter 4, which covers the RAM (Random Access Memory) board.

The low level state of ALE is used to latch the lower eight bits of the multiplexed address into an eight-bit latch. The latch is shown as U3 (74ALS573) in CPU board schematic diagram (Figure 3.4). ALE is also buffered to the backplane (by U5c - 74LS125) to act as a timing/control signal for peripheral cards. Two other signals are also relevant to external memory access - RD (read - pin 15) and WR (write - pin 16), both active LOW. These signals are two examples of alternative uses of port 3 pins; thus whenever the Bus feature of the 8751 is utilized, use of port 3 as a conventional port is excluded. However, this is a small price to pay for the powerful facilities the Bus

Figure 3.3 - Timing Diagram for External Memory Access.

affords. The signals RD and WR are also buffered to the backplane by U5. They are used to enable data to or from memory and peripheral cards.

To enable peripheral cards to be addressed, four address lines (A12-A15) have been 'borrowed' from the Bus - a technique known as 'memory mapping'. This allows up to sixteen individual cards in the rack to be addressed - more than sufficient for most applications. The CPU sees the peripherals as sixteen high order address locations; there is no conflict between the peripheral addresses and the first 4K of external RAM. This was considered an adequate quantity of RAM at first, but at a later stage in the project the requirement for addressing larger quantities of external memory arose - possibly up to 32K, or perhaps even 64K. To allow for these larger memory requirements, one line of port 1 (P1.6 -PERI(BAR)/MEMORY) was buffered to the backplane (a second, spare line - P1.7, was similarly buffered, for general use). The Pl.6 signal line has been gated on all peripheral and memory boards with the relevant address decode logic to select either memory or peripheral accesses. A zero latched by firmware to P1.6 will select peripheral devices; a one latched to P1.6 will select memory access. Details of several other port 1 pins which provide optional facilities (e.g. serial handshake lines for RS232 options) for various peripheral cards, are given in the chapters which relate to the particular peripheral cards.

32-

Bus buffers are provided for ports PO and P2; these are U2 and U4 respectively. Both buffers are 74LS245's - these provide the necessary increased output fan-out and also protect the 8751 against accidental damage. The control of the output enable by the gating provided by U7A enhances this protection in the case of PO - the direction being controlled by the WR signal. Directional control of U4 is not required, as the upper address lines are uni-directional. A control line has been allocated to backplane pin A18 (REL), to allow another intelligent device to gain control of the backplane lines. This could possibly be, say, a video controller card ( a likely future requirement) with a need for asynchronous access to the RAM memory board. Typically the device would participate in an interrupt/status handshake with the CPU board, before completing the Bus release by taking REL high, thus tri-stating the active control/address circuits.

#### 3.2.2. Clock circuitry

The 8751 features an on-board crystal oscillator which requires a minimal set of external components, as shown in Figure 3.4. The oscillator circuit is in fact a single stage amplifier connected as a Pierce oscillator (Ref. 8). XTAL 1 (pin 19) is the input to the oscillator and XTAL 2 (pin 18) is the output. To prevent the extremely small input capacitance of the FETs (field effect transistors) that form the oscillator amplifier 'pulling' the crystal above its

required operating frequency (overtone start-up is disastrous to the operation of the 8751 serial port, for example, which is referenced to the clock frequency), two balanced phase-shifting capacitors shunt each side of the crystal to ground. Fisher (Ref.7) reports suitable values of 30 pF (obtained empirically) for these capacitors giving reliable start-up in the frequency range 500 kHz to 15 MHz, with pulse rounding at the latter frequency. (At the time of writing the 8751 is specified to 12 MHz - although at the start of the project the part was limited to 8 MHz).

Appendix 1 lists some sample serial port baud rates for the 3.6864 and 7.3728 MHz crystals; the baud rate is determined by the clock frequency and by the reload constant loaded into the timer register 'TH1'. Crystal selection is not a straight-forward matter in this case; for most microprocessors, an approximate operating frequency will suffice, but the accuracy of the 8751 serial port timing is important for reliable serial data transfer. Crystals have several selection parameters (Ref. 8), and are quoted as for either series or parallel resonance oscillators. A crystal quoted for series resonance will work reliably in a parallel resonance circuit, but will oscillate at a frequency slightly removed from that quoted by the crystal manufacturer, hence it is important in this case to obtain the correct component. Parallel resonant crystals can be purchased off the shelf from

component distributors for 3.6864 MHz, and so early development work was based on this frequency. Later tests were performed at 7.3728 MHz, using crystals made to order (Ref. 7).

A penalty for having an on-board UART is the impracticality of including 'hesitate' circuitry ('freezing' the CPU by withholding clock pulses) for the clock oscillator; the reception of serial data being essentially asynchronous, clearly it would be unsatisfactory to disable the UART for even short time intervals. In a typical 8080 or 8085 system, for example, the 8224 clock generator (Ref. 9) would provide the hesitate function via the READY input. This line would appear as a backplane signal in such a system, enabling other boards in the system to pause the CPU - typically while awaiting external data. This rules out the use of some families of interface chips - e.g. PIA's (Ref. 16) which provide a hesitate signal to the host CPU - for use on the various interface cards that comprise the miniature rack This matter is discussed further in Chapter system. 5, in the section covering the BCD interface design.

The CPU board provides two clock lines (Clock 1, Clock 2) which may be utilized by other boards in the system, via the backplane connections. U6 is a high speed CMOS clock divider (HC 4024); the high input impedance and the CMOS logic levels of the inputs are an excellent match to X1 pin's low drive output parameters, allowing a direct connection to the 8751's

Pierce oscillator. Links are provided on the board to enable the user to select the required clock rate(s).

During testing the author selected the clock 1 rate to be 921.6 KHz; Clock 1 is used by several cards - e.g.

ADG (Chapter 7) - whilst clock 2 is provided for possible future use. The jumper configuration used is, of course, partly dependent on the crystal frequency.

# 3.2.3. Reset

The reset signal, which provides a positive CPU reset pulse on power-up, is provided by the watchdog card (section 3.4.) on backplane pin AlO. The watchdog card also features a manual reset push-button which allows an operator to reset the system.

#### 3.2.4. External Memory Features

Data memory external to the CPU is covered in the next chapter; P1.6 is used as a memory select line, with P1.7 being similarly buffered (U7b, U7c) for possible future use. External program memory is also allowed for - the jumper connected to pin 31 specifying whether the program resides on internal or external EPROM (Erasable Programmable Read-Only Memory). Up to 64K of external EPROM may be addressed, although the 4K on-chip is considered adequate for the Company's applications. PSEN (Program Store Enable - active LOW) is the control signal used to gate external PROM's, and is buffered to the backplane by U5d. An inexpensive EPROM-less version (the 8031) of the 8751 is available, should

the Company require the development of EPROM programs in excess of 4K in size, in which case these programs could reside in the external 64K memory areas, on a separate EPROM board.

#### 3.2.5. Miscellaneous - Timers etc.

Two timer pins (TO and T1) are connected directly to the backplane (pins Al3 and Al2 respectively), as are two interrupt lines (INTO and INT1 - backplane pins All and Al4 respectively); the timer pins may be used (software configurable) as either event counters or one-bit I/O lines (Ref. 1). The interrupt lines are similarly software configured as either active low (input) interrupt pins or general-purpose I/O lines invariably they are used for interrupts. Normally a device (interface board) requiring attention would force, say, the INTO line LOW, and the CPU would respond by reading the status register of each card until the interrupting device is identified - an interrupt triggered serial poll sequence referred to herein as an 'interrupt/status handshake'. Usually the sequence completes with an exchange of data between the two boards - an entirely conventional method of servicing 8085 type peripheral chips such as, say, the 8251 USART (Refs. 21,22). An acceptable alternative approach to addressing peripherals considered during development was the use of DMA (Direct Memory Access) using a DMA controller chip such as the Intel 8237, which is designed for DMA implementation on 8085-type bus systems. However,

this would have meant a separate DMA board due to the size of the DMA chip (40-pin) - an unacceptable hardware overhead.

The 8751 serial port pins RXD (Receive Data - pin 10) and TXD (Transmit Data - pin 11) are also connected to the backplane (pins C27 and C26 respectively), to provide serial data to the RF board or the Serial board - both of which are described in Chapter 6. (See this chapter also for details of use of port 1 pins - P1.0 and P1.1 - as serial data handshake lines). The serial port options (baud rate, parity checking/generation, start/stop bits etc.) are all firmware selectable, details of which, together with a sample firmware listing, are contained in Appendix 3.

A small 5v reservoir (22 micro-Farad) has been included on the card, in common with all the other cards (with the exception of the watchdog card, which has larger capacitors associated with the various power lines - see 3.4. below) in the system. The capacitor is sited near the 5v backplane power pins (C/A 32) to ensure a smooth DC line for the whole card. As the card utilizes one single 5v supply, there are no connections to the +12v line (pins C/A 30), or the -12v line (pins C/A 31). Ground connection to the backplane occurs on pins C/A 1. Gridded ground planes and similar noise rejecting PCB layout techniques were used in pre-production artworks for the CPU board (and/where space

considerations permitted on other boards) in an attempt to minimize the pickup of noise (Ref. 17).

# 3.3. The DVI Board

The DVI (Digital Voltage Input) board was designed to interface digital signals (voltage or current) to the CPU board. Figure 3.5. shows the circuit diagram. The requirement was for an opto-isolated eight-input board, memory mapped to the Bus. The board can be thought of as a memory mapped development of the simple opto-isolator board ('paddle' board) described in Chapter 2. The use of the memory-map hardware and associated device address switches means that a greater number of inputs can be monitored by one node - the rack can be populated by several DVI cards, each with a different device address.

/Continued Over

# 3.3.1. Memory mapping hardware

This hardware is described in detail at this stage, as it is a common feature of most cards in the system. The memory mapping device is the LS85 comparator (U6); it was one of a number of circuit elements chosen after consultation with the Contractor's staff, with reference to their bulk component stock. comparator's considered were the Fairchild F521 (8-bit) and the 'LS682 (the latter component was used on the watchdog card - see 3.4. below - in preference to cascaded '85 comparators). The comparator has two sets of four-bit input lines (A and B) - when the data present on both sets are equal then a logic one is output on pin 6 (the A=B output). The 'A' lines are connected to a four-way switch bank (switching to ground), pull-ups selecting logic ones when the switches are open-circuit. The switches define the card address within the rack.

The '85 comparator features an input enable, which is driven high by the presence of a logic one on the AND-tied output of two open-collector inverters. One of the inverters (U7a) buffers the signal PERI(BAR)/MEMORY obtained from backplane pin A8 (this is the firmware dependent signal present on P1.6, selecting either memory or peripheral accesses via the Bus, described earlier - see section 3.2.). Another 'LSO5 buffer (U7b) is used to invert the active LOW read (RD) signal. Hence the comparator provides an output 'one' on pin 6 when the card is correctly

addressed, provided the input enable condition is satisfied - i.e., RD being LOW and peripheral addressing being enabled. The output is inverted (U7c) to give an active LOW output in order to drive the output-enable pin of an 'LS245 octal buffer (U5) LOW under the conditions detailed above.

# 3.3.2. <u>Input isolation</u>

The '245 is used to drive data obtained from the outputs of two Litronix ILQ74 quad opto-isolators (U1 and U2) onto the Bus during the read interval. opto-isolators are the same type of components as used for isolation of inputs in the hardware of the simple nodes of the pilot scheme described in Chapter 2. A current in the range 4-100 milliamps through a photodiode in U1 or U2 will drive a LOW output on the (collector) output of the corresponding phototransistor. (A series resistor, user-specified, is used for current limiting on each input - allowing input signals to be sourced from whatever DC supply is convenient). Pull-ups on the outputs ensure TTL levels; the signals are also fed to a high-gain (Darlington) transistor array, which is used to drive eight elements of a ten element bargraph array, used in this application as an LED front-panel signal state indicator. The ULN2803A (U4) incorporates internal base resistors that ensure TTL compatibility.

#### 3.3.3. Connector hardware

It is useful to mention at this stage the reason for the choice of front-panel connector for the input

signals. The connector used is the T and B Ansley 20-way polarized socket (Farnell Part No. 612 2004ES), designed to accept the corresponding polarized ribbon-connector plug. The socket features two side-mounted lock/eject tabs as well as right angled PCB solder pins for ease of assembly. The socket is of the type used as a component of the Pheonix FLK-20 20-way C-rail connector - allowing a simple one-piece ribbon cable connection between C-rail signal cables and a DVI card in a typical installation. The FLK-20 is a compact connector, splitting the 20-way signals into two tiers (ten signal connections and ten return or ground connections) of screw-tightening cable clamps. Plate 3.2. shows a photograph of a prototype DVI card.

#### 3.3.4. Handshake Options

The availability of two spare signal/earth pairs on the front panel socket (and two spare LED indicators) prompted the addition of two opto-isolated handshake lines to the card, to allow a possible alternative use - as an opto-isolated parallel bus interface. The opto-isolator (U3) used is the Litronix ILD74, a dual isolator similar in performance to the quad package (U1, U2). Both halves of the isolator can be used as input lines (the isolator outputs are open-collector - the 8751 incorporates pull-ups within the input ports); the U3a output may be optionally inverted (using jumpers AB and DC) or connected (jumper BC) directly to the selected backplane line - either an interrupt

line or timer input (although, of course, the line selected may simply be a general purpose input line, according to the 8751's firmware configuration of the port pin). A typical use of this option would be as an input flag line for a remote parallel interface.

U3b allows, by means of jumpers, the implementation of either a second input flag line (jumper 1 and 4), or an output control line (jumper 2 and 3).

As a general comment it can be stated that the options described above were added simply because the space was available on the board; most applications which require the use of the interface will omit U3, the card serving an eight-input passive isolation device. As the three inverters (U7d, e and f) are already present on the board, little extra production cost is incurred for the additional facilities. The marginal value of these extra facilities preclude the addition of the status register hardware found on other boards, so the DVI board is excluded from the list of serial pollable devices - i.e., it cannot take part in an interrupt/status handshake with the CPU.

#### 3.4. Watchdog card

This card (see Figure 3.6.), is a development of two sections of the system described in Chapter 2 - the power input and transient suppression section, and the watchdog circuit. A third function - node identity - is added. Each section is described in detail below.

#### 3.4.1. Power input

Because of the presence of RS232 buffers, ADC's (Analog to digital converters) etc., etc., on certain cards in the system, the original single-supply requirement was relaxed. Power on this system is derived from an external commercial switch-mode power supply, which by it's nature offers further buffering against mains-born noise. The outputs of the power supply (see Appendix 10 for further details) are +5v, +12V, -12V and Common, which are admitted to the system by a cranked plug (Cannon type AXR-3-15) inserted into a mating 4-way socket (Cannon type AXR-3-32), flush-mounted on the front panel. The minimal depth of the plug ensures that the total depth of the whole assembly is not excessive with respect to the internal depth of common wall-mounting industrial enclosures. The circuit diagram of the card (Fig. 3.6.) reveals that the 5v supply is conditioned in the same way as in the pilot scheme; the other supplies are less critical and are simply decoupled (47 micro-Farad capacitors) before being routed to the backplane.

The operation of the power supply is monitored on the front panel of the card by LED's (light emitting diodes); also present on the front panel are a push-button, LED and switch which are associated with the manual reset and watchdog enable functions, described later.

# 3.4.2. Watchdog Circuits

This circuit (Ref. 3) is similar to the '555' timer circuit used in the original 'node' system (see Chapter 2); the same system is used - a train of pulses are used to retrigger the 555 (in this case configured as an astable) - but the source of trigger pulses is different. The CPU must source the pulses in the form of data bytes on the Bus - the watchdog card is memory mapped in the same manner as the DVI card, for example. (Rather than repeat the description of the '85 comparator circuitry, the author will refer the reader to the DVI board circuit description in section 3.3.1. in future). When the card is selected by a 'MOVX' write command within the CPU, the eight-bit '682 comparator (U2) compares the data byte on the bus with the settings on an eight-way switch register (note that the pull-ups for the switches are incorporated within the '682), and outputs an active LOW signal if equality is detected. The output pulse is buffered to the '555' (U4) retrigger input; active LOW output pulses from the '555' are diode-coupled to the RESIN input of U5 (see below). A manual push button ('RESET') is provided on the front panel, with LED indication; a toggle switch (SW1) is also provided, to disable the watchdog function during system testing.

The '555' used on this board is a variant of the 'standard' 555 timer, the Texas TCL555CD. This is a new product, a low-power CMOS type, allowing the use

of smaller value timing components to achieve the corresponding decay periods. This adds to both the compactness of the circuit (the timing capacitor is quoted representatively in units of nano-Farads rather than, say, micro-Farads and hence is relatively small and stable) and to its timing range.

An extra chip (U5 - Texas TL7705) has been included on the Watchdog board to monitor the 5V power supply rail and detect 'brown-outs' or major supply fluctuations. The chip has a 'SENSE' input (pin 7) which is, in this case, connected directly to the 5V supply line. The SENSE input will detect supply fluctuations and the chip will output a RESET pulse to reset the active devices connected to the backplane reset line(s), the output pulse timing being determined by an external (pin 3) capacitor. The chip provides an active LOW open - collector output via an internal n-p-n transistor and an active HIGH open-collector output via an internal p-n-p transistor. These outputs are provided with external pull-up/pull-down resistors and connect directly to the backplane reset lines. The reset function may also be triggered by an active low input pulse on pin 2 (RESIN), which may be sourced from the watchdog output (described earlier) or the buffered (U7e) RESET push-button.

# 3.4.3. Node Identity

If the interfacing system is to be a 'node' in a

distributed system, the node identity (it's number in the system) needs to be accessible to the CPU firmware. For the pilot scheme, the node number was stored as a constant in EPROM inside the 8751, but this is inconvenient for the user, as it is necessary to 'blow' (i.e., EPROM program) different versions of the firmware according to the node's identity.

To cater for convenient access to the node number, and ease of visual discrimination, the comparator switches also double as node 'identity' switches; when the CPU firmware uses a MOVX instruction to 'read' from the card memory-mapped address location, the address decode logic will enable - via a '245 buffer (U3) - the data onto the bus. The 8751 firmware would perform this access as part of its initial RESET sequence during start-up, and incorporate the node number into its self-test calculations; at a later stage the regenerated node number would be written back to the watchdog card to service the watchdog timer.

# 3.5. Review

After an initial DC check-out, the three boards described in this chapter were tested in combination, plugged into the backplane of the sub-rack. The PDS system's EMV51 emulator was used in lieu of the 8751 to enable rapid de-bugging. Most of the testing was performed using the emulator's high-level macro language, which enabled a convenient and thorough system test.

#### 3.5.1. CPU board

The CPU board was tested with both the 3.6864 MHz crystal and the 7.3728 MHz crystal. No problems were experienced at either speed with signal crosstalk. Particularly pleasing were the CLOCK 1 and CLOCK 2 signals, which exhibited a clean square waveform when viewed on an oscilloscope (Phillips PM3215). The waveform (see Appendix 1) displayed a 50% duty cycle with minimal ringing. The author tested the 8751's response to interrupts using the DVI board's options (see 3.5.2. below). Response to reset etc. is dealt with under 3.5.3.

# 3.5.2. The DVI Board

Problems were experienced with this board concerning the values of the pull-ups; the board did, in fact, perform satisfactorily from the user's point of view - i.e., it functioned correctly as a system component as originally designed. However, a logic probe placed on the U5 inputs indicated an invalid signal logic level for the theoretical logic '1' state - an effect caused by the pull-down action of the current flowing into U4's internal base resistors. Substituting 3.3k or 4.7k resistors for the 10k pull-ups solved the problem.

The introduction of lower value pull-ups also speeded up the rise-time of pulses associated with open-collector ('LSO5) gates - although the exponentially rising waveforms observed during testing

had no detrimental effect on the operation of the logic. Later (production) versions of the board used S1L and D1L resistor networks to minimize the component population and improve reliability; this is true also of other boards in the system, which is why the reader will sometimes encounter, for example, a pair of series resistors (e.g. Figure 3.6) in a circuit where a single larger-valued component would suffice.

#### 3.5.3. Watchdog Board

This board was tested in several 'breadboard' versions and at the time of writing a production design has yet to be finalized, although the version shown in Figure 3.6. performed satisfactorily. Tests were made with the CPU board to check the correct operation of the reset, node identity and watchdog functions. Although the watchdog circuit was found to function correctly, the author was unhappy about the large number of discrete components associated with the watchdog circuit, giving a cluttered PCB layout compared with other boards in the system. Also, the presence of many discrete components on a PCB increases assembly effort/cost and reduces reliability.

The author has experimented in replacing the 555 circuit with a second TL705 chip - configured similar to U5 but used as a watchdog timer. To use a TL7705 as a watchdog requires the use of the RESIN input as the input of the retrigger pulses; in this mode the

TL705 is pulsed into the reset mode and held there - an absence of pulses causes the device to revert to its quiescent state, causing an output pulse on pins 5 and 6. This unconventional use of the TL7705 is still experimental, but offers clear advantages in circuit layout.

#### CHAPTER 4: MEMORY EXPANSION

Although the 8751's 4k of EPROM and 128 bytes of RAM are sufficient for many applications, the small quantity of RAM (in particular) will be too limited for some of the Company's applications. It is a common need to buffer slow peripherals - especially devices such as serial printers - with buffers. 0n the other large (e.g. 2k) RAM hand. any local 'number-crunching' tasks that the system may be called upon to perform may prove demanding as regards EPROM space. The 8751's address architecture allows for both data and program memory to be expanded externally, each to 64k maximum.

This chapter describes the RAM board in detail and discusses EPROM memory expansion; as the Company does not require the development of an EPROM board at the time of writing, the author has limited his activities to providing the necessary backplane signals, thus allowing the addition of the board at a later date. As there are obvious similarities between the two memory systems, many points concerning circuit design that are covered in the description of the RAM board apply also to the design of an EPROM board.

#### 4.1. The RAM Memory Board

Memory systems for microprocessor data storage are normally based on one of two types of memory: 'static' RAM's or 'dynamic' RAM's (often referred to as SRAM's or DRAM's). SRAM's are usually preferred for small (up to 64k) memory stacks, as they are totally self-contained. They are however, more expensive to manufacture per storage element than DRAM's. The major drawback with DRAM memory is the need to 'refresh' the memory - i.e., read (and write back) every bit in the memory at the 'refresh rate' quoted by the I.C. manufacturer.

Refresh control is a task unsuitable for a busy CPU, and is often implemented with special refresh and 'arbiter' (it is necessary to resolve the conflicts that arise from simultaneous refresh and data requests) circuits. The overheads in cost and size that the circuitry incurs prohibits the economic use of DRAM memory in small systems. Thus, SRAM's are the obvious choice for systems designers. However. many another alternative recently available has become IRAM's ('integrated' RAM's - also known as 'pseudostatic' RAM's), which offer a cheaper alternative to SRAM's.

IRAM's are DRAM memories included on the same chip together with the necessary refresh and arbiter circuits. To the user the external characteristics make IRAM'S appear to be compatible with SRAM'S - that is, they occupy the same JEDEC (Reference 10) International Memory Site for 'byte-wide' memories as SRAM's, and share the same ease of application. The major difference between the two products lies in the interpretation of one all-important parameter - Access Time.

When the 8751 issues a 'MOVX' instruction for the purpose of reading data from external RAM memory, the read timing profiles shown in Figure 3.3. apply. ALE (which runs at half normal speed during a MOVX instruction) is used as the main timing pulse, the memory (SRAM or IRAM) being enabled by (and, therefore, timed from) either the rising or falling edge. In the case of the Intel 2186 asynchronous IRAM, the falling edge is used. (The 2186 will be used as a convenient model for discussion, for the time being). The RD signal is used to gate the IRAM's output buffers onto the Bus; although the data need not be available from the RAM at this point, it must arrive

before the 8751's read sampling interval, which occurs during the eleventh clock period after ALE goes LOW, as shown in the diagram. Thus, the critical timing (Tc) for the 2186 is the time between the falling edge of ALE and the start of the sampling period (SP); this represents ten complete clock cycles. Table 4.1. below shows the timing figures for Tc at three different clock frequencies, and the access times for three different versions of the 2186 (-25,-30,-35 indicates 250nS, 300nS and 350nS respectively. These are the access times without refresh contention).

| Clock freq. | Tc     | Access  | Time with | refresh |      |

|-------------|--------|---------|-----------|---------|------|

| (MHz)       | (nS)   | 2186-25 | 2186-30   | 2186-35 | (nS) |

| 3.6864      | 1898.9 | 675     | 800       | 950     |      |

| 7.3728      | 949.4  | 11      | 11        | 11      |      |

| 11.0592     | 632.9  | 11      | Ħ         | tr      |      |

Table 4.1 - Access Time (with refresh) for the 2186 IRAM.

From the table above, for example, it can be seen that the 350nS part is (marginally) too slow for the 7.3728 MHz clock rate, so the 300nS version would be the correct choice. The 350nS part is suitable for the slower (3.6864 MHz) rate, and, of course, is cheapest. The author experimented during development with both of these versions of the IRAM, and also with an 8k x 8 bit SRAM's, (e.g., the Hitachi HM6264 - See Appendix 11). The latter part was found to be satisfactory (the access time of 150nS made it a possible contender for use as a program memory store), but was significantly more expensive than the 2186, which was therefore preferred for data storage.

Figure 4.1. shows the circuit for the RAM memory board, based on the 2186-30 part. It is expected by the author (as a result of enquiries) that Intel will double the size of the IRAM within the next

12 months (the first of the current series of Intel IRAM's was released as a 4k x 8 bit part, which was subsequently replaced by the 8k x 8 bit part); to allow for this links have been incorporated into the design to cater for the anticipated upgrade. The circuit is based on a stack of four IRAM's (U3, U4, U5 and U6), giving a total memory capability of 32k x 8 bit board. The memory may be mapped into either the 0-32k or 32k-64k address range, using further links. Thus, if 64k of memory is needed, then it is necessary to use two boards, until the upgraded IRAM becomes available. The circuit is now described in detail.

# 4.1.1. Chip enable Gating

A 2186 memory cycle commences when Chip Enable (CE - pin 20) is driven LOW. The signal that provides the transition is, as indicated earlier, ALE - but it is necessary to gate the signal with others (Reference 11) to prevent illicit access, particularly during power-up. The IRAM is self-resetting when the 5 volt supply is applied, provided CE, OE (output enable active LOW) and WE (write enable - active LOW) are inactive. This is certainly true in the case of the last two named signals, but ALE needs to be gated out, as it commences clocking immediately the 8751 is initialized. Pulsing CE before the 2186 has terminated its internal reset procedure would result in incorrect operation of the device, so ALE is gated with RESET to prevent this occurrence. The signal is also gated with the memory/peripheral select line, to inhibit access during peripheral transfers via the Bus (see the previous chapter). Table 1 below shows the

truth table for the chip enable gating, which is implemented with NAND gates (Figure 4.1.- Ula, b and c).

# Table 4.2. - The Truth Table for Gating ALE

A two-to-four line decoder (U2) is used to select the individual 2186's. The open collector version ('LS156) is used to allow the versatility in IRAM component choice mentioned earlier. When the 8k RAM's are used the S1 and Sh inputs of the '156 select the 0-32k or 32k-64k range; wire links are employed to configure the inputs to the '156. Only the 'A' section of the '156 would be used with the 16k devices, and only one half of the '156 is ever enabled, according to the option selected - the appropriate link combinations are shown on the circuit diagram.

When the card is linked for the 0-32k range, Al3 and Al4 are connected to the AO and Al inputs to the decoder; Al5 is connected to the Sl input of the 'B' section of the '156 the 'A' section being disabled, with Sh held LOW. The gating of the enable to the decoder us deferred until Ula pulses LOW - on the falling edge of ALE, whereupon the selected CE is driven LOW, and the memory cycle for the chip commences.

# 4.1.2. Reading from data memory

A data memory read cycle commences with a negative-going CE transition as outlined above. address information on lines AO-A12 is latched into the IRAM at this time. The IRAM then accesses the addressed data byte as part of а standard 'read-modify-write' cycle, as is common with other types of read/write memories. Within the time-period detailed above, the data is present in the RAM's output buffer, to be gated to the Bus by RD (which is connected to OE - pin 22). The rest of the read-modify-write cycle is internal to the 2186 consisting of writing the unmodified data back into the memory location. This part of the cycle is most relevant to WRITE transfers, described below.

#### 4.1.3. Writing to Data Memory

The write timing is less critical than the read timing (see above), the data being latched into the IRAM on the falling edge of WR. The standard R-M-W

cycle commences as for READ transfers (described above), on a negative CE pulse. The latched (by WR) data byte from the Bus is written to the addressed memory location in lieu of the previously fetched byte (hence the 'modify'). Once the data byte has been sampled by the IRAM, the timing of the remainder of the write cycle is in general unimportant to the operation of the host CPU, and it is therefore true to say that the read timing is generally the more limiting factor in the application of RAMs. Further details on the operating conditions of the 2186 and other memories discussed herein can be found in Appendix 11.

# 4.2. External EPROM Facilities