# HIGHLY EFFICIENT LINEAR CMOS POWER

# **AMPLIFIERS FOR WIRELESS COMMUNICATIONS**

A Dissertation Presented to The Academic Faculty

by

Ham Hee Jeon

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology May, 2012

Copyright © Ham Hee Jeon 2012

# **HIGHLY EFFICIENT LINEAR CMOS POWER**

# **AMPLIFIERS FOR WIRELESS COMMUNICATIONS**

Approved by:

Dr. J. Stevenson Kenney, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Kevin T. Kornegay School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Chang-Ho Lee School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Jongman Kim School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Paul A. Kohl School of Chemical and Biomolecular Engineering *Georgia Institute of Technology*

Date Approved: February, 15, 2012

To my wife and parents

#### ACKNOWLEDGEMENTS

First, I would like to acknowledge the supervision of my research advisor, Professor J. Stevenson Kenney. Without his support, this research would not have been completed. I am also grateful to my committee members, Professor Kevin T. Kornegay, Professor Jongman Kim and Professor Paul A. Kohl for their precious time in reviewing my thesis.

I would like to specially thank Dr. Chang-Ho Lee for his valuable support and helpful guidance during my research. He continued to motivate my research with his insights and vision in this research area. I also would like to thank Dr. Joy Laskar and Dr. Kyutae Lim for their advice and support for my research.

I am indebted to the members of the power amplifier group: Hyungwook Kim, Kun-Seok Lee, Eungjung Kim, Jihwan Kim, Youngchang Yoon, Hyunwoong Kim, Yan-Yu Huang, Kwanyeob Chae, Michael Oakley and former group members: Ockgoo Lee, Kyu Hwan An, and Jeongwon Cha, for their willingness to engage in in-depth discussions throughout my research work.

I also would like to thank the members of the Microwave Application Group: Joonhoi Hur, Kilhoon Lee, Kwanwoo Kim, Jong Min Park, Seungho Beck, Seungil Yoon, Taejoong Song, Sanghyun Woo, Hyungsoo Kim, Sang Min Lee, Jaehyouk Choi, and Stephen Kim.

I wish to thank Samsung Design Center engineers: Dr. Woonyun Kim, Dr. Jae Joon Chang, Dr. Wangmyong Woo, Dr. Changhyuk Cho, Dr. Yunseo Park, Dr. Minsik Ahn, Dr. Ki Seok Yang, Dr. Dong Ho Lee and Dr. Jeonghu Han for their helpful discussion and encouragement.

I wish to thank Angelika Braig for her continuous support and the Georgia Electronic Design Center (GEDC) for providing a good research environment.

I am deeply grateful to my parents, Gye Lim Jeon and Young Ye Lee for their constant love and support in my life. Finally, I would like to specially thank my wife, Chaeri Jang, for her love and encouragement. She has been my greatest source of inspiration in my life.

# TABLE OF CONTENTS

|                                                 | Page  |

|-------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                | iv    |

| LIST OF TABLES                                  | Х     |

| LIST OF FIGURES                                 | xi    |

| LIST OF SYMBOLS AND ABBREVIATIONS               | xvi   |

| SUMMARY                                         | xviii |

| <u>CHAPTER</u>                                  |       |

| 1. Introduction                                 | 1     |

| 1.1. Technology trends                          | 1     |

| 1.2. Motivation                                 | 4     |

| 1.3. Organization of dissertation               | 8     |

| 2. RF power amplifiers                          | 10    |

| 2.1. Introduction                               | 10    |

| 2.2. Key design factors of RF PA                | 11    |

| 2.2.1. Efficiency                               | 11    |

| 2.2.2. Linearity                                | 13    |

| 2.2.3. Output power and stability               | 16    |

| 2.3. Prior arts                                 | 17    |

| 2.3.1. Linearity enhancement techniques of a PA | 17    |

| 2.3.2.1. Predistortion linearization technique  | 17    |

| 2.3.2.2. Feedforward linearization technique    | 20    |

| 2.3.2.3. Feedback linearization technique       | 21    |

| 2.3.2.4. Harmonic traps                         | 23    |

|    | 2.3.1.5. Capacitance cancellation technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                                                                     |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|    | 2.3.2. Efficiency enhancement techniques of a PA                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                     |

|    | 2.3.3. Output power improvement techniques of a PA                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26                                                                                                                     |

| 3. | Challenges of CMOS power amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30                                                                                                                     |

|    | 3.1. Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30                                                                                                                     |

|    | 3.2. Lossy substrate of CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                     |

|    | 3.3. Losses of CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32                                                                                                                     |

|    | 3.3.1. Low quality factor of passive components                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32                                                                                                                     |

|    | 3.3.2. Eddy current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                                                                     |

|    | 3.3.1. Skin effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                                                     |

|    | 3.4. Reliability problems of CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                                                                                                     |

|    | 3.5. Linearity and transconductance of CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37                                                                                                                     |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                        |

| 4. | A Novel feedback bias technique for the CMOS power amplifier in the r<br>stage cascode topology                                                                                                                                                                                                                                                                                                                                                                                                             | nulti-<br>38                                                                                                           |

| 4. | · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                        |

| 4. | stage cascode topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38                                                                                                                     |

| 4. | stage cascode topology       4.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38<br>38                                                                                                               |

| 4. | <ul> <li>stage cascode topology</li> <li>4.1. Introduction</li> <li>4.2. Cascode topology and design issues of CG transistor</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     | 38<br>38<br>39                                                                                                         |

| 4. | <ul> <li>stage cascode topology</li> <li>4.1. Introduction</li> <li>4.2. Cascode topology and design issues of CG transistor</li> <li>4.3. Cascode feedback bias technique</li> </ul>                                                                                                                                                                                                                                                                                                                       | <ul><li>38</li><li>38</li><li>39</li><li>42</li></ul>                                                                  |

| 4. | <ul> <li>stage cascode topology</li> <li>4.1. Introduction</li> <li>4.2. Cascode topology and design issues of CG transistor</li> <li>4.3. Cascode feedback bias technique</li> <li>4.3.1. Negative feedback and distortion suppression</li> <li>4.3.2. The coupled signals by intrinsic capcitors in transistor and the</li> </ul>                                                                                                                                                                         | <ul> <li>38</li> <li>38</li> <li>39</li> <li>42</li> <li>42</li> <li>42</li> </ul>                                     |

| 4. | <ul> <li>stage cascode topology</li> <li>4.1. Introduction</li> <li>4.2. Cascode topology and design issues of CG transistor</li> <li>4.3. Cascode feedback bias technique</li> <li>4.3.1. Negative feedback and distortion suppression</li> <li>4.3.2. The coupled signals by intrinsic capcitors in transistor and the negative feedback formation of cascode feedback bias technique</li> </ul>                                                                                                          | <ul> <li>38</li> <li>38</li> <li>39</li> <li>42</li> <li>42</li> <li>42</li> <li>45</li> </ul>                         |

| 4. | <ul> <li>stage cascode topology</li> <li>4.1. Introduction</li> <li>4.2. Cascode topology and design issues of CG transistor</li> <li>4.3. Cascode feedback bias technique</li> <li>4.3.1. Negative feedback and distortion suppression</li> <li>4.3.2. The coupled signals by intrinsic capcitors in transistor and the negative feedback formation of cascode feedback bias technique</li> <li>4.3.3. The feedback bias network</li> </ul>                                                                | <ul> <li>38</li> <li>38</li> <li>39</li> <li>42</li> <li>42</li> <li>42</li> <li>45</li> <li>50</li> </ul>             |

| 4. | <ul> <li>stage cascode topology</li> <li>4.1. Introduction</li> <li>4.2. Cascode topology and design issues of CG transistor</li> <li>4.3. Cascode feedback bias technique</li> <li>4.3.1. Negative feedback and distortion suppression</li> <li>4.3.2. The coupled signals by intrinsic capcitors in transistor and the negative feedback formation of cascode feedback bias technique</li> <li>4.3.3. The feedback bias network</li> <li>4.3.4. The effects of cascode feedback bias technique</li> </ul> | <ul> <li>38</li> <li>38</li> <li>39</li> <li>42</li> <li>42</li> <li>42</li> <li>45</li> <li>50</li> <li>55</li> </ul> |

| 5. | A highly efficient balanced linear power amplifier for WCDMA applica<br>in a 0.18-µm CMOS technology | i <b>tions</b><br>72 |

|----|------------------------------------------------------------------------------------------------------|----------------------|

|    | 5.1. Introduction                                                                                    | 72                   |

|    | 5.2. Balanced PA topology                                                                            | 73                   |

|    | 5.2.1. Load immunity                                                                                 | 74                   |

|    | 5.2.2. Enhanced matching network and constant gain                                                   | 76                   |

|    | 5.2.3. Improved stability                                                                            | 78                   |

|    | 5.3. A highly efficient balanced CMOS linear PA design                                               | 79                   |

|    | 5.3.1. Balanced PA in CMOS technology                                                                | 79                   |

|    | 5.3.2. L-C quadrature splitter/combiner                                                              | 81                   |

|    | 5.3.3. PA design                                                                                     | 84                   |

|    | 5.3.4. Stability enhancement                                                                         | 85                   |

|    | 5.4. Measurement results                                                                             | 88                   |

|    | 5.5. Conclusion                                                                                      | 96                   |

| 6. | A triple-mode balanced linear CMOS power amplifier using a switched quadrature coupler               | 98                   |

|    | 6.1. Introduction                                                                                    | 98                   |

|    | 6.2. Average efficiency enhancement                                                                  | 100                  |

|    | 6.2.1. Analysis of four-port network operation under the termination oports                          | of two<br>100        |

|    | 6.2.2. Triple-mode operation                                                                         | 102                  |

|    | 6.2.2. Output matching network                                                                       | 102                  |

|    | 6.3. Advantages of balanced PA topology                                                              | 108                  |

|    | 6.4. Key design blocks                                                                               | 111                  |

|    | 6.4.1. IPD quadrature coupler                                                                        | 111                  |

|    | 6.4.2. RF switches                                                                                   | 118                  |

| 6.4.3. Amplifier design         | 120 |

|---------------------------------|-----|

| 6.5. Measurement results        | 123 |

| 6.6. Conclusion                 | 130 |

| 7. Conclusion                   | 132 |

| 7.1. Technical contributions    | 132 |

| 7.2. Future research directions | 134 |

| PUBLICATIONS                    | 135 |

| REFERENCES                      | 137 |

| VITA                            | 145 |

## LIST OF TABLES

|                                                                                | Page  |

|--------------------------------------------------------------------------------|-------|

| Table 1: Classes of amplifier operation.                                       | 12    |

| Table 2: Comparison of silicon versus GaAs technology.                         | 31    |

| Table 3: Network loss and relative magnitude ratio.                            | 48    |

| Table 4: Comparison of a single-ended PA versus a balanced PA.                 | 79    |

| Table 5: Comparison of linear PA performances for WCDMA applications           | 96    |

| Table 6: Comparison of recently reported multi-mode linear CMOS power amplifie | rs131 |

## LIST OF FIGURES

|                                                                                                                        | Page     |

|------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 1.1: (a) Estimates of the cellular handset market. (b) Mobile data growth.                                      | 2        |

| Figure 1.2: Evolution of 3GPP standards.                                                                               | 3        |

| Figure 1.3: Mobile handset sales by standard.                                                                          | 4        |

| Figure 1.4: Fundamental block diagram of a wireless communication system.                                              | 5        |

| Figure 1.5: Transmit power control depending on the distance between the user and base station.                        | the<br>6 |

| Figure 1.6: Probability distribution function of DG 09 voice and data                                                  | 7        |

| Figure 2.1: PA design parameters and trade-offs.                                                                       | 10       |

| Figure 2.2: Brief definition of the power amplifier.                                                                   | 11       |

| Figure 2.3: Distortion generations of a nonlinear PA.                                                                  | 13       |

| Figure 2.4: Definition of the third-order intercept point.                                                             | 15       |

| Figure 2.5: ACLR spectrum of the modulated carrier signal.                                                             | 16       |

| Figure 2.6: Basic concept of the predistortion system.                                                                 | 18       |

| Figure 2.7: Digital/analog predistortion system.                                                                       | 19       |

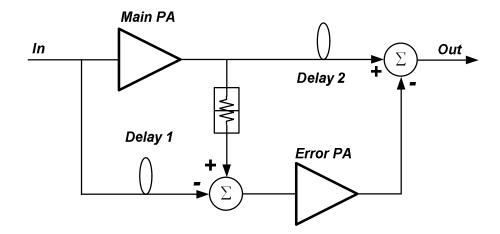

| Figure 2.8: Feedforward system.                                                                                        | 20       |

| Figure 2.9: RF feedback system.                                                                                        | 21       |

| Figure 2.10: Cartesian feedback system.                                                                                | 22       |

| Figure 2.11: Harmonic traps of the PA.                                                                                 | 23       |

| Figure 2.12: Concept of the capacitance-compensation technique.                                                        | 24       |

| Figure 2.13: Configuration of the Doherty PA.                                                                          | 25       |

| Figure 2.14: (a) Output power characteristics of the Doherty PA. (b) The efficiency characteristics of the Doherty PA. | 26       |

| Figure 2.15: Wilkinson power divider/combiner.                                                                         | 26       |

| Figure 2.16: Push-pull PA.                                                                                                                                                     | 27         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 2.17: Series combining transformer.                                                                                                                                     | 28         |

| Figure 2.18: Parallel combining transformer.                                                                                                                                   | 28         |

| Figure 3.1: Signal coupling in the silicon substrate.                                                                                                                          | 32         |

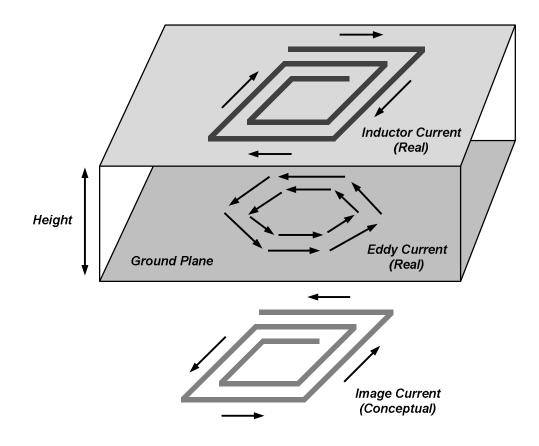

| Figure 3.2: Generation of the eddy current in the silicon substrate.                                                                                                           | 34         |

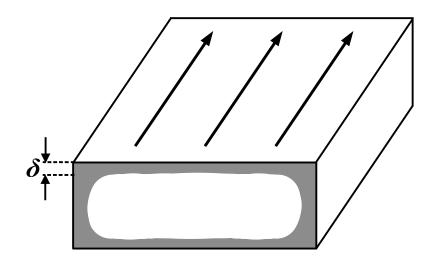

| Figure 3.3: Skin effects in the wide conductor.                                                                                                                                | 35         |

| Figure 3.4: Reliability problem in the cascode CMOS PA.                                                                                                                        | 36         |

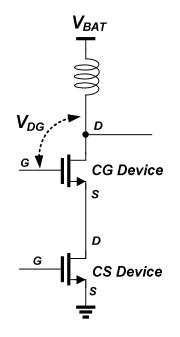

| Figure 4.1: Conventional cascode PA.                                                                                                                                           | 40         |

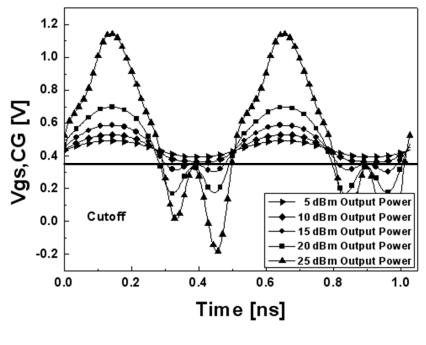

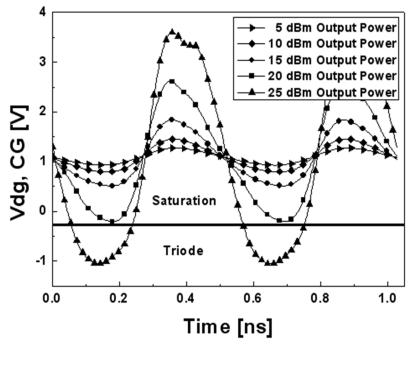

| Figure 4.2: Voltage waveforms of the CG device in cascode topology. (a) Voltage difference between the gate and the source. (b) Voltage difference between drain and the gate. | the<br>41  |

| Figure 4.3: Negative feedback system.                                                                                                                                          | 43         |

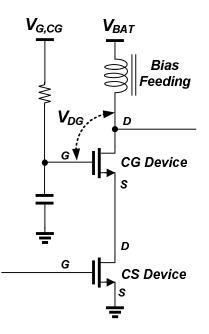

| Figure 4.4: Concept of the cascode feedback bias technique.                                                                                                                    | 46         |

| Figure 4.5: (a) Negative feedback loop formation by the fundamental signal. (b) negative feedback loop formation by the harmonic signals.                                      | tive<br>47 |

| Figure 4.6: Impedances depending on the node of the PA.                                                                                                                        | 51         |

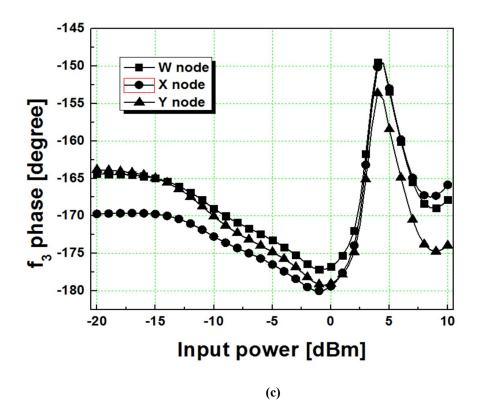

| Figure 4.7: Comparison of the signal phase depending on the nodes. (a) the fundamen signal. (b) the second harmonic signal. (c) the third harmonic signal.                     | ntal<br>55 |

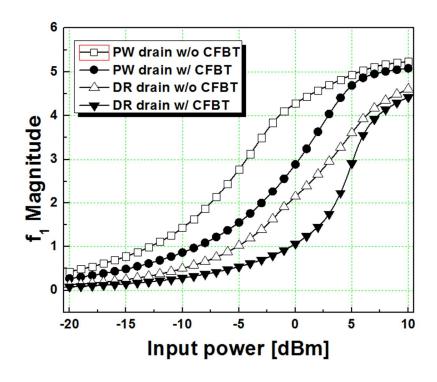

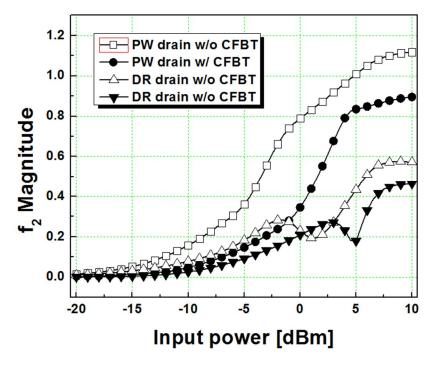

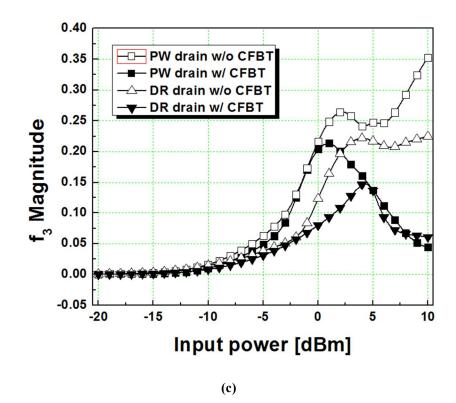

| Figure 4.8: Comparison of the signal magnitude. (a) the fundamental signal. (b) the second harmonic signal. (c) the third harmonic signal.                                     | 57         |

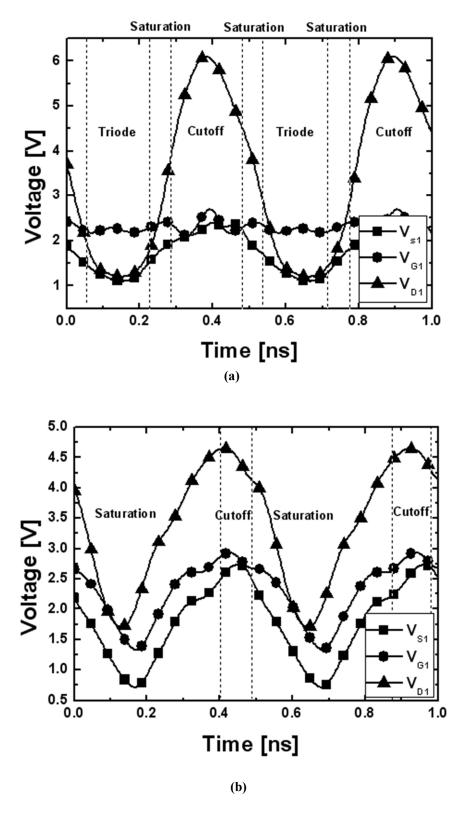

| Figure 4.9: Voltage waveforms of CG device. (a) without the cascode feedback bias technique. (b) with the cascode feedback bias technique.                                     | 58         |

| Figure 4.10: Comparison of the ratio of the operation region variations (a) turn-on vs turn-off. (b) triode vs saturation region during turn-on region.                        | 59         |

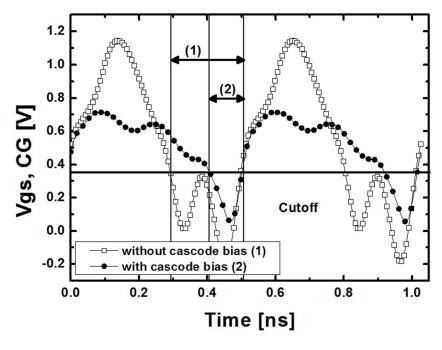

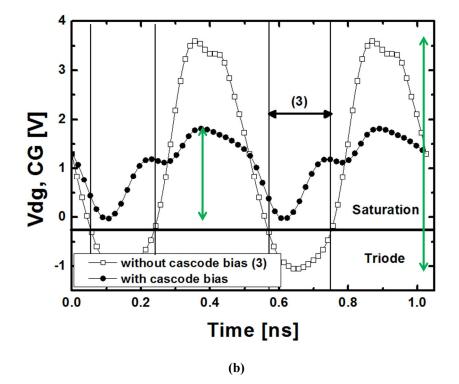

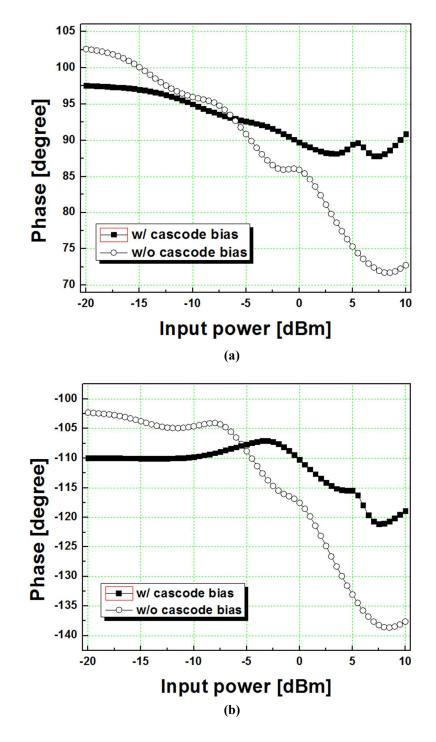

| Figure 4.11: The comparison of phase deviation of CG transistor. (a) the driver stage.                                                                                         | (b)<br>61  |

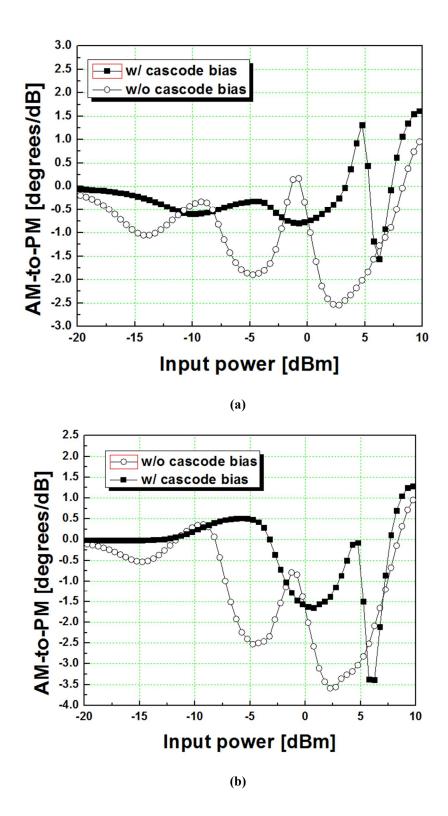

| Figure 4.12: The comparison of AM-to-PM of CG transistor. (a) the driver stage. (b) to power stage.                                                                            | the<br>62  |

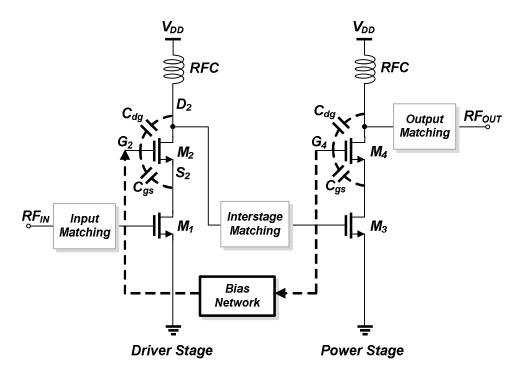

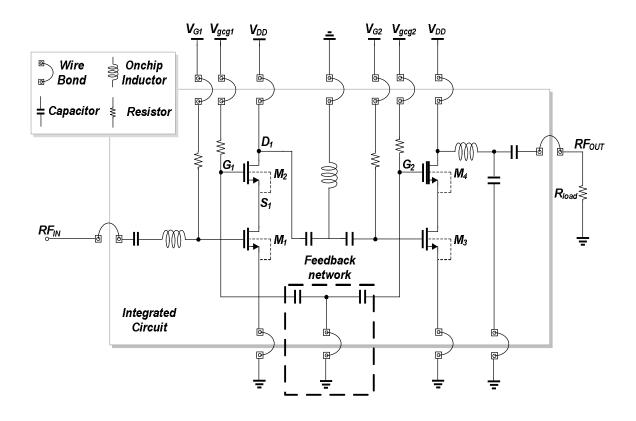

| Figure 4.13: Overall schematic of the CMOS PA with cascode feedback bias techniqu                                                                                              | ue.<br>64  |

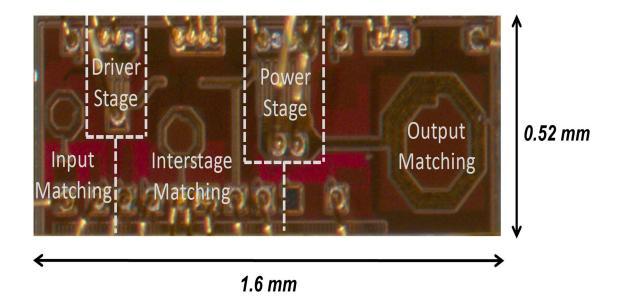

| Figure 4.14: Microphotograph of the linear CMOS PA.                                                                                                                                                                   | 65        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

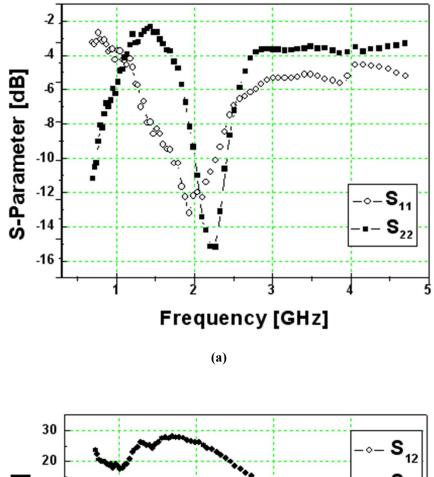

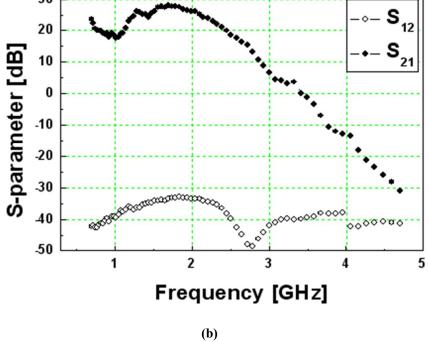

| Figure 4.15: Measured small signal performances of the PA with cascode feedback bia technique. (a) S <sub>11</sub> and S <sub>22</sub> . (b) S <sub>21</sub> and S <sub>12</sub> .                                    | as<br>66  |

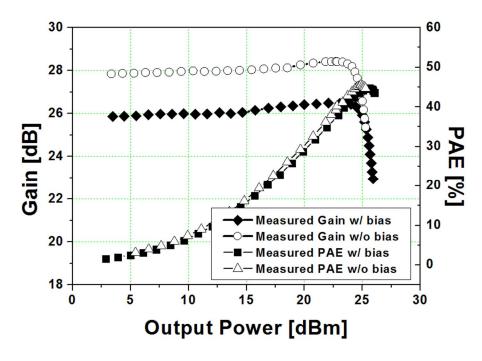

| Figure 4.16: Measured PA performance. (a) Comparison of the gain and the PAE with<br>and without the cascode feedback bias technique. (b) Comparison of IMD3<br>with and without the cascode feedback bias technique. | 68        |

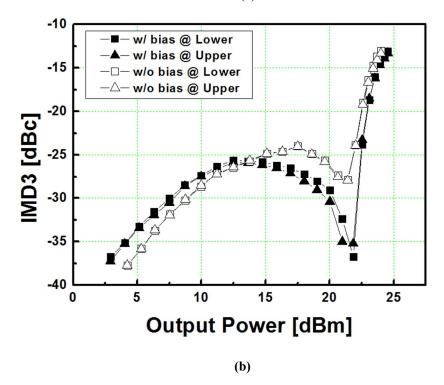

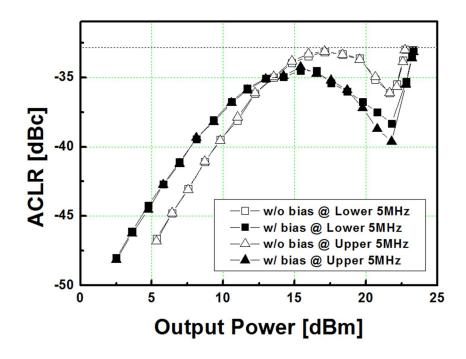

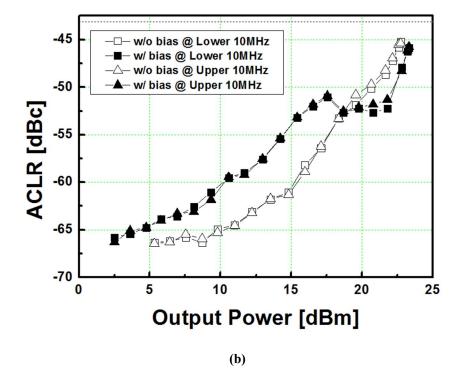

| Figure 4.17: Comparison of measured ACLR. (a) 5MHz offset. (b) 10MHz offset.                                                                                                                                          | 69        |

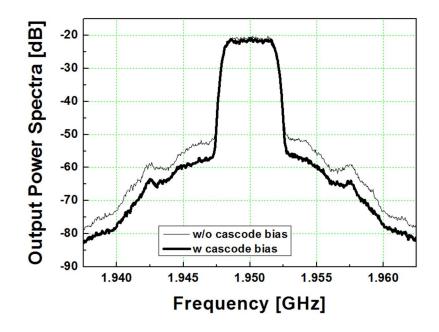

| Figure 4.18: Comparison of the measured ACLR spectra with and without the cascode feedback bias technique at 23.5 dBm output power.                                                                                   | e<br>70   |

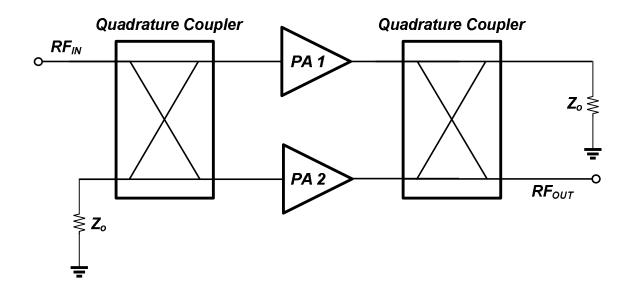

| Figure 5.1: Block diagram of the balanced PA.                                                                                                                                                                         | 73        |

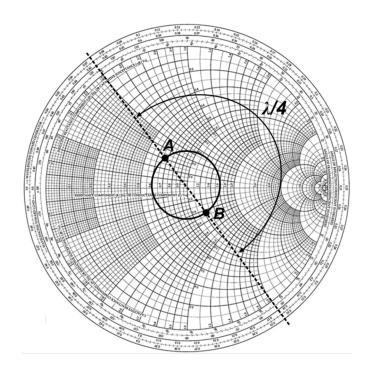

| Figure 5.2: Load impedance transition of a balanced topology in the Smith Chart.                                                                                                                                      | 75        |

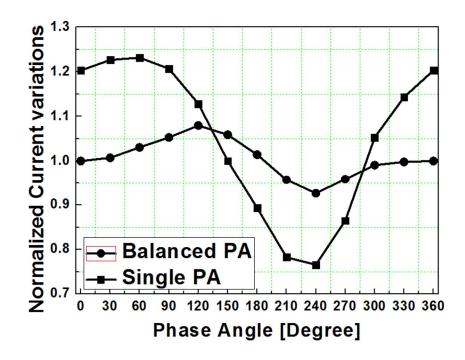

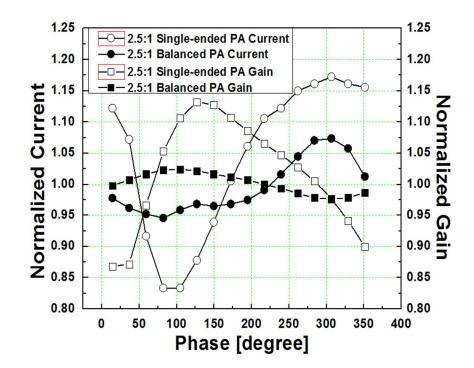

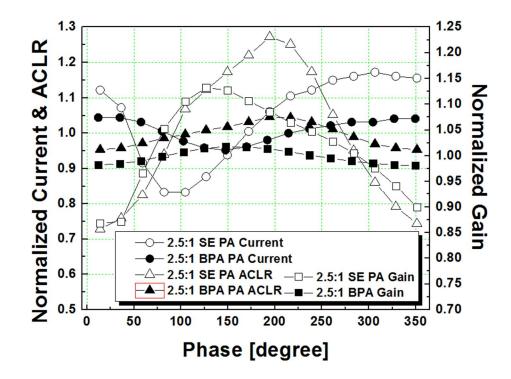

| Figure 5.3: Simulated normalized current variations of the balanced PA vs the single-<br>ended PA under a 2.5:1 VSWR condition.                                                                                       | 75        |

| Figure 5.4: Quadrature operation of the balanced PA.                                                                                                                                                                  | 76        |

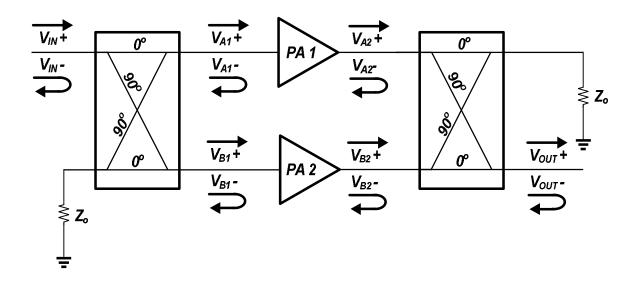

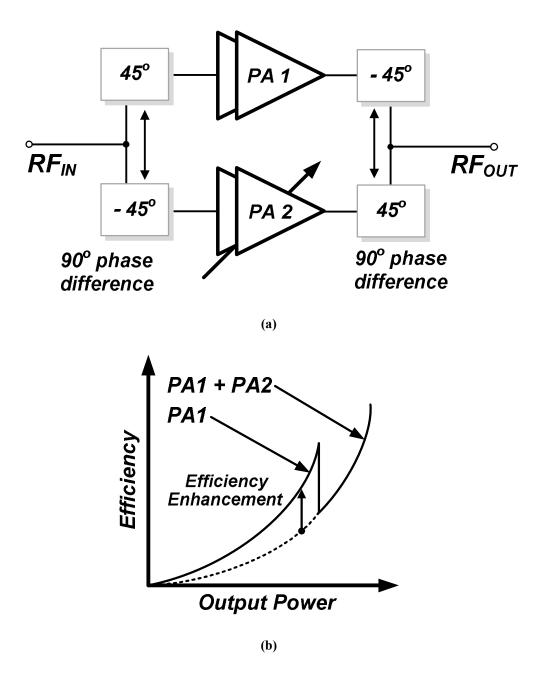

| Figure 5.5: The balanced CMOS PA (a) block diagram. (b) efficiency versus output power.                                                                                                                               | 80        |

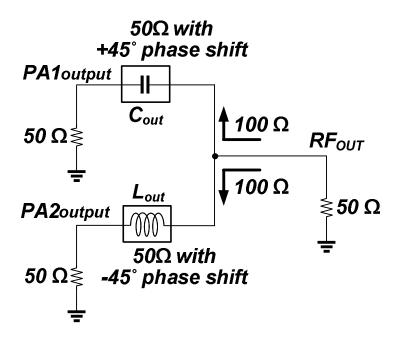

| Figure 5.6: L-C quadrature splitter/combiner.                                                                                                                                                                         | 82        |

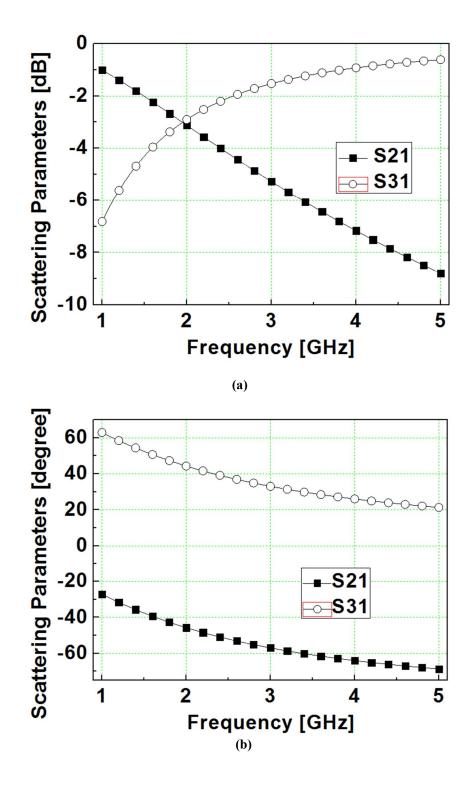

| Figure 5.7: Simulation results of the L-C quadrature splitter/combiner. (a) dB. (b) Phase                                                                                                                             | se.<br>83 |

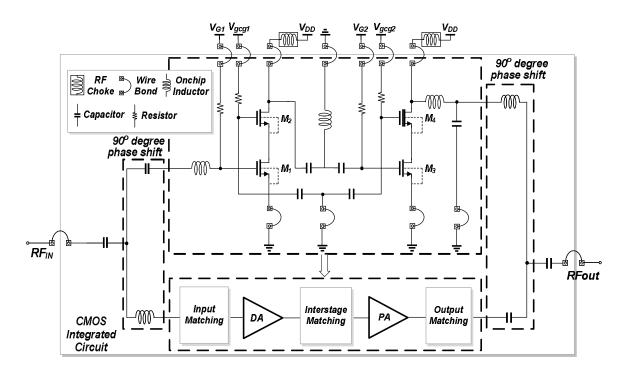

| Figure 5.8: Overall schematic diagram of the balanced PA.                                                                                                                                                             | 85        |

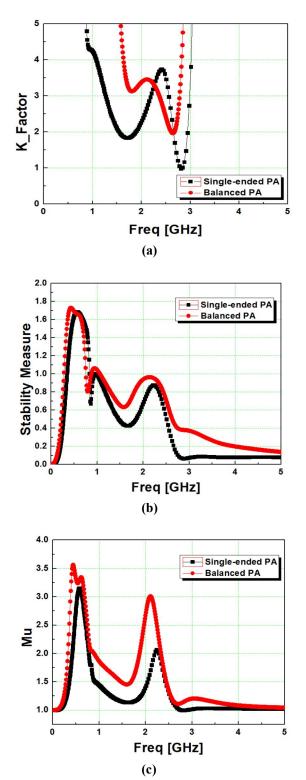

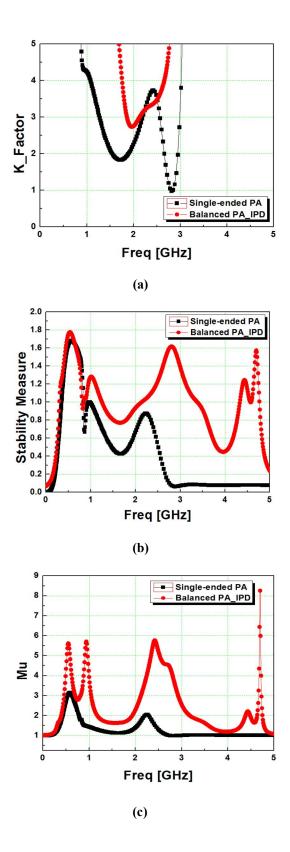

| Figure 5.9: Stability comparison of single-ended PA versus balanced PA using small signal. (a) K factor. (b) B factor. (c) Mu factor.                                                                                 | 86        |

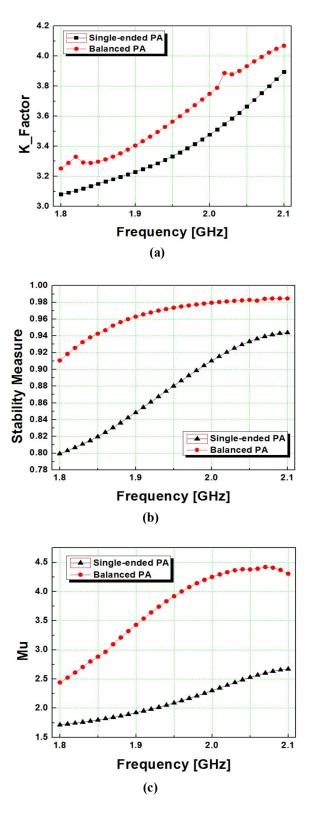

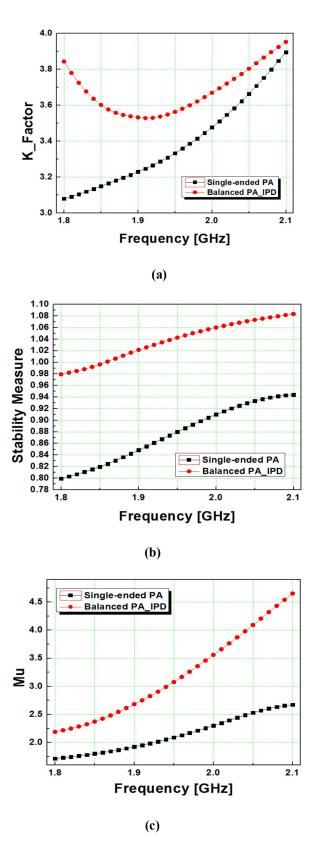

| Figure 5.10: Stability comparison of single-ended PA versus balanced PA using large signal. (a) K factor. (b) B factor. (c) Mu factor.                                                                                | 87        |

| Figure 5.11: Microphotograph of the balanced PA                                                                                                                                                                       | 88        |

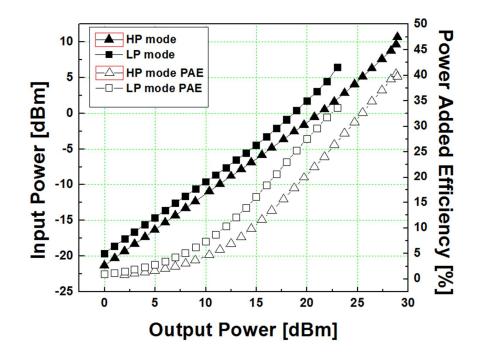

| Figure 5.12: Measured power sweep results of both HP and LP mode.                                                                                                                                                     | 89        |

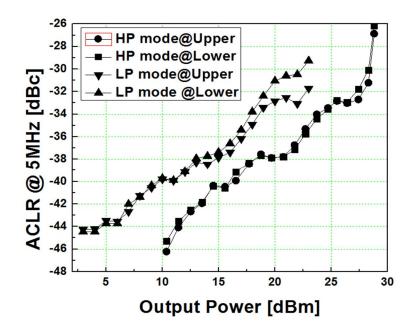

| Figure 5.13: Measured ACLR results of both HP and LP mode.                                                                                                                                                            | 90        |

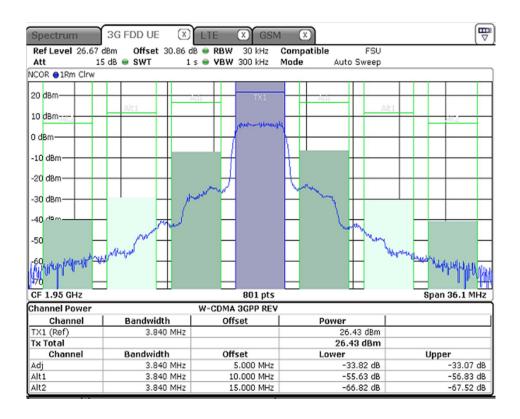

| Figure 5.14: Captured ACLR spectrum at 26.4 dBm output power.                                                                                                                                                         | 90        |

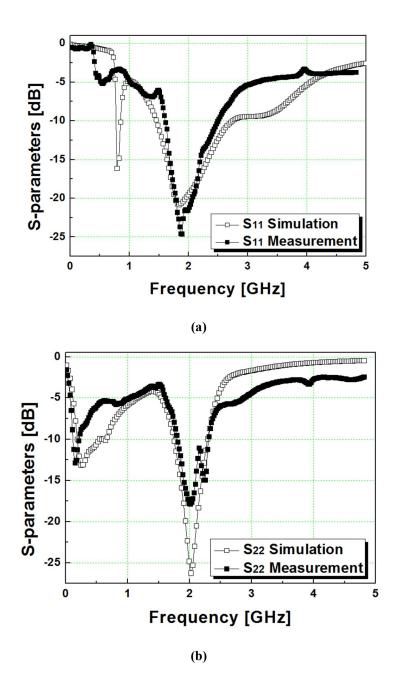

| Figure 5.15: Measured scattering parameters of the balanced PA. (a) $S_{11}$ . (b) $S_{22}$ .                                                                                                                         | 91        |

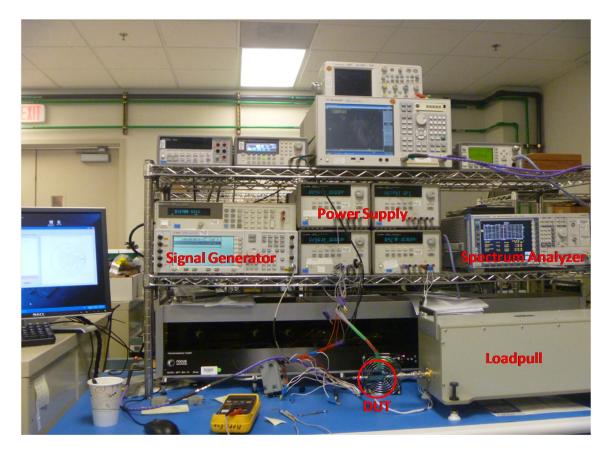

| Figure 5.16: Test bench for loadpull measurement and its equipments.                                                                                                                  | 92            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

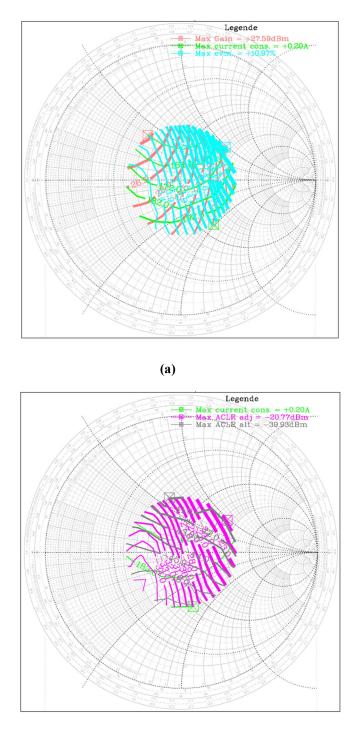

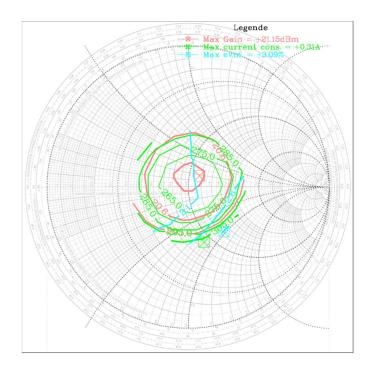

| Figure 5.17: Captured load insensitivity characteristics of single-ended PA upto 2.5:<br>VSWR condition. (a) gain, EVM and current. (b) ACLR of 5MHz and 10<br>spacing.               |               |

| Figure 5.18: Captured load insensitivity characteristics of balanced PA upto 2.5:1 VS condition. (a) gain, EVM and current. (b) ACLR of 5MHz and 10 MHz spacing.                      | SWR<br>94     |

| Figure 5.19: Comparison of balanced PA and single-ended PA under 2.5:1 VSWR condition.                                                                                                | 95            |

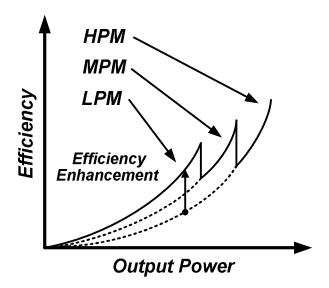

| Figure 6.1: Efficiency enhancements at lower power level by multi-mode operations                                                                                                     | . 99          |

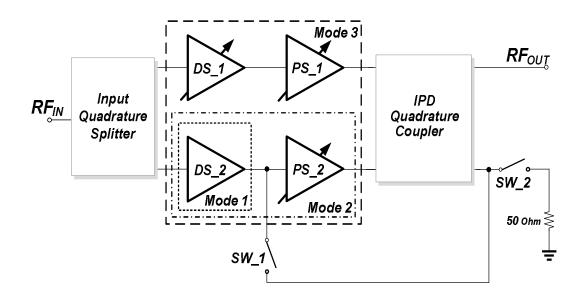

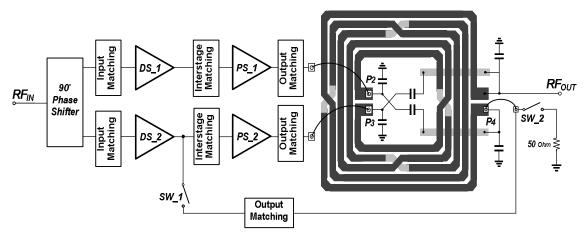

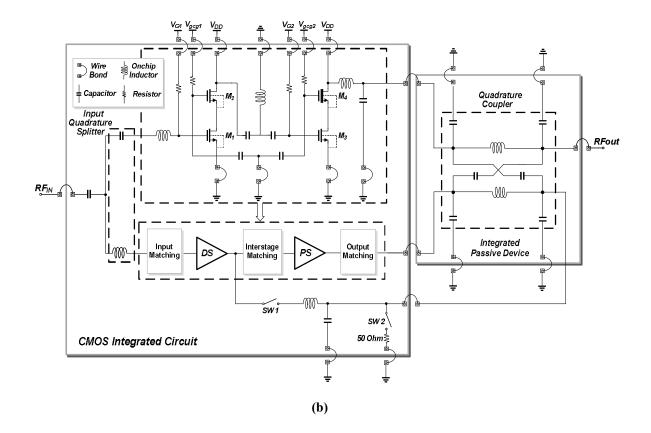

| Figure 6.2: Block diagram of the triple-mode balanced PA with a switched quadratur coupler.                                                                                           | re<br>99      |

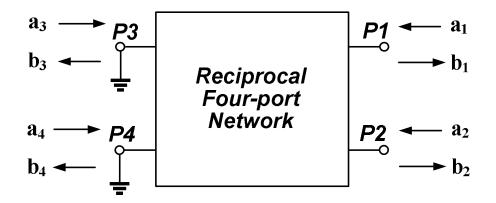

| Figure 6.3: Reciprocal four-port network with terminations of ports 3 and 4.                                                                                                          | 100           |

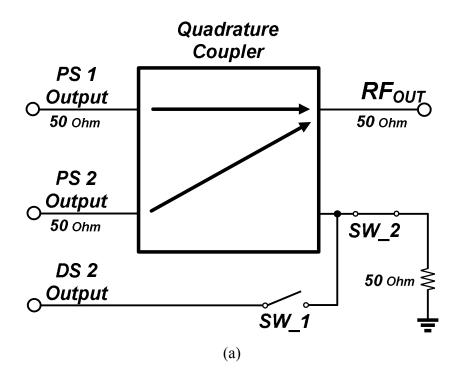

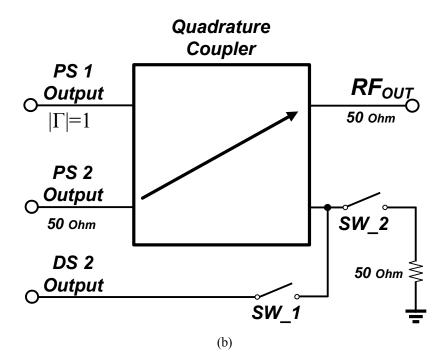

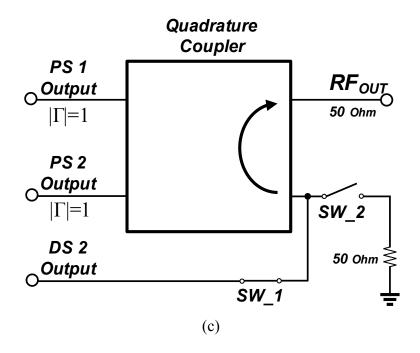

| Figure 6.4: Switched quadrature coupler operations (a) High power mode. (b) Middle power mode. (c) Low power mode                                                                     | e<br>106      |

| Figure 6.5: The Quadrature coupler operation depending on the impedance of ISO powhen the THRU port is terminated.                                                                    | ort<br>106    |

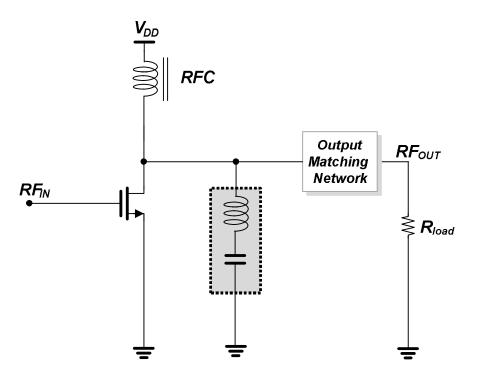

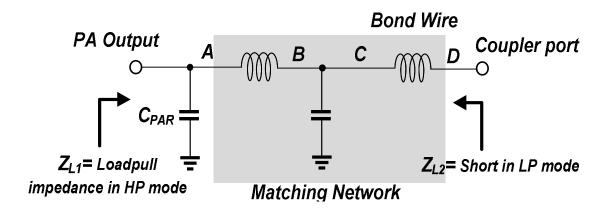

| Figure 6.6: PA output matching network.                                                                                                                                               | 107           |

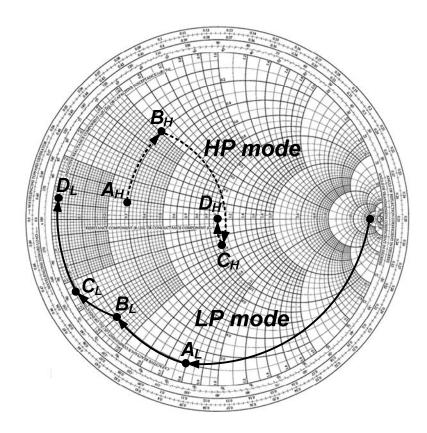

| Figure 6.7: Impedance transitions depending on the power mode.                                                                                                                        | 108           |

| Figure 6.8: Stability comparison of single-ended PA versus balanced PA using small signal. (a) K factor. (b) B factor. (c) Mu factor.                                                 | 109           |

| Figure 6.9: Stability comparison of single-ended PA versus balanced PA using large signal. (a) K factor. (b) B factor. (c) Mu factor.                                                 | 110           |

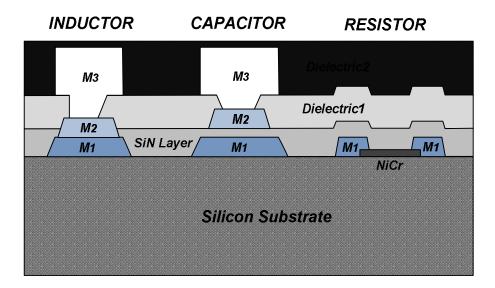

| Figure 6.10: Silicon integrated passive device (IPD) process.                                                                                                                         | 112           |

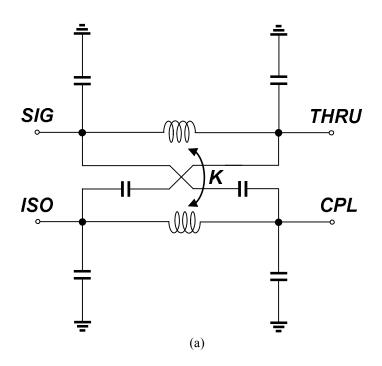

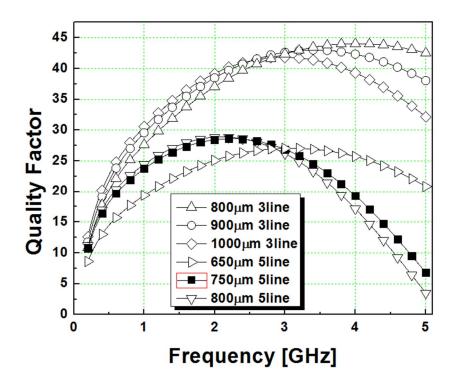

| Figure 6.11: Implementation of the output quadrature coupler (a) Simplified schemat<br>the designed quadrature coupler. (b) Simplified diagram of the designed<br>quadrature coupler. | tic of<br>113 |

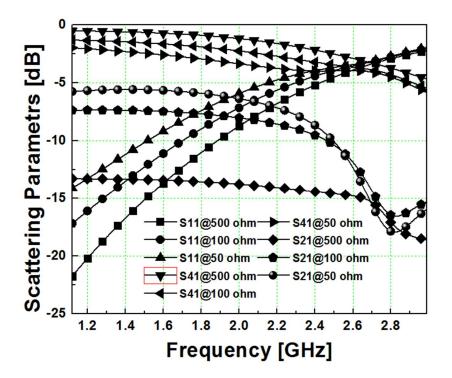

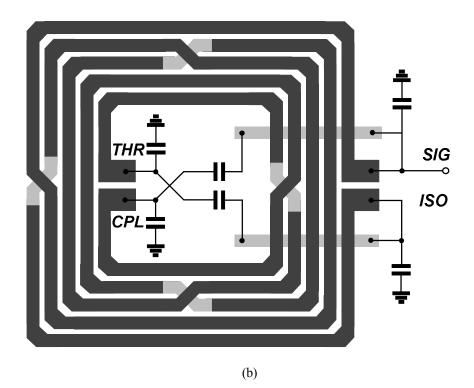

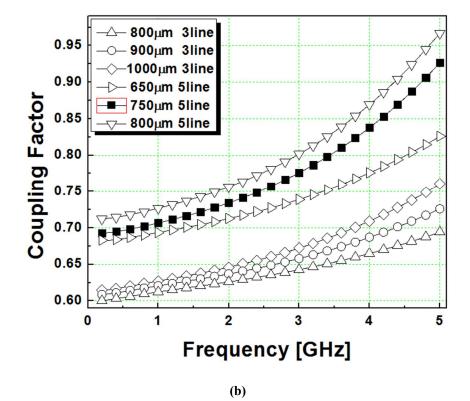

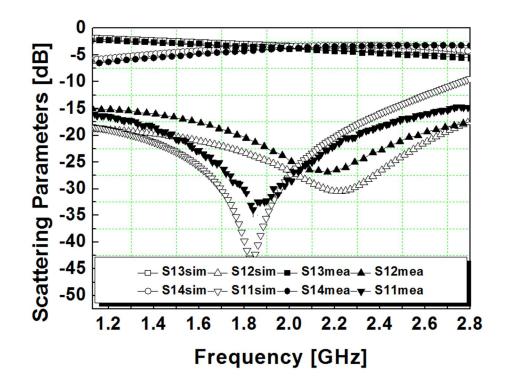

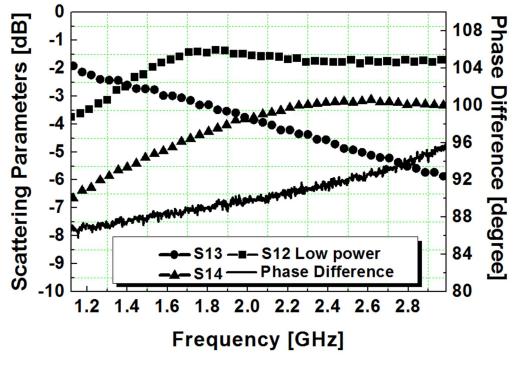

| Figure 6.12: EM simulation results of the IPD quadrature coupler (a) The quality fac<br>(b) The coupling coefficient.                                                                 | tor.<br>115   |

| Figure 6.13: Measurement results of the IPD quadrature coupler.                                                                                                                       | 117           |

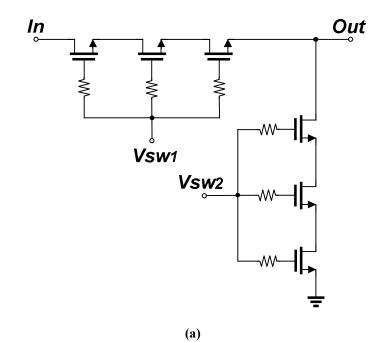

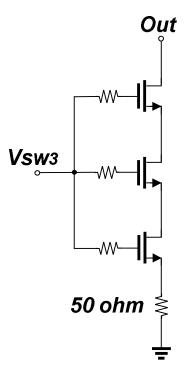

| Figure 6.14: RF switches for the low-power mode operation (a) Schematic of switch (b) Schematic of switch 2.                                                                          | 1.<br>119     |

| Figure 6.15: Triple-mode balanced PA (a) Simplified block diagram. (b) Overall schematic of the designed PA.                                           | 121       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

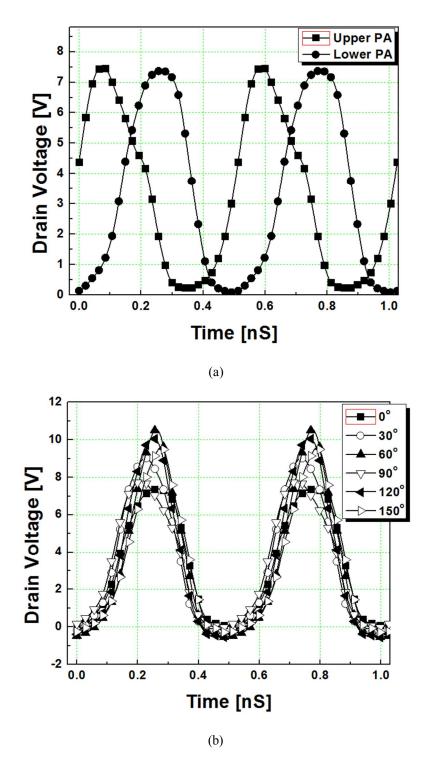

| Figure 6.16: Simulated drain voltage waveforms. (a) Both PA's waveform when the power is 7 dBm. (b) Waveforms of lower path PA under 10:1 of VSWR      | input     |

| condition.                                                                                                                                             | 122       |

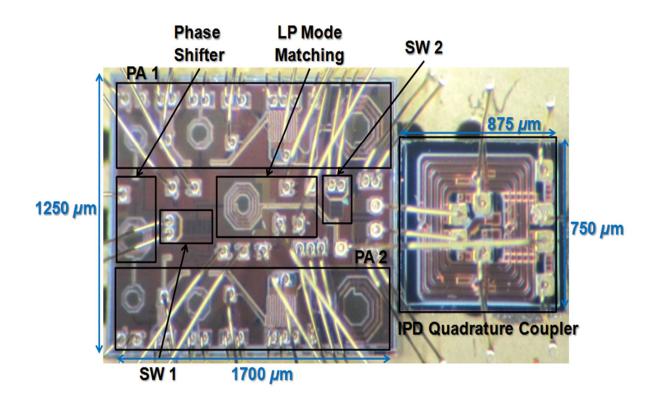

| Figure 6.17: Microphotograph of the designed PA and the IPD quadrature coupler.                                                                        | 123       |

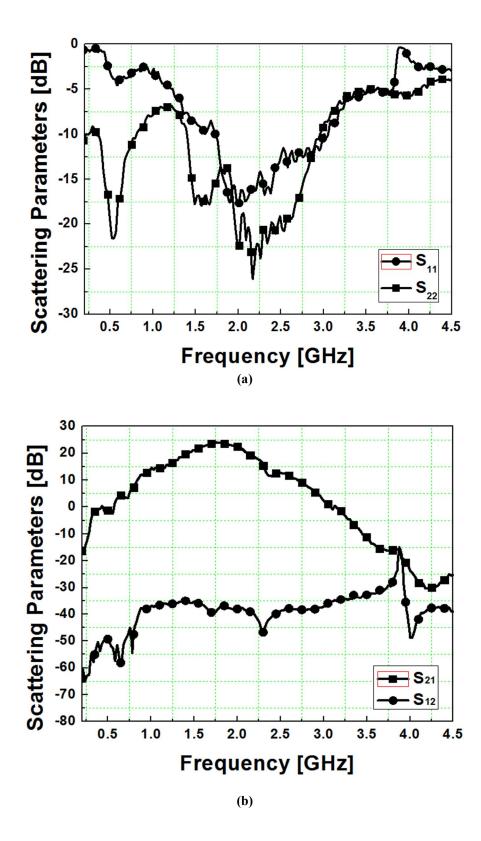

| Figure 6.18: Measured small signal performances of the PA (a) $S_{11}$ and $S_{22}$ (b) $S_{21}$ a $S_{12}$ .                                          | nd<br>125 |

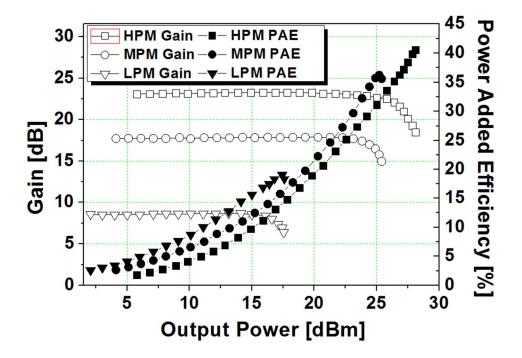

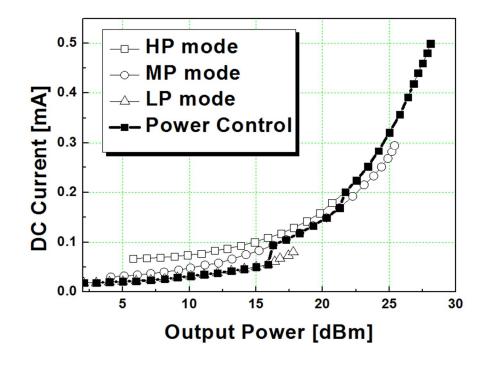

| Figure 6.19: Measurement results of the PAE and the gain.                                                                                              | 126       |

| Figure 6.20: Measurement results of the current consumption.                                                                                           | 127       |

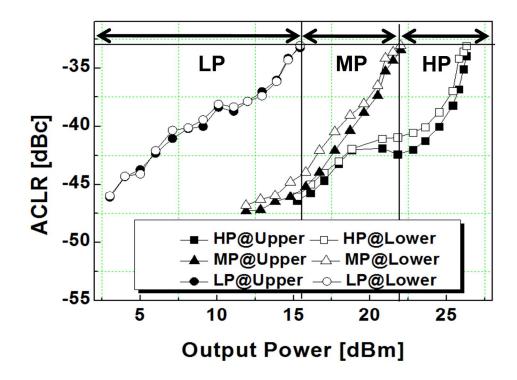

| Figure 6.21: Measured results of a 5 MHz offset ACLR.                                                                                                  | 127       |

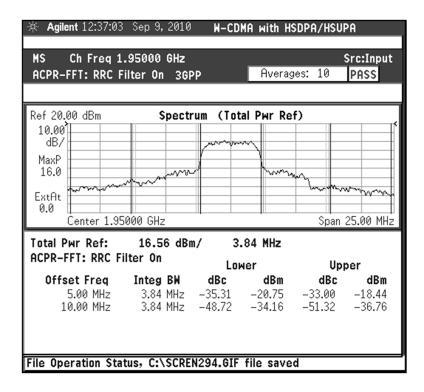

| Figure 6.22: Output spectrum with the 3GPP modulated signal at 26.6 dBm.                                                                               | 128       |

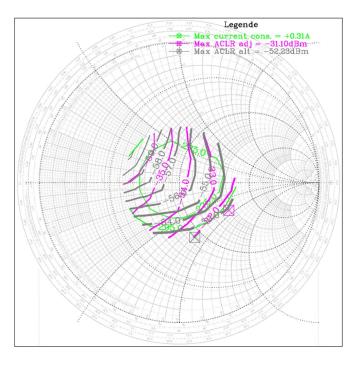

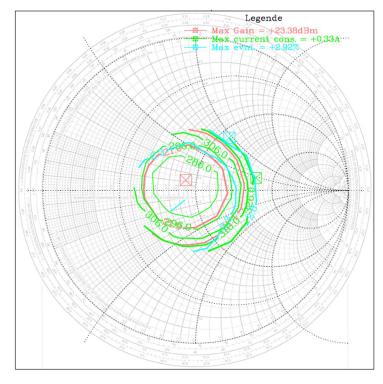

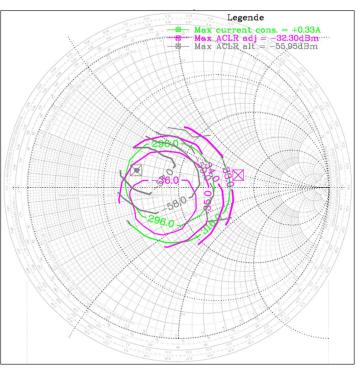

| Figure 6.23: Captured load insensitivity characteristics of balanced PA upto 2.5:1 V condition. (a) gain, EVM and current. (b) ACLR of 5MHz and 10 MHz |           |

| spacing.                                                                                                                                               | 129       |

| Figure 6.24: Comparison of balanced PA and single-ended PA under 2.5:1 VSWR condition.                                                                 | 130       |

## LIST OF SYMBOLS AND ABBREVIATIONS

| AM-AM            | amplitude-to-amplitude                  |

|------------------|-----------------------------------------|

| AM-PM            | amplitude-to-phase                      |

| ACLR             | adjacent channel leakage ratio          |

| CDMA             | code division multiple access           |

| CE               | collector efficiency                    |

| CG               | common gate                             |

| CMOS             | complementary metal oxide semiconductor |

| CS               | common source                           |

| DA               | driver amplifier                        |

| DE               | drain efficiency                        |

| EDGE             | enhanced data rates for GSM evolution   |

| EVM              | error vector magnitude                  |

| GaAs             | gallium arsenide                        |

| GSM              | global system for mobile                |

| HBT              | hetero-junction bipolar transistor      |

| HEMT             | high electron mobility transistor       |

| HP               | high-power                              |

| IC               | integrated circuit                      |

| IP <sub>3</sub>  | third-order intercept point             |

| IL               | insertion loss                          |

| IMD <sub>3</sub> | third order intermodulation distortion  |

| InGaP            | indium gallium phosphide                |

| LP               | low-power                                         |

|------------------|---------------------------------------------------|

| LTE              | long term evolution                               |

| MIM              | metal-insulator-metal                             |

| MOSFET           | metal oxide semiconductor field effect transistor |

| MP               | medium-power                                      |

| P <sub>1dB</sub> | output referred 1-dB compression point            |

| PA               | power amplifier                                   |

| PAE              | power added efficiency                            |

| PAPR             | peak-to-average power ratio                       |

| РСВ              | printed circuit board                             |

| PDF              | probability distribution function                 |

| P <sub>sat</sub> | saturated (peak) output power level               |

| Q                | quality factor                                    |

| RF               | radio frequency                                   |

| SiGe             | silicon germanium                                 |

| SNR              | signal-to-noise ratio                             |

| SRF              | self-resonant frequency                           |

| WCDMA            | wideband CDMA                                     |

| WiMAX            | worldwide interoperability for microwave access   |

| WLAN             | wireless local area network                       |

| 3GPP             | the 3rd generation partnership project            |

#### SUMMARY

The rapidly expanding wireless market requires low cost, high integration and high performance of wireless communication systems. Complementary metal oxide semiconductor (CMOS) technology provides benefits of cost effectiveness and higher levels of integration. However, the design of highly efficient linear CMOS power amplifier (PA) that meets the requirement of advanced communication standards is a challenging task because of the inherent difficulties in CMOS technology. The objective of this research is to realize PAs for wireless communication systems that overcome the drawbacks of CMOS process, and to develop design approaches that satisfy the demands of the industry.

In this dissertation, a cascode feedback bias technique is proposed for improving linearity and reliability of the multi-stage cascode CMOS PA. A fully-integrated single chip linear PA in a 0.18- $\mu$ m CMOS process is implemented with the technique. This PA achieved 46.4% of peak PAE at 26 dBm output power and 40% of linear PAE at 23.5 dBm output power. In addition, to achieve load variation immunity characteristic and to enhance matching and stability, a fully-integrated balanced PA is implemented in a 0.18- $\mu$ m CMOS process. Measurement results show the excellent load variation immunity characteristics. This dissertation also proposed a triple-mode balanced PA using a switched quadrature coupler. The method that uniquely utilizes the isolation port of the quadrature coupler as a signal path was analyzed. With the triple-mode operation, this work significantly reduced quiescent current and further improved the efficiency in the back-off power. For low losses and a high quality factor of passive output combining, a

transformer-based quadrature coupler is implemented using integrated passive device (IPD) process in this work. Various practical approaches for linear CMOS PA are suggested with the verified results, and they demonstrate the potential PA design approach for WCDMA applications using a standard CMOS technology.

### **CHAPTER 1**

## INTRODUCTION

### 1.1 Technology trends

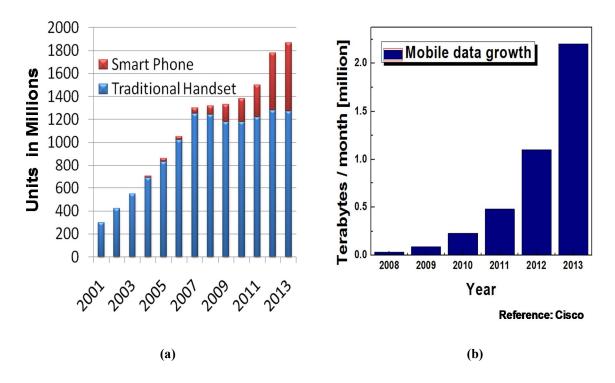

Advances in semiconductor technology have prompted rapid growth in the wireless communication industry over the past twenty years. With emerging technologies, wireless mobile communication systems have undergone rapid development and become widely distributed, establishing their position as necessities in daily life. As market trends accelerate, users demand not only voice and simple messaging, but also various multimedia data services, necessitating the convergence of technologies, including video, music, camera, gaming, global positioning system (GPS), and mobile Internet access into one mobile device. The advent of smartphones has made communication using handset possible, exposing a new paradigm of communications. Smartphones allow data communications anytime and anywhere. Figure 1.1 (a) shows the growth and the forecast of smartphones. In the expanding wireless communication handset market, the number of smartphones is continuously increasing while the number of traditional handsets has become stagnant. Figure 1.1 (b) shows the forecast of the overall mobile data growth. As data communications using mobile handsets continue to expand, the market demand for higher data-rate of wireless communication systems is accelerating.

Figure 1.1 (a) Estimates of the cellular handset market. (b) Mobile data growth.

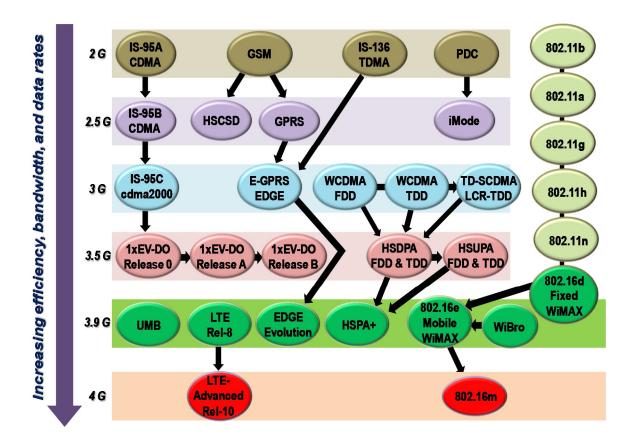

The rapid development of technology has compelled the release of standards for second generation (2G), third generation (3G), and fourth generation (4G) wireless communication systems. The standards include global system for mobile communications (GSM), code division multiple access (CDMA), Enhanced Data rates for GSM Evolution (EDGE), wideband CDMA (WCDMA), ultra mobile broadband (UMB), worldwide interoperability for microwave access (WiMAX), and long term evolution (LTE). Figure 1.2 shows the evolution of the 3rd generation partnership project (3GPP) standards. From 2G to 4G, the standards have evolved toward increasing efficiency, bandwidth, and data rates. For example, the 4G LTE standard requires peak-data rate up to 326.4 Mbit/s downlink and 86.4 Mbit/s uplink, while the 3G WCDMA standard requires peak-data rate of 384 Kbit/s for downlink and uplink.

Figure 1.2 Evolution of 3GPP standards.

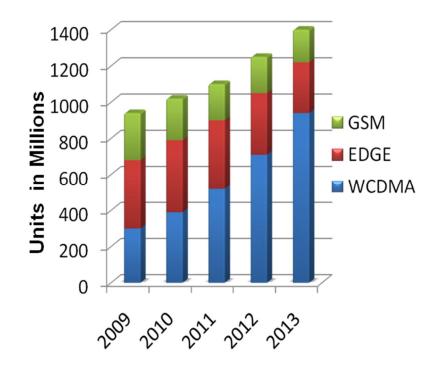

Figure 1.3 shows mobile phone sales by standards. The ratio of WCDMA applications, which have higher data rate communication than 2G, is continuously increasing and the 3G standards are becoming dominant in the mobile handset market.

In summary, the trend in the rapidly developing industry has moved toward the efficient operation and the high-data rate wireless communication systems. The WCDMA and the latest standard applications, which have higher data rate communications, will dominate the market and the necessity of linear PA that supporting the standard applications will increase.

Figure 1.3 Mobile handset sales by standard.

#### 1.2 Motivation

The wireless communication industry is becoming increasingly competitive in price as well as performance of its communication systems. For the price competitiveness, the complementary metal-oxide-semiconductor (CMOS) technology has lower wafer cost per area than other III-V compound technology. In addition, because most analog and digital circuits have been implemented by CMOS technology, this technology has been deemed an excellent candidate for benefiting both cost and performance through reductions in the front-end module costs and a high level of system integration.

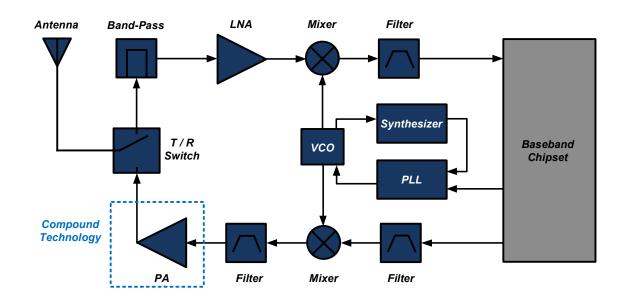

Figure 1.4 presents a fundamental block diagram of a wireless communication system. Progress in CMOS technology has enabled the construction of most RF block circuits with enhanced performance in CMOS process. The complete integration of a

single-chip transmitter in CMOS technology, however, is still constricted by power amplifiers (PAs) because of the inherent challenges of CMOS technology such as low breakdown voltage, low transconductance, poor linearity, an inaccurate RF model, and low substrate resistivity [1]. Most of the III-V compound technologies have been dominant in the PA handset market for various applications. However, because of the attractive advantages of low cost and high integration in CMOS technology, there has been a great deal of effort to overcome the drawbacks in CMOS PA and to implement a fully-integrated single-chip wireless system.

Figure 1.4 Fundamental block diagram of a wireless communication system.

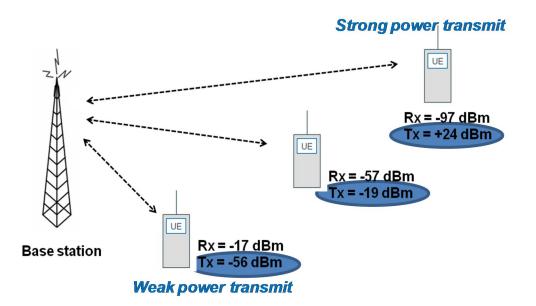

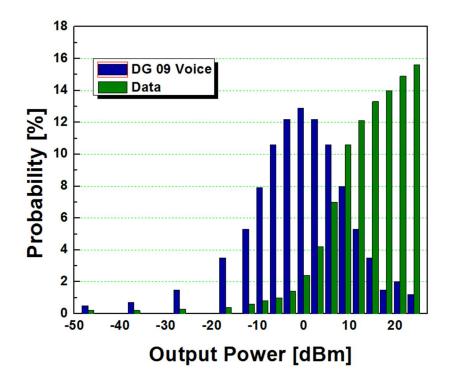

As a second motivation of this work, the necessity of multi-mode operation is considered. With the mobility of wireless communication systems, the operating power of the systems varies. Figure 1.5 shows the basic idea of transmit power control for mobile devices. The mobile device transmits various levels of power, depending on the distance from mobile devices to base stations. That is, the mobile device transmits strong power to communicate with a base station that is far away while it transmits weak power to one in a short distance, thereby continuously varying the operating output power of the wireless communication system. The probability of the system operation of transmit power control is studied for the efficient operation of the system, and the probability distribution functions (PDF) of DG 09 voice and data are shown in Figure 1.6. According to the PDF of the transmitted signal, the PA is more likely to be operated at a lower power level for voice communication and at a peak power level for data communication [2][3]. To extend the battery life of mobile devices, the efficiency of PAs must be optimized at both back-off power and peak power levels. Multi-mode operations can provide enhancement of the PA efficiency at a low output power level as well as minimizing quiescent currents, thereby increasing the battery life of the whole system.

Figure 1.5 Transmit power control depending on the distance between the user and the base station.

Lastly, the load variation immunity of wireless system is contemplated. The changes of the operating environment conditions of wireless communication system, such as the changes in antenna impedance and contacts with conductive or grounded surfaces can cause load impedance variations. The load impedance mismatch under uncontrolled environment conditions can degrade the system performance and even cause critical reliability problems of wireless communication devices. The Apple's smartphone, Iphone 4, which experienced performance degradations by touching certain places of the phone, is an example for why the system should be immune to load impedance variation.

Figure 1.6 Probability distribution function of DG 09 voice and data.

This dissertation examines highly efficient CMOS PAs for wireless communication systems. In its examination, it covers the background of CMOS PA design, and the design parameters of the PA, including linearity, efficiency, gain, reliability, output power, and stability, all of which contribute to optimal PA performance. Then it analyzes the challenges of CMOS technology for PA design, and more specifically, investigates balanced PA configuration for load insensitivity and efficiency enhancement in back-off output power level by employing multi-mode operations.

This dissertation focuses on the following and includes three original contributions:

- Development of a novel cascode feedback bias technique that is easily applicable to multi-stage cascode topology, and that improves linearity and alleviates the reliability issue of the PA.

- Implementation of the first highly efficient balanced CMOS PA that addresses the load immunity of WCDMA applications.

- 3. Introduction of the first triple-mode balanced CMOS PA using a switched integrated passive device (IPD) quadrature coupler, including an analysis and demonstration of the concept of utilizing the isolation port of the quadrature coupler as a signal path with RF switches.

## 1.3 Organization of dissertation

This dissertation is organized as follows:

Chapter 1 presents the technology trends and market demands for wireless communication systems and introduces the motivation of this research for a highly efficient CMOS PA with improvement of linearity and reliability, load immunity and multi-mode operation.

Chapter 2 reviews the background knowledge of the PA and prior attempts to overcome the obstacles to PA design.

Chapter 3 discusses the challenges of CMOS PA design, including the lossy substrate, the low quality factor of passive components, reliability, and nonlinearity issues of CMOS technology.

Chapter 4 proposes the cascode feedback bias technique that enhances linearity and alleviates the reliability problem of the single-ended CMOS PA, and presents a highly efficient linear CMOS PA for the WCDMA application.

Chapter 5 presents the balanced PA topology, analyzes its advantages, which are load immunity, matching network improvement, constant gain and enhanced stability, and demonstrates the implementation of a balanced linear CMOS PA for WCDMA applications.

Chapter 6 introduces the triple-mode balanced linear CMOS power amplifier using switched quadrature coupler. To enhance the efficiency at back-off power levels and reduce quiescent current, the PA utilizes triple-mode operations, and employs a balanced topology for load insensitivity. To obtain low loss and a high quality factor (Q) of passive output combining, a transformer-based quadrature coupler is implemented using a silicon-based integrated passive device (IPD) process.

Chapter 7 concludes the dissertation by summarizing the main contributions.

## **CHAPTER 2**

## **RF POWER AMPLIFIERS**

### 2.1 Introduction

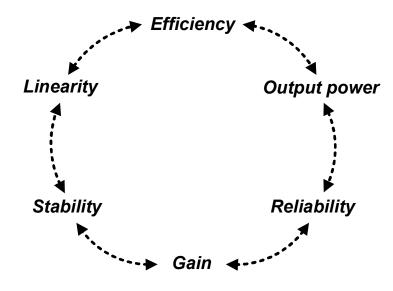

Achieving desirable performance of a PA entails various RF PA challenges and design considerations. The key design parameters of the RF PA can be classified into efficiency, linearity, gain, output power, reliability, and stability, all of which involved trade-offs as shown in Figure 2.1. This chapter summarizes the background of the RF PA and reviews past approaches to enhancing its efficiency, linearity, and output power.

Figure 2.1. PA design parameters and trade-offs.

## 2.2 Key design factors of RF PA

#### 2.2.1 Efficiency

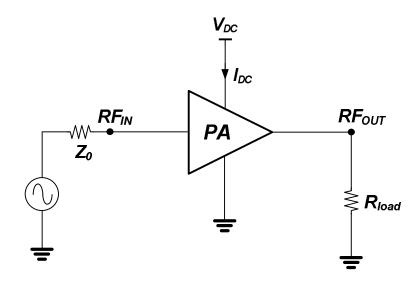

As a brief definition, the PA is a block that converts the DC power to RF power by amplifying input signals, as shown Figure 2.2. Because the PA is the most "powerhungry" block in the wireless communication system, efficiency is considered the most important factor in the PA performance. The efficiency of the PA is defined as

$$\eta = \frac{P_{OUT}}{P_{DC}} \tag{2.1}$$

where  $P_{OUT}$  is the power delivered to the output and  $P_{DC}$  is the power consumption of the PA, and it is called the drain efficiency (DE) for the PAs with FET transistors or the collector efficiency (CE) for the PAs with BJT transistors.

Figure 2.2. Brief definition of a power amplifier.

The power-added efficiency (PAE), the ratio of the RF power of the PA to the DC power consumption, is also defined as equation (2.2). The PAE includes the gain information of the PA, and it is almost same with DE/CE when the gain is high enough.

$$\eta_{added} = \frac{P_{OUT} - P_{IN}}{P_{DC}}$$

(2.2)

where  $P_{IN}$  is the power delivered from the input.

The maximum efficiency of the PAs is determined by the operation of the PA that is based on the voltage and current waveforms at the output. The classes of the PAs categorize into two types: linear PA and switching PA operations. The linear PA operation includes class A, AB, B, and C, while the switching PA operation includes class D, E and F. Table 1 summarizes the classes of PA operations in terms of efficiency, and linearity.

TABLE 1. CLASSES OF AMPLIFIER OPERATION.

| Classification               | Α         | AB      | В        | С    | D    | Ε    | F    |

|------------------------------|-----------|---------|----------|------|------|------|------|

| Maximum<br>Efficiency<br>(%) | 50        | 50-78.5 | 78.5     | 100  | 100  | 100  | 100  |

| Linearity                    | Excellent | Good    | Moderate | Poor | Poor | Poor | Poor |

As presented in Table 1, the efficiency and the linearity are in trade-off for the linear PA operation. Because both efficiency and linearity can be optimized in the class AB operation, it is the most popular choice for linear PA designs. Moreover, class AB operation has a slightly larger fundamental current amplitude compared to class A or B operations, accompanying the increased output power to the load.

#### 2.2.2 Linearity

Because the PA is a nonlinear component, the linearity is one of the key features of the PA performances. The linearity of the PA can be represented by the 1-dB gain compression point ( $P_{1dB}$ ), the amplitude-to-amplitude distortion (AM-AM), the amplitude-to-phase distortion (AM-PM), the third-order intercept point (IP3), the error vector magnitude (EVM) and the adjacent channel leakage ratio (ACLR) for out of band.

Figure 2.3. Distortion generations of a nonlinear PA.

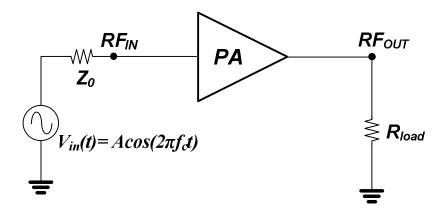

The distortions of the PA can be mainly caused by 1) clipping at the large AC signal swings and 2) disrupting by the non-linear transconductance at small AC signal swings. Moreover, the transconductance distortion at the small AC signal swings (i.e., low amplitude signals) can be categorized into the harmonic distortion by a single carrier and the intermodulation distortion by multi-carriers (i.e., modulated signals). Figure 2.3 shows the harmonic generations of the non-linear PA by a single carrier of  $Acos(2\pi f_c t)$ . The harmonic generation is derived by the power series, as shown in equation (2.3), (2.4) and (2.5).

$$V_{out}(t) = G[v_{in}(t)] = g_0 + g_1 v_{in}(t) + g_2 v_{in}(t)^2 + g_3 v_{in}(t)^3 + \cdots$$

(2.3)

$$V_{out}(t) = g_0 + g_1 A \cos(2\pi f_c t) + g_2 A^2 \cos^2(2\pi f_c t) + g_3 A^3 \cos^3(2\pi f_c t) + \cdots$$

(2.4)

$$V_{out}(t) = g_0 + \frac{g_2 A^2}{2} + (g_1 A + \frac{3g_3 A^3}{4})\cos(2\pi f_c t) + \frac{g_2 A^2}{2}\cos(4\pi f_c t) + \frac{g_3 A^3}{4}\cos(6\pi f_c t) + \cdots$$

(2.5)

From the power series expansion,  $g_3$  term and higher order terms cause the distortion of the linearity, specifically, the dominated  $g_3$  term at the high power level results in the gain compression because of its negative sign. General wireless communication standards require the specific amount of power back-off to meet the stringent IMD or ACLR specifications. The  $P_{1dB}$  can be derived from the transconductance characteristic, as shown in equation (2.6).

$$P_{1dB} = \frac{g_1^2 A_{1dB}^2}{2R_L} \cdot 10^{-1/10}$$

(2.6)

where  $A_{1dB}$  is the input power level that the fundamental term is decreased by 1-dB.

The third order intermodulation distortion (IMD3), which is generated by two tone carriers, is an important parameter that indicates the linearity of the PA. While the most of harmonic signals and higher frequency signals can be easily filtered out, the intermodulated components of the signals at the frequency of  $2f_1 - f_2$  and  $2f_2 - f_1$  are difficult to be filtered out, which degrades the linearity of the PA.

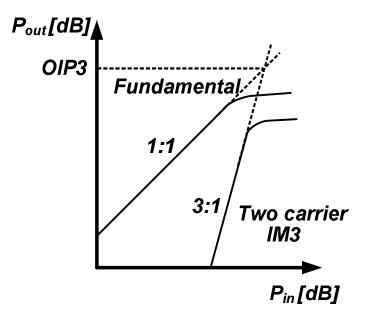

Figure 2.8 shows the third order intercept point (IP3) that is the virtual intercept point of the fundamental signal and the third-order intermodulated signal (i.e., IMD3). Because the increasing ratio of the IMD3 is three times larger than that of the fundamental signal, they can be extrapolated to be intercepted at the *IP3* point, as shown

in Fig. 2.4. The  $P_{1dB}$  and the output referred IP3 (OIP3) have a theoretical relation of OIP3= $P_{1dB}$  + 9.6dB.

Figure 2.4. Definition of the third-order intercept point.

The AM-PM distortions caused by non-linear reactive impedance can result in a time-varying phase distortions, and it can degrade the linearity of the PA as well. Specifically, the input capacitance between the gate and the source,  $C_{gs}$ , is well known for the dominant source of AM-PM distortion.

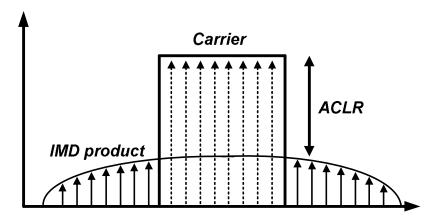

The ACLR, the ratio of the signal power level at the center of the main channel to the signal power level at a specific offset in the adjacent channel, is the critical linearity specification of the code division multiple access (CDMA). Figure 2.9 presents the ACLR spectrum of the modulated signals. Usually, the ACLR specification of the PAs is more stringent than the EVM specification for WCDMA applications.

Figure 2.5. ACLR spectrum of the modulated carrier signal.

#### 2.2.3 Output power and stability

The output power of a PA is an important in the evaluation of PA performance. Output power is defined as

$$P_{out} = \frac{V_{out}}{\sqrt{2}} \cdot \frac{I_{out}}{\sqrt{2}} = \frac{V_{out}}{\sqrt{2}} \cdot \frac{V_{out}}{\sqrt{2}R_I} = \frac{V_{out}^2}{2R_L}$$

(2.7)

With the power supply voltage and the desired output power, the output impedance can be calculated. Because of the power restrictions of a transistor such as breakdown voltage, device impedance, and limited supply voltage, output power combining can be an effective way to avoid the reliability problems of technology and achieve higher output power.

The stability of PA should carefully be considered over frequency. The necessary and sufficient conditions for the PA to be unconditional stable are that the stability factor (K) is greater than unity and the stability measure factor (B) is positive. Derivations of stability factor and stability measure factor are shown in equation (2.8) and (2.9). The Mu factor, which represents the distance from the center of the Smith chart to the nearest output load stability circle, be used for the additional stability factor, and it requires greater than unity for unconditional stability. The unconditionally stable condition of PA should be satisfied with the small signal over frequency as well as the large signal of the operating frequency range.

$$K = \frac{1 - \left|S_{11}\right|^2 - \left|S_{22}\right|^2 + \left|S_{11}S_{22} - S_{12}S_{21}\right|^2}{2\left|S_{12}S_{21}\right|} > 1$$

(2.8)

$$B = 1 + |S_{11}|^2 - |S_{22}|^2 - |S_{11}S_{22} - S_{12}S_{21}|^2 > 0$$

(2.9)

$$Mu = \frac{1 - |S_{11}|^2}{\{|S_{22} - *S_{11} \cdot (S_{11}S_{22} - S_{12}S_{21})| + |S_{12}S_{21}|\}} > 1$$

(2.10)

#### 2.3 Prior arts

#### 2.3.1 Linearity enhancement techniques of a PA

Wireless communication systems have been focus of a wide range of linearity improvement techniques. Concepts for linearity improvement such as predistortion, feedback, and feedforward techniques have been developed and adopted successfully in various applications. Also, at the device level, the efforts have been proposed toward improving linearity using harmonic traps and reducing the capacitive component variation.

#### **2.3.1.1** Predistortion linearization technique

The predistortion (PD) linearization technique is conceptually simple. The basic concept of PD is to achieve a linear function of input, illustrated in Figure 2.10. At the

front of the PA, a predistorter provides an inverse function of the amplitude and phase distortion that the PA generates.

$$Y(t) = G(Z(t)) = G(F(X(t)))$$

(2.11)

Figure2.6. Basic concept of the predistortion system.

The PD can be categorized as an analog PD, a digital PD, and a hybrid PD. Among the advantages of analog PD are their size, cost, and ease of implementation with RF PAs. However, exact PA models are required to predistort against the nonlinearity of the PA, and intermodulation distortion (IMD) suppression can be limited due to the lack of accuracy, so it generally focuses on the reduction of third order intermodulation distortion [4]-[6].

Compared to analog PD, digital PD provides superior linearity enhancement performance, and the correction is insensitive to temperature, supply voltage and device variation because of the inherent digital operation. However, a digital PD circuit requires complex, DSP-based system architecture, and the operational bandwidth is limited by the speed of digital circuits. Moreover, large DC power consumption for DSP operations is required, and the long time constant envelope memory effects of the PAs can be a bottleneck to further linearization [7][8].

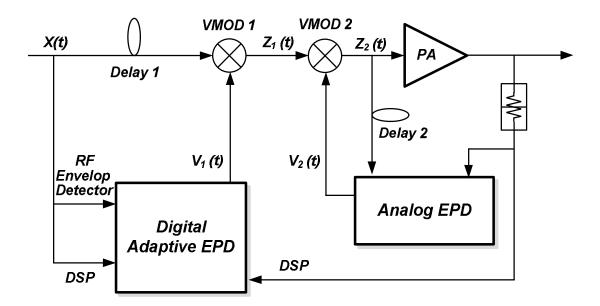

Figure 2.11 depicts the hybrid PD linearization system, which implementing analog envelope PD and digital envelope PD simultaneously. The Hybrid PD compensates for the drawbacks of analog EPD and digital EPD, such that the digital EPD system provides accurate linearization while the analog EPD system makes up for the long-time memory effect that cannot be corrected by digital EPD [9].

Figure 2.7. Digital/analog predistortion system.

It is generally known that analog PD provides 5 to 10 dB adjacent channel leakage ratio (ACLR) enhancements and digital PD provides more than 20 dB ACLR enhancements. Because predistortion occurs before amplification, the low power levels are handled for linearization so that they reduce the efficiency degradation of the system.

#### 2.3.1.2 Feedforward linearization technique

The feedforward technique is known as the technique most effective at enhancing the linearity of a PA system [10]. Achieving 20 to 30 dB IMD/ACLR reduction, it can be employed for wideband linearization. Figure 2.12 describes the basic feedforward system. The feedforward system has two cancellation loops; the signal cancellation loop and the error cancellation loop. In the signal cancelation loop, the attenuated output signal is subtracted by the input signal, providing an error signal. In the error cancellation loop, the distortion of the PA is subtracted by the amplified error signal, suppressing the distortions of the PA. However, the imbalanced power summations between the main signal and the error signal are very critical, and the system is quite complicated, resulting in a physically large size. In addition, because a power summation occurs at the PA output, large losses can occur by the delay line and the combiner, lowering the efficiency of the system.

Figure 2.8. Feedforward system.

#### **2.3.1.3** Feedback linearization technique

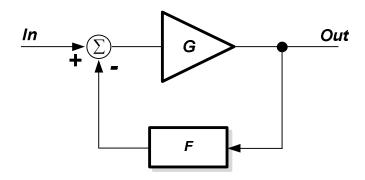

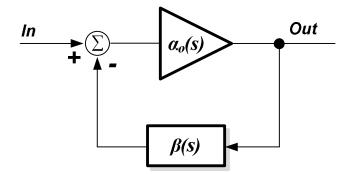

The feedback linearization technique is one of the most popular linearization techniques in analog and RF areas, reducing the distortion by a factor of loop gain. The simplest negative feedback system, shown in Figure 13, linearizes by driving the output to follow the input. In RF, however, the operating signal bandwidth is a main bottleneck for employing feedback linearization, and delays from the feedback loop can cause instability of the system.

Figure 2.9. RF feedback system.

Envelope feedback alleviates the problem of delay by employing the signal envelope as the feedback parameter, and polar-loop feedback, which is added phase-locked loop to envelope feedback, enables the correction of the AM-PM distortion effect that cannot be controlled by envelope feedback [11][12]. However, polar-loop feedback suffers from the demands of the extremely large bandwidth of the phase feedback path compared to amplitude bandwidth, resulting in non-optimized performance of the system.

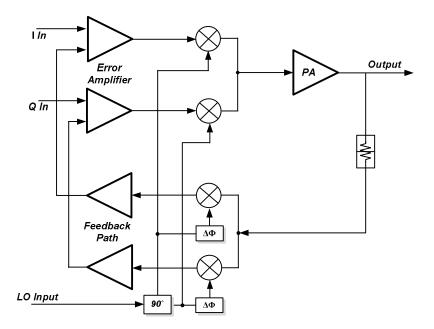

Figure 2.10. Cartesian feedback system.

Cartesian feedback relieves problems resulting from different bandwidth requirements by utilizing modulation feedback, and requires approximately the same bandwidth as that of the in-phase and quadrature-phase components [13]. As shown in Figure 2.14, Cartesian feedback consists of two identical feedback paths operated independently with the in-phase and quadrature channels. It performs down-conversion of the separated output of the in-phase and quadrature phases to the baseband frequency and feedback to the input, achieving two feedback paths. Although feedback linearization shows excellent performance, bandwidth limitations restrict it from performing wideband applications.

#### 2.3.1.4 Harmonic traps

The harmonic trap is one of the simplest ways to enhance linearity of the PA. Utilizing the inductor and capacitor in series, it can terminate the signals of resonance frequency. Figure 2.15 depicts harmonic traps applied in the PA.

$$\omega^2 = \frac{1}{LC}$$

: Resonance frequency (2.12)

Generally, the second and the third harmonic signal traps are employed at the input or the output in the multi-stage configuration. The prior work of using the second harmonic trap reported 6 dB of IMD3 improvement [14]. However, achieving the desired effects requires the accurate simulations and implementation, because the resonance frequency is vulnerable to mismatch due to unexpected implementation conditions.

Figure 2.11. Harmonic traps of the PA.

#### 2.3.1.5 Capacitance cancellation technique

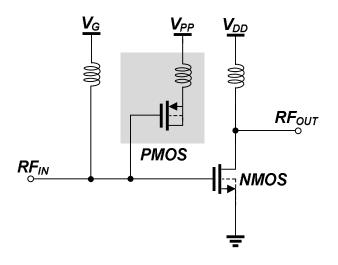

The capacitance-compensation technique is applicable to CMOS PA for enhancing linearity. The intrinsic capacitances exist between the ports of transistors, specifically, the gate-source capacitor,  $C_{gs}$ , of common source transistor is a major source of nonlinearity under the  $g_m$  and  $g_{ds}$  optimized linear class AB operation [15]. The variation of input capacitance by large signal originates phase distortions. Figure 2.16 shows the concept of the capacitance-compensation technique. Because input capacitance of PMOS transistor has the reverse transition to that of NMOS transistor, by connecting the gate node of the PMOS transistor to the gate node of NMOS transistor, changes of  $C_{gs}$  in the NMOS transistor are compensated by those of  $C_{gs}$  in the PMOS transistor, preventing linearity degradation by AM-PM distortion. This prior art that employs this technique represented 8 dB of IMD 3 and ACLR improvement [16].

Figure 2.12. Concept of the capacitance-compensation technique.

#### 2.3.2 Efficiency enhancement techniques of a PA

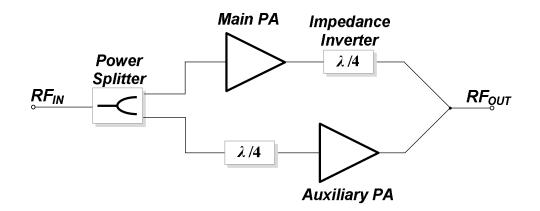

A great deal of effort has been devoted to improving the efficiency of PA operations through approaches such as the envelope elimination and restoration (EER) PA, the outphasing PA, Doherty PA and the envelope tracking system [17]-[22]. Among the efficiency enhancement techniques, the Doherty technique provides low power-level efficiency improvement. Because of this characteristic of this technique, it can be useful in the mobile handset, satisfying recent demand of the mobile handset market. Figure 2.4 shows the concept of the Doherty PA, which consists of a main PA, an auxiliary PA, and impedance inverters, so called quarter-wave transformers.

Figure 2.13. Configuration of the Doherty PA.

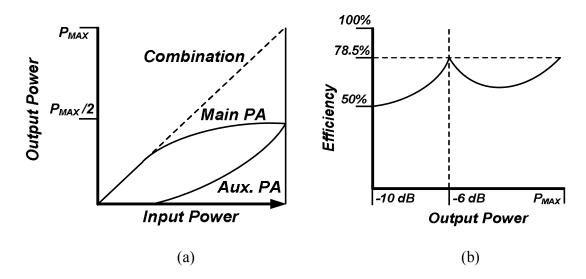

While the main PA usually has the bias of class B operation, the auxiliary PA has the bias of class C operation, such that the main PA operates alone until the input power is large enough to turn on the auxiliary PA. As the input power increases, the auxiliary PA turns on such that it supports the output power of the entire Doherty PA system, as shown in Figure 2.5(a). The overall efficiency is shown in Figure 2.5(b). The high efficiency at the back-off output power level is achieved by using the technique.

Figure 2.14. (a) Output power characteristics of the Doherty PA. (b) Efficiency characteristics of the Doherty PA.

#### 2.3.3 Output power improvement techniques of a PA

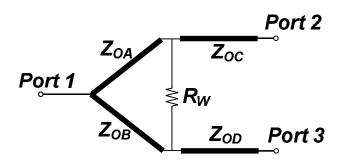

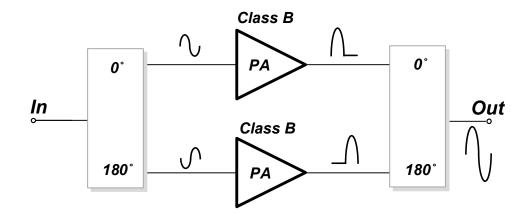

As shown in Figure 2.17, the Wilkinson divider/combiner for in-phase combining is a well known method. For quadrature combining, the branch-line coupler and coupledline directional couplers, which are often implemented using a microstrip or a stripline, can be used [23]. The push-pull PA shown in Figure 2.18, two identical PA biased class B that are driven differently, provides power combining and it has even product and harmonic cancellation merits [19]. A parallel topology based on a lattice-type LC balun can be attractive solutions [24].

Figure 2.15. Wilkinson power divider/combiner.

Figure 2.16. Push-pull power amplifier.

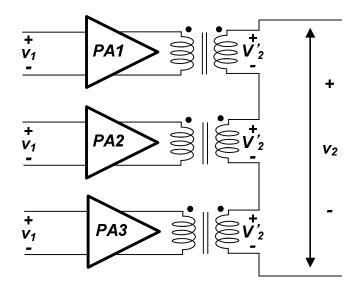

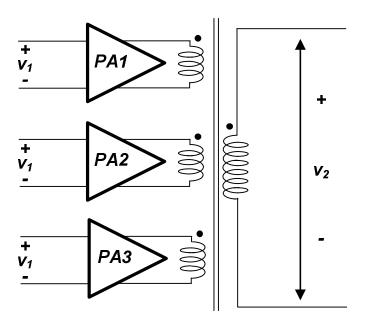

Transformer power combining, achievable in CMOS integration, provides the function of power combining as well as an impedance transformation for output matching. The distributed active transformer introduced by I. Aoki represents a series-combining transformer that combines voltage at the load, as shown in Figure 2.19 [25][26], and a parallel-combining transformer proposed by K. H. An presented in Figure 2.20 [27]. In the transformer type power-combining technique, lower input impedance, higher power combining ratio, and higher transformer efficiency are preferred to achieve better performance of the power combining.

A series-combining transformer has smaller input impedance as the powercombining ratio increases, enabling a large voltage swing when multiple PAs are combined. However, for input impedance, the power combining ratio can be sensitive to the parasitic resistance of the primary inductor. Furthermore, transformer efficiency is strongly dominated by the physical size of the secondary inductor, which is normally large when the number of combining PAs increases.

Figure 2.17. Series combining transformer.

Figure 2.18. Parallel combining transformer.

A parallel-combining transformer combines power in the current domain, and the input impedance and the power-combining ratio are less sensitive to the parasitic resistance of the primary inductor compared to series power combining. However, the

input impedance increases as the number of combined power stages increases, which degrades the optimal matching conditions of individual PAs, which in turn weaken the overall efficiency of PA performance. Both techniques demonstrate excellent power-combining performance and usability for CMOS power amplifiers.

# **CHAPTER 3**

# **CHALLENGES OF THE CMOS POWER AMPLIFIER**

#### 3.1 Challenges

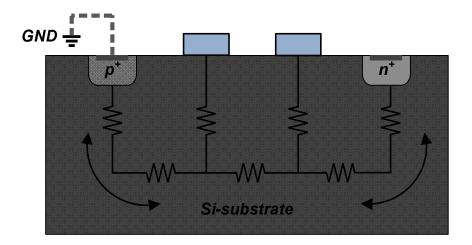

Although CMOS technology has merits of low cost and high integration potential, it has inferior performance compared to III-V compound technology because of its low transconductance, low quality factor of passive components, lossy substrate, reliability and so on. The III-V compound technologies including metal-semiconductor field-effecttransistor (MESFET), pseudomorphic high electron mobility transistor (pHEMT), and Gallium arsenide (GaAs) heterojunction bipolar transistor (HBT) with InGaP emitter have been dominant in designing the PA for various applications of the handset market, while PAs in CMOS technology have been released for only some applications such as Bluetooth, and GSM/GPRS. Table 1 shows a comparison of the GaAs and silicon technology properties. The table shows that the electron mobility of the GaAs HBT process is six times faster than that of CMOS technology. Therefore, it is not surprising that the PAs using CMOS process inherently have poorer performances compared to the PAs using III-V technology. However, because of the potential of CMOS technology to lower the production cost and facilitate integration, a great deal of effort has been dedicated to overcoming its drawbacks of CMOS technology, specifically, efficiency, linearity, and output power. In this chapter, the design challenges of CMOS PA will be discussed.

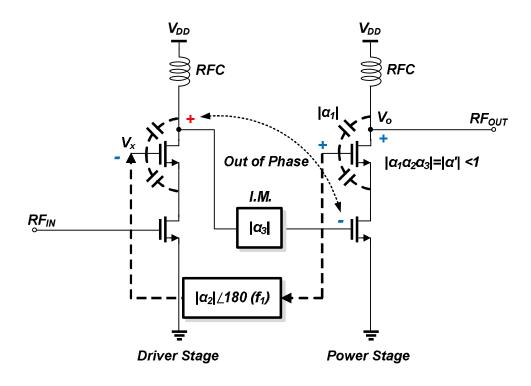

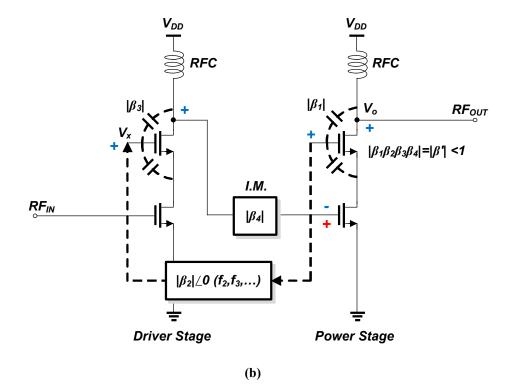

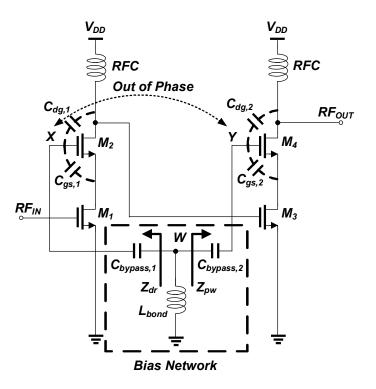

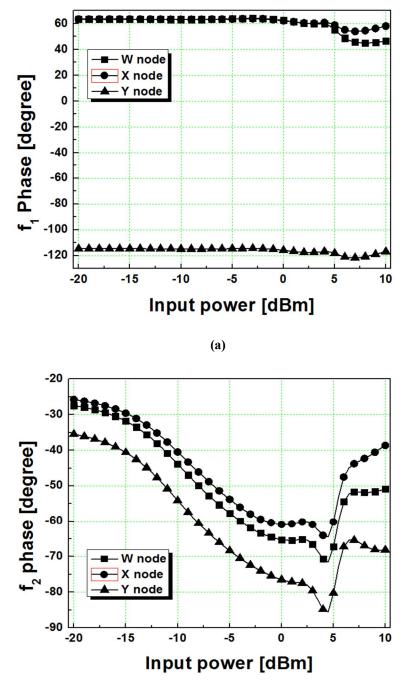

| Properties                                        | Silicon | GaAs            |  |