# A Study on the Acceleration of Arrival Curve Construction and Regular Specification Mining using GPUs

by

Nirmal Joshi Benann Rajendra

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2018

© Nirmal Joshi Benann Rajendra 2018

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Statement of Contributions

Chapter 3 of this thesis has been adopted from the work [7] that was accepted for publication under IEEE Design & Test (Volume: 35, Issue: 4, Aug. 2018). Author of this thesis is one of the co-authors for the accepted paper along with the first author, Carvajal, G., Salem, M., and Fischmeister, S. In this chapter, Carvajal, G., Salem, M. and Fischmeister, S. aided in formalising the idea of the construction of the arrival curves. Carvajal, G. also aided in the developing the intuition and approach for the construction of arrival curves.

All the work presented in this thesis were completed under the supervision of Fischmeister, S. in the Electrical and Computer Engineering department at the University of Waterloo, who contributed with his ideas, reviews, and suggestions.

#### Abstract

Data analytics is a process of examining datasets using various analytical and statistical techniques. Several tools have been proposed in the literature to extract hidden patterns, gather insights and build mathematical models from large datasets. However, these tools have been known to be computationally demanding as the datasets become larger over time. Two such recently proposed tools are the construction of arrival curves from execution traces and mining specifications in the form of regular expressions from execution traces. Though the architectures in CPUs have extensively improved over the years to execute such computationally intensive tasks, further enhancements have been impeded due to increased heat dissipation. This has resulted in enabling parallel computing through GPUs as a vastly favorable alternative to overcome the computational challenges.

In this thesis, we present an exploratory work on applying GPU computing to the construction of arrival curves and mining specifications in the form of regular expressions as case studies. The novel approaches taken for each of the case studies are first presented followed by the algorithmic breakdown to expose the parallelism involved. Lastly, experiments using commodity GPUs are presented to showcase the significant speedups obtained in comparison to the equivalent non-parallel implementations.

#### Acknowledgements

I would like to extend my gratitude to everyone who has supported me throughout my masters.

First and foremost, I would like to express my deepest gratitude towards my supervisor, Prof. Sebastian Fischmeister for being an approachable supervisor and giving me all the opportunities to help me grow both on a technical and personal level. Thank you for making time to meet with me even though you always had a busy schedule.

I am also extremely grateful to Dr. Gonzalo Carvajal. Thank you for always being there to offer guidance and support ever since I was a URA. Thank you for going the extra mile to check up on me and making sure I was in the right direction. Also, a special thanks to his students - Andrew, Hans, Jaime, Mario and Pedro.

I would like to also immensely thank Dr. Apurva Narayan for being my guide and support since my first day of masters. Thank you for the pleasure of having the experience to work, research with you and for always being there in person to help me whenever I needed it the most.

I thank my readers, Prof. Hiren Patel and Prof. Paul Ward for their valuable time in reviewing my thesis.

I felt incredibly privileged and humbled to have worked with my friends and colleagues at the Real-time Embedded Software Group especially Adan, Anderson, Anson, Carlos, Giovani, Jack, Mahmoud, Murray, Oleg, Sean and Waleed. I sincerely thank you all for your company and for sharing your knowledge. Being a part of the Embedded Soccer Group was awesome.

Special shoutout and thanks to David YeounJun Park and Tommy Nguyen for always being there and accompanying me as I transitioned from Bachelors to Masters with them. I would like to also thank Andrew Alberts for being a friend and that genius classmate who helped me complete CS 666. To Bharat, Gowtham, George, Hareesh, JJ, Mahesh, Ranga, Sara, Sathyan and Vicky, thank you for the weekend football memories.

My heartfelt thanks to my family especially my parents for their unconditional love, guidance, support and always being there. They are the backbone of my success and achievements.

Last but not least, I would like to thank God for giving me the strength, hope and making all of this possible.

#### Dedication

This thesis is dedicated to my dad - Mr. Benann Thiruthuvanathan, my mom - Mrs. Carmel Mercy Benann and my brother - James Benann. I will always be grateful to them for supporting me, no matter what decision I make.

# **Table of Contents**

| Li | List of Tables  |         |                       |          |

|----|-----------------|---------|-----------------------|----------|

| Li | List of Figures |         |                       | xi       |

| A  | bbrev           | viation | IS                    | xiii     |

| 1  | Intr            | oducti  | ion                   | 1        |

|    | 1.1             | Contri  | ibutions              | 4        |

|    | 1.2             | Organ   | ization of Thesis     | 4        |

| 2  | Bac             | kgrou   | ad                    | <b>5</b> |

|    | 2.1             | Nvidia  | a GPU                 | 5        |

|    |                 | 2.1.1   | Programming in CUDA   | 6        |

|    |                 | 2.1.2   | CUDA Memory Model     | 9        |

|    |                 | 2.1.3   | Example               | 10       |

|    | 2.2             | AMD     | GPU                   | 12       |

|    |                 | 2.2.1   | Programming in OpenCL | 13       |

|    |                 | 2.2.2   | OpenCL Memory Model   | 15       |

|    |                 | 2.2.3   | Example               | 16       |

| 3 | Ena                             | bling                                                                                  | Rapid Construction of Arrival Curves from Execution Traces   | 18                                                                                                                                 |

|---|---------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.1                             | Introd                                                                                 | luction                                                      | 18                                                                                                                                 |

|   | 3.2                             | Backg                                                                                  | round and Related Work                                       | 19                                                                                                                                 |

|   |                                 | 3.2.1                                                                                  | Analytical Arrival Curves                                    | 19                                                                                                                                 |

|   |                                 | 3.2.2                                                                                  | Empirical Arrival Curves                                     | 20                                                                                                                                 |

|   | 3.3                             | Defini                                                                                 | $\operatorname{tions}$                                       | 20                                                                                                                                 |

|   |                                 | 3.3.1                                                                                  | Traces Model                                                 | 20                                                                                                                                 |

|   |                                 | 3.3.2                                                                                  | Empirical Arrival Curves                                     | 21                                                                                                                                 |

|   | 3.4                             | Appro                                                                                  | ach                                                          | 21                                                                                                                                 |

|   |                                 | 3.4.1                                                                                  | Intuition                                                    | 21                                                                                                                                 |

|   |                                 | 3.4.2                                                                                  | Algorithm                                                    | 24                                                                                                                                 |

|   |                                 | 3.4.3                                                                                  | Parallel Approach                                            | 27                                                                                                                                 |

|   | 3.5                             | Exper                                                                                  | iments                                                       | 28                                                                                                                                 |

|   |                                 |                                                                                        |                                                              |                                                                                                                                    |

|   |                                 |                                                                                        |                                                              |                                                                                                                                    |

| 4 | Acc<br>Tra                      |                                                                                        | on of Mining Arbitrary Regular Specifications from Execution | 32                                                                                                                                 |

| 4 |                                 | ces                                                                                    | on of Mining Arbitrary Regular Specifications from Execution |                                                                                                                                    |

| 4 | Tra                             | <b>ces</b><br>Introd                                                                   |                                                              | 32                                                                                                                                 |

| 4 | <b>Tra</b><br>4.1               | <b>ces</b><br>Introd<br>Relate                                                         | luction                                                      | <b>32</b><br>32                                                                                                                    |

| 4 | <b>Tra</b><br>4.1<br>4.2        | <b>ces</b><br>Introd<br>Relate                                                         | luction                                                      | <b>32</b><br>32<br>33                                                                                                              |

| 4 | <b>Tra</b><br>4.1<br>4.2        | ces<br>Introd<br>Relate<br>Backg                                                       | luction                                                      | <ul> <li>32</li> <li>32</li> <li>33</li> <li>34</li> </ul>                                                                         |

| 4 | <b>Tra</b><br>4.1<br>4.2        | ces<br>Introd<br>Relate<br>Backg<br>4.3.1                                              | luction                                                      | <ul> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>34</li> </ul>                                                             |

| 4 | <b>Tra</b><br>4.1<br>4.2        | ces<br>Introd<br>Relate<br>Backg<br>4.3.1<br>4.3.2<br>4.3.3                            | luction                                                      | <ul> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> </ul>                                                 |

| 4 | <b>Tra</b><br>4.1<br>4.2<br>4.3 | ces<br>Introd<br>Relate<br>Backg<br>4.3.1<br>4.3.2<br>4.3.3                            | luction                                                      | <ul> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> <li>37</li> </ul>                                     |

| 4 | <b>Tra</b><br>4.1<br>4.2<br>4.3 | ces<br>Introd<br>Relate<br>Backg<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                   | luction                                                      | <ul> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> <li>37</li> <li>37</li> </ul>                         |

| 4 | <b>Tra</b><br>4.1<br>4.2<br>4.3 | ces<br>Introd<br>Relate<br>Backg<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1          | luction                                                      | <ul> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> <li>37</li> <li>37</li> <li>38</li> </ul>             |

| 4 | <b>Tra</b><br>4.1<br>4.2<br>4.3 | ces<br>Introd<br>Relate<br>Backg<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1<br>4.4.2 | uction                                                       | <ul> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> <li>37</li> <li>37</li> <li>38</li> <li>38</li> </ul> |

| R | References                 |                                                  |    |  |  |

|---|----------------------------|--------------------------------------------------|----|--|--|

|   | 6.2                        | Future Work                                      | 65 |  |  |

|   | 6.1                        | Conclusion                                       | 64 |  |  |

| 6 | Conclusion and Future Work |                                                  |    |  |  |

|   | 5.5                        | Vector Datatypes                                 | 61 |  |  |

|   | 5.4                        | Determining the Number of Threads/Work-Items     | 59 |  |  |

|   | 5.3                        | Algorithmic Design for Parallelization           | 57 |  |  |

|   | 5.2                        | Memory Coalescence                               | 56 |  |  |

|   | 5.1                        | Grid/Global Size Strided Loops in a Kernel       | 55 |  |  |

| 5 | Con                        | amon Abstractions                                | 55 |  |  |

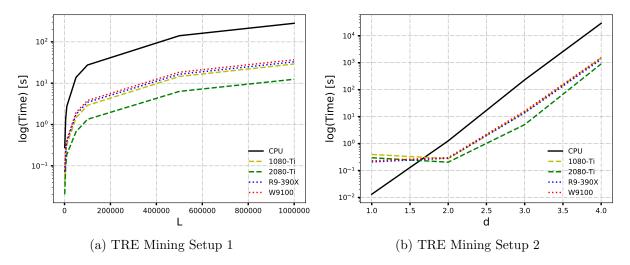

|   |                            | 4.5.2 Case Study: Nested Words (NW)              | 51 |  |  |

|   |                            | 4.5.1 Case Study: Timed Regular Expression (TRE) | 48 |  |  |

|   | 4.5                        | Experiments                                      | 48 |  |  |

# List of Tables

| 3.1 | Arrival Curve Construction Speedup Results                                                         | 29 |

|-----|----------------------------------------------------------------------------------------------------|----|

| 4.1 | Mapping of Template $\langle \alpha; \beta \rangle [x, y]$ to Alphabet $\Sigma = \{A, B, C\}$      | 37 |

| 4.2 | 2D Mapping Array M for Instances of Interest                                                       | 41 |

| 4.3 | TRE Mining Speedup Results                                                                         | 50 |

| 4.4 | Mining $(P S)^*.(\langle P.(P S)^*.S.(P S)^*\rangle[0,2000]))+$ on a QNX Trace                     | 51 |

| 4.5 | NW Mining Speedup Results                                                                          | 53 |

| 4.6 | Mining $[\langle a]^n . [\langle c]^m . [\rangle d]^m . [\rangle b]^n; m, n > 0$ on a Twitter Feed | 54 |

| 5.1 | Time Measurements for Algorithmic Restructuring                                                    | 59 |

| 5.2 | Time Measurements for Different OpenCL Kernel Configurations                                       | 60 |

# List of Figures

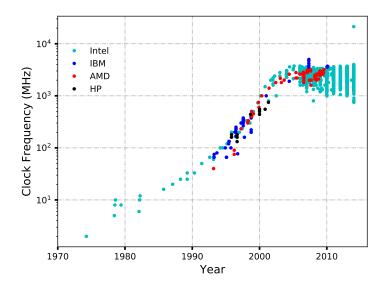

| 1.1 | CPU Clock Frequency Trend over Time [17]                                                        | 2  |

|-----|-------------------------------------------------------------------------------------------------|----|

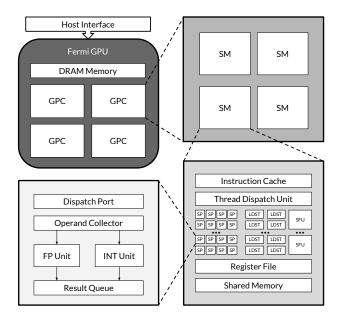

| 2.1 | Overview of Nvidia's Fermi Architecture                                                         | 6  |

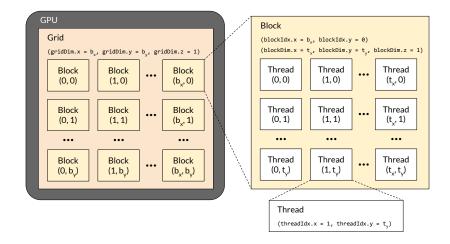

| 2.2 | CUDA Thread Hierarchy                                                                           | 7  |

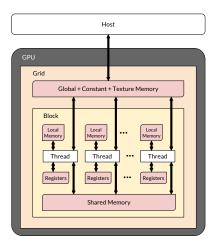

| 2.3 | Overview of the CUDA Memory Model                                                               | 9  |

| 2.4 | Vector Addition Example in CUDA                                                                 | 11 |

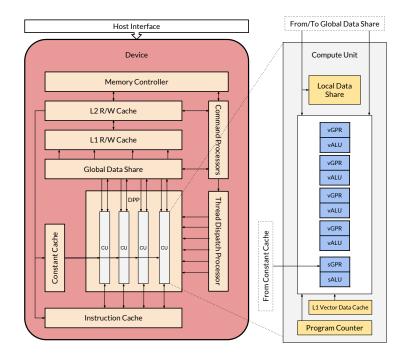

| 2.5 | Overview of the Graphics Core Next Architecture                                                 | 12 |

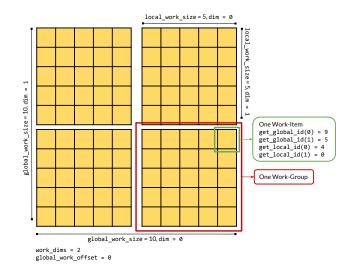

| 2.6 | Example Organization of OpenCL Work-Items and Work-Groups                                       | 14 |

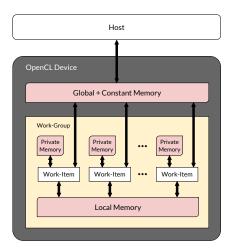

| 2.7 | Overview of the OpenCL Memory Model                                                             | 15 |

| 2.8 | Vector Addition Example in OpenCL                                                               | 17 |

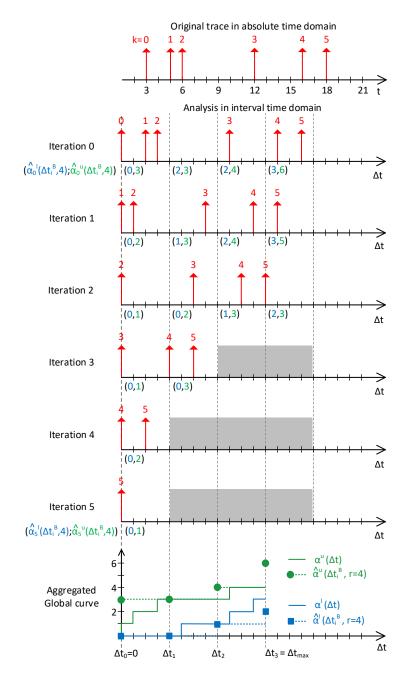

| 3.1 | Processing Flow Example for Computing the Arrival Curves [7]                                    | 23 |

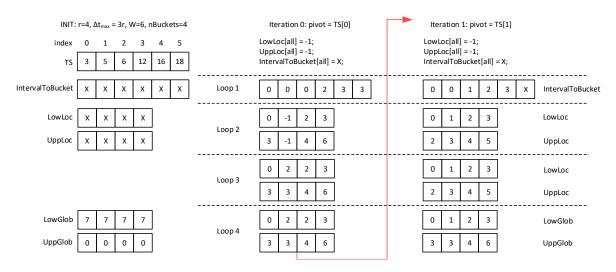

| 3.2 | Illustration of the Algorithm Execution for the First Two Iterations over the Example Trace [7] | 26 |

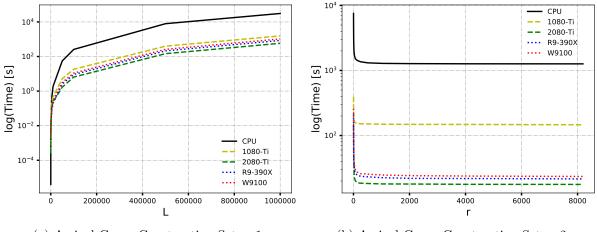

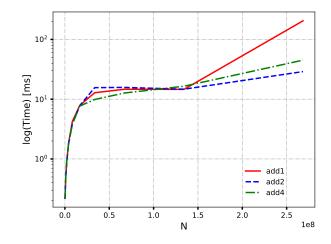

| 3.3 | Arrival Curve Construction Execution Time Evaluation on a Synthesized<br>Trace                  | 28 |

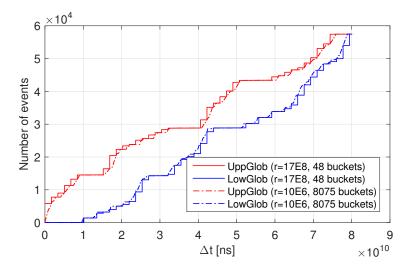

| 3.4 | Arrival Curves Constructed from a Sub-Trace with Different Bucket Widths [7]                    | 30 |

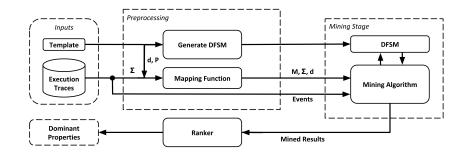

| 4.1 | High-Level Overview of the Mining Framework                                                     | 38 |

| 4.2 | Illustrative DFSM for Template $\langle \alpha; \beta \rangle [x, y]$                           | 39 |

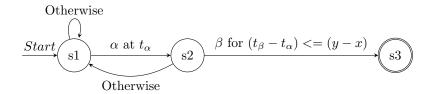

| 4.3 | DFSM Representation of a TRE Template and Execution Flow for TRE Mining                         | 44 |

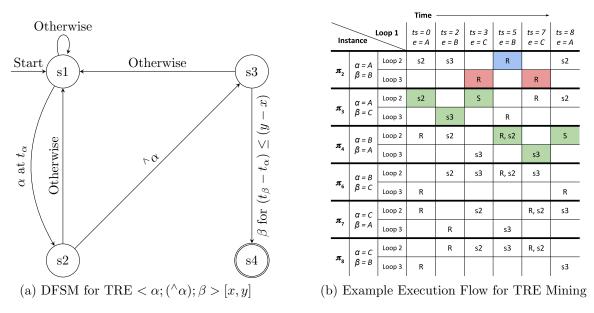

| 4.4  | DFSM Representation of a NW Template and Execution Flow for NW Mining       | 46 |

|------|-----------------------------------------------------------------------------|----|

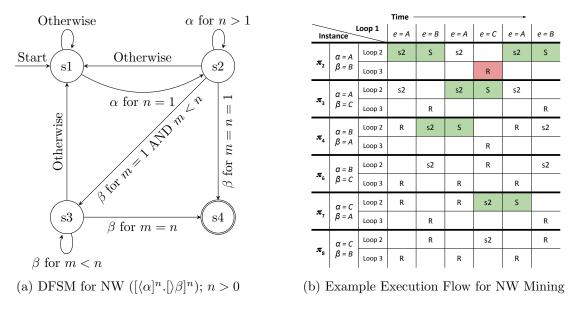

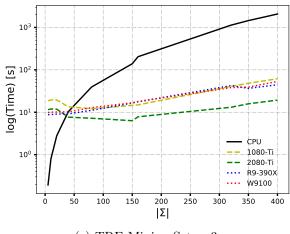

| 4.5  | TRE Mining Execution Time Evaluation on Synthesized Traces (Setups 1 and 2) | 48 |

| 4.5  | TRE Mining Execution Time Evaluation on Synthesized Traces (Setup 3) .      | 49 |

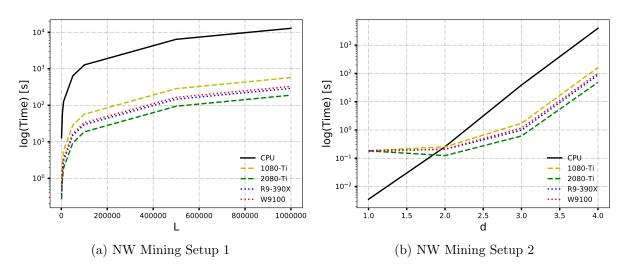

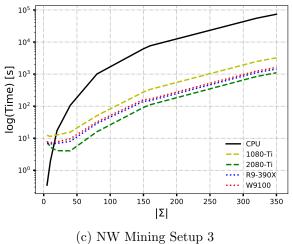

| 4.6  | NW Mining Execution Time Evaluation on Synthesized Traces (Setups 1 and 2)  | 52 |

| 4.6  | NW Mining Execution Time Evaluation on Synthesized Traces (Setup 3) $\ .$   | 52 |

| 5.1  | Work-Group Strided Loop Example in OpenCL                                   | 56 |

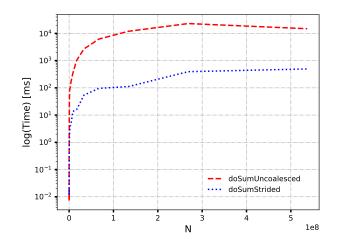

| 5.2  | Uncoalesced Memory Access Kernel Example in OpenCL                          | 56 |

| 5.3  | Time Comparison Between Coalesced and Uncoalesced Memory Access             | 57 |

| 5.4  | Example Sequential <i>for</i> Loop with Dependencies                        | 57 |

| 5.5  | OpenCL Kernel v1 for the Sequential update Function                         | 58 |

| 5.6  | OpenCL Kernel v2 for the Sequential update Function                         | 58 |

| 5.7  | Vector Addition Kernel Using float Scalar Data Type                         | 62 |

| 5.8  | Vector Addition Kernel Using float2 Vector Data Type                        | 62 |

| 5.9  | Vector Addition Kernel Using float4 Vector Data Type                        | 62 |

| 5.10 | Performance Comparison Between a Scalar Data Type and Vector Data Types     | 63 |

# Abbreviations

- ACE Asynchronous Compute Engine 13

- AMD Advanced Micro Devices, Inc. 12–16, 28, 29, 60, 65

- **API** Application Programming Interface 3, 13

- CPU Central Processing Unit 1, 2, 6, 7, 10, 12–16, 27, 29, 30, 56, 64

- CU Compute Unit 13, 14, 16, 60, 61

- **DDR** Double Data Rate 65

- DFSM Deterministic Finite State Machine 34, 35, 37–41, 43, 45, 47

- DPP Data-Parallel Processor 12, 13

- **DRAM** Dynamic Random Access Memory 5

- FPGA Field Programmable Gate Array 2, 65

- **GCN** Graphics Core Next 12

- GCP Graphics Command Processor 13

- ${\bf GDS}\,$ Global Data Share15

- **GPC** Graphics Processor Cluster 5

- GPGPU General Purpose GPU 3, 12

- **GPU** Graphics Processing Unit 2–8, 10, 12, 14–16, 19, 27–30, 33, 49, 53, 55–57, 59–61, 64, 65

- LDS Local Data Share 13, 16

- NC Network Calculus 18

- **NW** Nested Word 33, 36, 39, 43, 45, 47, 48, 52–54

- NWA Nested Word Automaton 39, 46

- NWAs Nested Word Automata 45

- **OpenCL** Open Computing Language 3–5, 13–16, 27–29, 47, 49, 53, 55, 56, 58–61, 64, 65

- **OpenMP** Open Multi-Processing 65

- **PE** Processing Element 14

- **PEs** Processing Elements 14

- **RTC** Real-Time Calculus 20

- sALU scalar Arithmetic Logic Unit 13

- sGPR scalar General Purpose Register 13

- SIMD Single-Instruction Multiple-Data 3, 6, 8, 10, 13, 14

- **SIMT** Single-Instruction Multiple-Thread 8

- SM Streaming Multiprocessor 5, 6, 8–10, 14, 60

- **SP** Streaming Processor 6, 9

- **TRE** Timed Regular Expression 33, 34, 36, 38–40, 43, 45, 47–49, 53, 65

- vALU vector Arithmetic Logic Unit 13, 61

- vGPR vector General Purpose Register 13

- **VLIW** Very Long Instruction Word 62

# Chapter 1

# Introduction

Data generated by numerous information sensing systems such as Internet of Things (IoT) devices, mobile applications, sensors, websites and social media are primarily large and unstructured. Applying advanced data analytics techniques based on data mining, machine learning, abstraction of mathematical models to these large datasets can help analyze and build structured datasets. These advanced techniques can be used to build a broad spectrum of reliable tools that can automate the data analysis process for any given set of data. However, these data analysis tools can be computationally demanding as the datasets increase in size.

Examples of two such tools are the construction of arrival curves and mining of arbitrary regular specifications. Arrival curves are well-known abstractions for mathematically modelling the temporal executions in real-time systems. There exists substantial literature that uses arrival curves for the design and analysis of real-time systems [7]. However, a tool for the construction of arrival curves has been ignored or omitted due to the computational challenges involved [7]. Similarly, specification mining is the process of examining execution traces of sophisticated programs to identify patterns of event occurrences. Mined specifications represent formal properties that characterize a program's dynamic behaviour, which can be used for debugging, verification, anomaly detection, among other applications [30, 29]. Recent literature reports multiple techniques and tools for automatic mining of temporal properties expressed in the form of regular expressions (hence, the term regular specification mining), which can be represented using deterministic finite state machines. However, these mining algorithms suffer from the time complexity arising from the inherent formulation of the automaton and the size of execution traces as shown in [30, 29].

For the last 40 years, one of the significant ways to boost the Central Processing Unit

Figure 1.1: CPU Clock Frequency Trend over Time [17]

(CPU) performance for computationally demanding tasks was by achieving gains through clock frequency [45]. Increasing clock frequency means completing tasks faster. However, as shown in Figure 1.1, the trend of clock frequency over time was growing steadily but started to flatten around early 2000. The reason behind the trend is that increasing clock frequency results in increasing the complexity of the CPU hardware which in turn causes heat dissipation in large amounts and high power consumption [45]. This limitation on the CPU clock frequency improvement resulted in turning the spotlight to parallel computing strategies for computationally intensive tasks. Specifically, applying parallel computing through heterogeneous systems involving Graphics Processing Unit (GPU)s appear to be a valuable solution as the commodity parallel hardware are becoming cost-effective [40, 50].

Heterogeneous systems consist of a host and connected device(s). Generally, the host is a CPU. The host delegates or offloads computationally intensive tasks to the device(s) and then collects the results of the tasks from the device(s) yielding in an overall better timing performance relative to a CPU-only execution. The device(s) are generally parallel computing device(s) that execute the tasks in parallel. Examples of such devices can be CPU, GPU, Field Programmable Gate Array (FPGA), and Digital Signal Processor (DSP).

Originally, GPUs were designed to accelerate the graphics processing pipeline. This involved having a fraction of the graphics processing pipeline stages implemented in hardware that were optimized, task-specific and performed fixed functions [34]. Though some of these stages were configurable, they lacked programmability. Eventually, programmability was added to the graphics pipelines to enable flexibility of certain features in graphics such as texture and lighting [34]. Over time, as the graphical applications increased in complexity, GPUs evolved primarily focusing on the programmable stages of graphics pipeline [34]. Modern GPU architectures contain large arrays of programmable processing units. In other words, older generations of GPUs can be best described as a task-specific pipeline with additions of programmability whereas modern GPUs can be described as a programmable engine with task-specific units [34]. The programmable units of modern GPU use Single-Instruction Multiple-Data (SIMD) programming model [34]. This implies that the GPU can process different data points or different elements in a dataset in parallel using a single instruction. This support of having programmable units with a parallel programming model in GPUs opened opportunities for exploring the use of GPUs for general purpose computations.

Efforts were made by researchers to map the general purpose applications to the existing graphics Application Programming Interface (API) in order to use the GPUs for general purpose computing [50]. As a result, the GPUs used for such computing purposes are known as General Purpose GPU (GPGPU). This mapping to graphics API implies each computation had to be expressed and reduced in terms of pixels even if the computation had no relation to graphics [34]. This obfuscated the use of GPU for general purpose computing thereby causing debugging to be very tedious [34]. Eventually, this limitation was overcome through the development of commercial tools and programming environments such as Open Computing Language (OpenCL) and CUDA enabling direct and non-graphical interface with the programmable units. These tools provide programming environments to exploit an application's parallel computing opportunities by providing the means to specify the parallelism through high-level programming. Hence, such tools provide a high-level programming model that opens avenues to take complete advantage of GPU's powerful architecture while enabling productive implementations of compute-intensive applications such as data analysis tools [34].

To showcase the interest of using heterogeneous systems containing GPUs to improve the performance of data analysis tools, we propose an exploratory study in this thesis on applying accelerators such as GPUs (with OpenCL and CUDA) to data analysis tools like the construction of arrival curves and regular specification mining. The approach taken in this study uses OpenCL GPUs as primary accelerators followed by exploring the results of implementing the same algorithm on CUDA GPUs.

## **1.1 Contributions**

The main contribution of this thesis are:

- Propose two novel algorithms construct arrival curves and mine specifications in the form of regular expressions from execution traces to show the application of accelerators to tools.

- Discuss the computational approach to formulate both the algorithms. This also includes the discussing the parallelism involved and the acceleration results of using parallel hardware for such algorithms.

- Present the abstractions in the form of optimizations that were considered when applying GPU computing to both case studies. These abstractions can be considered while applying CUDA and OpenCL GPU accelerators to other tools or algorithms.

## 1.2 Organization of Thesis

The remainder of this thesis advances as follows: We discuss the background required for GPU computing in chapter 2 by going over the architecture and programming model of the GPUs used. Chapters 3 and 4 present the case studies of the construction of the arrival curves and the regular specification mining respectively along with the results of the acceleration. Chapter 5 discusses the common abstractions that were considered as a result of using the two GPU programming models in the case studies. Lastly, Chapter 6 includes concluding remarks along with future work.

# Chapter 2

## Background

This chapter describes the architecture of GPUs along with the programming models of the tools used for each of them. GPUs used in this study are manufactured by Nvidia and AMD. Hence, the Nvidia GPUs are programmed using CUDA, and the AMD GPUs are programmed using OpenCL.

### 2.1 Nvidia GPU

This section will present a general overview of a Nvidia GPU architecture. The detailed specifications of a Nvidia GPU depend on the architecture model of the GPU like Pascal and Fermi. An illustration of one of Nvidia's earliest GPU architecture, the Fermi architecture, is shown in Figure 2.1. In order to get the simplified overview of the Nvidia GPU architecture and to understand the programming model described later, the key components in the Nvidia GPU architecture are the following:

- Graphics Processor Clusters (GPCs)

- Streaming Multiprocessors (SMs)

- Streaming processors (SPs) (also known as CUDA cores)

Each Graphics Processor Cluster (GPC) contains a collection of SMs along with the Dynamic Random Access Memory (DRAM) global memory and it is interconnected to the other GPCs. Each Streaming Multiprocessor (SM), in turn, consists of many SPs, thread

Figure 2.1: Overview of Nvidia's Fermi Architecture

dispatch unit, instruction cache, shared memory, register file, load/store unit (LDST) and special function units (SFU) which perform special hardware instructions such as sine/cosine/exponent operations. The thread dispatch unit dispatches the threads to the Streaming Processor (SP). Usually, the number of threads handled in a SM is 1024. Each SM further divides the number of threads into *wraps*. The SPs are responsible for performing various complex computations. To perform such computations, each SP contains an Integer Unit (INT Unit) and Floating Point Unit (FP Unit). Over time, many architectures such as the new Turing architecture were developed by improving on the Fermi architecture and by adding more of the SPs thereby, increasing the throughput.

#### 2.1.1 Programming in CUDA

The CUDA programming model is one of the many tools available for programming a heterogeneous system. As mentioned before, a heterogeneous system consists of a host which is the CPU and a device which in this case is a Nvidia GPU. The host and the device also contain their own memory - host memory and device memory respectively. The function that gets executed on the GPU is called the kernel. This is the key component for enabling parallelism through SIMD when using tools like CUDA. The kernel enables the programmer to focus on the design and logic of the application algorithm instead of worrying about the details on thread allocation or deallocation in GPU. In other words, the kernel can be written as a sequential program which is then used by CUDA to schedule the kernel on the GPU threads [9]. The high-level flow of a CUDA program is the following:

- 1. CPU allocates memory locally for the given data.

- 2. CPU allocates GPU memory and transfers the data from CPU to GPU.

- 3. CPU launches the kernels asynchronously on the GPU to execute on the copied data.

- 4. CPU waits on GPU to finish and then copies the results of the execution to CPU.

Figure 2.2: CUDA Thread Hierarchy

It is important to note that the control is returned back to the CPU after launching the kernel(s) thereby, enabling the CPU to perform any other additional tasks. Each line or instruction in the kernel is executed by a large number of threads in the GPU. CUDA allows a two-level thread hierarchy that enables the programmer to organize the threads required to execute a kernel. Organizing the number of threads is a critical part to exploiting the parallelism within Nvidia GPU. The thread hierarchy is such that the threads are grouped into blocks and the blocks are further grouped into a grid as shown in Figure 2.2. In other words, a grid is made up of blocks and each block in a grid is made up of threads. The threads inside a block can synchronize amongst themselves and also cooperate among each other using shared memory. However, threads from different blocks cannot interact and cooperate with each other. CUDA offers built-in variables to uniquely identify a thread as listed below:

- blockIdx Holds the block index within a grid.

- threadIdx Holds the thread index within a block.

- blockDim Holds the block dimension measured in terms of threads.

- gridDim Holds the grid dimension measured in terms of blocks.

Each of these variables are of type uint3, a built-in CUDA struct containing three variables - x, y and z. These can be accessed inside a kernel using the following syntax: blockIdx.x, blockIdx.y, blockIdx.z, threadIdx.x, threadIdx.y, threadIdx.z, blockDim.x, blockDim.y, blockDim.z, gridDim.x, gridDim.y and gridDim.z. This implies that the CUDA organzies the grids and blocks in 3-dimensional. By default, the x, y and z variables of the variables holding the dimension value is set to 1.

In order to launch a kernel with configurations on the number of threads required, the following syntax can be used -

#### kernel\_name<<<grid\_dim, block\_dim>>>(list of arguments)

The variable grid\_dim can be of type uint3 that indicates the number of blocks per grid along each of the three dimensions of the grid. Similarly, the variable block\_dim can be of type uint3 that indicates the number of threads per block along each of the three dimensions of the block. As an example, the following declaration: uint3 grid\_dim(512); indicates 1-D grid containing 512 blocks. Similarly, this uint3 block\_dim(1024, 1024); declares a 2-D block containing 1024 threads along each of the 2 dimensions. These variables can then be used to launch the kernels.

After launching a kernel with some grid and block dimensions, the blocks are distributed and scheduled to the SMs for execution. Multiple thread blocks can be assigned to the same SM depending on the resources available in the GPU. However, once a thread block is scheduled in a SM, it remains in that SM until the execution is complete. The scheduling and the distribution of the thread blocks to the SMs is taken care by CUDA.

CUDA uses a Single-Instruction Multiple-Thread (SIMT) model for thread management and execution. The major difference between SIMD and SIMT is that SIMD model executes a single instruction on multiple data points whereas in a SIMT model, multiple threads execute the same instruction independently. This group of threads that execute the same instruction at the same time is called a wrap which is usually made up of 32 threads [9]. Each SM divides the block of threads further into wraps and then, schedules the execution of threads.

Figure 2.3: Overview of the CUDA Memory Model

#### 2.1.2 CUDA Memory Model

The main types of programmable memory in the CUDA memory model are register file, shared, local, constant, texture and global memory. Overall view of the memory model is shown in Figure 2.3. Each SM contains a register file which acts like private memory for each thread by allowing storage of registers required by the threads. There is effectively negligible wait time on the register file and hence has the fastest memory access [11]. The lifetime of the register variables is shared with the kernel i.e. the variables cannot be accessed once the kernel finishes execution [9]. Shared memory is present in each SM as well and accessible by all the SPs present in the SM. The threads in a thread block cooperate with each other using the shared memory. This can result in race conditions if the threads were to be executed in an undefined order. However, CUDA primitives are available to prevent such race conditions within a thread block [9]. The shared memory is limited in each SM and has higher latency than that of the register file but the lifetime of the shared memory is shared with the thread block.

The local memory is a special view of the global memory used for register variables unable to fit into the allocated register space such as large local structures or arrays and variables that exceed the register limit [9]. Since local memory is in the same physical location as that of the global memory, it has the same bandwidth and latency as that of the global memory. The constant memory is present in the device memory identical to the global memory and contains only read-only data for the kernels. It is declared in the global scope and is visible to all the kernels. Another memory that resides in the device like the global memory is the texture memory which is useful for storing 2D or 3D data. Texture memory can be accessed only through a read-only cache [9] as the cache performs floatingpoint interpolation. This facility in Texture memory is advantageous to applications that are designed around 2D or 3D data.

Lastly, the global memory is the largest memory available on the GPU. It has the highest latency and is also most commonly used memory due to its size. The global memory is available to all the SMs at the same time and its lifetime is shared with the application. This can cause undefined program behaviour due to race conditions arising from threads in two different thread blocks accessing the same global memory location. Hence, it is advised to take caution when designing the memory access to the global memory. The CPU in the heterogeneous system transfers the data to the GPU by first allocating memory in the global memory and then moving the data from the CPU memory to the GPU memory.

In addition to these, the Nvidia GPU also contains non-programmable caches: L1 cache, L2 cache, read-only constant and read-only texture [9]. Each SM contains an L1 cache, a read-only constant cache, a read-only texture cache and the L2 cache is shared among all the SMs. The L1 and L2 caches are used to store the data in local and global memory whereas the read-only constant cache and the read-only texture cache is used to store data in the constant and texture memory respectively.

#### 2.1.3 Example

Figure 2.4 shows an example CUDA program that does vector addition in parallel. This program can be stored with the .cu file extension. The CUDA compiler driver, nvcc that is part of the CUDA toolkit, follows the CUDA compilation trajectory as listed below:

- Separating the device functions (like kernels) from the host code

- Compile the device functions using the Nvidia compiler

- Compile the host code using a C++ compiler

- Link CUDA runtime libraries to support SIMD steps along with GPU memory allocation and data transfer between CPU and GPU

This example starts with the initialization of two vectors of size 1024 each and each containing consecutive numbers starting from 1. After initializing, the necessary GPU memory is allocated using cudaMalloc and data is transferred from CPU to GPU using cudaMemcpy. The kernel in this example is the doSum function and gets executed on the

```

1 #include <cuda_runtime.h>

\mathbf{2}

3 #define SIZE 1024

4 #define START 1

5 using namespace std;

6

7

__global__ void doSum(int *a, int *b, int *sum) {

8

unsigned int i = threadIdx.x ;

9

sum[i] = a[i] + b[i];

10 }

11

12 void initVector(vector<int> &v) {

13

int x = START;

14

for (int i = 1; i <= SIZE; ++i) {</pre>

15

v.push_back(x++);

16

}

17 }

18

19 int main(int argc, char *argv[]) {

20

vector < int > h_a, h_b;

21

vector < int > h_sum(SIZE, 0);

22

int *d_a, *d_b, *d_sum;

23

24

initVector(h_a);

25

initVector(h_b);

26

cudaMalloc((void**)&d_a, sizeof(int)*SIZE);

27

cudaMalloc((void**)&d_b, sizeof(int)*SIZE);

28

cudaMalloc((void**)&d_sum, sizeof(int)*SIZE);

29

cudaMemcpy(d_a, h_a.data(), SIZE*sizeof(int),

cudaMemcpyHostToDevice);

30

cudaMemcpy(d_b, h_b.data(), SIZE*sizeof(int),

cudaMemcpyHostToDevice);

31

32

doSum<<<1, 1024>>>(d_a, d_b, d_sum);

33

34

cudaMemcpy(h_sum.data(), d_sum, SIZE*sizeof(int),

cudaMemcpyDeviceToHost);

35

cudaFree(d_a);

36

cudaFree(d_b);

37

cudaFree(d_sum);

38

39

return 0;

40 }

```

Figure 2.4: Vector Addition Example in CUDA

GPU. This kernel is launched with a 1-D grid containing a single 1-D thread block made up of 1024 threads. Each thread runs the kernel by first obtaining its thread index in the block using threadIdx.x followed by the addition operation at the vector index equal to the thread index. While the addition is done in parallel, CPU is waiting on the cudaMemcpy call to copy the results from the GPU to CPU. The results will be copied into the CPU memory once all the threads complete the kernel execution.

### 2.2 AMD GPU

An alternative to using a Nvidia GPU in a heterogeneous system is an Advanced Micro Devices, Inc. (AMD) GPU. The codename for the microarchitecture used in AMD GPUs launched from 2011 is Graphics Core Next (GCN). This microarchitecture was launched to improve the architecture of its predecessor, TeraScale, especially for GPGPU computations. This section discusses the components of the GCN in a AMD GPU used in a GPGPU setting. Figure 2.5 shows an overview of the GCN architecture.

Figure 2.5: Overview of the Graphics Core Next Architecture

The main component that forms the heart of the GCN is the Data-Parallel Processor

(DPP) array [5]. The DPP contains a collection of compute units that operate independent of each other and in a parallel manner on data streams of floating-point or integer type [5]. Each Compute Unit (CU) is the basic computational block in the architecture. A CU is made up of 4 SIMD vector units (stream processors), a program counter, scalar General Purpose Register (sGPR), scalar Arithmetic Logic Unit (sALU) and Local Data Share (LDS) and a L1 vector data cache [3]. Each SIMD vector unit contains a vector General Purpose Register (vGPR) and vector Arithmetic Logic Unit (vALU) capable of executing single or double precision floating point operations simultaneously using 16 threads (work-items) [3]. Hence, 4 SIMD vector units results in total of 64 threads to execute simultaneously which is called a *wavefront* and this term is analogous to a wrap in CUDA. The LDS within each compute unit is used as a register file to synchronize among the different SIMD units and is designed to have low-latency bandwidth [3].

The command processors are responsible for receiving high-level API commands from the driver and mapping them onto the two processing pipelines - Asynchronous Compute Engine (ACE) and Graphics Command Processor (GCP) [3]. The ACE is responsible for parallel compute operations and the GCP is responsible for graphics operations and fixed hardware functions [3]. The memory controller brings together all the components and the caches together to provide data to every part of the system [3].

#### 2.2.1 Programming in OpenCL

OpenCL is an industrial standard framework developed by the Khronos Group and used for writing programs that can be executed in heterogeneous systems containing OpenCLcompliant hardware as the device. OpenCL was built on the notion, "Write once, run on anything" which is similar to Java's "Write once, run everywhere" [39]. In other words, OpenCL enables portability across multiple OpenCL-compliant devices. The relevant tools to compile and run OpenCL code is provided by the vendor of OpenCL-compliant devices. Examples of such tools are AMD APP SDK and Xilinx SDAccel Development Environment.

OpenCL provides two compilation options - the traditional offline compilation and the runtime compilation [43]. Through runtime compilation, OpenCL allows execution on new hardware not available to the developer of the OpenCL program without the need to recompile the main application [43]. Through runtime compilation, OpenCL provides an interface to enumerate the available devices connected to the host i.e. CPU. On enumerating and selecting the required set of devices, OpenCL encapsulates the devices' details into a container called context. Device management is done through the context object [43].

Identical to CUDA, the functions that are executed in the devices are called kernels.

Figure 2.6: Example Organization of OpenCL Work-Items and Work-Groups

The given kernels are compiled runtime in a container called program [43]. After selecting the kernel in the program container, the appropriate arguments are associated to the kernels and dispatched to a queue data structure called the command queue [43]. The CPU offloads tasks to the device using the command queue. The device executes the functions in the command queue in the same order as they were queued.

The devices used for OpenCL contain at least one processor cores known as Compute Units which in turn contain one or more Processing Elements (PEs). The PEs are designed to execute SIMD instructions which thereby enables data-level parallelism [43]. From an AMD GPU perspective, OpenCL Compute Units are the same as the Compute Units (CUs) inside the GPU and each Processing Element (PE) is the SIMD engine inside the CU of the GPU. OpenCL also uses the concept of work-groups and work-items which are analogous to thread blocks and threads respectively in CUDA. The compute unit in an OpenCL device executes a work-group at a time [39] similar to a thread block executed by a SM in CUDA. Each work-item in a work group is assigned a global ID that uniquely identifies a workitem [39]. This can be obtained using get\_global\_id(dim) function call inside a kernel. The dim argument indicates the dimensionality of the data being processed [39]. The dimensionality is specified when queueing the kernel to the command queue. The minimum dimensionality is 1 and the maximum dimensionality is device dependent. Specifically, the following arguments are used to specify the work-item and work-groups while queueing the kernel:

• work\_dims: The number of dimensions.

Figure 2.7: Overview of the OpenCL Memory Model

- global\_work\_offset: Offset to the global ID in each dimension.

- global\_work\_size: Total work-items in each dimension across all work-groups.

- local\_work\_size: Number of work-items in a work-group in each dimension.

Figure 2.6 shows an example organization of work-items and work-groups in a twodimensional setting. Since a work-group can contain multiple work-items, get\_local\_id(dim) to get the local ID of a work-item to distinguishes it from the other work-items in the same work-group. After these arguments are specified, OpenCL determines the number of workgroups required before executing the kernel. If local\_work\_size is set to NULL, OpenCL will determine the best way to distribute the work-items based on the device architecture [39].

#### 2.2.2 OpenCL Memory Model

OpenCL offers four types of memory - global memory, constant memory, local memory and private memory as shown in Figure 2.7. The global memory allows storage of data to be read or written by the entire device. This memory is designed to be large with high latency and may be shared with the host to transfer data to and from the host (CPU) [43]. This can be the Global Data Share (GDS) in a AMD GPU. Constant memory is similar to the global memory except that it is only read-only by the device. The location of the constant memory depends on the device architecture. Some devices may have a specific memory location for Constant memory and the others may assign a part of the memory region in global memory to be constant memory [39]. The local memory is available to all the work-items in each work-group mainly for synchronization. This memory can be accessed by the work-items in a work-group faster than the global or constant memory but its size can be limited [39]. The LDS in each CU of a AMD GPU is the local memory. Lastly, private memory is a memory region for each work-item. Though it is limited in size, the private memory has the lowest latency access in the OpenCL memory model.

In order to use this memory model, the following address space qualifiers are available: \_\_global, \_\_constant, \_\_local and \_\_private. These address space qualifiers are used to define the address space of kernel arguments or other variables in the device code. \_\_global is for global memory, \_\_constant is for constant memory, \_\_local is for local memory and \_\_private is for private memory [39]. If a kernel argument or variable does not have an address space qualifier, then private memory is used for storage [39].

#### 2.2.3 Example

Figure 2.8 shows an OpenCL with C++ bindings example to do vector addition in parallel. This file can be stored as a .cpp file and compiled using a C++ compiler such as g++ with compiler options linking to the OpenCL library provided by the device vendor. To avoid redundancy, the function definition of initvector() function and the definition of SIZE and START have been ignored and are same as that of the CUDA example in section 2.1.3.

Before executing the actual computation, a preprocessing step is involved as OpenCL runtime compilation is used. First, the array of platforms available on the host is obtained, and the platform at index 0 is used in this example. Using this platform, a Context object is built which is in turn used to build the Device object. The device code that is hardcoded as a string is used to define a Program object. This Program object is compiled using the Device object to create a Kernel object. A CommandQueue object is declared using the Context and Device objects. After allocating the necessary GPU memory, the CommandQueue object is used to enqueue the transfer of input data using enqueueWriteBuffer() and the kernel as well. The kernel in this example is the doSum function and is launched with a 1-D data containing a global size of 1024 work-items. Each work-item runs the kernel by first obtaining its work-item ID using get\_global\_id(0) followed by the addition operation at the vector index equal to the work-item ID. While the addition is done in parallel, CPU is waiting on the response of the enqueue operation of enqueueReadBuffer() that copies the results from the GPU to the CPU. The results will be copied into the CPU memory once all the work-items complete the kernel execution.

```

1 #include "cl.hpp"

2 using namespace std;

3 using namespace cl;

4

5 const char *src =

6 "__kernel void doSum(__global int *a, __global int *b, __global int *

sum) {" \

7

п

int i = get_global_id(0); " \

8 "

sum[i] = a[i] + b[i]; "\

9 "}":

10

11 int main(int argc, char *argv[]) {

12

cl_int err;

vector < int > h_a, h_b;

13

14

vector < int > h_sum(SIZE, 0);

15

Buffer d_a, d_b, d_sum;

16

initVector(h_a);

17

initVector(h_b);

18

vector < Platform > pl;

19

Platform::get(&pl);

20

cl_context_properties properties[] = { CL_CONTEXT_PLATFORM, (

cl_context_properties)(pl[0])(), 0};

21

Context context(CL_DEVICE_TYPE_GPU, properties);

22

vector<Device> d = context.getInfo<CL_CONTEXT_DEVICES>();

23

Program::Sources source(1, make_pair(src, strlen(src)));

24

Program p = Program(context, source);

25

p.build(d);

26

Kernel k(p, "doSum", &err);

27

CommandQueue queue(context, d[0], 0, &err);

28

size_t bytes = sizeof(int)*SIZE;

29

d_a = Buffer(context, CL_MEM_READ_ONLY, bytes);

30

d_b = Buffer(context, CL_MEM_READ_ONLY, bytes);

31

d_sum = Buffer(context, CL_MEM_READ_WRITE, bytes);

32

queue.enqueueWriteBuffer(d_a, CL_TRUE, 0, bytes, h_a.data());

33

queue.enqueueWriteBuffer(d_b, CL_TRUE, 0, bytes, h_b.data());

34

k.setArg(0, d_a);

35

k.setArg(1, d_b);

36

k.setArg(2, d_c);

37

queue.enqueueNDRangeKernel(k, NullRange, 1024, NullRange);

38

queue.enqueueReadBuffer(d_sum, CL_TRUE, 0, bytes, h_sum.data());

39

return 0;

40 }

```

Figure 2.8: Vector Addition Example in OpenCL

# Chapter 3

# Enabling Rapid Construction of Arrival Curves from Execution Traces

### 3.1 Introduction

Verification of functional and non-functional properties in contemporary embedded systems are becoming more challenging and computationally intensive due to the inherent complexity and interconnectivity of such systems. Mathematical models and formal methods have been used in the past to derive performance metrics during the design phases [48, 37, 23]. Traditional formal methods have proved to effective on mapping worst-case behaviour for closed systems with trivial complexity to generalized mathematical representations. However, these approaches have failed to be useful and reliable for complex systems that have a high number of unpredictable interactions between the different components [7]. These limitations have turned the spotlight to processing execution traces in runtime analysis. The execution traces record the unpredictable behaviour in complex systems specifically the ones not considered during design time.

Arrival Curves offers a way to model the temporal behaviour of real-time systems. Coarsely grained approximations of arrival curves have been used by multiple frameworks to model worst-case behaviours and determine performance metrics by applying Network Calculus (NC) theory operations on these arrival curves [48, 37, 23]. Over time, various literature that focuses on the potential uses of fine-grained construction of arrival curves from execution traces in advanced techniques were published [20, 38, 24, 32]. However,

the caveat in the construction of such fine-grained arrival curves from large datasets of execution traces is that the process is computationally demanding which thereby results in the incomplete utilization of these curves in a real-world setting.

This chapter presents the algorithmic formulation for the construction of arbitrarily detailed arrival curves as a toolset by iterating over registered events in time-stamped execution traces. The algorithm also provides opportunities for data-level parallelism and experiments in this chapter show significant speedups when applying such parallelism to commodity parallel hardware such as GPUs.

The rest of the chapter is organized as follows: Section 3.2 overviews background of arrival curves and related work around the construction of arrival curve. Section 3.3 introduces some definitions to formalize the approach involved. Section 3.4 describes the core of the proposed algorithm for the construction of fine-grained arrival curves from execution traces including a discussion on the parallel approach involved. Section 3.5 shows the results of applying stress tests based on synthesized traces to the proposed algorithm with GPUs followed by an illustration of the constructed arrival curves using a QNX trace.

### **3.2** Background and Related Work

#### 3.2.1 Analytical Arrival Curves

Arrival curves are represented as a function of interval time domain by providing the upper and lower limits on the number of registered events that occur in a system within a given time interval of length  $\Delta t$  [37]. Theoretically, arrival curves can be constructed from execution traces containing timestamps and events by sliding a time interval window of arbitrary length along the time axis while keeping track of the maximum and the minimum number of events occurring within each window. However, instead of using the execution traces, traditional approaches constructed the arrival curves by bounding any possible curve after analyzing generic behavioural patterns [7]. As a result, various scenarios were approximated using event pattern models that observe the period, jitter and delay of events (PJD models) [48, 37, 42]. Let the arrival curves constructed as a result be called *analytical* arrival curves.

#### 3.2.2 Empirical Arrival Curves

However, the caveat behind using analytical arrival curves is that it will produce loose conservative approximations for unpredictable behavioural patterns that deviate from the general PJD pattern models [7]. This unpredictable behaviour arises due to the increasing complexity of embedded systems which has in turn increased the interest in alternative runtime analysis techniques that uses execution traces. Specifically, these techniques focus on producing fine-grained models that record the unpredictable workloads due to the unforeseen interactions between the various components in an embedded system.

Let the arrival curves constructed from execution traces of an embedded system be called *empirical* arrival curves. Though techniques to construct empirical arrival curves have potential uses in resource management [24, 32] and anomaly detection [38], it is a computationally intensive task as highlighted by the authors of [38] and therefore, remains overlooked in literature [7]. The only existing work that is designed to construct such curves from execution traces is the Real-Time Calculus (RTC) Toolbox [47]. However, this toolbox fails to process arbitrarily large execution traces [7]. This chapter will show the computational approach to construct the empirical arrival curves and also demonstrate the use of parallelism to overcome the computational intensive barrier.

### 3.3 Definitions

#### 3.3.1 Traces Model

A trace is a chronological sequence of events occurring during the execution of a program. The trace may register multiple details about an event, such as an index, timestamp, and additional information pertaining to the functionality of the system. In this context, the index and the timestamp are the only parameters of interest.

**Definition 1** (*Event source*) An event source generates elements  $ts_k, k \ge 0$ , representing the timestamp of an event measured in an absolute time domain t. Timestamps are multiples of an atomic time unit ( $ts_k \in \mathbb{N}$ ), and events are generated as time progresses ( $ts_k < ts_{k+1}$ ). [7]

**Definition 2** (*Trace*) A trace  $TS = [ts_0, ts_1, \ldots, ts_{N-1}]$  is a finite sequence of N timestamps collected from an event source. [7]

#### 3.3.2 Empirical Arrival Curves

**Definition 3** (*Empirical arrival curve*) The pair of curves  $(\alpha^l(TS, \Delta t); \alpha^u(TS, \Delta t))$ provide a lower and upper bound on the number of events seen in any time interval of length  $\Delta t$  in a trace TS. [7]

To formulate an algorithm to construct empirical arrival curve, the term *quantized* arrival curves is used. Quantized arrival curves are approximations of empirical arrival curves calculated based on discrete buckets (i.e. windows of some time interval) of width r atomic time units.

**Definition 4** (Quantized arrival curves) Given a set of discrete buckets  $\Delta t_i^B$  of width r atomic time units (r > 1), with bucket  $\Delta t_i^B$  enclosing all intervals  $\Delta t$  in the range  $ir \leq \Delta t < (i+1)r$ , with  $i \in \mathbb{N}^0$ . Quantized lower  $\hat{\alpha}^l(TS, \Delta t, r)$  and upper  $\hat{\alpha}^u(TS, \Delta t, r)$  arrival curves will provide a unique representative value for all intervals  $\Delta t$  enclosed in a bucket [7]. Quantized curves must comply with the following property:

$$\forall r > 1 : \hat{\alpha}^{l}(TS, \Delta t, r) \le \alpha^{l}(TS, \Delta t) \land \hat{\alpha}^{u}(TS, \Delta t, r) \ge \alpha^{u}(TS, \Delta t)$$

(3.1)

Equation 3.1 states that upper arrival curves and lower arrival curve need to be approximated from above and from below respectively [23]. The definition of quantized arrival curves also indicates a way to express a sequence of events occurring in a range of time intervals as a single bucket.

It is important to note that this definition considers the equivalence relations  $\hat{\alpha}^{l}(\Delta t, r = 1) \equiv \alpha^{l}(\Delta t)$  and  $\hat{\alpha}^{u}(\Delta t, r = 1) \equiv \alpha^{u}(\Delta t)$  as there is no quantization involved for r = 1. The remaining sections will be using the notations  $\hat{\alpha}^{l}(\Delta t_{i}^{B}, r)$  and  $\hat{\alpha}^{u}(\Delta t_{i}^{B}, r)$  to represent the quantized value of the lower curve and upper curve respectively for all intervals  $\Delta t$  in the bucket *i*.

### 3.4 Approach

#### 3.4.1 Intuition

To construct the arrival curves, it is only required to check for intervals aligned to the events in the execution trace instead of checking all possible time intervals in the trace [32, 37]. This is general intuition behind the algorithmic formulation. Using this intuition, an iterative approach can be taken to construct the curves by iterating over the timestamps in the trace accumulating results obtained at each timestamp (pivot).

Figure 3.1 shows the processing flow of computing the arrival curves for a sample trace TS = [3, 5, 6, 12, 16, 18] where each element denotes the timestamp of an event. This sample trace is represented illustratively on the top of the figure using absolute time axis t horizontally with red arrows representing the timestamps. This processing flow involves mapping each timestamp  $ts_k$  in the absolute time domain t to the interval time domain  $\Delta t$  using a reference timestamp  $ts_p$ , with  $p \in [0, N - 1]$ . This mapping is in accordance with a function  $M : t \to \Delta t$ :

$$M(ts_k, ts_p) = ts_k - ts_p, \text{ with } p \le k \le N - 1 \tag{3.2}$$

During each iteration, a new distribution of events, p, is generated in the  $\Delta t$  domain and the local lower curve  $\hat{\alpha}_p^l(\Delta t_i^B, r)$  and local upper curve  $\hat{\alpha}_p^p(\Delta t_i^B, r)$  is computed for each pivot. These local curves are obtained by computing the minimum (lower bound) and maximum (upper bound) on the number of events occurring in time intervals measured from the pivot, which is the origin in the interval time domain  $\Delta t$ , to the limits of each interval bucket  $\Delta t_i^B$ . This process of computing local curves is repeated for the next succeeding timestamp which will be the new pivot.

In the case of r = 1 (no quantization), the following rules are used to compute the local curves [37]:

- The local lower value  $\alpha_p^l(\Delta t)$  is the number of events in the interval  $(0, \Delta t]$  in the current iteration.

- The local upper value  $\alpha_p^u(\Delta t)$  is the number of events in the interval  $[0, \Delta t)$  in the current iteration.

According to the definition of quantized arrival curves, a unique value must be assigned to every time interval lengths within a bucket for r > 1 to ensure that quantized lower and upper curves computed, as a result, approximates the curves computed using r = 1 from below and above respectively. This condition is fulfilled using the following rules [7]:

• The local lower value  $\hat{\alpha}_p^l(\Delta t_i^B, r > 1)$  is the number of events in the interval (0, ir) in the current iteration.

Figure 3.1: Processing Flow Example for Computing the Arrival Curves [7]

• The local upper value  $\hat{\alpha}_p^u(\Delta t_i^B, r > 1)$  is the number of events in the interval [0, (i + 1)r) in the current iteration.

The above rules will be used to compute the arrival curves. The example in Figure 3.1 has r set to 4 time units and another parameter,  $\Delta t_{max}$  set to 3r.  $\Delta t_{max}$  is the maximum timespan of interest [7] and is, by default, less than or equal to  $ts_{N-1} - ts_0$ . The grey dashed vertical lines in the interval time domain shown in the figure separate each interval within a single bucket. The tuple shown below the  $\Delta t$  axis and right of the dashed vertical lines contains the lower and upper bound on the number of events for each bucket. For example, during iteration 0, the pivot is at timestamp t = 3 and hence, in the interval time domain, it is at the origin. Using the rules above for r > 1, the  $\hat{\alpha}_0^l(\Delta t_0^B, 4)$  and  $\hat{\alpha}_0^u(\Delta t_0^B, 4)$ values in the first time interval  $\Delta t_0$  (i = 0) are 0 and 3 as shown in the appropriate tuple in the figure. Similarly, for the second time interval  $\Delta t_1$  (i = 1),  $(\hat{\alpha}_0^l(\Delta t_0^B, 4), \hat{\alpha}_0^u(\Delta t_0^B, 4))$ is (2, 3) and so on until  $\Delta t_i = \Delta t_{max}$ . These are the local values during iteration 0. This computation is repeated for each timestamp as the pivot and the global lower and upper curves are obtained by taking the maximum and the minimum number of events over all the local curves. This is illustrated using the last plot at the bottom of Figure 3.1. The grayed areas in the figure denote that these areas are ignored when computing the global curves as no event occurs in those buckets. Also, it is important to know that the value of the curves at  $\Delta t = 0$  is zero [37].

## 3.4.2 Algorithm

Algorithm 1 shows the pseudo-code of the formulated algorithm to construct quantized arrival curves with given arguments TS, r > 1,  $\Delta t_{max}$  and W where W is the length of the array IntervalToBucket which stores the number of events that occur within the maximum timespan  $\Delta t_{max}$ . If the minimum delay  $d_{min}$  between consecutive events in TS is known, then  $W \ge (\Delta t_{max}/d_{min})$ . The results of local curves during each iteration are stored in LowLoc and UppLoc and the aggregated results are stored in LowGlob and UppGlob. INT\_MAX in the pseudo-code is any arbitrarly large positive integer.

The outermost loop in the algorithm is used iterate over the timestamps in TS and perform the computations for each timestamp. Initially the local lower and upper arrays are initialized to INT\_MAX and -1 respectively during each iteration of this loop. Loop 1 deals with populating IntervalToBucket by mapping each timestamp  $ts_k \geq ts_p$  to a bucket computed using its distance from the pivot timestamp  $ts_p$ . This means that at the end of Loop 1, IntervalToBucket will be populated with value *i* for all timestamps

#### Algorithm 1: Construct Quantized Arrival Curves from a Trace [7]

```

Input: TS, \Delta t_{\max}, r, W

1 nBuckets \leftarrow |\Delta t_{\max}/r|

2 LowGlob[1:nBuckets] \leftarrow INT_MAX

3 UppGlob[1:nBuckets] \leftarrow 0

4 LowLoc[nBuckets], UppLoc[nBuckets], IntervalToBucket[W]

5 for p \leftarrow 0 to N - 1 do

h \leftarrow 0, LowLoc[1: nBuckets] \leftarrow -1, UppLoc[0: nBuckets] \leftarrow -1

6

// Loop 1: Compute quantized values of intervals

7

for k \leftarrow p to N - 1 do

8

IntervalToBucket[h] \leftarrow |(TS[k] - TS[p])/r|

9

h = h + 1

\mathbf{10}

if (h \ge W \text{ or IntervalToBucket}[h] > nBuckets) then

11

break

12

end

\mathbf{13}

end

14

// Loop 2: Find local upper and lower value for each bucket \Delta t_i^B

15

for i \leftarrow 1 to nBuckets do

16

if i \in IntervalToBucket then

17

\mathbf{UppLoc}[i] = (\text{index of last element equal to } i)

\mathbf{18}

\mathbf{LowLoc}[i] = (\text{index of first element equal to } i) - 1

19

\mathbf{20}

end

end

\mathbf{21}

// Loop 3: Fill gaps in local upper curve and similarly for local lower curve

22

for i \leftarrow 1 to nBuckets do

\mathbf{23}

if UppLoc[i] < 0 then

\mathbf{24}

\mathbf{UppLoc}[i] = \mathbf{UppLoc}[i-1]

\mathbf{25}

end

\mathbf{26}

end

\mathbf{27}

// Loop 4: Update global curves

\mathbf{28}

for i \leftarrow 1 to nBuckets do

\mathbf{29}

\mathbf{UppGlob}[i] = \max(\mathbf{UppLoc}[i], \mathbf{UppGlob}[i])

30

\mathbf{LowGlob}[i] = \min(\mathbf{LowLoc}[i], \mathbf{LowGlob}[i])

\mathbf{31}

32

end

33 end

```

considered such that  $ir \leq \Delta t < (i+1)r$  in the interval time domain. Loop 2 extracts lower and upper values for the bucket  $\Delta t_i^B$  by looking at the the value *i* in IntervalToBucket and then updating UppLoc and LowLoc array appropriately at index *i* [7]. The last index of IntervalToBucket with bucket *i* is the local upper value and the first index of IntervalToBucket with bucket *i* minus 1 is the local lower value [7]. The subtraction of 1 when getting the local lower value is done to adhere to the rules of the intervals stated in the previous section.

However, values in IntervalToBucket may not contain all the buckets in the range from 1 to nBuckets if the timestamps in TS are separated by more than r time units thereby, not updating all the indices of UppLoc and LowLoc. This is taken care of by Loop 3 which extrapolates the values to fill the gaps where the indices have not been updated [7]. Loop 3 only shows the operation on UppLoc where the missing values are filled with the previous maximum value. Similarly, another loop can be added to fill the gaps for LowLoc by iterating backwards from nBuckets to 1 and updating the gaps with the next minimum value [7]. Lastly, Loop 4 takes care of updating the global curves index-wise by comparing the current global value with the local value and updating appropriately.

Figure 3.2: Illustration of the Algorithm Execution for the First Two Iterations over the Example Trace [7]

Figure 3.2 shows the execution of this algorithm for the first two iterations in the example trace TS = [3, 5, 6, 12, 16, 18]. The array values shown in the figure are the results after completing the execution of each loop. As discussed above, Loop 1 populates IntervalToBucket which is then used by Loop 2 to populate UppLoc and LowLoc. As mentioned earlier, not all the indices will be updated by Loop 2, and hence, Loop 3 fills the gaps. Lastly, Loop 4 updates the UppGlob and LowGlob. To ensure that the algorithm

follows the intuition discussed under Section 3.4.1, the values in UppGlob and LowGlob for iterations 0 and 1 in this figure are the same as that of the tuples in iterations 0 and 1 of the processing flow example in Figure 3.1.

## 3.4.3 Parallel Approach

This algorithm was formulated with the idea to transform the computations into embarrassingly parallel workloads. Such workloads are usually independent and need little or no communication between them.

**Redesign**: Loop 3 can be modified to perform the filling of gaps on the global curves instead of the local curves. However, this adds extra computation to Loop 2 as Loop 4 will be merged with Loop 2 to update global curves and also, add "markers" in the global curves to indicate the beginning and the end of gaps. These "markers" can then be used by Loop 3 to fill the gaps appropriately. This redesign allows Loop 3 to be moved outside the outermost loop thereby, adding potentially more parallel code, and the CPU can wait on the GPU to complete all parallel computations before copying the results from the GPU and then execute Loop 3.

**Loop 1**: From the pseudo-code in Algorithm 1 and the illustration of the arrival curve construction shown in Figure 3.2, each iteration of Loop 1 operate independently of one another for a given timestamp pivot. Using loop-based parallel pattern [11], Loop 1 can be transformed into a CUDA or OpenCL kernel.

**Outermost Loop**: As the update to the global curves for an event in a trace depends on the results of processing the previous events, the outermost loop in this algorithmic formulation cannot be parallelized. Hence, for each iteration of the outermost loop, kernels can be launched or enqueued into the command queue.

**Loop 2**: Loop 2 involves data dependencies between iterations. The operation can be described as a form of stream compaction i.e. given a vector, utilize a subset of this vector and output into another vector. This can also be parallelized in a kernel but not all threads or work-items will be active or executing the same instructions as only a subset of the input vector is used. Hence, the acceleration obtained from Loop 2 kernel will depend on the size of this subset which in turn depends on the distribution of the timestamps in TS and r. However, this drawback can be nullified as long as the overall parallelism achieved in the algorithm for a given set of parameters is large enough to overcome the overall sequential iterations.

**Parallelism Factor**: The loops that can be parallelized as discussed above involve parallelism over L and the number of buckets which depends on r. The number of buckets

increases as r decreases. Hence, the key factors to obtain acceleration via parallelism are L and r. Intuitively, a higher value of L, a lower value of r or a combination of both results in a higher number of iterations to operate on, thereby providing more opportunities for parallel computing.

# 3.5 Experiments

This section presents the execution time evaluation of sequential and parallel versions of the algorithm with GPUs on traces synthesized using a set of assigned values for L followed by the illustration of the arrival construction results on a QNX trace.

Figure 3.3: Arrival Curve Construction Execution Time Evaluation on a Synthesized Trace

#### Using Synthesized Traces on GPUs

The sequential version of the algorithm was implemented in C++ and executed on an 8-core Intel i7-3820 CPU 32GB of RAM. To demonstrate that the speedup obtained also depends on device specifications, two GPUs are used for each programming model. The CUDA implementation was executed on a Nvidia GeForce GTX 1080 Ti GPU and the recently released, Nvidia GeForce RTX 2080 Ti GPU which has relatively higher number of CUDA cores and better memory bandwidth. The OpenCL implementation was executed on an AMD R9-390X GPU and an AMD FirePro W9100 GPU. Though both GPUs have the same number of stream processors, the AMD R9-390X GPU has better memory bandwidth. The speedup is calculated as the ratio between the sequential CPU execution time to the GPU execution time. The setups used in this case are the following:

| Constant   | Variable  | Variable | 1080 Ti | 2080 Ti | R9-390X | W9100   |

|------------|-----------|----------|---------|---------|---------|---------|

| Parameters | Parameter | Values   | Speedup | Speedup | Speedup | Speedup |

|            |           | 10       | 0.015   | 0.016   | 0.002   | 0.002   |

|            |           | 100      | 0.052   | 0.061   | 0.032   | 0.032   |

|            |           | 1000     | 0.389   | 0.669   | 0.810   | 0.747   |

|            |           | 5000     | 1.793   | 3.956   | 5.798   | 3.564   |

| r=2        | L         | 10000    | 3.913   | 7.874   | 9.387   | 6.193   |

|            |           | 50000    | 10.612  | 32.769  | 21.325  | 17.455  |

|            |           | 100000   | 14.076  | 39.708  | 28.308  | 23.269  |

|            |           | 500000   | 19.921  | 54.087  | 37.346  | 30.380  |