# Book

# High-Performance and Time-Predictable Embedded Computing

Luis Miguel Pinho\* Eduardo Quiñones Marko Bertogna Andrea Marongiu Vincent Nélis\* Paolo Gai Juan Sancho

\*CISTER Research Centre CISTER-TR-180705

2018/07/01

#### High-Performance and Time-Predictable Embedded Computing

Luis Miguel Pinho\*, Eduardo Quiñones, Marko Bertogna, Andrea Marongiu, Vincent Nélis\*, Paolo Gai, Juan Sancho

\*CISTER Research Centre Polytechnic Institute of Porto (ISEP-IPP) Rua Dr. António Bernardino de Almeida, 431 4200-072 Porto Portugal Tel.: +351.22.8340509, Fax: +351.22.8321159 E-mail: Imp@isep.ipp.pt, nelis@isep.ipp.pt http://www.cister.isep.ipp.pt

#### Abstract

Nowadays, the prevalence of computing systems in our lives is so ubiquitous that we live in a cyber-physical world dominated by computer systems, from pacemakers to cars and airplanes. These systems demand for more computational performance to process large amounts of data from multiple data sources with guaranteed processing times. Actuating outside of the required timing bounds may cause the failure of the system, being vital for systems like planes, cars, business monitoring, e-trading, etc.

High-Performance and Time-Predictable Embedded Computing presents recent advances in software architecture and tools to support such complex systems, enabling the design of embedded computing devices which are able to deliver high-performance whilst guaranteeing the application required timing bounds.

Technical topics discussed in the book include: Parallel embedded platformsProgramming modelsMapping and scheduling of parallel computationsTiming and schedulability analysisRuntimes and operating systems

The work reflected in this book was done in the scope of the European project P SOCRATES, funded under the FP7 framework program of the European Commission. High-performance and time-predictable embedded computing is ideal for personnel in computer/communication/embedded industries as well as academic staff and master/research students in computer science, embedded systems, cyber-physical systems and internet-of-things.

River Publishers Series in Information Science and Technology

# High-Performance and Time-Predictable Embedded Computing

Luís Miguel Pinho, Eduardo Quiñones, Marko Bertogna, Andrea Marongiu, Vincent Nélis, Paolo Gai and Juan Sancho (Editors)

11/1

## High-Performance and Time-Predictable Embedded Computing

# **RIVER PUBLISHERS SERIES IN INFORMATION SCIENCE AND TECHNOLOGY**

Series Editors

K. C. CHEN

National Taiwan University Taipei, Taiwan and University of South Florida, USA

#### SANDEEP SHUKLA

Virginia Tech USA and Indian Institute of Technology Kanpur, India

Indexing: All books published in this series are submitted to the Web of Science Book Citation Index (BkCI), to CrossRef and to Google Scholar.

The "River Publishers Series in Information Science and Technology" covers research which ushers the 21st Century into an Internet and multimedia era. Multimedia means the theory and application of filtering, coding, estimating, analyzing, detecting and recognizing, synthesizing, classifying, recording, and reproducing signals by digital and/or analog devices or techniques, while the scope of "signal" includes audio, video, speech, image, musical, multimedia, data/content, geophysical, sonar/radar, bio/medical, sensation, etc. Networking suggests transportation of such multimedia contents among nodes in communication and/or computer networks, to facilitate the ultimate Internet.

Theory, technologies, protocols and standards, applications/services, practice and implementation of wired/wireless networking are all within the scope of this series. Based on network and communication science, we further extend the scope for 21st Century life through the knowledge in robotics, machine learning, embedded systems, cognitive science, pattern recognition, quantum/biological/molecular computation and information processing, biology, ecology, social science and economics, user behaviors and interface, and applications to health and society advance.

Books published in the series include research monographs, edited volumes, handbooks and textbooks. The books provide professionals, researchers, educators, and advanced students in the field with an invaluable insight into the latest research and developments.

Topics covered in the series include, but are by no means restricted to the following:

- · Communication/Computer Networking Technologies and Applications

- Queuing Theory

- Optimization

- Operation Research

- Stochastic Processes

- Information Theory

- Multimedia/Speech/Video Processing

- Computation and Information Processing

- Machine Intelligence

- Cognitive Science and Brian Science

- Embedded Systems

- Computer Architectures

- Reconfigurable Computing

- Cyber Security

For a list of other books in this series, visit www.riverpublishers.com

### High-Performance and Time-Predictable Embedded Computing

### Editors

Luís Miguel Pinho CISTER Research Centre, Polytechnic Institute of Porto, Portugal

## Eduardo Quiñones

Barcelona Supercomputing Center, Spain

Marko Bertogna University of Modena and Reggio Emilia, Italy

Andrea Marongiu Swiss Federal Institute of Technology Zurich, Switzerland

**Vincent Nélis** CISTER Research Centre, Polytechnic Institute of Porto, Portugal

> Paolo Gai Evidence Srl, Italy

> > Juan Sancho ATOS, Spain

Published, sold and distributed by: River Publishers Alsbjergvej 10 9260 Gistrup Denmark

River Publishers Lange Geer 44 2611 PW Delft The Netherlands

Tel.: +45369953197 www.riverpublishers.com

ISBN: 978-87-93609-69-3 (Hardback) 978-87-93609-62-4 (Ebook)

©The Editor(s) (if applicable) and The Author(s) 2018. This book is published open access.

#### **Open Access**

This book is distributed under the terms of the Creative Commons Attribution-Non-Commercial 4.0 International License, CC-BY-NC 4.0) (http://creativecommons.org/ licenses/by/4.0/), which permits use, duplication, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, a link is provided to the Creative Commons license and any changes made are indicated. The images or other third party material in this book are included in the work's Creative Commons license, unless indicated otherwise in the credit line; if such material is not included in the work's Creative Commons license and the respective action is not permitted by statutory regulation, users will need to obtain permission from the license holder to duplicate, adapt, or reproduce the material.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper.

### Contents

| Pr | eface          |         |                                                            | xiii  |

|----|----------------|---------|------------------------------------------------------------|-------|

| Li | st of C        | Contrib | utors                                                      | XV    |

| Li | st of F        | igures  |                                                            | xvii  |

| Li | st of <b>T</b> | ables   |                                                            | xxi   |

| Li | st of A        | Abbrevi | ations                                                     | xxiii |

| 1  | Intr           | oductio | n                                                          | 1     |

|    |                | 0       | Pinho, Eduardo Quiñones, Marko Bertogna,                   |       |

|    | Anai<br>1.1    |         | ongiu, Vincent Nélis, Paolo Gai and Juan Sancho<br>luction | 1     |

|    | 1.1            | 1.1.1   |                                                            | 1     |

|    |                | 1.1.1   | and Embedded Computing Domains                             | 3     |

|    |                | 1.1.2   | Parallelization Challenge                                  |       |

|    | 1.2            |         | -SOCRATES Project                                          |       |

|    | 1.3            |         | enges Addressed in This Book                               |       |

|    |                | 1.3.1   |                                                            |       |

|    |                | 1.3.2   |                                                            |       |

|    |                |         | on Many-core Systems                                       | 9     |

|    |                | 1.3.3   |                                                            |       |

|    |                |         | Analysis                                                   | 9     |

|    |                | 1.3.4   | -                                                          |       |

|    |                | 1.3.5   | Real-time Operating Systems                                |       |

|    | 1.4            | The U   | JpScale SDK                                                |       |

|    | 1.5            |         | nary                                                       |       |

|    |                |         | ences                                                      | 12    |

vi Contents

| 2 | Mar | iycore l                          | Platforms                                                                                                                                |                                                     | 15                                                             |

|---|-----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|

|   | And | rea Mar                           | ongiu, Vinc                                                                                                                              | cent Nélis and Patrick Meumeu Yomsi                 |                                                                |

|   | 2.1 | Introd                            | uction                                                                                                                                   |                                                     | 15                                                             |

|   | 2.2 |                                   |                                                                                                                                          | tectures                                            | 17                                                             |

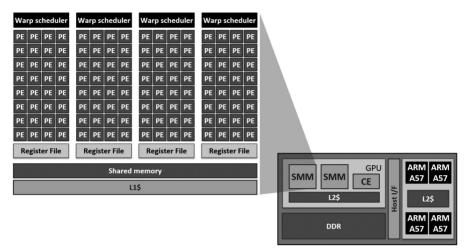

|   |     | 2.2.1                             | Xeon Phi                                                                                                                                 |                                                     | 17                                                             |

|   |     | 2.2.2                             |                                                                                                                                          |                                                     | 18                                                             |

|   |     | 2.2.3                             | -                                                                                                                                        | Tegra X1                                            | 19                                                             |

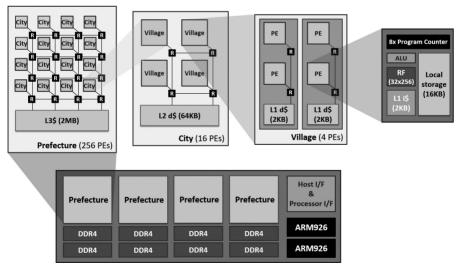

|   |     | 2.2.4                             |                                                                                                                                          | e                                                   | 21                                                             |

|   |     | 2.2.5                             |                                                                                                                                          | electronics STHORM                                  | 22                                                             |

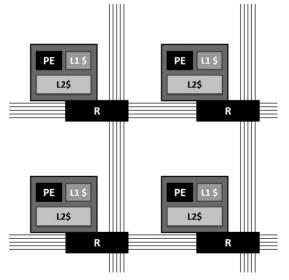

|   |     | 2.2.6                             |                                                                                                                                          | 7-V                                                 | 23                                                             |

|   |     | 2.2.7                             |                                                                                                                                          | one II                                              | 24                                                             |

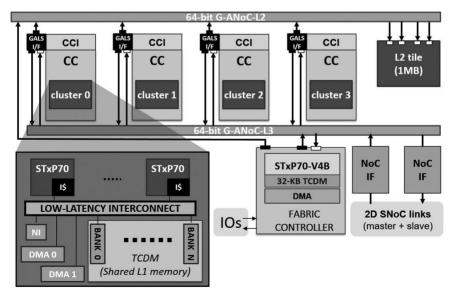

|   |     | 2.2.8                             | •                                                                                                                                        | IPPA-256                                            | 25                                                             |

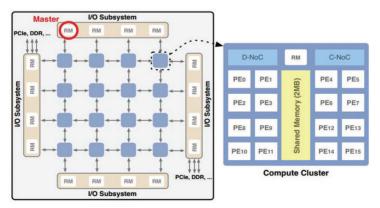

|   |     |                                   | 2.2.8.1                                                                                                                                  | The I/O subsystem                                   | 26                                                             |

|   |     |                                   | 2.2.8.2                                                                                                                                  | The Network-on-Chip (NoC)                           | 26                                                             |

|   |     |                                   | 2.2.8.3                                                                                                                                  | The Host-to-IOS communication                       | _0                                                             |

|   |     |                                   |                                                                                                                                          | protocol                                            | 28                                                             |

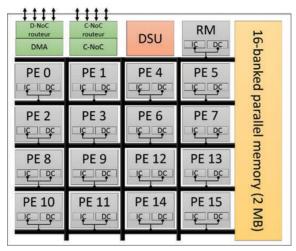

|   |     |                                   | 2.2.8.4                                                                                                                                  | Internal architecture of the compute                | _0                                                             |

|   |     |                                   |                                                                                                                                          | clusters                                            | 28                                                             |

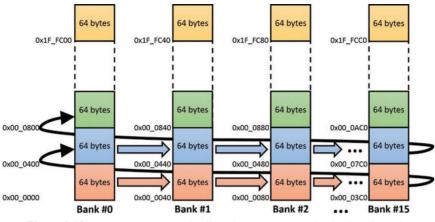

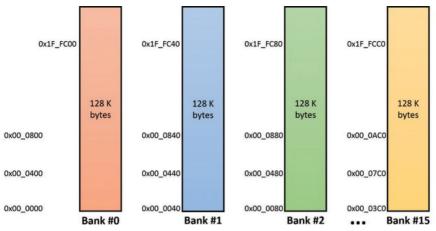

|   |     |                                   | 2.2.8.5                                                                                                                                  | The shared memory                                   | 29                                                             |

|   | 2.3 | Sumn                              |                                                                                                                                          |                                                     | 30                                                             |

|   |     |                                   | •                                                                                                                                        |                                                     | 31                                                             |

|   |     |                                   |                                                                                                                                          |                                                     |                                                                |

| 3 |     |                                   |                                                                                                                                          | rogramming with OpenMP                              | 33                                                             |

|   |     |                                   | rrano, Sara                                                                                                                              | a Royuela, Andrea Marongiu                          |                                                                |

|   |     | Eduard                            |                                                                                                                                          |                                                     |                                                                |

|   | 2 1 |                                   | o Quiñones                                                                                                                               | S C                                                 |                                                                |

|   | 3.1 | Introd                            | $\tilde{c}$                                                                                                                              |                                                     | 33                                                             |

|   | 5.1 |                                   | uction<br>Introduct                                                                                                                      | ion to Parallel Programming Models                  | 34                                                             |

|   | 5.1 | Introd                            | Iuction<br>Introduct<br>3.1.1.1                                                                                                          | ion to Parallel Programming Models<br>POSIX threads | 34<br>35                                                       |

|   | 5.1 | Introd                            | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2                                                                                               | ion to Parallel Programming Models<br>POSIX threads | 34<br>35<br>35                                                 |

|   | 5.1 | Introd                            | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3                                                                                    | ion to Parallel Programming Models<br>POSIX threads | 34<br>35<br>35<br>36                                           |

|   | 5.1 | Introd                            | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4                                                                         | ion to Parallel Programming Models<br>POSIX threads | 34<br>35<br>35<br>36<br>36                                     |

|   | 3.1 | Introd                            | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4<br>3.1.1.5                                                              | ion to Parallel Programming Models<br>POSIX threads | 34<br>35<br>35<br>36<br>36<br>36                               |

|   |     | Introd<br>3.1.1                   | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4<br>3.1.1.5<br>3.1.1.6                                                   | ion to Parallel Programming Models POSIX threads    | 34<br>35<br>35<br>36<br>36<br>36<br>37                         |

|   | 3.1 | Introd<br>3.1.1<br>The C          | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4<br>3.1.1.5<br>3.1.1.6<br>DpenMP Pa                                      | ion to Parallel Programming Models<br>POSIX threads | 34<br>35<br>35<br>36<br>36<br>36<br>36<br>37<br>37             |

|   |     | Introd<br>3.1.1<br>The C<br>3.2.1 | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4<br>3.1.1.5<br>3.1.1.6<br>DpenMP Pa<br>Introduct                         | ion to Parallel Programming Models<br>POSIX threads | 34<br>35<br>36<br>36<br>36<br>36<br>37<br>37<br>37             |

|   |     | Introd<br>3.1.1<br>The C          | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4<br>3.1.1.5<br>3.1.1.6<br>DpenMP Pa<br>Introduct<br>Parallel M           | ion to Parallel Programming Models POSIX threads    | 34<br>35<br>36<br>36<br>36<br>37<br>37<br>37<br>37             |

|   |     | Introd<br>3.1.1<br>The C<br>3.2.1 | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4<br>3.1.1.5<br>3.1.1.6<br>DenMP Pa<br>Introduct<br>Parallel M<br>3.2.2.1 | ion to Parallel Programming Models<br>POSIX threads | 34<br>35<br>36<br>36<br>36<br>36<br>37<br>37<br>37<br>39<br>39 |

|   |     | Introd<br>3.1.1<br>The C<br>3.2.1 | Luction<br>Introduct<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4<br>3.1.1.5<br>3.1.1.6<br>DpenMP Pa<br>Introduct<br>Parallel M           | ion to Parallel Programming Models POSIX threads    | 34<br>35<br>36<br>36<br>36<br>37<br>37<br>37<br>37             |

|   |            | 3.2.3          | An Open       | MP Example                                   | 42       |

|---|------------|----------------|---------------|----------------------------------------------|----------|

|   | 3.3        | Timin          | g Propertie   | es of OpenMP Tasking Model                   | 43       |

|   |            | 3.3.1          |               | DAG Scheduling Model of Parallel             |          |

|   |            |                |               | ions                                         | 43       |

|   |            | 3.3.2          |               | nding the OpenMP Tasking Model               | 44       |

|   |            | 3.3.3          | OpenMP        | and Timing Predictability                    | 46       |

|   |            |                | 3.3.3.1       | Extracting the DAG of an OpenMP              |          |

|   |            |                |               | program                                      | 47       |

|   |            |                | 3.3.3.2       | WCET analysis is applied to <i>tasks</i>     |          |

|   |            |                |               | and tasks parts                              | 48       |

|   |            |                | 3.3.3.3       | DAG-based scheduling must not                |          |

|   |            |                |               | violate the TSCs                             | 49       |

|   | 3.4        | Extrac         | ting the T    | iming Information of an OpenMP               |          |

|   |            | Progra         | um            |                                              | 51       |

|   |            | 3.4.1          |               | Structure Stage                              | 52       |

|   |            |                | 3.4.1.1       | Parallel control flow analysis               | 53       |

|   |            |                | 3.4.1.2       | Induction variables analysis                 | 53       |

|   |            |                | 3.4.1.3       | Reaching definitions and range analysis      | 53       |

|   |            |                | 3.4.1.4       | Putting all together: The wave-front         |          |

|   |            |                |               | example                                      | 53       |

|   |            | 3.4.2          | Task Exp      | bansion Stage                                | 54       |

|   |            |                | 3.4.2.1       | Control flow expansion and                   |          |

|   |            |                |               | synchronization predicate resolution         | 54       |

|   |            |                | 3.4.2.2       | $t_{id}$ : A unique task instance identifier | 56       |

|   |            |                | 3.4.2.3       | Missing information when deriving            |          |

|   |            |                |               | the DAG                                      | 57       |

|   |            | 3.4.3          | Compile       | r Complexity                                 | 58       |

|   | 3.5        |                | •             |                                              | 58       |

|   |            | Refere         | ences         |                                              | 59       |

| 4 | Ман        |                | ah a durlin a | and Cahadulahilitu Analusia                  | $\alpha$ |

| 4 | -          |                | _             | , and Schedulability Analysis                | 63       |

|   |            | 0              |               | Bertogna, Alessandra Melani,                 |          |

|   |            | ~              |               | l Maria A. Serrano                           | ()       |

|   | 4.1<br>4.2 |                |               |                                              | 63<br>64 |

|   | 4.2<br>4.3 |                |               |                                              | 66       |

|   | 4.3        |                |               | duler                                        | 00       |

|   |            | 4.3.1          |               | mality of EDF on Preemptive                  | 66       |

|   |            | 122            |               | essors                                       | 67       |

|   |            | 4.3.2<br>4.3.3 |               | luling Algorithms                            | 67       |

|   |            | 4.3.3          | Linned        | Preemption Scheduling                        | 08       |

|     | 4.3.4  | Limited F  | Preemption Schedulability Analysis                    | 69  |

|-----|--------|------------|-------------------------------------------------------|-----|

| 4.4 | Global | Scheduler  | with Migration Support                                | 70  |

|     | 4.4.1  | Migratior  | n-based Scheduler                                     | 70  |

|     | 4.4.2  | Putting A  | ll Together                                           | 72  |

|     | 4.4.3  |            | ntation of a Limited Preemption                       |     |

|     |        | Schedule   | · · · · · · · · · · · · · · · · · · ·                 | 73  |

| 4.5 | Overal |            | bility Analysis                                       | 75  |

|     | 4.5.1  | Model Fo   | rmalization                                           | 75  |

|     | 4.5.2  |            | terference of cp-tasks                                | 78  |

|     | 4.5.3  | Response   | Time Analysis                                         | 80  |

|     |        | 4.5.3.1    | Inter-task interference                               | 80  |

|     |        | 4.5.3.2    | Intra-task interference                               | 82  |

|     |        | 4.5.3.3    | Computation of cp-task parameters                     | 84  |

|     | 4.5.4  | Non-cond   | litional DAG Tasks                                    | 86  |

|     | 4.5.5  | Series-Pa  | rallel Conditional DAG Tasks                          | 86  |

|     | 4.5.6  | Schedula   | bility Condition                                      | 86  |

| 4.6 | Specia | lizing Ana | lysis for Limited Pre-emption Global/                 |     |

|     | Dynan  | nic Approa | ch                                                    | 87  |

|     | 4.6.1  | Blocking   | Impact of the Largest NPRs (LP-max)                   | 88  |

|     | 4.6.2  | Blocking   | Impact of the Largest Parallel NPRs                   |     |

|     |        | (LP-ILP)   |                                                       | 88  |

|     |        | 4.6.2.1    | LP worst-case workload of a task                      |     |

|     |        |            | executing on c cores                                  | 89  |

|     |        | 4.6.2.2    | Overall LP worst-case workload                        | 90  |

|     |        | 4.6.2.3    | Lower-priority interference                           | 91  |

|     | 4.6.3  |            | tion of Response Time Factors                         |     |

|     |        |            | •••••                                                 | 92  |

|     |        | 4.6.3.1    | Worst-case workload of $	au_i$ executing              |     |

|     |        |            | on c cores: $\boldsymbol{\mu}_i[c]$                   | 92  |

|     |        | 4.6.3.2    | Overall LP worst-case workload of lp(k)               |     |

|     |        |            | per execution scenario $s_l: \rho_k[s_l] \dots \dots$ | 94  |

|     | 4.6.4  |            | ity                                                   | 95  |

| 4.7 |        |            | lysis for the Partitioned/Static Approach             | 96  |

|     | 4.7.1  |            | ulation                                               | 96  |

|     |        | 4.7.1.1    | Tied tasks                                            | 97  |

|     |        | 4.7.1.2    | Untied tasks                                          | 99  |

|     |        | 4.7.1.3    | Complexity                                            | 100 |

|     | 4.7.2  |            | Approaches                                            | 100 |

|     |        | 4.7.2.1    | Tied tasks                                            | 101 |

|   |      |          | 4.7.2.2 Untied tasks                                | 103 |

|---|------|----------|-----------------------------------------------------|-----|

|   |      | 4.7.3    | Integrating Interference from Additional            |     |

|   |      |          | RT Tasks                                            | 103 |

|   |      | 4.7.4    | Critical Instant                                    | 104 |

|   |      | 4.7.5    | Response-time Upper Bound                           | 105 |

|   | 4.8  | Sched    | luling for I/O Cores                                | 107 |

|   | 4.9  | Sumn     | nary                                                | 107 |

|   |      | Refere   | ences                                               | 109 |

| 5 | Tim  | ing Ana  | alysis Methodology                                  | 113 |

|   | Vinc | ent Néli | s, Patrick Meumeu Yomsi and Luís Miguel Pinho       |     |

|   | 5.1  |          | luction                                             | 113 |

|   |      | 5.1.1    | Static WCET Analysis Techniques                     | 115 |

|   |      | 5.1.2    | Measurement-based WCET Analysis Techniques          | 118 |

|   |      | 5.1.3    | Hybrid WCET Techniques                              | 119 |

|   |      | 5.1.4    | Measurement-based Probabilistic Techniques          | 120 |

|   | 5.2  | Our C    | Choice of Methodology for WCET Estimation           | 121 |

|   |      | 5.2.1    | Why Not Use Static Approaches?                      | 122 |

|   |      | 5.2.2    | Why Use Measurement-based Techniques?               | 124 |

|   | 5.3  | Descr    | iption of Our Timing Analysis Methodology           | 127 |

|   |      | 5.3.1    | Intrinsic vs. Extrinsic Execution Times             | 127 |

|   |      | 5.3.2    | The Concept of Safety Margins                       | 128 |

|   |      | 5.3.3    | Our Proposed Timing Methodology at a Glance         | 130 |

|   |      | 5.3.4    | Overview of the Application Structure               | 131 |

|   |      | 5.3.5    | Automatic Insertion and Removal                     |     |

|   |      |          | of the Trace-points                                 | 133 |

|   |      |          | 5.3.5.1 How to insert the trace-points              | 133 |

|   |      |          | 5.3.5.2 How to remove the trace-points              | 135 |

|   |      | 5.3.6    | Extract the Intrinsic Execution Time: The Isolation |     |

|   |      |          | Mode                                                | 136 |

|   |      | 5.3.7    | Extract the Extrinsic Execution Time:               |     |

|   |      |          | The Contention Mode                                 | 137 |

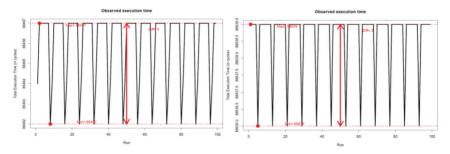

|   |      | 5.3.8    | Extract the Execution Time in Real Situation:       |     |

|   |      |          | The Deployment Mode                                 | 141 |

|   |      | 5.3.9    | Derive WCET Estimates                               | 141 |

|   | 5.4  |          | nary                                                | 143 |

|   |      | Refere   | ences                                               | 143 |

| Х | Contents |

|---|----------|

| Х | Contents |

| Ope | nMP R   | untime             |                                                  | 145 |

|-----|---------|--------------------|--------------------------------------------------|-----|

| And | rea Mar | ongiu, Gii         | useppe Tagliavini and Eduardo Quiñones           |     |

| 6.1 | Introc  | luction            |                                                  | 145 |

| 6.2 | Offloa  | ading Libr         | ary Design                                       | 146 |

| 6.3 | Taski   | ng Runtim          | le                                               | 148 |

|     | 6.3.1   | Task De            | pendency Management                              | 155 |

| 6.4 | Exper   | rimental R         | esults                                           | 158 |

|     | 6.4.1   | Offloadi           | ng Library                                       | 159 |

|     | 6.4.2   |                    | Runtime                                          | 160 |

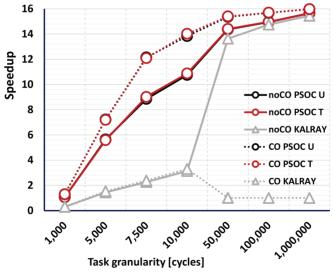

|     |         | 6.4.2.1            | Applications with a linear generation pattern    | 160 |

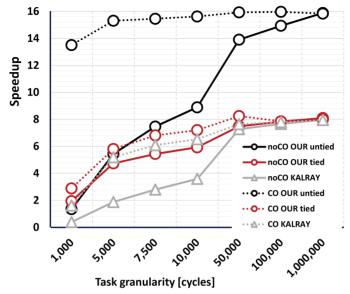

|     |         | 6.4.2.2            | Applications with a recursive generation pattern | 162 |

|     |         | 6.4.2.3            | Applications with mixed patterns                 | 162 |

|     |         | 6.4.2.3<br>6.4.2.4 | Impact of cutoff on LINEAR and                   | 105 |

|     |         | 0.4.2.4            | RECURSIVE applications                           | 165 |

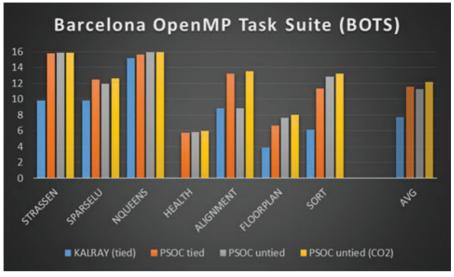

|     |         | 6.4.2.5            | Real applications                                | 165 |

|     | 6.4.3   |                    | on of the Task Dependency Mechanism              | 167 |

|     | 0.4.5   | 6.4.3.1            | Performance speedup and memory                   | 107 |

|     |         | 0.4.3.1            |                                                  | 168 |

|     |         | 6.4.3.2            | usage                                            | 100 |

|     |         | 0.4.3.2            | on the MPPA                                      | 170 |

| 5.5 | Sumn    | narw               | · · · · · · · · · · · · · · · · · · ·            | 170 |

| ).) |         | •                  |                                                  | 171 |

|     | Kelei   | chees              |                                                  | 1/1 |

|     |         | -                  | g Systems                                        | 173 |

|     |         |                    | rico Guidieri, Bruno Morelli,                    |     |

|     |         | 0                  | useppe Tagliavini and Paolo Gai                  |     |

| 7.1 |         |                    |                                                  | 173 |

| 7.2 |         |                    | t                                                | 175 |

|     | 7.2.1   |                    | ne Support in Linux                              | 175 |

|     |         | 7.2.1.1            | Hard real-time support                           | 176 |

|     |         | 7.2.1.2            | Latency reduction                                | 178 |

|     |         | 7.2.1.3            | Real-time CPU scheduling                         | 180 |

|     | 7.2.2   |                    | of Existing Embedded RTOSs                       | 180 |

|     | 7.2.3   | Classific          | cation of Embedded RTOSs                         | 186 |

| 7.3 | -       | irements for       | or The Choice of The Run Time System             | 187 |

|     | 7.3.1   | •                  | ming Model                                       | 187 |

|     | 7.3.2   | Preempt            | ion Support                                      | 187 |

|       | 7.3.3  | Migration | Support                                  | 188 |

|-------|--------|-----------|------------------------------------------|-----|

|       | 7.3.4  |           | g Characteristics                        | 188 |

|       | 7.3.5  |           | nalysis                                  | 188 |

| 7.4   | RTOS   |           | · · · · · · · · · · · · · · · · · · ·    | 190 |

|       | 7.4.1  |           | cessor                                   | 190 |

|       | 7.4.2  |           | Processor                                | 190 |

| 7.5   | Operat |           | n Support                                | 191 |

|       | 7.5.1  |           |                                          | 191 |

|       | 7.5.2  |           | Interprise Support                       | 191 |

|       |        | 7.5.2.1   | Exokernel support                        | 191 |

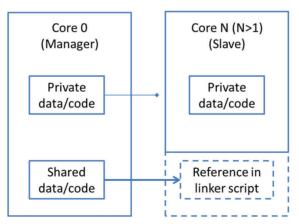

|       |        | 7.5.2.2   | Single-ELF multicore ERIKA               |     |

|       |        |           | Enterprise                               | 192 |

|       |        | 7.5.2.3   | Support for limited preemption, job, and |     |

|       |        |           | global scheduling                        | 192 |

|       |        | 7.5.2.4   | New ERIKA Enterprise primitives          | 193 |

|       |        | 7.5.2.5   | New data structures                      | 194 |

|       |        | 7.5.2.6   | Dynamic task creation                    | 196 |

|       |        | 7.5.2.7   | IRQ handlers as tasks                    | 196 |

|       |        | 7.5.2.8   | File hierarchy                           | 197 |

|       |        | 7.5.2.9   | Early performance estimation             | 197 |

| 7.6   | Summ   | ary       |                                          | 200 |

|       |        |           |                                          | 200 |

| Index |        |           |                                          | 203 |

About the Editors

205

### Preface

Nowadays, the prevalence of electronic and computing systems in our lives is so ubiquitous that it would not be far-fetched to state that we live in a cyberphysical world dominated by computer systems. Examples include pacemakers implanted within the human body to regulate and monitor heartbeats, cars and airplanes transporting us, smart grids, and traffic management.

All these systems demand more and more computational performance to process large amounts of data from multiple data sources, and some of them with guaranteed processing response times; in other words, systems required to deliver their results within pre-defined (and sometimes extremely short) time bounds. This timing aspect is vital for systems like planes, cars, business monitoring, e-trading, etc. Examples can be found in intelligent transportation systems for fuel consumption reduction in cities or railways, or autonomous driving of vehicles. All these systems require processing and actuation based on large amounts of data coming from real-time sensor information.

As a result, the computer electronic devices which these systems depend on are constantly required to become more and more powerful and reliable, while remaining affordable. In order to cope with such performance requirements, chip designers have recently started producing chips containing multiple processing units, the so-called multi-core processors, effectively integrating multiple computers within a single chip, and more recently the many-core processors, with dozens or hundreds of cores, interconnected with complex networks on chip. This radical shift in the chip design paved the way for parallel computing: rather than processing the data sequentially, the cooperation of multiple processing elements within the same chip allows systems to be executed concurrently, in parallel.

Unfortunately, the parallelization of the computing activities brought up many challenges, because it affects the timing behavior of the systems as well as the entire way people think and design computers: from the design of the hardware architecture, through the operating system up to the conceptualization of the end-user application. Therefore, although many-core processors are promising candidates to improve the responsiveness of these systems, the interactions that the different computing elements may have within the chip can seriously affect the performance opportunities brought by parallel execution. Moreover, providing timing guarantees becomes harder, because the timing behavior of the system running within a many-core processor depends on interactions that are most of the time not known by the system designer. This makes system analysts struggle in trying to provide timing guarantees for such platforms. Finally, most of the optimization mechanisms buried deep inside the chip are geared only to increase performance and execution speed rather than providing predictable time behavior.

These challenges need to be addressed by introducing predictability in the vertical stack from high-level programming models to operating systems, together with new offline analysis techniques. This book covers the main techniques to enable performance and predictability of embedded applications. The book starts with an overview of some of the current manycore embedded platforms, and then addresses how to support predictability and performance in different aspects of computation: a predictable parallel programming model, the mapping and scheduling of real-time parallel computation, the timing analysis of parallel code, as well as the techniques to support predictability in parallel runtimes and operating systems.

The work reflected in this book was done in the scope of the European project P-SOCRATES, funded under the FP7 framework program of the European Commission. The project website (www.p-socrates.eu), provides further detailed information on the techniques presented here. Moreover, a reference implementation of the methodologies and tools was released as the UpScale Software Development Kit (http://www.upscale-sdk.com).

Luís Miguel Pinho Eduardo Quiñones Marko Bertogna Andrea Marongiu Vincent Nélis Paolo Gai Juan Sancho

February 2018

### **List of Contributors**

Alessandra Melani, University of Modena and Reggio Emilia, Italy

**Andrea Marongiu**, *Swiss Federal Institute of Technology in Zürich (ETHZ), Switzerland; and University of Bologna, Italy*

Bruno Morelli, Evidence SRL, Italy

Claudio Scordino, Evidence SRL, Italy

Eduardo Quiñones, Barcelona Supercomputing Center (BSC), Spain

Errico Guidieri, Evidence SRL, Italy

Giuseppe Tagliavini, University of Bologna, Italy

Juan Sancho, ATOS, Spain

Luís Miguel Pinho, CISTER Research Centre, Polytechnic Institute of Porto, Portugal

Maria A. Serrano, Barcelona Supercomputing Center (BSC), Spain

Marko Bertogna, University of Modena and Reggio Emilia, Italy

Paolo Burgio, University of Modena and Reggio Emilia, Italy

Paolo Gai, Evidence SRL, Italy

#### xvi List of Contributors

**Patrick Meumeu Yomsi**, CISTER Research Centre, Polytechnic Institute of Porto, Portugal

Sara Royuela, Barcelona Supercomputing Center (BSC), Spain

Vincent Nélis, CISTER Research Centre, Polytechnic Institute of Porto, Portugal

## **List of Figures**

| Figure 1.1  | P-SOCRATES Global perspective.                  | 7  |

|-------------|-------------------------------------------------|----|

| Figure 1.2  | P-SOCRATES combines high-performance            |    |

|             | parallel programming models, high-end embedded  |    |

|             | many-core platforms and real-time systems       |    |

|             | technology.                                     | 7  |

| Figure 1.3  | Vertical stack of application decomposition.    | 8  |

| Figure 1.4  | The UpScale SDK.                                | 11 |

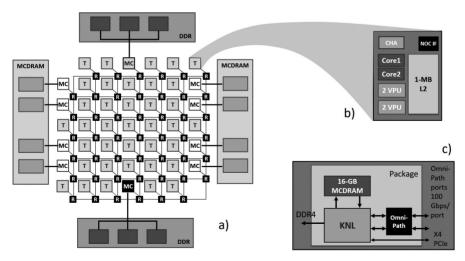

| Figure 2.1  | Knights Landing (KNL) block diagram:            |    |

| 0           | (a) the CPU, (b) an example tile, and (c) KNL   |    |

|             | with Omni-Path Fabric integrated on the CPU     |    |

|             | package                                         | 17 |

| Figure 2.2  | PEZY-SC architecture block diagram.             | 19 |

| Figure 2.3  | NVIDIA Tegra X1 block diagram.                  | 20 |

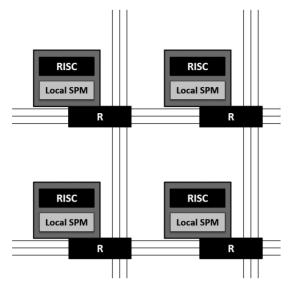

| Figure 2.4  | Tilera <i>Tile</i> architectural template.      | 21 |

| Figure 2.5  | STMicroelectronics STHORM heterogeneous         |    |

| U           | system.                                         | 22 |

| Figure 2.6  | Block diagram of the Epiphany-V chip from       |    |

| 0           | Adapteva.                                       | 23 |

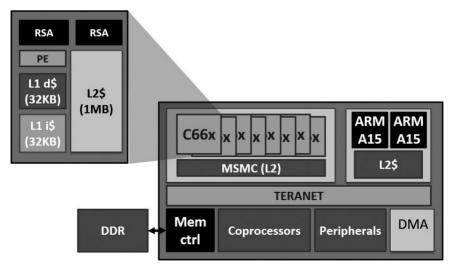

| Figure 2.7  | Texas Instrument Keystone II heterogeneous      |    |

| U           | system.                                         | 24 |

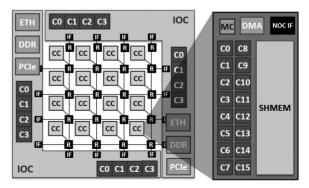

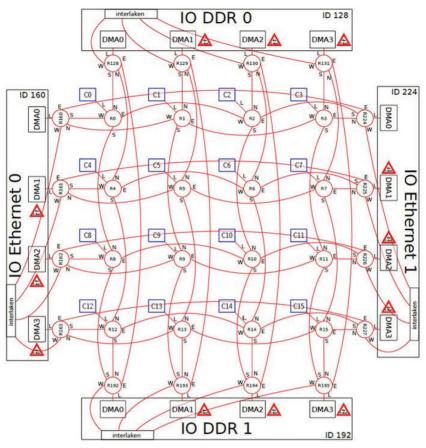

| Figure 2.8  | High-level view of the Kalray MPPA-256          |    |

| 0           | processor.                                      | 25 |

| Figure 2.9  | MPPA-256 NoC architecture.                      | 27 |

| Figure 2.10 | A master task runs on an RM of an I/O           |    |

| 0           | subsystem                                       | 28 |

| Figure 2.11 | Internal architecture of a compute cluster      | 29 |

| Figure 2.12 | Memory accesses distributed across memory banks |    |

| C           | (interleaved)                                   | 30 |

| Figure 2.13 | Memory accesses targeting a same memory bank    |    |

| -           |                                                 | 31 |

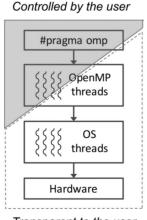

| Figure 3.1  | OpenMP components stack                         | 38 |

| 0           | (contiguous).                                   |    |

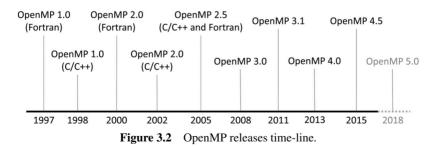

| Figure 3.2   | OpenMP releases time-line                                        | 39  |

|--------------|------------------------------------------------------------------|-----|

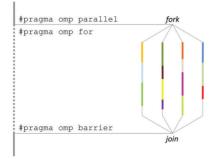

| Figure 3.3   | Structured parallelism.                                          | 40  |

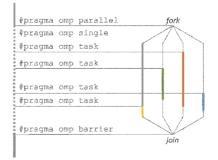

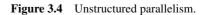

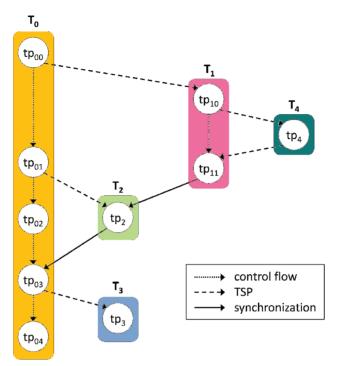

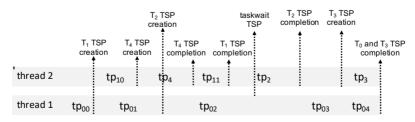

| Figure 3.4   | Unstructured parallelism.                                        | 40  |

| Figure 3.5   | OpenMP-DAG composed of task parts based                          |     |

|              | on the code                                                      | 48  |

| Figure 3.6   | DAG composed on task region parts                                | 50  |

| Figure 3.7   | aDAG of the OpenMP program.                                      | 55  |

| Figure 3.8   | The DAG of the OpenMP program                                    | 56  |

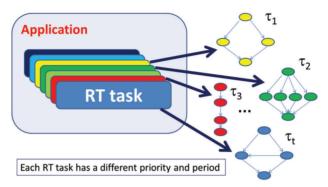

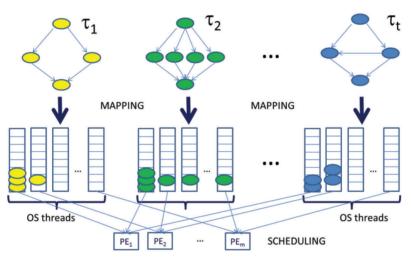

| Figure 4.1   | An application is composed of multiple real-time tasks.          | 65  |

| Figure 4.2   | RT tasks are mapped to OS threads, which are                     |     |

| 0            | scheduled on the processing elements                             | 65  |

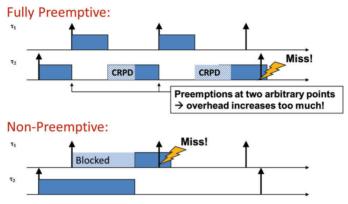

| Figure 4.3   | Fully preemptive vs. non-preemptive scheduling:                  |     |

| 0            | preemption overhead and blocking delay may cause                 |     |

|              | deadline misses.                                                 | 69  |

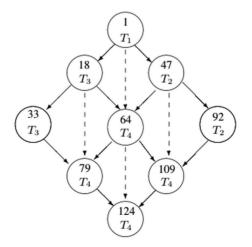

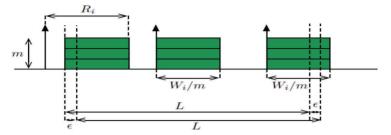

| Figure 4.4   | A sample cp-task. Each vertex is labeled                         |     |

| C            | with the WCET of the corresponding sub-task                      | 76  |

| Figure 4.5   | Work-case scenario to maximize the workload                      |     |

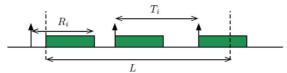

| C            | of an task $\tau_i$ , in the sequential case                     | 81  |

| Figure 4.6   | Worst-case scenario to maximize the workload                     |     |

|              | of an interfering cp-task $\tau_i$                               | 82  |

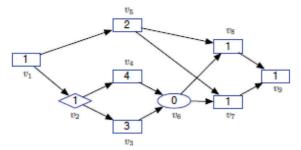

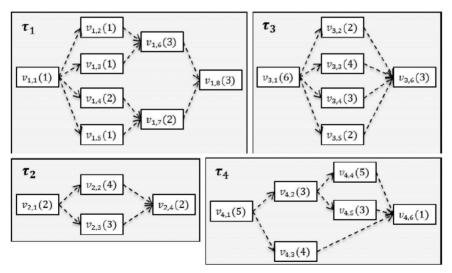

| Figure 4.7   | DAGs of lp(k) tasks; the $C_{i,j}$ of each node $v_{i,j}$        |     |

|              | is presented in parenthesis                                      | 89  |

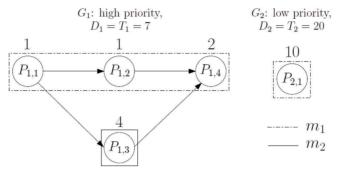

| Figure 4.8   | Tasks example.                                                   | 104 |

| Figure 4.9   | Different release patterns for the example of                    |     |

|              | Figure 4.8. (a) represents the most optimistic case,             |     |

|              | while (c) the most pessimistic, i.e., yelding to the             |     |

|              | highest WCET. (b) represents an intermediate                     |     |

|              | case                                                             | 105 |

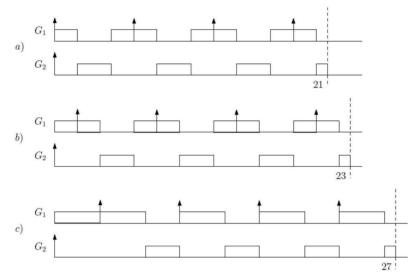

| Figure 5.1   | Example distribution of execution time                           | 115 |

| Figure 5.2   | Extended task dependency graph (eTDG) of an example application. | 133 |

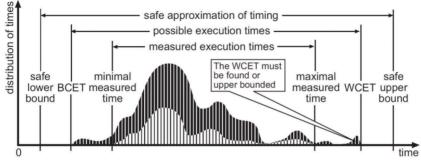

| Figure 5.3   | Impact of an unused variable on the execution time               | 155 |

| i igui e eie | of an example application.                                       | 135 |

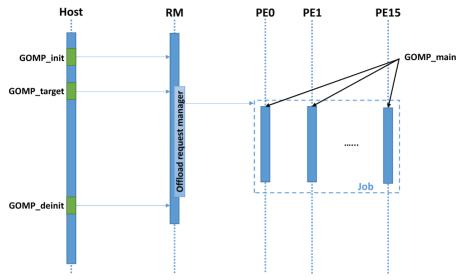

| Figure 6.1   | Timing diagram of an offloading procedure.                       | 147 |

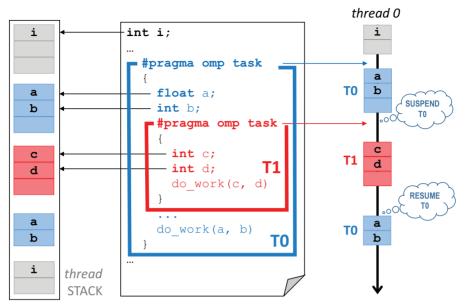

| Figure 6.2   | Task suspension in the baseline implementation                   | /   |

|              | (considering tied tasks and WFS).                                | 151 |

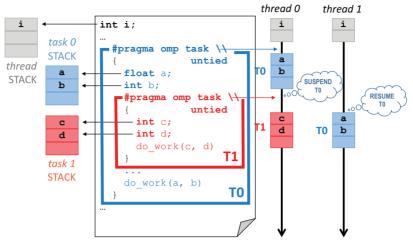

| Figure 6.3   | Untied task suspension with task contexts                        |     |

| 0            | and per-task stacks.                                             | 152 |

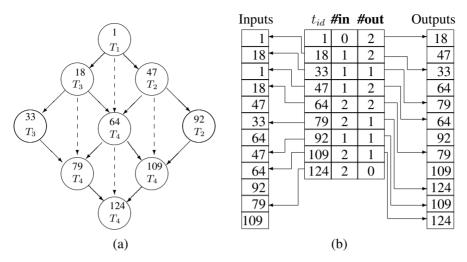

| Figure 6.4  | On the left (a), the DAG of an OpenMP program.         |     |

|-------------|--------------------------------------------------------|-----|

|             | On the right (b), the sparse matrix data structure     | 1   |

|             | implementing DAG shown on the left.                    | 157 |

| Figure 6.5  | Costs of offload initialization                        | 159 |

| Figure 6.6  | Speedup of the LINEAR benchmark (no cutoff)            | 161 |

| Figure 6.7  | Speedup of the RECURSIVE benchmark                     |     |

|             | (no cutoff)                                            | 163 |

| Figure 6.8  | Structure of the MIXED microbenchmark                  | 164 |

| Figure 6.9  | Speedup of the MIXED benchmark                         | 164 |

| Figure 6.10 | Speedup of the LINEAR benchmark                        |     |

|             | (with cutoff)                                          | 165 |

| Figure 6.11 | Speedup of the RECURSIVE benchmark                     |     |

|             | (with cutoff)                                          | 166 |

| Figure 6.12 | Speedups for the BOTS benchmarks                       | 167 |

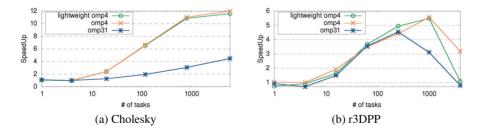

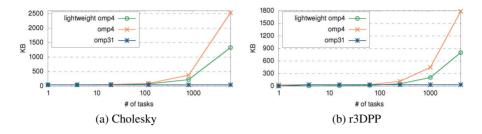

| Figure 6.13 | Performance speedup of the Cholesky (a) and            |     |

|             | r3DPP (b) running with <i>lightweight omp4</i> , omp4, |     |

|             | and <i>omp 3.1</i> , and varying the number of tasks   | 168 |

| Figure 6.14 | Memory usage (in KB) of the Cholesky (a) r3DPP         |     |

| -           | (b) running with <i>lightweight omp4</i> , omp4, and   |     |

|             | omp 3.1, and varying the number of tasks               | 169 |

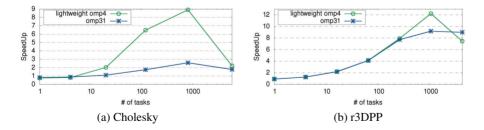

| Figure 6.15 | Performance speedup of the Cholesky (a) and            |     |

| 0           | r3DPP (b) running on the MPPA with <i>lightweight</i>  |     |

|             | omp4, omp4, and omp 3.1, and varying the number        |     |

|             | of tasks.                                              | 170 |

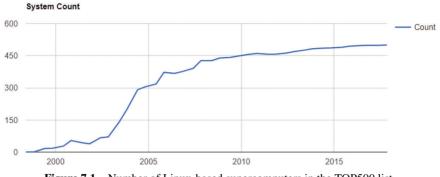

| Figure 7.1  | Number of Linux-based supercomputers                   |     |

| 8           | in the TOP500 list.                                    | 174 |

| Figure 7.2  | Structure of the multicore images in the original      |     |

| 3           | ERIKA Enterprise structure.                            | 195 |

| Figure 7.3  | Structure of the Single-ELF image produced             |     |

| 8           | by ERIKA Enterprise.                                   | 196 |

|             |                                                        | 1/0 |

## **List of Tables**

| Table 3.1 | Parallel programming models comparison               | 35  |

|-----------|------------------------------------------------------|-----|

| Table 4.1 | Worst-case workloads of tasks in Figure 4.7          | 90  |

| Table 4.2 | Five possible scenarios of taskset in Figure 4.7,    |     |

|           | assuming a four core system                          | 91  |

| Table 4.3 | Computed worst-case workload for each                |     |

|           | of the scenarios in Table 4.2                        | 91  |

| Table 6.1 | Memory usage of the sparse matrix (in KB),           |     |

|           | varying the number of tasks instantiated             | 170 |

| Table 7.1 | Classification of RTOSs                              | 186 |

| Table 7.2 | ERIKA Enterprise footprint (expressed in bytes)      | 198 |

| Table 7.3 | Timings (expressed in clock ticks)                   | 199 |

| Table 7.4 | Footprint comparison between ERIKA and NodeOS        |     |

|           | for a 16-core cluster (expressed in bytes)           | 199 |

| Table 7.5 | Thread creation/activation times (expressed in clock |     |

|           | ticks)                                               | 199 |

|           |                                                      |     |

### **List of Abbreviations**

| ADEOS   | Adaptive Domain Environment for Operating Systems, a      |

|---------|-----------------------------------------------------------|

|         | patch used by RTAI and Xenomai                            |

| ALU     | Arithmetic logic unit                                     |

| API     | Application Programming Interface                         |

| APIC    | Programmable timer on x86 machines                        |

| AUTOSAR | International consortium that defines automotive API      |

| BCET    | Best-Case Execution Time                                  |

| BFS     | Breadth First Scheduling                                  |

| BOTS    | Barcelona OpenMP task suite                               |

| BSD     | Berkeley software license                                 |

| CBS     | Constant Bandwidth Server, a scheduling algorithm         |

| CFG     | Control Flow Graph                                        |

| CMP     | chip multi-processor                                      |

| COTS    | Commercial Off-The-Shelf                                  |

| CPU     | central processing unit                                   |

| CUDA    | Compute Unified Device Architecture                       |

| DAG     | Direct Acyclic Graph                                      |

| DDR     | double data rate                                          |

| DMA     | direct memory access (engine)                             |

| DRAM    | dynamic random-access memory                              |

| DSP     | digital signal processor                                  |

| DSU     | debug system unit                                         |

| EDF     | Earliest Deadline First Scheduler, a scheduling algorithm |

| ELF     | binary format that contain executables                    |

| eTDG    | Extended Task Dependency Graph                            |

| EVT     | Extreme Value Theory                                      |

| FIFO    | First-In First-Out                                        |

| FLOPS   | floating-point operations per second                      |

| FPGA    | Field-Programmable Gate Array                             |

| GPGPU   | General Purpose Graphics Processing Unit                  |

| GPL     | General Public License                                    |

|         |                                                           |

#### xxiv List of Abbreviations

| GPOS       | General purpose Operating System                                      |  |

|------------|-----------------------------------------------------------------------|--|

| GPU        | Graphics Processing Unit                                              |  |

| GRUB       | Greedy Reclamation of Unused Bandwidth, a scheduling                  |  |

| OKOD       | algorithm                                                             |  |

| HAL        | Hardware Abstraction Layer                                            |  |

| HMI        | Human Machine Interface                                               |  |

| HPC        | High Performance Computing                                            |  |

| HRT        | High Resolution Timers                                                |  |

| ID         | Identifier                                                            |  |

| IEC        | International Electrotechnical Commission                             |  |

| IG         | Interfactorial Electrotechnical Commission                            |  |

| IID        |                                                                       |  |

| ILP        | Independent and Identically Distributed instruction-level parallelism |  |

| IRQ        | Hardware Interrupt                                                    |  |

| ISA        | Instruction Set Architecture                                          |  |

|            |                                                                       |  |

| LHC        | Large Hadron Collider<br>Last-In First-Out                            |  |

| LIFO       |                                                                       |  |

| LL-RTE     | Low-level runtime environment                                         |  |

| LRU        | Least recently used                                                   |  |

| MBPTA      | Measurement-Based Probabilistic Timing Analysis                       |  |

| MCU        | Microcontroller Unit                                                  |  |

| MEET       | Maximum Extrinsic Execution Time                                      |  |

| MIET       | Maximum Intrinsic Execution Time                                      |  |

| MPPA       | Multi Purpose Processor Array                                         |  |

| NOC        | network-on-chip                                                       |  |

| NOP        | No Operation                                                          |  |

| NUCA       | non-uniform cache architecture                                        |  |

| OpenCL     | Open Computing Language                                               |  |

| OpenMP     | Open multi processing (programming model)                             |  |

| OpenMP DAG | OpenMP Direct Acyclic Graph                                           |  |

| OS         | Operating system                                                      |  |

| PCFG       | Parallel Control Flow Graph                                           |  |

| PCIe       | peripheral component interconnect express                             |  |

| PE         | processing element                                                    |  |

| PLRU       | Pseudo-LRU                                                            |  |

| POSIX      | Portable Operating System Interface for UNIX                          |  |

| PPC        | PowerPC                                                               |  |

| P-SOCRATES | Parallel Software Framework for Time-Critical                         |  |

|            | Many-core Systems                                                     |  |

|            |                                                                       |  |

| pWCET   | Probabilistic Worst-Case Execution Time |  |

|---------|-----------------------------------------|--|

| RCU     | Linux Read-Copy-Update technique        |  |

| RM      | Resource manager                        |  |

| RT      | Real time                               |  |

| RT task | Real-Time task                          |  |

| RTE     | Runtime environment                     |  |

| RTOS    | Real time operative system              |  |

| SDK     | Software Development Kit                |  |

| SMP     | Symmetric Multi Processor               |  |

| SMT     | simultaneous multi-threading            |  |

| SoC     | System-on-Chip                          |  |

| SOM     | system-on-module                        |  |

| SP      | Stack pointer                           |  |

| TBB     | Thread Building Blocks                  |  |

| TC      | Task context                            |  |

| TDG     | Task Dependency Graph                   |  |

| TDMA    | Time Division Multiple Access           |  |

| TLB     | translation lookaside buffer            |  |

| TLP     | Thread-Level Parallelism                |  |

| TSC     | Task Scheduling Constraint              |  |

| TSP     | Task Scheduling Point                   |  |

| VLIW    | Very Large Instruction Word             |  |

| VPU     | vector processing unit                  |  |

| WCET    | Worst Case Execution Time               |  |

| WFS     | Work First Scheduling                   |  |

|         |                                         |  |

# 1

### Introduction

#### Luís Miguel Pinho<sup>1</sup>, Eduardo Quiñones<sup>2</sup>, Marko Bertogna<sup>3</sup>, Andrea Marongiu<sup>4</sup>, Vincent Nélis<sup>1</sup>, Paolo Gai<sup>5</sup> and Juan Sancho<sup>6</sup>

<sup>1</sup>CISTER Research Centre, Polytechnic Institute of Porto, Portugal

<sup>2</sup>Barcelona Supercomputing Center (BSC), Spain

<sup>3</sup>University of Modena and Reggio Emilia, Italy

<sup>4</sup>Swiss Federal Institute of Technology in Zurich (ETHZ), Switzerland; and University of Bologna, Italy

<sup>5</sup>Evidence SRL, Italy

<sup>6</sup>ATOS, Spain

This chapter provides an overview of the book theme, motivating the need for high-performance and time-predictable embedded computing. It describes the challenges introduced by the need for time-predictability on the one hand, and high-performance on the other, discussing on a high level how these contradictory requirements can be simultaneously supported.

#### 1.1 Introduction

High-performance computing has been for a long time the realm of a specific community within academia and specialized industries; in particular those targeting demanding analytics and simulations applications that require processing massive amounts of data. In a similar way, embedded computing has also focused mainly on specific systems with specialized and fixed functionalities and for which timing requirements were considered as much more important than performance requirements. However, with the ever-increasing availability of more powerful processing platforms, alongside affordable and scalable software solutions, both high-performance and embedded computing are extending to other sectors and application domains.

#### 2 Introduction

The demand for increased computational performance is currently widespread and is even more challenging when large amounts of data need to be processed, from multiple data sources, with guaranteed processing response times. Although many systems focus on performance and handling large volumes of streaming data (with throughput and latency requirements), many application domains require real-time behavior [1–6] and challenge the computing capability of current technologies. Some examples are:

- In cyber-physical systems, ranging from automotive and aircrafts, to smart grids and traffic management, computing systems are embedded in a physical environment and their behavior obeys the technical rules dictated by this environment. Typically, they have to cope with the timing requirements imposed by the embedding domain. In the Large Hadron Collider (LHC) in CERN, beam collisions occur every 25 ns, which produce up to 40 million events per second. All these events are pipelined with the objective of distinguishing between interesting and non-interesting events to reduce the number of events to be processed to a few hundreds [7]. Similarly, bridges are monitored in real-time [8] with information collected from more than 10,000 sensors processed every 8 ms, managing responses to natural disasters, maintaining bridge structure, and estimating the extent of structural fatigue. Another interesting application is in intelligent transportation systems, where systems are developed to allow for fuel consumption reduction of railway systems, managing throttle positions, elaborating big amounts of data and sensor information, such as train horsepower, weight, prevailing wind, weather, traffic, etc. [9].

- In the banking/financial markets, computing systems process large amounts of real-time stock information in order to detect time-dependent patterns, automatically triggering operations in a very specific and tight timeframe when some pre-defined patterns occur. Automated algorithmic trading programs now buy and sell millions of dollars of shares time-sliced into orders separated by 1 ms. Reducing the latency by 1 ms can be worth up to \$100 million a year to a leading trading house. The aim is to cut microseconds off the latency in which these systems can reach to momentary variations in share prices [10].

- In industry, computing systems monitor business processes based on the capability to understand and process real-time sensor data from the factory-floor and throughout the whole value chain, with Radio Frequency Identification (RFID) components in order to optimize both the production and logistics processes [11].

The underlying commonality of the systems described above is that they are time-critical (whether business-critical or mission-critical, it is necessary to fulfill specific timing requirements) and with high-performance requirements. In other words, for such systems, the correctness of the result is dependent on both performance and timing requirements, and meeting those is critical to the functioning of the system. In this context, it is essential to guarantee the timing predictability of the performed computations, meaning that arguments and analyses are needed to be able to make arguments of correctness, e.g., performing the required computations within well-specified bounds.

#### 1.1.1 The Convergence of High-performance and Embedded Computing Domains

Until now, trends in high-performance and embedded computing domains have been running in opposite directions. On one side, high-performance computing (HPC) systems are traditionally designed to make the common case as fast as possible, without concerning themselves with the timing behavior (in terms of execution time) of the *not-so-often cases*. As a result, the techniques developed for HPC are based on complex hardware and software structures that make any reliable timing bound almost impossible to derive. On the other side, real-time embedded systems are typically designed to provide energy-efficient and predictable solutions, without heavy performance requirements. Instead of *fast* response times, they aim at having *deterministically bounded response times*, in order to guarantee that deadlines are met. For this reason, these systems are typically based on simple hardware architectures, using fixed-function hardware accelerators that are strongly coupled with the application domain.

In the last years, the above design choices are being questioned by the irruption of multi-core processors in both computing markets. The huge computational necessities to satisfy the performance requirements of HPC systems and the related exponential increments of power requirements (typically referred to as the power wall) exceeded the technological limits of classic single-core architectures. For these reasons, the main hardware manufacturers are offering an increasing number of computing platforms integrating multiple cores within a chip, contributing to an unprecedented phenomenon sometimes referred to as "the multi-core revolution." Multi-core processors provide better energy efficiency and performance-per-cost ratio, while improving application performance by exploiting thread-level parallelism (TLP). Applications are split into multiple tasks that run in parallel on different cores, extending to the *multi-core* system level an important challenge already faced by HPC designers at *multi-processor* system level: parallelization.

In the embedded systems domain, the necessity to develop more flexible and powerful systems (e.g., from fixed-function phones to smart phones and tablets) have pushed the embedded market in the same direction. That is, multi-cores are increasingly considered as the solution to cope with performance and cost requirements [12], as they allow scheduling multiple application services on the same processor, hence maximizing the hardware utilization while reducing cost, size, weight, and power requirements. However, real-time embedded applications with time-criticality requirements are still executed on simple architectures that are able to guarantee a predictable execution pattern while avoiding the appearance of timing anomalies [13]. This makes real-time embedded platforms still relying on either single-core or simple multi-core CPUs, integrated with fix-function hardware accelerators into the same chip: the so-called System-on-Chip (SoC).

The needs for energy-efficiency (in the HPC domain) and for flexibility (in the embedded computing domain), coming along with Moore's law, greedy demand for performance, and the advancements in the semiconductor technology, have progressively paved the way for the introduction of "*manycore*" systems, i.e., multi-core chips containing a high number of cores (tens to hundreds) in both domains. Examples of many-core architectures are described in the next chapter.

The introduction of many-core systems has set up an interesting trend wherein both the HPC and the real-time embedded domains converge towards similar objectives and requirements. Many-core computing fabrics are being integrated with general-purpose multi-core processors to provide a heterogeneous architectural harness that eases the integration of previously hardwired accelerators into more flexible software solutions. In recent years, the HPC computing domain has seen the emergence of accelerated heterogeneous architectures, most notably multi-core processors integrated with General Purpose Graphic Processing Units (GPGPU), because GPGPUs are a flexible and programmable accelerator for data parallel computations. Similarly, in the real-time embedded domain, the Kalray Multi-Purpose Processor Array (MPPA), which includes clusters of guad-core CPUs coupled with many-core computing clusters. In both cases, the many-core fabric acts as a programmable accelerator. More recently, the Field-Programmable Gate Array (FPGA) has been used as a flexible accelerator fabric, complementing the above.

In this current trend, challenges that were previously specific to each computing domain, start to be common to both domains (including energy-efficiency, parallelization, compilation, and software programming) and are magnified by the ubiquity of many-cores and heterogeneity across the whole computing spectrum. In that context, cross-fertilization of expertise from both computing domains is *mandatory*.

#### 1.1.2 Parallelization Challenge

Needless to say that many industries with both high-performance and realtime requirements are eager to benefit from the immense computing capabilities offered by these new many-core embedded designs. However, these industries are also highly unprepared for shifting their earlier system designs to cope with this new technology, mainly because such a shift requires adapting the applications, operating systems, and programming models in order to exploit the capabilities of many-core embedded computing systems. On one hand, neither have many-core embedded processors, such as the MPPA, been designed to be used in the HPC domain, nor have HPC techniques been designed to apply embedded technology. On the other hand, real-time methods to determine the timing behavior of an embedded system are not prepared to be directly applied to the HPC domain and these platforms, leading to a number of significant challenges.

On one side, different parallel programming models and multiprocessor operating systems have been proposed and are increasingly being adopted in today's HPC computing systems. In recent years, the emergence of accelerated heterogeneous architectures such as GPGPUs have introduced parallel programming models such as OpenCL [14], the currently dominant open standard for parallel programming of heterogeneous systems, or CUDA [15], the dominant proprietary framework of NVIDIA. Unfortunately, they are not easily applicable to systems with real-time requirements, since, by nature, many-core architectures are designed to integrate as much functionality as possible into a single chip. Hence, they inherently share out as many resources as possible amongst the cores, which heavily impacts the ability to providing timing guarantees.

On the other side, the embedded computing domain world has always seen plenty of application-specific accelerators with custom architectures, manually tuning applications to achieve predictable performance. Such types of solutions have limited flexibility, complicating the development of embedded systems. Commercial off-the-shelf (COTS) components based on

#### 6 Introduction

many-core architectures are likely to dominate the embedded computing market in the near future, even if complemented with custom function-specific accelerators. As a result, migrating real-time applications to many-core execution models with predictable performance requires a complete redesign of current software architectures. Real-time embedded application developers will therefore either need to adapt their programming practices and operating systems to future many-core components, or they will need to content themselves with stagnating execution speeds and reduced functionalities, relegated to niche markets using obsolete hardware components.

This new trend in the manufacturing technology and the industrial need for enhanced computing capabilities and flexible heterogeneous programming solutions of accelerators for predictable parallel computations bring to the forefront important challenges for which solutions are urgently needed. This book outlines how to bring together next-generation many-core accelerators from the embedded computing domain with the programmability of many-core accelerators from the HPC computing domain, supporting this with real-time methodologies to provide time predictability and highperformance.

#### 1.2 The P-SOCRATES Project

The work described in this book was performed in the scope of the European project P-SOCRATES (Parallel Software Framework for Time-Critical Many-core Systems)<sup>1</sup>, funded under the FP7 framework program of the European Commission. The project, finished in December 2016, aimed to allow applications with high-performance and real-time requirements to fully exploit the huge performance opportunities brought by the most advanced COTS many-core embedded processors, whilst ensuring predictable performance of applications (Figure 1.1). The project consortium included Instituto Superior de Engenharia do Porto (coordinator), Portugal, the Barcelona Supercomputing Centre, Spain, the University of Modena and Reggio Emilia, Italy, the Swiss Federal Institute of Technology Zurich, Switzerland, Evidence SRL, Italy, Active Technologies SRL, Italy and ATOS, Spain.

P-SOCRATES focused on combining techniques from different domains: the newest high-performance software techniques for exploiting task parallelism, the most advanced mapping and scheduling methodologies and timing

<sup>&</sup>lt;sup>1</sup>htttp://www.p-socrates.eu

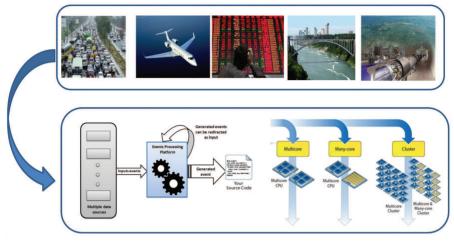

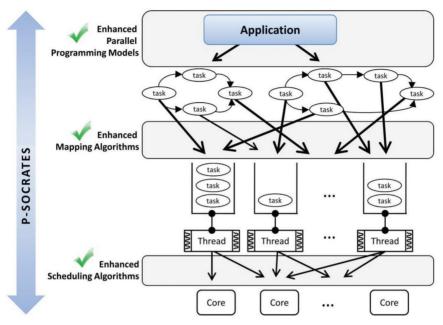

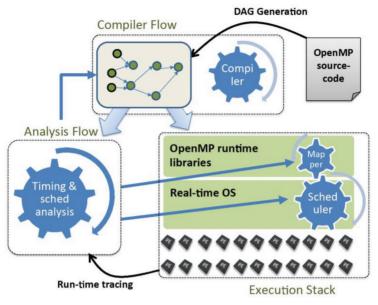

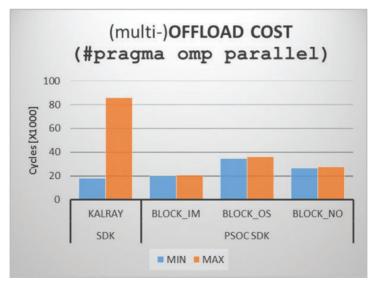

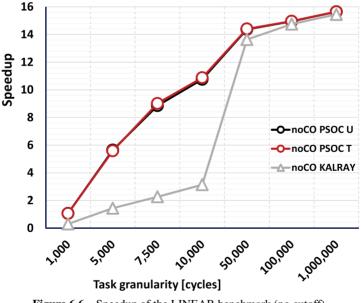

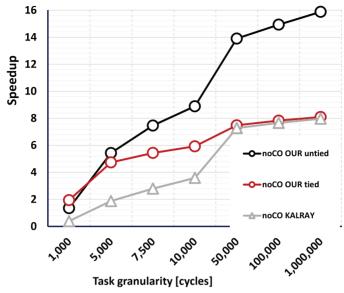

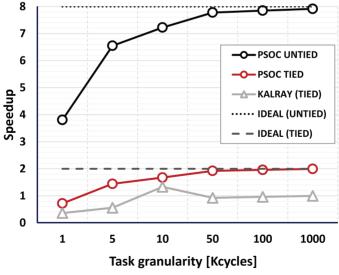

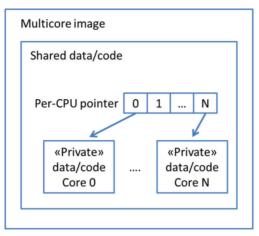

Figure 1.1 P-SOCRATES Global perspective.