# COMPILATION TECHNIQUES AND LANGUAGE SUPPORT TO FACILITATE DEPENDENCE-DRIVEN COMPUTATION

#### BY

#### ALBERT SIDELNIK

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2013

#### Urbana, Illinois

#### Doctoral Committee:

Professor David A. Padua, Chair, Co-Director of Research

Research Assistant Professor María J. Garzarán, Co-Director of Research

Doctor Bradford L. Chamberlain, Cray Inc.

Professor Wen-mei W. Hwu

Professor Sanjay J. Patel

Professor Keshav Pingali, University of Texas, Austin

### Abstract

As the demand increases for high performance and power efficiency in modern computer runtime systems and architectures, programmers are left with the daunting challenge of fully exploiting these systems for efficiency, high-level expressibility, and portability across different computing architectures. Emerging programming models such as the task-based runtime StarPU and many-core architectures such as GPUs force programmers into choosing either low-level programming languages or putting complete faith in the compiler. As has been previously studied in extensive detail, both development approaches have their own respective trade-offs.

The goal of this thesis is to help make parallel programming easier. It addresses these challenges by providing new compilation techniques for high-level programming languages that conform to commonly-accepted paradigms in order to leverage these emerging runtime systems and architectures. In particular, this dissertation makes several contributions to these challenges by leveraging the high-level programming language Chapel in order to efficiently map computation and data onto both the task-based runtime system StarPU and onto GPU-based accelerators. Different loop-based parallel programs and experiments are evaluated in order to measure the effectiveness of the proposed compiler algorithms and their optimizations, while also providing programmability metrics when leveraging high-level languages. In order to exploit additional performance when mapping onto shared memory systems, this thesis proposes a set of compiler and runtime-based heuristics that determine the profitable processor tile shapes and sizes when mapping multiply-nested parallel loops.

Finally, a new benchmark-suite named P-Ray is presented. This is used to provide machine characteristics in a portable manner that can be used by either a compiler, an auto-tuning framework, or the programmer when optimizing their applications.

For the two best companions, Yuki and Bandita.

## Acknowledgements

For the most part, graduate school is a roller coaster of emotions. There are moments where nothing works as you go down the rabbit hole of pursuing a research topic, and then there are other moments where everything just "clicks". The work in this thesis is a culmination of lots of sweat, plenty of expletives thrown at compilers and operating systems, unwanted gray hairs, and many late nights spent in the lab and at various coffee shops. At the end of the day, I am glad to have gone through this journey.

I would like to first start by thanking my advisors David Padua and María Garzarán. If it were not for their support, guidance, and patience, this work would not exist.

I would also like to acknowledge and thank my thesis committee members Brad Chamberlain, Wen-mei Hwu, Sanjay Patel, and Keshav Pingali for their valuable comments. In particular, I would like to give a special thanks to Brad Chamberlain. His feedback during the different stages of my graduate school experience has been extremely helpful.

I am fortunate to have the experience of working and collaborating with some of the sharpest researchers in the field, including Gheorghe Almasi, Bryan Catanzaro, Michael Garland, and Jose Moreira. I have learned an immense amount from them.

It is also important that I give a special thanks to Mary Beth Kelly, Megan Osfar, and Sherry Unkraut. If it were not for them, I would be even more confused than I typically am.

Lastly, I want to thank my friends and family, especially my parents for supporting me in all of my various adventures.

# Table of Contents

| List of | Figur  | es                                                    |

|---------|--------|-------------------------------------------------------|

| List of | Table  | s xiii                                                |

| List of | Algor  | $ithms \dots \dots xiv$                               |

| Chapte  | er 1   | Introduction                                          |

| 1.1     | Overv  | iew                                                   |

| 1.2     | Contr  | ibutions                                              |

| 1.3     | Thesis | S Organization                                        |

| Chapte  | er 2   | Background                                            |

| 2.1     | Gener  | al Compiler Preliminaries                             |

|         | 2.1.1  | Control Flow Analysis                                 |

|         | 2.1.2  | Dependences: Data and Control                         |

|         | 2.1.3  | Data-Parallelism                                      |

| 2.2     | Depen  | dence-Driven Execution Models                         |

|         | 2.2.1  | StarPU Runtime System                                 |

| 2.3     | Chape  | el Language Overview                                  |

|         | 2.3.1  | Domains and Distributed Arrays                        |

|         | 2.3.2  | Data Parallelism in Chapel                            |

|         | 2.3.3  | Task Parallelism in Chapel                            |

|         | 2.3.4  | Distributions (Built-in and User-defined)             |

| Chapte  | er 3   | Compilation for Dependence-Driven Models 24           |

| 3.1     | Introd | uction                                                |

| 3.2     | Motiv  | ation                                                 |

| 3.3     | Gener  | ating Task-Dependence Graphs From Data-Parallel Loops |

|         | 3.3.1  | Prerequisites                                         |

|         | 3.3.2  | Loop Partitioning                                     |

|         | 3.3.3  | Agglomerated Flow Graph                               |

|         | 3.3.4  | Interval Analysis                                     |

|         | 3.3.5  | Interval Containment Tree                             |

|         | 3.3.6  | Data Placement and Communication                      |

|                  | 3.3.7 Co   | ode Generation                                                                                                          |

|------------------|------------|-------------------------------------------------------------------------------------------------------------------------|

| 3.4              | Evaluatio  | on                                                                                                                      |

|                  | 3.4.1 En   | nvironmental Setup                                                                                                      |

|                  | 3.4.2 Ex   | xperimental Methodology                                                                                                 |

|                  |            | xperiments                                                                                                              |

|                  |            | esults                                                                                                                  |

| 3.5              |            | ng Non-Loop Based Parallel Constructs                                                                                   |

| 3.6              |            | Support for Arbitrary Execution Order                                                                                   |

|                  |            | anguage Extensions                                                                                                      |

|                  |            | xamples                                                                                                                 |

| 3.7              | Current I  | Limitations                                                                                                             |

| 3.8              |            | Vork                                                                                                                    |

|                  |            | acro-Dataflow Compilation                                                                                               |

|                  |            | anguage Extensions to Express Dependences                                                                               |

| 3.9              |            | ns                                                                                                                      |

|                  |            |                                                                                                                         |

| Chapte           | er 4 Lo    | oop Optimizations for Dependence-Driven Models 97                                                                       |

| 4.1              | Introduct  | ion                                                                                                                     |

| 4.2              | Multi-Dir  | nensional Blocked-Coalesced Form                                                                                        |

| 4.3              | Heuristics | s for Tile Sizes                                                                                                        |

|                  | 4.3.1 Of   | ff-Line Timing Benchmarks                                                                                               |

|                  | 4.3.2 Co   | ost Model                                                                                                               |

|                  |            | emory Footprint                                                                                                         |

|                  | 4.3.4 He   | euristic                                                                                                                |

| 4.4              | Evaluatio  | n                                                                                                                       |

|                  | 4.4.1 Er   | nvironmental Setup                                                                                                      |

|                  | 4.4.2 Ex   | xperiments                                                                                                              |

|                  | 4.4.3 Ex   | xperimental Methodology                                                                                                 |

|                  | 4.4.4 Re   | esults                                                                                                                  |

| 4.5              | Limitatio  | ns                                                                                                                      |

| 4.6              | Related V  | Vork                                                                                                                    |

|                  | 4.6.1 Lo   | oop Coalescing                                                                                                          |

|                  |            | ile Size and Shape Selection                                                                                            |

| 4.7              | Discussion | n                                                                                                                       |

|                  |            |                                                                                                                         |

| $\mathbf{Chapt}$ | er 5 C     | ompilation for Heterogeneous Architectures                                                                              |

| 5.1              |            | ion $\dots \dots \dots$ |

| 5.2              | Motivatio  | on                                                                                                                      |

| 5.3              | Generatin  | ng Code for GPU Accelerators                                                                                            |

|                  | 5.3.1 G    | PU User-Defined Distribution                                                                                            |

|                  | 5.3.2 G    | PU Domains and Distributed Arrays                                                                                       |

|                  |            | ata Movement                                                                                                            |

|                  | 5.3.4 Pa   | arallel Execution on the GPU 145                                                                                        |

| Bi | bliog | raphy          |                                                                                                                            |

|----|-------|----------------|----------------------------------------------------------------------------------------------------------------------------|

| Cł | napte | er 8           | Conclusions                                                                                                                |

| Cł | napte | er 7           | Future Work                                                                                                                |

|    | 6.7   | Conclu         | sion                                                                                                                       |

|    | 6.6   |                | d Work                                                                                                                     |

|    | C     | 6.5.2          | Experimental Results                                                                                                       |

|    |       | 6.5.1          | Experimental Environment                                                                                                   |

|    | 6.5   |                | tion                                                                                                                       |

|    | c r   | 6.4.2          | Implementation Details                                                                                                     |

|    |       | 6.4.1          | Requirements                                                                                                               |

|    | 6.4   |                | nentation                                                                                                                  |

|    | C 1   | 6.3.4          | Effective Bandwidth                                                                                                        |

|    |       | 6.3.3          | Processor Mapping                                                                                                          |

|    |       | 6.3.2          | Cache Mapping                                                                                                              |

|    |       | 6.3.1          | Cache Coherence Protocol Block Size                                                                                        |

|    | 6.3   | _              | ed Characteristics                                                                                                         |

|    | 6.2   |                | tion                                                                                                                       |

|    | 6.1   |                | $uction \dots \dots$ |

| Cł | napte |                | Multi-core Micro-benchmark Suite                                                                                           |

| ~· |       | 0              |                                                                                                                            |

|    | 5.10  |                | sion                                                                                                                       |

|    | 5.9   | Relate         | d Work                                                                                                                     |

|    | 5.8   | Limita         | tions                                                                                                                      |

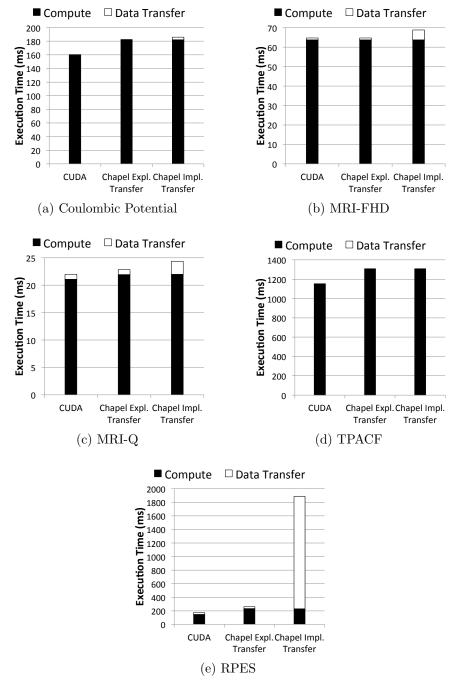

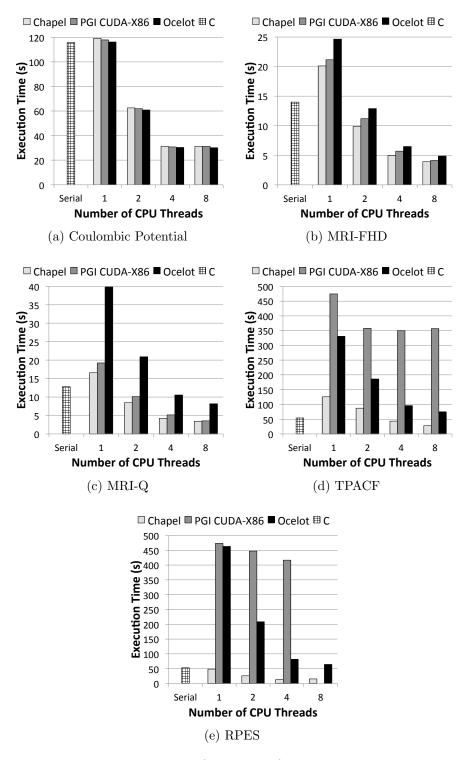

|    |       | 5.7.3          | Experimental Results                                                                                                       |

|    |       | 5.7.2          | Environmental Setup                                                                                                        |

|    |       | 5.7.1          | Parboil Benchmarks                                                                                                         |

|    | 5.7   | Evalua         | tion $\dots \dots \dots$   |

|    |       | 5.6.2          | Coulombic Potential                                                                                                        |

|    |       | 5.6.1          | 2D Jacobi                                                                                                                  |

|    | 5.6   |                | ole Codes                                                                                                                  |

|    |       | 5.5.3          | Kernel Argument Spilling to Constant Memory                                                                                |

|    |       | 5.5.2          | Scalar Replacement of Aggregates and Dead Argument Elimination . 154                                                       |

|    | J.J   | 5.5.1          | Implicit Data Transfers Between Host and Device                                                                            |

|    | 5.5   |                | ler Transformations and Optimizations                                                                                      |

|    | 5.4   |                | ating Code for Multi-core                                                                                                  |

|    |       | 5.3.8          | Synchronization                                                                                                            |

|    |       | 5.3.6<br>5.3.7 | Targeting Specialized GPU Memory Spaces                                                                                    |

|    |       |                |                                                                                                                            |

|    |       | 5.3.5          | Code Generation for the GPU                                                                                                |

| Annondiv A | Sparse Matrices Representation | • | ว1ว        |

|------------|--------------------------------|---|------------|

| Appendix A | Sparse Mairices Representation |   | <b>414</b> |

|            |                                |   |            |

# List of Figures

| 2.1  | Interval Analysis Applied to a CFG                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | Interval Analysis [1, 2]                                                                                                                           |

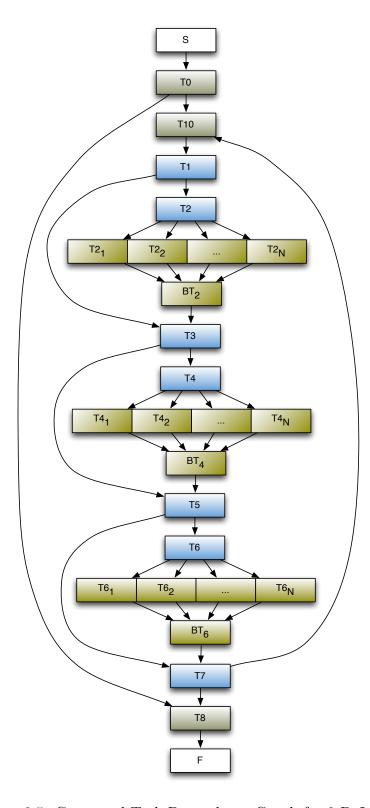

| 2.3  | StarPU Task-Dependence Graph                                                                                                                       |

| 2.4  | Example Demonstrating Chapel's Support for Domains                                                                                                 |

| 3.1  | 2-D Jacobi Method Implemented in Chapel                                                                                                            |

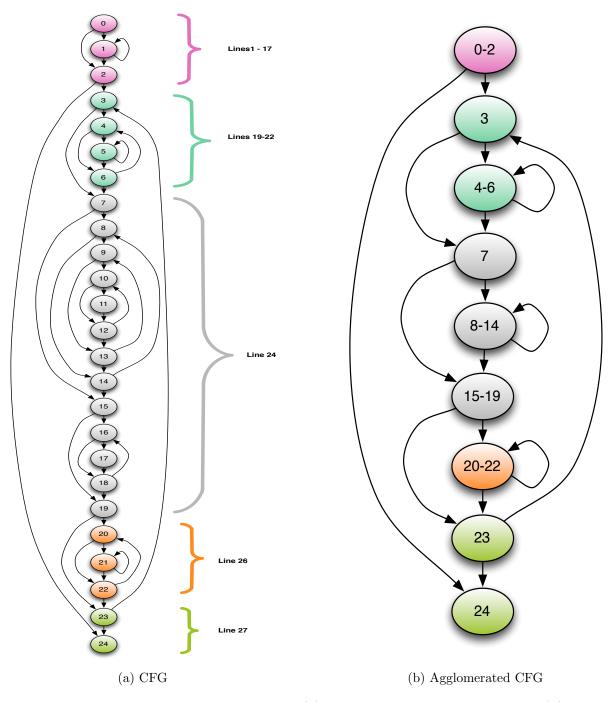

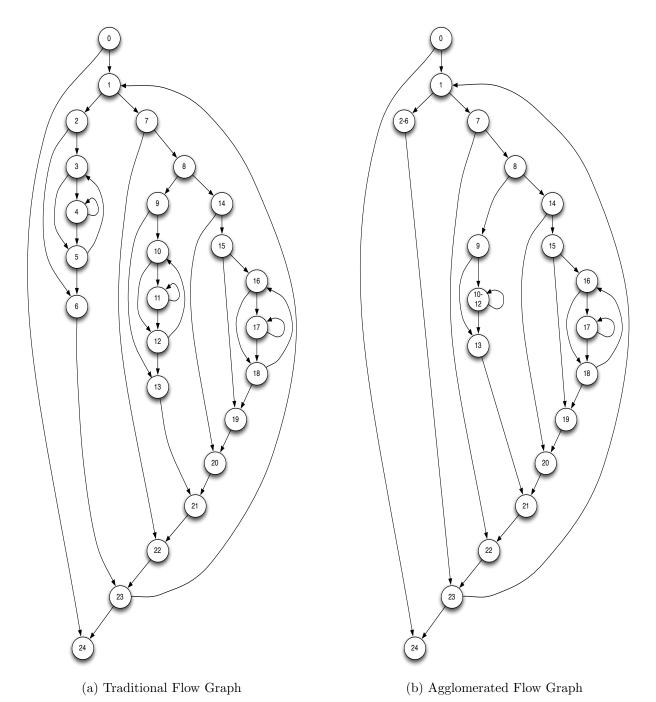

| 3.2  | Traditional Flow Graph (a) and Agglomerated Flow Graph (b)                                                                                         |

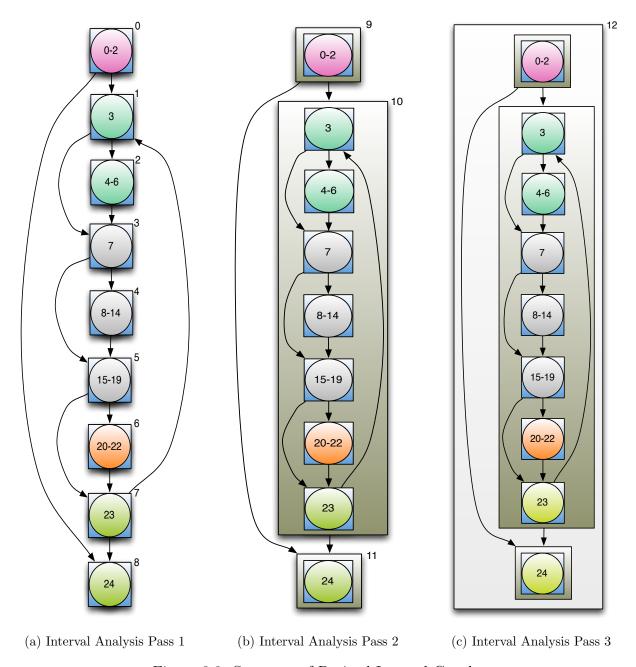

| 3.3  | Sequence of Derived Interval Graphs                                                                                                                |

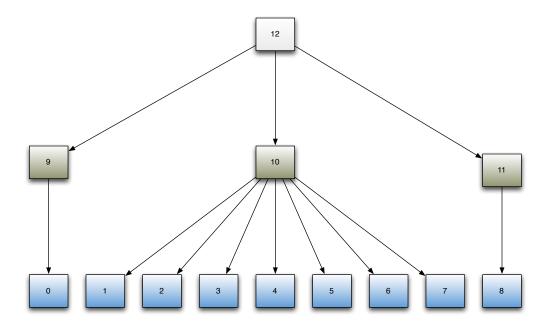

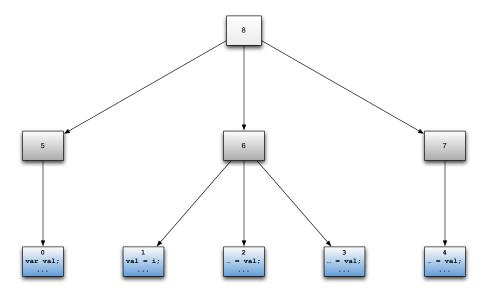

| 3.4  | Interval Containment Tree                                                                                                                          |

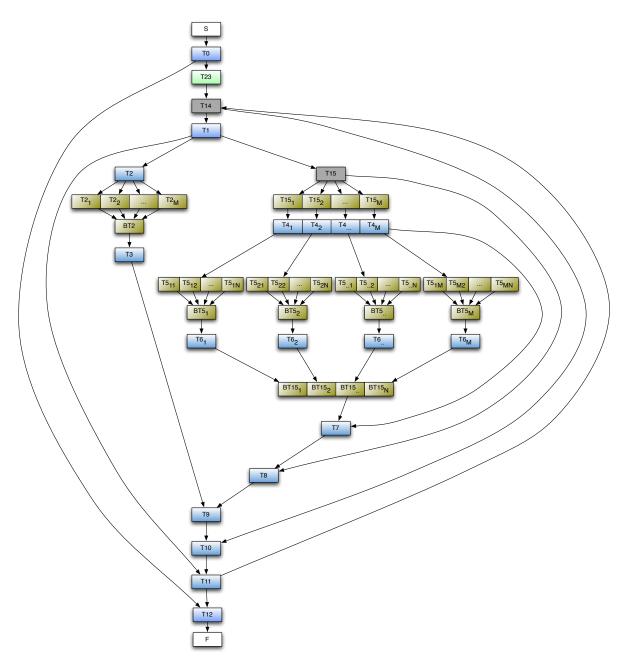

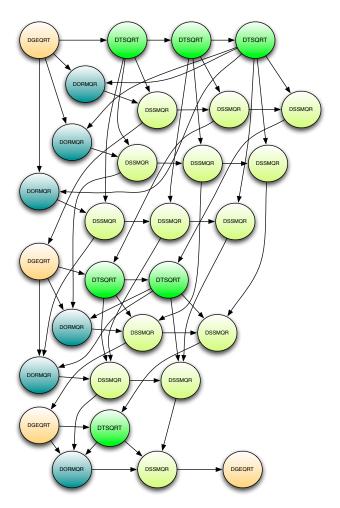

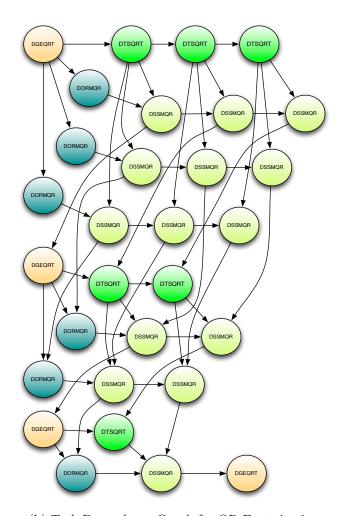

| 3.5  | Generated Task-Dependence Graph for 2-D Jacobi                                                                                                     |

| 3.6  | Low-Level Generated Code for 2-D Jacobi                                                                                                            |

| 3.7  | Synthetic Parallel Loop Example                                                                                                                    |

| 3.8  | Traditional Flow Graph and Agglomerated Flow Graph                                                                                                 |

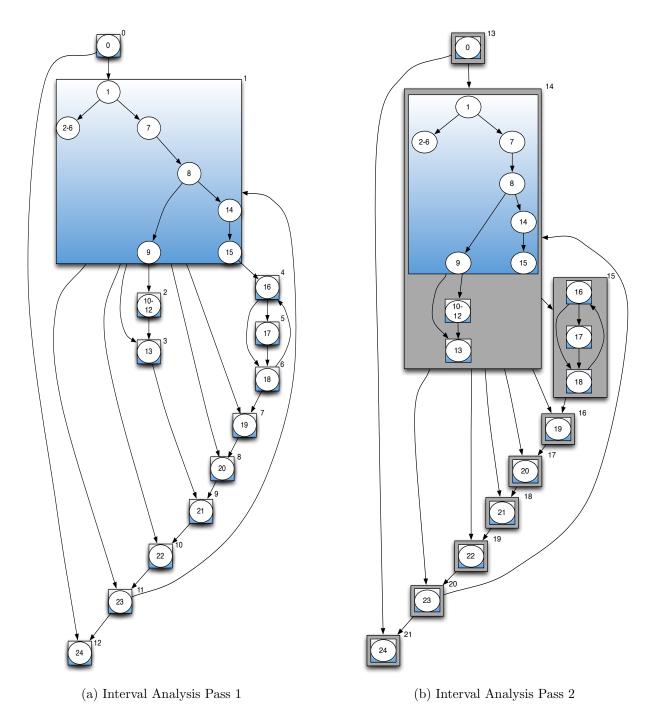

| 3.9  | Generated Interval Analysis Graphs: Passes 1 and 2                                                                                                 |

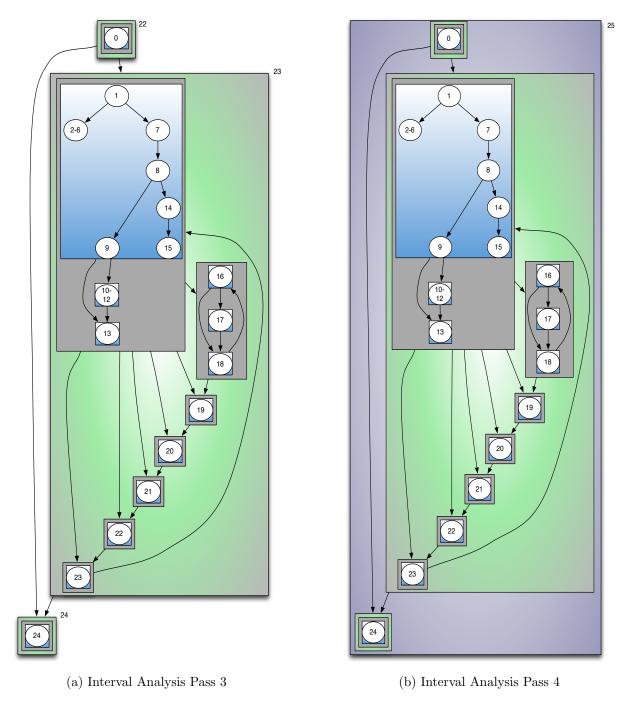

| 3.10 | Generated Interval Analysis Graphs: Passes 3 and 4                                                                                                 |

| 3.11 | Interval Containment Tree                                                                                                                          |

| 3.12 | Optimized Interval Containment Tree                                                                                                                |

| 3.13 | Data Placement Example                                                                                                                             |

| 3.14 | Traditional Flow Graph and Agglomerated Flow Graph                                                                                                 |

| 3.15 | Interval Containment Tree                                                                                                                          |

| 3.16 | Task Graph for a Program Containing Multiply-Nested Parallel Loops (from                                                                           |

|      | Figure 3.7)                                                                                                                                        |

| 3.17 | Speedup of OpenMP (over Native Chapel) Using 32 Threads                                                                                            |

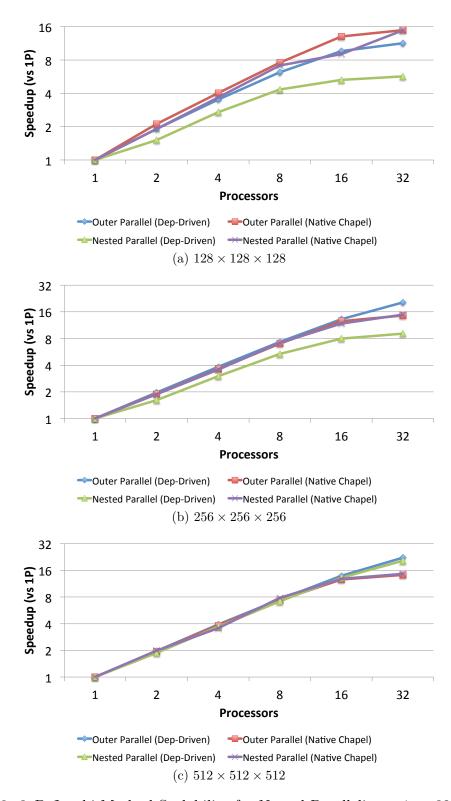

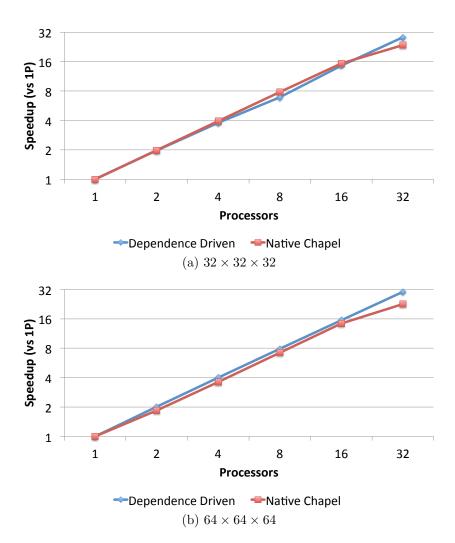

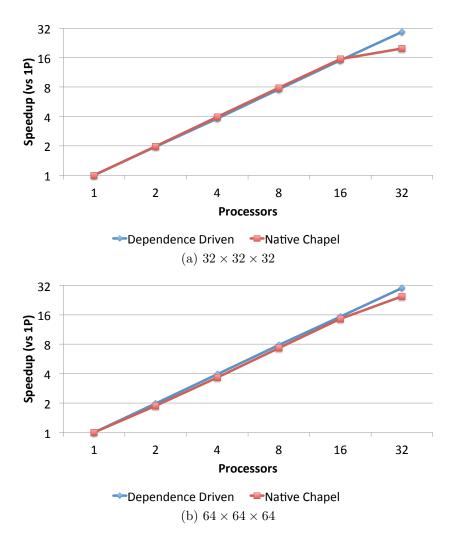

| 3.18 | 3–D Jacobi Method Scalability for Nested-Parallelism : 1 $\rightarrow$ 32 Processors . 6                                                           |

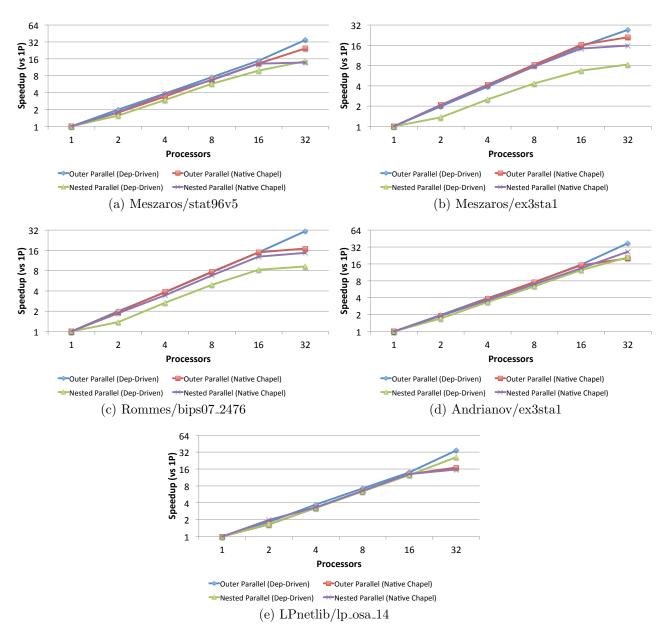

| 3.19 | Sparse-Matrix Vector Multiplication Scalability for Nested-Parallelism with                                                                        |

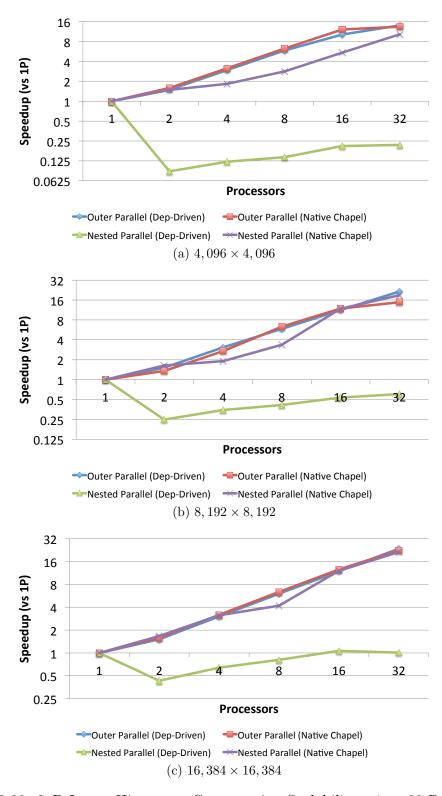

|      | Multiple Vectors $(v = 16, 384) \dots \dots$ |

| 3.20 | Coulombic Potential (CP) Scalability for Nested- and Outer-Parallelism : 1 $\rightarrow$                                                           |

|      | 32 Processors                                                                                                                                      |

| 3.21 | MRI-FHd Scalability With Single-Level Parallelism : $1 \rightarrow 32$ Processors 7                                                                |

| 3.22 | MRI-Q Scalability With Single-Level Parallelism : $1 \rightarrow 32$ Processors 7                                                                  |

| 3.23 | 2–D Image Histogram Computation Scalability : $1 \rightarrow 32$ Processors 7                                                                      |

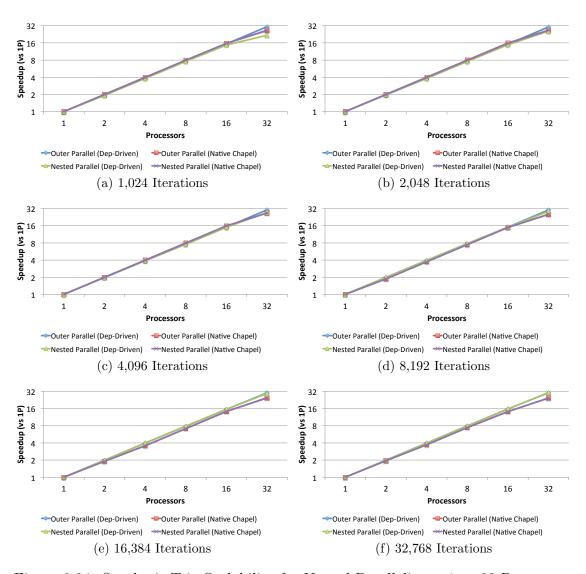

| 3.24 | Synthetic. Trig Scalability for Nested-Parallelism : $1 \rightarrow 32$ Processors                                                                 |

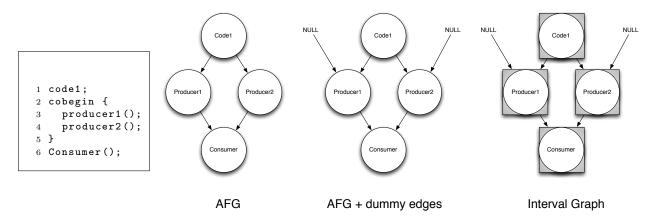

| 3.25 | Translating a Task-Parallel cobegin into an Interval Graph                                                                                         |

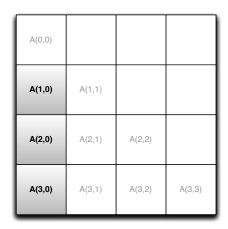

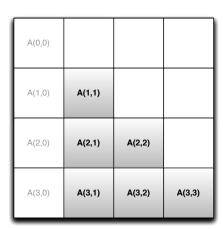

| 3.26 | Tiled Cholesky Factorization                                                                                                                       |

| 3.27 | Sequential Tiled Cholesky Factorization                                   | 80  |

|------|---------------------------------------------------------------------------|-----|

| 3.28 | Implicit versus Explicit Parallel Model                                   | 82  |

|      | Loop Nest: Before and After Language Extension                            | 83  |

|      | Using a when Statement Across a Block                                     | 84  |

|      | Using a when Statement Across a domain                                    | 85  |

| 3.32 | Asynchronous Cholesky Factorization                                       | 87  |

|      | Tiled QR Factorization                                                    | 88  |

|      | Asynchronous QR Factorization                                             | 89  |

| 3.35 | Optimized QR Factorization With Fewer Dependences                         | 90  |

| 4.1  | Nested Parallel Loops With Static Loop Bounds                             | 98  |

| 4.2  | Loop Coalescing Example                                                   | 100 |

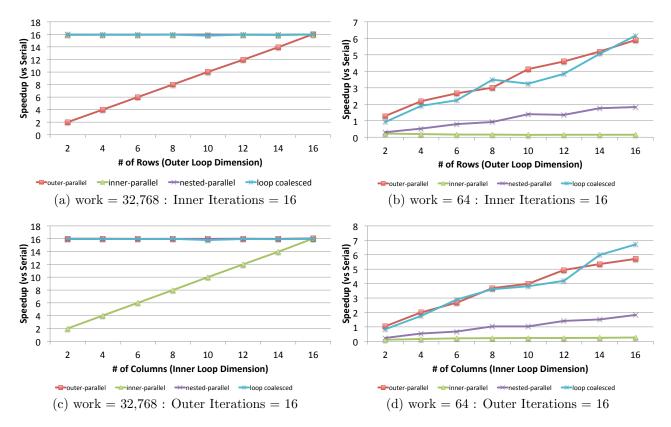

| 4.3  | Single Level Parallelism Compared with Multi-Dimensional Parallelism      | 101 |

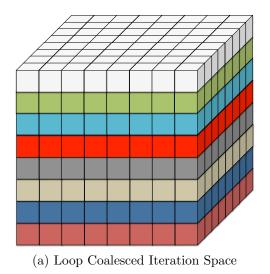

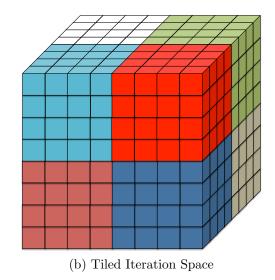

| 4.4  | Multiply-Nested Parallel Loop                                             | 104 |

| 4.5  | Loop Coalescing vs Tiled Comparison of Iteration Spaces Partitioned Among |     |

|      | 8 Threads                                                                 | 105 |

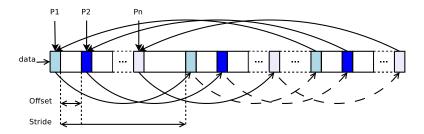

| 4.6  | Loop Body Timing Micro-benchmark                                          | 108 |

| 4.7  | Task Creation Micro-benchmark                                             | 109 |

| 4.8  | Barrier Overhead Micro-benchmark                                          | 109 |

| 4.9  | Data Copying Overhead Micro-Benchmark                                     | 110 |

|      | Heuristic to Determine Blocking Dimensions                                | 118 |

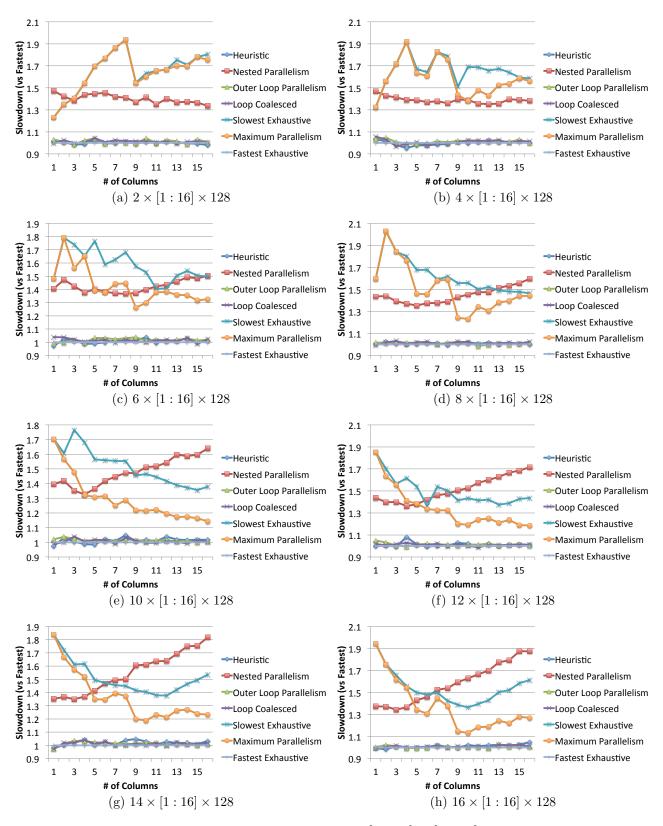

|      | 3–D Jacobi Iteration : $[1:16] \times [1:16] \times 128$                  | 126 |

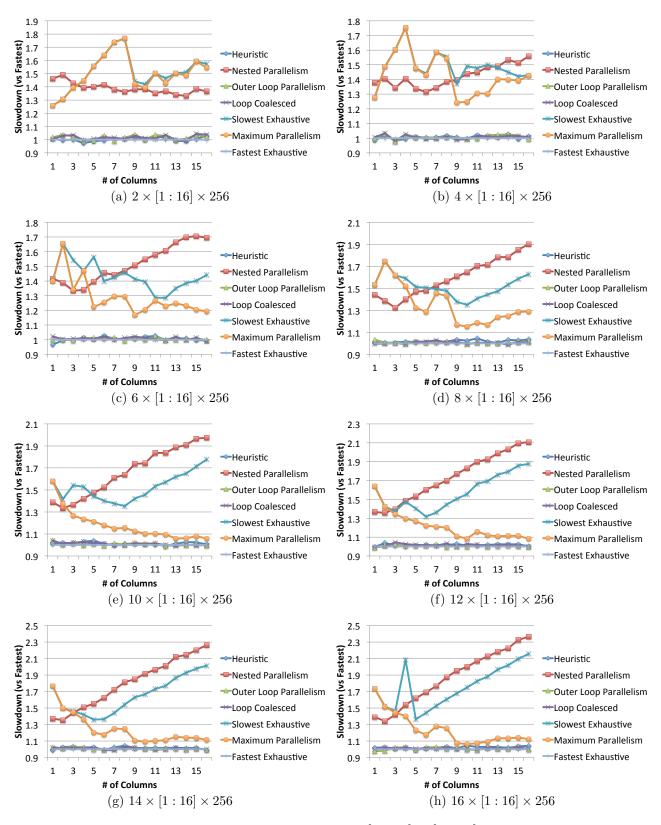

|      | 3–D Jacobi Iteration : $[1:16] \times [1:16] \times 256$                  | 127 |

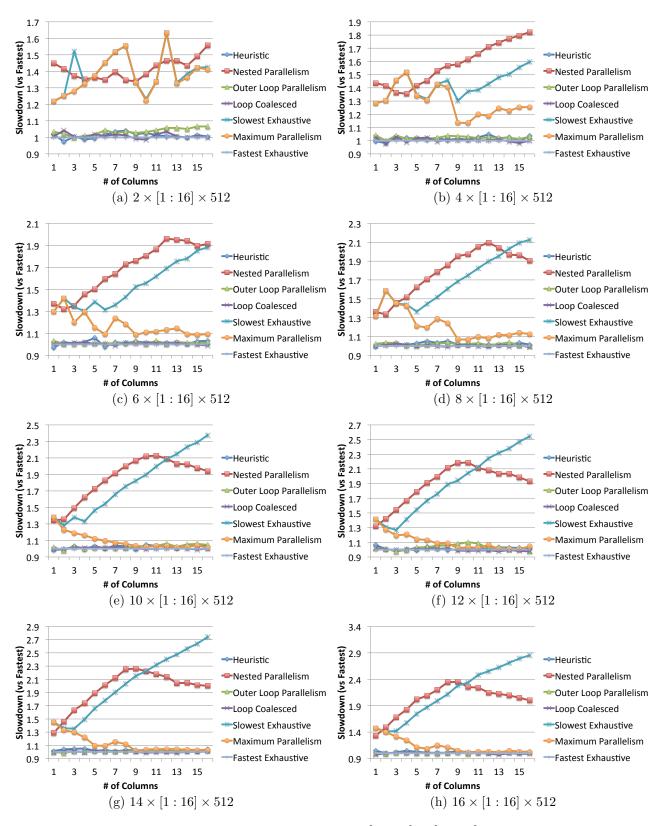

|      | 3–D Jacobi Iteration : $[1:16] \times [1:16] \times 512$                  | 128 |

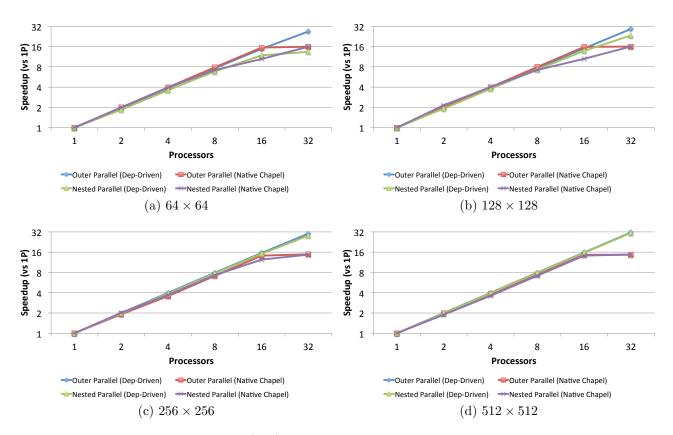

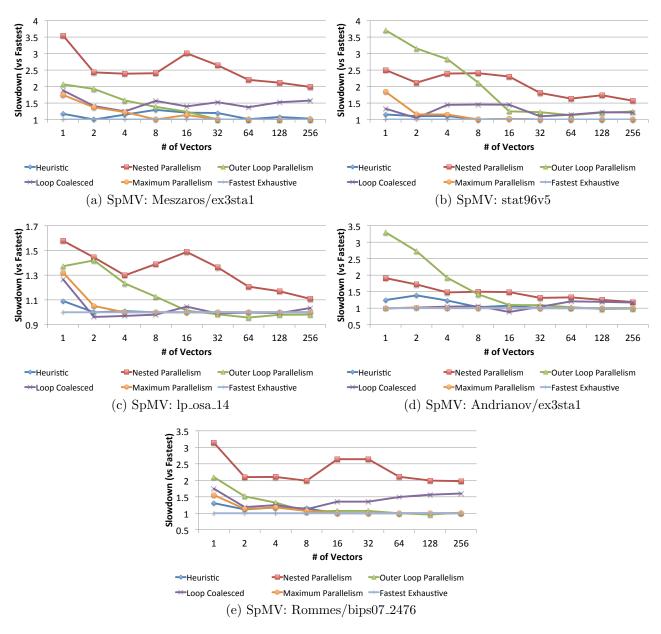

|      | Sparse Matrix-Vector Multiplication With Multiple Vectors                 | 130 |

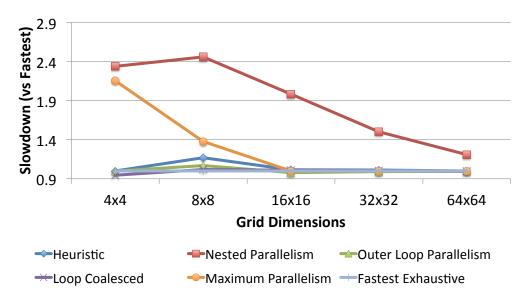

|      | Coulombic Potential                                                       | 132 |

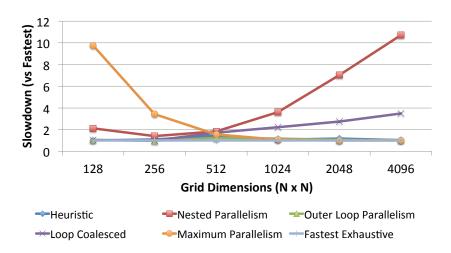

|      | 2–D Image Histogram                                                       | 132 |

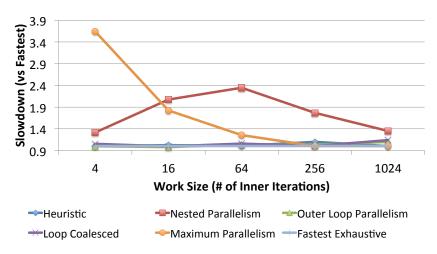

| 4.17 | Synth.Trig                                                                | 133 |

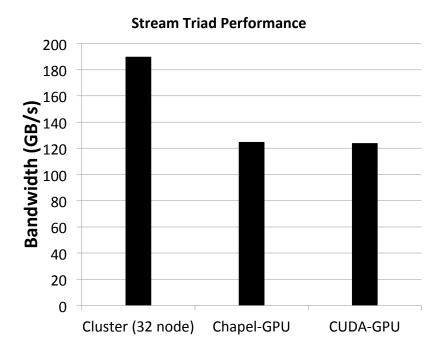

| 5.1  | Comparison of STREAM Triad Implementations                                | 140 |

| 5.2  | Results for the STREAM Triad Benchmark Comparing a 32-node Cray XT4       |     |

|      | 2.1 GHz Quad-Core AMD Opteron and NVIDIA GTX280 GPU                       | 142 |

| 5.3  | Implicit Data Movement Example                                            | 144 |

| 5.4  | Explicit Data Movement Example                                            | 145 |

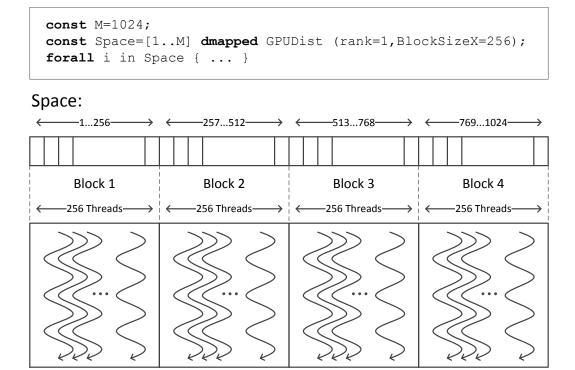

| 5.5  | Mapping a Chapel 1D Domain Onto CUDA's Thread Blocks                      | 146 |

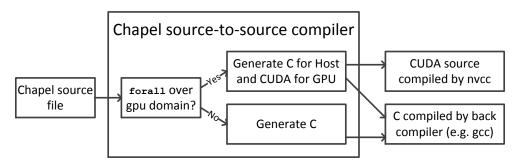

| 5.6  | Overview of Chapel Compilation Process                                    | 147 |

| 5.7  | Constant Cache Example                                                    | 149 |

| 5.8  | Translation of a GPU forall into Multi-core forall                        | 152 |

| 5.9  | Chapel Implementation of Jacobi 2D                                        | 157 |

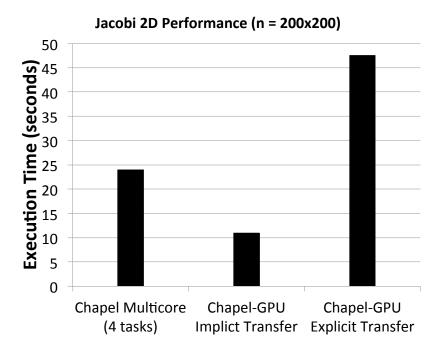

| 5.10 | Performance of Jacobi 2D                                                  | 158 |

| 5.11 | 1                                                                         | 159 |

| 5.12 | GPU Performance of the Parboil Benchmarks Comparing Chapel to CUDA .      | 162 |

| 5.13 | Multi-core Performance of the Parboil Benchmarks                          | 164 |

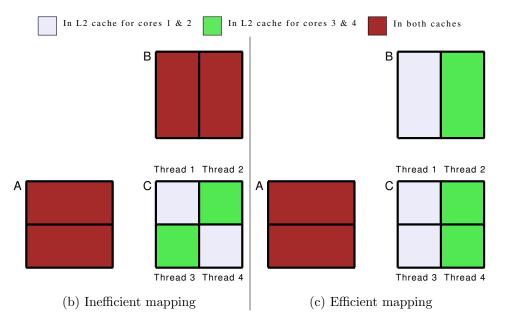

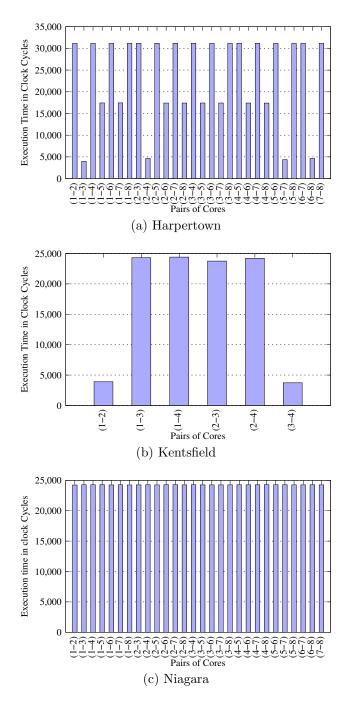

| 6.1 | Data Locality Depending on Thread to Core Affinity |

|-----|----------------------------------------------------|

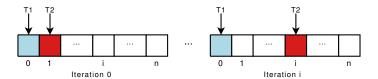

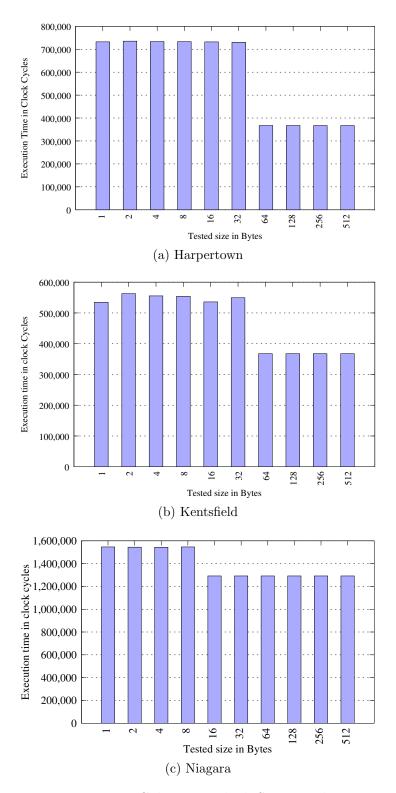

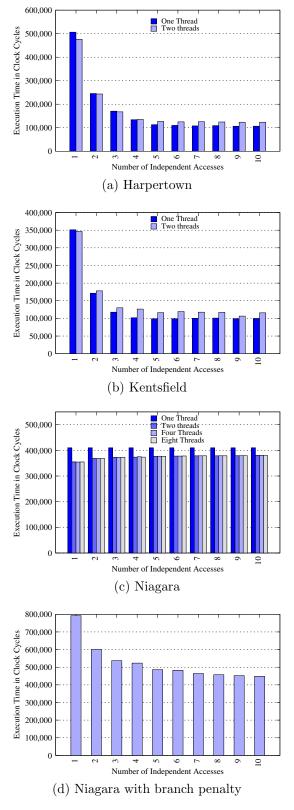

| 6.2 | Coherence Block Size Benchmark                     |

| 6.3 | Pointer Chaining: General Case                     |

| 6.4 | Coherence Block Size Results                       |

| 6.5 | Coherence Block Size and Communication Latency     |

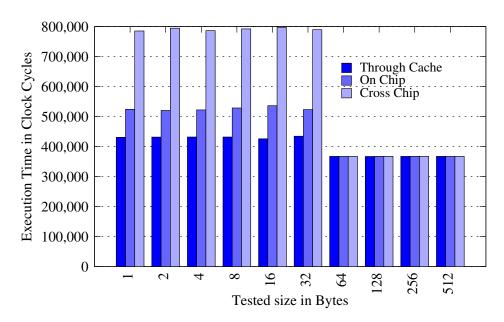

| 6.6 | Cache Mapping                                      |

| 6.7 | Processor Mapping                                  |

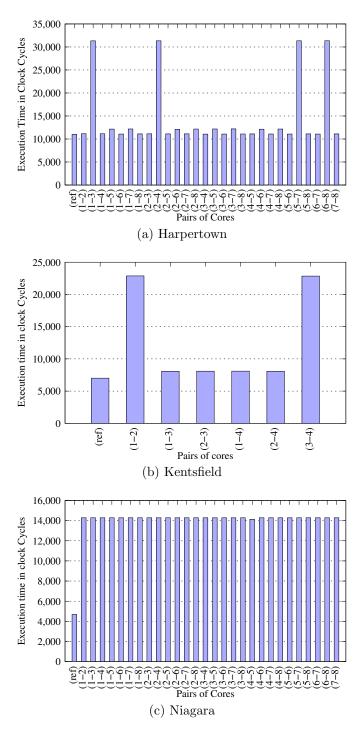

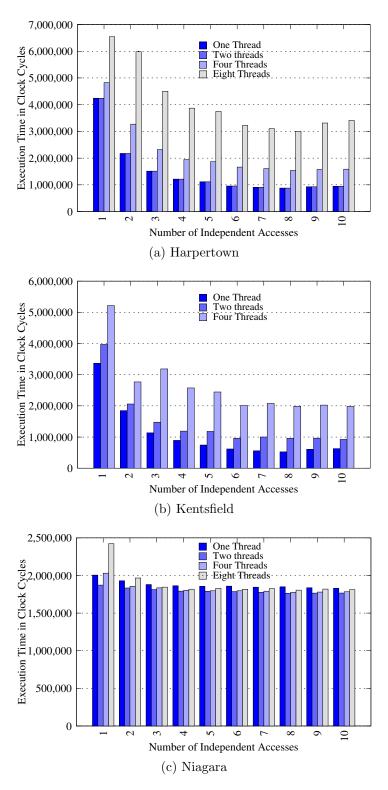

| 6.8 | Effective Bandwidth to L2 Results                  |

| 6.9 | Effective Bandwidth to Memory Results              |

| A.1 | Matrix: Meszaros/ex3sta1                           |

| A.2 | Matrix: Meszaros/stat96v5                          |

| A.3 | Matrix: LPnetlib/lp_osa_14                         |

| A.4 | Matrix: Andrianov/ex3sta1                          |

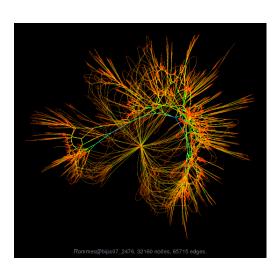

| A.5 | Matrix: Rommes/bips07_2476                         |

# List of Tables

| 3.1 | Architecture Tested                                                       | 60  |

|-----|---------------------------------------------------------------------------|-----|

| 3.2 | Sparse Matrices Evaluated                                                 | 63  |

| 4.1 | Timing Benchmarks                                                         | 107 |

| 4.2 | Architecture Tested                                                       | 119 |

| 4.3 | Evaluated Benchmarks and Their Parallel Loop Depths                       | 119 |

| 4.4 | Tile-Dimensions (ROWS x COLS) for Jacobi 3–D: Heuristic (top) vs Exhaus-  |     |

|     | tive Search (bottom)                                                      | 129 |

| 4.5 | Tile-Dimensions (ROWS x COLS) for SpMV : Heuristic (top) vs Exhaustive    |     |

|     | Search (bottom)                                                           | 131 |

| 4.6 | Tile-Dimensions (ROWS x COLS) for Coulombic Potential: Heuristic (top)    |     |

|     | vs Exhaustive Search (bottom)                                             | 131 |

| 4.7 | Tile-Dimensions (ROWS x COLS) for 2–D Image Histogram Computation :       |     |

|     | Heuristic (top) vs Exhaustive Search (bottom)                             | 132 |

| 4.8 | Tile-Dimensions (ROWS x COLS) for Synth. Trig: Heuristic (top) vs Exhaus- |     |

|     | tive Search (bottom)                                                      | 134 |

|     |                                                                           |     |

| 5.1 | Parboil Source Code Comparison (Chapel vs CUDA)                           | 163 |

| 6.1 | Architectures Tested                                                      | 179 |

| 6.2 | Effective Bandwidth to L2                                                 | 186 |

| 6.3 | Effective Bandwidth to Memory                                             | 186 |

|     |                                                                           |     |

# List of Algorithms

| 1  | Interval Node Construction                 | 11  |

|----|--------------------------------------------|-----|

| 2  | Interval Graph Partitioning                | 11  |

| 3  | General Algorithm For Task Partitioning    | 40  |

| 4  | AgglomerateFG(STMT, ABB)                   | 41  |

| 5  | Data Placement Algorithm                   | 52  |

| 6  | Heuristic to Determine Blocking Dimensions | 118 |

| 7  | Loop Transformation for Multi-core         | 153 |

| 8  | LoopDist() Function                        | 154 |

| 9  | Implicit Data Transfer                     | 155 |

| 10 | Spill Scalar Args Into Constant Mem        | 156 |

| 11 | Calculate Block Size                       | 171 |

| 12 | Calculate Cache Mapping                    | 173 |

| 13 | Calculate Processor Mapping                | 174 |

| 14 | Calculate Bandwidth                        | 174 |

| 15 | Pointer Chaining                           | 177 |

## Chapter 1

## Introduction

#### 1.1 Overview

The ability to fully leverage parallelism, both explicitly with low-level programming languages, and implicitly through compilers or libraries, has always been a complex and multifaceted challenge. Even with the valiant efforts of researchers over the past five decades, there is still much to learn. Until the beginning of the 2000s, computer architects were able to dodge this problem by focusing their efforts on single-core performance. This meant increased clock speeds, larger memory hierarchies, and deeper pipeline architectures that are able to extract more instruction level parallelism. This has allowed users to get their free performance lunch [3]. However, this has led to its own set of challenges due to the physical demands of increased CPU power, more heat dissipation, and the bandwidth limiting disparity between processor and memory speeds known as the memory wall [4]. While these problems are still hurdles today, architects have been able to temporarily alleviate their impact by increasing the number of processor cores on the same die, developing even deeper memory hierarchies, and providing larger vector units and other specialized functional units. As a result of this, users are now forced to deal with an ever-increasing amount of parallelism.

Additionally, homogeneous multicomputers are no longer the only form of machine architecture used. Heterogeneous parallelism is pervasive in our culture, from consumer devices containing multiple cores and GPUs such as modern smartphones and automotive electronics to traditional large-scale supercomputers. It is now common to see large-scale heterogeneous architectures consisting of GPU accelerators and multiprocessors with large core counts and vector units [5]. For example, as of November 2012, the number one computer on the Top500 list is Oak Ridge National Laboratory's Titan [6]. This machine is configured with 299,008 AMD Opteron cores and 18,688 NVIDIA Tesla GPUs.

As mentioned earlier, the problems of increased demand in power, heat dissipation, and the memory wall still exist in current architectures. Even beyond the idea of performance portability, there is now a loss of functional portability when compiling and executing the same program across different classes of architectures. For example, having an application that has been hand-tuned for a NVIDIA-based GPU and retargeting it to execute on a multi-core system is not trivial [7, 8, 9]. With these new dimensions of complexity, one major software challenge is having the ability to efficiently exploit all of the hardware parallelism without sacrificing programmer productivity and, at the same time, striving to be portable. One approach that some have taken to address these challenges is to introduce new runtime systems and execution models that are dependence-based [10, 11, 12, 13] (sometimes called codelets [14, 15]), new declarative programming languages [16, 17, 18], and libraries [19]. While these systems have shown great promise in terms of application performance, relying on new programming models would force applications written in commonly used imperative programming languages to be rewritten into a declarative programming paradigm. This might not be economical for applications with a large existing code base or when the application is no longer actively maintained.

In addition to increasing processing power and memory sizes, the length of a program's source code and the amount of data it occupies is also increasing. In many cases, this is

making applications more complex, typically requiring domain experts to develop them. In order for these domain experts to have a remote chance of leveraging such complex systems, high-level programming languages (with the help of more intelligent compilers) need to bridge this gap. Moreover, if the HPC community plans to tackle the challenge of reaching exascale levels by the 2020 time frame [20], these complexities need to be addressed with urgency.

This thesis presents methods and ideas to help address the challenges of making parallel programming easier. This will be addressed at four levels: at the programming language level, in the compiler, dynamically in the runtime, and offline during compilation using microbenchmarks. As a foundation, this work will start with Chapel [21], a high-level language designed from the ground up to deal with parallelism. Using Chapel and leveraging its support for first-class user-defined distributions [22], new compiler techniques are developed to support the mapping of multiply-nested parallel loops onto dependence-driven execution models, such as StarPU or ETI Swarm. In addition to these dependence-based execution models, it will be shown how the same set of data-parallel loops can now also be retargeted onto GPU architectures without any modifications to the loops. The reverse of this will also be shown, where code that has been hand-tuned for a specific platform (such as a GPU) can be mapped back onto a traditional multi-core platform.

To deal with the problem of exploiting the available parallelism, machine cost models will be used to drive new heuristics that will determine the correct amount of parallelism necessary to maximize performance. This is important because there are situations where using all of the parallelism can be detrimental to the performance of an algorithm due to an excess of overhead from the runtime or other libraries. Part of the heuristics will be based on a cost model of the execution model and the underlying memory architecture.

To aid programmers in extracting additional performance for parallel programs, a new micro-benchmark suite will be presented. This benchmark suite is based on simple and portable micro-benchmarks that determine machine characteristics specific to multi-cores and the memory hierarchy that can be used as parameters to optimize parallel programs by a compiler, an expert programmer, or an auto-tuner.

#### 1.2 Contributions

In order to tackle the challenges described in Section 1.1, this thesis makes the following contributions:

#### • Generation of Task Graphs from Explicitly Parallel Loops

With the introduction of agglomerated flow graphs, and by using interval analysis [1] as a basis, new compilation techniques are developed to hierarchically partition programs around explicitly single and multiply-nested data-parallel loops and other control-dependent statements. This partitioning forms a new intermediate representation based on task-dependence graphs which are composed of executable nodes connected by dependence constraints. The task graphs can then be mapped and scheduled onto a dependence-driven runtime system. This work also presents new algorithms to deal with data placement and communication between the tasks in a task-dependence graph. Once the task-graph form is fully instantiated, code generation is performed to generate the necessary instructions for correct execution. Experimental results will show that only a minimal amount of overhead has been added, with little to no impact on performance scalability.

#### • Language Extensions to Express Arbitrary Task Execution Order

New language extensions are developed that express the explicit order of execution among different program components (e.g. statements, loops, blocks, procedures). By leveraging the loop partitioning transformations being produced, these language extensions can now provide enough information that a task-dependence graph can be

formed and, thus, mapped onto any given parallel architecture. Additionally, the compiler can leverage these language extensions as a complement (or replacement) for traditional data-dependence analysis to help it determine the legality of loop-based transformations.

#### • Methods to Determine Tile Dimensions for Coarse-grain Parallelism

A set of compiler and runtime-based heuristics are presented that will be used to determine the appropriate number of processors to use and what the processor multi-dimensional shapes need to be. These heuristics are based on a cost model that is derived from offline micro-benchmark measurements to find certain machine characteristics and overheads in driving the correct processor configurations. Rather than just selecting the maximum amount of parallelism supported on the system, the algorithm chooses the processor configuration that minimizes both the impact of a static load-imbalance and the memory footprint of data used in the loops. The effectiveness of this approach is then compared against other commonly-applied compiler optimizations. Part of this work will also introduce a new loop-transformation that combines tiling with traditional loop-coalescing in order to decrease the synchronization overhead from parallel loops.

# • A Portable Mapping of Data and Computations Between GPU and Traditional Multi-core Architectures

New compiler transformations that increase programmer productivity are presented. By leveraging the programming language Chapel, a single source code implementation can be used to target not only conventional multiprocessors, but also GPU architectures. Rather than resorting to different parallel libraries or annotations for a given parallel platform, this contribution will only need to leverage Chapel's support for user-defined distributions and its support for data-parallel loops. Experimental results

from the Parboil benchmark suite are presented and demonstrate that codes written in Chapel achieve performance that are comparable to the original versions implemented in CUDA on both GPUs and multi-core platforms.

### Portable Micro-benchmark Suite to Determine Machine Characteristics for Parallelism and Locality

A suite of micro-benchmarks named P-Ray is presented. These micro-benchmarks provide a way of introspecting hardware characteristics specific to multi-core architectures. Such characteristics include the number of cores that share the L2 cache, the different processors interconnection topologies, and the bandwidth to memory for multi-cores. The presented experiments show that, for several different architectures tested, both desktop and server, P-Ray generates accurate results. By utilizing some of the machine characteristics that were discovered with these micro-benchmarks, a more accurate cost model can be constructed.

### 1.3 Thesis Organization

For each core contribution of this thesis, the problem will be introduced, along with any necessary background that has not been described yet. In some cases, a set of examples will be provided. Next, the main contribution and all of its necessary algorithms are presented. From there, different experiments will be evaluated, followed by a discussion of the current limitations and relevant future work to that section.

The remainder of the dissertation is structured into chapters as follows:

• Chapter 2: Presents a high-level background and overview of concepts necessary to understand the remainder of the dissertation. Specifically, it will give a short overview of components from compiler theory and parallel programming, the Chapel programming language, and dependence-driven execution models.

- Chapter 3: Describes the compilation techniques used to translate explicitly-parallel loops into a suitable form so that they can be mapped onto dependence-driven execution models.

- Chapter 4: Presents a new heuristic that will be used in determining the ideal processor configuration when targeting different runtime systems. Additionally, a new loop transformation that combines loop tiling and loop coalescing will be provided.

- Chapter 5: Discusses the techniques and optimizations used to map data-parallel codes onto heterogeneous architectures. This will also cover the algorithms used to "go backwards" and map GPU-centric code back onto a traditional multi-core platform.

- Chapter 6: Present the portable micro-benchmark suite named P-Ray and associated examples.

- Chapter 7: Propose future work.

- Chapter 8: Final thoughts and conclusions.

## Chapter 2

## Background

This chapter discusses topics that are important in understanding the remainder of the dissertation. First, this chapter presents an overview and defines some of the concepts in this thesis from the compiler and parallel computing literature. Second, a brief overview of the Chapel programming language will be presented. The material presented will be enough for the reader to understand the main concepts of the language related to data-parallelism. Finally, an overview of dependence-driven execution models will be discussed, which includes an overview of the StarPU runtime system.

### 2.1 General Compiler Preliminaries

This section describes the necessary high-level ideas relevant to compilers used in this thesis. Most of the topics discussed in this section assume the use of an imperative programming language, primarily because the input language assumed in this is imperative.

#### 2.1.1 Control Flow Analysis

#### Basic Block (BB)

A basic block is set of instructions in a linear sequence, where the only entry point is the first statement in the sequence, and the only exit point being the last statement in the sequence. Also et al. present a simple algorithm to partition a program into a set of basic blocks [23].

#### Control Flow Graph(CFG)

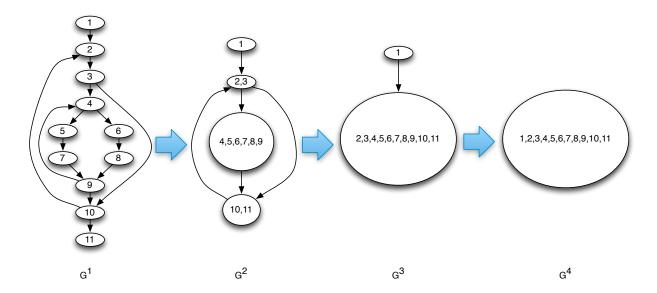

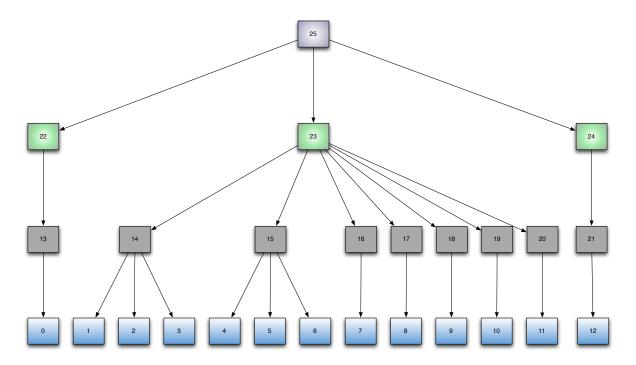

A control flow graph is a program representation where each node in the graph is a basic block, and the edges connecting the nodes represent a possible execution order (e.g. conditional-branch). More specifically, a CFG is the triple G = (V, E, s), where (V, E) make up a directed graph, V is the set of all basic blocks, E is the set of edges connecting all nodes in V, and  $s \in V$  is the entry point of the program. In Figure 2.1, the leftmost graph represents a control flow graph, where each numbered node represents a basic block.

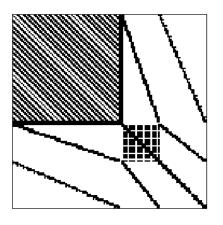

Figure 2.1: Interval Analysis Applied to a CFG

#### Interval Analysis

One way of finding structure in a control flow graph is to identify "hierarchies" of loops by applying interval analysis [1]. Intervals analysis is the technique used to partition a reducible [24] flow graph into disjoint regions named intervals. Informally, an interval is a natural loop [23] with a set of nodes forming an acyclic subgraph between the header node and a back edge that completes the loop. Let a flow graph G = (V, E, s), and  $I_G(h)$  be an interval of G with entry node h. Given an entry node h, an interval has the following properties [2]:

- Entry node h is in  $I_G(h)$ .

- Every edge that connects to  $I_G(h)$  connects only through the entry node h.

- Entry node h dominates [25] all other nodes inside of  $I_G(h)$ .

- Every cycle inside of  $I_G(h)$  includes the entry node h.

- Every node whose predecessors are in  $I_G(h)$  is added to  $I_G(h)$  until there are no such nodes.

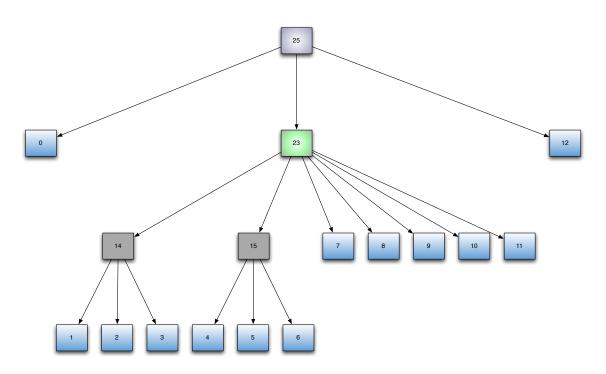

Well-known algorithms [1, 2] for constructing an interval node and partitioning a control flow graph into an interval graph are presented in Algorithms 1 and 2. Algorithm 1 constructs a single interval node, while Algorithm 2 partitions the CFG into an interval graph.

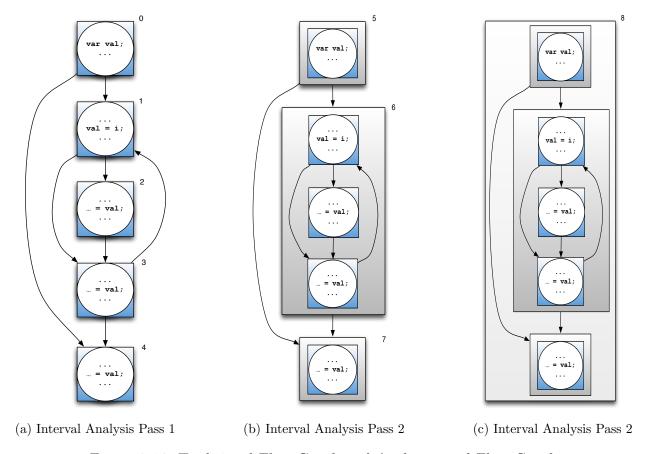

To find the nested loop structure (and determine the reducibility) of the flow graph G, interval analysis can be applied successively to create a sequence of derived graphs. Starting with  $G^1$  (the original flow graph), each successive pass of Algorithms 1 and 2 creates  $\{G^2, G^3, \ldots, G^d\}$ , where  $G^d$  is the limit flow graph. The limit flow graph is the last possible application of interval partitioning where only a single node remains. Starting with a node in  $G^{i+1}$  represents an interval in  $G^i$ . Once a limit flow graph is encountered, if it contains

```

Algorithm 1: Interval Node Construction

Input: h : node of graph G

Output: I(h) : interval node with header h

I(h) \leftarrow h;

while \exists \ a \ node \ m \ such \ that \ m \notin I(h) \land m \neq s \land \ all \ predecessors \ of \ m \ are \ in \ I(h) \ do

[I(h) \leftarrow I(h) \cup m;

```

```

Algorithm 2: Interval Graph Partitioning

Input: Control flow graph G = (V, E, s)

Output: H : set of potential header nodes

Output: L : set of intervals

H \leftarrow \{s\};

L \leftarrow \emptyset;

while H \neq \emptyset do

select and delete a node h from H;

I(h) \leftarrow computed using Algorithm 1;

L \leftarrow L \cup I(h);

H \leftarrow H \cup \{n \mid n \text{ has a predecessor in } I(h) \land n \not\in L\};

```

Figure 2.2: Interval Analysis [1, 2]

a single node, it can be said that the graph G is reducible. Conceptually, by consecutively applying interval analysis, a loop nesting structure forms. This nesting structure starts to form from the innermost loop to the outermost per each successive step of the algorithm. This is a feature that will soon be exploited when partitioning nested parallel loops into separate tasks for the dependence-driven runtime.

Consider the graphs shown in Figure 2.1. The leftmost graph represents a control flow graph. Each numbered node in this graph is a basic block. After applying interval analysis to the CFG, an interval graph is formed as demonstrated by the second graph from the left. Applying interval analysis again forms the third graph from the left. Applying interval analysis one final time results in the limit flow graph as shown on the rightmost graph.

It has been shown that the likelihood of a graph being irreducible is rare [26, 27]. In cases where the graph is irreducible, *node splitting* [2] can be used to transform the graph into one that is reducible. For the remainder of this dissertation, it can be assumed that all

programs will be reducible, as Chapel is a structured programming language that does not support unstructured control idioms (e.g. GOTO, setjmp(), longjmp(), etc.). In the case of Chapel's intermediate representation: it does generate GOTOs internally, but none of these internal GOTOs cause a branch into a loop.

Interval analysis traditionally has had numerous uses, such as being an alternative for iterative dataflow analysis [28]. The work in Chapter 3 leverages interval analysis by partitioning an explicitly-parallel program into a hierarchical set of interval graphs (up to the limit flow graph) that consist of nested-parallel loops with control statements joining them together.

#### 2.1.2 Dependences: Data and Control

#### **Data Dependence**

The ability to reason about what dependences exist between data has many uses in compilers. This includes the ability to determine the correctness of compiler transformations when the order of execution between statements has changed, to detect parallelism automatically, and to perform loop vectorization.

A data dependence is simply the relation between two statements in a program that have a partial execution order between them. Given two statements  $S_1$  and  $S_2$ , there is a data dependence between  $S_1$  and  $S_2$  if all of the following conditions are true:

- 1. Both  $S_1$  and  $S_2$  access memory location M

- 2. Either  $S_1$  or  $S_2$  performs a write to memory location M

- 3. There is a path of execution from  $S_1$  to  $S_2$  or from  $S_2$  to  $S_1$

A data-dependence can be further classified into one of the following types:

#### 1. Flow Dependence (or True Dependence)

A statement  $S_2$  has a flow dependence on statement  $S_1$  (denoted as  $S_1\delta S_2$ ) when there is a path from  $S_1$  to  $S_2$ , and  $S_1$  stores a value at location M and  $S_2$  reads from location M.

#### 2. Anti-dependence

A statement  $S_2$  has an anti-dependence on statement  $S_1$  (denoted as  $S_1\delta^{-1}S_2$ ) when there is a path from  $S_1$  to  $S_2$ , and  $S_1$  reads a value at location M and  $S_2$  writes a value at M.

#### 3. Output Dependence

A statement  $S_2$  has an output dependence on statement  $S_1$  (denoted as  ${}_1\delta^O S_2$ ) when  $S_1$  writes a value at location M and then  $S_2$  will write a value at M.

An important observation from these definitions is that if there are no dependences between the statements  $S_1$  and  $S_2$ , both can be executed in parallel with respect to each other.

#### Dependences in Loops

The notion of data dependences can also applied in the presence of loops. Similar to how a data dependence was defined earlier, a statement  $S_1$  can have a dependence on a statement  $S_2$  even across different loop iterations. As a result of this, there are two classifications of dependences when related to loops: loop-carried and loop-independent.

#### 1. Loop-Carried Dependence

A loop-carried dependence exists when there is a dependence between two statements  $S_1$  and  $S_2$  across different iterations of a loop. This form of dependence limits the amount of parallelism that exists in the loop unless further transformations are applied [29].

#### 2. Loop-Independent Dependence

A loop-independent dependence exists when there is a dependence between two statements  $S_1$  and  $S_2$  only on the same iteration of a loop. Assuming that all dependences between the statements in a loop are independent, then the iterations of the loop are independent, thus each iteration of the loop can now be fully parallelized.

#### Control Dependence

Similar to data dependences specifying an ordering between statements, control dependences specify whether a statement has executed. A statement S is said to be control dependent on a conditional branch  $B_1$ , if by taking branch  $B_1$  will always cause S to execute. If another branch  $B_2$  of that conditional statement executes, then S does not need to execute.

Computing the control dependences for a graph has led to many advances such as new compiler optimizations [30], the automatic detection of parallelism [31], and computing SSA form [32].

#### 2.1.3 Data-Parallelism

A major component of the work from this thesis depends on data-parallelism. Simply, data-parallelism is a form of parallelism where the same instructions or operation is applied to different sections of data in parallel, either on different processors or different devices within a processor. There are numerous advantages to choosing data-parallelism, including determinacy, and high-level expressiveness. Data-parallelism is fundamental to numerous programming models and languages, including OpenMP [33], NESL [34], ZPL [35], and CUDA [36]. While there are different high-level, data-parallel primitives, including parallel prefix [37], the main focus of this work will be on data-parallel loops.

#### Data-Parallel Loops

For the remainder of this dissertation, the reader can assume that a data-parallel loop is defined as a loop where the only dependences that occur inside of the loop are loop-independent (i.e. no loop-carried dependences). Each iteration of the loop can now execute independently of the other iterations, as if the loop were executed sequentially. Additionally, the iteration space of the loop is fixed upon entering the loop, and there is no way to prematurely exit the loop. The parallel for from OpenMP and the forall from Chapel are examples of this. However, in the case of Fortran 95's forall loop, it is different from the one defined here, because Fortran 95's forall loop can only contain assignments to arrays, as opposed to containing other forms of statements, even including other parallel loops nested inside of it.

In order to ensure correctness after a data-parallel loop has completed, an implicit barrier synchronization in the form of an implicit join is commonly placed between the end of the loop and the start of the next statement in the program. A join is a synchronization construct that forces the worker threads in a group to stop at the barrier point until all of the worker threads of this group reach the synchronization point. Once all of the threads reach the join, execution for the master thread can resume. When dealing with more dynamic forms of parallelism, there have been improvements to the concept of barriers, including support for clocks [38] or phasers [39].

The doacross [40, 41] is a special form of a parallel loop where the parallelism is constrained due to forward loop-carried dependences across iterations of the loop. In this case, a doacross loop's iterations are scheduled onto threads and executed in a pipelined order, which allow portions of the loop body to be overlapped in execution. In order to ensure program correctness, synchronization primitives (e.g. signal() and wait()) are commonly used to enforce the correct execution order.

A situation can also exist where data-parallel loops are nested inside of data-parallel

loops. Nested parallelism occurs in numerous situations. For example, when operating on a multi-dimensional array where the operations are parallel along all dimensions. There can also be a noticeable amount of overhead as a result of inner parallelism, including overheads from task and barrier creation and task destruction. If the nested-parallel loop bounds are statically known, and if the parallel loops are perfectly-nested, techniques such as loop coalescing [42] can be performed. Given a multi-dimensional loop L that is perfectlynested and data-parallel, and  $L=(N_m,N_{m-1},\ldots,N_1)$ , where  $N_m,N_{m-1},\ldots,N_1$  denote the normalized loop limits, loop coalescing is a compiler optimization that combines the multi-dimensional iteration space of L into a single-dimensional loop L' with  $\prod_{i=1}^{m} N_i$  total iterations. Loop coalescing has the benefit of decreasing a substantial amount of overhead in task management in addition to improving loop schedules. This benefit remains as long as the amount of time spent computing the new single-dimensional indices is not greater than the overhead of dynamically spawning the threads for the inner parallel loops. Otherwise, there is no benefit to this transformation. The downside to loop-coalescing is that this transformation is oblivious to locality, and in some cases could decrease it. Part of the work in Chapter 4 introduces a method that combines loop coalescing with tiling for perfectlynested parallel loops. In the situation where the loops are not perfectly-nested, techniques such as loop distribution [43] may be applied in order to force the loops to become perfectlynested.

### 2.2 Dependence-Driven Execution Models

The goal of this section is to provide the reader with an intuition for what dependence-driven execution models are, including the description of an example dependence-driven runtime system named StarPU. While there are differences in terminology, implementation, and overall design between dependence-driven execution models, they all share the core idea that

a computation can begin as soon as all of its dependence constraints (task, data, or control) have been resolved. The root of this is derived from the classic dataflow-architecture based approach [44] where the instructions of a program are executed in a partial ordering that has been defined by its dependences. Unlike the von Neumann architecture, the dataflow model has no program counter and the execution of code can only be performed once all of its input arguments are available to it. The dataflow model has no global state since data (sometimes referred to as a *token*) is communicated along the edges connecting dependent nodes. Due to its stateless nature, the dataflow model is well suited to declarative programming paradigms including functional languages [45, 46, 47].

In a dependence-driven execution model, a program is represented by a directed graph DFG = (V, E, s) where V represents computation nodes (also called actors), E are the directed arcs that represent dependences between the nodes, and s is the starting point of the program. A node  $n \in V$  can execute (fire) as soon as all of its incoming dependences are resolved. The type of dependence and the granularity of a node differs based on the specific programming model. In the early days of dataflow, nodes were fine-grain (at the single instruction level), and as soon as the operands for the instruction were available (i.e. tokens on all of its input edges), the instruction could then execute atomically. While this exposes a high-degree of parallelism, the overheads from scheduling and communication were extremely high. Additionally, exploiting locality was difficult [48]. To alleviate scheduling overheads, the nodes had to be coarsened, effectively making this into macro-dataflow. In the macrodataflow approach, the granularity of the nodes are typically at the task-level (i.e. more than one instruction). This reduces scheduling overhead, and locality can now be exploited within the node. The downside is that this still requires an explicit communication of tokens between the nodes in order to enforce the stateless design of the programming model. For example, in StarPU [11], a node is always a task (sometimes referred to as a codelet [14]).

As the number of processing units increases, so does the degree of parallelism available.

In an attempt to leverage this new-found parallelism, there has been a resurgence of execution models that are dependence-driven. Examples include StarPU [11], Intel Concurrent Collections (CnC) [16], SWARM by ET International [14], and PLASMA [49], among others. This new breed of dependence-driven execution models is fundamentally designed for shared memory multi-core and many-core systems along with some support for distributed memory machines.

#### 2.2.1 StarPU Runtime System

This section will give a brief overview of the StarPU dependence-driven runtime system. For the implementation work that is part of this thesis, StarPU was chosen as the targeted runtime due to its maturity, well-studied performance, and support for data coherence between tasks.

StarPU is a dependence-driven execution runtime system that allows for the parallel execution of code on heterogeneous architectures including multi-core processors and many-core architectures such as GPU accelerators. Using a dynamic task-dependence graph as its input, the StarPU runtime system is able to efficiently schedule tasks onto the heterogeneous components of the machine. The runtime system also supports a software-based distributed shared memory (DSM) with relaxed consistency and data replication onto the components. In addition to automatically selecting a task scheduling policy based on different criteria, there is support for user-provided scheduling policies and performance analysis tools. The remainder of this section will describe the essential components necessary to understand the execution model used.

#### StarPU Task-Dependence Graph Construction

The simplest method of creating a program for StarPU is to declaratively describe the program in terms of *task* nodes. These tasks are C-style functions that can be executed

```

1 declare_deps(tagB, 1, tagA);

2 declare_deps(tagC, 1, tagA);

3 declare_deps(tagD, 1, tagA);

4 declare_deps(tagE, 1, tagB);

В

D

5 declare_deps(tagF, 1, tagB);

6 declare_deps(tagG, 2, tagE, tagF);

7 declare_deps(tagH, 3, tagG, tagC, tagD);

Ε

9 taskA->tag_id = tagA;

10 taskB->tag_id = tagB;

11 . . .

12 taskH->tag_id = tagH;

G

14 task_submit(taskA);

15 task_submit(taskB);

17 task_submit(taskH);

19 tag_wait(tagH);

```

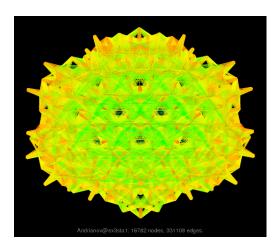

Figure 2.3: StarPU Task-Dependence Graph

independently of the other tasks. These task node are then asynchronously inserted to a task-dependence graph. Since StarPU has support for heterogeneous architectures, the task can be specified to execute either on a traditional CPU or take the form of a data-parallel kernel as used in CUDA [36] or OpenCL [50]. In order to start expressing dependences between the tasks, a tag (a task identifier) needs to be associated with the task. Once a task with an associated tag has completed its computation, any tasks that were dependent on that tag (assuming that was their only dependence) can start execution on the device. The creation of tasks and tags are decoupled. This was done in order for dependences between tags to be specified without having had created the task data structures.

Consider the example in Figure 2.3. The directed graph on the right represents a task-dependence graph where the nodes are the tasks, and the edges are their dependences. As shown on the left side of the figure, lines 1-7 construct the tag dependences and lines 9-12 associate a tag with a particular task. Once the graph is constructed, and the the individual tasks are submitted to the runtime, execution can begin. Since node A does not have any incoming edges, it can start immediately. Finally, line 19 blocks any subsequent execution

until the task with tagH completes.

#### StarPU Data Management

In order for the programmer to not deal with the explicit data management across different heterogeneous components, StarPU provides facilities to handle data management automatically through its distributed shared memory based on the *modified-shared-invalid* (MSI) coherence protocol. In order for the MSI protocol to keep the system coherent, data is able to be replicated across the different memory nodes (e.g. the CPU and GPU memory spaces).

In order to use the DSM, data is first registered with the runtime; then proceeds to perform the memory allocation on the respective devices and return a data handle back to the main application. This handle is then associated with a task. When a data lookup using the handle occurs inside of the tasks, the runtime performs the correct memory lookup.

### 2.3 Chapel Language Overview

This section presents a short overview of the Chapel programming language [21] and its support for data parallelism. The remainder of this thesis is based on the Chapel 1.4.0 release [51].

Chapel is an object-oriented parallel programming language designed from first principles, rather than as an extension to an existing language. The base language supports iterator functions, generic programming, and it also takes advantage of type inference to determine data types automatically. Chapel was designed to facilitate programming of next-generation parallel machines well, and make using current-generation machines more productive. Along with X10 [38] and Fortress [52], Chapel grew out of the DARPA *High Productivity Computing Systems (HPCS)* program. Chapel support for data parallelism, index sets, and distributed arrays are derived from ZPL [53] and High Performance Fortran (HPF) [54].

Chapel's concepts of task parallelism and lightweight synchronization are derived from the Cray MTA/XMT's extensions to C and Fortran [55]. Lastly, Chapel supports interoperability with C and CUDA through C-style extern mechanisms. For interoperability with other languages such as C++, Fortran, or Python, the Babel interoperability tool [56] can be used.

The reference implementation of the Chapel compiler is a source-to-source based compiler that generates C source code. There is also an option to use LLVM [57] as the compiler backend, but the work in this thesis does not leverage that.

#### 2.3.1 Domains and Distributed Arrays

The core component for data parallelism in Chapel is the concept of a *domain*, which is an extension to *regions* first described in ZPL [58]. A domain is a first-class language construct that describes an index space [51]. In addition to supporting iterations by loops, domains are used to describe the size and shapes of arrays. Consider the following example in Figure 2.4.

```

var D: domain(2) = [1..n, 1..n];

var A: [D] real;

for xy in D {

A(xy) = (1, 2);

}

```

Figure 2.4: Example Demonstrating Chapel's Support for Domains

Here, D is a 2D domain and is initialized to contain the set of indices (i,j) with  $i \in \{1,2,..,n\}$  and  $j \in \{1,2,..,n\}$ . The array A has its index set defined by the domain, resulting in an  $n \times n$  array. The loop performs an iteration over the 2D iteration space defined by domain D where each each iteration index xy is a two-element tuple.

## 2.3.2 Data Parallelism in Chapel

Chapel has rich support for data parallel computation, making it ideal for SIMD-like architectures such as the GPU [7]. The main construct for data parallelism in Chapel is the forall loop which iterates over the indices in a domain's index set or over a subset of the elements in an array. There is also built-in support for the reduction and scan operators. Chapel also allows users to define their own reduction and scan operations [59].

# 2.3.3 Task Parallelism in Chapel

Chapel's support for task parallelism includes begin, cobegin, and coforall statements. The unstructured begin statement will asynchronously spawn a task containing the contents of the begin block and possibly return at a later synchronization point specified by the programmer. The structured cobegin will spawn a separate task for each program statement inside of the cobegin block. The parent task that invoked cobegin will resume execution as soon as all cobegin inner tasks have completed. The structured loop statement coforall creates a separate task for each iteration of the loop. Similar to the cobegin, the parent task will wait for all coforall iteration tasks to complete before proceeding.

# 2.3.4 Distributions (Built-in and User-defined)

Data distributions in Chapel are essentially a recipe that the compiler uses to map a computation and its associated data to the nodes where the program executes. Languages such as HPF and ZPL have support for distributed arrays, but the semantics of the distributions are hard-wired into the compiler and runtime, leaving the programmer without enough flexibility to manipulate many forms of distributed data (such as sparse arrays). Similar to domains, distributions are first-class objects: they can be named, manipulated, and passed through functions.

Chapel provides a set of commonly-used distributions such as *Block* and *Cyclic*. Additionally, user-defined distributions [60, 22] enable the creation of a wide range of distributions that are application- or target-specific. User-defined distributions are developed directly in Chapel, typically using built-in features (e.g. classes, task parallelism, locales). This has the benefit that distribution developers can directly leverage the high-level facilities offered by the language rather than having to program in a lower-level language.

In order for users to write their own distributions, they must implement routines to fulfill the required interface. Interface components include the ability to create domains and arrays, wholesale assignment of index sets, iterators supporting sequential and parallel iteration over a domain, random access to elements of an array, and support for slicing and reindexing. If the user does not explicitly declare a distribution, Chapel will implicitly use a distribution that targets shared memory parallelism.

Chapel uses the dmapped keyword in order to map the domain's indices to the target architecture using the specified distribution. This approach is useful because Chapel distributions are designed so that they can be swapped in order to modify the implementation of a domain and its arrays without changing the code. The advantage to this is that the code is cleaner and more portable: users do not need to maintain a separate code base for each target architecture. The concept of user-defined Chapel distributions will be applied later in Chapter 5 for targeting GPU architectures.

# Chapter 3

# Compilation for Dependence-Driven Models

The chapter presents compiler algorithms that are used to map entire loop-based parallel imperative programs for efficient execution onto a dependence-driven execution model.

# 3.1 Introduction

There has been an active push in both industrial and academic labs to build exascale machine architectures with the goal of sharply decreasing energy consumption in order to achieve exascale levels of computing performance. For this to work, it would require new circuit topologies and machine architectures. There is also a fresh look needed at different parallel programming models as alternatives to the traditional approaches such as OpenMP [33] or OpenCL [50]. One of the major problems with the traditional loop-based parallel programming models is that parallelism is constrained by the use of barrier synchronization in fork-join styles of parallelism [61, 11, 13]. Any limitation on a program's parallelism could be detrimental since this is a vastly needed commodity for driving exascale levels of performance.

Instead, in the dependence-driven (e.g. dataflow) approaches, the only things limiting parallelism are the natural dependences that exist. For example, as part of the DARPA-sponsored Intel UHPC (Ubiquitous High-Performance Computing) project, Intel and its partners have been developing a novel architecture that is power efficient and scalable to exascale levels. An execution model chosen for this type of architecture is the dependence-driven system named SWARM (SWift Adaptive Runtime Machine) [14]. Since the vast majority of existing HPC applications are imperative and loop-based, the application programmers would need to rewrite their code to suit these dependence-driven models. A downside to this is the difficulty in porting the application to another language, which is not always practical or economical.

For this work, Chapel was chosen as the input language for reasons including:

- Chapel provides an extensible and easy to learn compiler infrastructure with an AST internal representation (IR). This makes adding new compiler passes straightforward and simple.

- The language has first-class support for different parallel constructs such as dataparallelism and task-parallelism.

- Chapel's user-defined domain maps [22] help in writing portable applications. The same loops can be used across a different class of parallel machines just by changing the domain map.

In determining a dependence-driven execution model, StarPU was chosen over other existing implementations for the following reasons:

• Support for data-coherence across tasks. This alleviates some of the complexity of coherent data management from the compiler, and pushes it into the runtime system.

- Support for execution on heterogeneous architectures. While not actively pursued as part of this thesis, this allows for the work presented here to be extended in order to leverage StarPU's support for heterogeneous systems.

- StarPU is a stable and production-worthy system that other research projects are currently leveraging [62, 63].

This chapter tries to address the question of whether it is possible (and worthwhile) to compile traditional (i.e. imperative and explicitly parallel) applications to execute on dependence-driven execution models. More concretely, this work will look at the compilation techniques that are necessary to map Chapel applications using multiply-nested parallel loops and execute them using the StarPU dependence-driven runtime system, while still requiring barriers for program correctness. Even though StarPU supports heterogeneous architectures including GPUs, the focus in this chapter will only be multi-core architectures. While the implementation of the concepts discussed in this chapter use both Chapel and StarPU, they would be similarly applicable to other similar languages and runtime systems.

A limitation of compiling data-parallel loops is that in order to ensure correctness, an implicit barrier synchronization (i.e. join) needs to occur after the loop, thus limiting potential parallelism [64]. As will be shown later in this chapter, the performance limitation of an implicit barrier synchronization will be further exacerbated when nested-parallelism is involved. To address this, a new language extension is defined to allow the user to explicitly express the dependences between different statements of a program, thus allowing other statements to execute concurrently if their dependences have been met. Additionally, Chapter 4 will describe an optimization that can reduce barrier synchronizations and find the ideal number of processor resources to utilize for a computation.

#### Contributions

The contributions of this chapter are as follows:

- The development of new compiler algorithms based on interval analysis that map multiply-nested parallel loops onto dependence-driven runtime systems.

- The introduction of agglomerated flow graphs and agglomerated basic blocks which represent a coarsened flow graph with disjoint parallel and sequential blocks of code.