## MASK DESIGN, FABRICATION AND TEST NMOS TRANSISTOR

## MOHD ZAINIZAN BIN SAHDAN

This thesis is submitted as partial fulfillment of the requirements for the award of the Master Degree of Electrical Engineering

Faculty of Electrical and Electronic Engineering Kolej Universiti Teknologi Tun Hussein Onn

29 OCTOBER, 2004

For My Mother Iswati Binti Khamis,

#### **ACKNOWLEDGEMENT**

I would like to express my gratitude to my supervisors, Professor Dr Hashim bin Saim for his support and Associate Professor Dr. Uda bin Hashim for his guidance and help rendered throughout this project. Their willingness to teach attitude and unfailing patience has been a great motivation for me to excel in my work. Without their guidance and invaluable time spent, this thesis would not been completed successfully.

To Associate Professor Dr. Zul Azhar Mohd Jamal for giving me the permission to use the KUKUM Microfabrication Cleanroom, Mr. K.C. Phang for the technical support, Marlia Morsen, Nur Hamidah Abdul Halim, Mohd Nuzaihan bin Mohd Nor and others whose name could not be mentioned here one by one. I really appreciate your encouragement and concern.

To my fiancé Azrini Idris and my parents Iswati Khamis and Sahdan Saikon, for giving me the encouragement and moral support. I appreciate their immense contribution and I dedicate this thesis especially to them.

#### **ABSTRACT**

Dalam proses fabrikasi MOSFET, satu set topeng digunakan bagi tujuan menutup atau membuka sesuatu kawasan pada silicon wafer. Set topeng yang digunakan dalam fabrikasi piawai adalah sangat tinggi kosnya dan tidak praktikal untuk tujuan pendidikan. Satu set topeng yang ekonomik adalah penyelesaiannya dengan menggunakan filem transparency yang mempunyai panjang saluran daripada 250um hingga maksimum 20um telah dihasilkan. Sebanyak 4 empat topeng telah direkabentuk dalam perisian AutoCAD 2002 drawing tools dan telah dicetak ke atas filem transparency. Kaedah contact printing digunakan untuk memindahkan bentangan topeng ke atas silicon wafer 4 inci menggunakan teknik standard photolithography untuk memastikan keseragaman lapisan. Proses fabrikasi MOSFET dilakukan selepas kesemua parameter dioptimumkan. Selepas MOSFET selesai dihasilkan, probe station dan MOSFET characterization analyzer software digunakan untuk menganalisa ciri-ciri MOSFET. Set topeng yang digunakan dalam projek ini adalah praktikal untuk tujuan pendidikan dan MOSFET yang dihasilkan juga berfungsi seperti yang dikehendaki.

#### **ABSTRACT**

In MOSFET fabrication, mask set was used to define certain region on a silicon wafer. The mask sets that used in standard fabrication are very expensive and not practical for education purposes. An economical solution of masks using transparency films with various channel length from 250um to 20 um was produced. Four mask set of MOSFET were designed using AutoCAD 2002 drawing tools and then printed on the transparency film. Contact printing method was utilized to transfer the mask layouts on a 4-inch silicon wafer using standard photolithography technique to check the line uniformity. The MOSFET fabrication process was done after optimizing the parameters. Probe station and MOSFET characterization analyzer software was used to characterize the fabricated MOSFET. The mask used in this project was practical for education purpose and the MOSFET was successfully fabricated.

# TABLE OF CONTENTS

| CHAPTER   | TIT                       | LE                 | PAGE |  |

|-----------|---------------------------|--------------------|------|--|

|           | DEC                       | CLARATION          | ii   |  |

|           | DEI                       | DICATION           | iii  |  |

|           | ACI                       | KNOWLEDGEMENT      | iv   |  |

|           | ABS                       | TRACT              | v    |  |

|           | ABS                       | TRAK               | vi   |  |

|           | TAE                       | BLE OF CONTENTS    | vii  |  |

|           | LIST                      | LIST OF FIGURES    |      |  |

|           | LIST                      | T OF TABLES        | xii  |  |

|           | GLOSSARY OF ABBREVIATIONS |                    |      |  |

|           | LIST OF APPENDIX          |                    | xv   |  |

|           |                           |                    |      |  |

| CHAPTER I |                           | RODUCTION          | 1    |  |

|           | 1.1                       | Background         | 1    |  |

|           | 1.2                       | Problem Statement  | 3    |  |

|           | 1.3                       | Project Objectives | 3    |  |

|           | 1 4                       | Scope of Work      | 4    |  |

|            |      |        |                                 | viii |

|------------|------|--------|---------------------------------|------|

| CHAPTER II | LITI | ERATUI | RE REVIEW                       | 5    |

|            | 2.1  | Backg  | round                           | 5    |

|            | 2.2  | The G  | eometric Parameter of NMOS      | 5    |

|            | 2.3  | The ga | ate capacitance                 | 7    |

|            | 2.4  | Transi | stor parameter                  | 7    |

|            | 2.5  | Curre  | nt-Voltage relationship         | 8    |

|            | 2.6  | MOSI   | FET Mask                        | 10   |

|            | 2.7  | MOSI   | FET Fabrication Process         | 11   |

|            |      | 2.7.1  | Deionized (DI) water            | 11   |

|            |      | 2.7.2  | Oxidation                       | 12   |

|            |      | 2.7.3  | Photolithography                | 16   |

|            |      | 2.7.4  | Etching                         | 17   |

|            |      | 2.7.5  | Diffusion                       | 20   |

|            |      | 2.7.6  | Physical Vapor Deposition (PVD) | 24   |

|            |      | 2.7.7  | Characterization                | 27   |

| CHAPTER III | MET | HODOLOGY                         | 29 |

|-------------|-----|----------------------------------|----|

|             |     |                                  |    |

|             | 3.1 | Background                       | 29 |

|             | 3.2 | Computer Aided Design (CAD) tool | 31 |

|             | 3.3 | Experimentation                  | 34 |

|             |     | 3.3.1 Oxidation Process          | 34 |

|             |     | 3.3.2 Photolithography           | 34 |

|             |     | 3.3.3 Diffusion                  | 35 |

|             |     | 3.3.4 Etching                    | 35 |

|             |     | 3.3.5 Metallization              | 36 |

|             | 3.4 | Testing MOSFET                   | 36 |

|            |                          |                                  | 1X |

|------------|--------------------------|----------------------------------|----|

| CHAPTER IV | EQUIPMENT AND CONSUMABLE |                                  |    |

|            | 4.1                      | Background                       | 37 |

|            | 4.2                      | KUKUM Microfabrication Cleanroom | 37 |

|            | 4.3                      | Process Equipment                | 39 |

|            | 4.4                      | Consumable                       | 45 |

| CHAPTER V  | RES                      | ULTS AND DISCUSSION              | 46 |

|            | - 1                      | D 1 1                            |    |

|            | 5.1                      | Background                       | 46 |

|            | 5.2                      | Mask Design and Fabrication      | 46 |

|            | 5.3                      | Fabrication Process              | 49 |

|            | 5.4                      | MOSFET Testing                   | 52 |

|            |                          |                                  |    |

| CHAPTER VI | CON                      | ICLUSION AND RECOMMENDATIONS     | 55 |

|            |                          |                                  |    |

|            | 5.1                      | Conclusion                       | 55 |

|            | 5.2                      | Recommendations                  | 56 |

|            | REF                      | ERENCES                          | 57 |

|            | KARA.                    | and the same                     | 57 |

|            | APP                      | ENDIX A                          | 59 |

|            | APP                      | ENDIX B                          | 60 |

|            | APP                      | ENDIX C                          | 61 |

# LIST OF FIGURE

| FIGU | RE NO. TITLE                                                           | PAGE |

|------|------------------------------------------------------------------------|------|

|      |                                                                        |      |

| 1.1  | Common symbol of NMOS transistor                                       | 2    |

| 2.1  | Basic geometric parameter of NMOS transistor                           | 6    |

| 2.2  | Alignment mark design                                                  | 10   |

| 2.3  | NMOS Transistor characteristic                                         | 28   |

| 3.1  | Flow chart of project implementation                                   | 30   |

| 3.2  | Planar and cross section of various steps creating NMOS transistor     | 32   |

| 4.1  | A view at Microfabrication Cleanroom, KUKUM                            | 36   |

| 4.2  | The Oxidation Furnace                                                  | 39   |

| 4.3  | The Diffusion Furnace                                                  | 40   |

| 4.4  | The Physical Vapor Deposition ( PVD ) furnace                          | 41   |

| 4.5  | The Ambios XP1                                                         | 41   |

| 4.6  | The Spinner                                                            | 42   |

| 4.7  | The Hot Plate                                                          | 42   |

| 4.8  | The Mask Aligner Module                                                | 43   |

| 4.9  | The Filmetrics                                                         | 43   |

| 4.10 | The 4 Point Probe                                                      | 44   |

| 5.1  | Mask drawing steps in AutoCAD 2002                                     | 47   |

| 5.2  | Mask sets on transparency films                                        | 48   |

| 5.3  | Photoresist patterning using standard chemical and lithography process | s 50 |

| 5.4  | Process development after etching                                      | 51   |

| 5.5  | Process development after striping                                     | 52   |

|     |                                                       | Xi |

|-----|-------------------------------------------------------|----|

| 5.6 | Characteristic of NMOS transistor using Probe Station | 53 |

| 5.7 | The Transfer Characteristic of NMOS transistor        | 53 |

| 5.8 | Output Parameter of NMOS transistor                   | 54 |

# LIST OF TABLE

| TABI | LE NO. TITLE PAGE                                                         | GE |

|------|---------------------------------------------------------------------------|----|

|      |                                                                           |    |

| 2.1  | The DC relationship of NMOS transistor                                    | 9  |

| 2.2  | Linear and parabolic growth rate pre-exponentials and activation energies | 14 |

| 3.1  | Steps in designing mask sets using AutoCAD 2002                           | 33 |

| 4.1  | Consumable used in NMOS Fabrication                                       | 45 |

|      |                                                                           |    |

xiii

#### GLOSSARY OF ABBREVIATIONS

$V_{GS} \qquad \quad \text{-} \qquad \text{Voltage gate to source (V)}$

V<sub>DS</sub> - Voltage drain to source (V)

V<sub>TH</sub> - Threshold Voltage (V)

i<sub>D</sub> - Drain current (mA)

IV - Current (mV) versus Voltage (V)

C<sub>ox</sub> - oxide capacitance (F)

Si - Silicon

IC - Integrated Circuit

CVD - Chemical Vapor Deposition

R<sub>s</sub> - Sheet Resistance (Ohm)

t<sub>ox</sub> - Oxide thickness (um)

# LIST OF APPENDIX

| APPENDIX | TITLE                                 | PAGE |

|----------|---------------------------------------|------|

|          |                                       |      |

| A        | Paper Published in PERFIK Conference  | 59   |

| В        | Poster Published in PERFIK Conference | 69   |

| C        | Process Flow of Fabrication Process   | 70   |

#### **CHAPTER I**

#### INTRODUCTION

## 1.1 Background

The microelectronic history start in December 1947 when three scientists Bardeen, Walter Brattain and William Shockley from Bell Laboratory of United State, invented the first semiconductor device, called transistor [1]. It was the component that gave birth to the solid state electronic era with all its famous progeny. Since that year, the semiconductor industry has seen the continuous development of new and improved processes.

The improvement of the process has in turn led to the more highly-integrated and reliable circuits that have fuelled the continuing electronics revolution [2]. This improvement falls into two broad categories; process and structure. Process improvements are those that allow the fabrication of the device and circuits in smaller dimension, higher density, quantity and reliability. The structure improvements are the

invention of new device designs allowing greater circuit performance, power control and reliability.

In the process development, semiconductor is the materials that are used to fabricate ICs. Semiconductors are useful in electronics because their electronic properties can be greatly altered in a controllable way by adding small amounts of impurities. These impurities, called dopants, add extra electrons or holes. A semiconductor with extra electrons is called an n-type semiconductor, while a semiconductor with extra holes is called a p-type semiconductor.

In IC fabrications, there are two type of semiconductor used, which are Silicon (Si) and Gallium (GaAs). The two main classes of transistor types are bi-polar and unipolar. Bi-polar devices are normally used in high speed semiconductor and low noise application. The main type of uni-polar is MOSFET (Metal Oxide Semiconductor Field Effect Transistor).

Figure 1.1: Common symbol of NMOS transistor

### 1.2 Problem Statement

In IC fabrication, mask sets are needed to transfer the designed pattern onto a wafer. The mask set produced by company in the market is very expensive and not practical for education purpose. In fabrication process, the most important thing is to get the correct recipe to fabricate transistor. This correct recipe will determine the performance of NMOS transistor that will give the best characteristic. This project was done experimentally to design a low cost mask set and to fabricate NMOS transistor using optimized parameters that would give the best characteristic.

## 1.3 Project Objective

There were four main objectives to be achieved in this project. The objectives are as follows;

i. To design a low cost mask set using transparency films.

ii. Optimize and characterize the process parameters and process flow of the transistor.

iii. Fabricate NMOS transistor using spin-on dopant technique.

iv. Test NMOS transistor to get the characteristics of the device.

# 1.4 Scopes

This project will be done by limiting the scopes into five. These scopes of the project are as follows;

- i. To establish process module, process parameter, process flow and process run card.

- ii. To design and produce a set of mask for MOSFET fabrication process.

- iii. To optimize and characterize process module.

- iv. To integrate the process module and start fabricates process of NMOS transistor.

- v. To analyze and test the product.

#### CHAPTER II

#### LITERATURE REVIEW

# 2.1 Background

Before doing this project, the first thing that was done was studying the characteristic of NMOS transistor. This chapter will explain the important part that must be known before implementing this project.

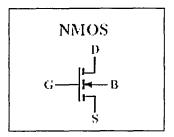

#### 2.2 The Geometric Parameter of NMOS

A 3-D structure in Figure 2.1 below illustrate the component of NMOS transistor source (S), drain (D) and gate (G). The gate of the NMOS transistor is usually made of polysilicon, which is formed from polycrystalline silicon and relatively good conductance. The gate is insulated by the layer of the silicon dioxide, SiO<sub>2</sub>, from a

conducting channel existing between two diffusion areas which form the drain and the source of the transistor.

Diffusion areas (source and drain) are created inside a substrate (also known in some technological context as the well) of the opposite type, e.g. n+ diffusion inside the p substrate, where 'n+' indicates silicon highly doped with donors.

Figure 2.1: Basic geometric parameter of NMOS transistor

From the top and cross-sectional views of the MOS transistor presented in Figure 2.1 we found that three basic geometrical parameters of the transistor are the following;

- L and W the length and width of the conducting channel between the source and drain.

- t<sub>ox</sub> thickness of the oxide layer between the gate and the diffusion/substrate areas.

## 2.3 The gate capacitance

The gate-oxide-channel structure forms a **capacitor**. The gate-oxide capacitance per unit area can be approximately calculated as:

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} \tag{2.1}$$

Where  $t_{ox} = 0.351$  pF/cm is the permittivity (a dielectric constant) of SiO<sub>2</sub>. Note that the capacitance is inversely proportional to the thickness of the silicon dioxide layer.

# 2.4 Transistor parameter

In this section we will discuss the relationship between constant (DC) voltages at the transistor terminals and the resulting drain current  $I_D$ . Apart from the voltages, the  $I_D$  current is also a function of;

i. The process parameters: the threshold voltages and a process transconductance, k<sub>c</sub> defined as follows;

$$k_c = \mu_c.C_{ox} \tag{2.2}$$

Where  $\mu_c$  is the effective mobility of the carrier and  $C_{ox}$  is the gate capacitance per unit area.

ii. The width, W, and length, L, of the channel between the source and the drain (Figure 2.1).

The parameter which links the process transconductance,  $k_c$ , with the transistor dimension is called the (non-linear) transistor transconductance parameter,  $g_c$ , and is defined by:

$$g_c = \frac{\mu_c . C_{ox}}{2} \frac{W}{L} \tag{2.3}$$

The gate voltage relative to the threshold voltage is defined as;

$$V_{\Delta} = V_G - V_T \tag{2.4}$$

The parameters  $K_c, g_c, \mu_c$  can be referred to  $k_n, g_n, \mu_n$  due to NMOS transistor.

## 2.5 Current-Voltage relationship

With the above parameters, the relationships between the DC I<sub>D</sub> current and relevant voltages can be summarized as in Table 2.1.

Table 2.1: The DC relationship of NMOS transistor

nMOS Cut-off region:  $V_{GS} < V_{Tn}$  $I_D = 0$ Linear region:  $V_{GS} \ge V_{Tn}, V_{DS} < V_{\Delta_n}$  $I_D = g_c \cdot (2V_\Delta - V_{DS}) V_{DS}$ Saturation region:  $V_{GS} \ge V_{Tn}, V_{DS} \ge V_{\Delta_n}$  $I_D = g_c \cdot V_{\Lambda}^2$

UN AMINA! The drain current I<sub>D</sub> is proportional to the ratio W/L of the transistor channel size. For given process parameters and voltages;

- The wider the transistor channel, W, the larger ID current and, i.

- The longer the transistor channel, L, the smaller ID current. ii.

The saturation occurs when

$$V_{DS} = V_{GS} - V_T$$

At the saturation point the current expressions for the linear and saturation regions are identical and can be derived by:

$$I_{sat} = g_c (2V_{\Delta}V_{\Delta} - V_{\Delta}^2) = g_c V_{\Delta}^2$$

(2.5)

#### 2.6 MOSFET Mask

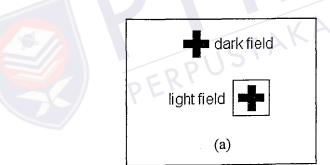

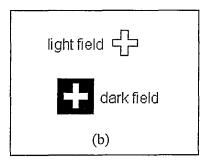

Based on Christopher T. Timmons [3], MOSFET mask design is based on four level mask steps. The mask design started with designing an alignment mark in the first mask level that was used as a reference for later levels. The mark was isolated for better alignment. Alignment was accomplished using alternating solid and outlined crosses as shown in Figure 2.2. The cross in the centre is used to align X and Y position while the outer cross is used for rotational alignment.

The alignment mark shown in Figure 2.2(a) is the design for the first mask. The dark field would leave cross island on the wafer after lithography process. This island would act as an indicator for the following masks in the alignment process. Figure 2.2(b) shows the mark design for mask 2, mask 3 and mask 4. The cross was light field, while the outer of the cross was made dark. The purpose was to make the alignment process easier by aligning the cross island through the window.

Figure 2.2: Alignment mark design. (a) Alignment mark for mask 1; (b) alignment mark for mask 2, mask 3 and mask 4.

#### 2.7 **MOSFET Fabrication Process**

There are many steps in MOSFET fabrication process. Information about fabrication process involved are clarified in this section.

#### 2.7.1 Deionized (DI) water

Deionized (DI) water is water that has no ions and it is one of the wet cleaning technologies and is a centrifugal spray cleaning technique. This process can reduce the volume of fresh chemical and is faster than immersion. The spin-drying process requires TUN AMINAT anti-static protection to prevent static-induced particle deposition on the wafers. There are two loops for DI water installation;

The make-up loop

It is the process of removing particles and colloids, total organic carbons, microorganisms, ionic impurities and total dissolved solids from raw water. In other words, it has pretreatment section for removal of gross particles of sizes larger than 1 um and purifier section for removal ionic impurities, bacteria and dissolved gases.

#### REFERENCE

- [1]. Burhanuddin Yeop Majlis (2000), "Teknologi Fabrikasi Litar Bersepadu", Penerbit Universiti Kebangsaan Malaysia.

- [2]. Peter Van Zant (2000), "Microchip Fabrication a Practice Guide to Semiconductor Processing", McGraw Hill.

- [3]. John F. Wakerly (1994), "Digital Design Principle and Practices", Prentice Hall International, Inc.

- [4]. Robert T. Paynter (2003), "Introductory Electronic Devices and Circuits", Prentice Hall International, Inc.

- [5]. Travis N. Blalock and Richard C. Jaegaer (2004), "Microelectronic Circuit Design", McGraw-Hill Higher Education.

- [6]. C.Y. Chang and S.M. Sze (1996), "VLSI Technology", McGraw Hill International Edition.

- [7]. John P. Hayes (1989), "Digital System Design and Microprocessors", McGraw Hill International Edition.

- [8]. Sorab K. Ghandi (1994), "VLSI Fabrication Principles", John Wiley & Son Inc.

- [9]. Mark N. Horenstein (1990), "Microelectronic Circuit & Devices", Prentice Hall.

- [10]. Muhammad H. Rashid (1999), "Microelectronic Circuits: Analysis and Design", PWS Publishing Company. 214-217.

- [11]. A. Chatterjee and R.A. Chapman (1997), "Sub-100nm Gate Length Metal Gate NMOS Transistor Fabricate by a Replacement gate Process", IEEE journal.

- [12]. Professor H. Scott Hinton (2002), "CMOS Fabrication Process", Technical Report, University of Kansas.

- [13]. R. Bashir and S. Venkatesan (1993), "Doping of Polycrystalline Silicon Film using an Arsenic Spin-on Glass source and surface smoothness", Journal of Vacuum Science Technology.

- [14]. S.A. Campbell (1996), "The Science and Engineering of Microelectronic Fabrication", New York: Oxford University Press.

- [15]. Hsiang Wan Liau, Yit Ping Kok and Azlan Abdul Aziz (2003), "Mask Fabrication and Photolithography in 30um Process", National Physics Conference 2003, page 61-61.

- [16]. Carolyne Johnson and Nazmul Ula (2003), "Incorporating Computer Aided Device and Process Simulated Tool in Undergraduates Course", Technical Report Department of Electrical Engineering and Computer Science, Loyola Marymount University.

- [17]. David T. Gray, Christopher Timmons and Robert W. Hendrick (2001), "Process Development for Undergraduate Microchip Fabrication Facility", American Society for Engineering Education Annual Conference & Exposition Copyright © 2001.

- [18]. Photoliography(04/05/2004), <a href="http://www.gatech.edu/research/labs/vc/processes/photolith.html#dehvdration">http://www.gatech.edu/research/labs/vc/processes/photolith.html#dehvdration</a>

- [19]. CMOS Design Technology and Design Rules (03/05/2004), <a href="http://www.wpi.edu/webcourse/ch02/#2.1">http://www.wpi.edu/webcourse/ch02/#2.1</a>

[20]. VLSI Processing Lab Manual (04/05/2004)

George Mason University,

<a href="http://bass.gmu.edu/courses/ece437/Lab\_manual\_fall2001.htm#Toc518201591">http://bass.gmu.edu/courses/ece437/Lab\_manual\_fall2001.htm#Toc518201591</a>