© 2018 Yang Xiu

#### FAILURES CAUSED BY SUPPLY FLUCTUATIONS DURING SYSTEM-LEVEL ESD

BY

YANG XIU

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2018

Urbana, Illinois

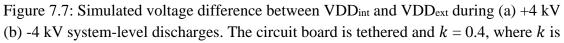

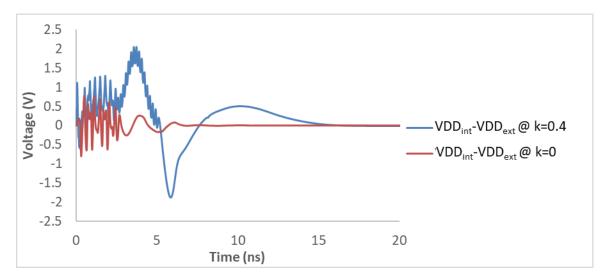

**Doctoral Committee:**

Professor Elyse Rosenbaum, Chair Professor Jose E. Schutt-Aine Professor Pavan Kumar Hanumolu Assistant Professor Songbin Gong

# ABSTRACT

It is necessary to design robust electronic systems against system-level electrostatic discharge (ESD). In additional to withstanding ESD without hard failures (permanent damage), it is important that the system is robust against soft failures (recoverable loss of function or data), which can be caused by ESD-induced noise on signal inputs and power nets. Besides radiation, the current injection into the circuit alone can cause these disturbances, especially the sharp current spike of a high amplitude in system-level ESD. The waveform of this current is similar in various ESD test setups. Circuit models with distributed elements enable accurate modeling of the system-level ESD current in contact discharge. Experiments have shown that ESD-induced noise on signal traces starts to disturb the IO input at very low ESD levels, and the effectiveness of the transient voltage suppressor (TVS) on board is limited. The noise on supply is global to integrated circuit (IC), as it travels across all the power domains. The waveform of the noise depends on the polarity of the ESD current and the type of ESD protection. The experiments have shown that the supply fluctuation can be quite severe, as a strong reverse of the on-chip supply is indicated by monitor circuits starting from the ESD levels below the common required passing level. This poses a requirement of a minimum amount of on-chip decoupling capacitances (decaps) to limit the amplitude of supply fluctuations. This requirement is similar whether the supply voltage is generated on-chip or off-chip, as

long as a large amount of off-chip decap is used and connected to the board ground. If the supply voltage is generated on-chip, the regulator needs to be carefully designed against ESD induced noise. In addition, the rail clamp, if not optimized, deteriorates the power integrity with its instability. The ESD-induced supply fluctuation may cause latch-up without careful attention to the well-bias scheme.

# ACKNOWLEDGMENTS

I would like to thank my advisor, Professor Elyse Rosenbaum, for her patience and guidance during the past five and one-half years. This work could not be completed without her support.

I would also like to thank many former and current students, including Robert Mertens, Min-Sun Keel, Zaichen Chen, Nicholas Thomson, Kuo-Hsuan Meng, Vrashank Shukla, Collin Reiman, and Dabin Zhang, for the help and inspiration from our discussions.

And finally, I very much appreciate the support of my family through all these years.

# TABLE OF CONTENTS

| LIST OF ABBREVIATIONSvii |                                                                               |   |  |

|--------------------------|-------------------------------------------------------------------------------|---|--|

| CHAPT                    | ER 1 INTRODUCTION                                                             | 1 |  |

| 1.1                      | Overview                                                                      | 6 |  |

| 1.2                      | Figures                                                                       | 7 |  |

| CHAPT                    | ER 2 MODELING OF SYSTEM-LEVEL ESD TEST CURRENT                                | 8 |  |

| 2.1                      | IEC 61000-4-2 test setup and calibration                                      | 8 |  |

| 2.2                      | Modeling approach1                                                            | 1 |  |

| 2.3                      | Distributed element modeling of the test bed                                  | 4 |  |

| 2.3                      | .1 ESD gun                                                                    | 4 |  |

| 2.3                      | .2 Bare test bed1                                                             | 6 |  |

| 2.4                      | System-level ESD current into an EUT 1                                        | 8 |  |

| 2.5                      | Figures                                                                       | 0 |  |

| CHAPT<br>OF AN           | ER 3 INTERFERENCE OF SYSTEM-LEVEL ESD WITH THE OPERATION IC2                  |   |  |

| 3.1                      | Case study of a 65-nm CMOS test chip                                          |   |  |

| 3.2                      | Measurement results of data upsets on the 65-nm test chip                     | 0 |  |

| 3.3                      | Summary of the observations                                                   | 4 |  |

| 3.4                      | Figures and tables                                                            | 5 |  |

| CHAPT                    | ER 4 POWER INTEGRITY SIMULATION AND MEASUREMENT                               | 9 |  |

| 4.1                      | Supply fluctuations of a generic circuit during ESD 4                         | 2 |  |

| 4.1                      | .1 Supply fluctuations in a single power domain                               | 2 |  |

| 4.1                      | .2 Interaction of multiple power domains                                      | 5 |  |

| 4.2                      | Measured and simulated supply fluctuations on a 130-nm test chip              | 0 |  |

| 4.3                      | Measured and simulated supply fluctuation transients on the 65-nm test chip 5 | 2 |  |

| 4.4                                                                      | Figures and tables                                                                  |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| CHAPTER 5 SUPPLY INSTABILITY CAUSED BY THE RAIL CLAMP                    |                                                                                     |  |  |  |

| 5.1                                                                      | Rail clamp stability analysis                                                       |  |  |  |

| 5.2                                                                      | Figures                                                                             |  |  |  |

| CHAPTER 6 POWER INTEGRITY OF INTERNALLY GENERATED SUPPLIES<br>DURING ESD |                                                                                     |  |  |  |

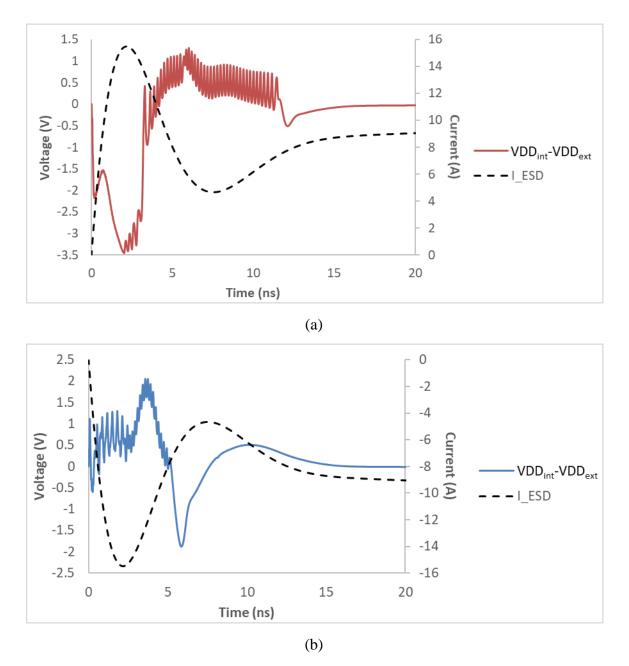

| 6.1<br>suppl                                                             | Experimental observation of ESD-induced noise on two internally regulated y domains |  |  |  |

| 6.2                                                                      | Simulation and analysis                                                             |  |  |  |

| 6.3                                                                      | Comparison of shared and separate on-chip ground nets                               |  |  |  |

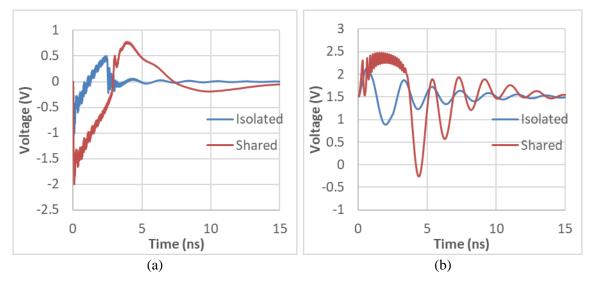

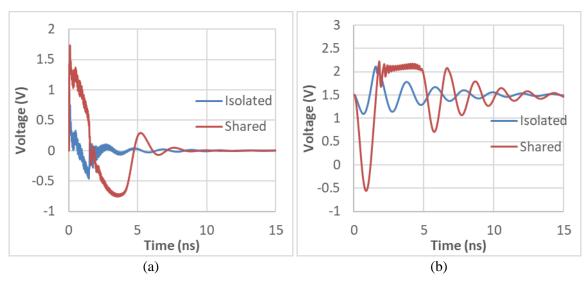

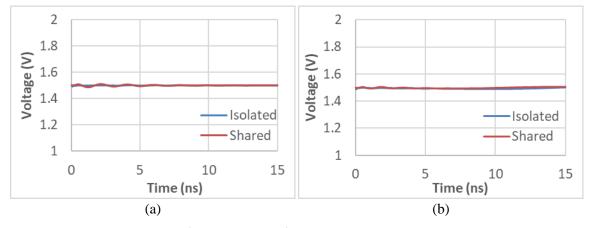

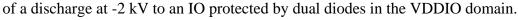

| 6.4                                                                      | Noise at the VDDIO domain                                                           |  |  |  |

| 6.5                                                                      | Figures and tables 101                                                              |  |  |  |

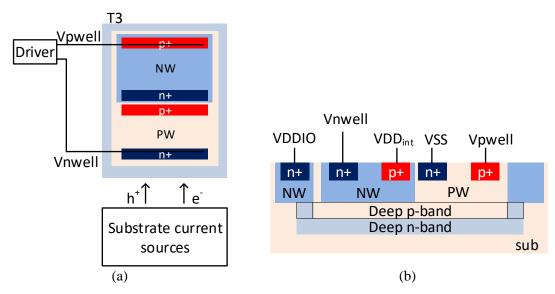

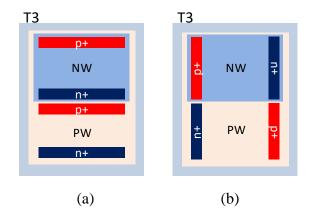

| CHAPT                                                                    | ER 7 LATCH-UP CAUSED BY SUPPLY FLUCTUATION 114                                      |  |  |  |

| 7.1                                                                      | Reverse body bias (RBB)                                                             |  |  |  |

| 7.2                                                                      | High-voltage tolerant IO                                                            |  |  |  |

| 7.3                                                                      | Figures and tables                                                                  |  |  |  |

| СНАРТ                                                                    | ER 8 MODELING OF AIR DISCHARGE CURRENT 127                                          |  |  |  |

| 8.1                                                                      | Figures                                                                             |  |  |  |

| СНАРТ                                                                    | ER 9 SUGGESTIONS FOR FUTURE WORK 131                                                |  |  |  |

| CHAPTER 10 CONCLUSION                                                    |                                                                                     |  |  |  |

| REFER                                                                    | ENCES                                                                               |  |  |  |

# LIST OF ABBREVIATIONS

| APD                | antiparallel diode                      |

|--------------------|-----------------------------------------|

| CDE                | cable discharge event                   |

| CDM                | charged device model                    |

| CMOS               | complementary metal-oxide semiconductor |

| decap              | decoupling capacitance                  |

| ESD                | electrostatic discharge                 |

| EUT                | equipment under test                    |

| VDDext             | externally generated VDD                |

| FFT                | fast Fourier transform                  |

| GD                 | glitch detector                         |

| HBM                | human body model                        |

| НСР                | horizontal coupling plane               |

| HMM                | human metal model                       |

| IC                 | integrated circuit                      |

| VDD <sub>int</sub> | internally generated VDD                |

| ORED               | out-of-range error detector             |

| РСВ                | printed circuit board                   |

| PDN                | power delivery network                  |

| PSRR               | power supply rejection ratio            |

| RBB  | reverse body bias            |

|------|------------------------------|

| SCR  | silicon controlled rectifier |

| SEED | system-efficient ESD design  |

| SOA  | safe operating area          |

| TLP  | transmission line pulse      |

| TVS  | transient voltage suppressor |

| VNA  | vector network analyzer      |

# CHAPTER 1 INTRODUCTION

Electrostatic discharge (ESD) is a concern for the reliability of all electronic systems. Static electricity can be built up by triboelectrification, which occurs during contact between two materials [1]. The charge is redistributed when the charged object contacts another object at a different electric potential. An integrated circuit (IC) in the discharge path is subject to damage due to heating or over voltage. To protect ICs from such damage, several committees (e.g. JEDEC, ESDA, IEC, ISO, etc.) have published many qualification procedures which specify that ICs must pass certain ESD target levels. These qualifications describe discharges that represent various scenarios in the manufacture, handling and operation of the ICs.

One group of these qualifications is classified as component-level ESD, such as the human body model (HBM) and charged device model (CDM). HBM testing requirements ensure that the IC is not damaged when an operator is handling a packaged IC, and CDM testing requirements ensure the IC is not damaged when a machine is handling the IC. These tests are always done when the IC is not powered. The target levels for componentlevel ESD have decreased over the years with stricter ESD control in the factory on the maximum amount of charge that can be accumulated in the environment and how the charge is dissipated. For example, electrically dissipative materials and electrostatic neutralizers are widely used.

System-level ESD describes the possible ESD hazard that occurs in a system. In this context, "system" refers to an electronic product, which is itself a broad category; examples include smart phones, automobile GPS navigation systems, power meters, and computer clusters. Widely used qualifications include IEC 61000-4-2: Electrostatic discharge immunity test, IEC 61000-4-5: Surge immunity test, ISO 10605: Road vehicles – Test methods for electrical disturbances from electrostatic discharge [2]. Each qualification targets a certain group of applications. For example, automobile electronic systems must meet ESD target levels specified by ISO 10605, and ethernet transceivers must survive in the cable discharge event (CDE) [3], [4].

In system-level ESD tests, the reaction of the equipment under test (EUT) is categorized in four classes [5]: A: EUT continues to function normally; B: EUT has an upset condition but recovers automatically; C: EUT has an upset condition and needs manual interference to recover; D: EUT is damaged. In this dissertation, Classes B and C are categorized as soft failures, while Class D is categorized as hard failures. For soft failures studied in this dissertation, it is assumed that they are caused by loss of function or data of the IC.

When the EUT is under a system-level ESD test, it may be powered off or powered on. Since the discharge occurs at the user site, there is less ESD environment control than where the ICs are assembled into the system. The challenge that system-level ESD poses to circuit design other than component-level ESD is that the amplitude of the discharging current is much higher and the system may be in operation. Hard failures to an IC can

occur during system-level ESD even though it passes the component-level ESD test [5]. A power-on system may have different behavior compared to its power-off state during ESD. The power-on system may also experience soft errors, which is not desired but essentially recoverable. A better understanding is necessary for engineers to address potential system-level ESD-related failures in the early design phase.

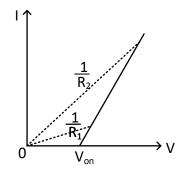

Efforts have been made to develop a co-design methodology between circuit and system design engineers to address the challenges of system-level ESD [6]. ICs are characterized with transmission line pulse (TLP) measurements and the models derived are used for prediction of the response of the EUT in system-level ESD to estimate the passing level. In the TLP measurement, a square current pulse, usually with a 10-ns rise time and a 100-ns pulse width, is injected to the IC. At the end of the pulse, when the current and voltage are stabilized, the current and voltage are measured as an average from the sampling window. The obtained current-voltage pairs at different pulse amplitudes are plotted as a quasi-static I-V curve of the IC.

However, system-level ESD pulses generally have shorter rise times and pulse widths than the TLP. Since the IC generally contains nonlinear elements with memory, its quasi-static I-V characteristics obtained from pulse measurements may depend on the rise time of the TLP. In addition, the quasi-static I-V characteristics also have self-heating effects [7]. Therefore, even for cases where the current and voltage of the IC are stabilized in system-level ESD, the I-V characteristics obtained in TLP cannot represent the quasi I-V characteristics in system-level ESD. It is not straightforward to predict the hard failure level for system-level ESD from TLP measurements due to pulse-width dependency [8], [9]. A more important concern is that many failures are related to the

transient response at the edges of the ESD pulse, and the transient behavior usually cannot be estimated from quasi-static I-V characteristics. The transient characteristics are affected by elements such as a parasitic capacitor [10]. It is important to gather information about inductances and decoupling capacitances (decaps) in the system to understand the response to system-level ESD.

One of the most commonly used qualification is IEC 61000-4-2 [11], which represents the discharge that occurs when a person holding a metal tool approaches a system that is at a different potential; the charged object may be either the person or the system. For commercial electronic products, only soft failures that do not result in degradation of performance or the performance is degraded to an unacceptable level after the test are allowed for 4 kV contact and 8 kV air discharge [12], [13]. Contact discharge is the test method where the charged electrode of the ESD tester is kept in contact with the conductive surfaces of the EUT or coupling planes; air discharge is the test method where the electrode approaches the EUT until it touches the insulating surfaces of the EUT [11].

The apparatus that is used to generate the stress is an ESD gun. For a contact discharge, the gun tip is kept in contact with a metal part of the system and then a switch is actuated; for an air discharge, the switch is actuated first and then the gun approaches the system —there is a spark when the discharge is initiated. The system is still under stress when there is no spark, since the capacitance between the EUT and the gun, which maintains the potential difference, increases as the gun approaches [14]. The discharge current waveforms resulting from contact discharge display less variability due to the absence of the spark. This dissertation focuses on contact discharge.

The ESD current waveforms obtained when testing a variety of systems may differ dramatically. The EUT constitutes the load seen by the gun, and these systems may present very different loads. Therefore, the ESD current that enters an IC within the EUT will depend on the larger system design, e.g. whether the EUT is battery operated or plugged into a power source, whether the EUT has a well-grounded shield, whether there are filtering elements at the input to the IC, etc. The accurate modeling of system-level ESD currents with different loads requires an understanding of the EUT as well as the ESD test bed.

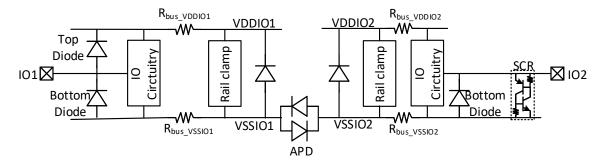

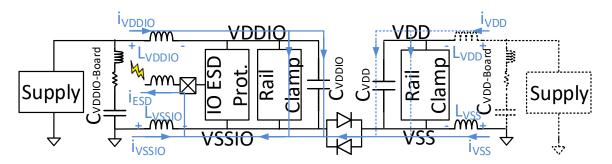

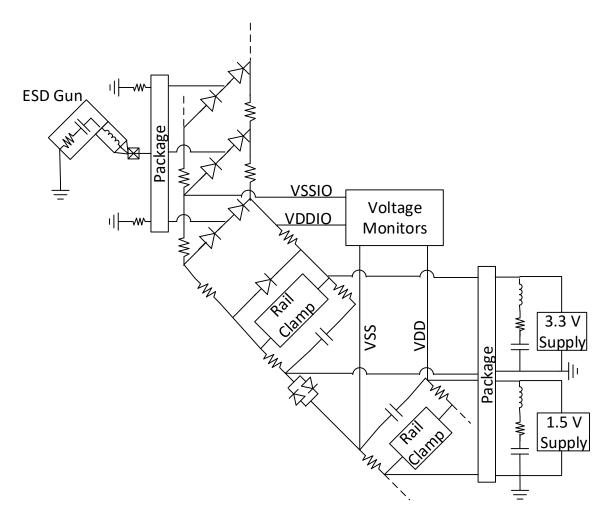

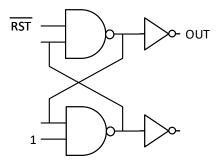

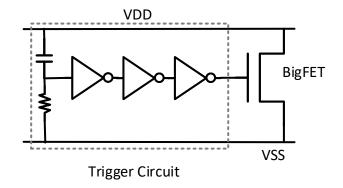

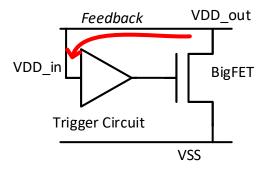

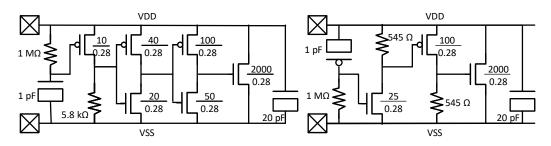

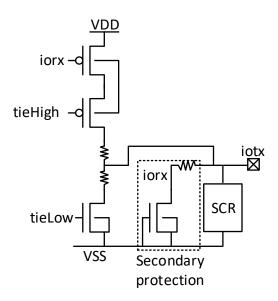

The ESD protection of an IC affects the IC's response to system-level ESD. Figure 1.1 shows a typical ESD protection scheme for a low-voltage complementary metal-oxidesemiconductor (CMOS) IC. The ESD protection circuit at an IO pin affects whether the ESD current leaves the IC through the power net or the ground net. For positive ESD currents into IO1, the top diode sends current to the power net, while the positive ESD current into IO2 goes through the silicon controlled rectifier (SCR) to the ground net. The rail clamp circuits limit the maximum possible voltage of each power domain during ESD. The reverse diodes between power and ground nets form a current path with smaller effective resistance than the other circuits when the supply is reversed. The ground nets of VDDIO1 and VDDIO2 domains are connected with antiparallel diodes (APDs). These APDs limit the maximum possible voltage for cross-domain circuitry while maintaining isolation between the two ground nets under normal operating conditions. These circuits consist of the main current path during ESD, and the choice of the protections affects the likelihood for soft failures to occur as well as hard failures. In addition, the amount of on-chip decap also plays a significant role. When the power

domain is regulated on chip, the design of the regulator needs to take into account its robustness against ESD.

Generally, the ESD current discharged in an IO exits the IC through the power nets and the ground nets. These currents then go through the power delivery network (PDN) of the system. The impedance of the system's PDN seen from the IC is not negligible, and there is a significant contribution from the package inductances. The " $L\frac{di}{dt}$ " effect of these package inductances is a concern for on-chip power integrity, which may result in soft failures, and sometimes hard failures.

## 1.1 Overview

This dissertation first addresses the modeling of the contact discharge current during system-level ESD and then studies how this current disturbs the operation of an IC with the focus on the induced supply fluctuations. The contact discharge current is modeled with distributed elements to represent the coupling between the ground strap and its environment in Chapter 2. After the discharge current is modeled, Chapter 3 illustrates the case study of upsets in the various monitors on a 65-nm CMOS test chip with different board designs. The observations indicate that the upsets come from signal input corruption as well as supply fluctuations. Then Chapter 4 discusses how the power integrity is compromised by ESD for externally regulated supply domains with the " $L \frac{di}{dt}$ " effect in particular, and Chapter 5 shows that the rail clamp in the ESD protection network can be one of the causes. The requirements for internally regulated supply domains to have robust power integrity against ESD are presented in Chapter 6. Chapter

7 shows the latch-up study of circuits using reverse body bias (RBB), where it is found that the supply fluctuation is one potential hazard leading to latch-up. In Chapter 8, a circuit model of air discharge is presented. Finally, Chapter 9 discusses future work and Chapter 10 concludes the dissertation.

# 1.2 Figures

Figure 1.1: Typical ESD protection scheme. IO1 is protected by dual diodes. IO2 is protected by an SCR and a bottom diode. Both power domains are protected by rail clamps and reverse diodes. The two VSSIO nets are connected by APDs.

# CHAPTER 2

# MODELING OF SYSTEM-LEVEL ESD TEST CURRENT

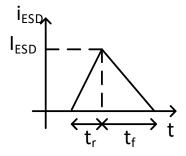

To understand how soft and hard failures occur during system-level ESD, it is important to correctly model the ESD current. Since many soft failures are related to the rising and falling edges of the ESD current pulse, the model needs to generate the amplitude, the rise and fall times of the current that match the real case. The system-efficient ESD design (SEED) methodology, as described in [6], uses circuit-level simulation to design for robustness against hard failures caused by direct contact discharge. To run the simulations, there must be available circuit models for the ESD gun, the test bed, and the EUT. EUT modeling has been described in many publications, e.g. [15], [16], [17], [18]; similarly, circuit equivalent models of ESD guns can be found in the open literature, e.g. [19], [20], [21]. Full wave modeling and simulation have been used to extract test bed models [15], but this approach is computationally intensive. More typically, the models are measurement-based [22], [23], [24].

# 2.1 IEC 61000-4-2 test setup and calibration

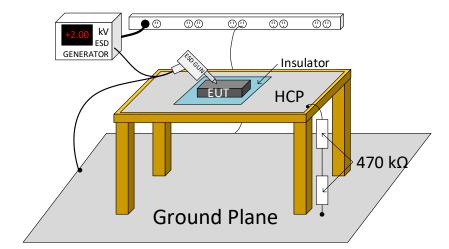

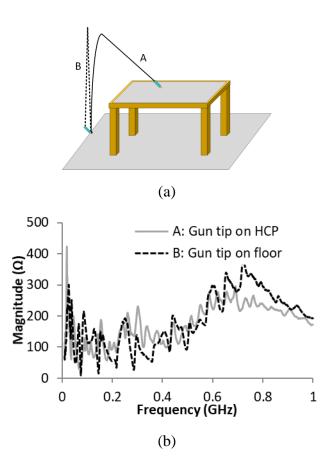

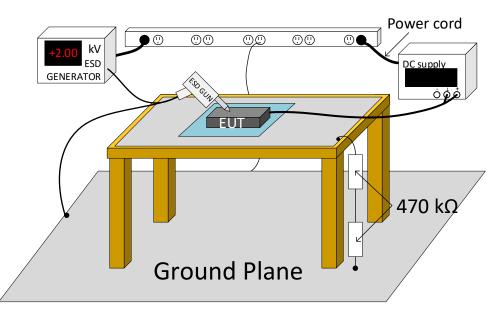

According to IEC 61000-4-2, the system-level ESD test is performed on the test bed shown in Figure 2.1. The EUT, if not required to mount on ground, is placed on the 1.6 m

by 0.8 m horizontal coupling plane (HCP). This floating metal plane is connected to the ground plane through two 470 k $\Omega$  bleeding resistors. The discharging current is generated by the ESD gun, with its ground strap connected to the ground plane. It is essentially a one-pin discharge without a clearly defined current return path.

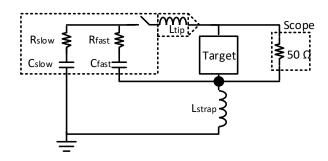

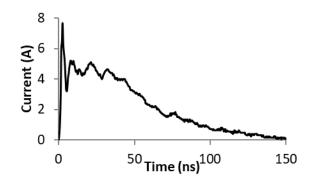

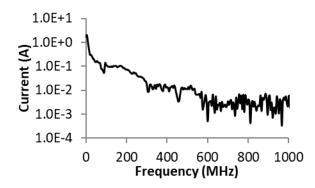

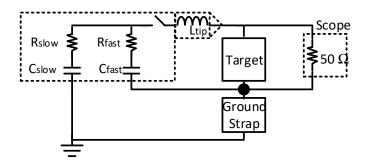

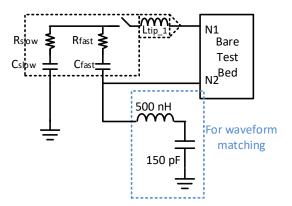

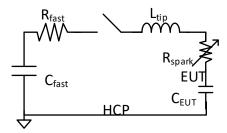

The ESD gun contains a 150-pF storage capacitor, a 330- $\Omega$  discharge resistor [25], and some pulse shaping elements. Lumped RLC models based on this RC circuit are widely used [26], [27], [28], [29]. The model shown in Figure 2.2 [21] is one of these RLC models that can be used to model the ESD gun discharging to a grounded 2  $\Omega$ target, which generates the current waveform shown in Figure 2.3 as required by the standard.  $R_{fast}$  and  $C_{fast}$  provide a first-order representation of the coupling between the gun and its environment, which in this case primarily consists of the calibration target's ground plane. These two elements would also capture the effect of (proprietary) components inside the gun added by the manufacturer to obtain an output waveform that conforms to the test standard. Representing the pulse-shaping circuitry and the coupling effects by a two-element RC model is likely an over-simplification, but is adequate for the case under consideration. The first peak shown in the figure comes from the pulseshaping elements and the parasitics, including the capacitor formed between the gun and the EUT, that gets charged along with the major discharge unit. Fast Fourier transform (FFT) of this current in Figure 2.4 shows that most current components lie below 500 MHz.

The target consists of twenty-five 51  $\Omega$  resistors, connected in parallel; the target's ground-side consists of a large metal plane. An SMA connector is mounted on the target so that measurement apparatus can be connected in parallel with the load. The voltage

across the target is measured and the current is calculated based on the impedance of the target. All other discharge currents shown in this dissertation were measured at the gun tip with an F-65A current probe. The current probe has a band-pass characteristic. Its 3-dB roll-off frequency is below 100 kHz, and it has a uniform response up to 1 GHz. In this dissertation, the target is custom made. The target's S<sub>11</sub> was measured so that any significant non-idealities could be accounted for in the simulation; the resultant data indicate that the target is more accurately represented as a 2.2  $\Omega$  resistor in series with an 8-nH inductor. The target begins to appear inductive above 44 MHz.

If the first peak of the ESD current waveform enters an IC without first being filtered, it is responsible for most of the soft failures. It may also cause hard failures resulting from the high electric field applied at the gate dielectric of the receiver. The peak current is not sensitive to the EUT characteristics; it is roughly equal to 3.75 A/kV. The rise time of the first peak depends on the system configuration, but it is usually on the scale of nanoseconds, or less. The large time-derivative of this current, di/dt, induces a strong magnetic field. This changing field induces voltages at neighboring nets and causes supply fluctuations, as will be shown in Chapter 3 and Chapter 4. The second peak of the waveform, if there is any, is mainly responsible for hard failures with its large energy injected into the system. This pulse may be longer than 100 ns, and excess carriers may accumulate in the substrate. These injected carriers may cause latch-up and data lost at high impedance nodes [30].

The current paths for the two peaks are not necessarily the same. The current of the second peak returns back to the gun through the ground strap, while the first peak is comprised primarily of displacement current flowing from the parasitic capacitances to

the EUT. Therefore, the current associated with the first peak does not necessarily flow through the ground strap [31].

The EUTs in this dissertation were placed on the HCP separated by an insulating layer. In one configuration, the EUT is not connected to earth ground (i.e., it is battery powered). This configuration is referred to as a mobile setup. In the other configuration, the EUT is connected to the earth ground directly or through another piece of equipment, referred to as a tethered setup. The second peak is much reduced in the mobile setup due to the absence of a low impedance path for current components at low frequencies.

## 2.2 Modeling approach

The modeling of the contact discharge current in system-level ESD needs the understanding of the test bed, which is the environment of the EUT. To obtain the most accurate solution, full-wave EM simulation is needed [15], [32], [27], but this requires long computation time. The current discharge waveform is a wide-band signal, and the measurement generally has "ripples" on top of a current pulse envelope. These ripples contain valuable information about the test bed. Substituting a VNA for the ESD gun allows one to characterize the impedance of the test bed over the frequency range of interest. The VNA measures the impedance at a constant input power at all selected frequencies, enhancing the accuracy of the measurements. Detailed information of the elements inside the gun is desired to obtain the gun model [23], but it is difficult to characterize the ESD gun using a network analyzer. The ESD gun contains a switch that closes only when a discharge is triggered. Therefore, the frequency-domain S-parameters of the gun must be measured when the switch is closed. If the switch is open, the S-

parameters of the gun cannot be measured without breaking the gun and performing measurements across the switch. Many works model the discharge setup with lumped RLC elements [19], [21], [33]. Due to the large size of the test bed, especially when the low-frequency current components are absent, the lumped RLC models cannot fully replicate the measured waveform. In particular, the ground strap in the setup should be treated as a transmission line [26].

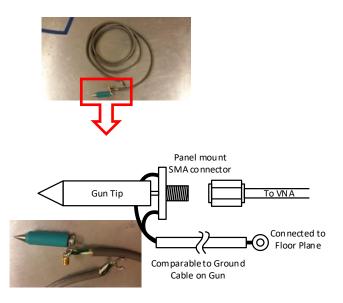

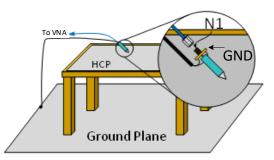

To aid the development of a distributed model of the test bed, the time-domain measurements will be augmented by frequency-domain Z-parameter measurements (here, only one port, thus  $Z_{11}$ ), obtained using a vector network analyzer (VNA) that can cover the frequency range from 10 MHz to 40 GHz. In essence, one wishes to know the load impedance seen by the ESD gun. To directly measure this quantity, the VNA is outfitted with a probe that accommodates an ESD gun tip. This special probe, referred to as a "mock gun tip," is designed to replicate the actual test setup as closely as possible [34], as shown in Figure 2.5. The mock gun tip consists of a removable ESD gun tip connected to the center conductor of an SMA connector; the shield of the SMA is directly attached to a cable whose length is comparable to that of the gun's ground strap. The far end of this cable is connected to the ground plane, as demanded by the test standard. This ensures that a similar loop area is created and presumably an equivalent inductance.

$Z_{11}$  characterizes the device-under-test connected between the SMA connector's center conductor and its shield; the SMA connector is shown in Figure 2.5. The SMA connector and the coaxial cable which connects the mock gun tip to the VNA are "calibrated out" before the  $Z_{11}$  measurement, but the mock gun tip is not de-embedded. Therefore, the gun tip and the "mock ground strap" are part of the device-under-test. It

would not be possible to accurately de-embed the gun tip and ground strap. The EUT does not have a fixed size relative to those of the gun tip and ground strap; thus, their impact on the total impedance "seen" by the gun is variable. In summary, the device-under-test for the  $Z_{11}$  measurements includes the gun tip, the ground strap, and everything between the gun tip and the ground plane. The same device-under-test is referred to as the test bed.

The IEC 61000-4-2 test standard [11] specifies that a cable must be used to connect the floor ground plane to the building's power ground; for the Z-parameter measurement, this cable is removed to eliminate ground loops. This cable adds a highly inductive path back to the gun, which conducts much less current than other paths. Current waveforms obtained with and without this cable show little difference.

After the calibration procedure is complete, the various components of the test bed are inserted one at a time, and  $Z_{11}$  is measured at each step. The measurements are first performed with a bare test bed, and then with the EUT on the HCP. In this way, the test bed model is constructed in a systematic fashion. Each time a new component is added to the system, the previously extracted model may need to be slightly modified to account for new interactions between parts of the system due to radiative or capacitive coupling. For example, the HCP together with the ground plane below it acts as a low-Q resonator. The field generated by this structure will interact with other components of the test bed, such as the ground strap, affecting their circuit-level representations.

However, at the end of this exercise, the test bed model will be fixed and can be subsequently used without any changes for a variety of different EUTs. Since the objective of this dissertation is to model direct injection through the test bed, the test bed

model does not need to be accurate above a few hundred MHz because the test bed is in series combination with the gun, which filters out frequency components above the mid-100-MHz range. The complete SEED model will represent the system consisting of ESD gun, test bed and EUT.

## 2.3 Distributed element modeling of the test bed

### 2.3.1 ESD gun

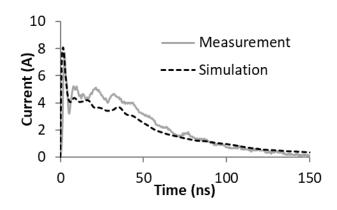

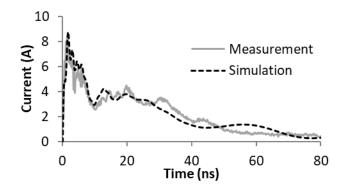

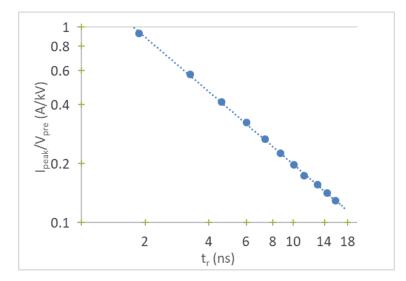

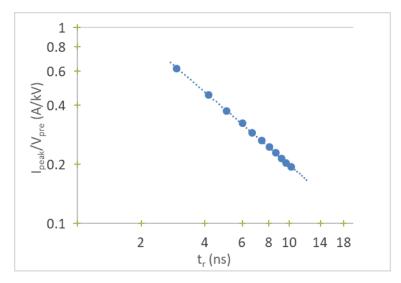

The modeling process starts with the adoption of the ESD gun model shown in Figure 2.6 and the extraction of its parameters. The model is adapted from the one shown in Figure 2.2.  $C_{fast}$  and  $R_{fast}$  are used to fit the first peak of the discharge waveform for a 2  $\Omega$  target (Figure 2.7). Since  $C_{fast}$  and  $R_{fast}$  control the higher-frequency portion of the discharge, they should be extracted with a representation of the rest of the setup that is accurate in the same frequency range. Thus, in the simulation model, the target and the ground strap are both represented by their measured Z-parameters; since the gun's ground strap cannot be removed, it is actually the ground strap from the mock gun tip that is measured. In this measurement, the mock gun tip is removed from the setup. The shield of the coaxial cable that connects to the VNA is in contact with the other end of the ground strap. At low frequencies, the ground strap is equivalent to an inductor, and the target is a 2.2  $\Omega$  resistor; while at higher frequencies, these lumped models are not appropriate. Using the  $Z_{11}$  representations for ground strap and target noticeably affects

the simulated waveform for the first 10 ns of the discharge, which is the time range over which  $C_{fast}$  and  $R_{fast}$  are extracted.

Due to the frequency limitation of the VNA, Z-parameters cannot be obtained at frequencies less than 10 MHz. This affects the low-frequency accuracy of the Z-parameter-based ground strap model, which results in a worsened match between simulation and measurement at time points in the range of 20 - 60 ns; see Figure 2.7. To improve the accuracy of this simulation, one would need a model of the ground strap that is based on both the  $Z_{11}$  measurements and the lumped impedance obtained at lower frequencies using an LCR meter. However, it is not necessary to go through this exercise since the Z-parameter-based gun strap model is used only for the extraction of  $C_{fast}$  and  $R_{fast}$ , which control only the high-frequency components of the discharge. The ground strap  $Z_{11}$  data are not used in later modeling, since the gun strap is incorporated into the  $Z_{11}$  measurement of the whole test bed.

As an additional check on the validity of the model, the ESD gun was discharged into a 510  $\Omega$  load formed by ten parallel 5.1 k $\Omega$  resistors. The current is measured with a current probe. Using the gun model of Figure 2.6, the discharge waveform was simulated and the result is shown in Figure 2.8, along with the measured waveform. The overall fit to measurement is fairly good. The first peak of the simulated current is higher than the measured one, but the discrepancy is not necessarily due to any shortcoming of the model. The imaginary part of the measured impedance of the target changes its polarity at around 400 MHz, indicating a series resonance caused by the resistors' package capacitance and lead inductance, so it is almost a short termination at that frequency, which will compromise the accuracy of the S-parameter measurement. Since the S-

parameter data are used to represent the target in this simulation, the measurement error could result in simulation overestimating the first current peak, as this consists of frequency components close to 400 MHz.

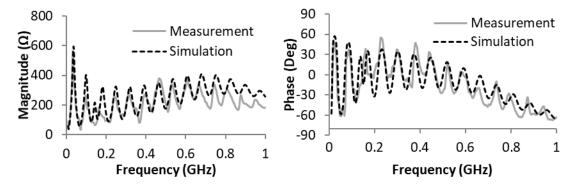

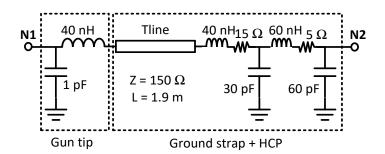

#### 2.3.2 Bare test bed

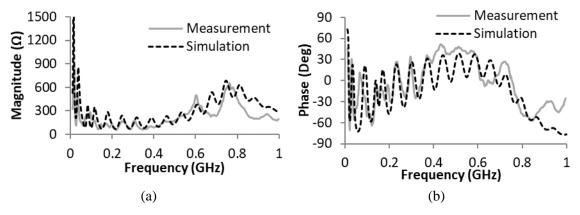

The input impedance of the bare test bed, which includes the gun tip, the HCP and the ground strap, is obtained by measuring  $Z_{11}$  between the points labeled N1 and GND in Figure 2.9. The mock gun tip probe is used for this measurement. N1 (node 1) is the point where the gun tip connects to the SMA cable, and GND is where the mock ground strap connects to the shield of the SMA cable; the SMA cable is connected to the VNA. The measurement results are plotted in Figure 2.10. A resonance is observed approximately every 70 MHz. The resonant behavior is attributed to the ground strap. A transmission line can capture this resonant behavior, because its impedance is a periodic function of frequency when there is an unmatched load. An empirical model of the test bed is formulated based on the Z-parameter data, and it is shown in Figure 2.11.

To gain insight into the mapping between the elements of the model and the physical test bed and, in particular, to determine the source of the resonances, additional experiments are performed. A longer ground strap cable is connected to the mock gun tip, and the test bed  $Z_{11}$  is measured two times: once, with the gun tip at the center of the HCP as before ("A" in Figure 2.12), and once with the gun tip touching the ground plane while the ground strap is pulled tight as indicated in the ESD test specification ("B" in Figure 2.12). Resonance now occurs roughly every 40 MHz, which indicates that the impedance of the test bed is strongly influenced by resonance in the ground strap cable. A

resonance occurs whenever the frequency is such that an integer multiple of halfwavelengths equals the cable length.

A comparison of the curves labeled "A" and "B" in Figure 2.12(b) reveals that the impedance at frequencies above 50 MHz is not sensitive to whether the gun tip is placed on the HCP (open at DC, like a capacitor) or placed on the floor plane (DC short). The HCP and the ground plane both act like the "shield" of the ground strap. At low frequencies, the impedance associated with the coupling from the HCP to its environment contributes significantly to the total impedance of the test bed. This effect is captured by the RLC elements in Figure 2.11. These elements also account for the non-uniformity of the transmission line formed by the ground strap and its environment, which is not captured by the transmission line element in the model.

The Z-parameter data of Figure 2.11 suggest a smaller value for  $L_{tip}$  than was extracted when the gun model of Figure 2.6 was fit to the waveform of Figure 2.7. The mock gun tip probe used for Z-parameter measurements includes the physical gun tip, so it is conjectured that part of the  $L_{tip}$  shown in Figure 2.6 is actually located inside the gun assembly.

The bare test bed model was derived using frequency-domain measurement data that were obtained without the actual gun body included in the setup. The size of the gun is not negligible, and therefore time-domain current waveforms of gun discharges to the HCP, as shown in Figure 2.13, are used to refine the model. This discharge does not involve any additional object that needs to be modeled. The combined model of the ESD gun and bare test bed is shown in Figure 2.14. The ESD gun model is connected to the bare test bed model at both node 1 (N1) and node 2 (N2). N2 represents the edge of the

HCP. This facilitates the representation of coupling between the ESD gun and the HCP. When the bare test bed and ESD gun models are integrated together, current through the gun's  $C_{fast}$  element is directed to N2. Note that while the coupling between the gun and the HCP is considered, coupling between the gun and the floor ground plane is not. Coupling between the gun and ground plane is assumed to be negligible because the gun is centered above the HCP and is small compared with the HCP. Therefore, the E-field lines from the gun will terminate on the HCP. A lumped LC circuit is added between N2 and ground in Figure 2.14 to account for current flow through the test bed back to the gun due to capacitive coupling between the gun and the HCP. The parameters of the lumped LC circuit are based on the geometry of the gun and its height above the HCP.

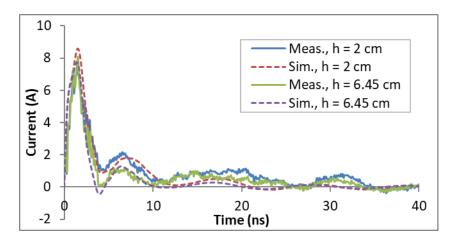

## 2.4 System-level ESD current into an EUT

Taken together, the ground plane of EUT and the HCP form a capacitor. The capacitance depends on the geometry of the EUT. Simulation and measurement results are compared for discharges to an EUT consisting of a 13.5-cm by 13.5-cm FR-4 circuit board first described in [35]. The discharge location is at a USB connector shield, which is connected to the ground plane of the EUT. The capacitance between EUT and HCP is estimated based on the area of the circuit board and its height above the HCP, assuming an infinitely large HCP. The effect of parallel-plate and the fringing capacitance are both included. By inserting this capacitor in the current return path, the model can reasonably well predict the current injected into the EUT from the gun, as shown in Figure 2.15. It is observed that the rise time and magnitude of the peak current are not sensitive to the vertical separation of the EUT from the HCP. Different from the current waveform

obtained from discharging into the 2- $\Omega$  calibration target, the second current peak is absent. This is expected because, in this mobile setup, the DC current path has a high impedance, consisting of the bleeding resistors. As a result, the second peak is only a small residual current, which decreases as the vertical separation of the EUT from the HCP increases.

When the EUT is placed very close to the HCP, such as a smartphone lying flat on the HCP, the capacitance between the EUT and the HCP is large due to the small spacing. The current waveform measured at the ESD gun tip approaches the one obtained when ESD current is discharged to the HCP directly, as shown in Figure 2.13.

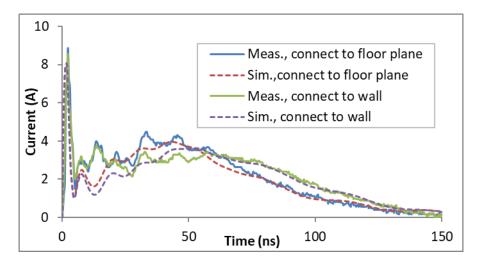

A tethered EUT has a path for the current to return to the gun through the power cord of a DC supply as shown in Figure 2.16. The DC supply used here is HP E3631A. Zparameter measurement data are used to find the input impedance of the tethered EUT; the results are shown in Figure 2.17. There are two sources for cable resonance, which are the ground strap and the power cord, but the ground strap has the stronger influence, since the wave on the cable of the supply needs to travel a longer distance before returning to the gun and therefore has higher loss. The power cord of the supply mainly contributes a low impedance path at low frequencies.

Due to the bandwidth limitations of the VNA, the precise inductance of the return path through the power supply cannot be extracted from the  $Z_{11}$  data; instead, the inductance is estimated based on the loop area formed by the power cord and then its value is refined to match the time-domain waveform. Note that the inductance along the return path through the EUT's power supply does not have a fixed value. A value of 5  $\mu$ H is extracted when the power supply is directly grounded to the ground plane by connecting

the ground prong of the power cord of the supply to the ground plane with copper tape, and the power is off. A larger value, 8  $\mu$ H, is extracted when the power supply is grounded at the wall outlet. The result is unsurprising as the loop size is larger in the second case. The simulated waveforms are shown in Figure 2.18. The first current peak is not sensitive to the placement of the tether. In contrast, making the loop area larger results in a lower amplitude of the second current peak with a longer trailing edge.

# 2.5 Figures

Figure 2.1: IEC 61000-4-2 test setup. The figure is taken from [36].

Figure 2.2: Lumped RLC model for IEC 61000-4-2 tester (ESD gun) discharging into a 2  $\Omega$  target.  $C_{slow}$  and  $C_{fast}$  are precharged to the ESD voltage level, typically on the order of kilovolts.

Figure 2.3: Measured current of IEC stress into a 2  $\Omega$  target.

Figure 2.4: FFT of current of an IEC discharge into a 2  $\Omega$  target.

Figure 2.5: Mock gun tip used for Z-parameter characterization of the IEC test setup.

Figure 2.6: Gun model.  $R_{slow} = 330 \Omega$ ,  $C_{slow} = 150 \text{ pF}$ ,  $R_{fast} = 238 \Omega$ ,  $C_{fast} = 5 \text{ pF}$ ,  $L_{tip} = 140 \text{ nH}$ . Ground strap is described by its measured  $Z_{11}$ .

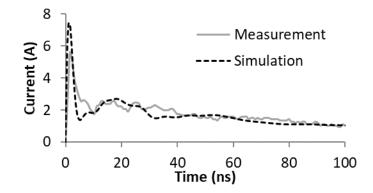

Figure 2.7: Discharge into a calibration target. Measured and simulated current waveforms. The model is shown in Figure 2.6.

Figure 2.8: Discharge into a 510  $\Omega$  target. Measured and simulated current waveforms. The model is shown in Figure 2.6.

Figure 2.9: Measurement setup of the bare test bed. The VNA measures  $Z_{11}$  between N1 and GND.

Figure 2.10: Measured and simulated  $Z_{11}$  of the bare test bed looking through the mock gun tip probe of the VNA.

Figure 2.11: Model of the bare test bed with gun tip, HCP and ground strap.

Figure 2.12: (a) Test setups for measuring the impedance of the longer ground strap in various positions. (b) |Z<sub>11</sub>| as seen looking through the mock gun tip probe of the VNA. Ground strap length is longer than that for the dataset of Figure 2.9. Two different test setups are characterized.

Figure 2.13: Current waveforms for an ESD gun discharge to the bare test bed.

Figure 2.14: Model of gun and bare test bed.

Figure 2.15: Measured and simulated ESD gun discharge current in mobile setup onto the ground plane of a 13.5-cm by 13.5-cm FR-4 circuit board at various heights above the HCP.

Figure 2.16: The tethered EUT under the system-level ESD test. The ground plane of the EUT is connected to the ground node of a DC supply. The power cord of the DC supply contains a ground wire. In the experiment, the supply is off and the ground wire is plugged into the outlet on the wall or in contact with the ground plane.

Figure 2.17: Input impedance (a) magnitude and (b) phase seen between N1 and ground for the tethered EUT.

Figure 2.18: Measured and simulated ESD gun discharge current in tethered setup onto the ground plane of a 13.5-cm by 13.5-cm FR-4 circuit board at various tether locations.

# CHAPTER 3

## INTERFERENCE OF SYSTEM-LEVEL ESD WITH THE OPERATION OF AN IC

System-level ESD can interrupt the normal functionality of the system in many ways. The near-field coupling between the gun and the EUT generates noise at signal traces. The fast-changing current transients also create noise at signal inputs by magnetic coupling and direct injection. The large magnitude of the time derivative of the injected current into the chip presents a problem for packages with large inductances. These packages include most wire-bond ones as well as the flip-chip ones with long traces of package routing. The on-chip ESD protection directs the ESD current to the on-chip PDN, and the inductances of the package connecting the on-chip PDN to the system's PDN lead to a difference of power and ground potential between the chip and system. This means that inputs that are referenced to the system ground may not be interpreted correctly by the IC which has a different ground reference potential, even if the input signal does not have noise coupled onto it. These effects are described in [35] and [37].

Even if the printed circuit board (PCB) design provides good isolation between traces, eliminating magnetic and capacitive coupling between traces, the signal inputs are still subject to noise coupling at the package level, including the magnetic coupling from supply/ground bond wires since they are part of the main current return path.

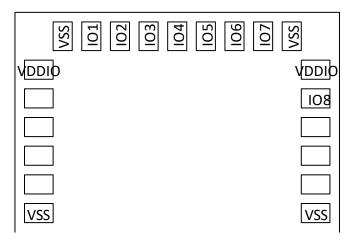

#### 3.1 Case study of a 65-nm CMOS test chip

A test chip was fabricated in 65-nm CMOS technology to investigate the effect of ESD on signal integrity. The power supply for the IO circuits, VDDIO, is 2.5 V, while the rest of the circuitry uses a 1.2 V supply, VDD. The two supplies share a common ground net, VSS. Most of the IOs for the experiments described in this section are located along one edge of the chip, as shown in Figure 3.1. There are two pairs of VDDIO-VSS pads at the two corners of the chip, and two more VSS pads are located five pads away from either of the VDDIO pads. Under the VDDIO pads are located rail clamps for the VDDIO domain. The VSS pad cells at the corners contain decaps for the VDDIO domain. The IO circuitry is described in Table 3.1. Many of the IOs contain a glitch detector (GD) to capture disturbances during ESD, specifically those in which the signal voltage crosses the switching threshold of the input circuitry. One of the IOs contains an out-of-rangeerror detector (ORED) [38] which can detect if the input goes above the on-chip VDDIO or below the on-chip VSS potentials. Potentially, the ORED output signal could be used to alert the system to the occurrence of ESD, thereby enabling it to take prompt corrective action. One of the IOs contains multiple low-pass filters; these act upon the input signal in parallel. Specifically, there are four analog RC filters with time constants of 3.2 ns, 10 ns, 32 ns, and 100 ns, as well as a digital filter driven by a 100 MHz clock that is generated on chip. The filters are in the VDD domain. The filters' outputs may be used to discern the time duration of ESD-induced glitches. For the input with the digital filter, timing between the glitch and the clock edge is important, and this effect would result in a higher rate of glitches to be observed than the input after the 100-ns analog filter.

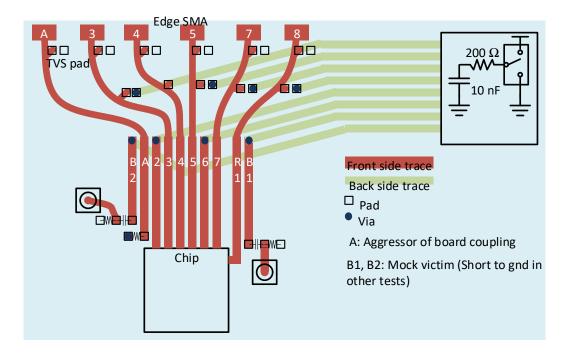

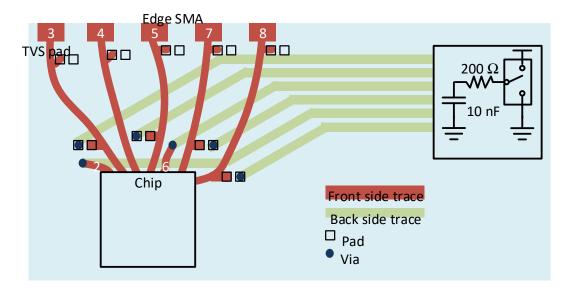

Two PCBs were fabricated for this chip, as shown in Figure 3.2, to study the effect of board-level coupling on the likelihood of glitch occurrences during ESD. Both boards contain traces that connect the IO3, 4, 5, 7 and 8 pins to the test pads at the board edge. In the experiment, the ESD current is injected to one of the test pads. The number on the traces refer to the number of the IOs they are connected to; e.g., trace labeled "2" is connected to IO2. On Board 1, the traces are close to each other (8 mil spacing over a distance of 2 in); on Board 2, the traces are far apart and isolated from one another by a big metal shape connected to the ground plane so that the coupling effect between these traces are minimized. When an IO is configured as a victim subject to the noise from a neighbor being stressed, the IO is connected to a trace on the back side. All the back-side traces are connected to a single circuit that generates the input to the IOs. This circuit consists of a switch followed by a low-pass RC filter. The switch connects the input to the VDDIO plane or the ground plane on board. The back-side traces on Board 2 are connected to the chip at a closer location than those on Board 1. This helps to further filter the disturbance from the coupling of the ESD gun to the input traces.

### 3.2 Measurement results of data upsets on the 65nm test chip

ESD gun discharges were applied at the test pads, using a mobile configuration. Table 3.2 shows the comparison of the minimum IEC levels needed to induce a glitch captured by the GDs on the two boards when discharging to the test pads connecting the IOs. When the test chip is mounted on Board 2, ESD currents to an IO induce fewer glitches at a neighboring IO than they do on Board 1, but the overall robustness, which is mostly

under 2 kV, still needs further improvement. The Board 2 design minimizes the noise contribution from board-level coupling, but the noise is still coupled through bond wires in the package. The voltage induced on bond wires by fast changing ESD current leads to a potential difference between ground reference on-board and on-chip, and signals referenced to board ground are not correctly interpreted by the chip. Furthermore, the results suggest that the package and chip-level effects produce noise that is of comparable magnitude to that generated on the circuit board. Coupling between bond wires, which is mostly inductive coupling, depends on the distance between the victim IO (i.e. the IO experiencing glitches) and the zapped IO (the IO receiving the ESD current). The general trend is that IOs progressively farther from the zapped IO are less likely to experience a glitch. IO8, the IO on the far right, with its bond wire orthogonal to those of the other IOs in VDDIO domain, is the most robust against glitches. The distance between the victim IO and the VDDIO-VSS pair is another significant factor, since the bond wires connected to the power and ground also belong to the major current path. For glitches that are caused by the difference between off-chip and on-chip supply and ground potentials, the impact should increase as the IOs get farthar away from the VDDIO-VSS pair, since the current directed to VDDIO or VSS by the ESD protection at the stressed IO generates a voltage drop along its path toward the VDDIO or VSS pin with the bus resistance of the path. In addition, on this test chip, the victim IOs and the stressed IOs are located within the same two VDDIO-VSS pairs except IO8. Out-of-range errors, as shown in Table 3.2, are caused by the same mechanism as glitches. These errors caught by the ORED also start to appear well below 2 kV.

Table 3.3 shows the minimum IEC level needed to trigger a glitch when the input is low-pass filtered before being received at the GD. For higher ESD levels, the results are shown in Table 3.4. It is observed that glitches occur for a range of ESD levels and the likelihood of detecting a glitch does not increase monotonically with the ESD level. It is also noted that the results provided by the GD that follows the 100-ns analog filter do not agree with those from the GD that follows the digital filter. Specifically,  $+0 \rightarrow 1$  glitches are reported by the GD that follows the digital filter at ESD levels above 3.5 kV but not by the GD that follows the 100-ns analog filter; furthermore,  $+1 \rightarrow 0$  glitches at 3 kV and 6 kV are only reported by the GD that follows the digital filter. In addition, it is expected that if a GD that follows an RC filter reports a glitch, all the other GDs that follow filters with smaller RC time constants will also report the glitch. However,  $+1 \rightarrow 0$  glitches reported by the GDs that follow the analog (RC) filters do not show this consistency. Positive ESD currents into the chip also induce many more upsets than do negative ESD currents, but noise induced by magnetic coupling between the traces and bond wires tend to cause glitches with comparable likelihood for both polarities of ESD currents. This implies that a mechanism other than magnetic coupling contributes to the occurrence of glitches.

It is suspected that the VDD supply on-chip collapses at ESD levels over 2 kV and that this is one of the sources of the anomalous results, specifically, the nonmonotonic relationship between ESD level and glitch detection, the inconsistent results between the GD which follows the 100-ns analog filter and the one that follows the digital filter and the dependence on the polarity of discharge. The input signal generated off-chip enters the chip through a Schmitt trigger and a level shifter in the VDDIO domain, and then

through buffers and a filter to the GD in the VDD domain. It is not clear which part of the circuitry is affected by the global on-chip supply noise. Based on the dependence of observed glitch on ESD current polarity, supply noise in the VDD domain is likely to cause loss of function of these GDs, which will be shown in Chapter 4.

Different from the results shown in Table 3.4, the results in Table 3.3 show a monotonic relationship between ESD level and detected glitches and the analog and digital filters appear to work equally well. Furthermore, the glitches have only a weak dependency on the polarity of the discharge. This observation suggests that the supply noise in the VDD domain is not strong enough to significantly disturb the function of the GDs below 2.5 kV, and that the GDs are accurately reporting on the occurrence of glitches. No glitches are reported for inputs that pass through RC filters with a time constant of 10 ns or longer which suggests that the noise duration is less than 10 ns.

Previous studies [35], [36] have shown that adding a transient voltage suppressor (TVS) to the signal line that may be subject to contact discharge can significantly reduce the impact of ESD on other inputs, since the TVS can sufficiently shunt the ESD current away from entering the IC. Similar experiments were performed on this system, where a TVS was added close to the test pad connected to IO4, and the vulnerability of the other IOs to the noise induced by contact discharge at this test pad is compared with the experiments when there is no TVS. The results are shown in Table 3.5.

The TVS used is rated for 15 kV contact IEC protection for 2.5 V IOs. The trigger voltage for this TVS is +3.1 V/-0.7V according to the data sheet, which is slightly lower than the on-chip protection in both positive and negative ESD. The TVS does increase the minimum IEC level to cause a glitch in almost all the cases, but the improvement has

polarity dependency, with limited effectiveness for  $-0 \rightarrow 1$  (negative ESD causing  $0 \rightarrow 1$ data transition) glitches and  $+1 \rightarrow 0$  glitches (positive ESD causing  $1 \rightarrow 0$  data transition). The reduced improvement compared with previous work indicates that for low voltage IOs with a reduced noise margin, the TVS has a limited effect on preventing soft input data errors during system-level ESD. It has been shown in [37] that  $-0 \rightarrow 1$  and  $+1 \rightarrow 0$ glitches are induced by the leading edge of the first current peak of the discharge. The turn-on speed of the TVS is finite, and the induced voltage at the package inductance of the TVS increases the total voltage across this component. Since the trigger voltages of the TVS and the ESD protections at the IOs are similar, the TVS has limited capability to instantly shunt the current away from the IO at the leading edge of the ESD current. Once the current enters the IO, the fast rate of the current change results in the glitches. After the leading edge, the TVS is on and most of the current is discharged through it. Therefore, the decreasing magnitude of the discharge current induces a lower voltage across the package inductances of the chip than the case without the TVS, and the chip becomes more robust to glitches.

#### 3.3 Summary of the observations

The measurement results illustrate the difficulties to prevent soft failures on the 65-nm test chip. It is suggested that the glitches due to the magnetic coupling between traces and bond wires are widespread among the low-voltage IOs due to their reduced noise margin, and the disturbances caused by the coupling do not immediately vanish when the victim IO moves away from the stressed one. The coupling of the package inductances is strong enough to trigger glitches below 1 kV. The TVS at the stressed IO may not be as efficient

to protect the signal integrity of the victim IOs as the case with high-voltage IOs. The power integrity starts to be compromised below 4 kV with the low supply voltage onchip.

### 3.4 Figures and tables

Figure 3.1: Pad assignment of the 65-nm test chip.

Table 3.1: Description of 2.5 V IOs on the 65-nm test chip. All receivers have a Schmitt trigger front-end except for the one at IO3.

|     | ESD protection level (HBM) | Circuitry                                        |

|-----|----------------------------|--------------------------------------------------|

| IO1 | 8 kV                       | Receiver                                         |

| IO2 | 2 kV                       | Receiver with GD                                 |

| IO3 | 8 kV                       | Receiver with ORED attached.                     |

| IO4 | 8 kV                       | Transmitter                                      |

| IO5 | 8 kV                       | Receiver whose input is sent to multiple filters |

| IO6 | 2 kV                       | Receiver with GD                                 |

| IO7 | 8 kV                       | Receiver with GD                                 |

| IO8 | 8 kV                       | Receiver with GD                                 |

(a)

(b)

Figure 3.2: Two board designs with different trace layouts for the 65-nm test chip. The front side traces are always connected to the IOs. (a) Traces on the front side are closely coupled to each other; (b) traces on the front side are isolated from each other by shapes connected to the ground plane. A TVS may be placed on board across the TVS pads. An

IO is configured as a victim when a  $0-\Omega$  resistor at the two pads close to each other connects the IO to the back side trace; the IO is configured is configured as a zapped IO when it is not connected to the back side trace.

Table 3.2: Minimum IEC level (kV) to trigger a glitch or out-of-range error with more than 50% possibility when discharging at test pads connected to IO3 and IO7 five times for the 65-nm test chip in the mobile setup. ORED\_H: input voltage is higher than VDDIO voltage; ORED\_L: input voltage is lower than VSS voltage.

| Board 1  | 0→1 |     |          |     | 1→0      |     |          |     |

|----------|-----|-----|----------|-----|----------|-----|----------|-----|

| Stressed |     |     | Negative |     | Positive |     | Negative |     |

| 10       | IO3 | IO7 | IO3      | IO7 | IO3      | IO7 | IO3      | IO7 |

| IO2      | 0.5 | 0.5 | 0.2      | 0.5 | 0.5      | 0.5 | 0.2      | 0.2 |

| IO5      | 0.2 | 0.2 | 0.2      | 0.2 | 0.2      | 0.2 | 0.2      | 0.2 |

| IO6      | 1   | 1   | 1        | 0.5 | 0.5      | 0.5 | 0.5      | 1   |

| IO8      | 1   | 0.2 | 1        | 0.2 | 1        | 0.2 | 1.5      | 0.2 |

| ORED_H   | NA  | 0.5 | NA       | 0.5 | NA       | 0.2 | NA       | 0.2 |

| ORED_L   | NA  | 0.2 | NA       | 0.2 | NA       | 0.5 | NA       | 0.5 |

| Board 2  | 0→1      |     |          |     | 1→0      |     |          |     |

|----------|----------|-----|----------|-----|----------|-----|----------|-----|

| Stressed | Positive |     | Negative |     | Positive |     | Negative |     |

| 10       | IO3      | IO7 | IO3      | IO7 | IO3      | IO7 | IO3      | IO7 |

| IO2      | 0.5      | 1*  | 0.5      | 1.5 | 0.2      | 1   | 0.2      | 1   |

| IO5      | 1        | 1   | 0.5      | 1   | 0.5      | 1   | 0.5      | 1   |

| IO6      | 1        | 0.5 | 1        | 0.5 | 0.5      | 1   | 0.5      | 0.5 |

| IO8      | 2        | 3   | 1.5      | 2   | 1.5      | 1.5 | 1.5      | 2.5 |

| ORED_H   | NA       | 0.5 | NA       | 1   | NA       | 0.2 | NA       | 0.2 |

| ORED_L   | NA       | 0.2 | NA       | 0.2 | NA       | 1   | NA       | 1   |

\*Discharging into IO7 at +1.5 kV does not cause IO2 to upset with more than 50% possibility.

Table 3.3: Minimum IEC level (kV) to trigger a glitch in more than 50% of trials when the signal is filtered before reaching the GD circuit. Discharges were applied to test pads connected to IO3 of the 65-nm test chip on Board 2 in the mobile setup.

| Board 2  | $0 \rightarrow 1$ |      |          |      | 1→0      |      |          |      |

|----------|-------------------|------|----------|------|----------|------|----------|------|

| Stressed | Positive          |      | Negative |      | Positive |      | Negative |      |

| 10       | IO3               | IO7  | IO3      | IO7  | IO3      | IO7  | IO3      | IO7  |

| 0 ns     | 1                 | 0.5  | 0.5      | 0.2  | 0.5      | 1    | 0.5      | 1    |

| 3.2 ns   | 1                 | 1    | 1.5      | 2    | 2        | >2.5 | 2.5      | >2.5 |

| 10 ns    | >2.5              | >2.5 | >2.5     | >2.5 | >2.5     | >2.5 | >2.5     | >2.5 |

| 32 ns    | >2.5              | >2.5 | >2.5     | >2.5 | >2.5     | >2.5 | >2.5     | >2.5 |

| 100 ns   | >2.5              | >2.5 | >2.5     | >2.5 | >2.5     | >2.5 | >2.5     | >2.5 |

| Digital  | >2.5              | >2.5 | >2.5     | >2.5 | 2.5      | >2.5 | >2.5     | >2.5 |

| Table 3.4: Same experiment as for Table 3.3 except that IEC levels are higher: $\pm 3 \text{ kV}$ ,    |

|--------------------------------------------------------------------------------------------------------|

| $\pm$ 3.5 kV, $\pm$ 4 kV, and $\pm$ 6 kV. The ESD levels at which glitches are noted are listed in the |

| table.                                                                                                 |

| Board 2 | 0→1          |           | 1→0          |          |  |  |

|---------|--------------|-----------|--------------|----------|--|--|

|         | Positive     | Negative  | Positive     | Negative |  |  |

| 3.2 ns  | 3, 3.5, 4, 6 | 3.5, 4, 6 | 3, 3.5, 4, 6 | 3.5, 6   |  |  |

| 10 ns   | none         | none      | 3, 3.5, 4, 6 | none     |  |  |

| 32 ns   | 3.5, 4       | none      | 3, 3.5, 4    | none     |  |  |

| 100 ns  | 3            | none      | 3.5, 4       | none     |  |  |

| Digital | 3, 4, 6      | none      | 3, 3.5, 4, 6 | none     |  |  |

Table 3.5: Minimum IEC level (kV) to trigger a glitch or out-of-range error with more than 50% possibility when discharging to the test pad connected to IO4 with and without TVS protection on the 65-nm test chip in mobile setup. ORED\_H: input voltage is higher than VDDIO voltage; ORED\_L: input voltage is lower than VSS voltage.

| Board 1 | 0→1      |        |          |        | 1→0      |        |          |        |

|---------|----------|--------|----------|--------|----------|--------|----------|--------|

|         | Positive |        | Negative |        | Positive |        | Negative |        |

|         | w/o      | w/ TVS |

|         | TVS      |        | TVS      |        | TVS      |        | TVS      |        |

| IO2     | 0.5      | >2     | 0.2      | 1      | 0.5      | 1.5    | 0.2      | >2     |

| IO5     | 0.2      | >2     | 0.2      | 0.5    | 0.2      | 0.2    | 0.2      | 1.5    |

| IO6     | 0.5      | >2     | 0.5      | 1      | 0.5      | 2      | 0.2      | >2     |

| IO7     | 0.5      | >2     | 0.5      | 1.5    | 0.2      | 1      | 0.2      | >2     |

| IO8     | 0.5      | >2     | 1        | >2     | 0.5      | 2      | 0.5      | >2     |

| ORED_H  | 0.5      | 2      | 0.2      | 1      | 0.2      | 0.2    | 0.2      | 0.2    |

| ORED_L  | 0.2      | 0.2    | 0.2      | 0.2    | 0.2      | 1      | 0.5      | 2      |

| Board 2 | 0→1        |        |            |        | 1→0        |        |            |        |

|---------|------------|--------|------------|--------|------------|--------|------------|--------|

|         | Positive   |        | Negative   |        | Positive   |        | Negative   |        |

|         | w/o<br>TVS | w/ TVS |

| IO2     | 1          | >2     | 1          | 1.5    | 0.2        | 1.5    | 1          | 2      |

| IO5     | 0.5        | >2     | 0.5        | 1      | 0.2        | 1      | 1          | >2     |

| IO6     | 1          | >2     | 1          | 1.5    | 0.5        | 1.5    | 1          | >2     |

| IO7     | 1          | >2     | 1          | >2     | 0.5        | >2     | 1          | >2     |

| IO8     | 1          | >2     | 1          | >2     | 0.5        | >2     | 1          | >2     |

| ORED_H  | 0.5        | 2      | 0.5        | 1.5    | 0.2        | 0.5    | 0.2        | 0.5    |

| ORED_L  | 0.2        | 0.2    | 0.2        | 0.5    | 0.5        | 2      | 0.5        | >2     |

## CHAPTER 4

# POWER INTEGRITY SIMULATION AND MEASUREMENT

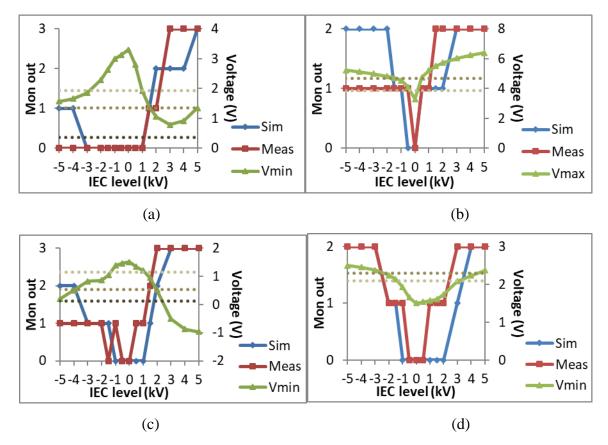

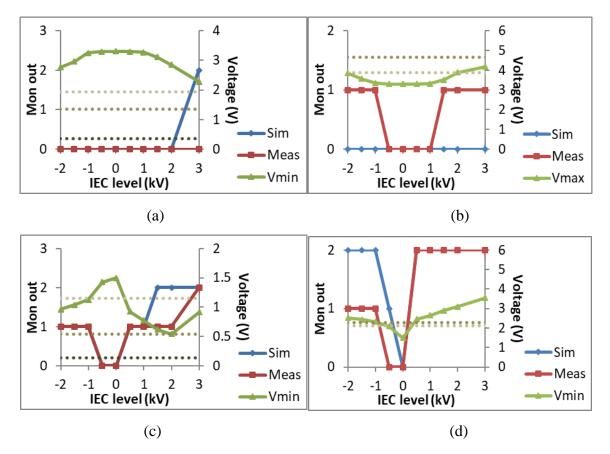

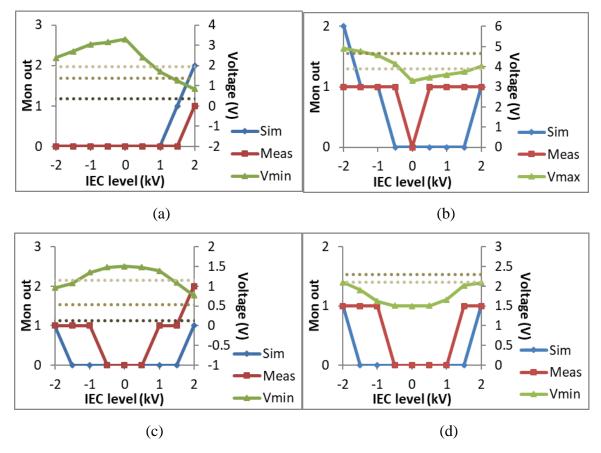

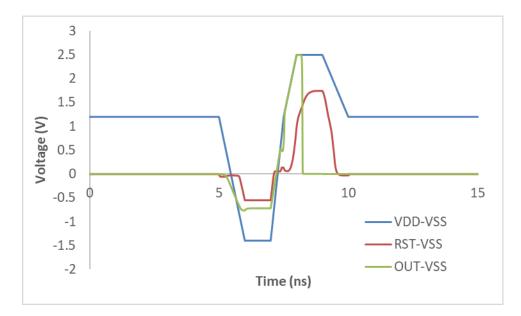

Previous experiment observations (see Table 3.4) have suggested that large amplitude noise may be induced on the on-chip PDN during ESD. This presents a global threat to the proper functioning of the IC rather than having the threat confined to the IOs subject to the ESD current injection or their neighbors. For cases where the large-amplitude ESD current enters the IC with a non-ideal system PDN, this is very likely to occur. If it is desired to detect soft errors and correct them on the hardware or software level, it is important to understand how the on-chip supply is affected in order to design robust circuitry to work in the presence of the supply disturbance or to have detection circuitry to identify such disturbances.

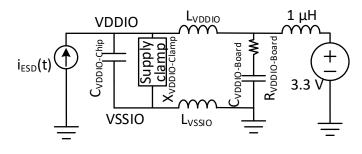

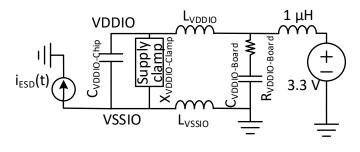

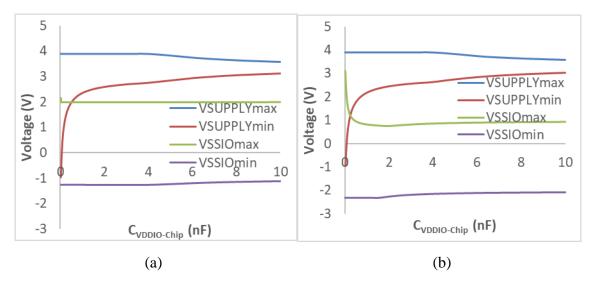

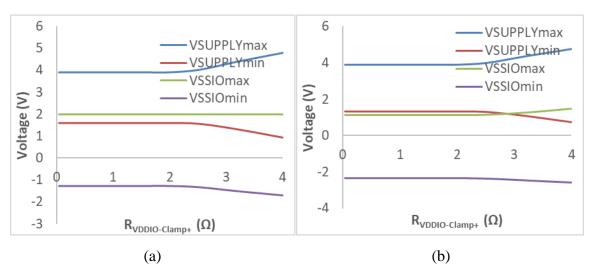

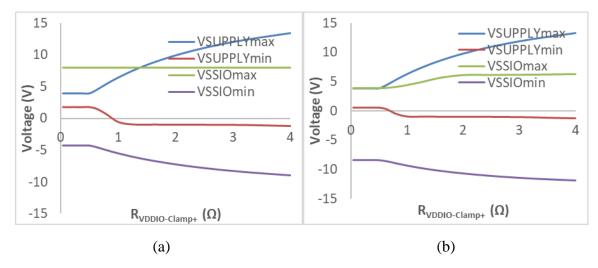

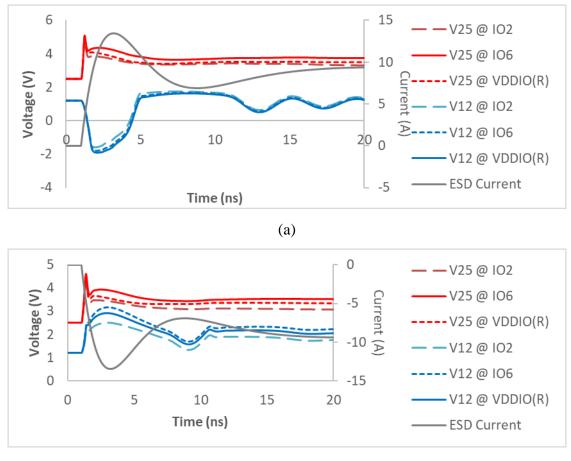

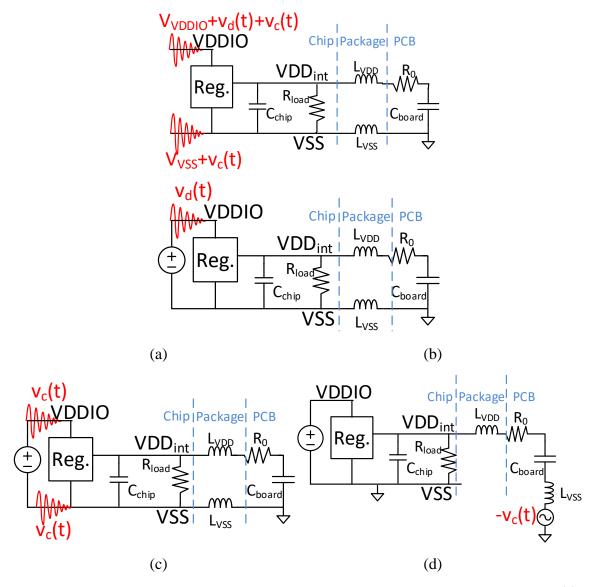

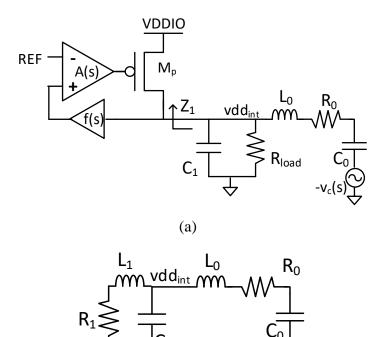

ESD currents easily get shunted to all power and ground nets on-chip since all these nets are connected through ESD protection circuits [39]. Figure 4.1 shows the current path through two on-chip power domains when a negative ESD occurs at an IO in the VDDIO domain. Another supply domain, VDD, is connected to the VDDIO domain through APDs linking VSS to VSSIO. In Figure 4.1, VSS and VSSIO are both connected to the system ground.

Due to the inductances of the package, when ESD current through an IO is directed to the on-chip power or ground net, the voltage on that net is decoupled from the

corresponding power or ground net on-board. A portion of the noise induced on one rail (power or ground) is converted to common-mode noise on the other rail by the on-chip decap; like the first rail, the second rail is isolated from the dc planes on the board by the package inductance. In summary, both the on-chip power and ground nets are affected, independent of which net the ESD protection at the IO directs the ESD current to. The on-chip decap may not be large enough to maintain the normal supply voltage on-chip; the decap may even discharge during ESD, which is referred to as supply collapse [39], [40]. This phenomenon is of particular concern for wire-bond packages, for which the package inductance is usually several nanohenries. System-level ESD currents which easily rise to several amps within 1 or 2 ns will result in several volts across the bond wires. This high amplitude ground bounce can forward bias one of the two diodes in the APD, and then the APD injects a large amount of current from one on-chip ground net to the other, affecting another power domain. The magnetic coupling between bond wires also causes excessive current in and out of the power and ground nets and generates supply fluctuations.

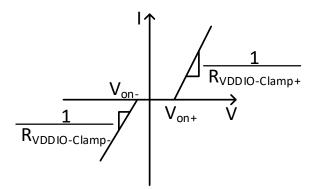

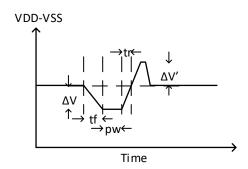

With fast rise and fall times, system-level ESD usually results in noise voltage transients with bipolarity. Therefore, a situation in which the supply voltage drops below its nominal value (under-voltage) and one in which supply voltage rises above (overvoltage) are both expected to occur. The under-voltage transients probably have a larger impact than the over-voltage ones.

The influence of system-level ESD currents on power integrity can be predicted with circuit simulation. With the accurate representation of on-chip supply voltage fluctuation transients, the performance of circuits can be understood and their outputs can be

correlated to the actual fluctuation in experiments. This is especially important for the detectors that are to identify the ESD transients.

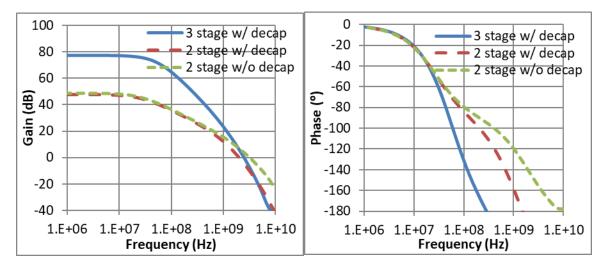

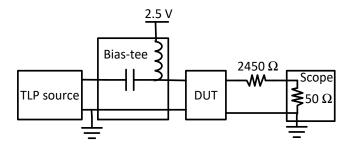

The circuit simulation requires the accurate input of the ESD current. The model shown in Chapter 2 gives an estimation of the system-level ESD current into the IO. The next task is to describe the ESD current division between the multiple paths through the on-chip PDN and the off-chip PDN. The model of the off-chip PDN needs to at least include the package and off-chip decaps, both accompanied by inductances. There have been many studies on the modeling of the PDN to characterize supply fluctuations caused by simultaneous switching noise and electromagnetic emission [41], [42], [43]. The offchip PDN design to minimize the self- and transfer-impedance has been shown to improve performance in system-level ESD as well [44]. The model of the on-chip PDN needs to at least include the bus resistance of the power and ground nets, the on-chip decaps, the rail clamps, the reverse diodes and the APDs. Component models used in the simulation should represent any nonlinearities. On-chip decaps consisting of MOSFETs are modeled as nonlinear elements in this dissertation. Some off-chip decaps and inductances in the PDN also have nonlinearities due to an excess of the voltage across them or self-heating, but these effects are not covered in the dissertation.

# 4.1 Supply fluctuations of a generic circuit during ESD

#### 4.1.1 Supply fluctuations in a single power domain

Supply fluctuations are mainly caused by a large inductance (several nanohenries) in the PDN. When the ESD current injected to an IO is directed to the PDN by the ESD protection at the IO, the rising and falling edges of this current induce voltages at the inductances of the PDN. However, it is not necessary to eliminate the inductances in the PDN, nor is it sufficient for the PDN inductances to decrease in order to eliminate supply fluctuations. As a simplified situation, consider the case of a chip that has only one power domain VDDIO. There will be no fluctuation of the on-chip supply voltage if condition (4.1) is satisfied, since the off-chip supply voltage is usually well-maintained by the off-chip decap.

$$L_{VDDIO} \frac{di_{VDDIO}(t)}{dt} \approx L_{VSSIO} \frac{di_{VSSIO}(t)}{dt}$$

(4.1)

where  $L_{VDDIO}$  is the equivalent inductance of the package connected to the VDDIO net,  $L_{VSSIO}$  is the equivalent inductance of the package connected to the VSSIO net, and  $i_{VDDIO}$  and  $i_{VSSIO}$  are the currents through the VDDIO and VSSIO nets out of the chip respectively. Since the magnitude of the ESD current can be much larger than the normal current consumption of the chip,

$$i_{VDDIO}(t) + i_{VSSIO}(t) = i_{ESD}(t)$$

$$(4.2)$$

where  $i_{ESD}(t)$  is the total ESD current injected to the IO. These two conditions suggest that the on-chip decap and the rail clamp, which are the main current paths between the VDDIO and VSSIO nets during ESD, should help to distribute the ESD current between the two nets to reach similar voltages across  $L_{VDDIO}$  and  $L_{VSSIO}$ . On the other hand, if the on-chip decap and rail clamp are fixed, reducing  $L_{VDDIO}$  and  $L_{VSSIO}$  will not necessarily result in improved power-integrity during ESD, if the currents through  $L_{VDDIO}$  and  $L_{VSSIO}$  are unbalanced (unless, of course, the inductances can be made very small).

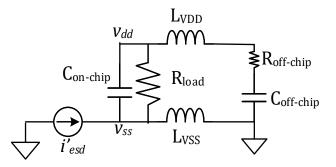

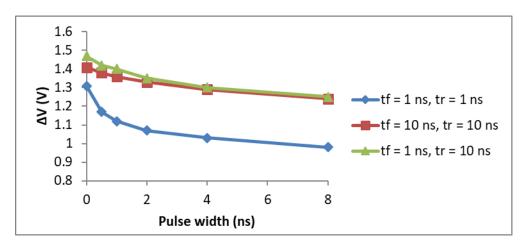

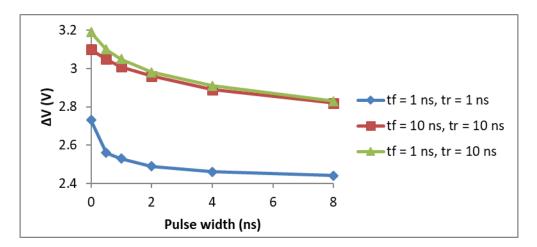

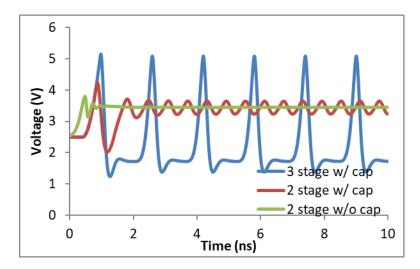

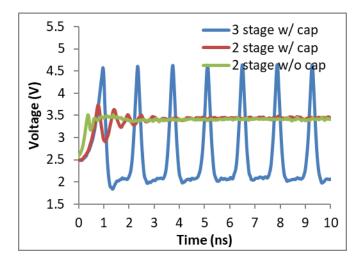

The amount of on-chip decap plays a significant role for the on-chip power integrity during ESD. Figure 4.2 illustrates a case when there is an ESD current  $i'_{esd}$  directed to  $v_{ss}$ , probably from a bottom diode at an IO or the APD. The disturbance induced on  $(v_{dd} - v_{ss})$  is assumed to be negative so that the rail clamp remains off. Based on the schematic shown in Figure 4.2, the ESD current will induce an amount of supply fluctuation given by

$$\frac{v_{dd} - v_{ss}}{i'_{esd}} = \frac{sL_{VSS}}{1 + \frac{Z_{off-chip}}{Z_{on-chip}}}$$

(4.3)

where

$$Z_{off-chip} = \frac{1}{sC_{off-chip}} + s(L_{VDD} + L_{VSS}) + R_{off-chip}$$

(4.4)

$$Z_{on-chip} = R_{load} || \frac{1}{sC_{on-chip}}$$

(4.5)

The amount of supply fluctuation needs to be small, suggesting that the magnitude of  $Z_{off-chip}/Z_{on-chip}$  be large, or that  $sL_{VSS}$  be small.  $L_{VSS}$  is the package inductance and it cannot be made negligibly small in some designs. Therefore, it is necessary to control the ratio between  $Z_{off-chip}$  and  $Z_{on-chip}$ .  $Z_{off-chip}$  is usually very small given the amount of off-chip decap. It is desired to have the magnitude of  $Z_{on-chip}$  be comparable to the

magnitude of  $Z_{off-chip}$  at frequencies of interest during system-level ESD. For a direct contact discharge, the edge of the first ESD current spike contains components at several hundred megahertz. In most designs,  $\left|\frac{1}{sC_{off-chip}}\right|$  is negligibly small in this frequency range.  $R_{load}$  varies from design to design, but it is usually in the range of several hundred ohms to several hundred kiloohms, which is large. If  $\left|\frac{1}{sC_{on-chip}}\right|$  is not sufficiently small, Condition (4.3) indicates that differential mode noise will appear on the supply. Physically, this occurs because there is more current through  $L_{VSS}$  than  $L_{VDD}$  and, consequently, different voltages are induced across the two inductors.

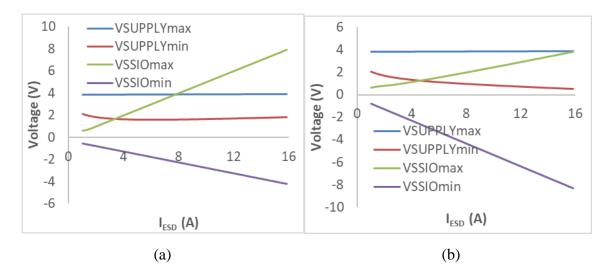

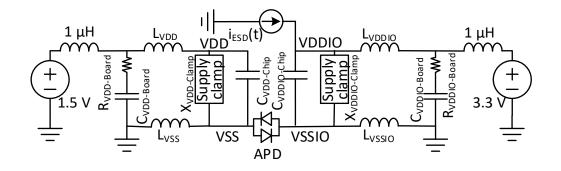

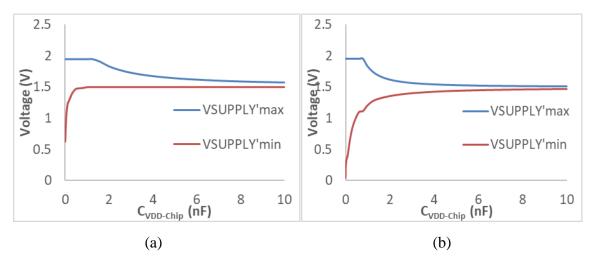

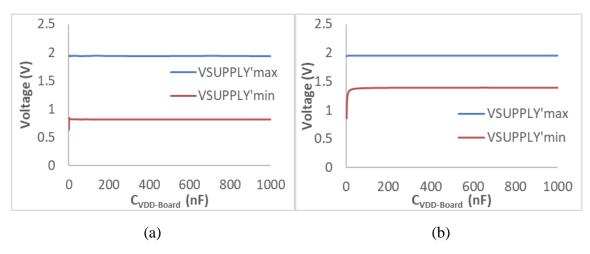

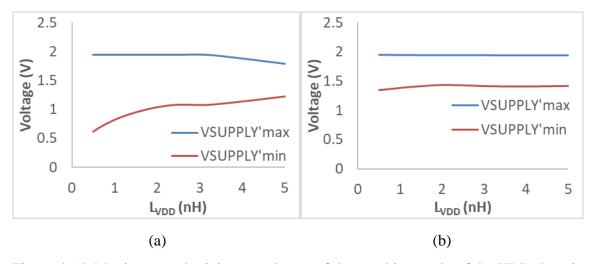

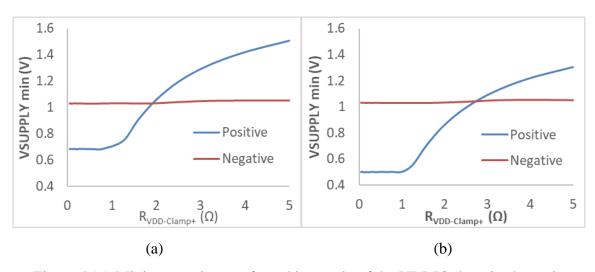

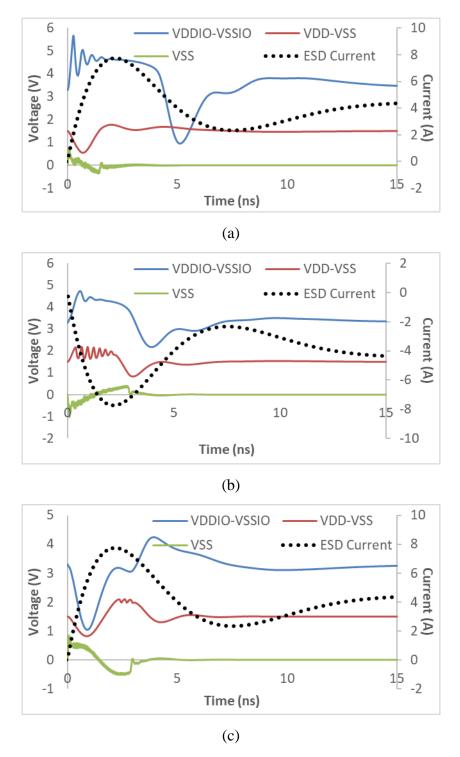

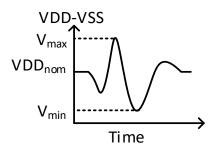

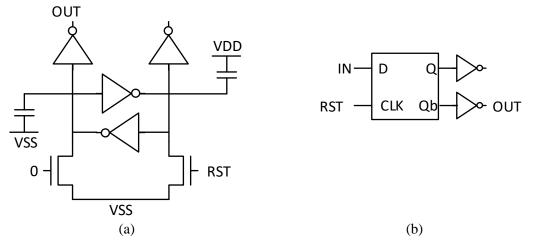

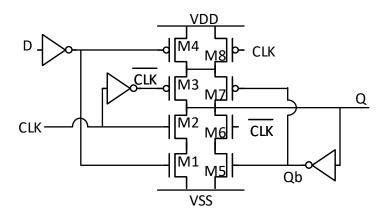

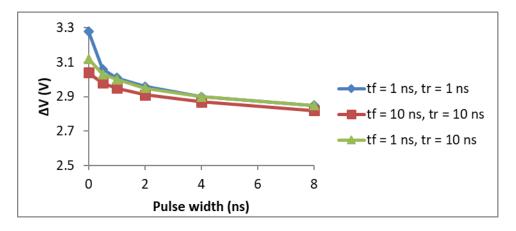

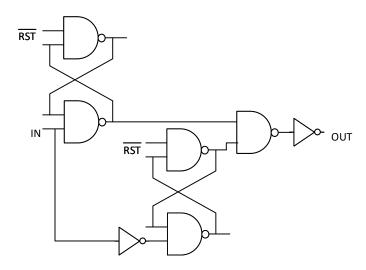

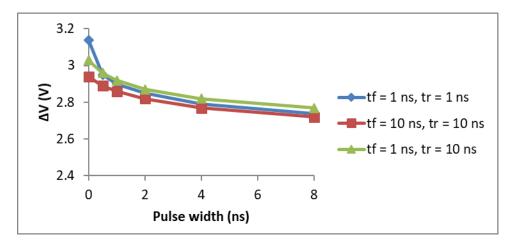

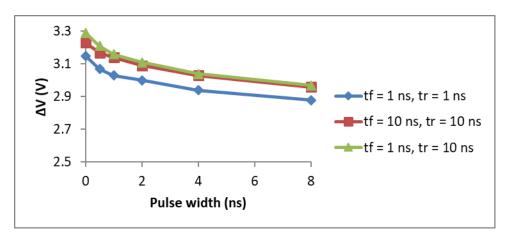

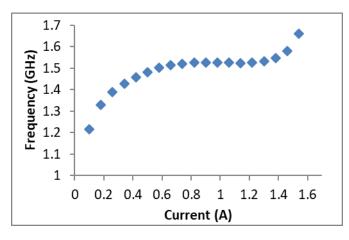

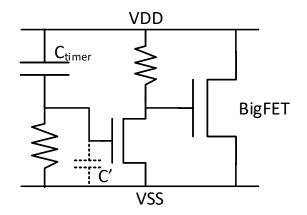

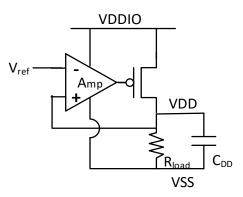

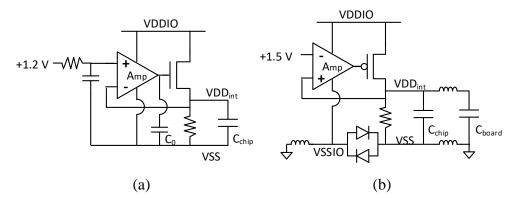

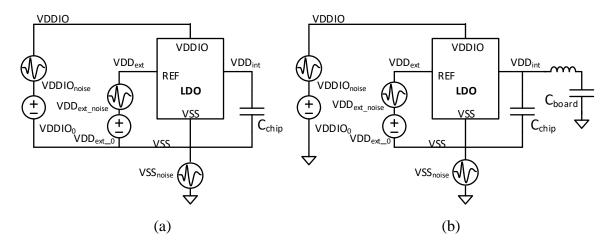

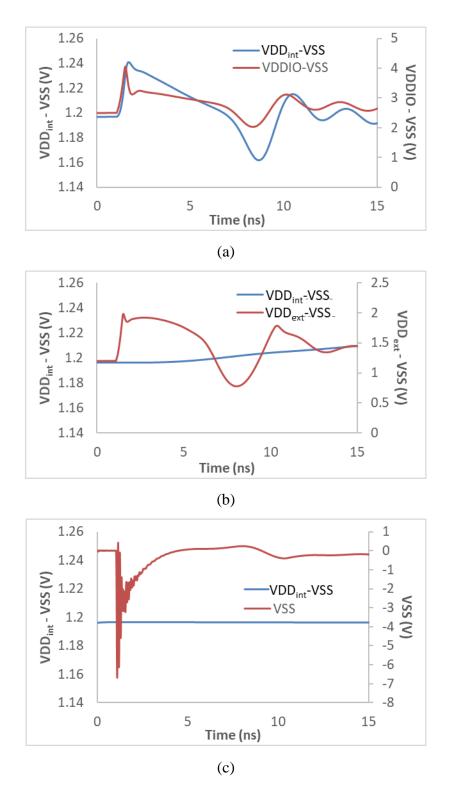

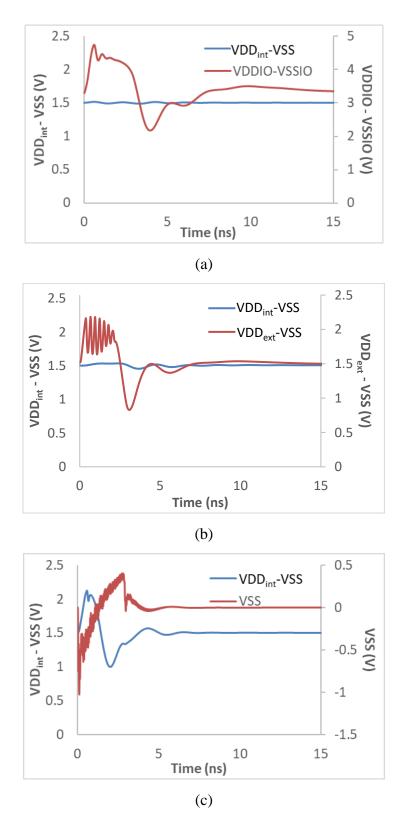

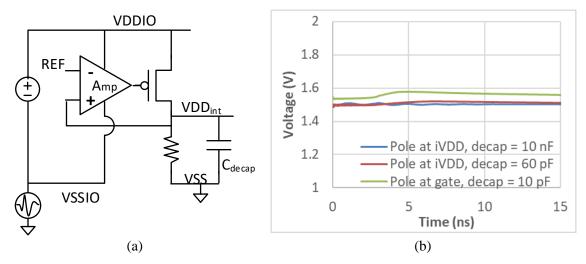

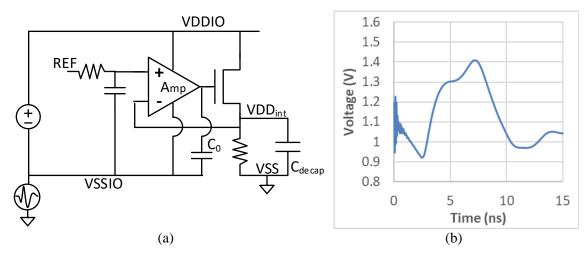

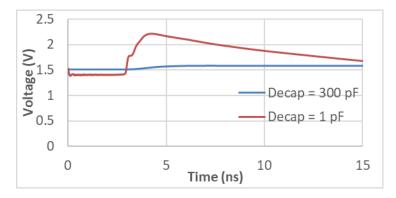

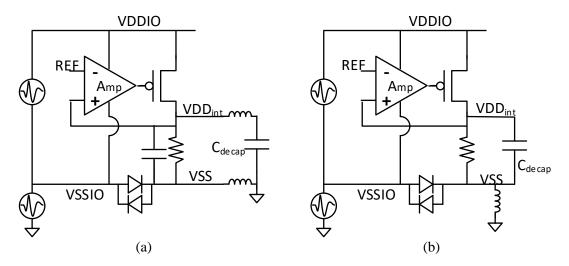

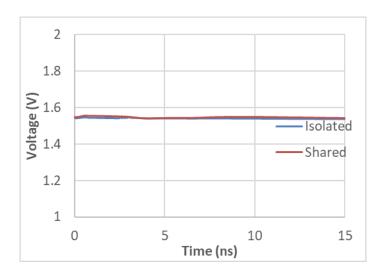

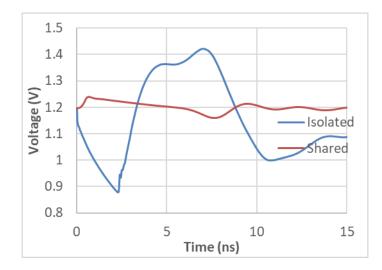

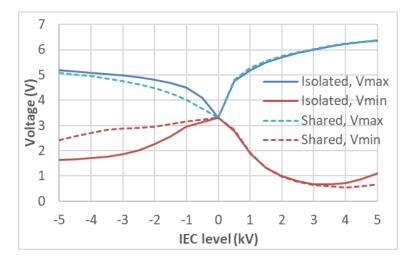

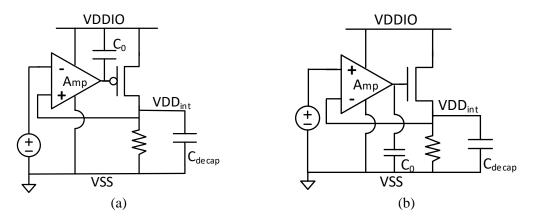

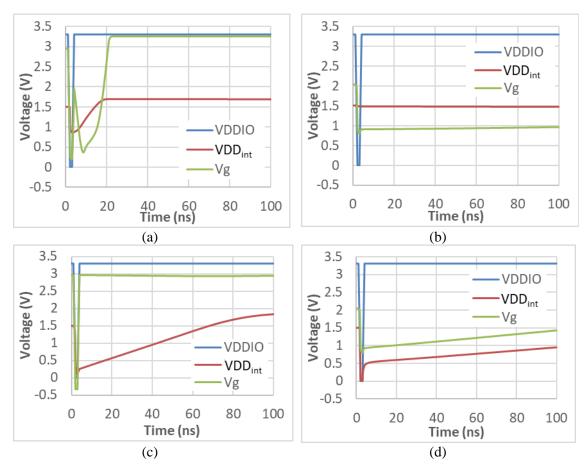

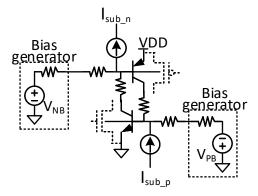

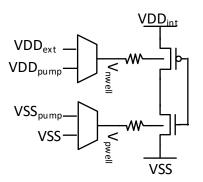

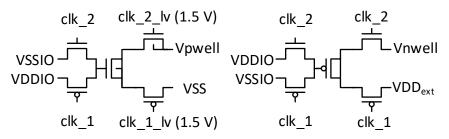

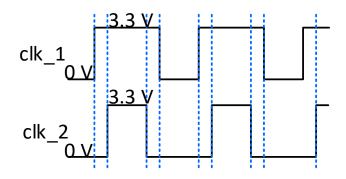

The rail clamp also affects the on-chip power integrity. For example, when a positive ESD current is injected to an IO with dual-diode protection, the current is directed to the on-chip power net from where it has multiple return paths to the system ground. The current may return to ground through the package inductances connected to the power net and the off-chip decap, or it may flow through the on-chip decap and the rail-clamps to the package inductances connected the ground net. When the on-chip supply voltage rises beyond the turn-on voltage of the rail clamp, the rail clamp turns on and directs a larger portion of the current to the ground net. The rail clamp will be kept on until the supply overvoltage diminishes. Without a rail clamp or a large on-chip decap, a larger fraction of the current exits the chip through the supply bond wires, and when the ESD current starts to decrease, the supply under-voltage transient is exacerbated by the unbalanced current distribution. Therefore, an efficient rail clamp can help reduce under-voltage transients that immediately follow an over-voltage one. This phenomenon happens for the first current peak entering the IC during the IEC test.