**University of Bath**

PHD

#### Investigations into the suitability of parallel computing architectures for the solution of large sparse matrices using the preconditioned conjugate gradient method

El-Ghajiji, Otman Abubaker

Award date: 1995

Awarding institution: University of Bath

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## Investigations into the suitability of parallel computing architectures for the solution of large sparse matrices using the preconditioned conjugate gradient method

Submitted by Mr. Otman Abubaker El-Ghajiji, B. Sc. (Hons.), M. Sc. (Bath), For the degree of Ph.D. of the University of BATH 1995

#### **COPYRIGHT**

Attention is drawn to the fact that copyright of this thesis rests with its author. This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognize that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author.

This thesis may be made available for consultation within the University library and may be photocopied or lent to other libraries for the purpose of consultation.

from of si

UMI Number: U601936

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI U601936 Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author. Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### ACKNOWLEDGMENTS

It was a great pleasure to have Dr. Paul J. Leonard as my supervisor at Bath University. He has been an unfailing source of knowledge, encouragement and support. His guidance was crucial for the development of the ideas for this research and the final form in this thesis.

Special thanks are due to Dr. R. W. Dunn for introducing me to multiprocessor system architectures.

I should also like to thank my colleagues and friends in the School of Electrical Engineering and the university of Bath who have made these past years so enjoyable.

### ABSTRACT

This thesis presents investigations into the suitability of parallel computing architectures for the solution of large sparse matrices using the preconditioned conjugate gradient method. The solution is based on the incomplete choleski conjugate gradient algorithm. The preconditioning phase of the algorithm involves a backsubstitution step. We have concentrated our work on how to obtain speedup results when this step is executed on parallel computing architectures.

On the surface the backsubstitution algorithm appears to be serial, but by exploiting the sparsity structure of the large sparse matrices, we have found that a speedup is attainable. The thesis shows, however, the speedup obtainable from the algorithm is significant.

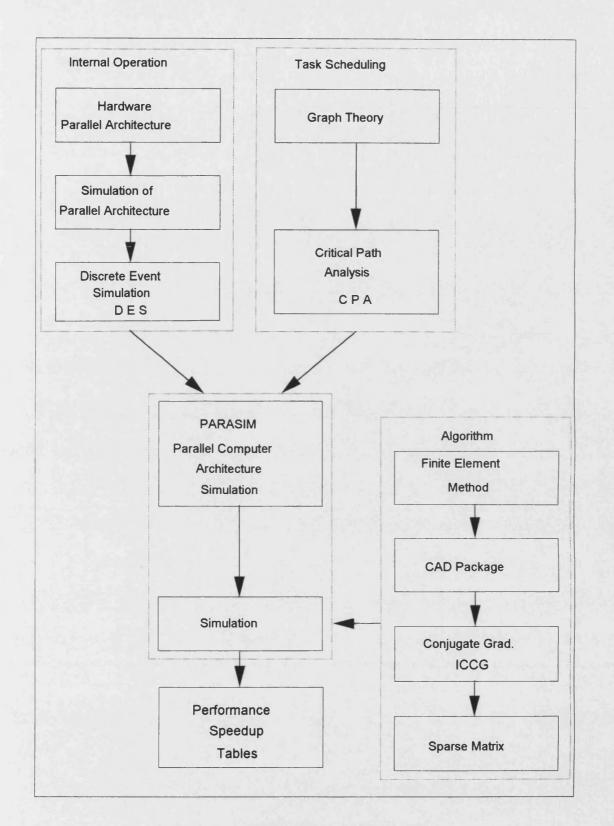

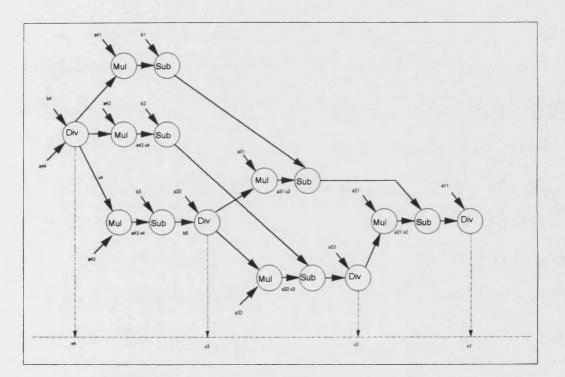

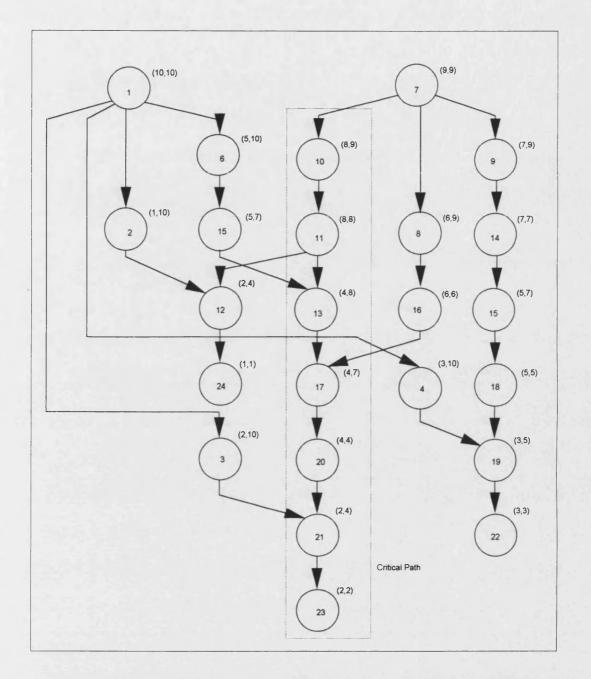

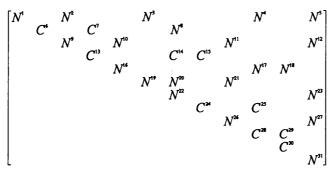

The backsubstitution algorithm steps were represented by a data dependency graph. A node in the graph corresponds to an arithmetic operation, and arcs between nodes represent data transfers. We have develop a scheduling and simulation tool, called PARASIM, to aid in the required investigations.

PARASIM (Parallel Simulator) is a software program, which represents algorithms in data dependency graph, and simulates the operation of parallel computing architectures. It is an interactive environment in which one can simulate MIMD architectures of both distributed memory, as well as architectures with shared memory and interprocessor communication enhancement mechanism.

PARASIM has control structures for expressing parallel execution of algorithms, data transfer and models for hardware subsystems, such as processors, memory and bus structures. An intelligent scheduling method based on the critical path analysis concept was incorporated into PARASIM. This scheduling method ensures that minimum execution time is achieved. The key two factors which will affect the speedup are load balancing and interprocessor communication. It is essential that all processing nodes have equivalent computational loads, and the interprocessor communication is reduced as much as possible.

The thesis presents simulation results for a number of models exploiting different sources of parallelism. The thesis points out that communication enhancement hardware, such as one-to-all broadcast and caching, would improve the speedup by a factor of 10 to 20% respectively. sparsity structures and element interconnections.

## ABBREVIATIONS

| BUTPC      | Bath University Transputer-based Parallel                                                 |

|------------|-------------------------------------------------------------------------------------------|

|            | Computer                                                                                  |

| CAD        | Computer Aided Design                                                                     |

| MISD       | Multiple Instruction Single Data                                                          |

| MIMD       | Multiple Instruction Multiple Data                                                        |

| CG         | Conjugate Gradient                                                                        |

| CPA        | Critical Path Analysis                                                                    |

| CPU        | Central Processing Unit                                                                   |

| FEM        | Finite Element Method                                                                     |

| FPU        | Floating Point Unit                                                                       |

| HLL        | High Level Language                                                                       |

| ICCG       | Incomplete Choleski Conjugate Gradient                                                    |

| IPC        | Inter-Processor Communication                                                             |

| LSI        | Large Scale Integration                                                                   |

| MIPS       | Millions of Instructions Per Second                                                       |

| <u>M M</u> | Memory Module                                                                             |

| 05         | Operating Systems                                                                         |

| PARASIM    | Parallel Systems Simulator: A software program developed for this research by the author. |

| PDE        | Partial Defirential Equations                                                             |

| PERT       | Project Evaluation and Review Technique                                                   |

| P N        | Processing Node                                                                           |

| PPA        | Parallel Processing Architecture                                                          |

| RAM        | Random Access Memory                                                                      |

| RISC       | Reduced Instruction Set Computer                                                          |

| SIMD       | Single Instruction Multiple Data                                                          |

| SISD       | Single Instruction Single Data                                                            |

| TSB        | Time-Shared Bus (multiprocessors)                                                         |

| TTL        | Transistor Transistor Logic                                                               |

| VLSI       | Very Scale Integration                                                                    |

## List of Tables

| TABLE 1: COMPARISON TABLE OF DIFFERENT SIMULATORS.                                 | 66                 |

|------------------------------------------------------------------------------------|--------------------|

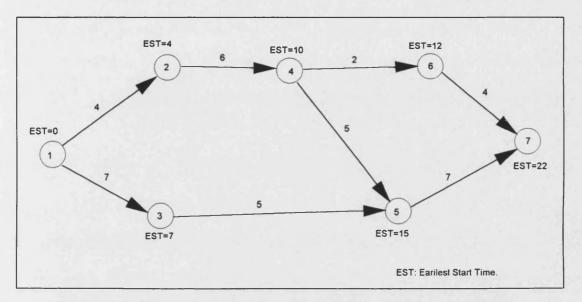

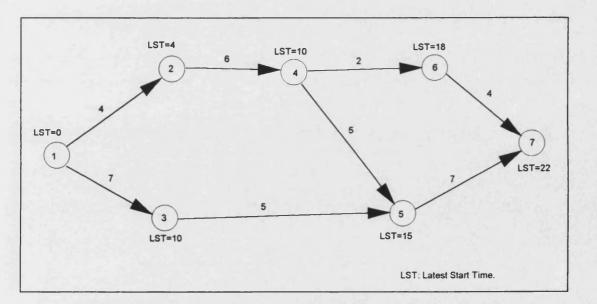

| TABLE 2: THE LINK INFORMATION (EARLIEST AND LATEST START TIMES) FOR THE NETWORK OF | 7 NODES.78         |

| TABLE 3: C CODE DECLARATION OF NODE STRUCTURE                                      |                    |

| TABLE 4: C CODE DECLARATION FOR LINK STRUCTURE.                                    |                    |

| TABLE 5: C CODE DECLARATION FOR TASK STRUCTURE.                                    |                    |

| TABLE 6: THE BASIC SCHEDULING ALGORITHM STEPS.                                     | 113                |

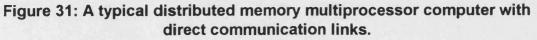

| TABLE 7: C CODE FOR DECLARATION THE PROCESSING NODE STRUCTURE.                     | 117                |

| TABLE 8: DETAILS OF THE PROCESSING NODE DECLARATION VARIABLES.                     | 117                |

| TABLE 9: CONTENTS OF NETWORK DESCRIPTION FILE.                                     | 122                |

| TABLE 10: OUTPUT INFORMATION OF THE SIMULATION PROGRAM PARASIM.                    | 126                |

| TABLE 11: CHARATERISTICS OF THE DATA MODELS USED IN SIMULATION SHOWING SPARSITY RA | по <b>з.</b> . 134 |

| TABLE 12: SINGLE ARITHMETIC TASK OPERATION TIMING AND MODELS USED                  | 144                |

| TABLE 13: MULTIPLE ARITHMETIC TASK OPERATION TIMING                                | 144                |

| TABLE 14: FIELD DESCRIPTION FOR TABLE HEADINGS FOR TABLES 16 TO 22.                | 146                |

| TABLE 15: NETWORK INFORMATION FOR MODELS 1 TO 12.                                  | 146                |

| TABLE 16: NETWORK INFORMATION FOR MODEL 13.                                        | 146                |

| TABLE 17: NETWORK INFORMATION FOR MODELS 14 TO 18.                                 | 147                |

| TABLE 18: NETWORK INFORMATION FOR MODELS 19 TO 30.                                 | 147                |

| TABLE 19: NETWORK INFORMATION FOR MODELS 31 TO 47.                                 | 147                |

| TABLE 20: NETWORK INFORMATION FOR MODELS 37 TO 47.                                 | 148                |

| TABLE 21: NETWORK INFORMATION FOR MODELS 48 TO 50.                                 | 148                |

| TABLE 22: FIELD HEADINGS FOR AVERAGE SPEEDUP TABLES.                               | 153                |

| TABLE 23: AVERAGE SPEEDUP RESULTS FOR 4 ARCHITECTURES FOR MODELS 1 TO 18.          | 153                |

| TABLE 24: AVERAGE SPEEDUP RESULTS FOR 4 ARCHITECTURES FOR MODELS 19 TO 36.         | 154                |

| TABLE 25: AVERAGE SPEEDUP RESULTS FOR 4 ARCHITECTURES FOR MODELS 37 TO 50.         | 154                |

| TABLE 26: COMPARISON OF MODELS 1 AND 3.                                            | 164                |

| TABLE 27: COMPARISON OF MODELS 9 AND 11.                                           | 165                |

| TABLE 28: COMPARISON OF MODELS 14 AND 15                                           | 165                |

| TABLE 29: COMPARISON OF MODELS 22 AND 28.                                          | 165                |

| TABLE 30: COMPARING MODEL 32 AND 47                                                | 166                |

| TABLE 31: COMPARING MODELS 4 AND 5                                                 | 166                |

| TABLE 32: COMPARING MODELS 4 AND 5                                                 | 166                |

## Table of Figures

| FIGURE 1: ORGANIZATION OF THIS THESIS                                           | 11  |

|---------------------------------------------------------------------------------|-----|

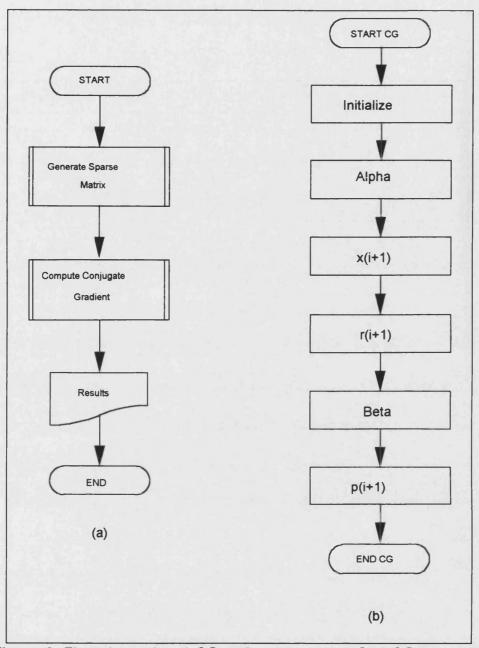

| FIGURE 2: FLOWCHARTS FOR A) CG MAIN PROGRAM, B) ONE CG ITERATION.               | 18  |

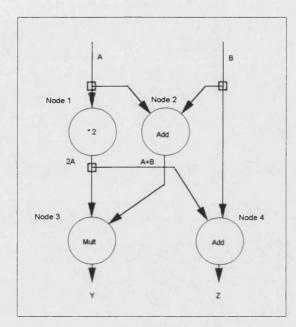

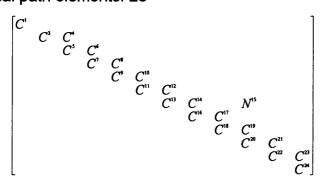

| FIGURE 3: DATAFLOW DETAILS FOR A FULL 3X3 MATRIX.                               | 24  |

| FIGURE 4: THE DATAFLOW FOR THE EXAMPLE SPARSE MATRIX SIZE 10x10.                | 26  |

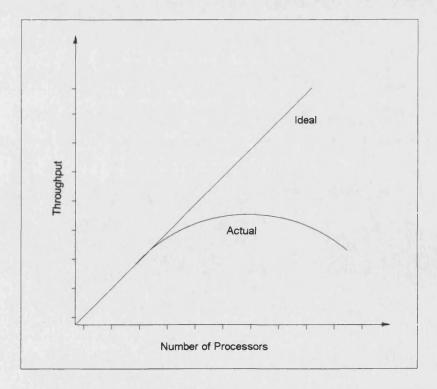

| FIGURE 5 THROUGHPUT OF A MULTIPROCESSOR COMPUTING SYSTEM.                       | 34  |

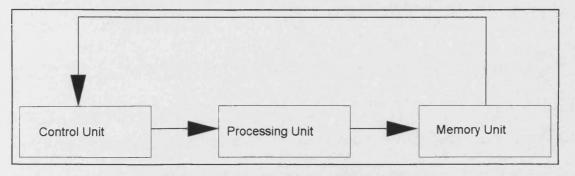

| FIGURE 6: SISD COMPUTER ARCHITECTURE                                            | 36  |

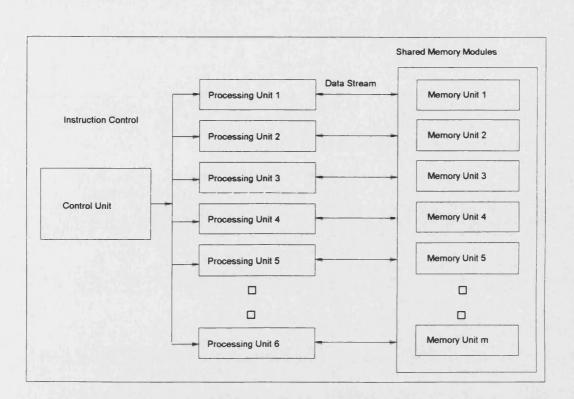

| FIGURE 7: SIMD COMPUTER ARCHITECTURE.                                           | 37  |

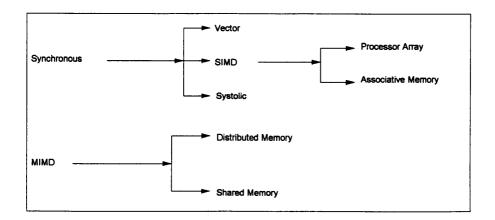

| FIGURE 8: HIGH-LEVEL TAXONOMY OF PARALLEL COMPUTING ARCHITECTURES               | 38  |

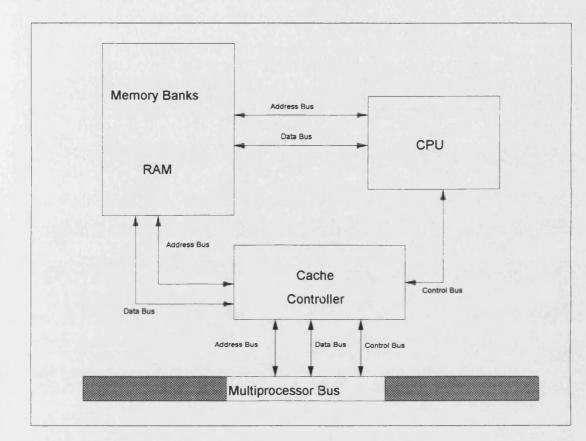

| FIGURE 9: CACHE ARCHITECTURE FOR THE PROCESSING NODE.                           | 40  |

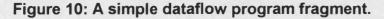

| FIGURE 10: A SIMPLE DATAFLOW PROGRAM FRAGMENT.                                  | 46  |

| FIGURE 11: A SECOND DATAFLOW PROGRAM FRAGMENT                                   | 47  |

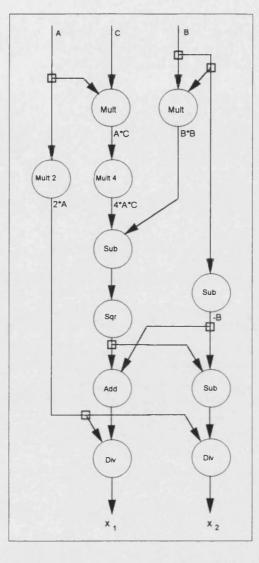

| FIGURE 12: DATAFLOW PROGRAM TO COMPUTE QUADRATIC ROOTS.                         | 48  |

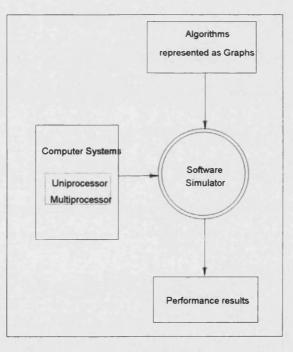

| FIGURE 13: SOFTWARE SIMULATION OF UNDERLYING ARCHITECTURES                      | 62  |

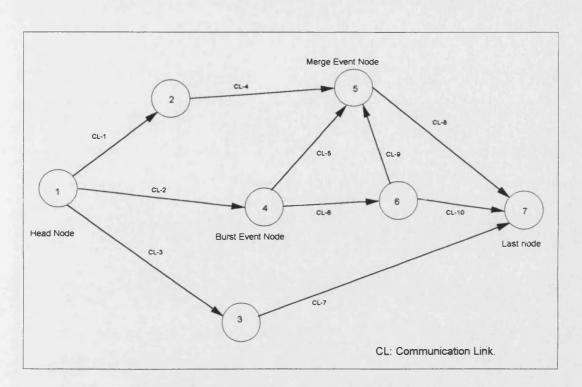

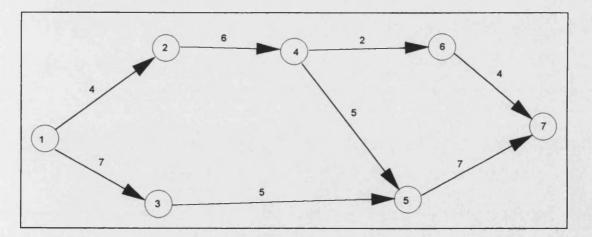

| FIGURE 14: A NETWORK OF CONNECTED NODES.                                        | 75  |

| FIGURE 15: ORIGINAL NETWORK.                                                    | 76  |

| FIGURE 16: FORWARD SWEEP TO COMPUTE THE EARLIEST START TIMES                    |     |

| FIGURE 17: REVERSE PASS TO COMPUTE THE LATEST START TIMES.                      | 77  |

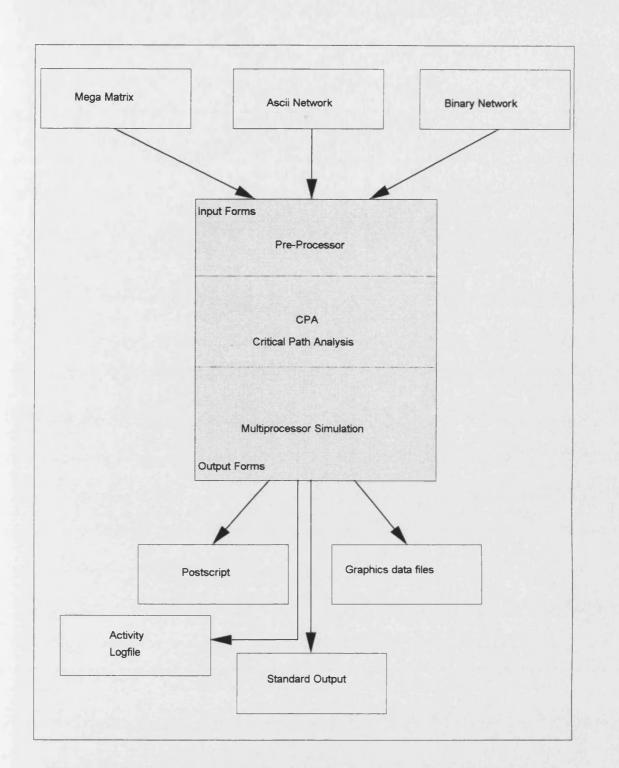

| FIGURE 18: FORMS OF INPUT AND OUTPUT TO/FROM THE SIMULATION PROGRAM PARASIM.    | 94  |

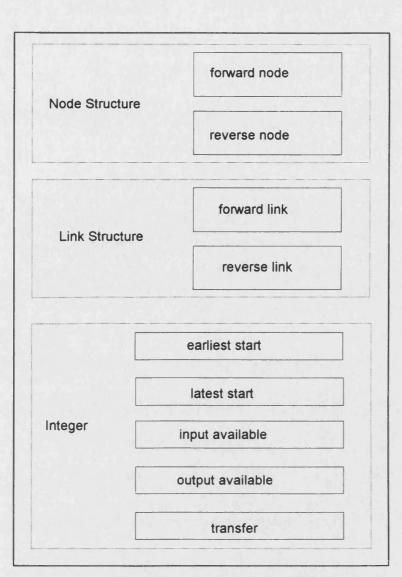

| FIGURE 19: GRAPHICAL PRESENTATION OF NODE STRUCTURE                             | 96  |

| FIGURE 20: GRAPHICAL PRESENTATION OF LINK STRUCTURE.                            | 98  |

| FIGURE 21: GRAPHICAL PRESENTATION OF TASK STRUCTURE.                            | 99  |

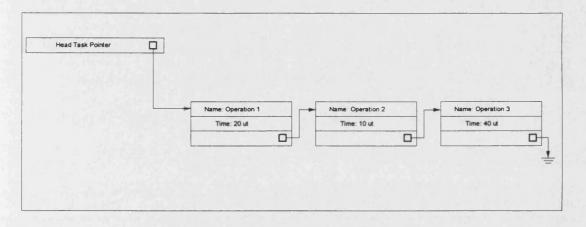

| FIGURE 22: GRAPHICAL PRESENTATION OF THE TASK LIST.                             | 100 |

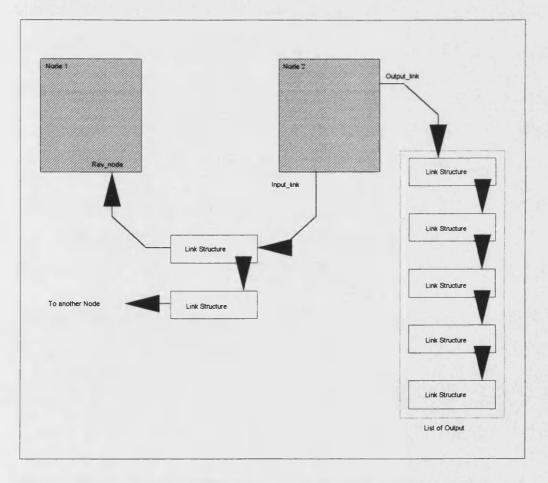

| FIGURE 23: A SEGMENT OF THE NETWORK PRESENTATION WHICH INCLUDES 2 NODES         | 102 |

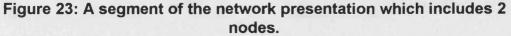

| FIGURE 24: FLOWCHART OF PARASIM STEPS IN OPERATION.                             | 104 |

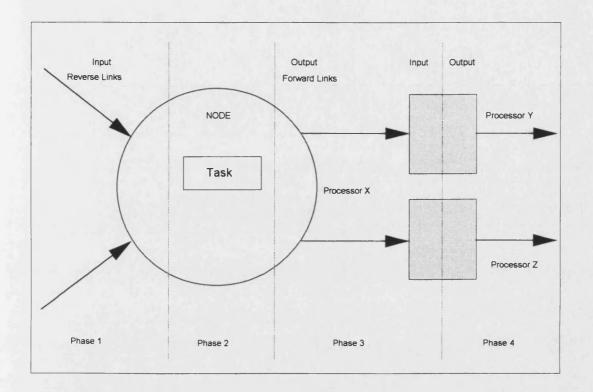

| FIGURE 25: PHASES OF EXECUTION FOR A NODE WITH INPUT AND OUTPUT LINKS.          | 106 |

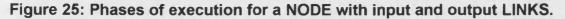

| FIGURE 26: INITIAL WINDOW POSITION DURING THE SIMULATION STEPS                  | 108 |

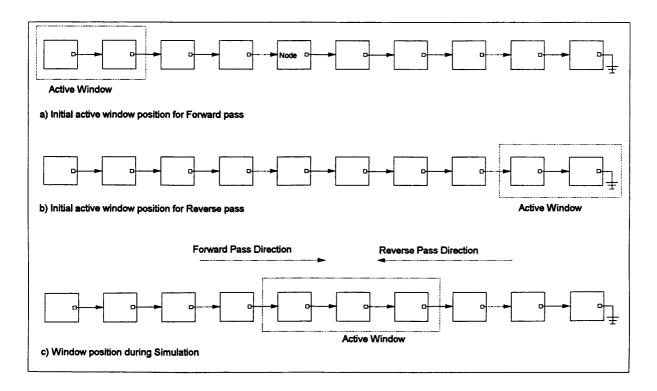

| FIGURE 27: FLOWCHART OF FORWARD_PASS() ROUTINE                                  | 109 |

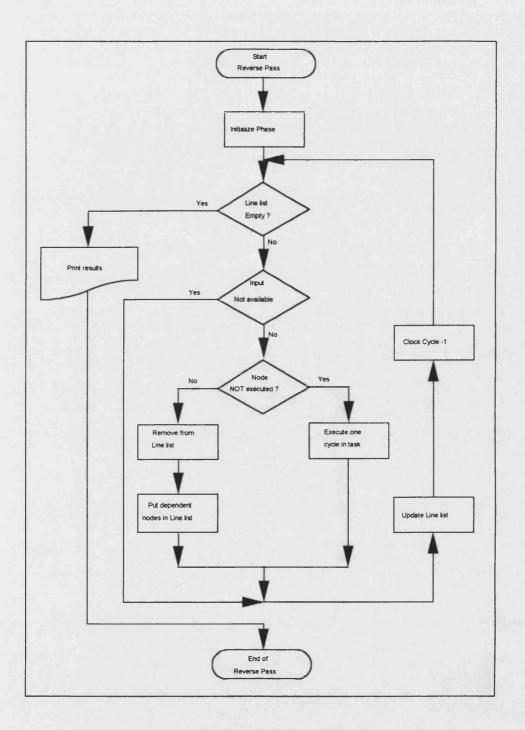

| FIGURE 28: FLOWCHART OF REVERSE_PASS() ROUTINE.                                 | 111 |

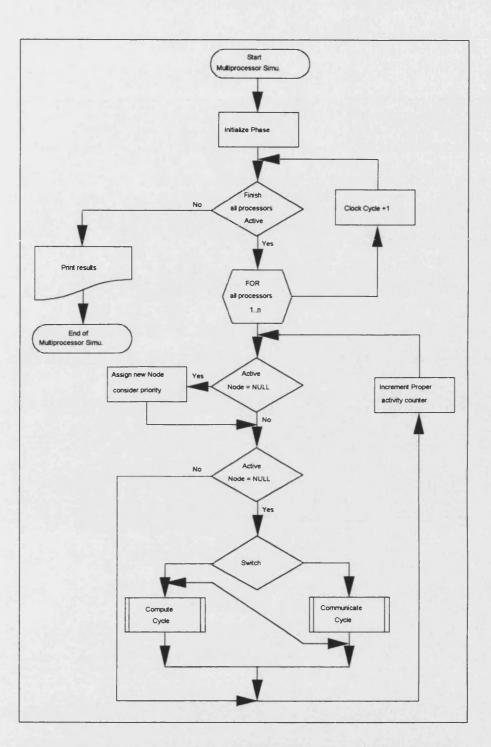

| FIGURE 29: FLOWCHART OF MULTIPROCESSOR SIMULATION ROUTINE.                      | 114 |

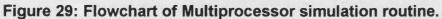

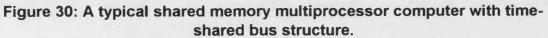

| FIGURE 30: A TYPICAL SHARED MEMORY MULTIPROCESSOR COMPUTER WITH TIME-SHARED BUS |     |

| STRUCTURE                                                                       | 116 |

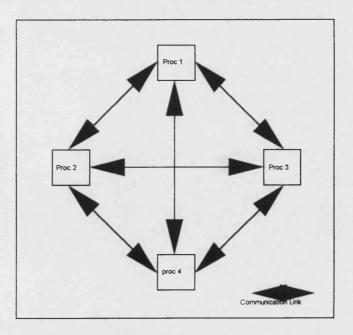

| FIGURE 31: A TYPICAL DISTRIBUTED MEMORY MULTIPROCESSOR COMPUTER WITH DIRECT     |     |

| COMMUNICATION LINKS.                                                            | 116 |

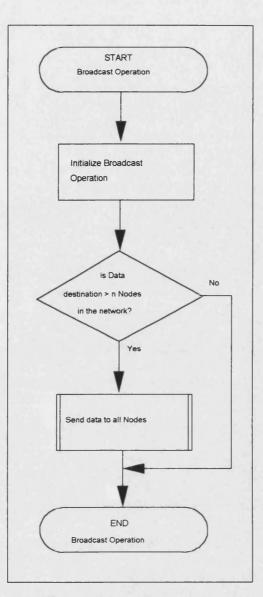

| FIGURE 32: FLOWCHART OF BROADCAST OPERATION CRITERION.                          | 119 |

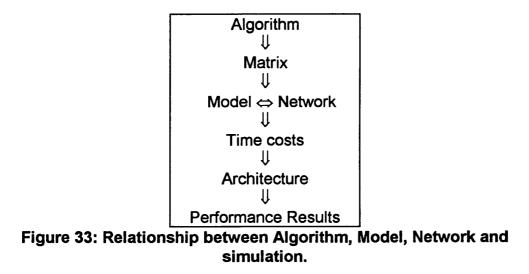

| FIGURE 33: RELATIONSHIP BETWEEN ALGORITHM, MODEL, NETWORK AND SIMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

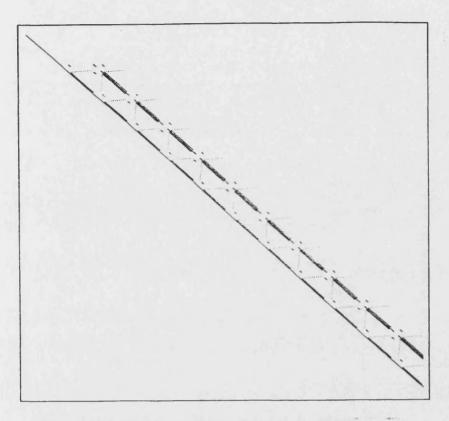

| FIGURE 34: ELEMENT DISTRIBUTION IN PROBLEM 2352                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

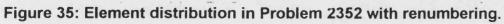

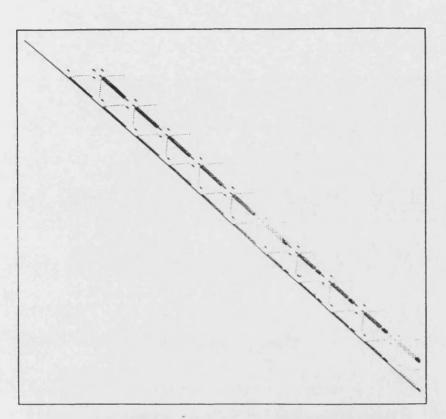

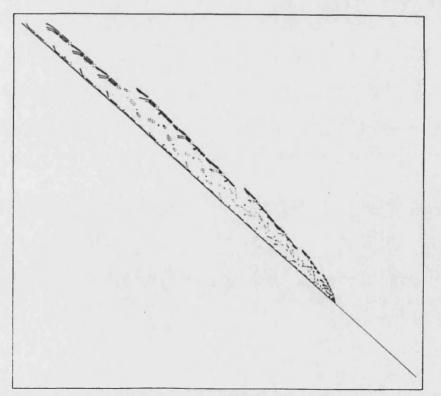

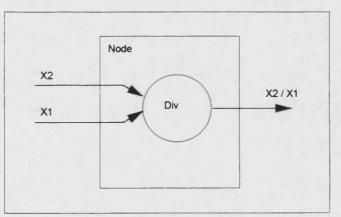

| FIGURE 35: ELEMENT DISTRIBUTION IN PROBLEM 2352 WITH RENUMBERING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

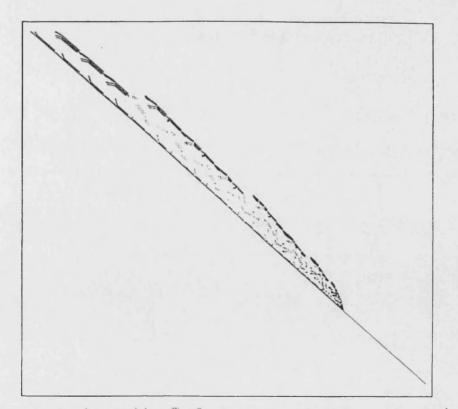

| FIGURE 36: ELEMENT DISTRIBUTION IN PROBLEM 2352A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FIGURE 37: ELEMENT DISTRIBUTION IN PROBLEM 2352A WITH WITH RENUMBERING                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FIGURE 38: AN EXAMPLE OF A DIAGONAL ELEMENT NODE WITH ITS TASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FIGURE 39: AN EXAMPLE OF A ROW ELEMENT WITH A MULTI-OPERATION TASK (ADD & MULT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

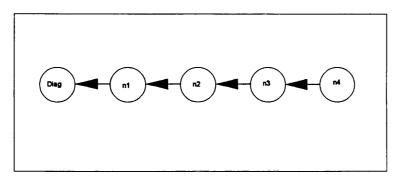

| FIGURE 40: CONNECTIONS TO THE DIAGONAL ELEMENT OF EACH MATRIX ROW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FIGURE 41: CONNECTING TWO MATRIX ELEMENTS TO A DIAGONAL ELEMENT BY DIRECT CONNECTION. 142                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

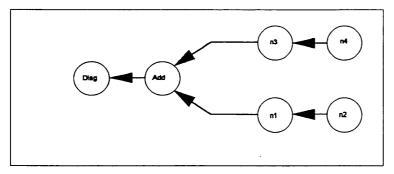

| FIGURE 42: A ROW WITH CLUSTERED NODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

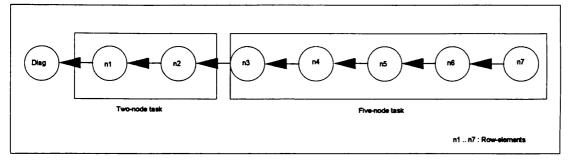

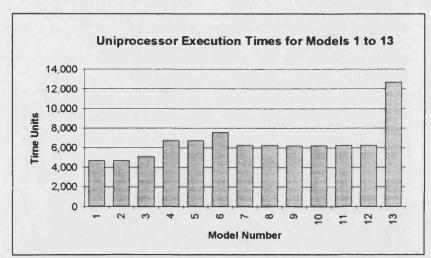

| FIGURE 43: SERIAL UNIPROCESSOR EXECUTION TIME IN TIME UNITS FOR MODELS 1 TO 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

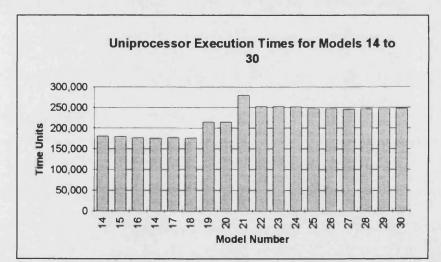

| FIGURE 44: SERIAL UNIPROCESSOR EXECUTION TIME IN TIME UNITS FOR MODELS 14 TO 30 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

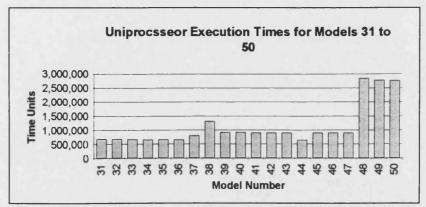

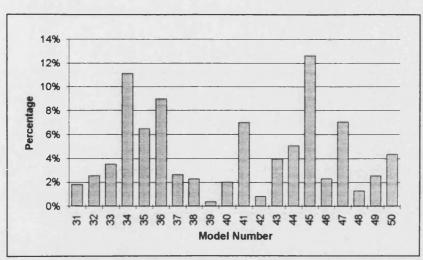

| FIGURE 45: SERIAL UNIPROCESSOR EXECUTION TIME IN TIME UNITS FOR MODELS 31 TO 50 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

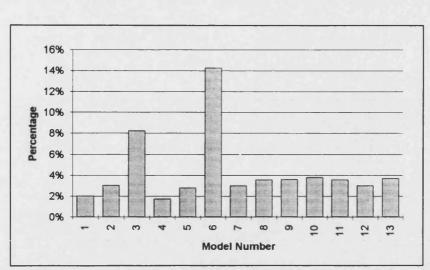

| FIGURE 46: PERCENTAGE OF CRITICAL PATH TIME TO THE UNIPROCESSOR EXECUTION TIME FOR MODELS 1                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| то 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

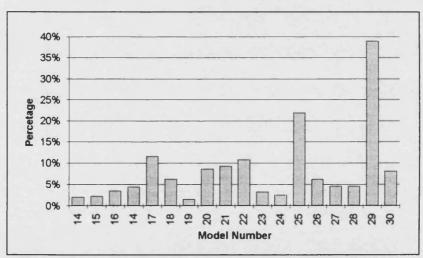

| FIGURE 47: PERCENTAGE OF CRITICAL PATH TIME TO THE UNIPROCESSOR EXECUTION TIME FOR MODELS                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14 то 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FIGURE 48: PERCENTAGE OF CRITICAL PATH TIME TO THE UNIPROCESSOR EXECUTION TIME FOR MODELS                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 31 то 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

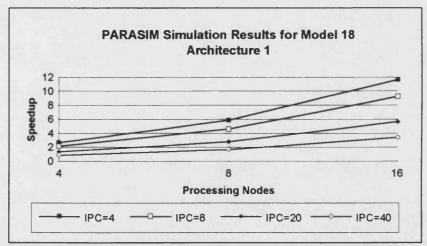

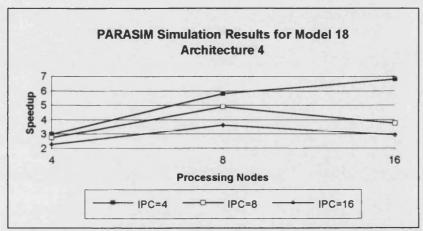

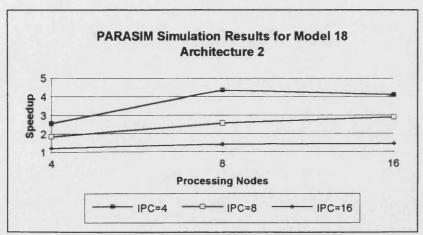

| FIGURE 49: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 4 VALUES OF IPC USING THE                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DISTRIBUTED MEMORY ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

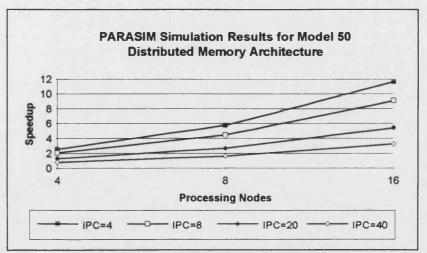

| FIGURE 50: SPEEDUP RESULTS FOR MODEL 50 USING DISTRIBUTED MEMORY ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

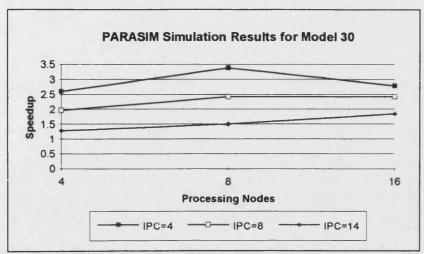

| FIGURE 51: SPEEDUP RESULTS FOR MODEL 30 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| COMMUNICATION USING SHARED MEMORY ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

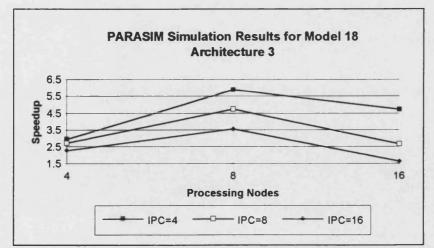

| FIGURE 52: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| COMMUNICATION USING SHARED MEMORY ARCHITECTURE WITH CACHE MECHANISM 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

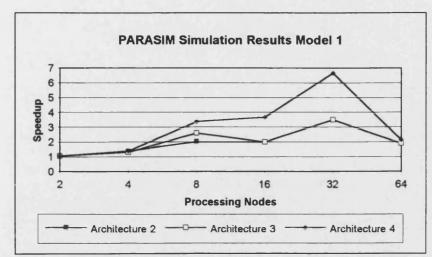

| FIGURE 53: SPEEDUP RESULTS FOR MODEL 1 SHOWING THE EFFECT OF 3 ARCHITECTURE TYPES WITH                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IPC=8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

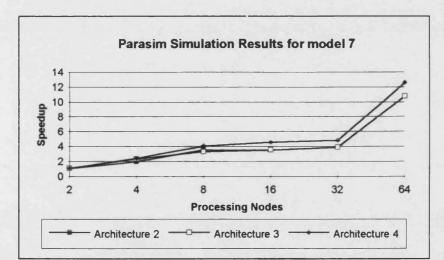

| FIGURE 54: SPEEDUP RESULTS FOR MODEL 7 SHOWING THE EFFECT OF 3 ARCHITECTURE TYPES WITH                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IPC=8160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

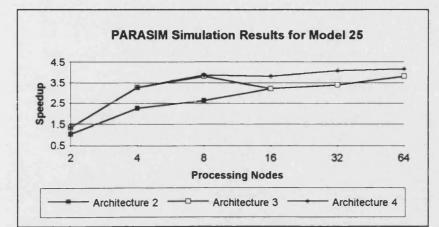

| FIGURE 55: SPEEDUP RESULTS FOR MODEL 25 SHOWING THE EFFECT OF 3 ARCHITECTURE TYPES WITH                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IPC=8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IPC=8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

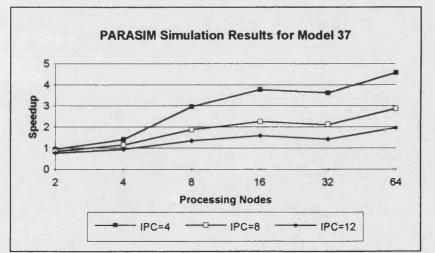

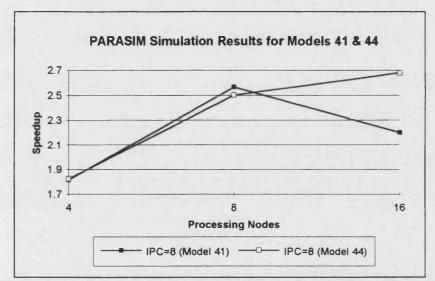

| FIGURE 56: SPEEDUP RESULTS FOR MODEL 37 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR         COMMUNICATION USING SHARED MEMORY ARCHITECTURE.         161         FIGURE 57: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR                                                                                                                                                                                                                                                                                     |

| FIGURE 56: SPEEDUP RESULTS FOR MODEL 37 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       161         FIGURE 57: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       161         FIGURE 57: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       161         FIGURE 57: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       161         FIGURE 57: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       162 |

| FIGURE 56: SPEEDUP RESULTS FOR MODEL 37 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR         COMMUNICATION USING SHARED MEMORY ARCHITECTURE.         161         FIGURE 57: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR                                                                                                                                                                                                                                                                                     |

| FIGURE 56: SPEEDUP RESULTS FOR MODEL 37 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       161         FIGURE 57: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       162         FIGURE 58: SPEEDUP RESULTS FOR MODEL 18 SHOWING THE EFFECT OF 3 VALUES FOR INTERPROCESSOR       162                                                                                                                                                                                                                         |

## **Table of Contents**

| ACKNOWLEDGMENTS                                                                                                                                                                                                      |                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| ABSTRACT                                                                                                                                                                                                             |                              |

| ABBREVIATIONS                                                                                                                                                                                                        |                              |

| TABLE OF FIGURES                                                                                                                                                                                                     |                              |

| LIST OF TABLES                                                                                                                                                                                                       |                              |

| TABLE OF CONTENTS                                                                                                                                                                                                    | vii                          |

| PART ONE                                                                                                                                                                                                             | <u>1</u>                     |

| INTRODUCTION AND BACKGROUND                                                                                                                                                                                          | 1                            |

| CHAPTER 1                                                                                                                                                                                                            | <u>2</u>                     |

| 1.0 INTRODUCTION                                                                                                                                                                                                     | 3                            |

| HOW TO IMPROVE THE PERFORMANCE OF CAD SYSTEMS:                                                                                                                                                                       |                              |

| 1.1 SIMULATING MULTIPROCESSORS:                                                                                                                                                                                      |                              |

| DISTRIBUTED MEMORY ARCHITECTURE:                                                                                                                                                                                     |                              |

| SHARED MEMORY ARCHITECTURE:                                                                                                                                                                                          |                              |

| 1.2 ACHIEVEMENTS                                                                                                                                                                                                     |                              |

| 1.3 THESIS OVERVIEW                                                                                                                                                                                                  |                              |

| CHAPTER 2                                                                                                                                                                                                            |                              |

| 2.0 Conjugate Gradient Algorithm                                                                                                                                                                                     |                              |

| 2.1 BACKGROUND INFORMATION                                                                                                                                                                                           | 13                           |

| 2.2 THE CONJUGATE GRADIENT ALGORITHM                                                                                                                                                                                 |                              |

| 2.2.1 THE C G ITERATION                                                                                                                                                                                              | 17                           |

| 2.3 PARALLEL FEATURES OF C G                                                                                                                                                                                         | 19                           |

| 2.5 I ARALLEL FEATURES OF C G                                                                                                                                                                                        | **********                   |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC                                                                                                                                                      |                              |

|                                                                                                                                                                                                                      | CG 22                        |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC                                                                                                                                                      | CG 22<br>24                  |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION                                                                                                                                    | CG 22<br>24<br>27            |

| <ul> <li>2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC</li> <li>2.6 DISCUSSION</li></ul>                                                                                                           | 2G 22<br>24<br>27<br>28      |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION<br>2.7 CONCLUSION                                                                                                                  | 2G22<br>24<br>27<br>28<br>30 |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION<br>2.7 CONCLUSION<br>2.8 REFERENCES<br>PART_TWO                                                                                    | 2G                           |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION<br>2.7 CONCLUSION<br>2.8 REFERENCES<br>2.8 REFERENCES<br>STRUCTURE AND SIMULATION OF PARALLEL COMPUTING ARCHITECTURES<br>CHAPTER 3 | 2G                           |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION                                                                                                                                    | 2G                           |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION                                                                                                                                    | 2G                           |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION                                                                                                                                    | CG                           |

| 2.5 PRECONDITIONED INCOMPLETE CHOLESKI'S CONJUGATE GRADIENT ICC<br>2.6 DISCUSSION                                                                                                                                    | CG                           |

•

| 3.1.4 DATA FLOW ARCHITECTURES         3.2 EXECUTION OF PARALLEL ALGORITHMS         3.3 CONCLUSION         3.4 REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3 CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |

| 3.4 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |

| CHAPTER 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |

| 4.0 SIMULATION OF PARALLEL COMPUTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |

| 4.1 DISCRETE EVENT SIMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                  |

| 4.2 DISCRETE EVENT MODELS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                  |

| 4.3 SIMULATION SYSTEM GOALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                  |

| 4.4 PERFORMANCE ESTIMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                  |

| 4.5 PREVIOUS ATTEMPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                  |

| 4.5.1 HARDWARE SUBSYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                  |

| 4.5.2 PROCESSOR INSTRUCTION SIMULATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |

| 4.5.3 H.L.L. SOURCE CODE SIMULATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 4.5.4 OPERATING SYSTEM SIMULATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                  |

| 4.5.5 STAND-ALONE SIMULATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                  |

| 4.6 DISCUSSION AND CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                  |

| 4.7 REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68                                                                                                                                               |

| ART THREE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |

| SCHEDULING AND SIMULATING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                  |

| HAPTER 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72                                                                                                                                               |

| 5.0 Critical Path Method and Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  |

| HAPTER 5         5.0 Critical Path Method and Scheduling         5.1 Introduction to Critical Path Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                  |

| CHAPTER 5         5.0 Critical Path Method and Scheduling         5.1 Introduction to Critical Path Method         5.2 The Network Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                  |

| 5.0 Critical Path Method and Scheduling<br>5.1 Introduction to Critical Path Method<br>5.2 The Network Diagram<br>5.3 Identification of Critical Path                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING<br>5.1 INTRODUCTION TO CRITICAL PATH METHOD<br>5.2 THE NETWORK DIAGRAM<br>5.3 IDENTIFICATION OF CRITICAL PATH<br>5.4 CRITICAL PATH AND PARALLEL PROGRAMS                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING<br>5.1 INTRODUCTION TO CRITICAL PATH METHOD<br>5.2 THE NETWORK DIAGRAM<br>5.3 IDENTIFICATION OF CRITICAL PATH<br>5.4 CRITICAL PATH AND PARALLEL PROGRAMS<br>5.5 APPLICATION OF CPM TO PARALLEL PROGRAMS                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING<br>5.1 INTRODUCTION TO CRITICAL PATH METHOD<br>5.2 THE NETWORK DIAGRAM<br>5.3 IDENTIFICATION OF CRITICAL PATH<br>5.4 CRITICAL PATH AND PARALLEL PROGRAMS<br>5.5 APPLICATION OF CPM TO PARALLEL PROGRAMS<br>5.6 MAPPING OF PARALLEL TASKS                                                                                                                                                                                                                                                                                                         |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING<br>5.1 INTRODUCTION TO CRITICAL PATH METHOD<br>5.2 THE NETWORK DIAGRAM<br>5.3 IDENTIFICATION OF CRITICAL PATH<br>5.4 CRITICAL PATH AND PARALLEL PROGRAMS<br>5.5 APPLICATION OF CPM TO PARALLEL PROGRAMS<br>5.6 MAPPING OF PARALLEL TASKS<br>5.7 SCHEDULING OF PARALLEL TASKS                                                                                                                                                                                                                                                                     |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING<br>5.1 INTRODUCTION TO CRITICAL PATH METHOD<br>5.2 THE NETWORK DIAGRAM<br>5.3 IDENTIFICATION OF CRITICAL PATH<br>5.4 CRITICAL PATH AND PARALLEL PROGRAMS<br>5.5 APPLICATION OF CPM TO PARALLEL PROGRAMS<br>5.6 MAPPING OF PARALLEL TASKS<br>5.7 SCHEDULING OF PARALLEL TASKS<br>5.7.1 RULES OF SCHEDULING:                                                                                                                                                                                                                                       |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING<br>5.1 INTRODUCTION TO CRITICAL PATH METHOD<br>5.2 THE NETWORK DIAGRAM<br>5.3 IDENTIFICATION OF CRITICAL PATH<br>5.4 CRITICAL PATH AND PARALLEL PROGRAMS<br>5.5 APPLICATION OF CPM TO PARALLEL PROGRAMS<br>5.6 MAPPING OF PARALLEL TASKS<br>5.7 SCHEDULING OF PARALLEL TASKS<br>5.7.1 RULES OF SCHEDULING:<br>5.7.2 OPTIMAL SCHEDULE:                                                                                                                                                                                                            |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING<br>5.1 INTRODUCTION TO CRITICAL PATH METHOD<br>5.2 THE NETWORK DIAGRAM<br>5.3 IDENTIFICATION OF CRITICAL PATH<br>5.4 CRITICAL PATH AND PARALLEL PROGRAMS<br>5.5 APPLICATION OF CPM TO PARALLEL PROGRAMS<br>5.6 MAPPING OF PARALLEL TASKS<br>5.7 SCHEDULING OF PARALLEL TASKS<br>5.7.1 RULES OF SCHEDULING:<br>5.7.2 OPTIMAL SCHEDULE:<br>5.7.3 SINGLE STATIC ALLOCATION                                                                                                                                                                          |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING         5.1 INTRODUCTION TO CRITICAL PATH METHOD         5.2 THE NETWORK DIAGRAM.         5.3 IDENTIFICATION OF CRITICAL PATH.         5.4 CRITICAL PATH AND PARALLEL PROGRAMS.         5.5 APPLICATION OF CPM TO PARALLEL PROGRAMS.         5.6 MAPPING OF PARALLEL TASKS         5.7 SCHEDULING OF PARALLEL TASKS.         5.7.1 RULES OF SCHEDULING:         5.7.2 OPTIMAL SCHEDULE:         5.7.3 SINGLE STATIC ALLOCATION         5.8 SCHEDULING THE BACKSUBSTITUTION ALGORITHM USING CRITICA         METHOD.         5.9 SIMULATION METHOD |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72<br>73<br>73<br>73<br>74<br>74<br>75<br>78<br>79<br>81<br>81<br>81<br>82<br>82<br>82<br>83<br>L PATH<br>84<br>86<br>87                         |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72<br>73<br>73<br>73<br>74<br>74<br>75<br>78<br>79<br>81<br>81<br>81<br>81<br>82<br>82<br>82<br>83<br>L PATH<br>84<br>83<br>87<br>83<br>87<br>88 |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72<br>73<br>73<br>73<br>74<br>74<br>75<br>78<br>79<br>81<br>81<br>81<br>82<br>82<br>82<br>83<br>L PATH<br>84<br>83<br>87<br>83                   |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72<br>73<br>73<br>73<br>74<br>74<br>75<br>78<br>79<br>81<br>81<br>81<br>82<br>82<br>82<br>82<br>83<br>L PATH<br>84<br>86<br>87                   |

| 5.0 CRITICAL PATH METHOD AND SCHEDULING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72<br>73<br>73<br>73<br>74<br>74<br>75<br>78<br>79<br>81<br>81<br>81<br>82<br>82<br>82<br>83<br>L PATH<br>84<br>83<br>87<br>83                   |