**University of Bath**

#### PHD

### A mems approach to submillimetre-wave frequency multiplier design

Partridge, James G.

Award date: 2000

Awarding institution: University of Bath

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# A MEMS APPROACH TO SUBMILLIMETRE-WAVE FREQUENCY MULTIPLIER DESIGN.

Submitted by James G. Partridge for the degree of PhD of the University of Bath 2000

#### COPYRIGHT

Attention is drawn to the fact that copyright of this thesis rests with its author. This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author. This thesis may be made available for consultation within the University Library and may be photocopied or lent to other libraries for the purposes of consultation.

24 Varbicke

UMI Number: U601746

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI U601746 Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author. Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

| UN |     | SITY | OF BAT<br>RY | <b>H</b> |

|----|-----|------|--------------|----------|

| 45 | 20  | JUN  | 2001         |          |

|    | PHD |      |              |          |

# Abstract

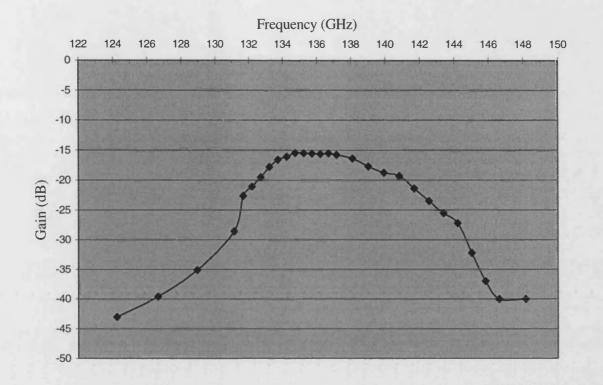

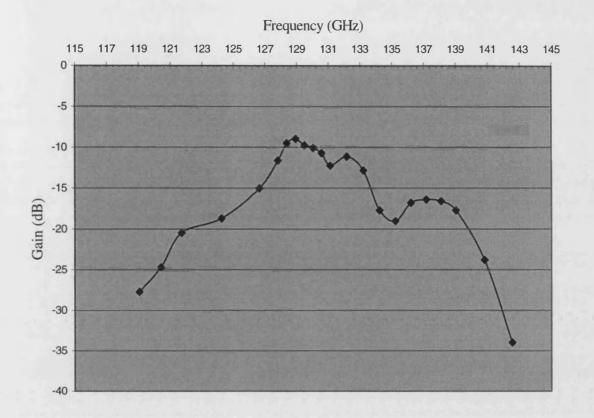

This thesis describes an investigation into micromachined integrated submillimetre wave components. The main focus of the work has been on the development of a micromachined frequency tripler (output frequency 810GHz) based on a Schottky varactor diode with a novel integrated device contact. The associated design and fabrication methods are described. Due to the lack of availability of a suitable pump source, RF measurements were not possible within the duration of the project. A micromachined frequency doubler operating with lower fundamental input frequency will undergo RF testing in the near future. Passive components including tuning stubs and rectangular waveguide bandpass filters have been fabricated using Epon SU8 epoxy resist. Transmission tests were performed on micromachined D-band waveguides and iris-coupled waveguide filters with pass-band centre frequencies of 135GHz.

# Contents

| 1. INTRO | DUCTION                                                 |

|----------|---------------------------------------------------------|

| 1.1 App  | LICATION OF TERAHERTZ FREQUENCY TECHNIQUES1             |

| 1.2 AVA  | AILABLE TECHNOLOGY                                      |

| 1.2.1    | Solid state sources                                     |

| 1.2.2    | The requirement for frequency multipliers               |

| 1.3 BAS  | SIC RECEIVER SYSTEMS                                    |

| 1.3.1    | Schottky barrier diode mixer receivers9                 |

| 1.3.2    | Superconducting mixer receivers                         |

| 1.3.3    | Schottky varactor diodes for frequency multiplication11 |

| 1.4 Fre  | QUENCY MULTIPLIER CONSTRUCTION                          |

| 1.5 Spl  | IT-BLOCK VERSUS MEMS                                    |

| 1.6 ME   | MS (MICRO-ELECTROMECHANICAL-MACHINED-SYSTEMS)           |

| 1.6.1    | Bulk micromachining16                                   |

| 1.6.2    | Surface micromachining16                                |

|          | CROMACHINING FOR TERAHERTZ APPLICATIONS                 |

| 1.8 The  | SIS OVERVIEW                                            |

| SECTION  | REFERENCES                                              |

|          |                                                         |

| 2. DEVIC | E THEORY AND DESIGN26                                   |

| 2.1 Fre  | QUENCY MULTIPLIERS                                      |

| 2.2 The  | SCHOTTKY BARRIER                                        |

| 2.2.1    | Formation of the barrier                                |

| 2.2.2    | Current-transport mechanisms                            |

| 2.2.3    | Emission over the barrier                               |

| 2.2.4    | Tunnelling through the barrier                          |

| 2.2.5    | Generalised IV relationship                             |

| 2.2.6    | Reverse characteristics                                 |

| 2.3 Mu   | LTIPLICATION USING NONLINEAR CHARGE/VOLTAGE OPERATION   |

| 2.4 LAY  | YER STRUCTURE AND JUNCTION DIAMETER                     |

| 2.5 PRA  | ACTICAL ASPECTS OF SCHOTTKY CONTACT FABRICATION         |

| 2.5.1    | Anodic etching of GaAs anode interfaces                 |

|      | 2.5.4        | Temperature effects for various metallisation schemes   | 46           |

|------|--------------|---------------------------------------------------------|--------------|

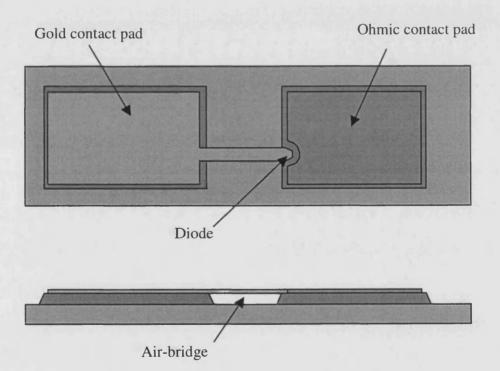

| 2    | .6 Pl        | ANAR DIODE CONSTRUCTION                                 | 47           |

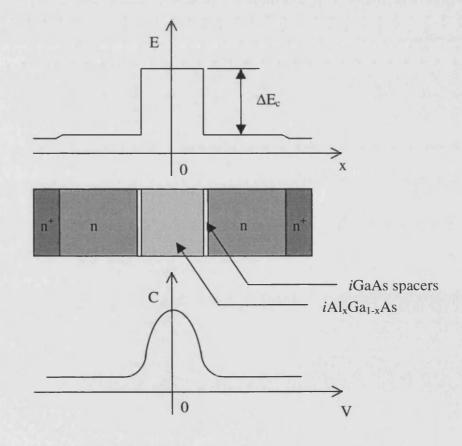

| 2    | .7 Hi        | ETEROSTRUCTURE VARACTOR DIODES                          | .49          |

| 2    | .8 Ci        | IAPTER SUMMARY                                          | .51          |

| S    | ECTIO        | N REFERENCES                                            | . 53         |

| 3. I | DESIG        | GN AND MODELLING                                        | . 58         |

| 3    | .1 Di        | ESIGN OF MICROMACHINED SUB-MM WAVE COMPONENTS           | . 58         |

|      | <i>3.1.1</i> | Advantages and limitations                              | . 58         |

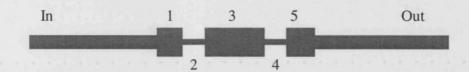

|      | 3.1.2        | Prototype multiplier circuits                           | . 59         |

| 3    | .2 M         | ODELLING METHODS                                        | . 60         |

| 3    | .3 Ti        | IE BURCKHARDT METHOD                                    | . 61         |

|      | 3.3.1        | Tripler and doubler designs                             | . 62         |

|      | 3.3.2        | 1-2-3 tripler                                           | . 62         |

|      | 3.3.3        | Doubler                                                 | . 65         |

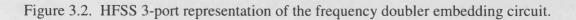

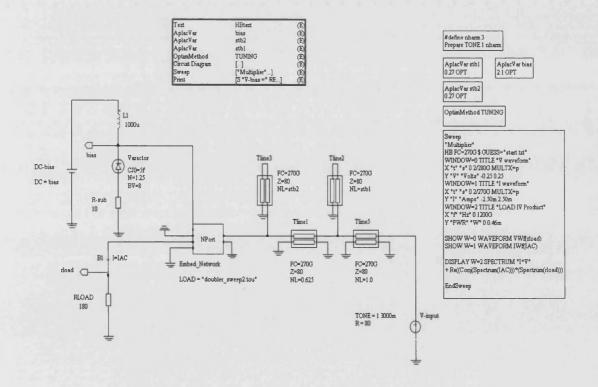

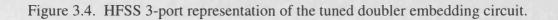

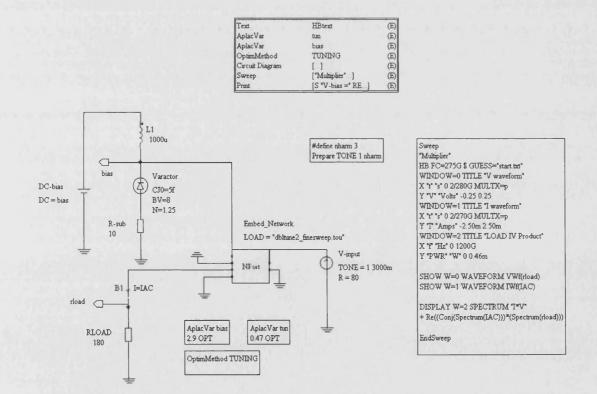

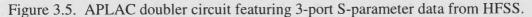

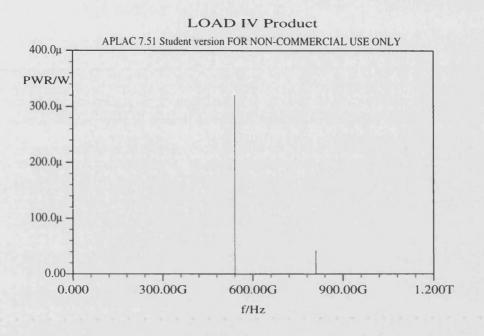

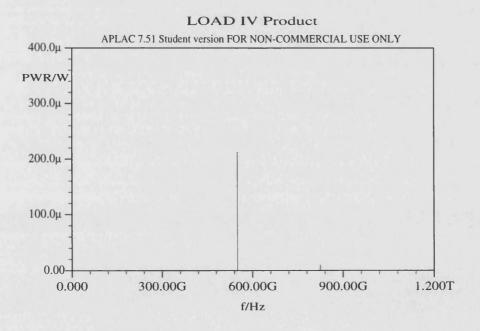

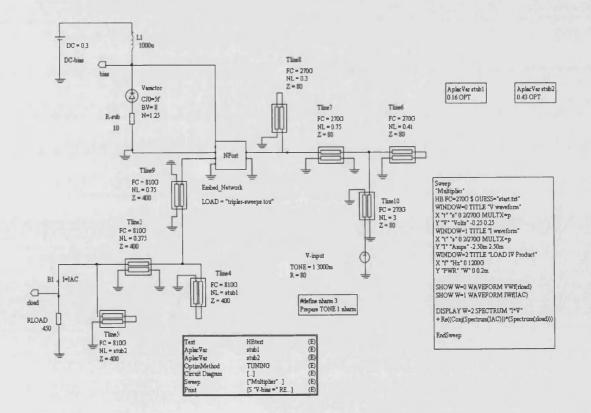

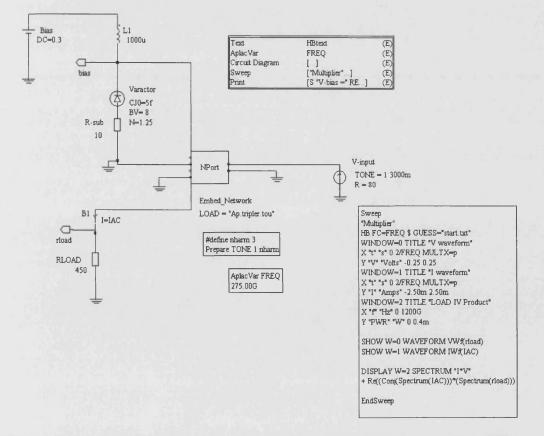

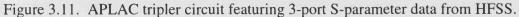

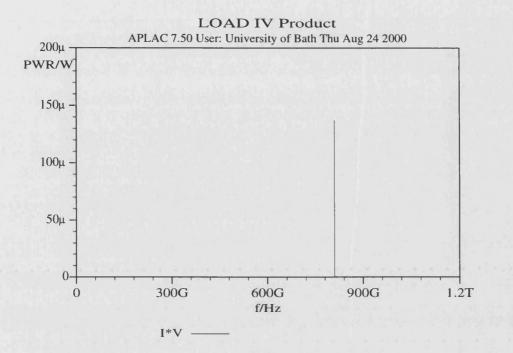

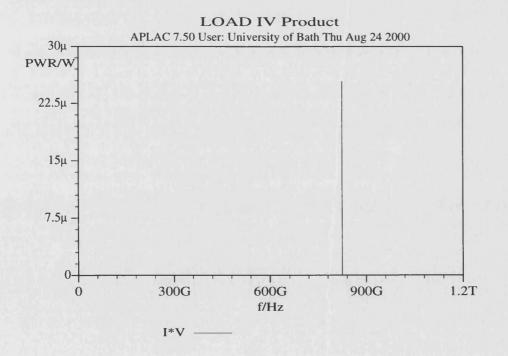

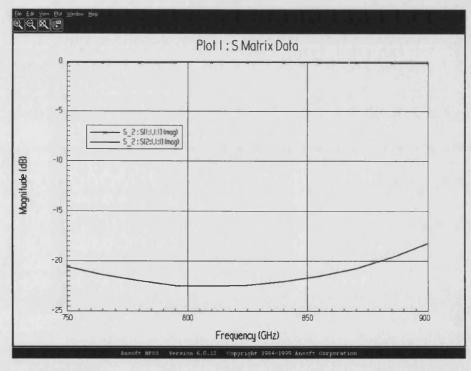

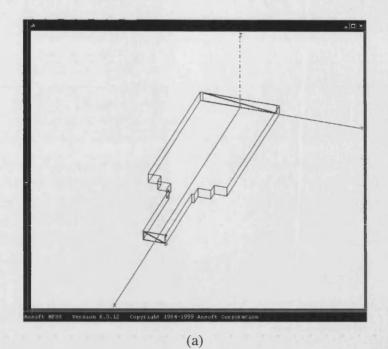

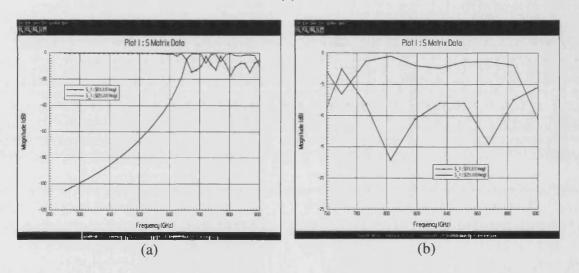

| 3    | .4 H         | FSS and APLAC modelling                                 | . 67         |

| 3    | .5 St        | JMMARY                                                  | .77          |

| 3    | .6 M         | ICROWAVE AND SUB-MM WAVE FILTERS                        | . 80         |

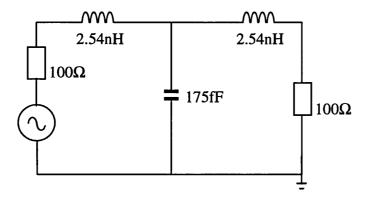

|      | 3.6.1        | Low frequency filter implementation                     | . 80         |

|      | 3.6.2        | A lumped element low-pass filter                        | . 81         |

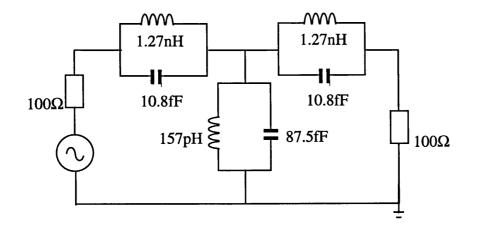

|      | 3.6.3        | Low-pass transformation to band-pass                    | . 82         |

|      | 3.6.4        | Impedance inversion                                     | . 83         |

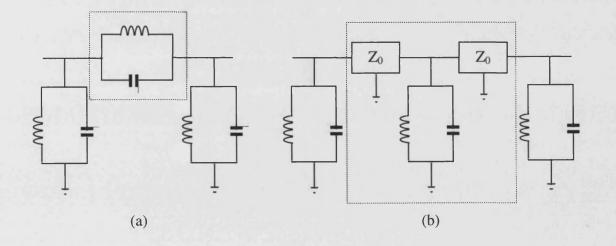

| 3    | .7 C         | OUPLED RESONATOR WAVEGUIDE FILTERS                      | . 84         |

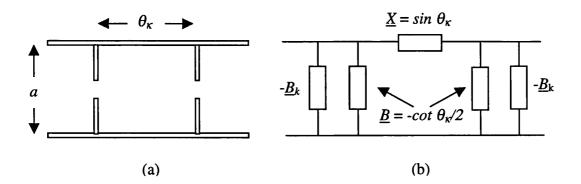

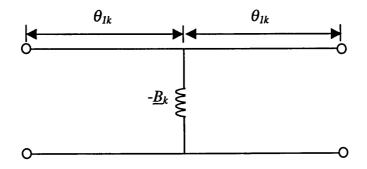

|      | 3.7.1        | Overview of direct-coupled resonator filter design      | . 85         |

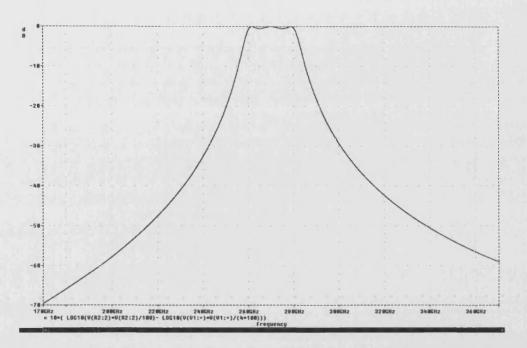

| 3    | .8 ST        | RIPLINE FILTERS                                         | . 89         |

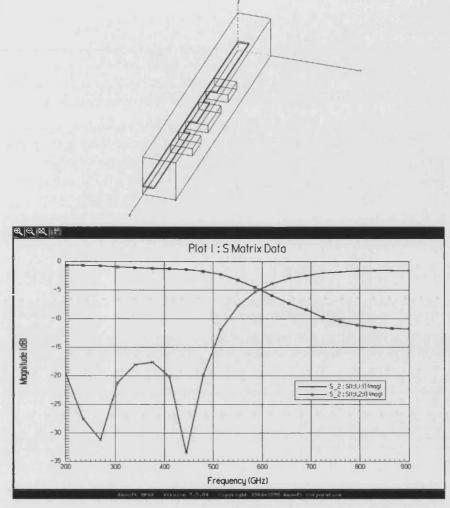

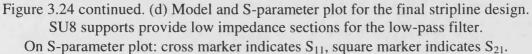

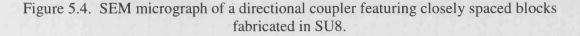

|      | 3.8.1        | Air-bridged stripline filter using SU8 support blocks   | . 91         |

| 3    | .7 W         | AVEGUIDE TUNERS                                         | . 94         |

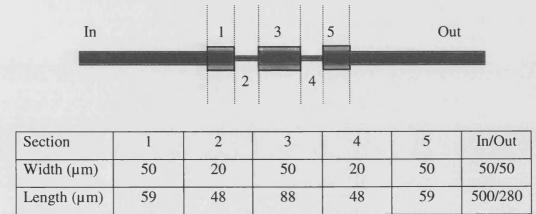

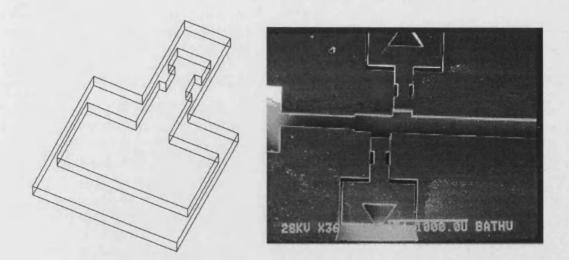

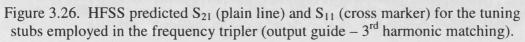

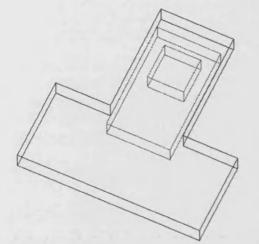

|      | 3.7.1        | Tuning stubs fabricated in SU8                          | . 95         |

|      | 3.7.2        | Prixed versus tuneable stubs for multiplier application | . <b>9</b> 8 |

| 3    | .8 W         | AVEGUIDE TRANSFORMER DESIGN                             | . 99         |

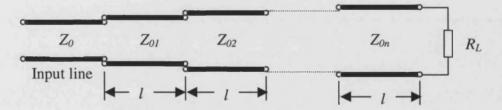

|      | 3.8.1        | Multisection transmission line transformers             | . 99         |

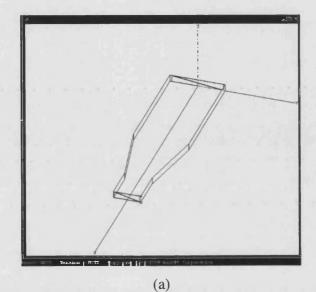

|      | 3.8.2        | 2 Tapered-line transformers                             | 101          |

| S    | ECTIC        | N REFERENCES                                            | 103          |

•

| 4. | FABRI    | CATION                                                  | 105 |

|----|----------|---------------------------------------------------------|-----|

|    | 4.1 Рно  | TOLITHOGRAPHY: AN OVERVIEW                              | 105 |

|    | 4.1.1    | Conventional photoresist                                | 105 |

|    | 4.1.2    | Equipment                                               | 106 |

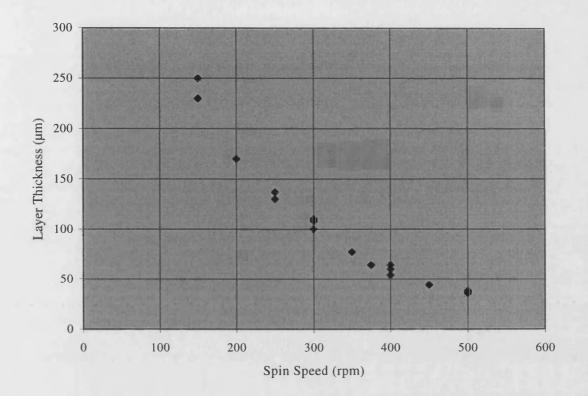

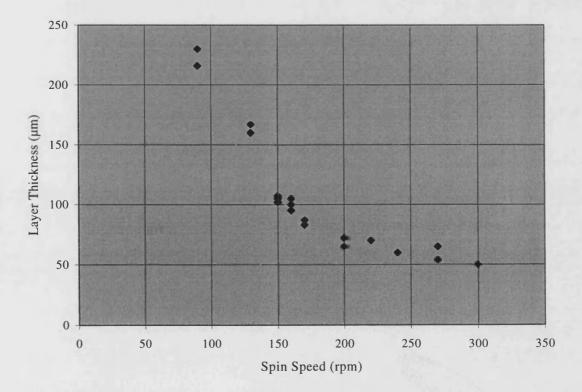

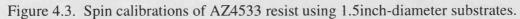

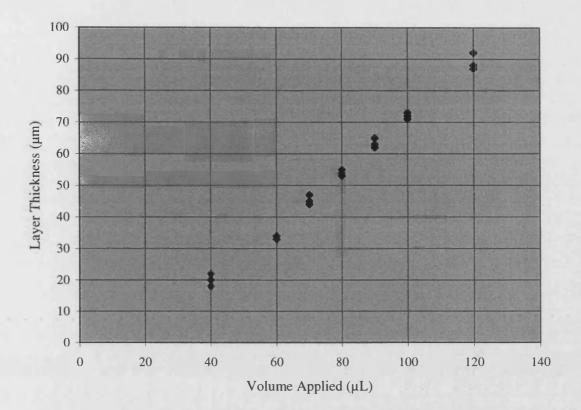

|    | 4.2 Thi  | CK RESIST PROCESSING USING STANDARD POSITIVE RESISTS    | 107 |

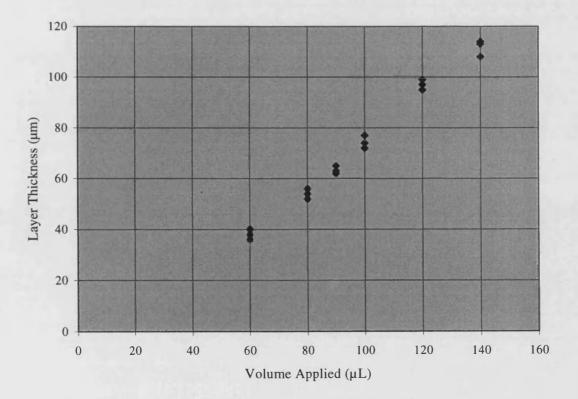

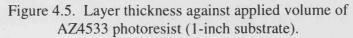

|    | 4.2.1    | Application and baking                                  | 107 |

|    | 4.2.2    | Exposure and development                                | 112 |

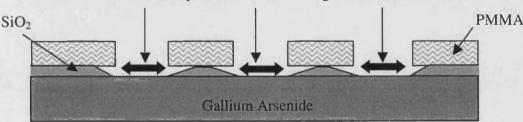

|    | 4.3 Gre  | EYSCALE AND CONTROLLED EXPOSURE TECHNIQUES              | 113 |

|    | 4.3.1    | Greyscale technique                                     | 113 |

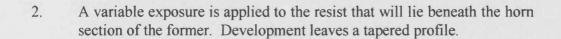

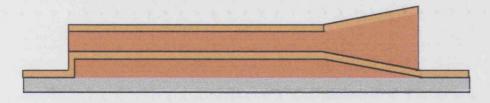

|    | 4.3.2    | Controlled exposure method                              | 114 |

|    | 4.3.3    | Conclusion on greyscale and controlled exposure methods | 116 |

|    | 4.3.4    | Fabrication sequence for tapered feed horn              | 116 |

|    | 4.4 SU8  | 3 NEGATIVE RESIST FOR MEMS APPLICATIONS                 | 118 |

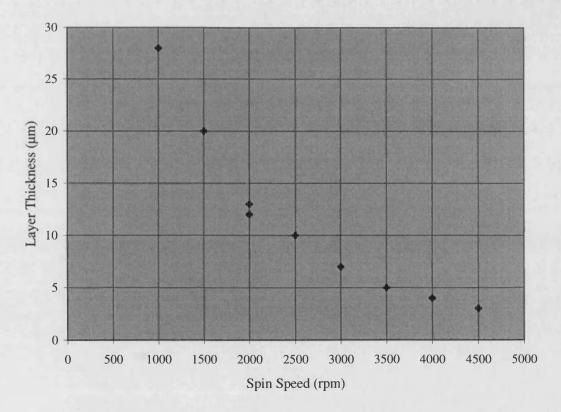

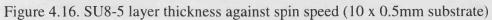

|    | 4.4.1    | SU8 processing                                          | 119 |

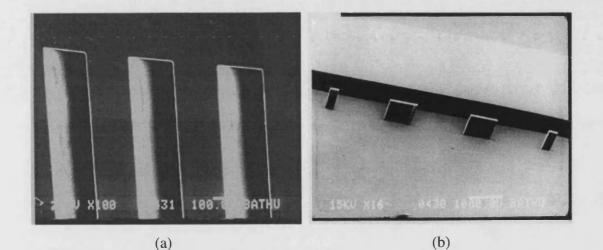

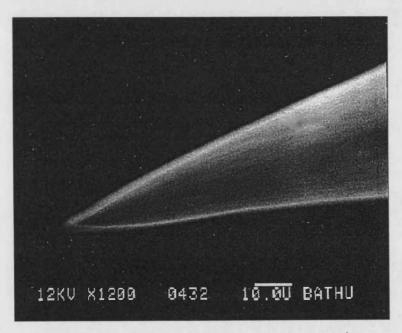

|    | 4.5 The  | ELECTROPLATED WHISKER METHOD                            | 124 |

|    | 4.6 The  | DROP-PLATING METHOD                                     | 126 |

|    | 4.7 Pro  | CESSING SEQUENCE FOR SCHOTTKY ANODE FORMATION           | 126 |

|    | 4.7.1    | Passivation and ohmic contacts                          | 126 |

|    | 4.7.2    | Anode via-hole etching                                  | 127 |

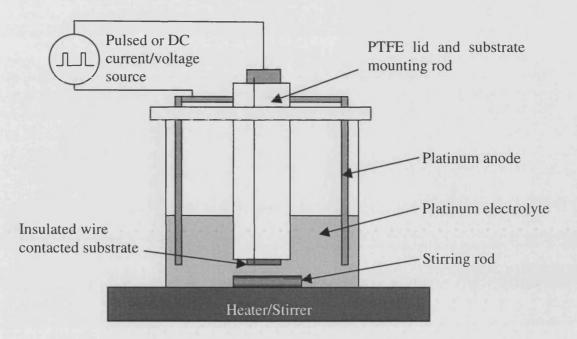

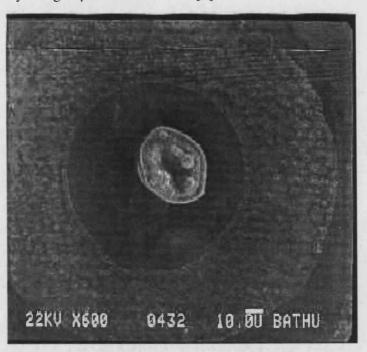

|    | 4.7.3    | Electroplating platinum anodes                          | 128 |

|    | 4.7.4    | Evaporated anodes                                       | 129 |

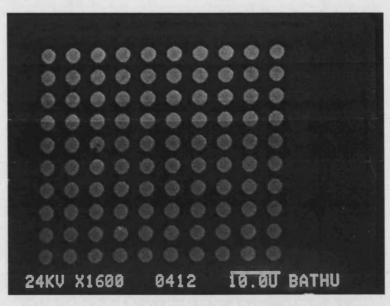

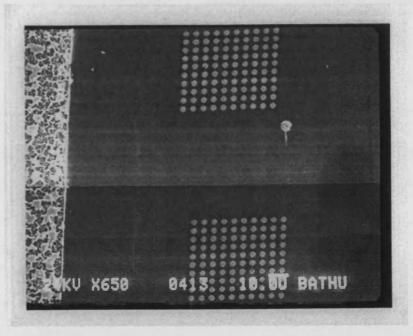

|    | 4.8 Ele  | CTRON BEAM LITHOGRAPHY                                  | 131 |

|    | 4.8.1    | Conclusions drawn from electron beam lithography        | 133 |

|    | 4.9 INT  | RODUCTION TO FABRICATION SCHEMES                        | 134 |

|    | 4.10 Prc | CESSING SCHEME FOR INTEGRATED FREQUENCY TRIPLER         | 135 |

|    | 4.11 Pro | CESSING SCHEME FOR INTEGRATED FREQUENCY DOUBLER         | 138 |

|    | 4.12 DE1 | TECTOR FABRICATION                                      | 141 |

|    | 4.13 Pro | CESSING SCHEME FOR TUNING STUBS                         | 143 |

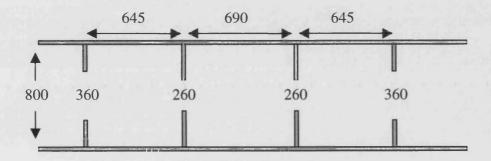

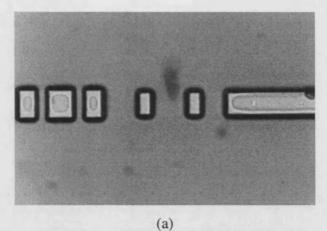

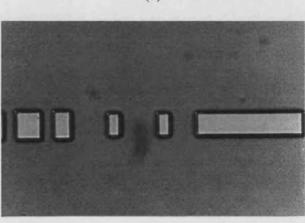

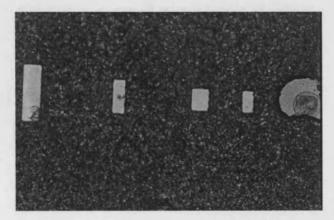

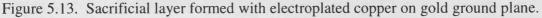

|    | 4.14 135 | GHz INDUCTIVE IRIS COUPLED BANDPASS FILTER              | 145 |

|    | 4.15 Fae | BRICATION SEQUENCE FOR E-PLANE SEPTA COMPONENTS         | 148 |

|    | SECTION  | References                                              | 151 |

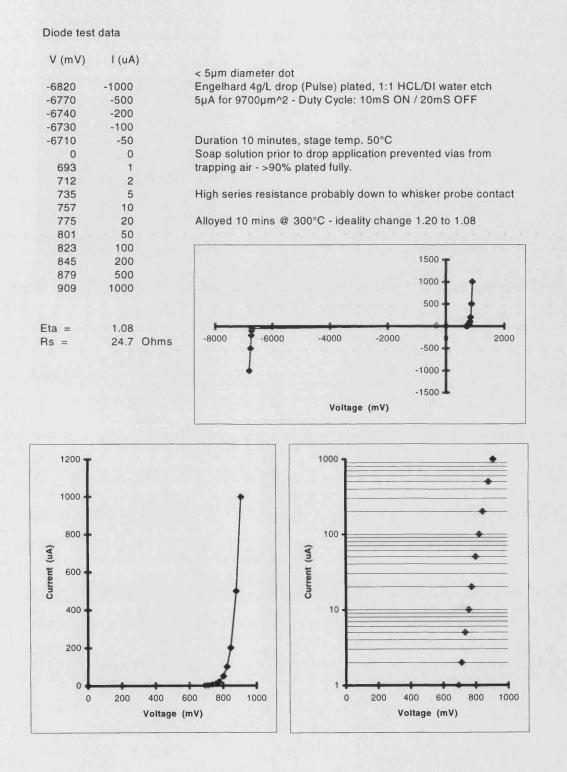

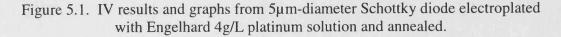

| RESULTS                                       | 153 |

|-----------------------------------------------|-----|

| 5.1 DIODE PROCESSING AND CHARACTERISTICS      | 153 |

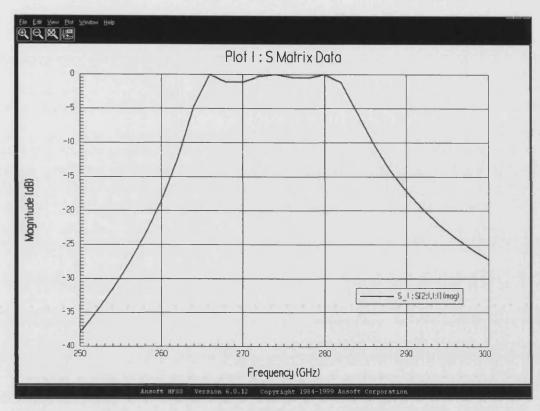

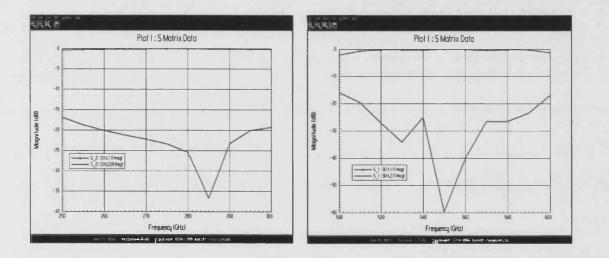

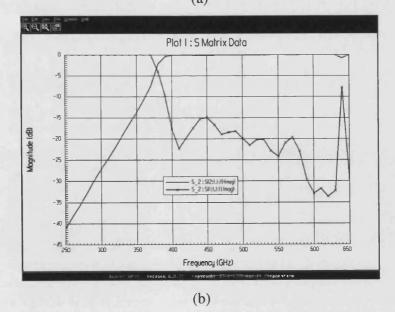

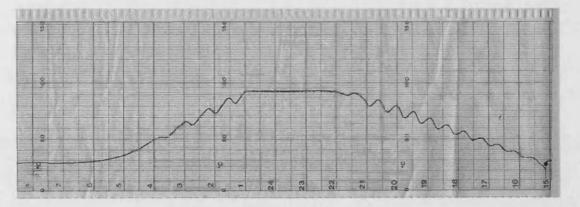

| 5.3 RF results                                | 163 |

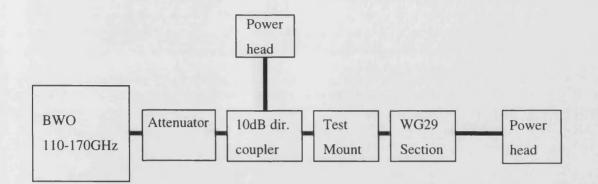

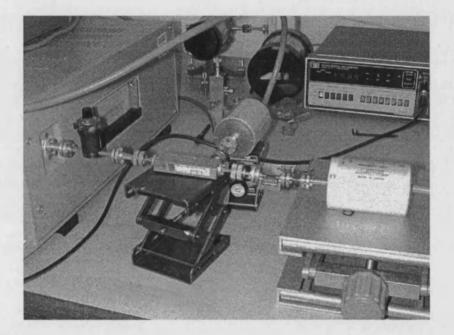

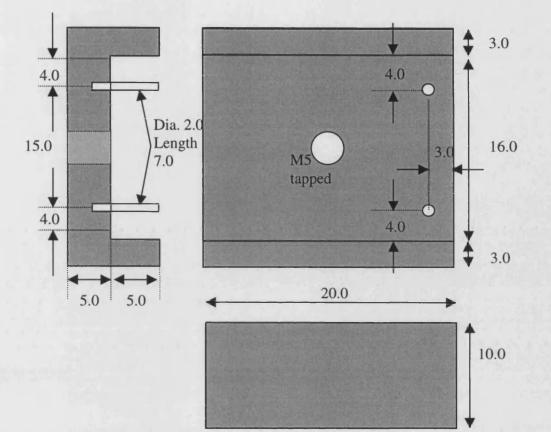

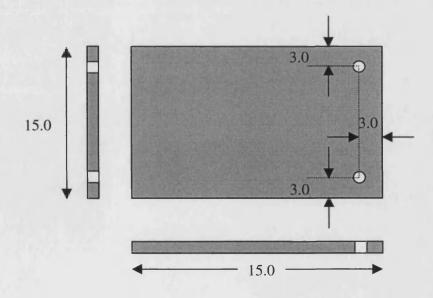

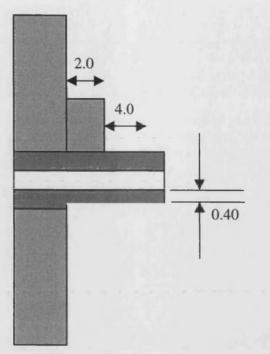

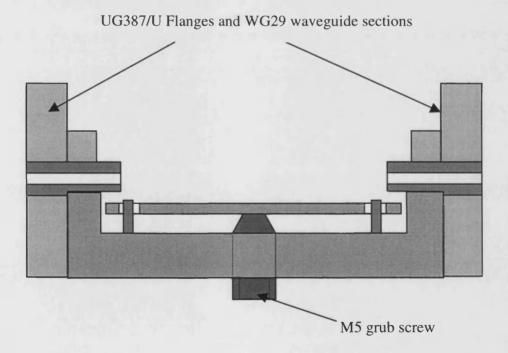

| 5.3.1 RF test apparatus                       | 163 |

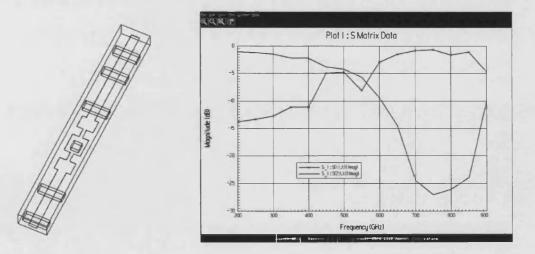

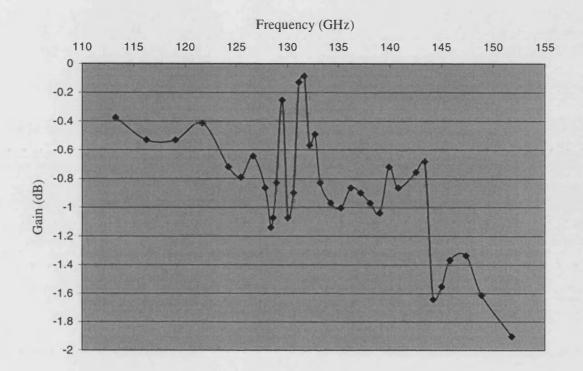

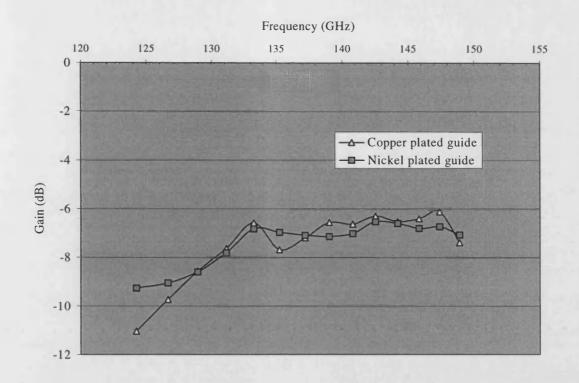

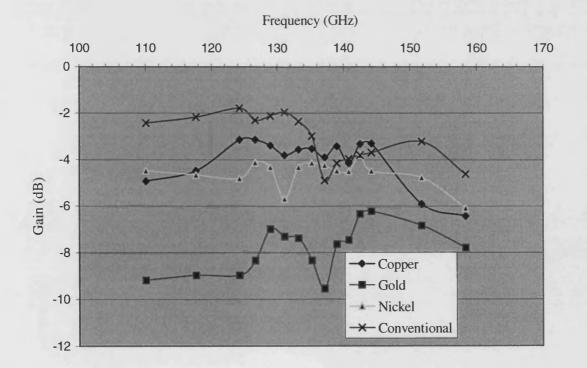

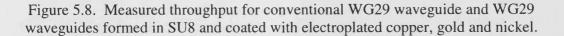

| 5.3.2 Coated SU8 waveguides                   | 165 |

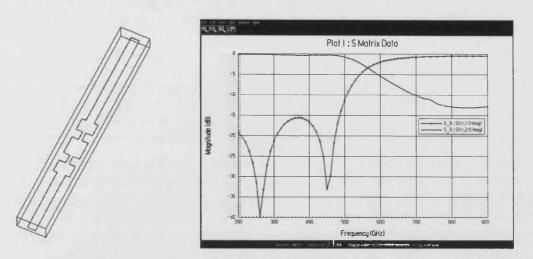

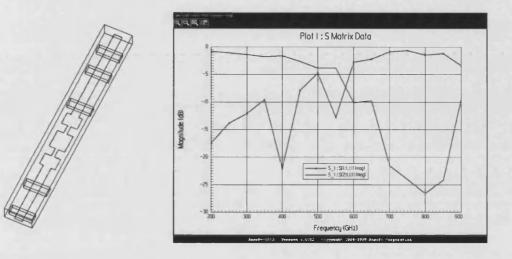

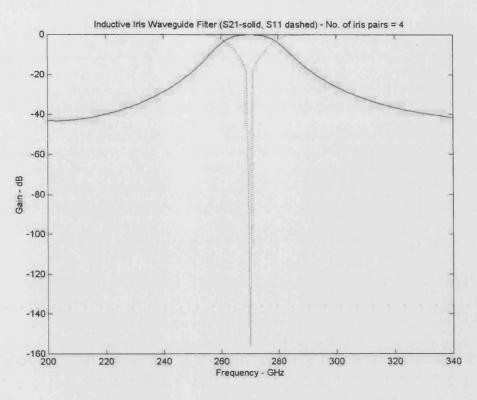

| 5.3.3 Coated SU8 iris resonator filters       | 168 |

| 5.4 AIR-BRIDGE STRIPLINE                      |     |

| Section References                            |     |

| CONCLUSION                                    | 175 |

| 6.1 SCHOTTKY DIODE AND CONTACT POST FORMATION | 175 |

| 6.2 | RF RESULTS         |  |

|-----|--------------------|--|

| 6.3 | CONCLUDING REMARKS |  |

| 6.4 | FUTURE WORK        |  |

|     |                    |  |

| PUBLICATIONS     |     |

|------------------|-----|

| ACKNOWLEDGEMENTS |     |

| APPENDIX 1       |     |

| APPENDIX 2       | 190 |

| APPENDIX 3       |     |

# 1. Introduction

The first pages of this introductory chapter aim to describe existing and proposed applications of terahertz frequency systems. The techniques used to machine these components are described in section 1.2 and typical components are illustrated. An overview of MEMS (Micro-Electro-Mechanical-Structures) then follows, since this technology has provided the necessary methods for forming many of the structures featured in this thesis. Finally, a summary of the contents of the remaining chapters is provided.

# **1.1** Application of terahertz frequency techniques

#### Radioastronomy

The developing fields of submillimetre and terahertz astronomy depend upon sensitive receivers, large accurate telescopes and good ground-based or space-borne observing platforms. This part of the spectrum is important for studies of the early stages of star formation in interstellar molecular clouds and nearby galaxies, and for observations of the cosmic background radiation [1].

For astronomical and remote sensing applications, the lowest noise and highest sensitivity is usually required, often necessitating the use of cooled detectors. For molecular line astronomy, high spectral resolution  $(f/\Delta f \sim 10^6)$  is also needed. Submillimetre-wave spectroscopy can be used to study spectral lines occurring due to rotational transitions of simple molecules, such as <sup>12</sup>CO, <sup>13</sup>CO, HCO<sup>+</sup>, CN and many others found in the interstellar medium. Such molecules are normally found in trace  $(<10^{-4})$  quantities, embedded in interstellar clouds of molecular hydrogen. Detailed analysis of the spectral line shapes can be used to determine, for example, temperatures, densities and motions of the material making up the molecular cloud. Physical and chemical models representing conditions within the cloud can be built up through observations of differing molecular species and of different transitions of the same molecular species. Different molecular species will tend to have different degrees of opacity (optical depth) to the electromagnetic radiation; observations made of different species can often be used to trace out gas distribution in different parts of

the cloud. Observations of different transitions of the same molecular species can be used to determine the state of excitation of that species within the cloud. Simple rotational spectra of linear molecules are characterised by a series of harmonically related frequencies, given by  $f = Jh / 4 \pi^2 I$ , where J is an integer, h is Planck's constant and I is the molecular moment of inertia. Thus, observations of higher transition lines at higher frequencies can be used to probe regions of high excitation.

Diffuse molecular clouds collapse under their self-gravitational attraction. Gravitational instability can lead to the formation of clumps of material within the cloud, out of which protostars are formed. The ionization by ultra-violet radiation and cosmic rays of atoms and molecules within these regions leads to a complex chemistry. Of key importance in understanding this chemistry is the study of carbon, both in atomic form (e.g. as neutral carbon CI) and in molecular form (e.g. as CO).

Recently, much attention has been given to the study of neutral carbon in molecular clouds. Observations of the  ${}^{3}P_{1} \rightarrow {}^{3}P_{0}$  transition of CI at 492GHz have shown that its distribution is widespread in interstellar molecular clouds [2] and external galaxies [3]. At 492GHz, CI has been readily detected in cold clouds, intermediate and high-mass clouds, bipolar outflows, carbon stars, shocked regions near supernovae and in external galaxies. The state of excitation is not established by observation of a single spectral line. CI in cool / tenuous regions congregates in the  ${}^{3}P_{0}$  ground state, producing high optical depth in the  ${}^{3}P_{1} \rightarrow {}^{3}P_{0}$  transition. When studying rotational spectra of molecules such as CO, it is customary to observe the optically thin lines of the weaker isomer  ${}^{13}$ C. At 492GHz, the  ${}^{13}$ C isotopic  ${}^{3}P_{1} \rightarrow {}^{3}P_{0}$  fine structure line lies only 1.6MHz away from the  ${}^{12}$ C line and cannot be resolved; the  ${}^{13}$ C 809GHz line has components up to 220MHz away. Complementary observations of the  ${}^{3}P_{2} \rightarrow {}^{3}P_{1}$  transition of CI at 809GHz would permit its state of excitation to be established and would also probe deeper into cool cloud cores.

The development of instrumentation for millimetre-wave astronomy is now fairly mature. It is important that technologies suitable for terahertz astronomy are similarly developed.

A number of ground based submillimetre telescopes are either in operation e.g. the James Clerk Maxwell Telescope (JCMT) and the Caltech Submillimeter Observatory, or under construction e.g. the SubMillimeter Array (SMA) of the Smithsonian Astrophysical Observatory. There are several space-borne missions planned by both ESA and NASA to carry submillimetre heterodyne receivers both for astronomy, e.g. FIRST (500-2000GHz), SMIM (400-1200GHz), LDR (300-3000GHz), and for remote sensing e.g. SOPRANO (500-1000GHz) and EOS-MLS (to 2.5THz).

Completed in 1987, the 15m diameter James Clerk Maxwell Telescope (JCMT) is still the world's largest facility designed specifically to operate in the sub-mm region of the spectrum. It is situated close to the summit of Mauna Kea, Hawaii, at an altitude of 4092m. At this height the telescope is above 97% of the water held in the atmosphere.

The JCMT operates facility heterodyne instruments [4] in four bands, A (215-275 GHz) [5], B (318-373GHz), C (430-510GHz) and D (630-710GHz). Major objects of study include stars in their earliest stages of formation, where they are surrounded by gas and dust disks that have not yet coallessed to form planets. Also taking up large amounts of telescope time are observations of extra-galactic objects. These studies are looking at overall star formation rates in different types of galaxies ranging from nearby to objects exhibiting high red-shift.

The space-borne Far InfraRed and Submillimetre Telescope (FIRST) is planned for launch in 2007 and carries the Heterodyne Instrument for *FIRST* (*HIFI*). This will cover at least the frequency range 492GHz to 1113GHz and will provide sensitive observations with resolving powers ranging from less than  $5x10^5$  to  $1.2x10^7$ . The instrument is optimised for the measurement of weak, broad spectral lines of distant galaxies and for performing fast line surveys of galactic objects [6].

SOFIA, the Stratospheric Observatory For Infrared Astronomy is a NASA operated Boeing 747 mounted high altitude telescope [7]. CASIMIR (CAltech Submillimeter and far-Infrared MIxing Receiver) is the submillimeter and far-infrared heterodyne receiver for SOFIA. This instrument will be used to study a wide range of astrophysical problems ranging from the evolution of galaxies to the birth and death of stars. The goal is to cover the 500-2100GHz frequency range in seven bands: SIS mixers in four bands up to 1200GHz, and HEB mixers in three bands covering 1200-2100GHz.

#### Atmospheric remote sensing

Absorption or emission lines corresponding to certain molecules in the Earth's atmosphere can be used to measure the density of these molecules or related parameters including temperature and pressure [8, 9]. Two methods are employed for attaining this data

- 1) Looking vertically through the atmosphere from ground based receivers.

- 2) Looking tangentially through the upper atmosphere with varying inclination, using satellite based receivers.

The latter method (known as limb-sounding), is a proven choice for observations investigating chemical and physical processes involved in ozone depletion and other reactions caused by air pollution. Many spectral lines that are observable at high altitude are not visible to ground based telescopes. The altitude range over which these measurements are made is typically 15-85km. In NASA's Upper Atmosphere Research Satellite (UARS) a multichannel instrument (63, 183 and 205GHz) is designed to measure ClO (25-45km), O<sub>3</sub> (15-80km) and H<sub>2</sub>O (15-85km) combined with pressure calculated from O<sub>2</sub> emission [10]. The European Submillimetre wave Atmospheric Sounder (SUMAS) has been operated on board a research aircraft at 10km. This instrument is equipped to measure, amongst others, the ClO molecular emission line at 649GHz [11].

#### Chemical and biological warfare agent detection

Terahertz technology is still waiting for a mass-market application. A possible first step in this direction comes from the defence market. In a paper by Woolard [12], terahertz spectroscopy is discussed with defensive military applications in mind.

The recent proliferation of chemical and biological agents as instruments of warfare and terrorism has lead the US Department of Defence to show considerable interest in the development of early warning systems for these agents. Very recent spectroscopic studies at millimetre- and submillimetre-wave have indicated that DNA (and possibly other cellular material) possesses large numbers of unique resonances due to localised phonon modes. Data is presented in [12] showing that in the 300-750GHz frequency range, unique contributions are visible from these localised phonons, arising from DNA base-pair interactions. These contributions are absent from far infrared data.

Technological challenges must be met before terahertz early warning systems are viable but considerable advancement of the terahertz field would almost certainly result from military backing.

#### Secure communications

The internet and mobile communications have become increasingly important as communications media in the modern world. There will continue to be an increasing demand for more services, faster access, combined with mobility and flexibility. The potential for submillimetre-wave wireless communication networks is very real. Certain applications can make use of the strong atmospheric absorption that occurs in parts of the millimetre and submillimetre spectrum. The high absorption and narrow beamwidths make these wavelengths well suited to applications such as covert, intrabuilding, high-speed, wireless communication links

#### **Plasma diagnostics**

By measuring the phase shift, absorption and scattering of millimetre wave radiation propagated through a plasma, it is possible to deduce the electron density and temperature of the plasma [13]. There is a region of extinction below a certain critical frequency ( $f_p$ ) which is dependent on the electron density ( $\rho_e$ ) such that

$$(f_p) = 8.974 \ \sqrt{\rho_e} \ \text{Hz.}$$

(1.1)

When electron densities reach  $10^{15}$  electrons/cm<sup>3</sup>, the critical frequency falls into the submillimetre wave range. An example application is within a Tokamak fusion reactor, where the plasma has a critical frequency within the submillimetre range and therefore requires a diagnostic system with an operating frequency exceeding this minimum [14].

Suzuki et al. [15] describe a fabrication process for submillimeter-wave detecting and mixing diodes with plasma diagnostics as a primary application. The devices are designed to exhibit low noise particularly in the image frequency (IF) range of plasma diagnostic systems (below 10MHz).

#### Mass market potential

Applications further down the frequency range (~100GHz) include vehicle avoidance systems and imaging systems to identify plastic guns and explosives in non-invasive security installations. In communications systems, higher frequencies offer greater bandwidth and speed (100s of megabits per second), higher antenna gain for a given antenna size, narrower antenna beam widths and smaller system size. If these applications are to be fully exploited inexpensive and reliable components and systems are necessary.

## **1.2** Available technology

The terahertz frequency region, usually defined as ranging from 100GHz-10THz, has not yet been opened up for commercial exploitation. One reason for this is the lack of availability of small solid-state power sources that operate at these frequencies. In addition, the technology required to form passive circuit components is expensive and time consuming. Addressing the source availability problem first, the following section describes current limits on devices that may have potential for future application in the submillimetre region.

#### **1.2.1** Solid state sources

Above 10THz the 'optical' region begins and is supported with developed devices such as near infra-red lasers and LEDs. Below this frequency point and above 250GHz, there is a region where useable solid-state sources do not exist [16]. A 712GHz RTD source [17] has been tested but the output power at that frequency was less than  $1\mu$ W. This falls short of the few hundred microwatts required for the most sensitive mixers operating at that frequency.

#### **Gunn diodes**

Gunn diodes are the standard choice for many millimetre-wave local oscillator applications and when allied to frequency multipliers can supply sufficient power for mixers operating at terahertz frequencies.

Fundamental to the operation of Gunn diode oscillators is the Negative Differential Region (NDR) in their IV characteristic. Tuning of the external circuit can change the resonant frequency of these transit-time devices and various modes of operation are

possible. DC to RF conversion efficiencies in the region of 1.2% have been reported for devices with operating frequencies exceeding 100GHz [18, 19].

State of the art performance of Gunn diodes has been achieved using n+/n/n+ structures with graded doping profiles. Attention paid to effective heat sinking has also proved valuable in optimising operating characteristics. Employing harmonic frequency generation has extended the upper frequency limit of these devices and output powers in the region of 1mW have been demonstrated at about 200GHz [20].

#### **Field Effect Transistors (FETs)**

This range of devices includes MESFETS (Metal Semiconductor FETs), HEMTS (High Electron MobilityTransistors) and pHEMTS (pseudomorphic High Electron Mobility Transistors). Recent developments in HEMT type structures indicate that they have the potential to operate in the terahertz region. Integrated circuits based on pHEMTS have been demonstrated at 140GHz and maximum operating frequencies of 800GHz are predicted [21]. As these devices are decreased in size in order to function at higher frequencies the demands on their fabrication processes become the limiting factor. Advances are continually being made in this area but these devices are subject to a  $1/f^2$  power scaling (common to all transit-time devices) that probably means signal processing will be a target application rather than power generation.

#### Heterojunction Bipolar Transistors (HBTs)

The cut-off frequencies for HBTs have not reached those of FET devices. Minimising the base width in these devices causes a reduction in surface recombination and increases the maximum operating frequency. With a base width of 5nm, the limit is now around 170GHz. It is unlikely then that the HBT will be considered over field effect devices for terahertz applications.

The vertical structure of the HBT does mean that multiple finger configurations can be implemented to increase device area and improve power handling. With this in mind the device is being considered for driving frequency multipliers.

#### **Resonant Tunnelling Diodes (RTDs)**

The resonant tunneling diode is a promising device for generating signals in the millimeter and submillimeter wave regions. However, the RTD has two problems. The first of these is its low output power. The second difficulty is that undesirable low frequency spurious oscillations often result from the RTD's inherently broadband negative differential resistance (NDR). To get more power, one solution is coherent power combining of multi-RTD's using a quasi-optical resonator.

A Fabry-Perot resonator with a grating has been reported for coherent power combining of a RTD array in the millimetre wave region [22]. Coherent power combining with two RTD's in the resonator was successfully observed at 75GHz. The authors have demonstrated a series configuration as a means to eliminate unwanted low frequency spurious oscillations and present some preliminary results.

#### **1.2.2** The requirement for frequency multipliers

Whilst continual improvement is being made in the fabrication technologies and maximum operating frequencies of the devices described in the previous section, there still exists a gap between 300GHz and 10THz where frequency multiplication is the only means of providing appreciable signal power. Frequency multipliers have been demonstrated up to and beyond 1THz [23, 24] and as such represent a vital means to bridge the terahertz gap. Section 1.3 provides an overview of heterodyne detection. The mechanical aspects of a frequency multiplier are reviewed in section 1.5.

### **1.3 Basic receiver systems**

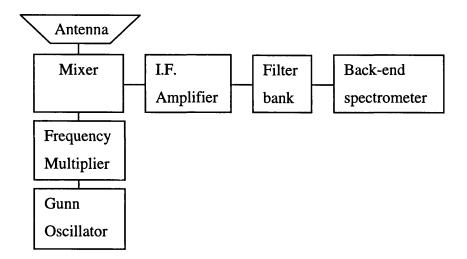

Figure 1.1 illustrates a simple heterodyne receiver system in block diagram form. The input signal is collected by the antenna and fed to the input of the mixer. A local oscillator (LO) signal is also fed to the input of the mixer and through non-linear mixing, difference and product frequencies are generated. The solid-state device chosen to perform the role of local oscillator is usually a Gunn diode, in which case the LO frequency will be limited to a maximum 160-200GHz and more typically around 100GHz. Receivers operating above 100GHz will normally feature diode frequency multipliers in the LO section.

Figure 1.1. Simple Heterodyne Receiver.

Assuming sufficient power is available from the LO chain, power at the mixer Intermediate Frequency (IF) is amplified and detected at the back-end spectrometer. At terahertz frequencies two distinct mixer types are available and these are described in the next sections. A brief description of the operation of a varactor as a frequencymultiplying device is given in section 1.3.3 with a more detailed analysis to be found in chapter two.

#### 1.3.1 Schottky barrier diode mixer receivers

Here, the incoming signal is mixed with the local oscillator using the non-linear I-V relation of a small-area GaAs Schottky barrier diode. At lower frequencies (< 500 GHz) the devices are normally waveguide mounted. Sliding tuners are conventionally used to optimise the embedding impedance seen by the diode. At higher frequencies, devices have traditionally been mounted in open-structure mounts, such as corner-cube reflectors, although the upper frequency limit on waveguide mount technology is being extended. Waveguide mounts permit the use of high quality corrugated feedhorns to couple radiation into the mixer. An extremely symmetric and well-defined beam pattern is critical in astronomy and remote sensing applications.

At higher frequencies (> 1 THz), GaAs Schottky diodes are the only currently viable mixer devices proven to operate satisfactorily. Diode mixers offer a well-established technology. The main limitations to the performance of these devices are their large

parasitic losses, compromising high frequency response and their large LO power requirements. Schottky diode mixers can be operated at room temperature but if they are cooled, typical operating temperatures are 77K and 20K (readily achieved using mechanical refrigerators). As a consequence of relaxed temperature requirements, Schottky diode mixer receivers are usually selected for space applications.

#### **1.3.2** Superconducting mixer receivers

The most sensitive heterodyne receivers for millimetre and submillimetre wavelengths use superconductor-insulator-superconductor (SIS) tunnel junctions as the mixing element. These devices consist of two superconducting electrodes separated by a thin (~ 2nm) insulating film. Typical double-sideband SIS receiver noise temperatures are  $T_R \approx 70$ K at 250GHz [25], 150K at 350GHz [26], 220K at 500GHz [27] and < 400K at 700GHz [28]. At frequencies where the photon energy exceeds the energy gap of the superconductor (> 700GHz for niobium) however, the performance of an SIS mixer falls off rapidly. DSB receiver noise temperature of 840K at 1040GHz has been reported using a Nb SIS mixer [29]. Operation at significantly higher frequencies will require the use of materials with higher superconducting transition temperatures.

An alternative type of superconducting detector has been proposed [30] that offers great potential as a mixer for terahertz frequencies. The device, a superconducting transition-edge microbolometer, consists of a short (<  $0.50 \,\mu$ m), narrow (~  $0.15 \,\mu$ m), thin (~ 10nm) superconducting microbridge contacted by thick normal metal (gold) films that connect to the RF coupling structure (e.g. waveguide mount; integrated antenna). These devices rely upon electron heating effects and are not limited by the superconducting energy gap. The devices must be small to generate sufficient IF bandwidth to be useful for astronomy and remote sensing applications. A DSB receiver noise temperature of  $T_R \sim 650$ K at 533GHz at an IF of 1.4GHz has been reported [31].

SIS mixers are the first choice for low-noise operation, but need cooling to around 4K, as do transition-edge microbolometers.

#### **1.3.3** Schottky varactor diodes for frequency multiplication

Chapter two describes the surrounding theory behind these devices but for the present it is sufficient to say that they provide harmonic multiplication above a fundamental RF input signal through the non-linear charge/voltage characteristic of a reverse biased Schottky barrier. This frequency conversion can in theory be 100% efficient due to the purely reactive nature of the reverse biased junction. This ideal is never achieved due to the substrate resistance associated with these devices and the stringent harmonic matching requirements that are imposed by the inherently narrow-band varactor. As with mixer (varistor) diodes, varactor diodes function at room temperature, although benefits in noise reduction can be gained if cooling is possible.

#### **1.4** Frequency multiplier construction

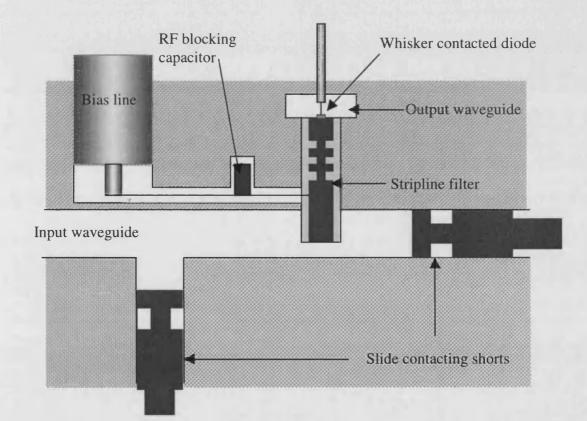

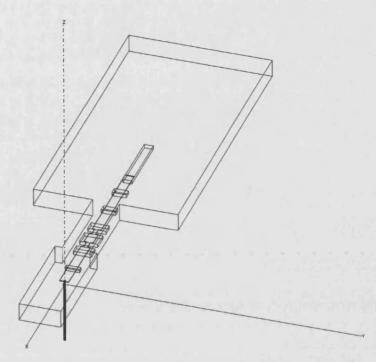

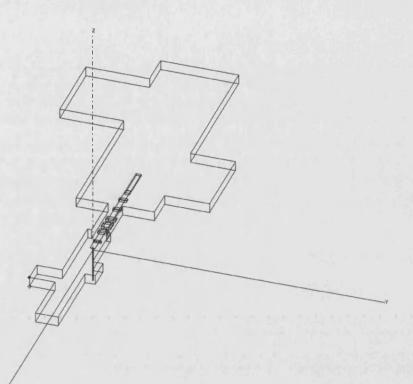

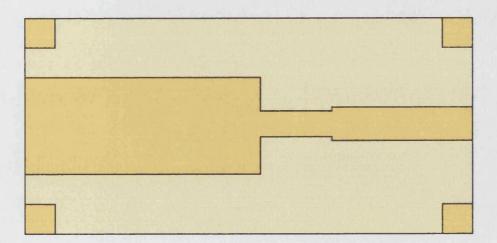

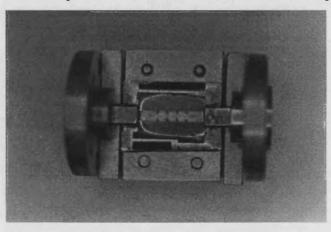

Figure 1.2. Schematic diagram illustrating a crossed waveguide multiplier with stripline coupling between the input and output guides.

Fig. 1.2 shows a typical crossed waveguide multiplier block design. This design was first employed by Takada et al. [32] and has been popularised by Archer [33]. It is now a proven performer for submillimetre multipliers. The design features sliding

tuners on the input waveguide that allow optimum tuning at the plane of the waveguide/stripline transition. The diode chip (featuring an array of similar devices) is housed in the output waveguide and is contacted by a whisker wire with a sparkeroded or chemically etched tip. An ohmic contact on the reverse side of the diode chip contacts to the stripline filter which is designed to transmit fundamental power, whilst reflecting the desired harmonic output frequency. Bias is provided via the whisker post and a contact to the stripline filter. RF rejection is performed by a coaxial cavity filter around the whisker post and a capacitor that transforms to a RF open circuit at the coaxial-line/stripline junction.

Erickson [34] has employed a similar multiplier configuration. This design is again based on crossed waveguides but a coaxial rather than stripline filter provides the frequency dependent connection.

The crossed waveguide mount has a proven record and has been a standard choice in many millimetre and submillimetre wave LO circuits. However different approaches have been sought in order to alleviate some of the problems experienced when forming crossed waveguide multiplier blocks.

Archer and Erickson designs are normally fabricated in 'split-block' form. The block is initially electroformed around a gold-coated mandrel of rectangular cross-section. This has the dimensions of the output waveguide and is usually etched out, leaving the gold coating inside the block. The block is then machined down to a regular shape and sliced perpendicularly to the output waveguide. The input waveguide, bias cavity and additional tuning cavities are then machined into the two halves of the block.

Edrich and Sanborn [35] presented an alternative layout for a frequency doubler (45-90GHz) utilising the properties of rectangular waveguide to provide the necessary input circuit harmonic rejection. The input waveguide featured a single sided E-plane taper ending in a cavity designed for rejection of the doubled output frequency (>16dB achieved) followed by the diode mounting area. The output waveguide extended from the diode region in line with the input waveguide and again featured a single sided taper to reach full height at the output port. The waveguide tapers facilitated improved impedance matching of the embedding circuit to the combined parallel diode pair used for harmonic multiplication.

Raisanen et al. [36] presented a novel approach to mixer and multiplier design based on a split-block. The design consisted of mirror image halves that were capable of being machined using either an endmill or a slitting saw, with no electroforming necessary. The input and output circuits of the doubler (110-220GHz) consisted of waveguide T-junctions. On the input side, tuners were mounted on two branches of the T with the feeding waveguide and a stripline probe located between them. The output circuit followed this arrangement with tuners situated around a planar diode chip and the output guide. A wide tuning range was obtained using this layout and waveguide lengths were minimal thereby reducing ohmic loss.

Newman and Erickson presented a design in 1999 [37] for a planar multiplier based around an antiseries diode configuration. Separate blocks based on the same configuration were produced for doublers with output frequencies of 160GHz and 320GHz. The input waveguide features multiple E-plane waveguide bends in order to reduce the overall size of the block. A dual stepped E-plane impedance transformer matches the input and diode circuit impedances. The diode chip is located in a cavity between the input waveguide and the quartz stripline filter feeding the output waveguide. A dual step E-plane waveguide transformer is again implemented for improved matching on the output waveguide. The stripline filter extends through a cavity and provides a path for the DC bias.

The designs reviewed above all feature waveguide input and output circuits machined or electroformed in metal. The Edrich design dispenses with coaxial/stripline harmonic filtering, instead achieving this design requirement via waveguide cavities. This approach could prove useful at terahertz frequencies due to its inherently lower loss. The in-line arrangement of the input and output circuits is also a departure from the crossed guides which feature in standard split-blocks. Edrich relied upon rigorous optimisation pre-production, rather than including multiple tuning circuits. Nowadays Finite Element Method (FEM) electromagnetic simulators allow designs to be optimised prior to fabrication, so in principle it is possible to design efficient fixedtuned multipliers before any machining takes place. At terahertz frequencies, tuning elements are difficult to make and incur appreciable loss. If designs are not totally fixed-tuned, alternative approaches to circuit tuning may be necessary.

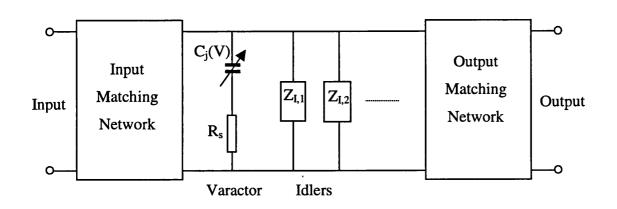

Multipliers designed for harmonic output above the second (triplers, quadruplers and quintuplers) have circuits that are further complicated by a requirement to provide current flow at certain intermediate harmonic frequencies. This requirement is discussed in terms of the varactor diode characteristic in section 2.3 and in terms of the external circuit in section 3.3.

## 1.5 Split-block versus MEMS

The technology behind split-block multipliers is now mature and the designs described in the preceding section illustrate innovative features that afford a wide tuning range and simplified machining requirements. However, the fact remains that as frequencies extend into the terahertz region, engineering tolerances become more stringent and forming waveguide circuit elements becomes increasingly difficult. In addition, once the block has been constructed mounting the diode chip can prove extremely difficult. The exact location of the diode can affect the circuit tuning capability and is therefore an important design parameter. Whisker contacted devices can fail due to mechanical shock and/or corrosion whilst multipliers based on planar devices (section 2.6) often require delicate soldering operations which can result in damage to the device/circuit.

Advantages of the split block approach include compatibility with other components and strength (particularly at low-temperature). For the purposes of testing, millimetre- and submillimetre-wave MEMS components should attach readily to measurement systems with conventionally machined flanges. This requirement is met during the normal machining process adopted for split-block components. Temperature stability is naturally afforded by components formed from brass or copper. By contrast MEMS components based on epoxy/semiconductor materials tend to be subject to differing rates of contraction as the ambient temperature falls. This can lead to build up of stress within the epoxy layers and ultimately, fracture. Despite the difficulties mentioned above MEMS techniques offer enormous advantages over conventional machining in terms of the tolerances that can be achieved and the speed of manufacture. Many prototype ideas can be included on a single mask plate and reach the finished component stage without laborious machining. Eventually it is envisaged that integration will reach a level where interconnected source, multiplier, mixer and filter modules will be replaced by a single micro-fabricated waveguide circuit. Rectangular waveguide components possible at microwave frequencies but unrealisable at terahertz frequencies, including inductive irises and stepped transformers, become trivial to form using surface micromachining techniques (section 4.4).

Planar integrated circuit technology offers practical advantages for terahertz systems, but planar components are subject to detrimental substrate modes and other loss mechanisms. These severely limit performance with increasing frequency of operation. Rectangular waveguide is a proven low-loss transmission medium in the submillimetre-wave frequency band and can be fabricated via surface or bulk micromachining.

#### **1.6 MEMS (Micro-Electromechanical-Machined-Systems)**

In the 1960s, fabrication of integrated circuits began. Physically small components capable of high-speed operation and/or vast information storage are now commonplace in affordable consumer products. In order to make this possible, high accuracy patterning techniques have been developed to form the many semiconductor devices and interconnecting tracks that constitute an integrated circuit chip. MEMS, first proposed by Feynman [38], utilises similar techniques to produce very small mechanical and electromechanical structures.

The necessary differences between MEMs and conventional processing arise due to the three-dimensional possibilities offered by MEMs structures. IC processing is planar and generally relies on stacking thin layers (typically of the order of 1 micron) with conducting, semiconducting or passivating properties. Micromachined structures often feature components exceeding 100 $\mu$ m in thickness and therefore require very different forming techniques. Broadly speaking, the methods involved in MEMs can be divided into two categories, bulk micromachining and surface micromachining [39].

#### 1.6.1 Bulk micromachining

This technique is relatively mature and was originally developed in the late 1950s in order to fabricate pressure sensors in silicon. It entails creating component features via selective etching of a bulk substrate material. By judiciously combining highly directional (anisotropic) etchants, with nondirectional (isotropic) etchants and using the wafer's crystallographic orientation, features with varying depths and sidewall inclines can be produced. This technique has found application in sub-mm wave component design in the guise of novel micromachined feedhorns [40] and airbridged device contacts [41]. By creating regions with increased levels of impurity doping the etch-rate can be slowed down and in the case of a pn junction, etching can be completely halted. Deep cavities suitable for, amongst others, sensor diaphragms and microwave resonators can be fabricated by employing these methods.

Despite its maturity, bulk micromachining has traditionally suffered from a lower attainable aspect ratio and less directional flexibility when compared with other MEMs techniques, which fall into the surface micromachining category. The outlook for bulk machining is positive though, due to advances in dry etching [42] with directional etch rates in silicon of up to  $4\mu$ m/minute reported.

#### **1.6.2** Surface micromachining

Surface micromachining represents a logical progression from standard IC lithography. A material is deposited as a film on to a substrate and subsequently patterned. As in the IC industry this film can be metallic (evaporated, sputtered or plated) or dielectric (evaporated, sputtered or spin-on polymer). Following patterning, the remaining areas of the layer can be used as an integral part of the component (structural material) or removed (sacrificial material) after acting as a mould, or to release other micromachined parts.

Typical structural materials employed in MEMs are metals including copper and aluminium, polycrystalline and single crystal silicon, silicon dioxide and nitride materials. Recently, spin-on photoresists have been developed which allow ultra

#### Chapter One: Introduction

thick layer formation (>1000µm) and offer excellent aspect ratios coupled with high resistance to acid and alkali attack (relevant when employed in process schemes involving etching and plating). Conventional photoresists, developed for planar processing can also be applied in MEMs fabrication sequences, example applications being release layers and formers for electroplated components.

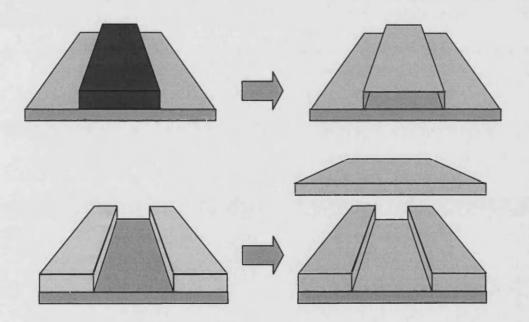

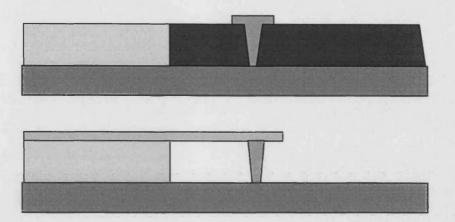

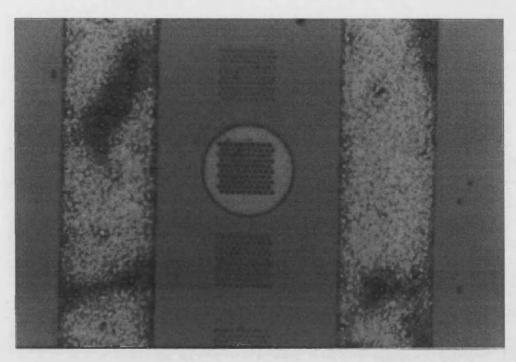

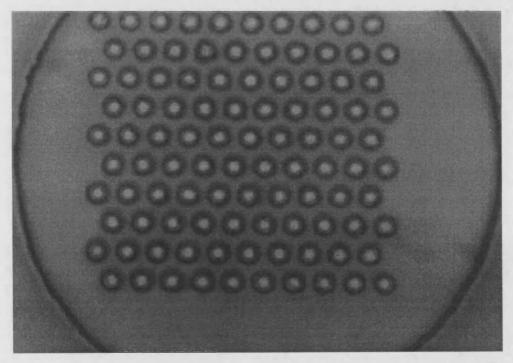

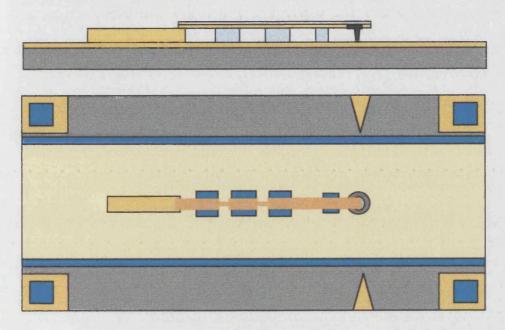

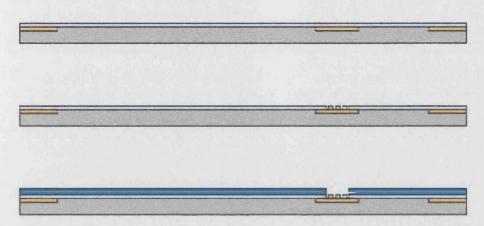

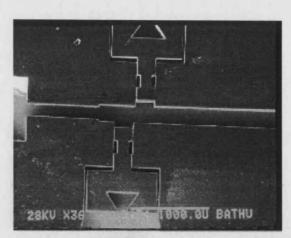

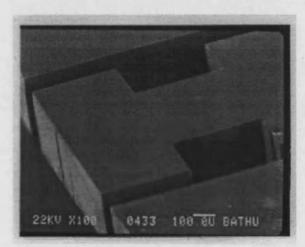

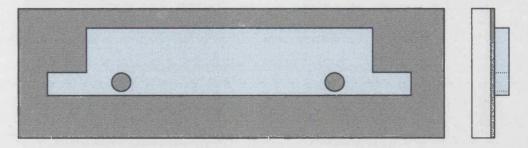

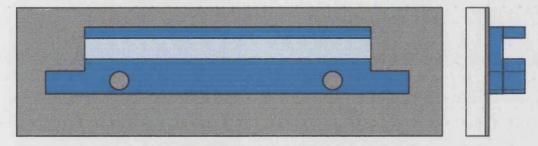

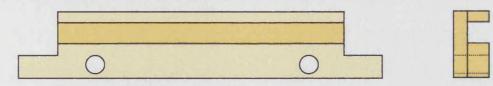

Surface micromachining has evolved into an accurate and low-cost method with new applications and materials emerging as interest from a variety of subject groups increases. Producing static and moving components, it readily lends itself to submillimetre wave component fabrication. The fabrication chapter of this thesis describes in detail the surface processing methods available for use within the Terahertz Technology Group at the University of Bath. In the structures shown in later chapters, conventional and MEMs photoresists have been employed in conjunction with electroplated and vacuum deposited metals to form millimetre and submillimetre passive and active components. The following diagrams (figs. 1.3 and 1.4) offer an introduction and illustrate two applications that will be discussed at greater length in chapter 4.

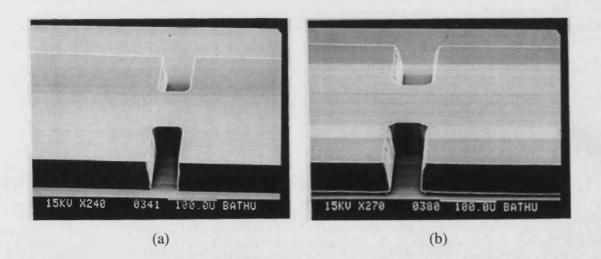

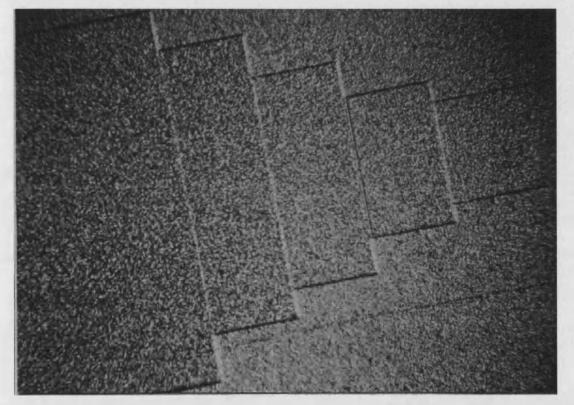

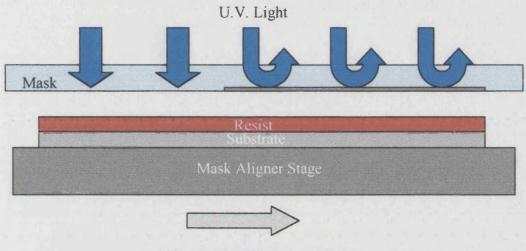

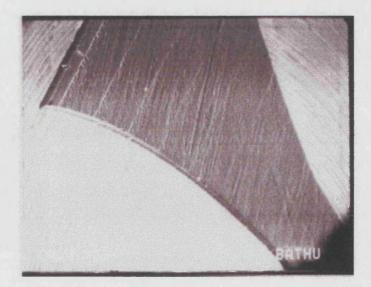

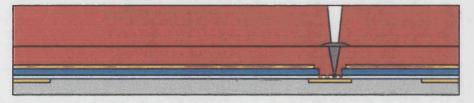

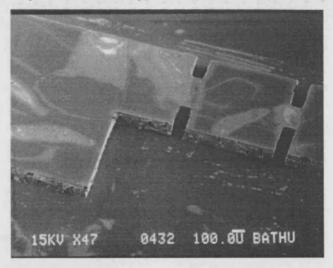

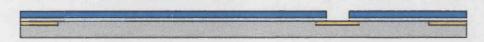

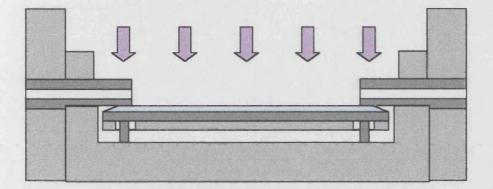

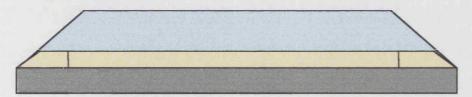

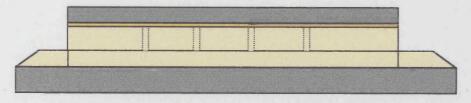

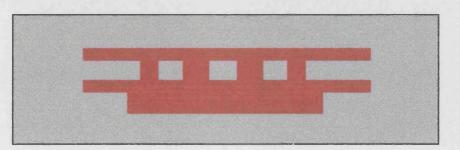

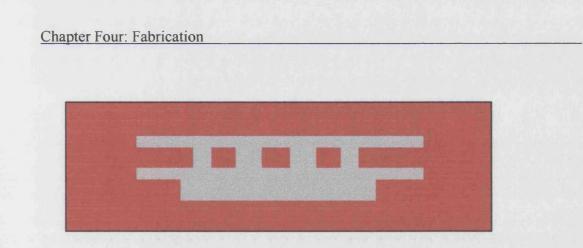

Figure 1.3. Positive resist waveguide former (top) and negative SU8 epoxy resist trench (bottom).

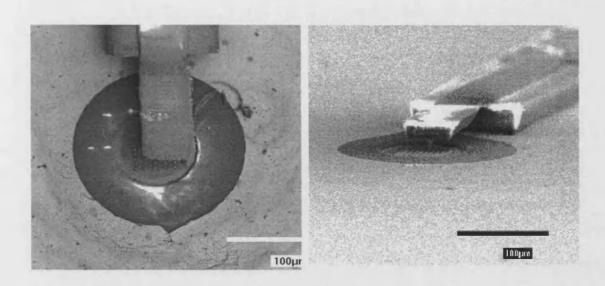

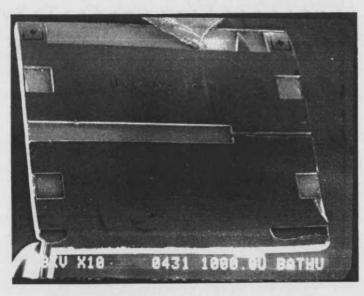

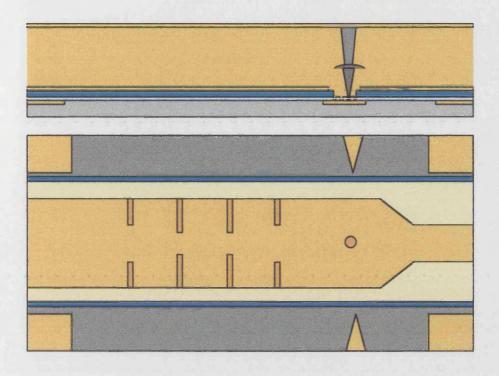

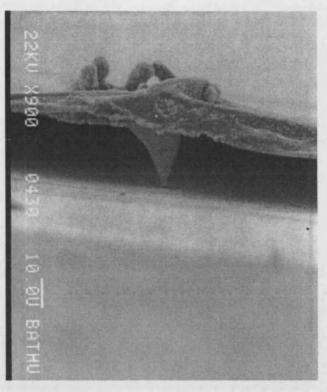

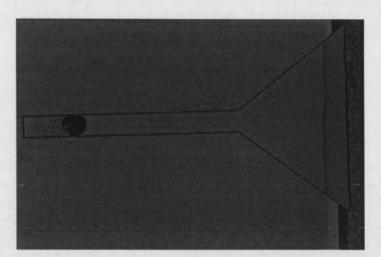

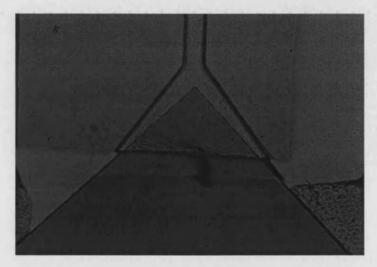

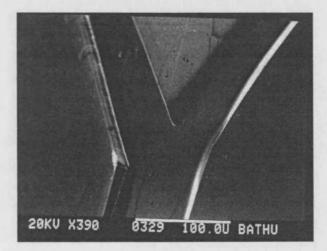

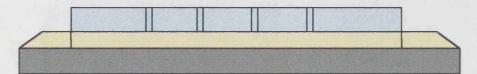

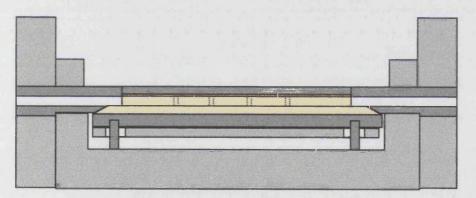

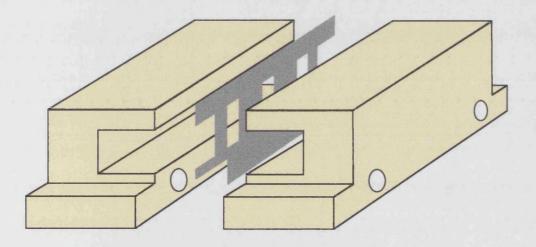

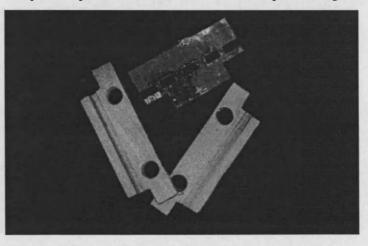

Figure 1.4. Electroformed device contact post in conventional photoresist with dielectric support and evaporated metal strip contact.

Figure 1.3 illustrates the fundamental difference between processing with conventional and negative epoxy resists (more detail in chapter 4). The approach adopted prior to the acquisition of epoxy based negative resist was to produce a waveguide former from conventional positive resist and wash this away after seeding and plating the former. Negative epoxy resist is a permanent feature once exposed and thus required a modified approach. Trenches were lithographically formed in the dielectric sheet, seeded, plated and finally capped with a metallic lid to form rectangular waveguides/filter-cavities etc.

Having introduced the basic concepts behind bulk and surface micromachining, the next section reviews some of the work carried out to date on terahertz micromachined components.

### 1.7 Micromachining for terahertz applications

The application of micromachining technology to terahertz circuits was explored as early as 1979 [43] with the fabrication of a 2.5THz 40 $\mu$ m wide by 400 $\mu$ m long (3.5 $\lambda$ ) tapered-dielectric-rod antenna micromachined from a silicon substrate.

In terms of bulk micromachining, the ability to form waveguide cavities in silicon via anisotropic etching is proven [44, 45]. This technique is normally based on a wet potassium hydroxide (KOH) etch through a pattern formed in Silicon Nitride [46]. Alignment is made to the 110 planes in order to produce smooth internal waveguide surfaces. In [44] electroless nickel plating was used as a seed layer, followed by gold to produce a low resistance internal coating. Half width waveguides were formed in two substrates, then the two halves were mated together to form WR8 and WR4 waveguides. Reported loss was less than 1dB/wavelength for the WR4 waveguides.

An example of combined bulk and surface micromachining is described in [40]. Here anisotropic etching of a silicon substrate is combined with patterning of a negative epoxy based photoresist (SU8) to form an antenna and broadband transition into rectangular waveguide suitable for operation at 585GHz.

Dichroic plates have been batch processed on sacrificial substrates using the same photosensitive resin as used in [40]. The patterned resin is released and plated and designs have been demonstrated that pass 640GHz whilst rejecting 240GHz [47].

In addition to the photolithographic techniques described thus far, alternative methods have been sought for the scaling down of conventional microwave components. Laser micromachining is a technique that involves computer controlled laser milling of silicon. Amongst other components, it has been successfully employed to produce 810GHz and 2.0THz corrugated feedhorn antennas. The technique has also been used to produce master components from which multiple replica horns can be fabricated [48].

Aiming for methods suitable for mass production and further cost reduction has led to research into casting or moulding of terahertz components [49]. Inexpensive high precision copies of conventionally fabricated terahertz structures have been produced through the casting of polyurethane structures using a silicone-based mould formed from a master. The silicone mould is formed on a conventionally machined master and then filled with polyurethane, which is subsequently cured and removed. Measurements have shown that a 690GHz mixer-block produced using this method and subsequently gold-plated performs as well as a metal block with the same dimensions.

Lubecke and Rebeiz [50] presented a detailed review of micromachining for terahertz applications, published at the end of 1998. This paper includes descriptions of the

aforementioned techniques and describes the development of micromachined planar transmission line technology for operation in the submillimetre-wave region.

# 1.8 Thesis overview

In following chapters, the design and fabrication of a number of micromachined submm wave components is presented. This introductory chapter has highlighted existing and potential terahertz applications and introduced the circuit topologies of typical sub-millimetre frequency mutlipliers. The following chapter contains fundamental theory relating to the Schottky devices conventionally used within submillimetre wave multiplier circuits. It also contains a review of fabrication techniques developed by various research groups in order to produce devices with optimal operating characteristics.

The third chapter introduces constituent elements of the fabricated components and outlines the design procedure adopted for the frequency multipliers that have provided the primary focus of the project. Critical design aspects are highlighted and solutions that are compatible with a MEMs approach are described. Modelling using commercially available finite-element-method and non-linear circuit simulator software is presented.

Processing schemes are presented in chapter four accompanied with full details of all novel processing methods. The scope and constraints of developed techniques are clarified and supported with detailed guidelines for processes suitable for the creation of micromachined waveguiding structures.

Chapter five contains results from DC device testing and RF testing of completed waveguiding structures. These results are discussed and performance-critical aspects of component fabrication are emphasised.

Suggested improvements and concluding remarks form the basis of chapter six. The drive to apply micromachining techniques to microwave, mm-wave and terahertz systems has gathered pace rapidly but many possibilities remain unexplored. Ideas forming the basis for continuing work are introduced.

### **Section References**

[1] T. G. Phillips and J. Keene, "Submillimeter Astronomy", Proceedings of the IEEE, vol. 80, no. 11, pp. 1662-1678, November 1992.

[2] L. T. Little, A. G. Gibb, B. D. Heaton, B. N. Ellison and S. M. X. Claude, "The CI/CO ratio in the molecular cloud G34.3+0.2", Monthly Notice of the Royal Astronomical Society, vol. 271, pp. 649-661, 1994.

[3] T. H. Buttgenbach, J. Keene, T. G. Phillips and C. K. Walker, "Submillimeter detection of extragalactic CI emission -- IC 342", Astrophysical Journal, vol. 397, L15-L17, 1992.

[4] A. van Ardenne, "Receiver developments for the James Clerk Maxwell (sub)mm telescope", Nederlands Elektronica- en Radiogenootschap, vol. 52, no. 4-6, pp. 121-130, 1987.

[5] S. R. Davies, C. T. Cunningham, L. T. Little, D. N. Matheson, "JCMT receiver A2-a 210-280 GHz SIS receiver", IEE Colloquium on Millimetre and Sub-Millimetre Wave Heterodyne Receivers, pp. 6/1-4, 1992.

[6] N. Mandolesi and F. Villa, "FIRST/Planck mission", IMTC/99 Proceedings of the 16th IEEE Instrumentation and Measurement Technology Conference, vol. 2, part 2, pp. 975-980, 1999.

[7] E. F. Erickson and J. A. Davidson, "SOFIA: the future of airborne astronomy", Astronomical Society of the Pacific Conference Series, vol. 73, 1995, pp.707-732.

[8] J. W. Waters, "Submillimeter-wavelength heterodyne spectroscopy and remote sensing of the upper atmosphere", Proceedings of the IEEE, vol. 80, no. 11, pp. 1679-1701, November 1992.

[9] J. W. Waters, "Submillimeter heterodyne spectroscopy and remote sensing of the upper atmosphere", 1999 IEEE MTT-S International Microwave Symposium Digest, pp. 391-394.

[10] C. A. Reber, "The Upper Atmosphere Research Satellite (UARS)", Geophysical Research Letters, vol. 20, no. 12, pp. 1215-1218, June 1993.

[11] T. Wehr, S. Crewell, K. Kunzi, J. Langen, H. Nett, J. Urban and P. Hartogh, "Remote sensing of ClO and HCl over northern Scandinavia in winter 1992 with an airborne submillimeter radiometer", Journal of Geophysical Research, vol.100, no. D10, pp. 20957-20968, Oct. 1995. [12] D. Woolard, R. Kaul, R. Suenram, A. H. Walker, T. Globus and A. Samuels,

"Terahertz electronics for chemical and biological warfare agent detection", 1999

IEEE MTT-S International Microwave Symposium Digest, pp. 925-928.

[13] A. Mardon, "Applications of millimetre waves", in Millimetre and submillimetre waves, Ed. F. A. Benson, Iliffe Books Ltd., 1969, pp. 525-527.

[14] P. Woskoboinikow, "Development of gyrotrons for plasma diagnostics", Review of Scientific Instruments, vol. 57, no. 8, pt. 2, pp. 2113-2118, Aug. 1986.

[15] T. Suzuki, T. Yasui, H. Fujishima, T. Nozokido, M. Araki, O. Boric-Lubecke, V. M. Lubecke, H. Warashina and K. Mizuno, "Reduced low-frequency noise Schottky barrier diodes for terahertz applications", IEEE Transactions on Microwave Theory & Techniques, vol. 47, no. 9, pt. 1, pp. 1649-1655, Sept. 1999.

[16] J. M. Chamberlain, R.E. Miles, C. E. Collins and D. P. Steenson, "Introduction to terahertz solid-state devices" in New Directions in Terahertz Technology, Ed. J. M. Chamberlain and R.E. Miles, Kluwer Academic Publishers, 1997, pp. 3-29.

[17] E. R. Brown, J. R. Soderstrom, C. D. Parker, L. J. Mahoney, K. M. Molvar and T. C. McGill, "Oscillations up to 712GHz in InAs/AlSb resonant tunneling diodes", Applied Physics Letters, vol. 58, pp. 2291-2293, 1991.

[18] H. Eisele, A. Rydberg and G. I. Haddad, "Recent advances in the performance of InP Gunn devices and GaAs TUNNETT diodes for the 100-300-GHz frequency range and above", IEEE Transactions on Microwave Theory & Techniques, vol. 48, no. 4, pt. 2, pp. 626-631, April 2000.

[19] H. Eisele and G. I. Haddad, "Efficient power combining with D-band (110-170 GHz) InP Gunn devices in fundamental-mode operation", IEEE Microwave & Guided Wave Letters, vol. 8, no. 1, pp. 24-26, Jan. 1998.

[20] A. Rydberg, "High efficiency and output power from second- and thirdharmonic millimeter-wave InP-TED oscillators at frequencies above 170 GHz", IEEE Electron Device Letters, vol. 11, no. 10, Oct. 1990, pp. 439-41

[21] S. E. Rosenbaum, B. K Kormanyos, L. M. Jelloian, M. Matloubian, A. S. Brown, L. E. Larson, L. D. Nguyen, M. A. Thompson, L. P. B. Katehi and G. M. Rebeiz, "155- and 213-GHz AlInAs/GaInAs/InP HEMT MMIC oscillators", IEEE Transactions on Microwave Theory & Techniques, vol. 43, no. 4, pt. 2, pp. 927-932, April 1995.

[22] T. Fujii, H. Mazaki, F. Takei, J. Bae, M. Narihiro, T. Noda, H. Sakaki and K. Mizuno, "Coherent power combining of millimeter wave resonant tunneling diodes in a quasi-optical resonator", 1996 IEEE MTT-S International Microwave Symposium Digest, vol. 2, pp. 919-922.

[23] M. Yu. Tretyakov, S. A. Volokhov, G. Yu. Golubyatnikov, E. N. Karyakin and A. F. Krupnov, "Compact tunable radiation source at 180-1500 GHz frequency range" International Journal of Infrared & Millimeter Waves, vol. 20, no. 8, pp. 1443-1451, August 1999.

[24] F. Maiwald, F. Lewen, B. Vowinkel, W. Jabs, D. G. Paveljev, M. Winnewisser and G. Winnewisser, "Planar Schottky diode frequency multiplier for molecular spectroscopy up to 1.3 THz", IEEE Microwave & Guided Wave Letters, vol. 9, no. 5, pp. 198-200, May 1999.

[25] S. R. Davies, C. T. Cunningham, L. T. Little and D. N. Matheson, "A 210-280 GHz SIS Heterodyne Receiver for the James Clerk Maxwell Telescope. Part 1: Design and Performance", International Journal of Infrared and Millimeter Waves, vol. 13, pp. 647-658, 1992.

[26] C. T. Cunningham, R. H. Hayward, J. D. Wade, S. R. Davies and D. N. Matheson, "A 345 GHz Heterodyne Receiver for the James Clerk Maxwell Telescope", International Journal of Infrared and Millimeter Waves, vol. 13, pp. 1827-1843, 1992.

[27] B. N. Ellison, S. M. Claude, A. Jones, D. N. Matheson, L. T. Little and S. R. Davies, "A submillimetre wave SIS receiver for the James Clerk Maxwell Telescope", International Conference on Millimeter and Submillimeter Waves and Applications, Ed. M.N. Afsar; Proceedings of SPIE 2250, pp. 527-528, 1994.

[28] G. de Lange, C. E. Honingh, J. J. Kuipers, H. H. A. Schaeffer, R. A. Panhuyzen, T. M. Klapwijk, H. van de Stadt and M. M. W. M. de Graauw, "Heterodyne mixing with Nb tunnel junctions above the gap frequency", Applied Physics Letters, vol. 64, pp. 3039-3041, 1994.

[29] M. Bin, M. C. Gaidis, J. Zmuidzinas, T. G. Phillips and H. G. LeDuc, "Lownoise 1 THz niobium superconducting tunnel junction mixer with a normal metal tuning circuit", Applied Physics Letters, vol. 68, pp. 1714-1716, 1996.

[30] D. E. Prober, "Superconducting terahertz mixer using a transition-edge microbolometer", Applied Physics Letters, vol. 62, pp. 2119-2121, 1993.

23

[31] A. Skalare, W. R. McGrath, B. Bumble, H. G. LeDuc et al., "Large bandwidth and low noise in a diffusion-cooled hot-electron bolometer mixer", Applied Physics Letters, vol. 68, pp. 1558-1560, 1996.

[32] T. Takada and M. Ohmori, "Frequency triplers and quadruplers with GaAs Schottky-barrier diodes at 450 and 600GHz", IEEE Transactions on Microwave Theory and Techniques, vol. 27, no. 5, pp. 519-523, May 1979.

[33] J. W. Archer, "An efficient 200-290-GHz frequency tripler incorporating a novel stripline structure", IEEE Transactions on Microwave Theory and Techniques, vol. 32, no. 4, pp. 416-420, April 1994.

[34] N. Erickson, "High efficiency submillimeter frequency multipliers", 1990 IEEE MTT-S International Microwave Symposium Digest, vol. 3, pp.1301-1304.

[35] J. Edrich and L. K. Sanborn, "Efficient and broadbanded frequency doublers for millimeter waves", Proceedings of the 4th European Microwave Conference 1974, pp. 435-438.

[36] A.V. Raisanen, D. Choudhury, R.J. Dengler, J.E. Oswald and P.H. Seigel, "A novel split waveguide mount design for millimetre- and submillimetre-wave frequency multipliers and harmonic mixers", IEEE Microwave and Guided Wave Letters, vol. 3, no. 10, pp. 369-371, October 1993.

[37] T. Newman and N. Erickson, "A planar varactor array multiplier chain to 300GHz", 1999 IEEE MTT-S International Microwave Symposium Digest, pp. 135-138.

[38] R. P. Feynman, "There's plenty of room at the bottom", presented at the American Physical Society Meeting, Pasadena, CA, December 26, 1959; reprinted in Journal of Microelectromechanical Systems, vol. 2, pp. 60-66, February 1992.

[39] H. J. De Los Santos, Introduction to Microelectromechanical (MEM) Microwave Systems, Artech House, 1999.

[40] C. M. Mann, J. L. Hessler, P. J. Koh, T. W. Crowe, W. L. Bishop, R. M. Weikle and D. N. Matheson, "A versatile micromachined horn antenna", in 20<sup>th</sup> ESTEC Antenna Workshop on Millimeter Wave Antenna Technology and Antenna Measurements, June 1997.

[41] D. Boccon-Gibod, P. Harrop, "High performance GaAs Schottky barrier diodes using a cantilevered metal contact", Proceedings of the 8<sup>th</sup> European Microwave Conference 1978, pp. 696-700.

[42] P. G. Hartwell et al., "Deep silicon RIE with profile control", 44<sup>th</sup> National Meeting of the American Vacuum Society, October 1997. Online at http://mems.ee.cornell.edu/macd/

[43] D. B. Rutledge, S. E. Schwarz, T. L. Hwang, D. J. Angelakos, K. K. Mei and S. Yokota, "Antennas and waveguides for far-infrared integrted circuits", IEEE Journal of Quantum Electronics, vol. QE-16, pp. 508-516, May 1980.

[44] W. R. McGrath, C. K. Walker, M. Yap and Y-C. Tai, "Silicon micromachined waveguides for millimeter-wave and submillimeter-wave frequencies", IEEE Microwave and Guided Wave Letters, vol. 3, pp. 61-63, January 1993.

[45] J. A. Wright, S. Tatic-Lucic, Y.-C. Tai, W. R. McGrath, B. Bumble and H. LeDuc, "Integrated silicon micromachined waveguide circuits for submillimeter wave applications", in 6<sup>th</sup> International Symposium on Space Terahertz Technology, March 1995, pp. 387-396.

[46] K. E. Peterson, "Silicon as a mechanical material", Proceedings of the IEEE, vol. 70, pp. 420-457, May 1982,

[47] V. M. Lubecke, C. Mann and K. Mizuno, "Practical micromachining techniques for high aspect ratio submillimeter wave components", in 9<sup>th</sup> International Symposium on Space Terahertz Technology, March 1998.

[48] C. K. Walker et al., "Laser micromachining of silicon: A new technique for fabricating high quality terahertz waveguide components", in 8<sup>th</sup> International Symposium on Space Terahertz Technology, pp. 358-376, March 1997.

[49] T. W. Crowe et al., "Inexpensive receiver components for millimeter wavelengths", in 8<sup>th</sup> International International Symposium on Space Terahertz Technology, pp. 377-384, March 1997.

[50] V. M. Lubecke, K. Mizuno and G. M. Rebeiz, "Micromachining for terahertz applications", IEEE Transactions on Microwave Theory and Techniques, vol. 46, no. 11, pp. 1821-1831, November 1998.

25

# 2. Device Theory and Design

# 2.1 Frequency multipliers

Before looking at the constituent elements of a frequency multiplier in detail, it is helpful to consider what requirements are placed on a working frequency multiplier. The most fundamental requirement is that an incoming signal with a frequency  $f_0$  will produce a multiplied frequency  $f_{out}$  at the output. It is desirable that this multiplication is as efficient as possible in order that suitable signal power is available for LO operation in a mixer. Bandwidth must be considered, and maximised if the multiplier is intended for use with varying input frequencies. The system must exhibit low noise, as any noise present in the multiplier output will appear as LO noise in the mixer [1, 2].

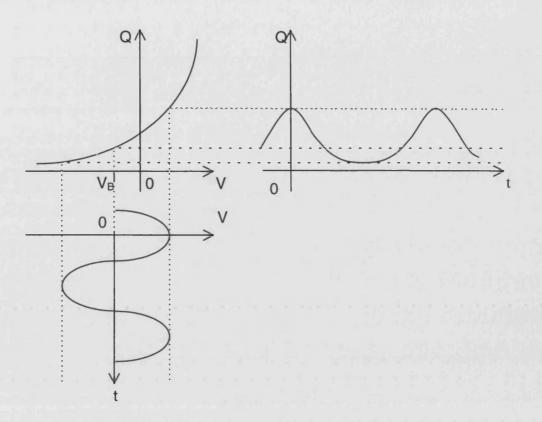

Harmonic multiplication requires a device with non-linear behaviour. To date, millimetre and submillimetre wave multipliers have normally used the non-linear CV or IV characteristics of a reverse or forward biased diode to provide harmonic multiplication. The most widely used device for this purpose is the Schottky diode and this may be operated in varistor or varactor mode depending on whether its IV or CV non-linearity is utilised. From the outset, it should be stated that whilst forward biased diodes have broad bandwidth and stable operating characteristics, varactor diodes can offer higher efficiency and low noise [1, 3]. For this reason submillimetre multipliers normally feature diodes operating predominantly in varactor mode.

# 2.2 The Schottky barrier

The Schottky-barrier diode is a two-terminal semiconductor device that utilises the non-linear properties (CV&IV) of a metal-semiconductor junction (fig. 2.1). Unequal work functions in the metal and semiconductor give rise to an electrostatic barrier at their interface. This barrier leads to rectifying properties and conduction that is controlled primarily by thermionic emission of majority carriers over the barrier. As a majority carrier device, the Schottky diode has increased high-frequency capability over devices such as pn diodes that exhibit minority carrier effects.

#### Chapter Two: Device Theory and Design

In microwave and sub-mm wave applications it is necessary to minimise device series resistance and junction capacitance and thus maximise cut-off frequency. A semiconducting material with high carrier mobility and saturation velocity is required to meet these criteria. Gallium arsenide has higher carrier mobility and saturation velocity than silicon and is the primary choice for high-speed mixer, detector and multiplier diodes. Silicon, being less expensive than gallium arsenide, still has a place for lower frequency applications. Platinum, gold and aluminium are commonly used to form the Schottky barrier.

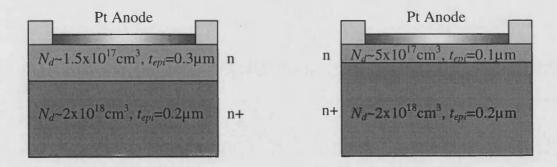

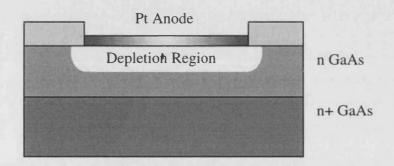

A schematic view of the Schottky diode layer structure is presented in fig. 2.1. Varactor and varistor structures are shown with typical layer properties for submillimetre wave operation and illustrate the differences between these devices in epilayer thickness and doping. Both varactor and varistor diodes are based on a metal/n/n+ layer scheme. The diode is formed as a metal/n-type interface and the heavily doped n+ layer serves to reduce substrate impedance. The varactor diode has a thicker n-type layer in order to accommodate the increased depletion region under conditions of high reverse bias. If the epilayer thickness  $t_e$  is smaller than the maximum width of the barrier  $w_{br}$ , then the epilayer is punched through before the reverse breakdown voltage is reached. If the epilayer thickness is chosen such that  $t_e > w_{br}$ , then the junction will adhere to the device capacitance/voltage relationship up to the breakdown voltage.

Figure 2.1 Submillimetre wave Schottky barrier (a) varactor and (b) varistor diodes.

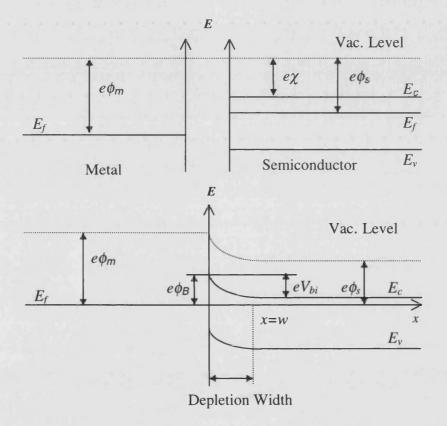

## 2.2.1 Formation of the barrier

Band structures are presented in fig. 2.2 for the individual metal and semiconductor and the combined Schottky junction. Electrons in the semiconductor have on average a higher energy than electrons in the metal. These electrons of higher energy move into the metal and collect on its surface. Ionised donor locations are left in the semiconductor, adjacent to the interface and an electric field is established due to the separation of positive charges in the semiconductor and negative charges on the surface of the metal. This field inhibits further flow of electrons into the semiconductor when the Fermi levels of both materials are equalised. The valence and conduction bands are thus forced to bend.

Figure 2.2 Metal/Semiconductor band diagram before and after contact.

In fig. 2.2, *e* is electron charge,  $\phi_s$  is the semiconductor work function,  $\phi_m$  is the metal work function and  $\phi_B$  is the difference between them.  $\chi$  is the electron affinity, describing the energy difference between an electron on the vacuum level and an

electron on the lower edge of the conduction band.  $E_c$ ,  $E_v$ , and  $E_f$  are the conduction, valence and Fermi energies respectively. The barrier width is w.

In the *depletion approximation* it is assumed that in the region of the semiconductor where the bands are bent upwards, the space charge is due entirely to the ionised donors. In the depletion region, uniform distribution of these donors is assumed and therefore a uniform space charge. The electric field will increase linearly from  $-E_{max}$  (x=0) to 0 (x=w) and the magnitude of the electrostatic potential will decrease quadratically, resulting in a potential barrier parabolic in shape. The width of the depletion region is given by [1]

$$w = \left[\frac{2\varepsilon_s}{qN_d}(V_{bi} - V_b - V_T)\right]^{1/2}, \qquad (2.1)$$

where  $N_d$  is the donor density,  $\varepsilon_s$  is the total permittivity of the semiconductor,  $V_{bi}$  is the built-in potential,  $V_b$  is a voltage applied externally to the barrier, k is Boltzman's constant and T is the temperature. The term  $V_T = kT/q$  (~26 mV at room temperature) arises from the presence of the transition region (at x=w) where the electron concentration falls from a value equal to  $N_d$  to a value negligible compared with  $N_d$ .

The space charge due to the ionised donors contained in the depletion region per unit area is then

$$Q_{sc} = \varepsilon_s \left| E_{\max} \right| = q N_d w = \left[ 2q \varepsilon_s N_d (V_{bi} - V_b - V_T) \right]^{1/2}.$$

(2.2)

As there is no minority carrier storage in a Schottky diode, there is no diffusion capacitance. The capacitance of the device is therefore due only to the charge in the depletion layer. Hence for microwave diodes (see section 2.4 for sub-mm equivalent)

$$c_{b} = \left| \frac{\partial Q_{sc}}{\partial V_{a}} \right| = \left[ \frac{q \varepsilon_{s} N_{d}}{2(V_{bi} - V_{b} - V_{T})} \right]^{1/2} = \frac{\varepsilon_{s}}{w}.$$

(2.3)

The idealised situation used to derive the equations above is in reality never achieved. The barrier height will depend not only on the materials and the applied bias, but also on the thickness of a thin oxide layer that (during fabrication) inevitably appears at the metal/semiconductor interface. Deviations from the ideal case will be discussed in the following sections.

#### 2.2.2 Current-transport mechanisms

In most practical Schottky diodes the dominant carrier transport mechanism is by emission of the electrons from the semiconductor over the barrier and into the metal. Quantum-mechanical tunnelling provides a second transport mechanism with electrons tunnelling through the potential barrier and appearing in the semiconductor.

## 2.2.3 Emission over the barrier

Motion of electrons through the semiconductor depletion region is governed by the mechanisms of diffusion and drift in the electric field of the barrier. When they arrive at the interface, their emission into the metal is determined by the rate of transfer of electrons across the semiconductor/metal interface. These two processes are essentially in series and the process that imposes a lower limit on the flow of electrons essentially sets the current.

Diffusion theory assumes that the diffusion and drift of electrons in the depletion region limit the current flow, and that the conduction electrons in the semiconductor immediately adjacent to the semiconductor are in thermal equilibrium with those in the metal. The thermionic-emission theory assumes that the effects of drift and diffussion are negligible and the transfer of electrons across the interface dictates the current flow. A synthesis of the two theories [4] considers the two mechanisms to be in series. Assuming that the thermionic-emission current must equal the drift-diffusion current, the theory predicts (except for high bias) that the current density at the junction is

$$J_{b} = \left[A^{**}T^{2} \exp\left(\frac{-q\phi_{b}}{kT}\right)\right] \left[\exp\left(\frac{qV_{b}}{kT}\right) - 1\right] = J_{s}\left[\exp\left(\frac{qV_{b}}{kT}\right) - 1\right].$$

(2.4)

At room temperature for high-mobility semiconductors doped to  $10^{16}$  to  $10^{17}$  cm<sup>-3</sup> and in the electric field strength range  $10^4$  to 2 x  $10^5$  Vcm<sup>-1</sup> (normal operating conditions) the Richardson constant  $A^{**}$ , remains essentially at a constant value. Reported values for  $A^{**}$  vary between 8.2 Acm<sup>2</sup>K<sup>-2</sup> [5] and 8.6 Acm<sup>-2</sup>K<sup>-2</sup> [6] for GaAs.

# 2.2.4 Tunnelling through the barrier

Schottky barriers formed on heavily doped semiconductors and/or operating at low temperature will have a junction current that is influenced by quantum mechanical tunnelling of electrons through the barrier. Field emission describes the condition where the temperature is low enough and the doping sufficiently high so as to allow electrons with energies close to the Fermi energy in the semiconductor to easily tunnel through the barrier. An increase in temperature causes the electrons to see a thinner and lower barrier. Thermionic field emission occurs when the quantum tunnelling current stabilises at a certain temperature dependent value. If the temperature is increased further, a point eventually arises where thermionic emission over the barrier is the dominant influence on the junction current.

The forward tunnelling current-voltage relationship is given (except at very low  $V_b$ ) by

$$J_b = J_s \exp\left(\frac{V_b}{E_0}\right),\tag{2.5}$$

where

$$E_0 = E_{00} \operatorname{coth}\left(\frac{qE_{00}}{kT}\right) \tag{2.6}$$

and

$$E_{00} = \frac{h}{4\pi} \left( \frac{N_d}{m^* \varepsilon_s} \right)^{\frac{1}{2}}.$$

(2.7)

In these formulae,  $m^*$  is the effective mass of electrons in the n-type semiconductor,  $\varepsilon_s$  is its permittivity and h is Planck's constant.

Experiments have been performed to determine the temperature ranges at which emission mechanisms dominate the device behaviour [5]. For Schottky diodes made on n-type GaAs with  $N_d \approx 2 \times 10^{17} \text{ cm}^{-3}$  the tunnelling of electrons may be neglected above 100K where pure thermionic emission dominates.

## 2.2.5 Generalised IV relationship

A generalised I-V relationship may be used to describe the Schottky junction at any temperature and for various dopant levels. This expression follows from the formal

similarity of the thermionic and tunnelling current definitions. The ideality factor  $\eta$  is introduced and described so  $\eta = 1$  for pure thermionic emission. An increase in  $\eta$  is due to deviation from this ideal model.

$$\eta = \frac{q}{kT} \frac{\partial V_b}{\partial (\ln J_b)}.$$

(2.8)

Using this definition, the I/V characteristic of the junction in which current flows due to pure thermionic emission ( $I_b >> I_s$ ) can be expressed in the form

$$I_{b} = SA^{**}T^{2} \exp\left(\frac{-q\phi_{b}}{\eta kT}\right) \exp\left(\frac{-qV_{b}}{\eta kT}\right) = SA^{**}T^{2} \exp\left(\frac{V_{b} - \phi_{b}}{V_{0}}\right), \quad (2.9)$$

where S is the area of the junction and

$$V_0 = \frac{k}{q} \eta T = 8.617 \times 10^{-5} \eta T \quad [V]$$

(2.10)

is the slope parameter of the I/V characteristic.

Diode ideality can be measured by determining the slope of the I/V curve in millivolts per decade of current. From equation (2.4) the change in voltage,  $\Delta V$ , giving a decade change in current is

$$\Delta V = \frac{\eta kT}{q\log(e)},\tag{2.11}$$

where *e* is the base of the natural logarithms. Thus for a known change in voltage over a decade of current, the ideality may be derived. The saturation current  $I_s=SJ_s$ , can then be determined from (2.4).

The DC resistance of the diode is calculated by using the deviation (caused by the series resistance) from exponential I/V behaviour at higher device currents. For a current of 1mA and a typical series resistance of 10 $\Omega$ , 10mV will be dropped across the series resistance. In general  $R_s$  is calculated from

$$R_s = \frac{\Delta V}{I}, \qquad (2.11)$$

where  $\Delta V$  is the deviation from the extrapolated low current characteristic and I is in the range 100-1000µA.

# 2.2.6 Reverse characteristics