**University of Bath**

PHD

Educational interface board for multi-family microprocessor teaching

Bakbak, Sami Ibrahim

Award date: 1988

Awarding institution: University of Bath

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## Educational Interface Board For multi-Family Microprocessor Teaching

Submitted by Sami Ibrahim Bakbak for the degree of Ph.D of the University of Bath 1988

### COPYRIGHT

Attention is drawn to the fact that copyright of this thesis rest with its author. This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author.

This thesis may be made available for consultation within the University Library and may be photocopied or lent to other libraries for the purposes of consultation.

Bath, May 1988

UMI Number: U005688

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI U005688 Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author. Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

. , #

.

5021540

### SUMMARY

The rapid growth in the microprocessor population and the increasing use of microprocessors in education has resulted in many different approaches to the problem of microprocessor teaching and development.

This thesis examines the various common**use**techniques for microprocessor education and discusses, compares the advantages and disadvantages of each approach. A design and implementation of an educational environment, for users to investigate and learn about various currently available microprocessor families, is shown.

### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to the following people who provided me with assistance and encouragement during the course of this project.

Mr. A.R.Daniels, for his supervision and constant guidance.

Dr. P.F. Whitworth, for his interest and help.

To all member of staff and collegues at the school of Electrical Engineering, University of Bath.

Finally, I would like to specially thank my family who gave me encouragement and support throughout these years.

### CONTENTS

|    | SUN  | MMAR   | RY     |       |      |      |     |     |      |     |     |    |      |     |     |    |   |   |   |   |    |   |      |

|----|------|--------|--------|-------|------|------|-----|-----|------|-----|-----|----|------|-----|-----|----|---|---|---|---|----|---|------|

|    | AC   | KNOW   | VLED   | GEM   | 1en  | 1TS  | ;   |     |      |     |     |    |      |     |     |    |   |   |   | × |    |   |      |

| 1. | INT  | RODU   | JCTIO  | N     | •    | •    | •   | •   | •    | •   | •   | •  | •    | •   | •   | ٠  | • | • | • | • | ٠  | • | 1    |

|    | 1.1  | Mic    | cropro | cess  | or l | bacl | kgı | rou | nd   | •   | •   | ٠  | •    | •   | •   | •  | • | • | • | • | •  | • | 1    |

|    | 1.2  | Mic    | cropro | xess  | or e | edu  | cat | ior | ח רפ | equ | ire | me | ente | S   | •   | •  | • | • | • | • | •  | • | 3    |

| 2. | A R  | EVIE   | W OF   | MIC   | CRC  | Ю    | )M  | PU  | TE   | ER  | ED  | UC | CA   | ГІС | )N. | AL |   |   |   |   |    |   |      |

|    | SYST | rems   | •      | ••    | •    | •    | •   | •   | •    | •   | •   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 7    |

|    | 2.1  | Eval   | luatio | n Ki  | ts   | •    | •   | •   | •    | •   | ٠   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 7    |

|    | 2.2  | Sing   | le Boa | ard N | Mic  | roc  | om  | pu  | ter  | S   | •   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 8    |

|    | 2.3  | Self   | conta  | lined | l mi | icro | CO  | mp  | oute | ers |     | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 9    |

|    | 2.4  | Com    | puter  | · sim | rula | tio  | n   | •   | •    | •   | •   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 10   |

|    | 2.5  | In-cir | rcuit  | emu   | lato | ors  |     | •   | •    | •   | •   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | . 11 |

|    | 2.6  | Mini   | /Micr  | o coi | mm   | un   | ica | tio | n    | •   | •   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 14   |

| 3. | MICF | ROPRO  | DCES   | SOR   | BU   | S S  | TF  | RU( | СТ   | UR  | ES  |    | •    | •   | •   | •  | • | • | • | • | •  | • | 17   |

|    | 3.1  | Intro  | ducti  | ion   | •    | •    | •   | •   | •    | •   | •   | •  | •    | •   | •   | •  | • | • | • | • | .• | • | 17   |

|    |      | 3.1.1  | Virt   | ual 1 | mer  | nor  | y   | •   | •    | •   | •   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 21   |

|    | 3.2  | Moto   | orola  | MC6   | 6800 | 00   | •   | •   | •    | •   | •   | •  | •    | •   | •   | •  | • | • | • | • | •  | • | 22   |

|    | 3.3  | The Intel 8086 Microprocessor • • • •                 | • | • | • | • | • | • | • | 25 |

|----|------|-------------------------------------------------------|---|---|---|---|---|---|---|----|

|    | 3.4  | The Intel 80286 • • • • • • • • • • • • • • • • • • • | • | • | • | • | • | • | • | 28 |

|    | 3.5  | Zilog Z80 microprocessor                              | • | • | • | • | • | • | • | 28 |

|    | 3.6  | The Motorola MC6800 microprocessor                    | • | • | • | · | • | • | • | 30 |

|    | 3.7  | The Motorola M6809 Microprocessor                     | • | • | • | • | • | • | • | 31 |

|    | 3.8  | The Mos Technology 6502 Microprocessor .              | • | • | • | • | • | • | • | 32 |

|    | 3.9  | The Texas 9900 microprocessor • • • •                 | • | • | • | • | • | • | • | 34 |

|    | 3.10 | The Zilog Z8000 Microprocessor • • • •                | • | • | • | • | • | • | • | 35 |

|    | 3.11 | Zilog Z80000 • • • • • • • • • • • • • • • • •        | • | • | • | ٠ | ٠ | • | • | 37 |

|    | 3.12 | The MC68020 microprocessor • • • • •                  | • | • | • | • | ٠ | • | • | 39 |

|    | 3.13 | The Intel 80386 • • • • • • • • • • • • • • • • • • • | • | • | • | ٠ | • | • | • | 40 |

|    | 3.14 | Summary                                               | • | • | • | • | • | • | • | 42 |

| 4. | MC6  | 8000 COMPUTER SYSTEM                                  | • | • | • | • | • | • | • | 46 |

|    | 4.1  | The supportive processor overview                     | • | • | • | • | • | • | • | 46 |

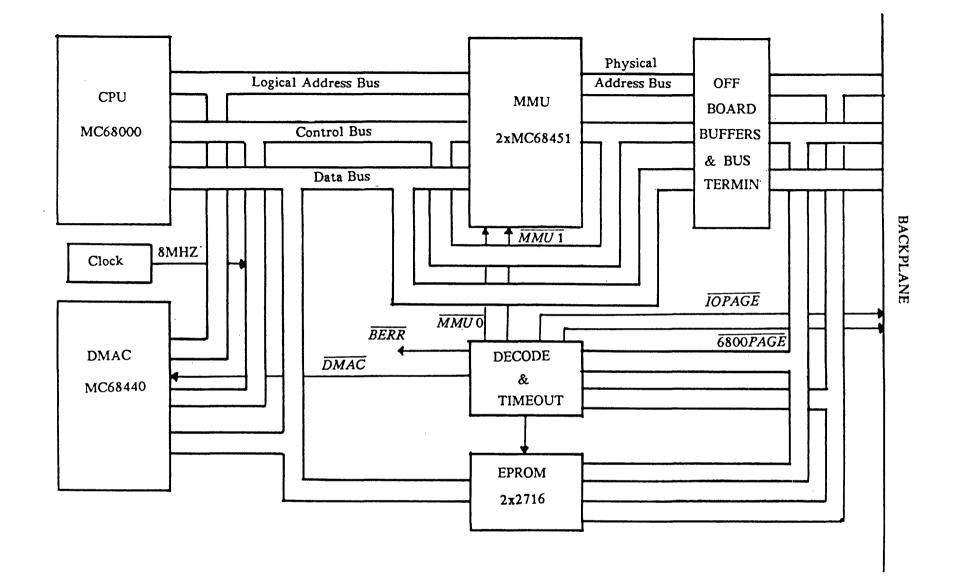

|    | 4.2  | The M68010 Microprocessor • • • • •                   | • | • | ٠ | • | • | • | • | 49 |

|    | 4.3  | The M68451 Memory Management Unit .                   | • | • | • | • | • | • | • | 50 |

|    | 4.4 | The H  |           | 00450    | Direc   | e ivien | 101  | <b>y</b> 1 |     | 0.55 |   |   |   |   |   |        |     |    |

|----|-----|--------|-----------|----------|---------|---------|------|------------|-----|------|---|---|---|---|---|--------|-----|----|

|    |     | Contro | oller .   | •••      | ••      | ••      | •    | •          | •   | •    | • | • | • | • | • | •<br>, | •   | 51 |

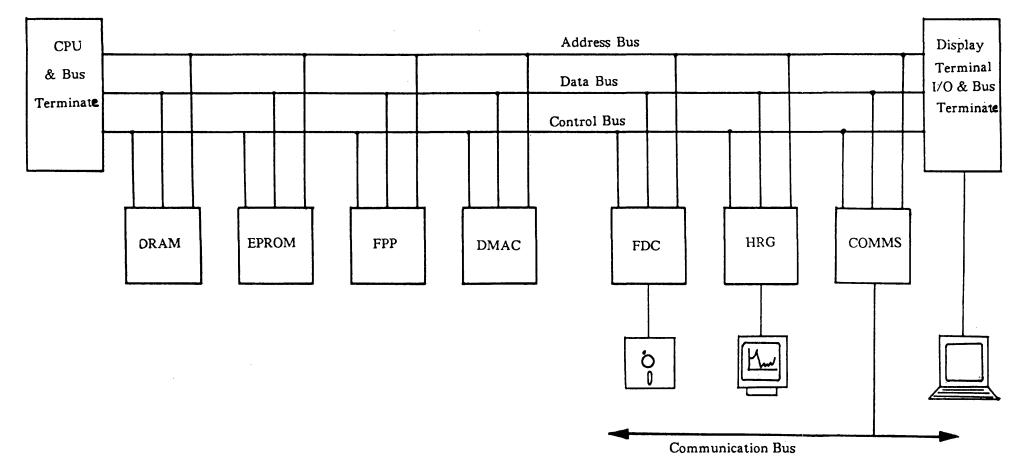

|    | 4.5 | The M  | 1C68000   | Multi-   | board   | comp    | oute | er s       | yst | tem  | l | • | • | • | • | •      | •   | 52 |

|    |     | 4.5.1  | The Cen   | tral Pro | ocessin | g Uni   | t    | •          | •   | •    | • | • | ٠ | • | • | •      | •   | 53 |

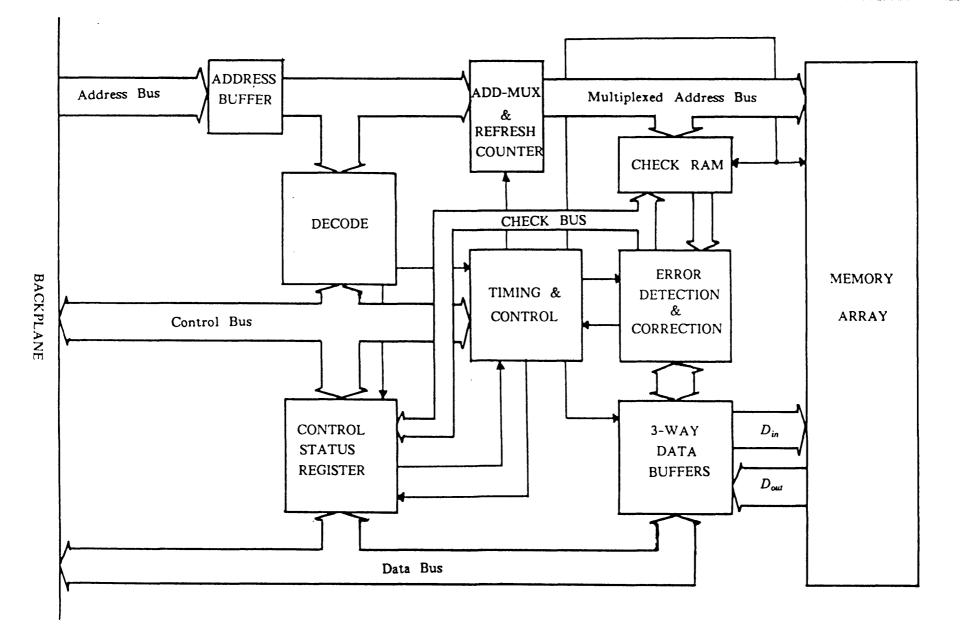

|    |     | 4.5.2  | The Mer   | nory Bo  | oard    | ••      | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 54 |

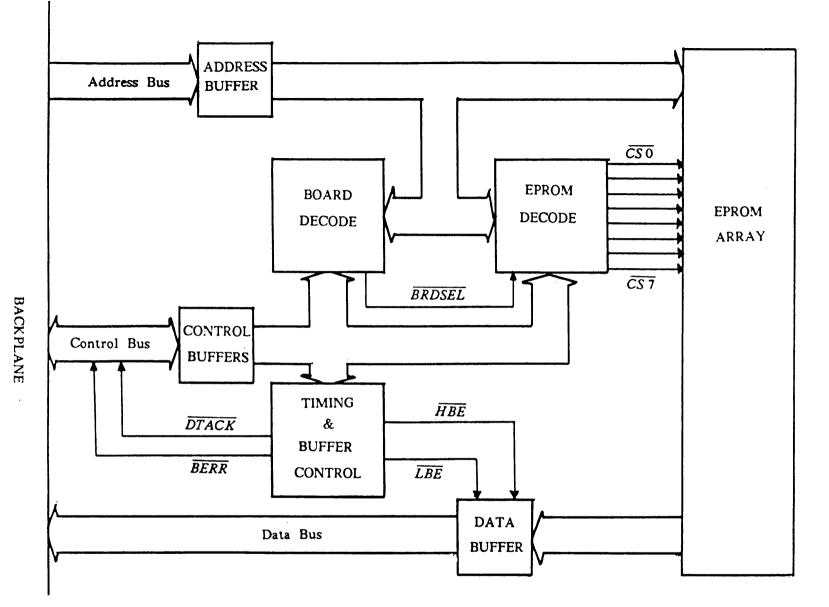

|    |     | 4.5.3  | The EPF   | OM/RO    | DM Bo   | ard .   | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 55 |

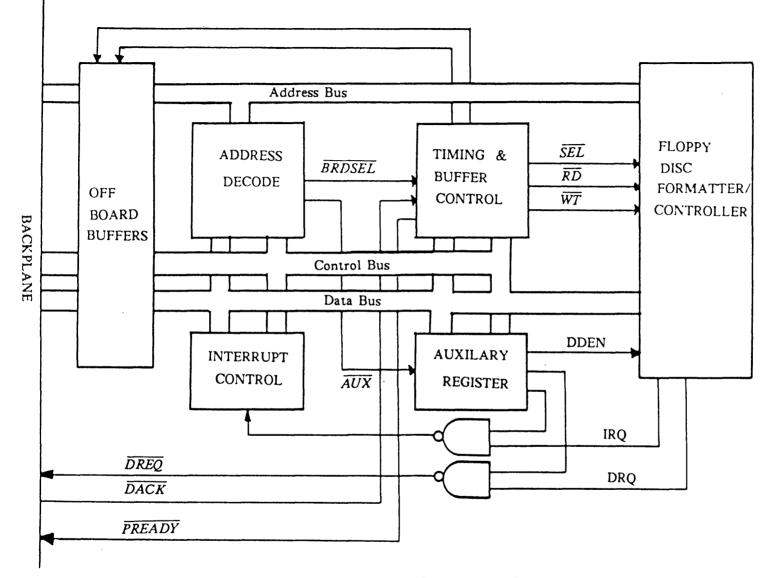

|    |     | 4.5.4  | The Flog  | opy Dis  | c Cont  | roller  | Bo   | ard        | L   | •    | • | • | • | • | • | •      | •   | 56 |

|    |     | 4.5.5  | Hard Di   | sc Inter | face B  | oard    | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 56 |

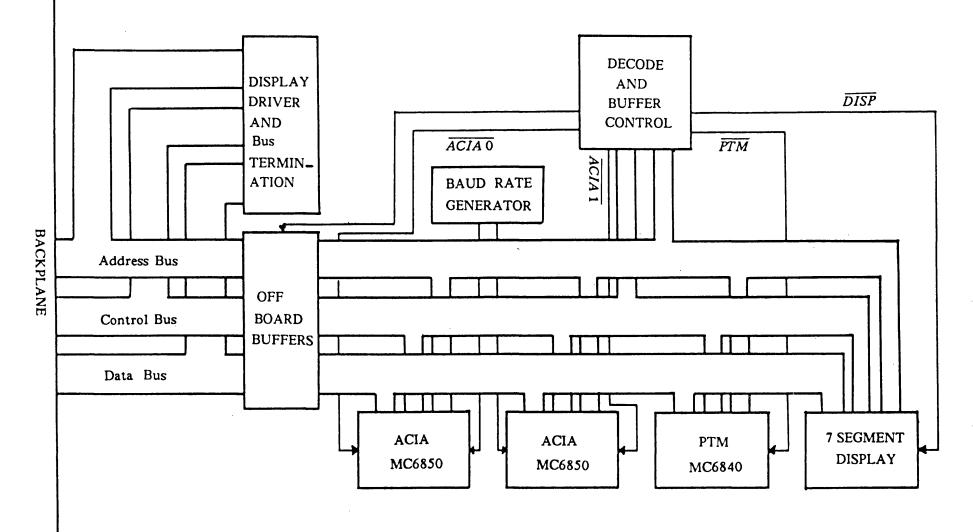

|    |     | 4.5.6  | The Bus   | Displa   | y and ] | Periph  | nera | ls I       | Boa | ard  |   | • | • | • | • | •      | •   | 56 |

|    |     | 4.5.7  | Addition  | al board | ds .    | ••      | •    | •          | •   | •    | • | • | • | • | • | •      | • , | 57 |

|    | 4.6 | The N  | 1C68000   | Single   | Board   | Comp    | oute | r          | •   | •    | • | • | • | • | • | •      | •   | 58 |

| 5. | THE | SOFT   | WARE E    | NVIRO    | NMEN    | ITS .   | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 66 |

|    | 5.1 | Introd | luction   |          | ••      | ••      | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 66 |

|    | 5.2 | The T  | RIPOS er  | nvironn  | nent    | ••      | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 67 |

|    |     | 5.2.1  | TRIPOS    | filing s | ystem   | ••      | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 67 |

|    |     | 5.2.2  | TRIPOS    | Tasks    | ••      | ••      | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 68 |

|    |     | 5.2.3  | Inter-tas | sk comr  | nunica  | tion    | •    | •          | •   | •    | • | • | • | • | • | •      | •   | 70 |

### 4.4 The Hitachi HD68450 Direct Memory Access

|    |     | 5.2.4 | TRIPOS   | device driv  | ers .      | •    | •    | •   | •  | •    | • • | • | • | • | • | 71 |

|----|-----|-------|----------|--------------|------------|------|------|-----|----|------|-----|---|---|---|---|----|

|    | 5.3 | The H | BCPL pro | gramming 1   | anguage    | •    | •    | •   | •  | •    | ••  | • | ٠ | • | • | 72 |

|    | 5.4 | The U | NIX envi | ronment      | • • •      | •    | •    | •   | •  | •    | ••  | • | • | • | • | 73 |

|    |     | 5.4.1 | The deve | lopment of   | UNIX       | •    | •    | •   | •  | •    | ••  | • | • | • | • | 73 |

|    |     | 5.4.2 | The Stru | cture of the | UNIX o     | pe   | rati | ing | sy | ster | n.  | • | • | • | • | 75 |

|    |     |       | 5.4.2.1  | The UNIX     | Kernel     | •    | •    | •   | •  | •    | ••  | • | • | • | • | 75 |

|    |     |       | 5.4.2.2  | The UNIX     | process    | •    | •    | •   | •  | •    | ••  | • | • | • | • | 76 |

|    |     |       | 5.4.2.3  | Interrupts   | and Exce   | epti | ion  | S   | •  | •    | ••  | • | • | ٠ | • | 78 |

|    |     |       | 5.4.2.4  | Inter-proce  | ss comm    | iun  | ica  | tio | n  | •    | ••  | • | • | • | • | 79 |

|    |     |       | 5.4.2.5  | The UNIX     | I/O Syst   | em   |      | •   | •  | •    | ••  | • | • | • | • | 81 |

|    |     |       | 5.4.2.6  | The UNIX     | file syste | em   | •    | •   | •  | •    | ••  | • | • | • | • | 83 |

|    |     |       | 5.4.2.7  | Directory s  | structure  | •    | •    | •   | •  | •    | ••  | • | • | • | • | 84 |

|    |     |       | 5.4.2.8  | The UNIX     | shell .    | •    | •    | •   | •  | •    | ••  | • | • | • | • | 84 |

|    |     |       | 5.4.2.9  | System boo   | ot         | •    | •    | •   | •  | •    | ••  | • | • | • | • | 86 |

|    |     |       | 5.4.2.10 | UNIX utili   | ties .     | •    | •    | •   | •  | •    | ••  | • | • | • | • | 87 |

|    | 5.5 | The C | program  | ming langua  | age •      | •    | •    | •   | •  | •    | ••  | • | • | • | • | 88 |

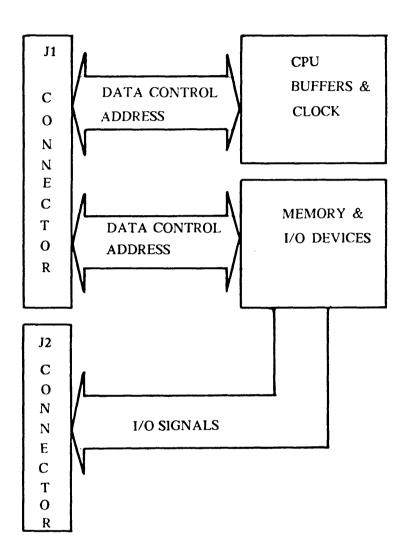

| 6. | THE | EDUC  | ATIONA   | L INTERFA    | CE BOA     | RE   | )    | •   | •  | •    | • • | • | • | • | • | 89 |

|    | 6.1  | Interface specification                                            |

|----|------|--------------------------------------------------------------------|

|    | 6.2  | Hardware design                                                    |

|    |      | 6.2.1 Address decoding logic • • • • • • • • • • • • • • • • • • • |

|    |      | 6.2.2 Arbitration logic • • • • • • • • • • • • • • • • • • •      |

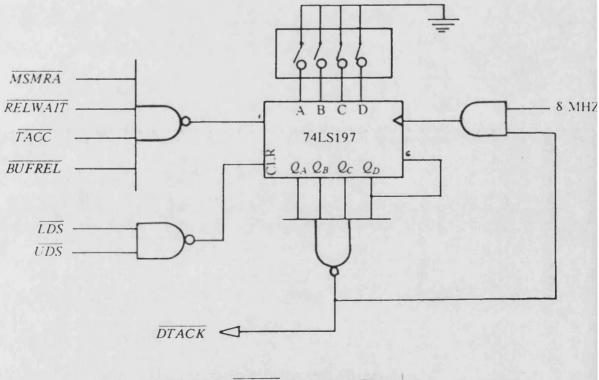

|    |      | 6.2.3 DTACK generation circuit                                     |

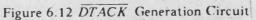

|    |      | 6.2.4 I/O controller                                               |

| 7. | Tarį | et systems                                                         |

|    | 7.1  | Target system specification                                        |

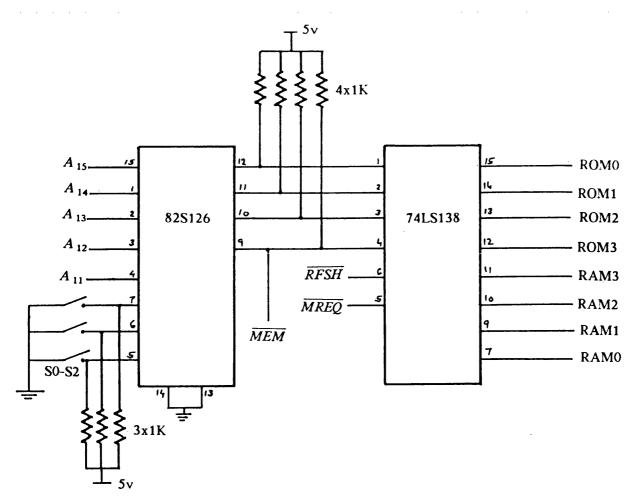

|    | 7.2  | The Z80 target system                                              |

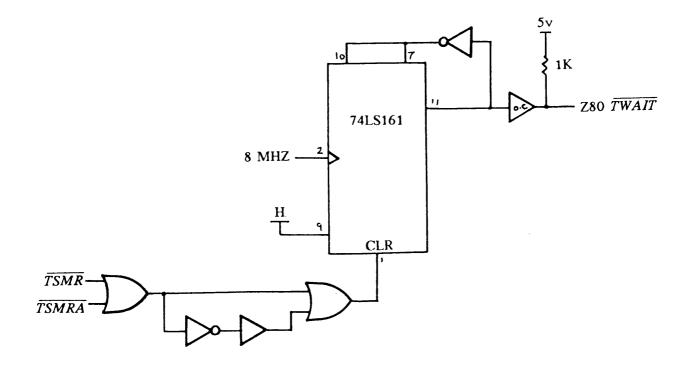

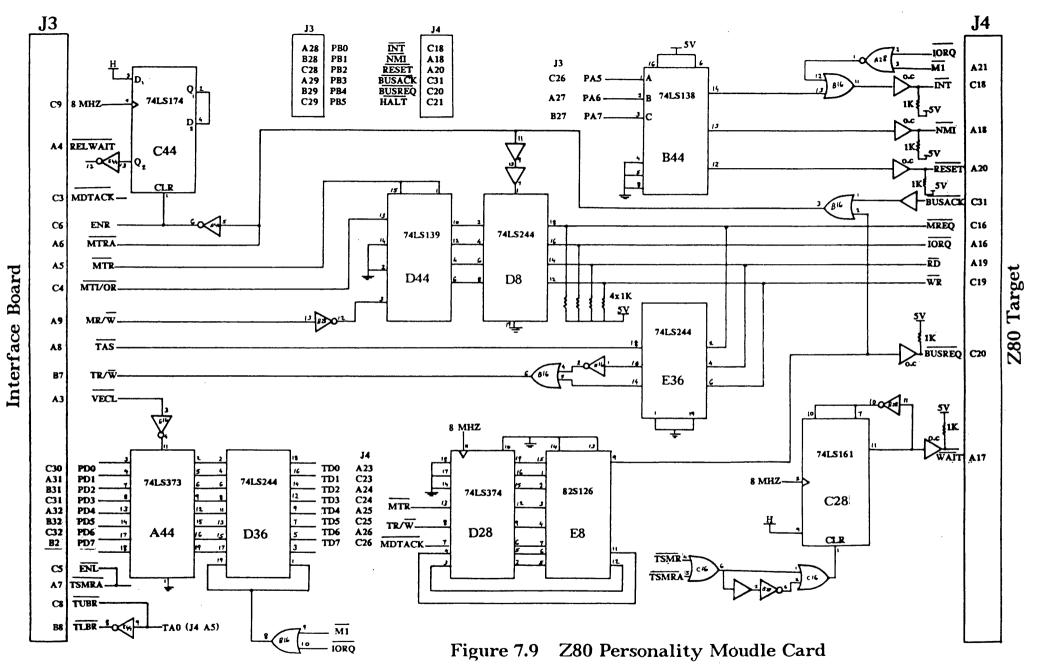

|    |      | 7.2.1 Circuit description                                          |

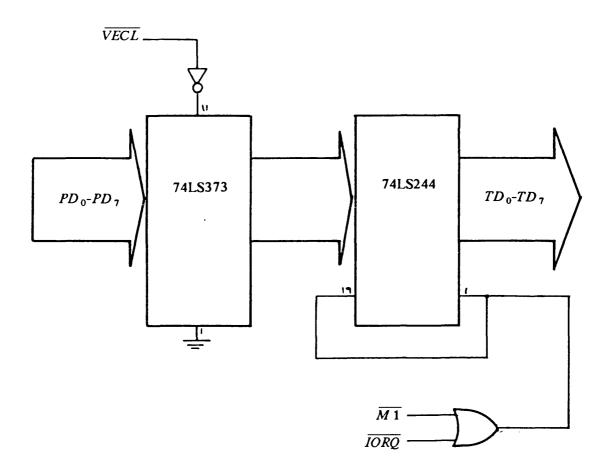

|    |      | 7.2.1.1 The target I/O facility                                    |

|    | 7.3  | The Z80 personality module card                                    |

|    | 7.4  | The Z80 target interface                                           |

|    |      | 7.4.1 Master to Z80 target memory access                           |

|    |      | 7.4.2 The Z80 target to shared memory access                       |

|    |      | 7.4.3 The Z80 target interrupts                                    |

|    | 7.5  | The MC68000 target system                                          |

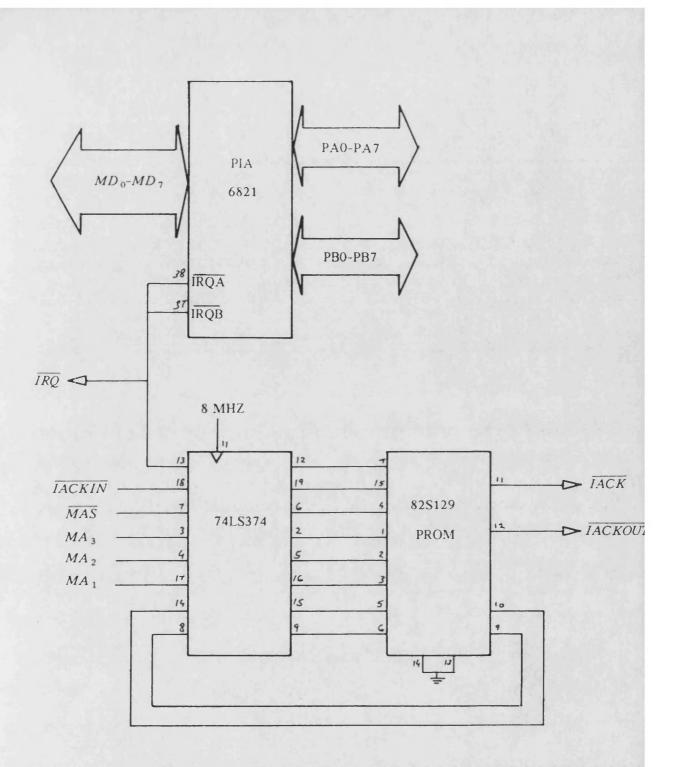

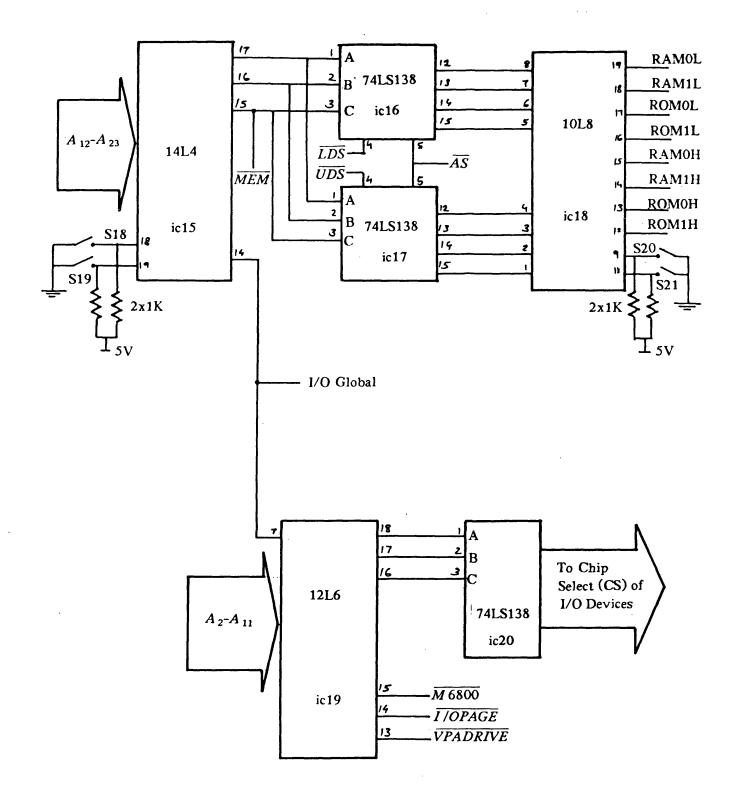

| 7.5.1 Memory maps and manipulation                          | • | 122 |

|-------------------------------------------------------------|---|-----|

| 7.6 The M68000 Personality Module Card                      | • | 126 |

| 7.7 Master to MC68000 target memory access                  | • | 126 |

| 7.8 M68000 target to shared memory access                   | • | 128 |

| 7.9 Target Interrupts • • • • • • • • • • • • • • • • • • • | • | 129 |

| 8. SOFTWARE/HARDWARE INTEGRATION                            | • | 144 |

| 8.1 The UNIX development software environment               | • | 144 |

| 8.1.1 Operation procedure                                   | • | 148 |

| 8.1.2 Support software                                      | • | 149 |

| 8.1.3 The software development cycle • • • • • • •          | • | 150 |

| 8.2 The TRIPOS development software environment             | • | 152 |

| 9. CONCLUSIONS                                              | • | 154 |

| APPENDIX A : Supportive System Bus Specification            | • | 159 |

| APPENDIX B : Z80 Target Bus Specification                   | • | 163 |

| APPENDIX C : M68000 Target Bus Specification                | • | 164 |

| APPENDIX D : PAL Equations                                  | • | 165 |

,

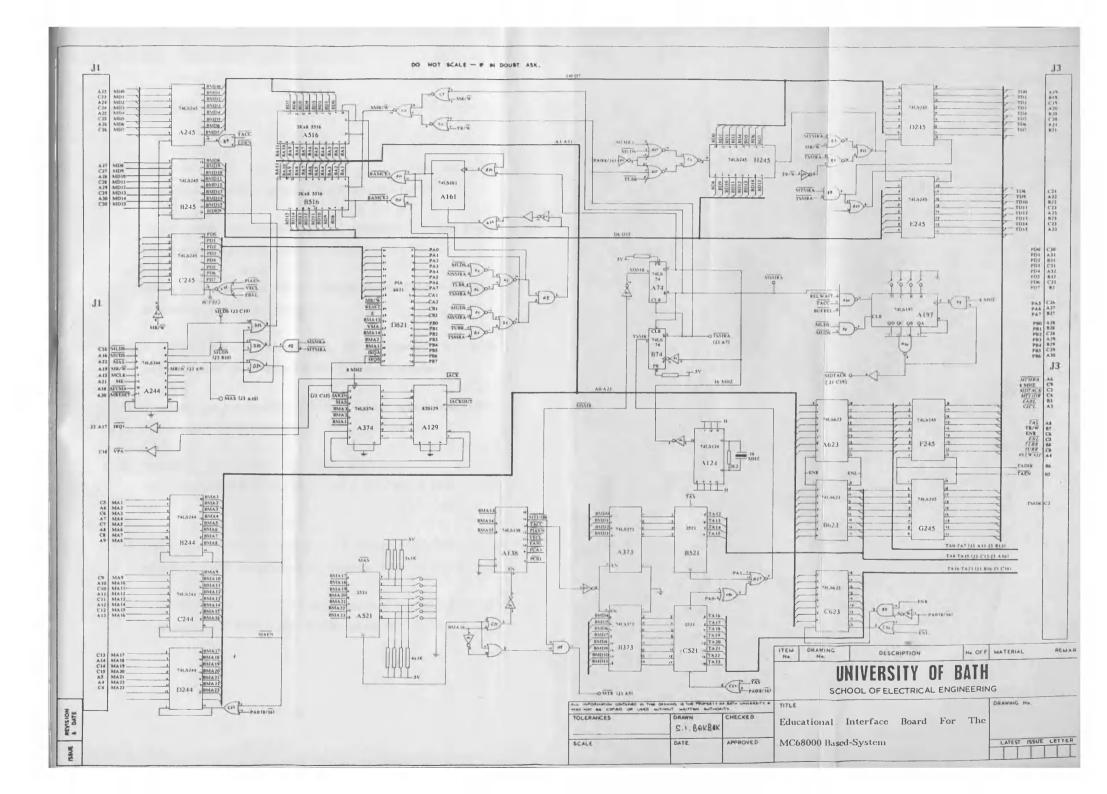

# APPENDIX E : The Educational Interface Board Circuit

| Diagram . | •   | • | • | • | ٠ | • | • | • | ٠ | ٠ | • | • | • | • | • | • | ٠ | ٠ | • | • | • | 168 |

|-----------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| REFERENC  | CES | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 169 |

•

.

### 1. INTRODUCTION

#### 1.1 Microprocessor background

The advancement of large-scale integration (LSI) and very large-scale integration (VLSI) technologies have led to the integration of over one million components on a single silicon chip, and the implementation of most functional units of a traditional processor in a small piece of silicon has led to a chip called a "microprocessor". A microprocessor is the central arithmetic and logic unit of a computer, which is responsible for the fundamental operations upon which all computer intelligence is based. The term was first introduced in 1972, after the era of microprocessors was heralded in 1971 with the introduction of the Intel 4004, a "micro-programmable computer on a chip" [1]. The 4-bit 4004 Central Processing Unit (CPU) contained 2300 transistors and could execute 45 different instructions.

As the earliest microprocessors were 4-bit devices of limited capabilities they were soon followed by 8-bit microprocessors that generally contained a central processing unit control circuitry for the central processing unit, an arithmetic logic unit (ALU) which could perform mathematical calculations, two 8-bit accumulators which are used in "number crunching" tasks, a 16-bit index register to access the memory, an 8-bit condition code register which displays the results of the previously executed instruction, a stack pointer which remembers where stored information was held during an interrupt and a program counter that allowed the microprocessor to know where it is in the program. In order for these microprocessors to perform their functions efficiently, they utilize their instructions in several addressing modes [3].

Although the second generation commenced with the introduction of the Intel 8008 in 1972, the domain of 8-bit microprocessors witnessed several significant improvements in hardware and system concepts with the introduction of the Intel 8080 and the Motorola 6800 in mid 1974 <sup>[3]</sup>. The advanced 8-bit microprocessors with their 8-bit external data bus usually contain 16-bit internal registers and can easily handle 16-bit words.

The need for increased performance and capabilities called for 16-bit microprocessors. The development of 16-bit microprocessors began in 1974 with the introduction of the PACE chip by National Semiconductor. The Texas Instruments TMS 9900 was introduced two years later. Subsequently, the Intel 8086 became commercially available in 1978, the Zilog Z8000 in 1979, and the Motorola MC68000 in 1980<sup>[2]</sup>.

For most of the present requirements and applications, 8 and 16-bit microprocessors have been successful. They have been used to build systems ranging from simple controllers to complex graphic design workstations. However, there are some applications where more processor speed, larger address space, improved performance, high reliability and functionality are required which can only be obtained by the use of 32-bit processors<sup>[4]</sup>.

Microprocessors with 32-bit internal paths have been in existence since 1980. However, the era of true 32-bit microprocessors begins in 1981 with the commercial introduction of the Intel iAPX  $432^{[2]}$  (it has been now withdrawn from the market due to its poor sales due to the radical nature of its object oriented architecture). National Semiconductor was one of first manufacturers to introduce a monolithic 32-bit microprocessor the 32032. Soon after that many powerful 32-bit microprocessors came to existence, like the Intel 80386, Zilog Z80,000, the Motorola MC68020 and recently the Motorola MC68030.

The early microprocessors performed basic CPU functions only. However as the microprocessor technology advanced, the integration of a large number of auxiliary functions on the same microprocessor chip became possible resulting in the increase popularity of computers built with very few chips.

### 1.2 Microprocessor education requirements

During their fifteen years of existence, microprocessors have evolved at a dramatic increase in terms of numbers, technology, complexity, power, functionality and applications. In conjunction with their progress, the power of the processor peripherals and support devices increased rapidly. This enormous technological achievement has introduced major problems and difficulties into the teaching of microprocessor technology to students. The same problem can also be felt by those who educate students in this field. The design and implementation of any prototype microprocessor based system has to pass through several education and development phases before it can reach the production line and the skills and understanding an Electrical Engineering student requires in order to design a system involving a microprocessor or a microcomputer must be defined.

Preparation and learning is the first step, where it is necessary for the student or the engineer to be familiar with digital techniques. That is, the basic understanding of the functions of logic gates and circuits, switching theory, combinational and sequential logic, wave shaping circuits etc. This stage also requires some knowledge of computer organization and microprocessor design techniques. Usually, the theoretical teaching of the subject to student is well established in the undergraduate curriculum programme. The same knowledge can be gained from the special courses offered to engineers who are without prior knowledge of the subject, or in some cases, by self education. Such courses cannot cover all the available devices nor can they examine all the possible approaches to problem solving. Microprocessor literature, microprocessor and computer magazines, and manufacturers manuals should be consulted regularly for up-to date knowledge.

The next phase is associated with the selection of the most suitable microprocessor for the application.

Since there are so many microprocessors available, one should reach a certain level in appreciation of the abilities of as many

- 4 -

microprocessors as possible before a processor is selected. In order to select the most suitable microprocessor for the job, it is required for the student or the engineer to examine several microprocessor families. If a student or an engineer is only familiar with one processor, he will check whether that processor can cope with the job or not. If that is the case, the processor will be used regardless of its suitability.

However, if the student or the engineer has been introduced to several microprocessor families, he will have the skills and experience to choose the most suitable processor and further can examine new devices for their suitability.

In order to expose students to different range of microprocessor families suitable equipment for the practical sessions in software and hardware development is needed a so called development system. A proper development system may have a keyboard and monitor for input and output, floppy disc drives for storage, system modules such as CPU module, memory module, in-circuit emulator, floppy disc controller module, system firmware and monitoring modules. The cost of such a system is usually high and it is essential to provide sufficient sets of development system for each microprocessor family, for the number of users. The number of users could be high, resulting in unnecessary large investment in equipment. This stage of the development represents the central discussion of this thesis.

Once the processor is selected, a set of questions concerning hardware versus software tradeoffs should be answered. Only then

- 5 -

can the detailed hardware design be started.

The next phase is related to software design, since the highest performance of a microprocessor based system is dependent on the quality of the software provided. This stage could be accomplished by the designer himself or by a software expert. The hardware designer should at least provide the necessary software required for testing and debugging the prototype system.

The last phase of the development is related to the production of a working system which successfully performs the required functions.

The work described in this dissertation can be divided to the following three main stages:

- i. Examination of the currently available microprocessor teaching techniques.

- ii. Design and implementation of the new adapted approach.

- iii. Integration of the hardware with development software environment.

## 2. A REVIEW OF MICROCOMPUTER EDUCATIONAL SYSTEMS

The rapid growth in the microprocessor population and the increasing use of microprocessors in education has resulted in many different approaches to the problem of microprocessor teaching and development ranging from simple evaluation kits to more complex in-circuit emulators.

This chapter examines the various available techniques for providing microcomputer education and development and discuss the strengths and weaknesses of each approach.

### 2.1 Evaluation Kits

Evaluation Kits, like the Motorola MEK6800D2 evaluation  $kit^{[5]}$ were originally introduced microprocessor by the manufacturers. They are used to familiarise users with the fundamentals of a specific microprocessor family. In addition to the microprocessor, they contain a small amounts of Random Access Memory (RAM), a resident de-bug monitor, a hexadecimal keypad which is used for input and a multisegment light-emitting display used for output. Only a very limited amount of information can be displayed at any one time, and programs have to be entered in hexadecimal code. The lack of a real editing facilities, together with the limited amount of diagnostic informations that can be displayed, and the necessity of entering programs in machine code, increases the possibility of keying errors and often leads to students frustration.

Although evaluation kits are suitable for gaining familiarity with a particular microprocessor family, they are not really suitable for system educational development or practical applications. As they are designed to be as cheap as possible, they are very difficult to expand.

### 2.2 Single Board Microcomputers

evaluation microprocessor Like the kits. the major manufacturers all offer single board computer families based on their own products<sup>[7]</sup>. The earliest generation of the single board computers had similar facilities to the evaluation kits. With the reduced cost of all types of memory and, with the support of sixteen bit microprocessors, an improved software features and peripheral devices are included in the latest version of the single board computers. The minimum software development facilities for single board computers would include a monitor program to allow users to examine their programs and if required single-step the microprocessor's registers and change memory locations, breakpoint setting etc. An assembler and an editor is provided to construct and input programs. Some single board computer correct the manufacturers support high level languages such as BASIC. Usually such systems would be provided with full QWERTY keyboard, video and storage facility interface.

Single board computers would appear to be a low cost approach to providing a microprocessor educational system, but, by the time additional facilities (such as the QWERTY keyboard, VDU interface,

- 8 -

T.V or a monitor,floppy disc drive, application modules,etc.) are added, they are no longer cost-effective specially if many stations are to be provided for a group of twenty to thirty students. Incidentally, as a result of the added facilities, the board complexity will increase. The true microprocessor architecture will be hidden if students adopt high level language, such as BASIC, at the early stage of microprocessor learning.

### 2.3 Self contained microcomputers

A number of self contained microcomputers, sometimes called "boxed computers" or "personal computers", such as Apple II, ACORN BBC, and IBM PC, are in common use now in homes, schools, and universities. They were designed primarily for use as general purpose processors of information. Typical systems consist of the microprocessor, up to 64K bytes of random access memory for 8 bit processors, read only memory (for the operating system and language VDU compiler/interpreter), with graphics capabilities and cassettes/floppy drives for storage and retrieval of information. Sixteen bit processor self contained systems available today have built in Winchester technology disk drives up to forty megabyte, as much as megabytes of random access memories, and can support simultaneously several users. They support many high level languages such as BASIC, Fortran, Pascal and C. Such systems are increasingly being used for universities and business applications in a stand alone mode or connected to a host mainframe/mini computer system. The hobbyist market is also growing for such systems, and

many companies develop extensive software products for use on such systems.

The boxed computer systems tend to provide better debugging facilities than the systems described previously.

The single unit nature of these systems and their compactness makes it difficult to expand them and difficult to interface their bus to external devices for direct memory access purposes.

Such systems are useful for teaching computer concepts and high level languages. But, due to their capital cost, they are not suitable if more than one microprocessor family is to be studied.

### 2.4 Computer simulation

For some universities, instead of providing microcomputers to allow students to approach the problem of microprocessor education, have run simulators, such as MicroSim<sup>[6]</sup>, on a host computer system. This approach can successfully make a variety of assembly languages available to the student and can allow a number of students to access the simulator without any difficulty in a multi-user environment. But true input/output programming can not be achieved, nor does such a system provide the student with exposure to the hardware or to the peripheral devices connected to the computer. Although simulators can provide useful software support at all levels, the majority of them cannot provide debugging facilities such as single step or trace capability.

### 2.5 In-circuit emulators

The introduction of the microcomputer was quickly followed by the realization that highly specialized design aids are required to support microcomputer-based development efforts.

The in-circuit emulators provide the ability to emulate microprocessor operation in real time, where the system operation is intended to be at clock speed and to display register and memory contents to the user for inspection. With accompanying software, emulators can provide an efficient and powerful development tool to integrate hardware and software development during all phases of the development cycle<sup>[8]</sup>.

There are three categories of in-circuit emulators available<sup>[9]</sup>.

The second form is the computer-hosted emulator, where a host computer is required for the emulation of a target processor operation. Such emulators like the Microcosm family, supporting the Intel 8086/186 family of processors, can receive control from an IBM Personal Computer, a DEC VAX or an Intel Series III development system.

The final form is the in-circuit emulator based-development system, where a microprocessor development system is required for the emulation operation. The in circuit emulator is built into the development system to allow the development system to be connected to the microprocessor target board under investigation. Through an emulator cable, which plugs into the target microprocessor socket, the in- circuit emulation based development system can emulate the target microprocessor and have control at operational speeds over all the signals normally controlled by the microprocessor. This powerful technique allows program execution in the system under test to be traced and interrupted by the user at the console of the development system. Furthermore, resources of the development system such as memory and I/O ports can selectively be made available to the target system.

The development system usually provide sophisticated debugging facilities such as single stepping, software tracing, breakpoints setting, and real time tracing. With single stepping, the program is executed one instruction at a time, where memory contents, processor register contents and the next several instructions, after each step, are displayed to the user to check that the results are those expected. Single stepping is a powerful method of preliminary testing, because bugs can be discovered before they can cause any damage to the program or data. With the updated display the user can alter register and memory contents while stepping through the same segment of code repeatedly and hence can test the code for operation under different conditions. A breakpoint is a trap, set in a program, which allows the program to be executed at full speed or in a trace mode up to where the breakpoint has been set. When the program reach the breakpoint, execution is halted and the development system debugger is in control. Setting breakpoints implies that the user can locate the correct memory address for the breakpoint. Symbolic debugging is a different technique, used by more advanced debuggers, where addresses are referred to as symbolic names, which are defined by the user in his original symbolic source program.

Since microprocessor design is critically dependent on operation in real time, and since single step and software tracing do not provide complete debugging facilities, many development system manufacturers offer logic analyzer or real time trace facilities in to the development system. In a real time trace, the user can connect test leads to a selected number of points on the target board and run the test program to capture data in real time; the traced data cannot include the contents of internal microprocessor registers or of memory.

The latest emulators, such as the SDT816 (Symbolic Debugging Tool for 8 and 16 bit microprocessors) manufactured by Positron Computer Limited U.K, have the ability to assist in symbolic debugging where a symbol table is stored locally. Up to thirty two hardware breakpoints can be set and the system also provides real time trace facilities. Additional to the system microprocessor, the SDT816 can also emulate coprocessor chips and other system chips as well. As there is an emulator for every related type of microprocessor family, the programs can even be executed and tested before any target board is built.

The in-circuit emulator based-development system is the most powerful technique available today to the problem of multi-family microprocessor education and development, and also the most expensive approach where prices ranging from approximately five thousand pounds to well beyond fifteen thousand pounds per station. The high cost is due to their hardware and software complexity. As a result of the high cost, their main use is in commercial firms, while their use in education is very limited . Another disadvantage is that the in-circuit emulators are sold as a complete package, which will tie the user to the development system manufacturer software only.

### 2.6 Mini/Micro communication

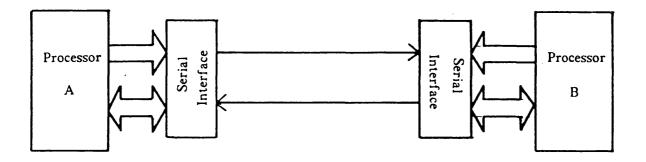

Another approach to the problem of multifamily microprocessor teaching is where a minicomputer is connected to a target processor by the use of serial or parallel link. Through a terminal, the student can get access to the host computer, run the editor and the cross assembler, then down load the object file to the target processor board for stand-alone execution of programs. In stand-alone operation, the target board will be connected to a terminal and the student can use a resident monitor program to examine and control the execution of programs<sup>[10]</sup>.

The disadvantage of this approach lies in the capital cost of the host computer plus the complexity of the target hardware.

Another Mini/Micro communication approach is where the target processor board is interfaced to a minicomputer through an externally controlled DMA channel. The technique is based on the processor initializing a counter system which will provide an address for data to be stored or retrieved when ever this is requested. When a transfer is requested, the counter system will take control over the processor bus and will provide the necessary address and control signals needed to complete the transfer.

Such an approach is described by Holdstock <sup>[12]</sup>, where a Motorola M6800 target board is interfaced to a Digital Equipment Corporation PDP 11/20. Due to the high performance and the high speed of the host computer used, the implementation of the interface to the target processor is forced to be as an input/output device using a DR11C 16 bit input/16 bit output parallel port. This has the disadvantage that the user is tied to a manufacturer supplied cards to provide TTL compatible lines for the target. The high capital cost of the minicomputer is another disadvantage.

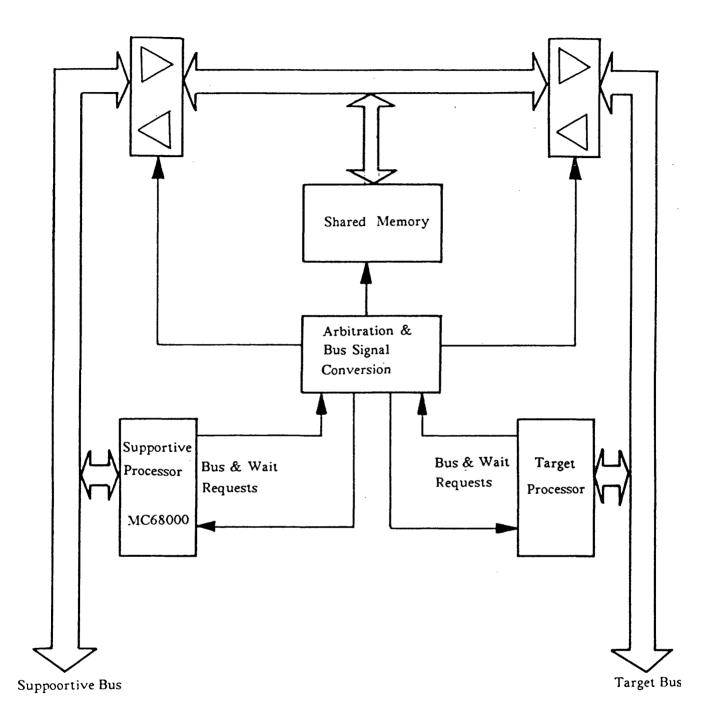

The method examined and implemented in this thesis is similar to the one suggested by Whitworth<sup>[13]</sup>. The suggested technique was based on providing an interface between a Z80 microcomputer and a target system such that the address, data and control lines of each can be translated to the timings and levels expected by devices attached to the other.

This work describes the design and implementation of an Educational Interface Board (EIB) which will allow the MC68000 based-computer system (master) running the UNIX operating system to communicate to any eight, sixteen , or thirty two bit microprocessor based system (target).

### **3.** MICROPROCESSOR BUS STRUCTURES

### 3.1 Introduction

As the function of the Educational Interface Board is to provide a healthy environment for any two dissimilar system buses to communicate, this chapter begins with a discussion of the basic requirement needed for a bus to bus interface followed by a study of various currently available microprocessor bus structures.

The basic structure for any computer system would include the following three major components, the microprocessor unit (MPU) or the central processor unit (CPU) (for arithmetic,logic, and control functions), memory, input/output interface for peripheral control, and three system buses, the data bus, the address bus and the control bus.

Regardless of the number of lines the processor may have, the address, data, and control signals must be available.

The address bus is used by the processor to inform memory and other peripherals of the location it requires to access.

The data bus transfers information between the processor and all the peripherals, including the memory.

The control lines carry all the control signals between the control unit of the processor and all other devices that make use of such signals.

Bus communication can be divided into two categories, synchronous and asynchronous.

The synchronous bus requires the information to be present on the bus at the appropriate time. This procedure implies that the timing mechanisms of the source and destination devices are synchronized. Such systems have to be designed to operate sufficiently slowly in order to accommodate even the slowest devices. The disadvantage of such systems is that the timing of the information transfer is determined by the slowest device in the system, hence preventing fast devices from communicating at their high speed. The principle advantage of such systems is their simple structure with less control signals required.

In the alternative approach, the asynchronous communication bus, the bus transactions are terminated as soon as the required data has been passed. An additional control signal is required in such systems in order for the device being accessed to inform the accessing device that the data is available. The accessing device may respond with another control signal to acknowledge the acceptance of data. The timing of the data transfer depends on the speed of the communicating device. This flexibility is accomplished at the expense of a more complex bus control structure.

As the microprocessor fetches and decodes instructions from memory, a number of control signals will be generated to enable the processor to synchronize its functions with the other components in the system. The number and nature of the control signals varies from one microprocessor manufacturer to another. However, the following control signals are common to most microprocessors.

- a. control signal (or signals) to determine the direction of the data transfer.

- b. A means of a request signal by some peripheral devices to take control over the system bus for direct memory accesses.

- c. A means of grant signal that is to be used by the processor to acknowledge transfer of control to external device.

- d. A means of control signal that is to be used by slow memory or I/O devices to effectively slow down the processor in order for the slow device to complete its task.

- e. A means of interrupting the processor to demand attention and to direct the program from its normal activity into another higher priority service program.

- f. A means of gaining absolute control over the processor. This is usually achieved by the use of RESET control signal, which resets most of the processor internal registers to zero before setting up the program counter to point at some pre-determined location.

As the Educational Interface Board was designed to provide a demonstrative and supportive tool for users, any features which are available on the target processor should be available for investigation. Also, it should be able to monitor and activate all the target control lines.

In general, the sequence of events involved in processor to memory or I/O transfer is as follow :

- i. A means of selecting a memory location to be accessed by initiating a bus cycle by the processor.

- ii. A means of informing the memory device of the direction of the transfer i.e a read cycle or write cycle.

- iii. Indicators to show that the address and/or the data lines are in a stable state.

- iv. An acknowledge indicator to inform the processor that the device is accepting the transfer.

As there are many processor/memory protocol techniques used, the above features have to be provided by one method or another.

When two dissimilar buses are to communicate, the following points require special consideration :

- 1. The width of the address and data buses of the two microprocessors concerned.

- 2. Whether any of the processors is using a multiplexed data and address bus. If this is the case, the interface board should be able to demultiplex and multiplex the buses as required.

- 3. The basic control signals for bus to bus interface must be available.

4. Voltage compatibility is an important factor to be considered. But since the common microprocessor interfaces and drivers available today are found to be TTL compatible, it is likely that this will be of any major problem.

The next subsection gives a brief introduction to virtual memory, memory management, paging and segmentation. These terms are to be mentioned later when describing various microprocessor bus structures.

### 3.1.1 Virtual memory

The first generation of microprocessor-based systems were implemented around 8-bit microprocessors. The address range of such systems was limited to 64 Kbytes. But with the decline cost of dynamic RAM (DRAM), it became economically possible to cover the entire address space, not including those spaces which are already occupied by ROM or I/O devices, with RAM. Such implementation has offered one to one correspondence between logical addresses ( which are generated by the processor over its address bus) and physical addresses ( which are real memory locations where data is read from or stored at). But soon the limitation of 64 Kbytes address range was realized. With today's 16 and 32 bit microprocessors, this address range is no longer a problem, however, other variables (such as cost, size and power consumption) are to be considered. Taking these factors into account, it becomes impractical to cover the address range of such processors with RAM. Virtual memory has been used to solve such a problem. The virtual memory technique is based on swapping the unused parts of a program between main memory and a secondary memory (such as a hard disk unit) as required. A memory management unit (MMU) is usually used for this purpose. One of its main functions is to translate the logical addresses into physical addresses to give the user the illusion that all the logical addresses are actually implemented.

Two common techniques are used by most memory management systems, they are paging and segmentation. With paging the memory is divided into fixed size blocks, pages, usually between 512 bytes and 2K bytes  $long^{[44]}$ . With the segmentation approach the logical space is divided into segments of varying length. Each scheme has its advantages, paging simplifies the allocation of memory to users and segmentation simplifies protection of different areas of user memory space<sup>[45]</sup>.

The next sections will present the study of several popular 8, 16 and 32-bit microprocessor bus structures.

### 3.2 Motorola MC68000

The Motorola MC68000 <sup>[16]</sup> was the first microprocessor to provide a true 32-bit internal architecture for its address and data paths. Externally, the MC68000 has a 16-bit  $(D_0-D_{15})$  bidirectional data bus and a 23-bit  $(A_1-A_{23})$  address bus that directly accesses 16 megabytes of memory.  $A_0$ , the least significant bit of the address bus is used internally to the processor to generate the data size specified by each instruction.

In simple systems, the MC68000 requires only four output signals to initiate data movement between memory and the processor. These signals are the address strobe  $(\overline{AS})$ , the upper data strobe  $(\overline{UDS})$ , the lower data strobe  $(\overline{LDS})$ , and the read/write signal  $(\mathbb{R}/\overline{W})$ . In a read cycle, the address strobe signal  $(\overline{AS})$  is asserted to indicate that a valid data address is being output on the address bus. Simultaneously, the  $\overline{UDS}$  and  $\overline{LDS}$  signals are asserted to enable the selection of either the lower/upper data byte or both bytes. The processor now waits for the participant memory or I/O device to present its data on the data bus and to assert the Data Transfer ACKnowledge  $(\overline{DTACK})$  signal to indicate the completion of the data transfer. This technique is the inverse logic used by most other microprocessors where the processor will complete the read/write cycle within a fixed time, unless the input wait signal is asserted. The major bus interface of the MC68000 is the asynchronous timing of the data bus transfers. With this interface flexibility, the access timing of the processor is dynamically controlled on each bus cycle by the device being accessed via the handshake signal  $\overline{DTACK}$ . Thus, devices with vastly different access times can be mixed to perform at maximum speed.

The asynchronous bus structure also handles hardware failures and invalid memory accesses. If an access is made to invalid memory or I/O location, the  $\overline{DTACK}$  signal will not be asserted. The MC68000 processor provides a mechanism to ensure that the processor will not be hung up indefinitely by a device that fails to respond. This is provided by the input signal,  $\overline{BERR}$ , which when asserted, causes the processor to enter exception processing to handle the error.

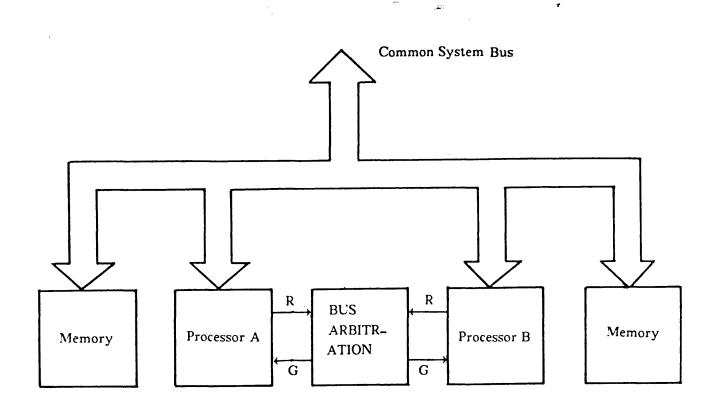

There are three signals associated with the MC68000 bus arbitration scheme, Bus Request ( $\overline{BR}$ ), Bus Grant ( $\overline{BG}$ ), and Bus Grant ACKnowledge ( $\overline{BGACK}$ ). When the processor receives a bus request signal, it responds by asserting the  $\overline{BG}$  signal which indicates the bus will be available as soon as the current bus cycle is completed. The external device must wait for the  $\overline{AS}$ ,  $\overline{DTACK}$  and  $\overline{BGACK}$  signals to be inactive before it can assert  $\overline{BGACK}$  signal and negating  $\overline{BR}$  signal to claim the mastership of the bus. The processor output lines then will enter a high impedance state until  $\overline{BGACK}$  signal is released by the external device indicating that it is through with the bus. The bus arbitration logic provided by the MC68000 processor is the most comprehensive and straight forward technique to date.

The MC68000 processor can also take advantage of existing M6800 support devices. To ensure bus compatibility, the MC68000 uses three special lines to access the 8 bit M6800 family of synchronous peripherals, they are Valid Peripheral Address ( $\overline{VPA}$ ), clock Enable (E), and Valid Memory Address ( $\overline{VMA}$ ) lines. When the M6800 peripheral address is decoded, the  $\overline{VPA}$  signal is asserted instead of the normal handshaking signal  $\overline{DTACK}$ . The assertion of  $\overline{VPA}$  signal informs the processor to become compatible with the M6800 family by waiting for the proper phase of the E clock and then asserting the  $\overline{VMA}$  signal to ensure the transfer. The  $\overline{VPA}$  signal

serves a different purpose when asserted during an interrupt acknowledge cycle. It indicates to the processor that it should obtain a vector from its table rather than the interrupting device.

The bidirectional  $\overline{HALT}$  line of the processor can perform several functions. Like any other microprocessor halt or hold signal, it is used to disable the processor. It is used in conjunction with bus error  $(\overline{BERR})$  signal to indicate to the processor to try running the bus cycle again. Also, the halt signal can be used with the  $\overline{RESET}$  line to initialize the MC68000 processor.

### 3.3 The Intel 8086 Microprocessor

The 8086 was the first 16-bit microprocessor to be produced by Intel. With it came a new generation of business and personal computer era supported by several manufacturers, notably IBM.

The 8088 is another member of the Intel family which is closely related to the Intel 8086. Both support sixteen bit transfers within the processor, and both have twenty address lines to directly access one megabyte of memory. The address lines of the 8086 are multiplexed, like its predecessor the 8085, with sixteen data lines and four status lines in order to have a 40-pin package. However, the 8088 has only eight data lines restricting its transfers with memory and I/O devices to bytes only. Other than the data bus width, both processors support the same instruction set.

The 8086 central processing unit logic has been divided into an

Execution Unit (EU) and Bus Interface Unit (BIU), mainly to allow the processor to fetch new instructions from memory while it is busy executing some other instructions. The two units operate asynchronously and the processor can in most cases overlap the instruction fetch with execution.

An important feature provided for the Intel 8086 is the provision for maximum or minimum mode system. To select the required mode, an input line  $(MN/\overline{MX})$  is tied high or low. When in the minimum mode the processor provides the complete standard microprocessor control signals required to interface memory or I/O devices. In the maximum mode multi-processor system, the processor can support a variety of Intel's co-processors which include the 8089 input/output processor and the 8087 numeric data processor. The minimum mode bus configuration which has less circuit complexity is more appropriate for this study of microprocessor bus structures, so only the minimum mode will be refeared to.

There are two address spaces provided by the processor, the Memory/IO ( $M/\overline{IO}$ ) control signal indicates whether memory or an I/O port is being accessed. The sixteen bit data bus is divided into low and high bytes.  $A_0$  (the least significant bit) of the address bus and  $\overline{BHE}$  (bus high enable) signals are used to select the low, the high or both bytes. An Address Latch Enable (ALE) signal is used to identify a valid memory address to allow system components to capture the address information before the same lines carry data information.

The data transmit/receive  $(DT/\overline{R})$  and data enable  $(\overline{DEN})$  are two

new signals not found in earlier Intel processors. They are used to control the direction and output enable of a bidirectional latched buffers on the data bus and are designed specifically to work with an 8236/8287 bus transceivers. The input HOLD signal is used by other devices to request the use of the system buses for direct memory accesses. When HOLD is asserted, the processor enters a hold state after completing its current bus cycle. The processor then asserts the HLDA (hold acknowledge) signal to acknowledge the hold request. The input signal READY informs the processor that the addressed memory or I/O device is ready to complete the current bus cycle. The bus continues to cycle until the READY signal is asserted. This signal is useful when the processor is to communicate with devices of different speeds.

Another innovative feature of the 8086 hardware design is the ability to use it in a wide range of microcomputer system configurations, from a simple one processor system to a multiprocessor environment. The processor has built in logic to handle bus access priorities. The signal  $\overline{LOCK}$ , which is provided only in the maximum mode, is used in a multi-processor system to prevent a processor from accessing the bus while another processor is reading or writing a memory location. Software single step facility is another feature of the Intel 8086 to support the programming of multiprocessor systems.

- 27 -

## 3.4 The Intel 80286

. . .

The 80286 is the second generation of sixteen bit microprocessors introduced by Intel. Several advanced features have been introduced in the 80286 processor, such as memory management mechanism and hardware provision of multi-tasking programming by operating in two modes real and protected. The 80286 is software compatible with its predecessors the Intel 8086 and 80186 when operated in real mode.

The processor uses separate (non-multiplexed) 16-bit data bus and 24-bit address bus. Additional to the buses width, the Intel 80286 has a similar bus structure to that of its predecessor the 8086.

### 3.5 Zilog Z80 microprocessor

The Zilog Z80 was designed as an enhanced version of Intel's 8080 microprocessor. It is an eight bit microprocessor with sixteen address lines capable of direct access to sixty four kilobytes of memory space. The success of the Z80 processor is due to its capability to execute the entire range of Intel's 8080 software and in particular, to use the popular operating system CP/M (Control Program for Microcomputers) developed by Digital Research.

The Z80 has additional features over the Intel 8080, like an on board refresh counter for dynamic memory, a non-maskable interrupt facility, and a vectored interrupt priority structure. Several Z80 processors are available, offering a range of clock speeds of 2.5

MHZ, 4 MHZ and 6 MHZ. Another improvement over the Intel 8080 is that the Z80 requires only a single 5V supply and single phase clock input.

Similar to the approach development by Intel, the Z80 has separate memory and input/output address spaces. The  $\overline{MREQ}$ (memory request) signal is used to select a valid memory address and the  $\overline{IORQ}$  signal is used to select a valid input/output address space.  $\overline{RD}$  and  $\overline{WR}$  signals are used to control the direction of data transfers. In a typical memory read cycle, the  $\overline{MREQ}$  signal will asserted when the address bus is stable. Then the  $\overline{RD}$  signal is asserted to indicate that the data can be enabled onto the data bus. Depending on the accessing of memory or input/output devices, wait states can be inserted as required. However, not too many wait states can be inserted, if the role of dynamic memory refresh is not to be affected.

The Z80 was the first microprocessor to include a hardware facility for automatic dynamic memory refresh. After each instruction fetch cycle, the refresh control signal becomes active to indicate the start of dynamic memory refresh.

When the Z80 processor has to give up its bus to an external device, the  $\overline{BUSRQ}$  signal must be asserted first to request the bus. When the Z80 complete its current bus cycle it sets its address, data,  $\overline{MREQ}$ ,  $\overline{IORQ}$ ,  $\overline{RD}$  and  $\overline{WR}$  lines to the high impedance state and activates  $\overline{BUSAK}$  signal to acknowledge the request.

#### 3.6 The Motorola MC6800 microprocessor

The MC6800 was Motorola's first eight bit microprocessor. It has 8 lines of data bus, and 16 address lines to access up to 64 kilobytes of memory space. Unlike the Z80 bus timings, the MC6800 requires a two phase non-overlapping clock  $\phi$ 1 and  $\phi$ 2.  $\phi$ 1 and  $\phi$ 2 are used as address and data validators respectively. During the first phase of the clock, an address will be placed on the bus by the processor. During the second phase of the clock, the data bus will be active. The implementation of direct memory accesses, refreshing dynamic memories, or accommodating slow memories rely heavily on the clock signal manipulations.

For direct memory access operations, the Three State Control (TSC) input signal can be used. With TSC activated (high), the address bus and  $R/\overline{w}$  signal are placed in high impedance state. The Valid Memory Address (VMA) and Bus Available (BA) signals are forced low in order to prevent any incorrect read or write data on any device enabled by the VMA signal. While the TSC line is active, the  $\phi$ 1 and  $\phi$ 2 clocks must be held high and low ,respectively, in order to delay program execution for DMA operation to take place. But since the MC6800 processor is a dynamic device, internal memories require periodic clock cycles to maintain correct data and the clocks can be stretched for no more than the required periodic cycle of 10 microseconds.

Direct memory access operation can also be provided by completely halting the processor, using the input  $\overline{HALT}$  signal, which

stops program execution. The required periodic cycle of the clock inputs of 10 microseconds has to be maintained.

As the  $\phi$  1 and  $\phi$  2 clocks time the entire M6800 system, any processor that accesses the M6800 system will be affected by the action of the M6800 clock. In the master/slave configuration, the master direct memory access cycle to the M6800 target system must complete within the 10 microseconds limit.

#### 3.7 The Motorola M6809 Microprocessor

The Motorola M6809 is an enhanced version of the M6800 family of microprocessors. The changes are mainly to improve its available software facilities.

The M6809 is an 8-bit microprocessor with 16 bit address bus. Unlike the MC6800, which uses a two phase non-overlapping clock, the M6809 has an internal clock, which is triggered by an external crystal, to generate two quadrature output clocks E and Q. The E clock phase, which is identical to  $\phi 2$  of the M6800, gives a synchronizing signal to be used as the system's clock for support devices. The Q phase of the clock is available to signal that the address and data leading edge of Q and data is latched on the falling edge of E.

The input signal MRDY is used to stretch the E and Q clock signals to enable the processor to interface with slow memory devices.

- 31 -

For direct memory accesses, the input signal DMA/BREQ is used. When activated, it causes the processor to be suspended at the end of the current instruction to enable direct memory access operations. The direct memory access operation is timed with the E and Q clock signals, so that the required periodic cycle of 10 microseconds is still applied.

A second version of the M6809 family is the M6809E, which has external clock inputs E and Q. The M6809E uses the TSC input signal to force the processor into high impedance state for direct memory accesses or dynamic memory refresh.

Three other status signals are available for the M6809E. The Last Instruction Cycle (LIC) output signal is activated during the last cycle of an instruction. The BUSY signal is used to indicate that the processor is performing functions which should not be interrupted by other external devices. The Advanced Valid Memory Address (AVMA) output line will inform that the processor will use the buses in the following cycle and efficient bus sharing in multiprocessor configuration can be allowed.

### 3.8 The Mos Technology 6502 Microprocessor

The 6502 is the most popular of the 6500 family of 8-bit microprocessors manufactured by MOS Technology. The 6502 processor has made its major success in the home computer market with the leading manufacturers Apple, Acorn BBC and Commodore.

The 6502 was produced as an enhancement of Motorola MC6800 microprocessor. It has similar CPU concepts and bus structure. The 6502 popularity was due to its increased performance with two index registers and a more powerful set of addressing modes.

Similar to all 8-bit microprocessors, the 6502 has eight data lines and sixteen address bus. In a similar way to the M6800 the 6502 uses two phase non-overlapping clock signals to control system timing. During the first phase the processor sets up a valid memory address and selects the data direction using the  $R/\overline{W}$  line. Data is then transferred during the second clock phase.

There are two major differences between the bus structure of the 6502 and the MC6800. Unlike the M6800, the clock pulses of the 6502 can not be stretched, therefore, the 6502 has to use a different accesses or refreshing dynamic memories. The 6502 control input signal RDY, which performs the task of M6800 TSC, DBE and  $\overline{HALT}$ signals, causes extra machine cycles, wait states, to be inserted within the normal machine cycle. For wait machine cycles to occur, the RDY signal must make a high-to-low transition during a phase one high clock pulse. The external device can hold RDY signal low for any required time delay. In addition the 6502 processor has no control signals that can force it into high impedance state, and the processor address and data buses must be latched during any direct memory access operation.

The SYNC output signal is used by the processor as an indication of the instruction fetch cycle.

#### 3.9 The Texas 9900 microprocessor

One of the early 16-bit microprocessors to appear on the market was the 9900 produced by Texas Instruments. The 9900 has been designed as a one-chip implementation of the CPU of the 990 series minicomputer. The 9900 has been a very effective processor for signal processing applications.

The 9900 has a separate 15-bit address bus and a 16-bit data bus in a 64-pin integrated circuit package. The 9980 is a reduced pin count version of the 9900 with only 8-bit data bus and 15-bit address bus.

The standard 9900 processor requires a four phase nonoverlapping clock, where none of them is used for address or data validator signal.

For a typical read cycle,  $\overline{MEMEN}$  (MEMory ENable) output signal is used to indicate its a memory access cycle. It is also used to differentiate between memory or I/O accesses. The DBIN (Data Bus In) signal is activated to indicate the beginning of a memory read cycle, when data should be placed on the bus by the memory device. The  $\overline{WE}$  (Write Enable) signal is used if it is a memory write cycle to validate data to be written to memory.

The  $\overline{HOLD}$  input signal is used to force the processor into high impedance state for direct memory accesses; the external device can assert the  $\overline{HOLD}$  line active for as long time as it require. The processor acknowledge the request by asserting HOLDA (HOLD

Acknowledge) line.

To accommodate slow memory devices, the READY input signal is used to indicate to the processor to insert wait state cycles as required.

## 3.10 The Zilog Z8000 Microprocessor

The Z8000 family of sixteen bit microprocessors is available in two versions, the Z8001 and the Z8002. The Z8002, 40-pin package device, can directly access sixty four by the sof memory. The Z8001, 48-pin package, is a more advanced processor and capable of addressing up to eight megabytes of external memory. Other than the difference in the address range, the two processors are closely related to each other. Both processors have time-multiplexed address and data bus to minimize the pin count of the microprocessor package.

The Z8000 processor architecture utilises a sixteen bit word organization. Each word of memory is made up of two independently accessible bytes. The Z8002 uses a sixteen bit address to specify one of 32K words of memory, where both bytes in a word are independently accessible. The least significant bit of the address bus, A0, is used to specify an even address byte ( $A_0=0$ ) or an odd address byte ( $A_0=1$ ). The Z8001 uses the concept of segmentation to increase its address space, where the address map is seen to consist of 128 memory segments per memory address space with each segment having a 64K bytes. The Intel 8080 provides similar segmentation facility, but can only access up to one megabytes of memory.

The Z8000 processor can operate in one of two different modes, system mode or normal mode. A control bit in the flag and control word (FCW) indicates the operation mode. In the system mode all instructions can be executed, while in the normal mode only unprivileged instructions are executed. The distinction between the system and normal modes of operations allows the implementation of a multi-tasking facility, where instructions that can directly affect the system hardware or can terminate all the programs are privileged instructions, which should not be executed by the user. In contrast, the Intel 8086 offers no equivalent hardware logic for multi-tasking facilities but does provide similar facilities using software method.

The Z8000 processor has two special control lines dedicated to a multi-processor environment. The Multi-micro Input ( $\overline{MI}$ ) signal is used by the Z8000 processor to prevent other processors from accessing the bus while it is performing critical manipulations, and the Multi-micro Output ( $\overline{MO}$ ) signal is used to disable the Z8000 processor while another processor is in charge of the bus.

For a typical data transfer cycle, an Address Strobe  $(\overline{AS})$  signal indicate a valid address, a Data Strobe  $(\overline{DS})$  signal shows valid data, a Read/Write  $(R/\overline{W})$  signal is used to select the direction of the transfer, a Byte/Word  $(B/\overline{W})$  signal to select the size of the data field being transferred, and a Normal/System  $(N/\overline{S})$  signal is used to indicate the current operation mode of the processor. Unlike the Z80, the Z8000 Memory Request  $(\overline{MREQ})$  signal is used to select a memory space or input/output space.

This processor has a more flexible dynamic memory refresh capabilities than its predecessor the Z80 microprocessor.

For direct memory accesses, the external device can request the control of the bus by asserting a Bus Request ( $\overline{BUSRQ}$ ) signal, and, when the processor is ready to relinguish the bus, it activates the Bus Acknowledge ( $\overline{BUSAK}$ ) signal to acknowledge the request. The combination of the  $\overline{BUSRQ}$  and  $\overline{BUSAK}$  signals provide the processor with hold state logic<sup>[18]</sup>. The  $\overline{WAIT}$  signal can be used by external devices to increase the delay between the address strobe and data strobe during bus transactions.

The *STOP* input signal can be used to halt the processor operations and can also be used to provide externally single stepping logic for programs under development.

## 3.11 Zilog Z80000

The Z80000 is the latest generation of Zilog microprocessors. The processor features 32-bit advanced architecture which directly supports operating systems and high level languages. The processor characteristics and facilities are merely an extension of the Z8000 family with new added features as on-chip memory management and small on-chip cache memory. The Z80000 has full 32-bit address and data time multiplexed lines, and can directly address up to 4 gigabyte of memory. The bus status and time signals used by the processor to perform asynchronous data transfers are similar to those used by its predecessor the Z8000. The address strobe ( $\overline{AS}$ ) signal indicates that the address and bus status signals are valid. The data strobe ( $\overline{DS}$ ) signal is used to time all data transfers. The read/write ( $\mathbb{R}/\overline{W}$ ) signal to select the transfer direction. Two status signals ( $\mathbb{BL}/\overline{W}$  and  $\mathbb{BW}/\overline{L}$ ) are driven by the processor to specify the size of the data (byte, word or long word) involved in the transfer operation. Four status output signals (STO-ST3) are used to encode the type of bus cycle (such as internal operation, I/O transaction, halt and  $\overline{NMI}$ acknowledge) performed by the processor. The external logic can then decode this information and respond in a number of different ways.

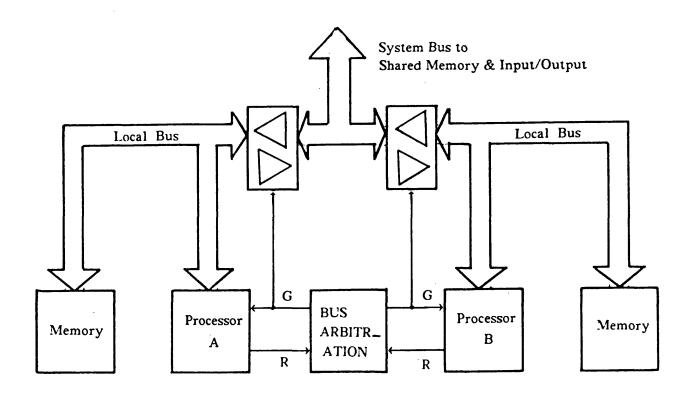

The processor architecture supports two control buses, local and global. The local bus consists of the two familiar signals  $\overline{BUSREQ}$  and  $\overline{BUSACK}$  that are used by external devices to gain mastership over the processor buses for direct memory accesses. In a multiprocessor environment, the Z80000 can request the mastership of a global bus by asserting the global bus request line ( $\overline{GREQ}$ ) and obtains the response of the bus arbiter via the global acknowledge signal ( $\overline{GACK}$ ).

During each data transfer, two response (RSPO-RSP1) signals are used by external hardware to return a code to the processor indicating ready, wait, bus error, or bus retry. The ready response informs the processor of a successful transfer. The wait response tells the processor that the responding device requires more time to complete the transfer, other wait cycle is then added before the sampling of the response lines again. Wait states can also be inserted by programming the hardware interface control register (HICR).

The Z80000 architecture includes 256 byte of high speed cache memory used to speed up the processor operations. The cache memory can be disabled for debugging purposes by using the control bit in the system configuration control long word register (SCCL).

#### 3.12 The MC68020 microprocessor

The MC68020 microprocessor is the full 32-bit implementation of the M68000 family architecture. Its address bus is capable of accessing a large linear (not segmented) address space of four gigabyte of memory. The MC68020 architecture is merely an extension of earlier processors in the family.

As the MC68000 processor, the asynchronous bus structure of the MC68020 uses a 32-bit address and data buses that are nonmultiplexed for simple interface design and high performance.

The MC68020 bus interface includes a new feature, dynamic bus sizing, which allows the processor to communicate with 8, 16 or 32-bit devices through the use of the Data transfer and Size ACKnowledge input signals ( $\overline{DSACK0}$  and  $\overline{DSACK1}$ ). The  $\overline{DSACK0}$  and  $\overline{DSACK1}$  signals replace and perform the same function as the  $\overline{DTACK}$ control signal of the MC68000 processor, they also inform the CPU of size of the port being accessed. Full compatibility with the reduced data buses of earlier processors in the family has been maintained by the dynamic bus sizing facility.

The MC68020 contains an instruction on-chip cache memory which improves the overall performance of the processor by reducing instruction access time. A cache disable signal ( $\overline{CDIS}$ ) is used to disable the activity of the cache memory. The cache memory can also be disabled by programming the cache control register (CACR). For debugging purposes, when the processor is forced to access the external memory to monitor the behaviour of the software and hardware under test, it is essential for the cache memory to be disabled.

The MC68020 has a similar bus operation as that described earlier for its predecessor the MC68000 microprocessor.

## 3.13 The Intel 80386

The 80386 is the full 32-bit implementation of high performance microprocessors developed by Intel.

The processor internal structure is divided into six functional units.

- i. The bus unit. Interfaces the CPU to the external system bus and controls all address, data, and control signals to and from the processor.

- ii. The prefetch unit. Responsible for fetching instructions from memory.

- iii. The decode unit. Prepares instructions for processing by the execution unit.

- iv. The execution unit. Executes the micro instructions.

- v. The segment unit. Translates logical addresses to linear addresses and performs bus cycle segmentation violation checks.

- vi. The paging unit. Translates the linear addresses generated by the segmentation or prefetch unit into physical addresses.

The internal units of advanced processors, such as the M68020 and the Intel 80386, are normally pipelined in order to enable them to operate in parallel on different instructions.

The 80386 has separate 32-bit address and data buses. Its data bus can be switched between 16 and 32 bits to allow existing 16 bit devices to communicate with the processor. The instruction set of the 80386 supports byte, word and long word transfers. Four byte enable signals (BEO-BE3) are used with the address bus to specify the data bytes that are active.

The 80386 uses only one signal, address status ( $\overline{ADS}$ ), to inform external logic of the beginning of a normal bus cycle. The processor, then, defines the type of bus cycle with the W/ $\overline{R}$ , M/ $\overline{IO}$  and D/ $\overline{C}$ signals.

The 80386 provides bus lock ( $\overline{LOCK}$ ) signal of multiprocessor applications. The lock signal informs other bus masters that the processor is performing a multiple bus cycle operation that must not be interrupted. The processor can run two kinds of bus cycles, non-pipelined and pipelined. The non-pipelined bus cycle is used when the processor is communicating with high speed memories. The pipelined bus cycle is used to give slow memory systems more time to respond to a bus cycle. Pipelining is enabled as external devices assert the next address signal ( $\overline{NA}$ ).

The 80386 uses the  $\overline{READY}$ , HOLD and HLDA signals in similar way as described for the Intel 8086.

#### 3.14 Summary

In this chapter, various microprocessor bus structures have been examined.

For some microprocessors the data and address bus organization is multiplexed. Such processors (e.g the Intel 8086) transmit instructions and addresses over a single 8 or 16 bit system bus. In all cases, multiplexing is used to reduce pin requirements of the chip package. Extra hardware interface would be required in order to communicate to such devices.

Almost all current microprocessors have provision for a direct memory access facility to allow transfers between devices and memory without processor intervention.

Some microprocessors, such as the M6800 processor ,use memory-mapped input/output. Others, as the Z80, use certain control lines to distinguish between memory and I/O operations.

The Z80 microprocessor was used by Whitworth <sup>[13]</sup>, in a similar study, as the supportive processor. The Z80 is short of many important hardware features which include the following :

- i. The Z80 address range is limited to access only 64K bytes of memory. Without implementing any form of memory management unit (MMU), the processor would be unable to access the address range of 16-bit processors. If MMU is to be implemented, the hardware interface complexity would increase further.

- ii. The Z80 data bus lacks the ability to store and manipulate different types of data. This would make it more difficult for the Z80 to communicate with 16-bit data buses. To provide this facility, the hardware interface complexity would increase even further.

- iii. The Z80 arbitration circuitry lacks the facility to connect several processors into one system.

Therefore, 8-bit processors in general are not suitable of supporting the multi-family microprocessor teaching project.

In this study, the MC68000 microprocessor is used as the supportive processor for the following reasons :

1. The MC68000 has one of the most comprehensive nonmultiplexed bus structure available to date.

- 2. Its powerful addressing capability enable it to access any target memory location.

- 3. The ability of the processor to store and manipulate different types of data enable it to support 8-bit devices on its 16-bit data bus.

- 4. The asynchronous timing of the MC68000 bus enables even the slowest target memory to communicate with the supportive processor.

- 5. The synchronous interface option provided by the MC68000 allows the MC6800 peripherals to interface with the supportive processor.

- 6. The processor bus arbitration logic enables multiple processors and DMA controllers to share the same bus.

- 7. Halt and Bus error signals are available that may used to single step the bus, abort illegal or invalid access attempts. This is vital to successfully recover in the event that interface circuits cause a deadly embrace.

- 8. A 3-bit function code signal is present that identifies the purpose and privilege level of each bus cycle.

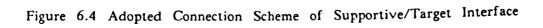

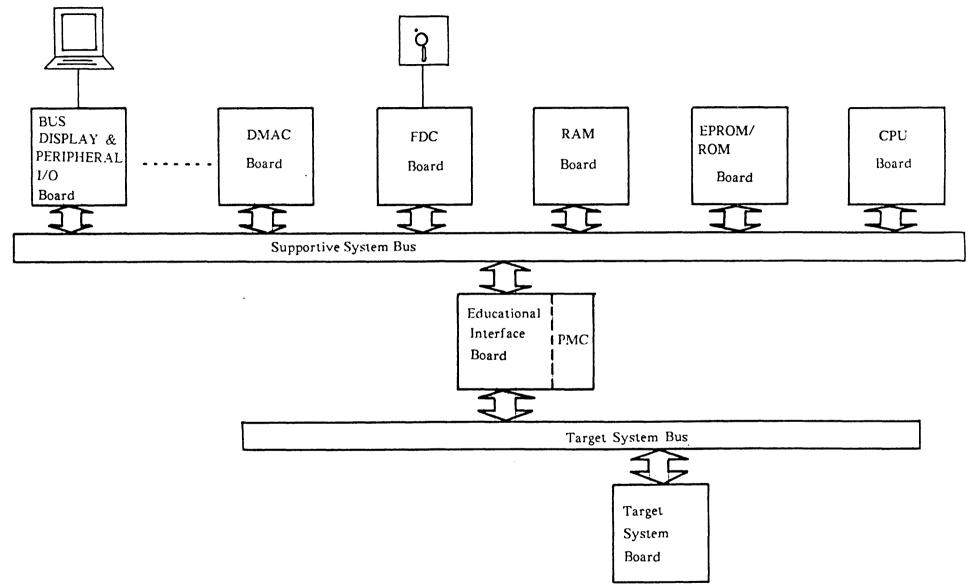

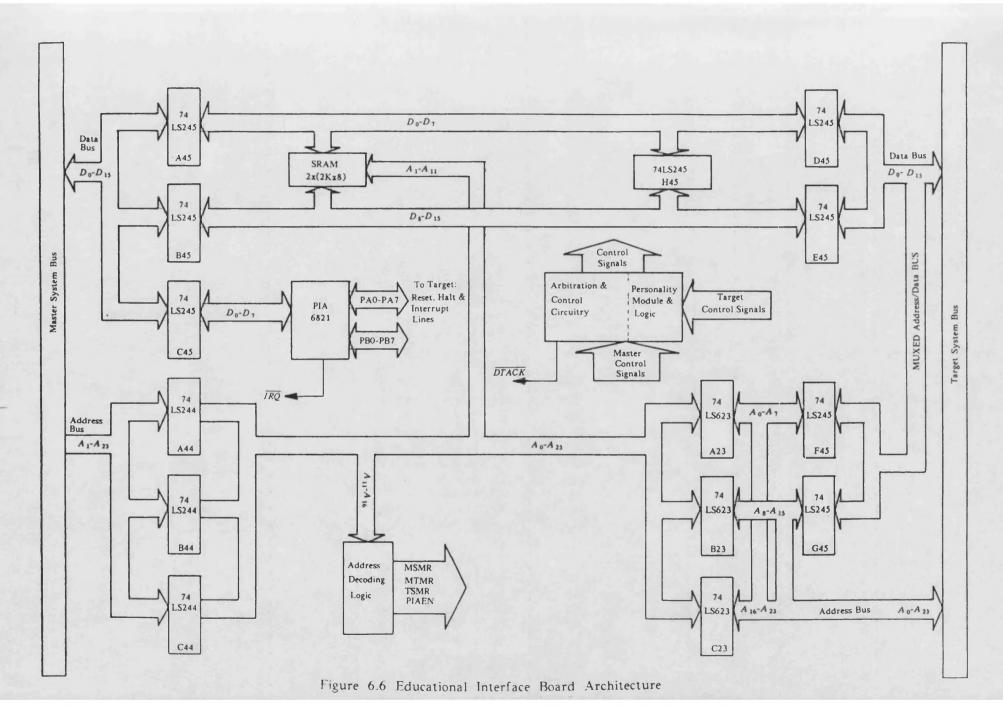

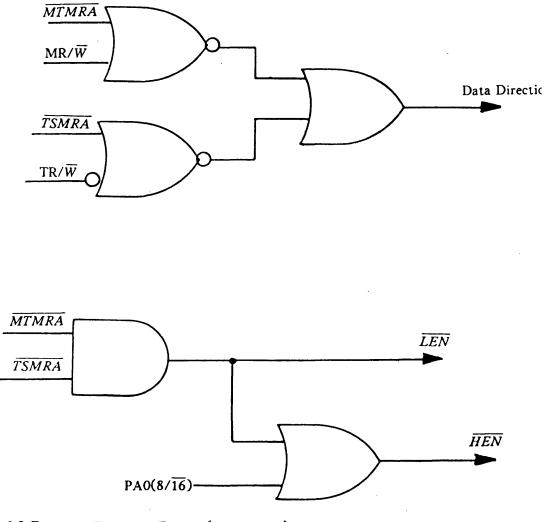

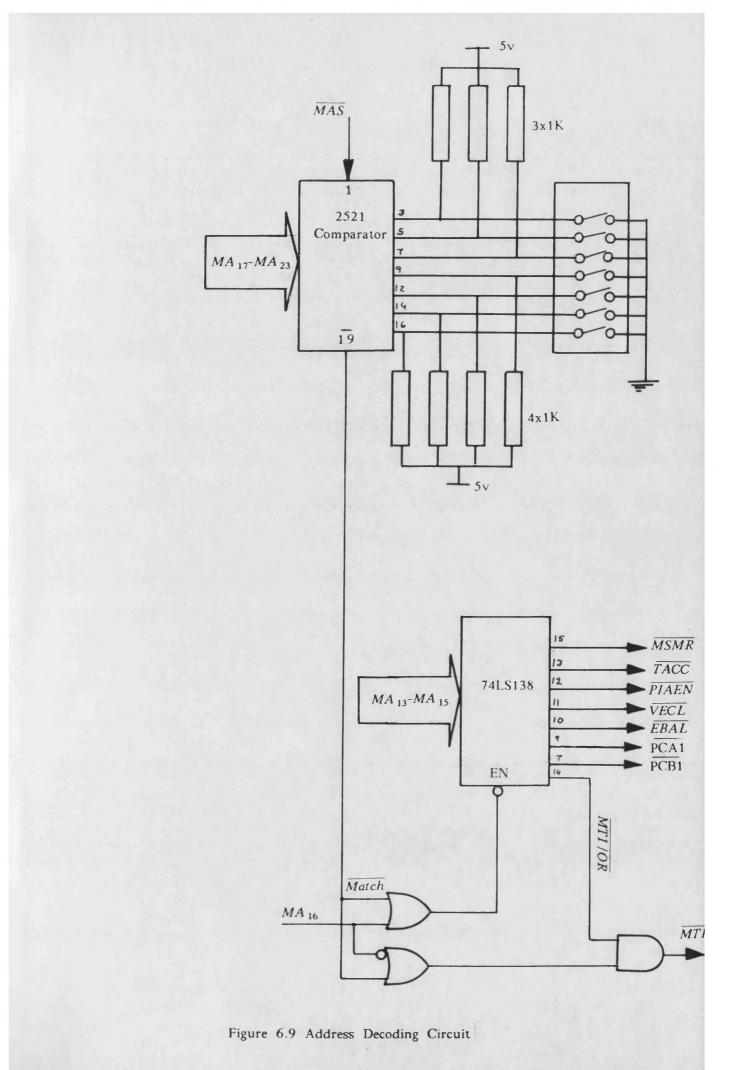

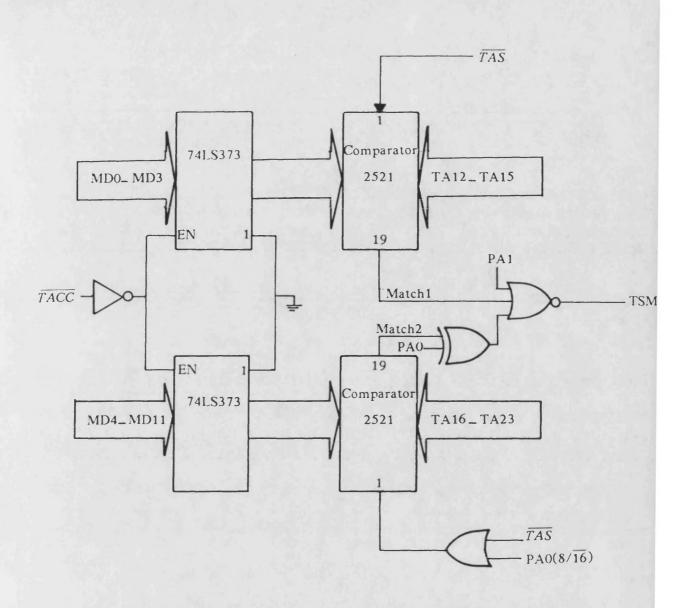

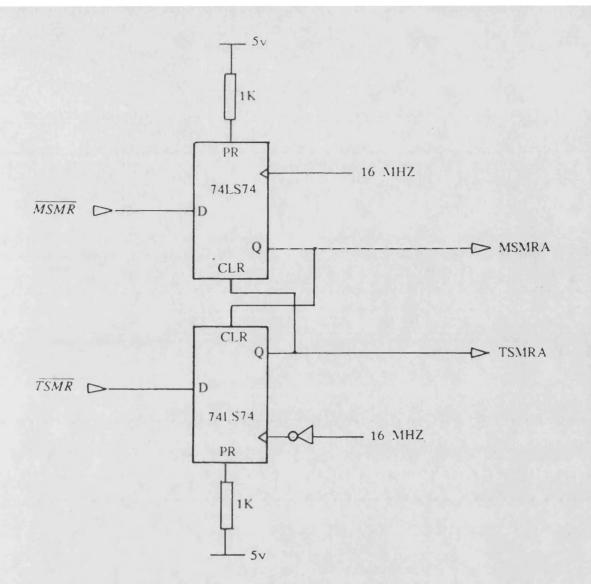

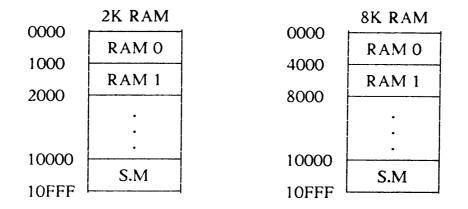

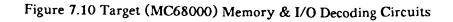

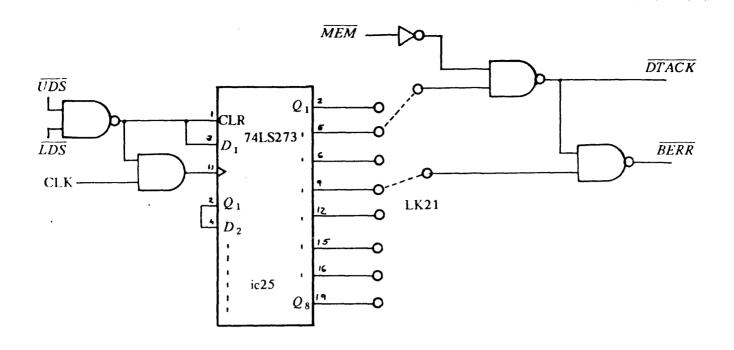

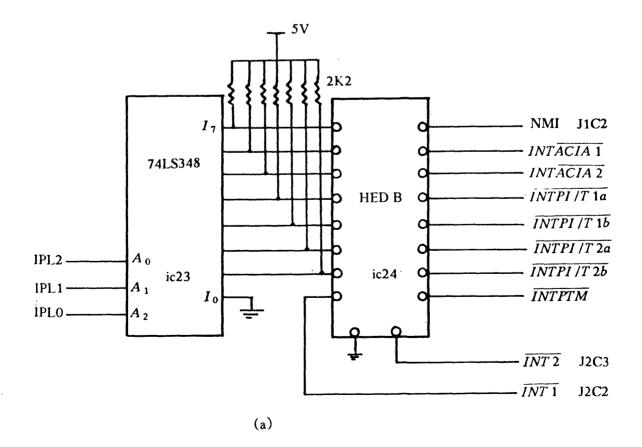

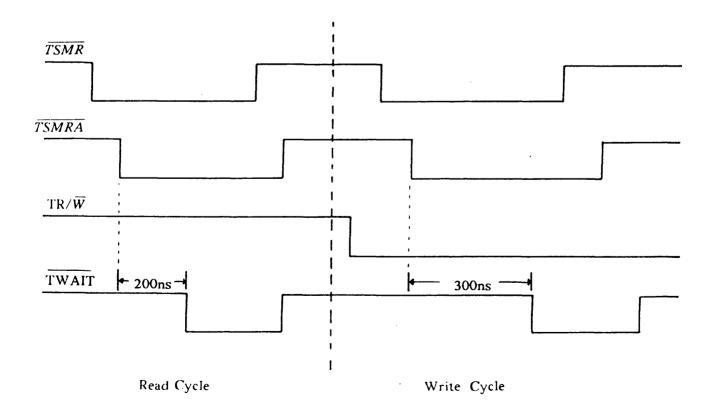

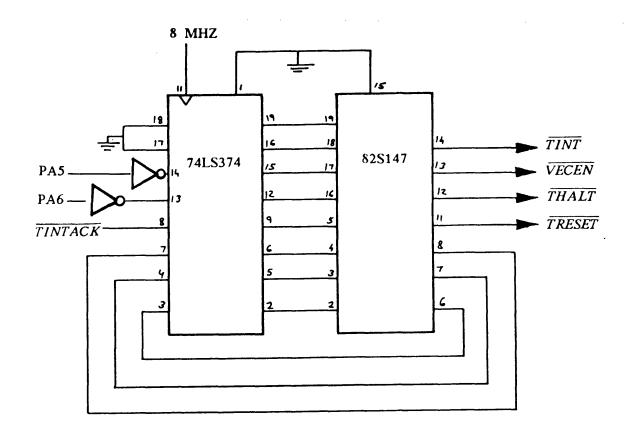

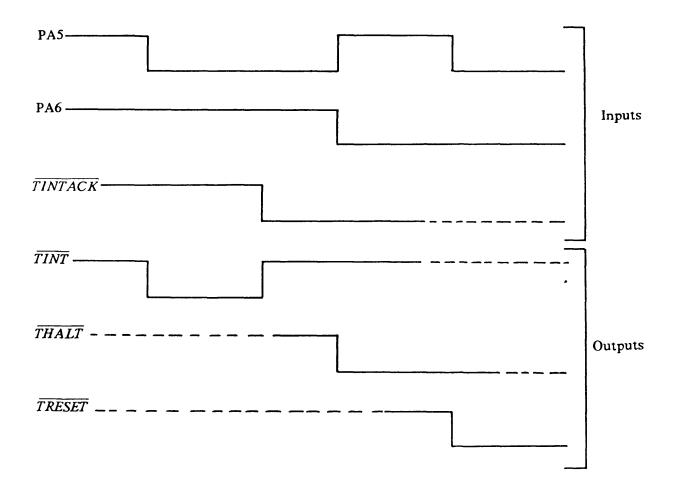

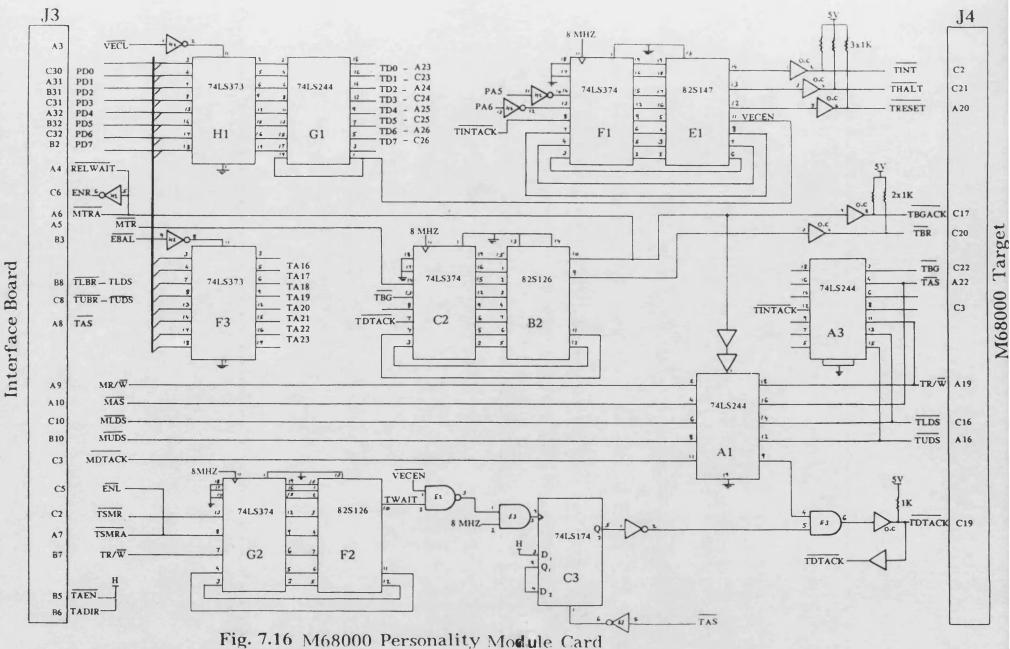

- 9. The available 3-bit encoded interrupt request input allows six prioritized, maskable interrupts and one non-maskable interrupt, with 255 vectors to transfer control to the proper interrupt handler routine.