**University of Bath**

PHD

Enhancing the performance of Decoupled Software Pipeline through Backward Slicing

Alwan, Esraa

Award date: 2014

Awarding institution: University of Bath

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Enhancing the performance of Decoupled Software Pipeline through Backward Slicing

submitted by

Esraa Hadi Obead Alwan

for the degree of Doctor of Philosophy

of the

## University of Bath

Department of Computer Science

January 2014

#### COPYRIGHT

Attention is drawn to the fact that copyright of this thesis rests with its author. This copy of the thesis has been supplied on the condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author.

Signature of Author .....

Esraa Hadi Obead Alwan

#### Abstract

The rapidly increasing number of cores available in multicore processors does not necessarily lead directly to a commensurate increase in performance: programs written in conventional languages, such as C, need careful restructuring, preferably automatically, before the benefits can be observed in improved run-times. Even then, much depends upon the intrinsic capacity of the original program for concurrent execution.

Using software techniques to parallelize the sequential application can raise the level of gain from multicore systems. Parallel programming is not an easy job for the user, who has to deal with many issues such as dependencies, synchronization, load balancing, and race conditions. For this reason the role of automatically parallelizing compilers and techniques for the extraction of several threads from single-threaded programs, without programmer intervention, is becoming more important and may help to deliver better utilization of modern hardware.

One parallelizing technique that has been shown to be an effective for the parallelization of applications that have irregular control flow and complex memory access patterns is Decoupled Software Pipeline (DSWP). This transformation partitions the loop body into a set of stages, ensuring that critical path dependencies are kept local to a stage. Each stage becomes a thread and data is passed between threads using inter-core communication. The success of DSWP depends on being able to extract the relatively fine-grain parallelism that is present in many applications.

Another technique which offers potential gains in parallelizing general purpose applications is slicing. Program slicing transforms large programs into several smaller ones that execute independently, each consisting of only statements relevant to the computation of certain, socalled, (program) points.

This dissertation explores the possibility of performance benefits arising from a secondary transformation of DSWP stages by slicing. To that end a new combination method called DSWP/Slice is presented. Our observation is that individual DSWP stages can be parallelized by slicing, leading to an improvement in performance of the longest duration DSWP stages. In particular, this approach can be applicable in cases where DOALL is not. In consequence better load balancing can be achieved between the DSWP stages.

Moreover, we introduce an automatic implementation of the combination method using Low Level Virtual Machine (LLVM) compiler framework. This combination is particularly effective when the whole long stage comprises a function body. More than one slice extracted from a function body can speed up its execution time and also increases the scalability of DSWP.

An evaluation of this technique on six programs with a range of dependence patterns leads to considerable performance gains on a core-i7 870 machine with 4-cores/8-threads. The results are obtained from an automatic implementation that shows the proposed method can give a factor of up to 1.8 speed up compared with the original sequential code.

## Acknowledgements

In the name of Allah the Beneficent, the Merciful.

First and before everything, I would like to express my great thanks to Allah for his mercy and blessing.

Undertaking this PhD has been a truly life-changing experience for me, and it would not have been possible to do without the support and guidance that I received from many people.

I heartily thank my supervisors Prof. John Fitch (University of Bath) and Dr. Julian Padget (University of Bath) for their over-seeing, guidance, commitment, patience and suggestions, providing me with invaluable comments and insights to improve my thesis and shape this research into what is has become today.

I warmly thank Prof. McCusker (University of Bath) for his valuable advice and friendly help, and his extensive discussions throughout one year of his supervision. I will forever be thankful to my dear Prof. Mohammed Hashim Matloob (Babylon University), who was a major influence in my decision to apply to Bath University.

I will forever be thankful to my colleagues Dr. Shadi Basurra, Dr. Firas Albadran and Mr. JeeHang Lee for their valuable advice and support throughout the duration of my study at Bath. A very special thank you to Mr. Max Harris for proofreading the thesis.

I am, as ever, especially indebted to my brothers and sisters, for their love, prayers and remarkable support throughout my whole life. My biggest regret in my life is that my beloved parents did not live to see me complete my PhD. No amount of words could fully convey my gratitude to them.

I'm also grateful to my dear friends Asieh, Fatemeh and Ta (Pawitra) for their encouragement and understanding during my life in academia.

Finally, I gratefully acknowledge the funding received towards my PhD from the Ministry of Higher Education and Scientific Research (MoHESR) in Iraq.

## Contents

| 1        | Intr | oduction                                   | 1          |

|----------|------|--------------------------------------------|------------|

|          | 1.1  | Problem Description                        | 5          |

|          | 1.2  | Outline                                    | 7          |

| <b>2</b> | Bac  | kground                                    | 8          |

|          | 2.1  | Definition and Terminology                 | 8          |

|          |      | 2.1.1 BasicBlock                           | 8          |

|          |      | 2.1.2 Directed Graph                       | 8          |

|          |      | 2.1.3 Control Flow Graph (CFG)             | 9          |

|          |      | 2.1.4 Strongly Connected Component (SCC) 1 | 0          |

|          |      | 2.1.5 Directed Acyclic Graph (DAG)         | 0          |

|          | 2.2  | Program Dependency Graph (PDG) 1           | 1          |

|          |      | 2.2.1 Data Dependency Graph                | 2          |

|          |      | 2.2.2 Control Dependency Graph(CDG)        | 4          |

|          | 2.3  | Static Single Assignment                   | 4          |

|          | 2.4  | LLVM                                       | 6          |

|          | 2.5  | LLVM System Architecture                   | 7          |

|          |      | 2.5.1 Front-End                            | 7          |

|          |      | 2.5.2 Optimization and the Pass system     | 21         |

|          |      | 2.5.3 Back-end                             | 24         |

|          |      | 2.5.4 Analysis Passes                      | 25         |

|          | 2.6  | Some of the LLVM Classes and Pass          | 26         |

|          | 2.7  | Summary 2                                  | 29         |

| 3        | Par  | allelizing Techniques 3                    | 80         |

|          | 3.1  | Slicing                                    | <b>B</b> 0 |

|          |      | 3.1.1 Types of Slices                      | 32         |

|          |      | 3.1.2 Static and Dynamic Slice             | 33         |

|          |      | 3.1.3 Slicing Control Flow Graph           | 35         |

|          |      | 3.1.4 Slicing with the PDG                 | 88         |

|          |      | 3.1.5 Intraprocedure Slice                 | 10         |

|          |      | 3.1.6   | Interprocedural slice                                                                                                                          | 41  |

|----------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          |      | 3.1.7   | Interprocedural slicing in the presence of aliasing $\ldots \ldots \ldots \ldots$                                                              | 43  |

|          |      | 3.1.8   | Parallel execution of a slice                                                                                                                  | 44  |

|          |      | 3.1.9   | Application of Program Slicing                                                                                                                 | 46  |

|          | 3.2  | Extrac  | ting parallelism                                                                                                                               | 48  |

|          |      | 3.2.1   | Instruction level Parallelism (ILP)                                                                                                            | 48  |

|          |      | 3.2.2   | Fine-grain Thread Level Parallelism (TLP)                                                                                                      | 48  |

|          |      | 3.2.3   | Loop level parallelism (LLP) $\ldots$                                                                                                          | 49  |

|          |      | 3.2.4   | Usage of DSWP                                                                                                                                  | 55  |

|          | 3.3  | Summ    | ary                                                                                                                                            | 66  |

| 4        | Imp  | olemen  | tation of DSWP and Slicing Techniques                                                                                                          | 67  |

|          | 4.1  | Motiva  | ation                                                                                                                                          | 67  |

|          | 4.2  | DSWF    | $P/Slice \text{ combination technique } \dots \dots$ | 70  |

|          |      | 4.2.1   | Determining a Thread Assignment                                                                                                                | 70  |

|          |      | 4.2.2   | Extracting Slices                                                                                                                              | 75  |

|          |      | 4.2.3   | Code Generation                                                                                                                                | 77  |

|          | 4.3  | Comp    | iler implementation                                                                                                                            | 87  |

|          | 4.4  | Summ    | ary                                                                                                                                            | 87  |

| <b>5</b> | Eva  | luation | n of DSWP/Slicing Transformation                                                                                                               | 89  |

|          | 5.1  | Comm    | nunication Overhead                                                                                                                            | 90  |

|          | 5.2  | DSWF    | P/Slice                                                                                                                                        | 91  |

|          |      | 5.2.1   | simple4.c program                                                                                                                              | 95  |

|          |      | 5.2.2   | linkedlist.c program                                                                                                                           | 96  |

|          |      | 5.2.3   | fft.c program                                                                                                                                  | 100 |

|          |      | 5.2.4   | pro-2.4.c program                                                                                                                              | 101 |

|          |      | 5.2.5   | test0697.c program                                                                                                                             | 102 |

|          | 5.3  | Buffer  | size and Slice length                                                                                                                          | 103 |

|          | 5.4  | Discus  | sion                                                                                                                                           | 105 |

|          |      | 5.4.1   | comparing result                                                                                                                               | 105 |

|          |      | 5.4.2   | Inlining effect                                                                                                                                | 107 |

|          | 5.5  | Summ    | ary                                                                                                                                            | 107 |

| 6        | Cor  | clusio  | n and Future Directions                                                                                                                        | 110 |

|          | 6.1  | Future  | e Directions                                                                                                                                   | 111 |

| Α        | Pro  | grams   |                                                                                                                                                | 123 |

| В        | Inst | ructio  | ns Latency                                                                                                                                     | 137 |

|          |      |         |                                                                                                                                                |     |

# List of Figures

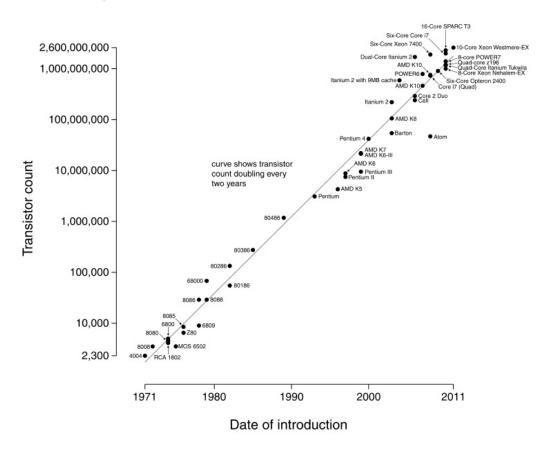

| 1-1    | Number of transistors integrated per die for Intel x86 processors. Adapted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|        | from (Wikipedia, 2011), updating Intel (Intel-Corporation, 2002)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

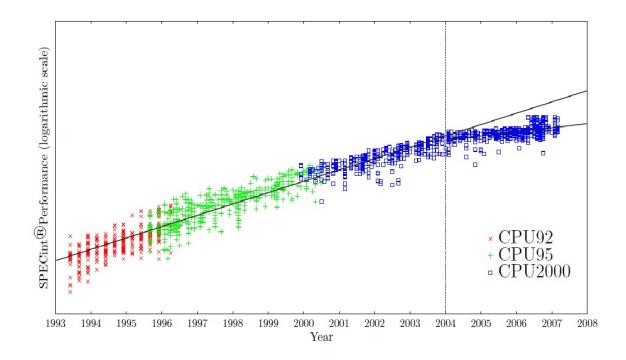

| 1-2    | Normalized SPEC scores for all reported configurations between 1993 and 2007.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|        | Adapted from (SPEC, 2013)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3  |

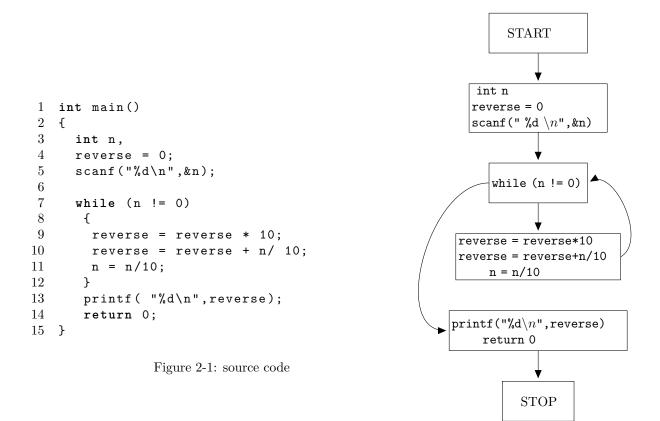

| 2-1    | source code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 |

| 2-2    | CFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 |

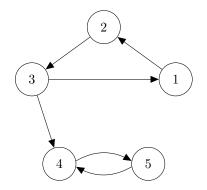

| 2-3    | Strong Connected Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11 |

| 2-4    | Direct Acyclic Graph for Strong Connected Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 |

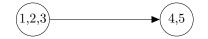

| 2-5    | Code Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13 |

| 2-6    | Data Dependency Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13 |

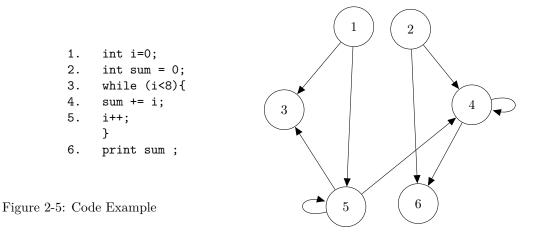

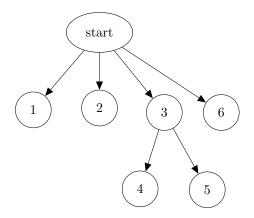

| 2-7    | Control Dependency Graph for the program in figure 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

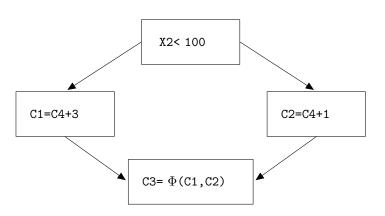

| 2-8    | (a) Original code fragment. (b)SSA form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15 |

| 2-9    | (a) Original code fragment. (b) Final SSA form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16 |

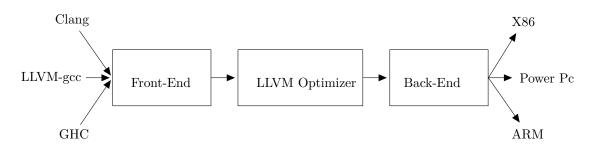

| 2-10   | LLVM's Implementation of the Three-Phase Design (Brown and Wilson, 2008)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

| 2-11   | C source code. Adapted from (Brown and Wilson, 2008)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19 |

| 2 - 12 | Intermediate Representation. Adapted from (Brown and Wilson, 2008) $\hfill \hfill \hf$ | 19 |

| 2 - 13 | Examples of LLVM types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19 |

| 2 - 14 | LLVM types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20 |

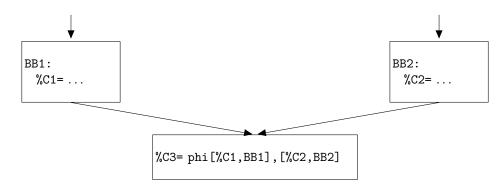

| 2 - 15 | Static Single Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20 |

| 2 - 16 | LLVM representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |

| 2 - 17 | arithmetic identities and their intermediate representation in LLVM $~\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

| 2 - 18 | Pattern matching Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22 |

| 2 - 19 | SimplifyInstruction used to apply transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23 |

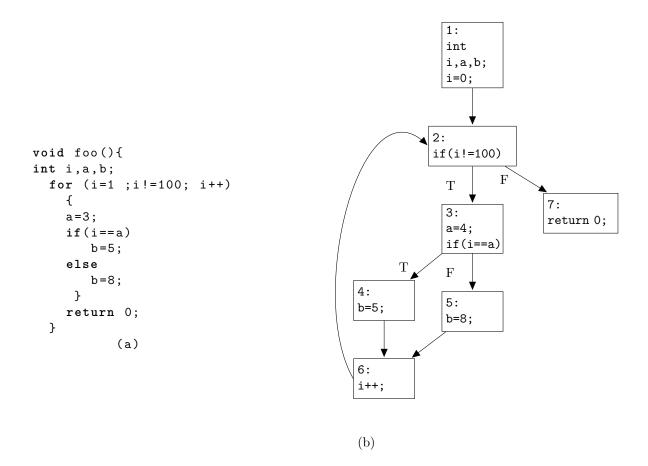

| 2-20   | (a) Piece of code. (b) Control flow graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25 |

| 2-21   | Memory dependency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28 |

| 2-22   | Register dependency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |

| 3-1    | (a) An example program. (b) A slice based on slicing criterion $<16, \{lines\}>.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|        | Adapted from (Silva, 2012)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

| 3-2    | Figure 1 :(a) Backward slicing . (b) Forward slicing. Adapted from (Zilles and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

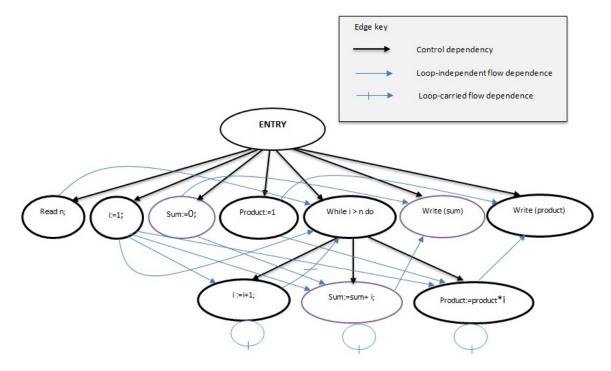

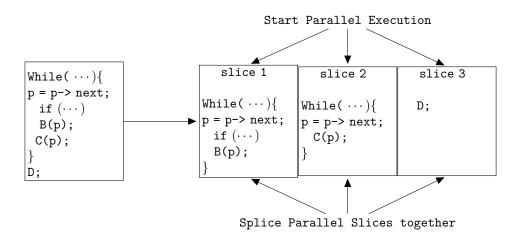

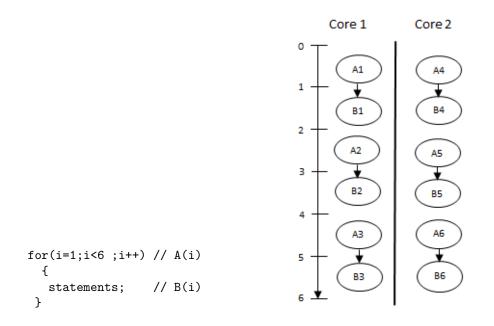

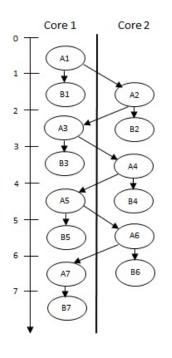

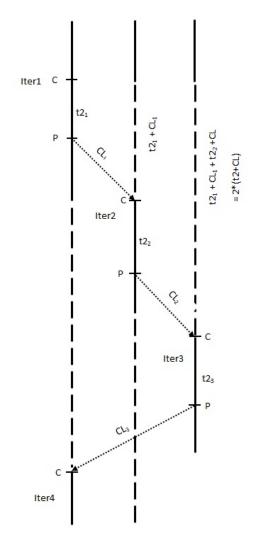

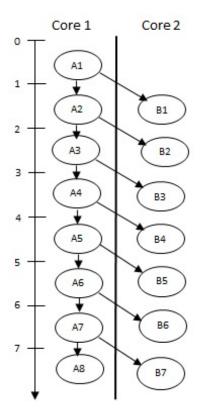

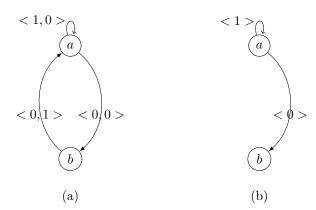

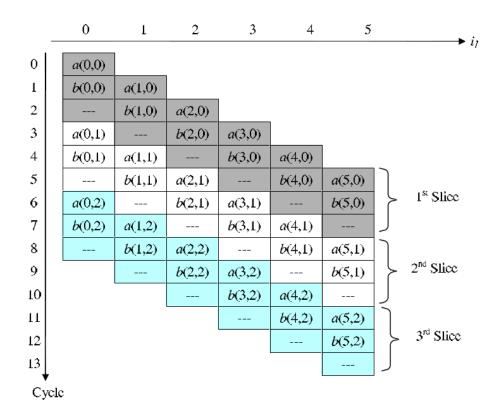

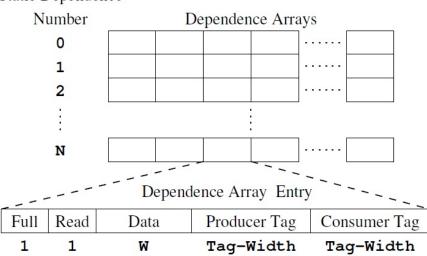

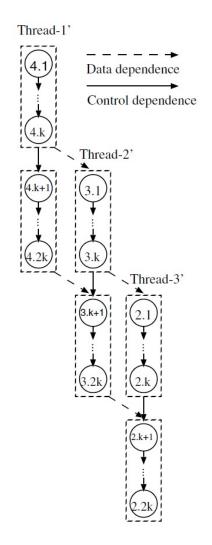

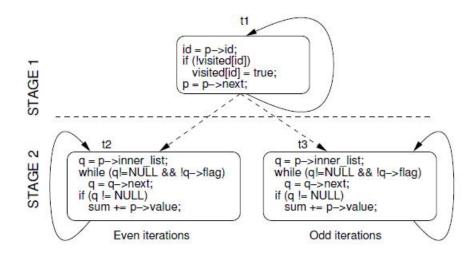

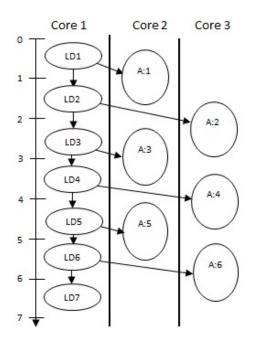

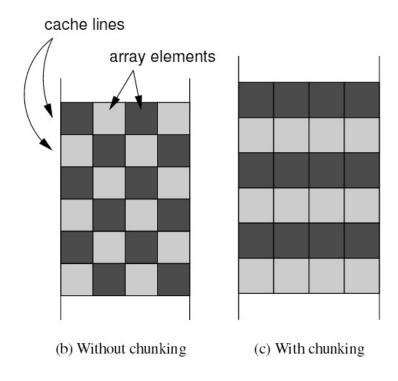

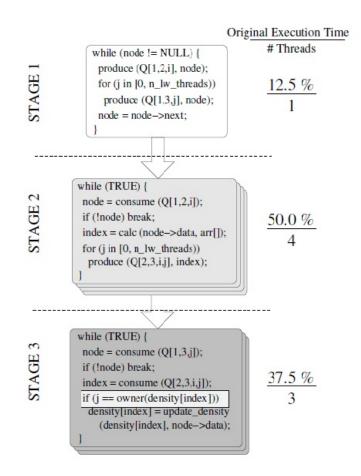

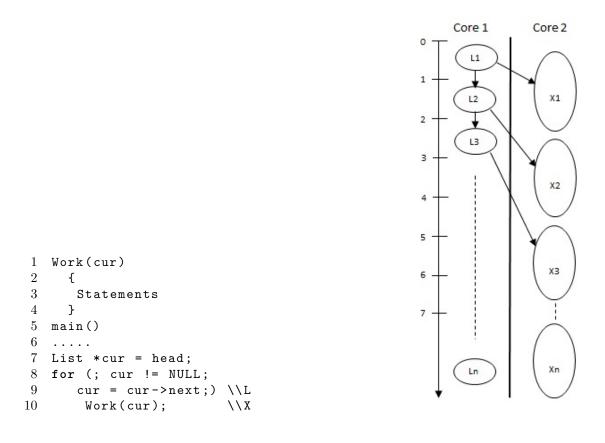

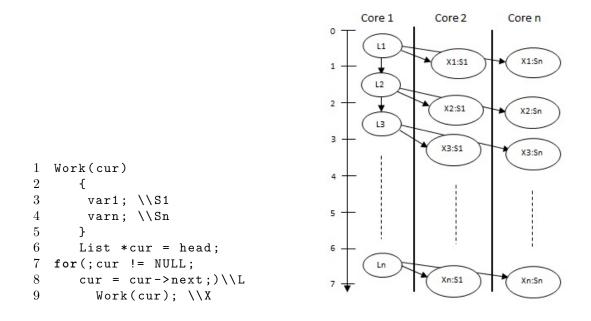

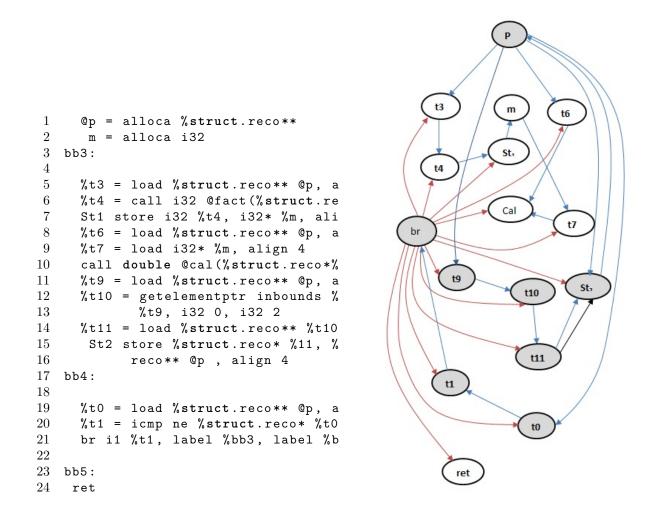

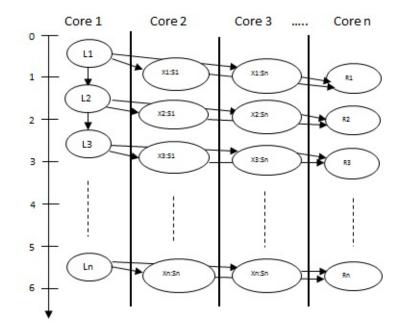

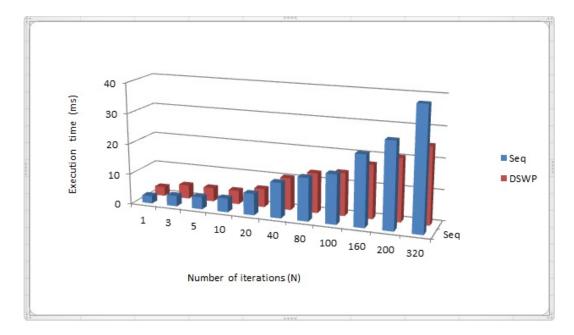

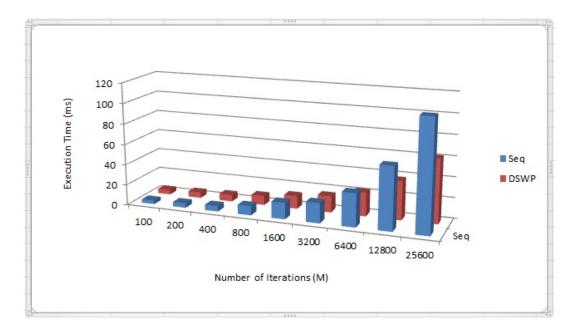

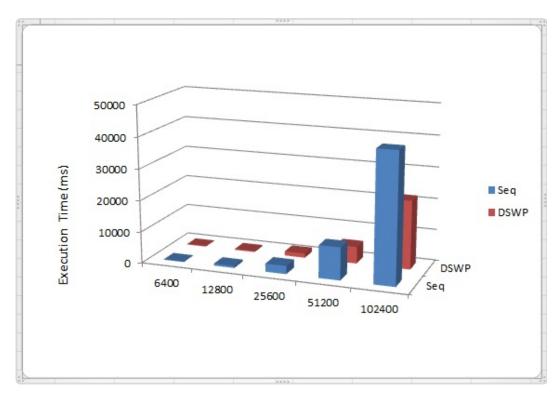

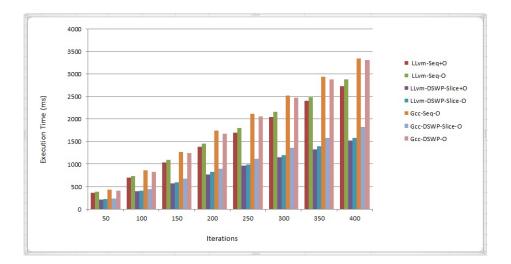

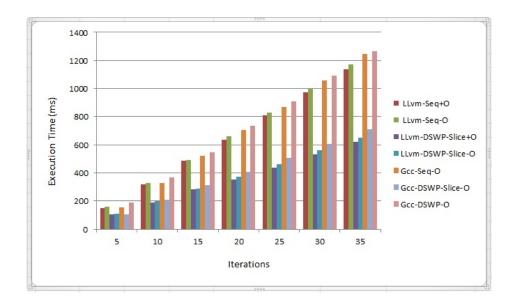

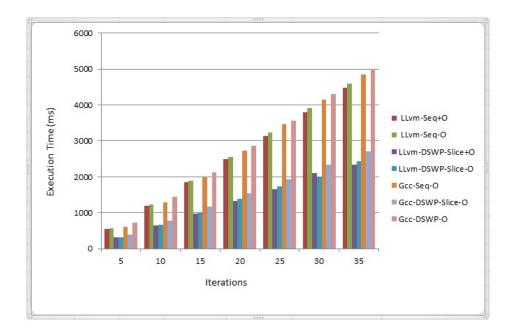

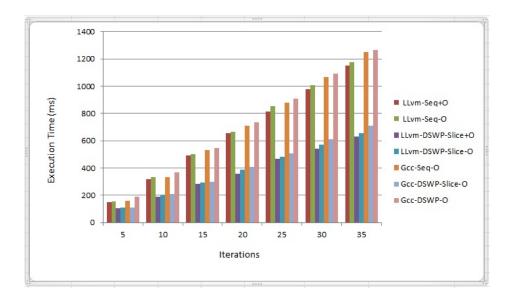

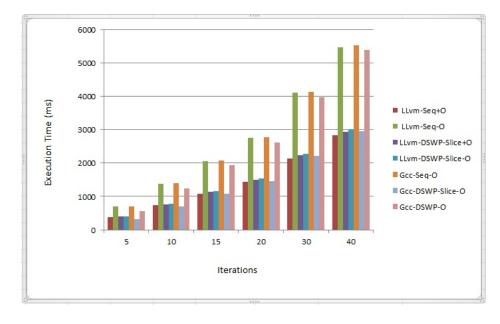

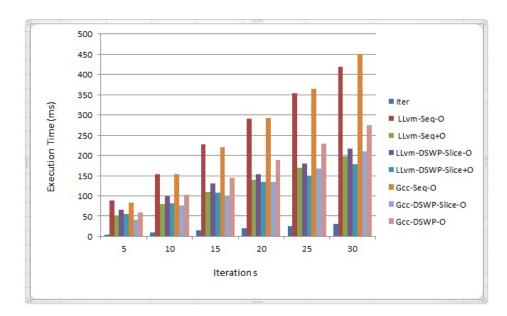

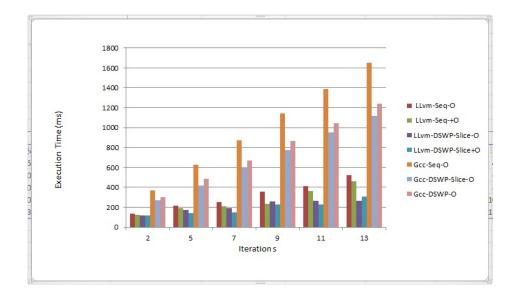

|        | Sohi, 2000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |