**University of Bath**

### PHD

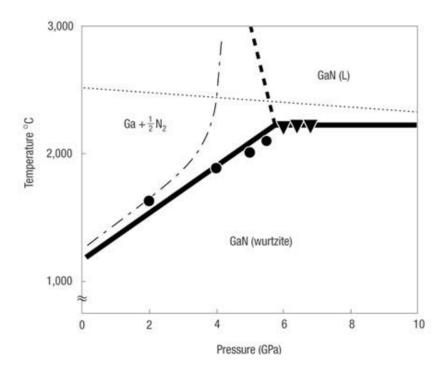

# Modelling, fabrication and development of GaN-based sensors and substrates for high strain environments

Edwards, Michael

Award date: 2012

*Awarding institution:* University of Bath

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Modelling, fabrication and development of GaN-based sensors and substrates for high strain environments

# Submitted by Michael John Edwards

# For the degree of PhD At the University of Bath Department of Mechanical Engineering 2012

# COPYRIGHT

Attention is drawn to the fact that copyright of this thesis rests with the author. A copy of this thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with the author and that they must not copy it or use material from it except as permitted by law or with the consent of the author.

Candidates wishing to include copyright material belonging to others in their theses are advised to check with the copyright owner that they will give consent to the inclusion of any of their material in the thesis. If the material is to be copied other than by photocopying or facsimile then the request should be put to the publisher or the author in accordance with the copyright declaration in the volume concerned. If, however, a facsimile or photocopy will be included, then it is appropriate to write to the publisher alone for consent.

This thesis may not be consulted, photocopied or lent to other libraries without the permission of the author and former members of the MORGaN (Materials for robust Gallium Nitride) consortium for a period of 2 years from the date of acceptance of this thesis.

## Acknowledgements

The research leading to these results has received funding from the European Community's Seventh Framework Programme FP7/2007-2011 under grant agreement n°214610, project MORGaN. This publication reflects only the author's views and that the Community is not liable for any use that may be made of the information contained therein. I would also like to thank colleagues at the University of Bath for making their facilities available for me to conduct my research.

I would like to acknowledge my academic supervisors, Prof. Chris Bowen and Dr. Duncan Allsopp, for their guidance, valued feedback, useful discussions and offering encouragement when required. I would also like to thank, Dr Andrew Dent for supporting me in the early stages of my PhD, teaching me how to use ANSYS finite element software and for listening at the end.

I would like acknowledge the help of Dr Quanzhong Jiang and Dr Chaowang Liu, for growing the GaN material used in this project, and Dr Emmanuel Le Boulbar, for working on the drumskin sensor with me and being good company. I would also like to offer special thanks to Dr Philip Shields and Dr Siva Sivaraya, for their help in the nanofabrication centre and assisting me with the fabrication of the ELOG templates. I would also like to thank Marie-Laure Hicks and the staff at IMCE for their help in the mechanical testing of GaN.

I would like to offer special thanks to colleagues in the MORGaN consortium for their inputs in my research and being great collaborative researchers. I would like to particularly thank Dr Tim Mollart of Element Six, Dr Gabriel Vanko of the Slovak Academy of Sciences, Dr Libor Rufer and Stephane Vittoz of TIMA laboratory in Grenoble, Dr Klas Brinkfeldt and Dr Per Johander of Swerea IVF, Mölndal, Michal Borysiewicz of ITE, Warsaw, and Prof Jaroslav Kovac, Prof Alexander Satka, Prof Daniel Donoval and Dr Rudolf Srnanek of the Slovak University of Technology for their valuable inputs in this thesis.

Finally and above all, I would like to thank friends and family for support. I would like to thank my parents and my brother Fred, for being on the end of the phone giving me the encouragement needed to complete this thesis. Fellow postgraduate researcher and friend, Rhodri Lewis thanks for keeping me in good spirits.

### ABSTRACT

GaN is a monocrystalline material that can be grown using metallo-organic chemical vapour deposition (MOCVD), and has desirable mechanical and semiconducting properties for operating as a sensor. It has a Young's modulus of 250 to 350 GPa, which shows little decrease with respect to temperature beyond 400°C. GaN also exhibits piezoelectric and piezoresistive effects, meaning that it will generate a charge and its electrical resistance will change when the material is strained respectively. In this PhD, GaN has been used as the base material for pressure sensors that potentially can be used in excess of 400°C and at a pressure in excess of 50 bar (5 MPa), with potential applications in aerospace and oil exploration. The pressure sensor is a circular diaphragm created from a GaN/sapphire wafer, and was designed and tested in order to determine if GaN can act as a sensing material in these environments.

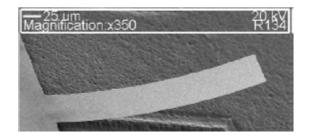

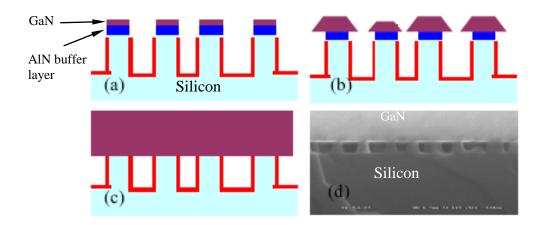

In addition to the diaphragm sensor, GaN templates that can potentially be used for sensors were grown using an epitaxial layer overgrowth (ELOG) method. These sensors are potentially more mechanically robust than similar templates etched out of GaN/sapphire wafers because they will have less inbuilt strain due to lower dislocation densities. It was possible to release beams and cantilevers from GaN ELOG templates. Mechanical probe tests were undertaken on these devices to see if they were fully released and robust.

GaN single crystal growth requires a substrate material, such as (111) silicon or (0001) sapphire, meaning that the thermal properties of the substrate are important for a device operating in excess of 400°C. GaN high electron mobility transistors are heat sensitive, experiencing a decrease in current between the drain and source terminals as the temperature increases. Therefore a GaN-based sensor needs a substrate with the highest possible thermal conductivity to act as a heat sink, which means removing as much heat as possible from the GaN sensor. Diamond has superior thermal conductivity to both sapphire and silicon, so a novel silicon/polycrystalline diamond composite substrate has been developed as a potential GaN substrate. Polycrystalline diamond (PD) can be grown on 4 inch diameter wafers using hot filament chemical vapour deposition (CVD), on (111) silicon (Si) from which single crystal GaN epitaxy can also be grown.

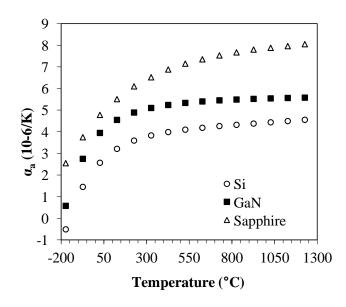

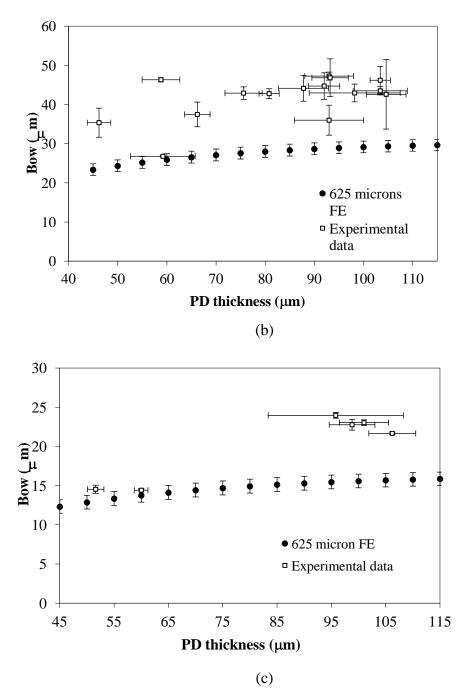

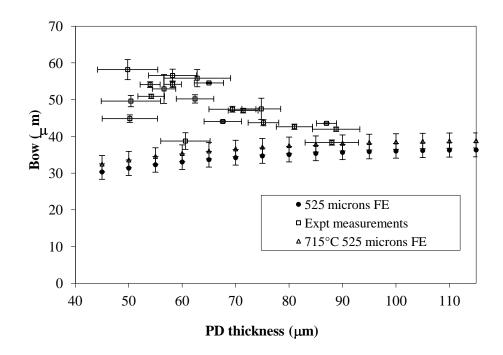

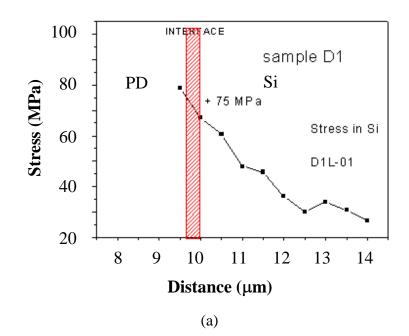

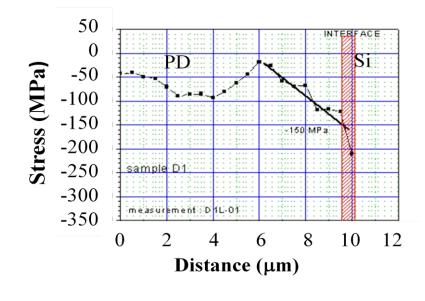

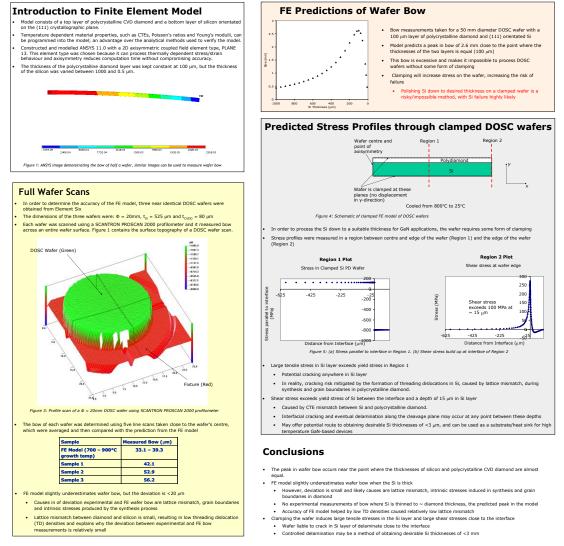

In order for the (111) Si/PD composite substrates to be useful heat sinks, the Si layer needs to be less than 2  $\mu$ m. PD was initially grown on 525 to 625  $\mu$ m thick Si wafers that required thinning to 2  $\mu$ m. Achieving this Si layer thickness is difficult due to the presence of tensile stress in the Si caused by a mismatch in the coefficients of thermal expansion (CTEs) between Si and PD. This stress causes the wafer to bow significantly and has been modelled using ANSYS FE software. The models show that the bow of the wafer increases when it is thinned, which will eventually cause the Si layer to delaminate at the Si/PD interface due to poor adhesion and a build up for shear stress. When the Si layer is mechanically thinned, the Si layer can crack due to clamping. The experimental wafer bow and micro-Raman measurements validate the model for when the silicon layer is thicker than 100  $\mu$ m and these results show that an alternative processing route is required.

# **Contents**

| NOMENCLATURE.                                                          | 11         |

|------------------------------------------------------------------------|------------|

| LIST OF DEFINITIONS.                                                   | 14         |

| CHAPTER 1: MOTIVATION AND LITERATURE REVIEW                            | 17         |

| 1.1 Introduction and Motivation                                        | 17         |

| 1.1.1 Introduction                                                     | 17         |

| 1.1.2 Motivation                                                       | 18         |

| 1.1.2 Thesis Structure                                                 | 20         |

| 1.2 Applications of GaN                                                | 22         |

| 1.3 Introduction to Piezoelectricity and Piezoresistivity              | 24         |

| 1.3.1 Piezoelectricity                                                 | 24         |

| 1.3.2 Piezoresistivity                                                 | 26         |

| 1.3.3 Piezoelectric and piezoresistive measurements in the literature. | 27         |

| 1.4 GaN HEMTs                                                          | 31         |

| 1.4.1 HEMT Terminology                                                 | 31         |

| 1.4.2 GaN HEMTs in the literature                                      | 34         |

| 1.5 GaN-based cantilever devices                                       | 38         |

| 1.5.1 Extrinsic stress due to CTE mismatch                             | 40         |

| 1.5.2 Intrinsic stress due to lattice mismatch                         | 41         |

| 1.5.3 Reducing internal stress                                         | 41         |

| 1.6 Properties of GaN and Substrate Materials (Polycrystalline Diamon  | d, Silicon |

| and Sapphire)                                                          | 44         |

| 1.6.1 Elastic matrices and their variants                              | 44         |

| 1.6.2. GaN materials data                                              | 50         |

| 1.6.2.1 Elastic coefficients                                           | 50         |

| 1.6.2.2 Coefficients of thermal expansion (CTEs)                                | 53        |

|---------------------------------------------------------------------------------|-----------|

| 1.6.2.3 Piezoelectric coefficients of GaN                                       | 55        |

| 1.6.3 Thermo-mechanical properties of (111) silicon                             | 59        |

| 1.6.4 Thermo-mechanical properties of polycrystalline CVD diamond               | 63        |

| 1.6.5 Thermo-mechanical properties of sapphire                                  | 65        |

| 1.6.6 Thermal Conductivity of Materials used in the PhD                         | 68        |

| 1.7 Aims of the PhD                                                             | 69        |

| CHAPTER 2: EXPERIMENTAL METHODS                                                 | 71        |

| 2.1 Introduction                                                                | 71        |

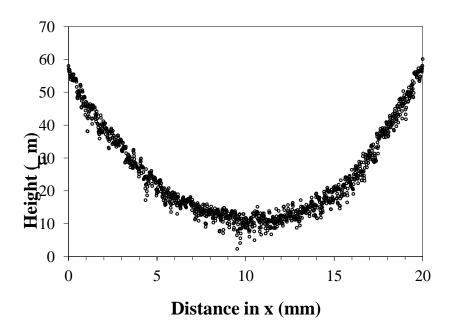

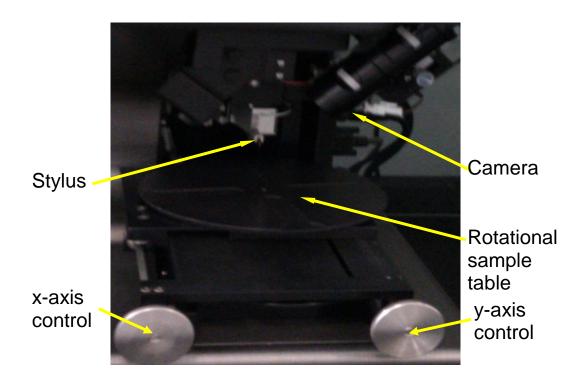

| 2.2 Experimental measurements of wafer bow                                      | 72        |

| 2.2.1 Experimental method and initial results for the Proscan 2000 profilometer | 73        |

| 2.2.2 Scanning samples with the Veeco Dektak 4.1 to determine the height of     |           |

| MEMS devices and wafer curvature                                                | 74        |

| 2.3 Modulus measurements of semiconducting materials                            | 75        |

| 2.3.1 Dynamic mechanical thermal analysis of semiconductor wafers               | 75        |

| 2.3.2 Impulse excitation                                                        | 78        |

| 2.4 Analysis Methods                                                            | 79        |

| 2.4.1 Micro-Raman                                                               | <b>79</b> |

| 2.4.2 Basic concepts of micro-Raman spectroscopy                                | 80        |

| 2.4.3 Scanning Electron Microscopy (SEM)                                        | 82        |

| 2.5 Nanofabrication methods                                                     | 83        |

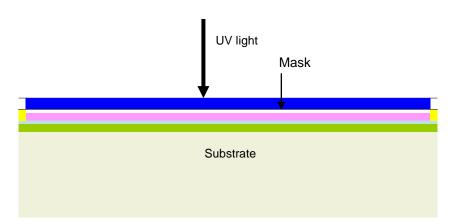

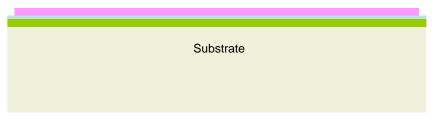

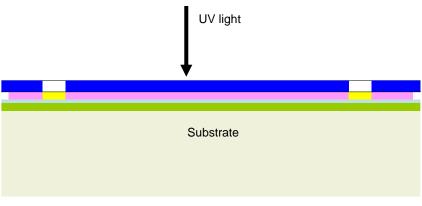

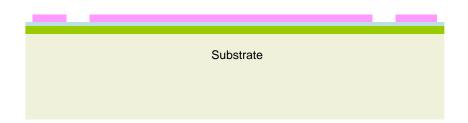

| 2.5.1 Photolithography                                                          | 84        |

| 2.5.2 Design of masks                                                           | 85        |

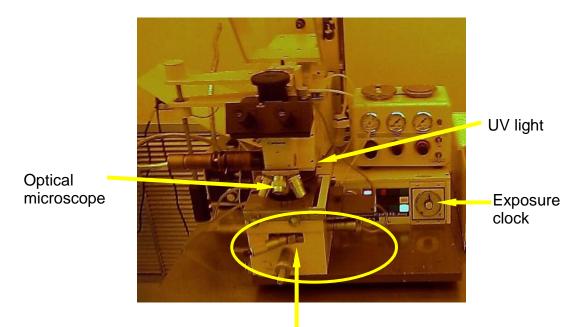

| 2.5.3 Mask aligner                                                              | 86        |

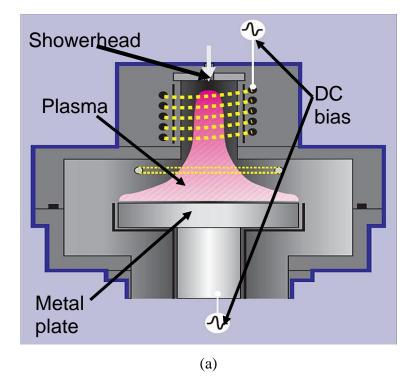

| 2.5.4 ICP etching                                                               | 88        |

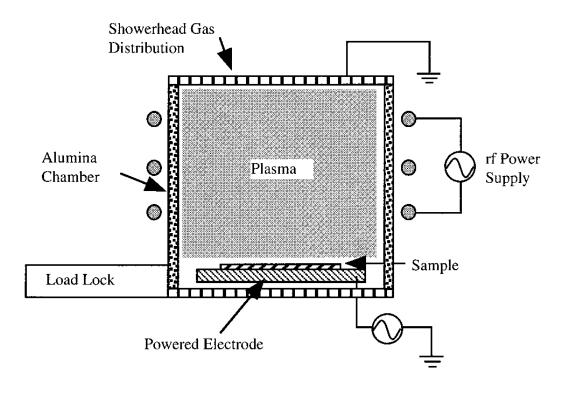

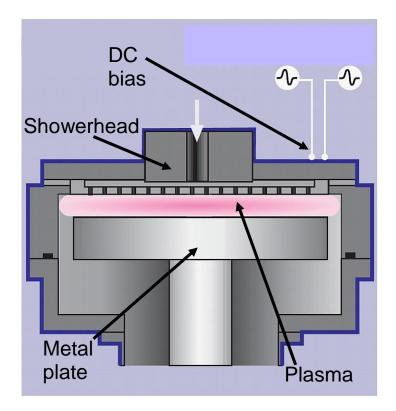

| 2.5.5 Plasma-enhanced chemical vapour deposition (PECVD)                        | 90        |

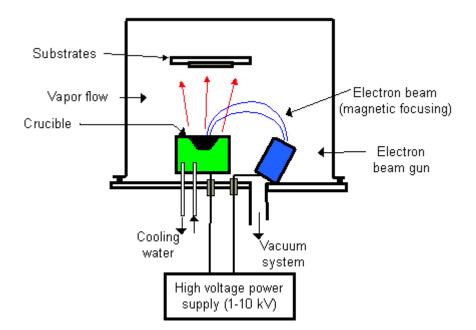

| 2.5.6 E-beam evaporation                                                        | 92        |

| 2.6 Finite element (FE) analysis                                                | 93        |

| 2.6.1 Piezoelectric constitutive relation                                       | <b>95</b> |

| <b>CHAPTER 3: OVERCOMING ISSUES RELATED TO THE DEVELOPM</b>          | MENT      |

|----------------------------------------------------------------------|-----------|

| OF A SILICON/POLYCRYSTALLINE CVD DIAMOND SUBSTRATE                   | 96        |

| 3.1 Motivation                                                       | 96        |

| 3.2 Aims of this chapter                                             | 98        |

| 3.3 Analytical Model and Comparison with FE                          | 99        |

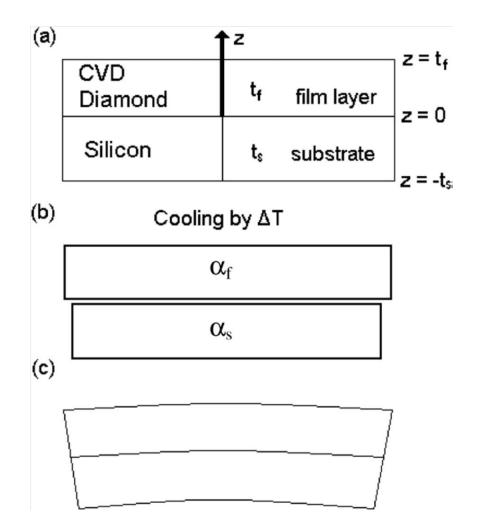

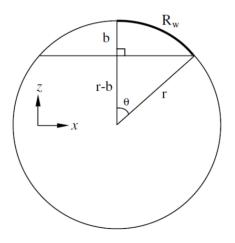

| 3.3.1 Analytical model                                               | <i>99</i> |

| 3.4 The Finite Element (FE) Model                                    | 103       |

| 3.4.1 Comparison between FE model and Analytical Method              | 105       |

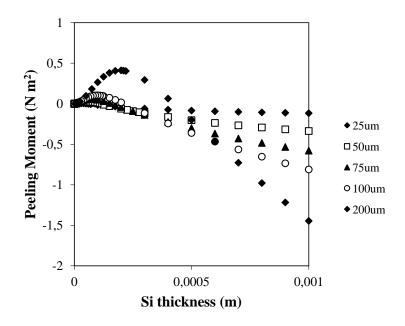

| 3.5 Prediction of wafer failure through interfacial peeling          | 109       |

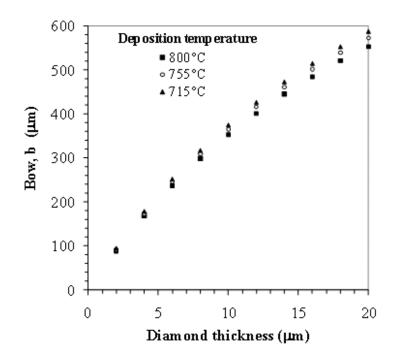

| 3.6 Comparison of FE Model with Experimental Data                    | 111       |

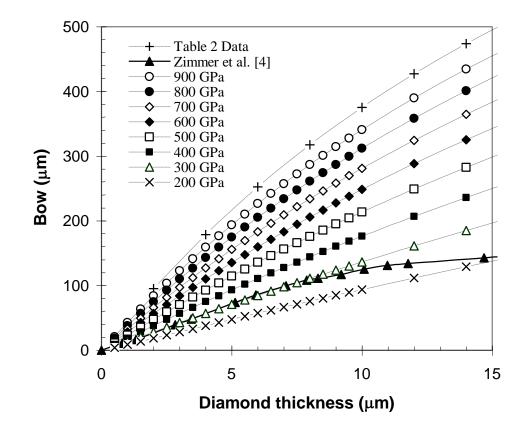

| 3.6.1 Comparison with the Literature                                 | 111       |

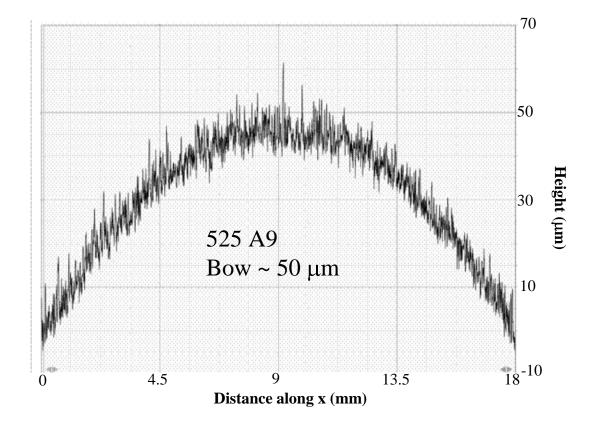

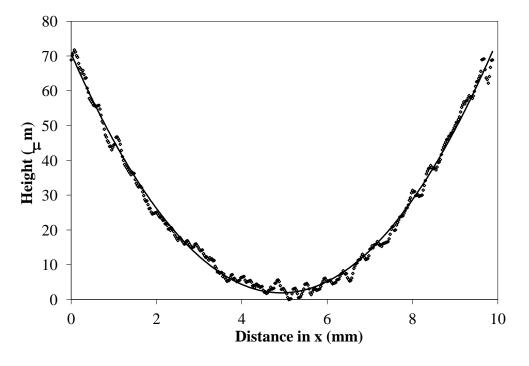

| 3.6.2 Experimental Measurements of Wafer Bow at Room Temperature     | 114       |

| 3.7 Micro-Raman measurements of Si/PD wafers                         | 122       |

| 3.8 FE and experimental measurements of wafer bow above room tempera | iture     |

|                                                                      | 126       |

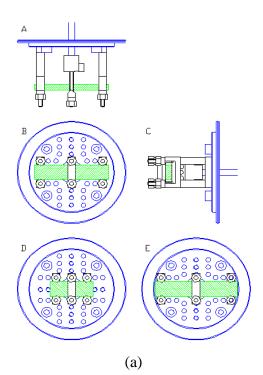

| 3.8.1 High Temperature Measurement System                            | 126       |

| 3.8.2 Results of the high temperature wafer bow measurements.        | 127       |

| 3.9 Concluding Remarks                                               | 129       |

| CHAPTER 4: CREATION OF SI/PD WAFERS SUITABLE FOR GAN                 |           |

| GROWTH AND DEVELOPMENT OF A SILICON ON INSULATOR (SO                 | OI)       |

| APPROACH FOR OVERCOMING DELAMINATION AND SI CRACKI                   | NG        |

|                                                                      | 131       |

| 4.1 Introduction and Motivation                                      | 131       |

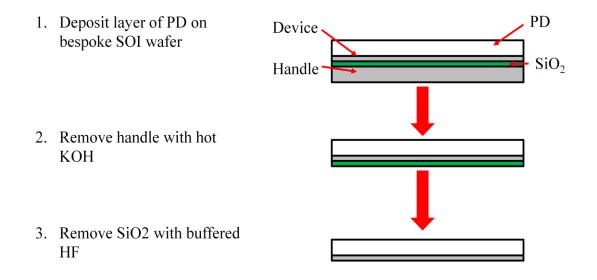

| 4.1.1 Basic Description of the SOI process                           | 133       |

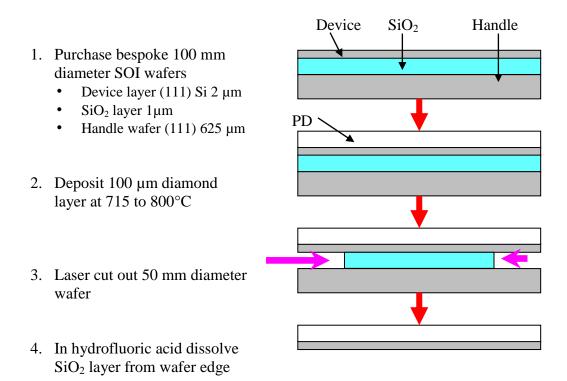

| 4.2 Initial SOI process for realising Si/PD substrates               | 135       |

| 4.3 Potential methods for releasing an intact (111) Si layer from a Si/SOI v | vafer |

|------------------------------------------------------------------------------|-------|

|                                                                              | 142   |

| 4.3.1 Method 1: Depositing SiO <sub>2</sub> on free PD surface               | 143   |

| 4.3.2 Method 2: Depositing a $SiO_2$ or $SiN_x$ interlayer                   | 144   |

| 4.4 Method 3: Anisotropic etching of the Si handle layer                     | 147   |

| Figure 4.15 Basic schematic of the process used to create suitable Si/PD wa  | fers  |

| for GaN using a chemical etching method.                                     | 148   |

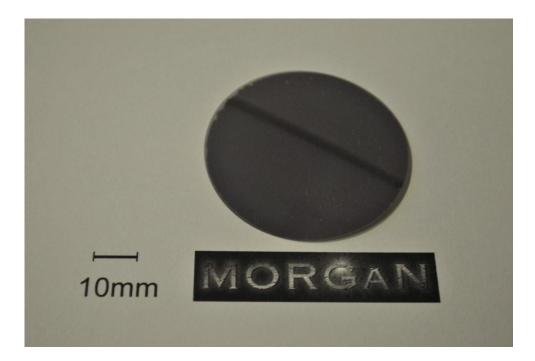

| 4.5 Experimental Characterisation of Si/PD SOI wafers                        | 149   |

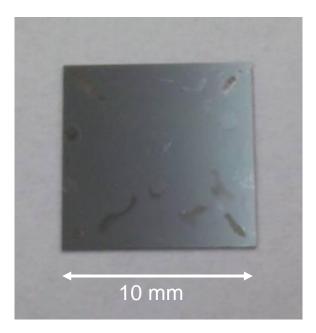

| 4.6 Production of suitable Si/PD substrates for GaN growth                   | 151   |

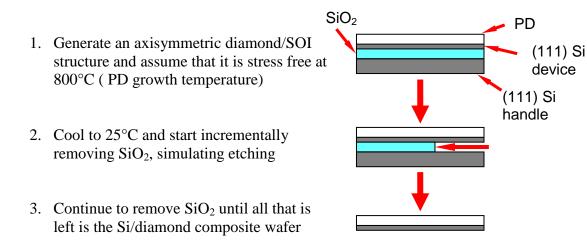

| 4.7 Thermal effects on thin Si/PD samples released from SOI wafers           | 153   |

| 4.8 Initial FE Modelling of GaN on Si/PD composite substrates                | 155   |

| 4.9 GaN on Si/PD substrates                                                  | 157   |

| 4.10 Concluding Remarks                                                      | 157   |

| CHAPTER 5: EXPERIMENTAL DETERMINATION OF THE ELASTIC                         | C     |

| PROPERTIES OF GAN AND SUBSTRATE MATERIALS                                    | 160   |

| 5.1 Motivation                                                               | 160   |

| 5.2 Outline of Chapter                                                       | 160   |

| 5.3 Initial Measurements                                                     | 161   |

| 5.3.1 Measurements of silicon and sapphire                                   | 162   |

| 5.3.2 Experimental issues identified with initial DMTA testing               | 163   |

| 5.3.3 Methods for improving the DMTA measurements and further tests with     |       |

| silicon and sapphire                                                         | 165   |

| 5.4 DMTA testing of free-standing GaN                                        | 168   |

| 5.4.1 Room temperature measurements of GaN sample                            | 170   |

| 5.4.2 GaN high temperature elastic modulus measurements and calibration      |       |

| approach                                                                     | 170   |

| 5.4.3 Isotropy of GaN in the (0001) Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 173                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 5.5 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 175                                                                                                                |

| CHAPTER 6: REALISATION OF A GAN-SENSOR MADE USING AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                    |

| EPITAXIAL LAYER OVERGROWTH (ELOG) TECHNIQUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 177                                                                                                                |

| 6.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 177                                                                                                                |

| 6.2 Aims of the chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 179                                                                                                                |

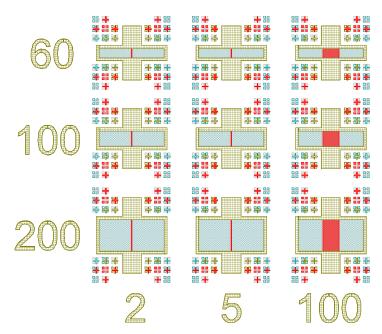

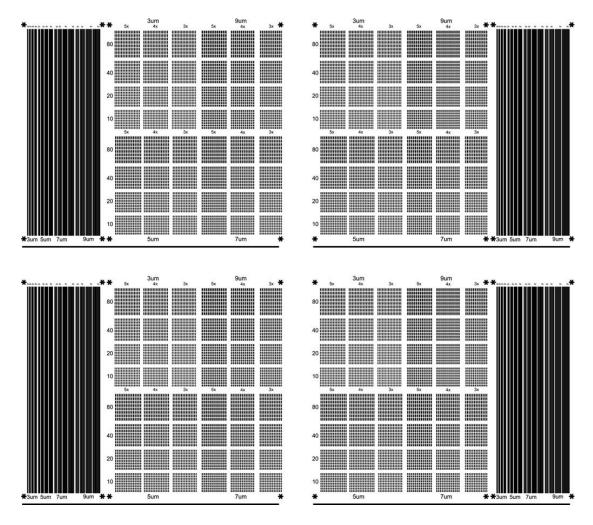

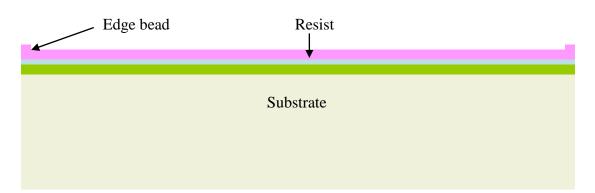

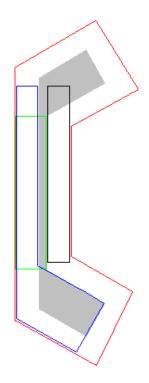

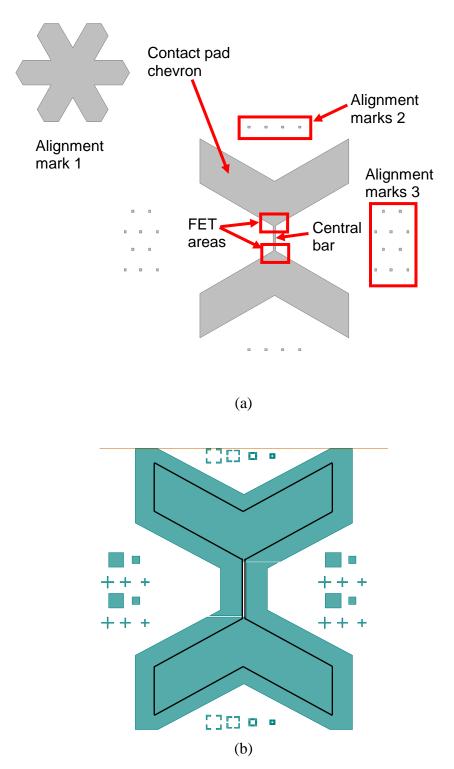

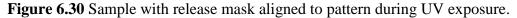

| 6.3 Design of the first mask set for cantilever devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 180                                                                                                                |

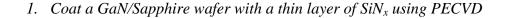

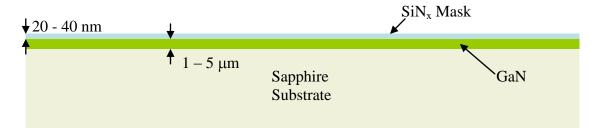

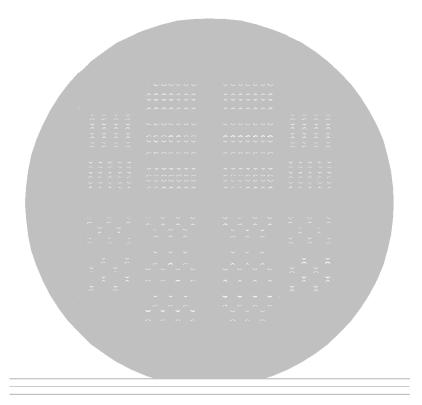

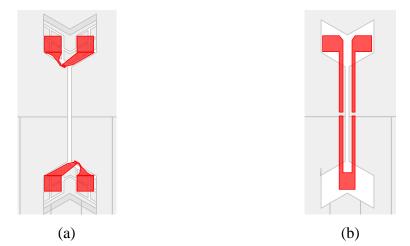

| 6.3.1 Method for Patterning GaN/Sapphire wafers for ELOG growth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 184                                                                                                                |

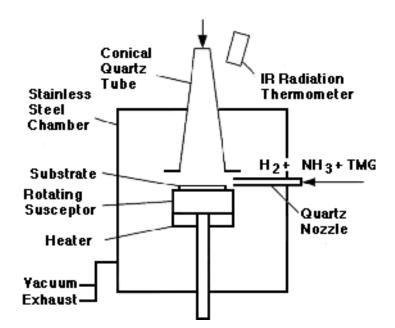

| 6.3.2 Description of the MOCVD/MOVPE process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 191                                                                                                                |

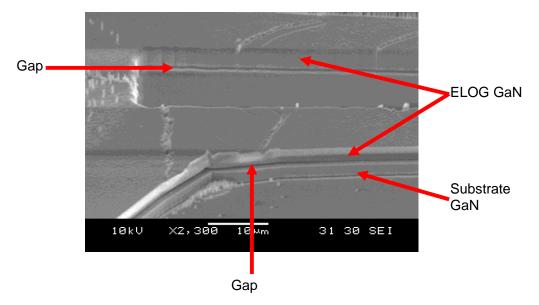

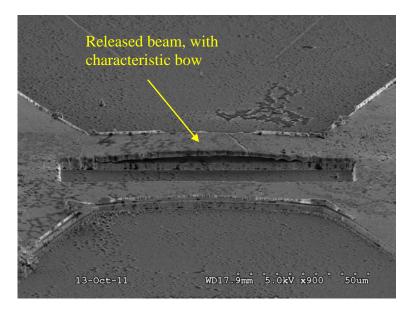

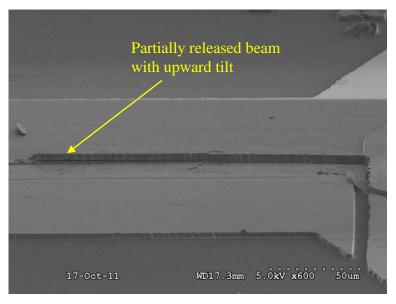

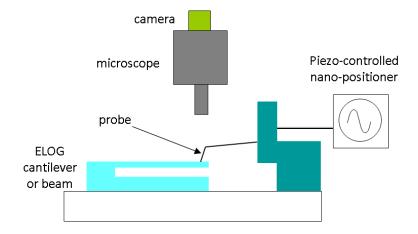

| 6.3.3 Results of the growth of ELOG cantilevers from first mask set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 193                                                                                                                |

| 6.3.4 Issues with first mask and ELOG growth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 196                                                                                                                |

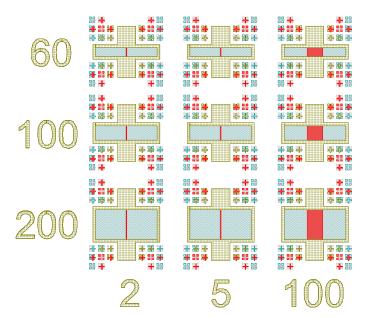

| 6.4 Design of the second Mask Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 198                                                                                                                |

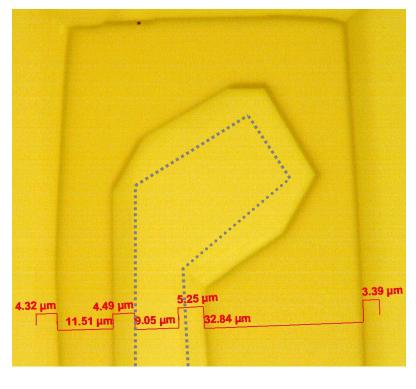

| 6.4.1 ELOG device terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 202                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • • •                                                                                                              |

| 6.4.2 Second generation ELOG mask methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 204                                                                                                                |

| <ul><li>6.4.2 Second generation ELOG mask methodology</li><li>6.5 Results from second generation ELOG templates</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 204<br>205                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                  |

| 6.5 Results from second generation ELOG templates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 205                                                                                                                |

| 6.5 Results from second generation ELOG templates<br>6.5.1 <i>Optical Imaging</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 205<br>205                                                                                                         |

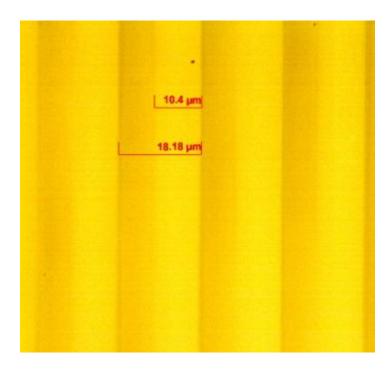

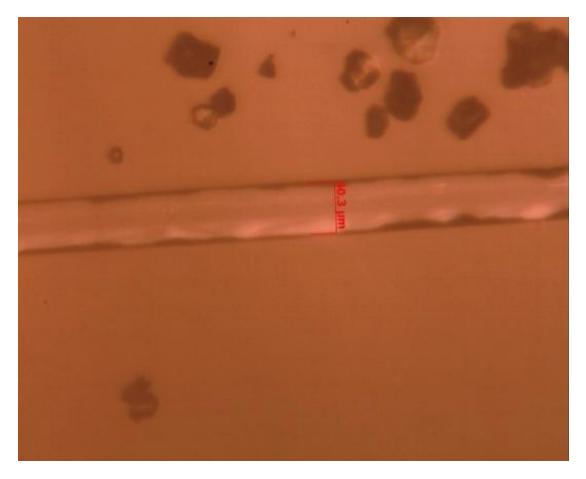

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging</li> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    | <b>205</b><br><b>205</b><br>205                                                                                    |

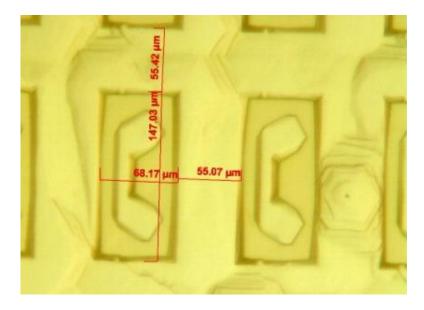

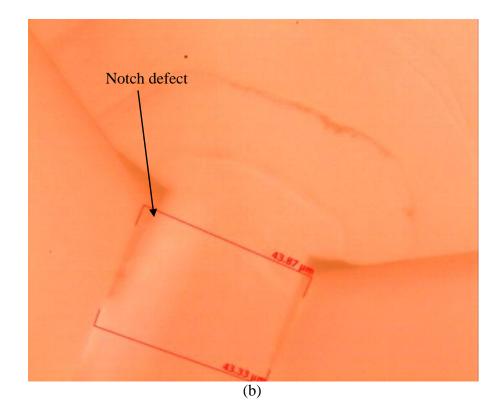

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging</li> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> <li>6.5.1.2 GaN/sapphire samples numbers 2226, 2846, 2847 and 2848</li> </ul>                                                                                                                                                                                                                                                                                                                            | <b>205</b><br><b>205</b><br>205<br>208                                                                             |

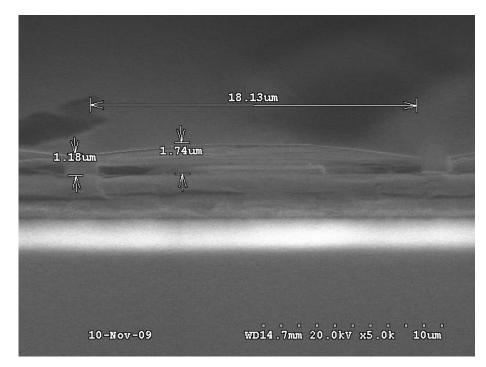

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging <ul> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> <li>6.5.1.2 GaN/sapphire samples numbers 2226, 2846, 2847 and 2848</li> </ul> </li> <li>6.5.2 SEM Imaging</li> </ul>                                                                                                                                                                                                                                                                                     | <ul> <li>205</li> <li>205</li> <li>205</li> <li>208</li> <li>212</li> </ul>                                        |

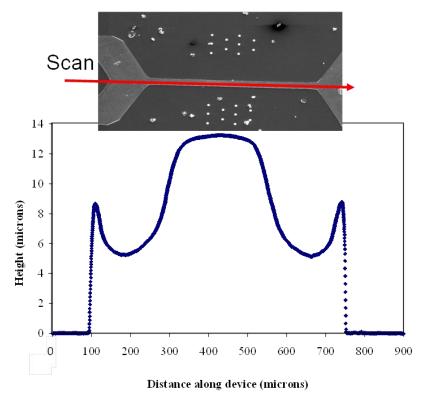

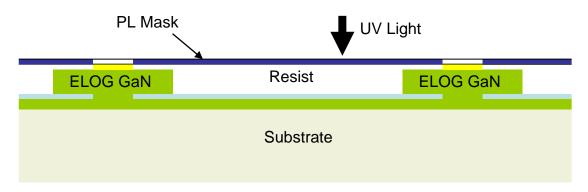

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging <ul> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> <li>6.5.1.2 GaN/sapphire samples numbers 2226, 2846, 2847 and 2848</li> </ul> </li> <li>6.5.2 SEM Imaging <ul> <li>6.5.3 Proscan 2000 and Dektak Measurements</li> </ul> </li> </ul>                                                                                                                                                                                                                     | <ul> <li>205</li> <li>205</li> <li>205</li> <li>208</li> <li>212</li> <li>215</li> </ul>                           |

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging <ul> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> <li>6.5.1.2 GaN/sapphire samples numbers 2226, 2846, 2847 and 2848</li> </ul> </li> <li>6.5.2 SEM Imaging <ul> <li>6.5.3 Proscan 2000 and Dektak Measurements</li> <li>6.5.4 Results from mixed ELOG/Pulsed ELOG (PLOG) growths</li> </ul> </li> </ul>                                                                                                                                                   | <ul> <li>205</li> <li>205</li> <li>205</li> <li>208</li> <li>212</li> <li>215</li> <li>219</li> <li>221</li> </ul> |

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging <ul> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> <li>6.5.1.2 GaN/sapphire samples numbers 2226, 2846, 2847 and 2848</li> </ul> </li> <li>6.5.2 SEM Imaging <ul> <li>6.5.3 Proscan 2000 and Dektak Measurements</li> <li>6.5.4 Results from mixed ELOG/Pulsed ELOG (PLOG) growths</li> <li>6.5.5 Discussion of second generation ELOG analysis</li> </ul> </li> </ul>                                                                                      | <ul> <li>205</li> <li>205</li> <li>205</li> <li>208</li> <li>212</li> <li>215</li> <li>219</li> <li>221</li> </ul> |

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging <ul> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> <li>6.5.1.2 GaN/sapphire samples numbers 2226, 2846, 2847 and 2848</li> </ul> </li> <li>6.5.2 SEM Imaging <ul> <li>6.5.3 Proscan 2000 and Dektak Measurements</li> <li>6.5.4 Results from mixed ELOG/Pulsed ELOG (PLOG) growths</li> <li>6.5.5 Discussion of second generation ELOG analysis</li> </ul> </li> </ul>                                                                                      | 205<br>205<br>205<br>208<br>212<br>215<br>219<br>221<br>aplate                                                     |

| <ul> <li>6.5 Results from second generation ELOG templates</li> <li>6.5.1 Optical Imaging <ul> <li>6.5.1.1 Sample 2828 (From first layer of the second generation mask set)</li> <li>6.5.1.2 GaN/sapphire samples numbers 2226, 2846, 2847 and 2848</li> </ul> </li> <li>6.5.2 SEM Imaging <ul> <li>6.5.3 Proscan 2000 and Dektak Measurements</li> <li>6.5.4 Results from mixed ELOG/Pulsed ELOG (PLOG) growths</li> <li>6.5.5 Discussion of second generation ELOG analysis</li> </ul> </li> <li>6.6 Proposed method for releasing ELOG MEMS structures from their templates</li> </ul> | 205<br>205<br>205<br>208<br>212<br>215<br>219<br>221<br>pplate<br>223                                              |

| <b>CHAPTER 7: MODELLING, DESIGN, DEVELOPMENT AND TESTI</b>                  | NG OF     |

|-----------------------------------------------------------------------------|-----------|

| A GAN/SAPPHIRE DRUMSKIN PRESSURE SENSOR                                     | 235       |

| 7.1 Motivation of Chapter                                                   | 235       |

| 7.2 Aims of Chapter                                                         | 236       |

| 7.3 Modelling                                                               | 237       |

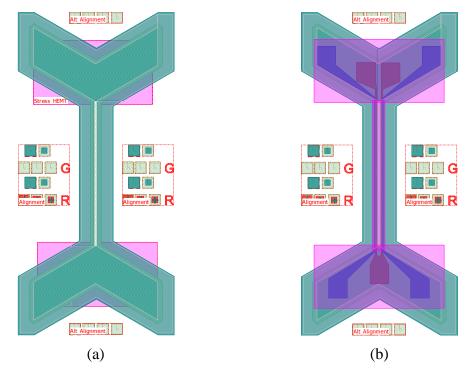

| 7.4 Results from modelling and design considerations                        | 239       |

| 7.4.1 Piezoelectric polarisation and optimisation of positions for the HEMI | [ sensors |

|                                                                             | 239       |

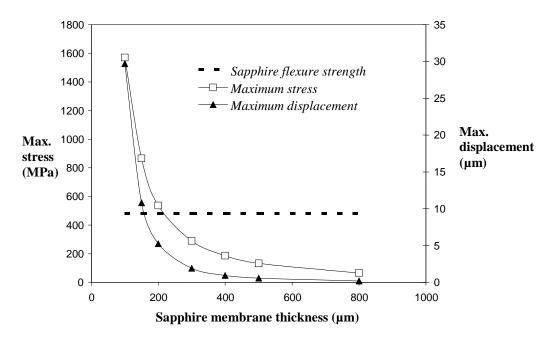

| 7.4.2 Optimisation of sapphire membrane thickness                           | 240       |

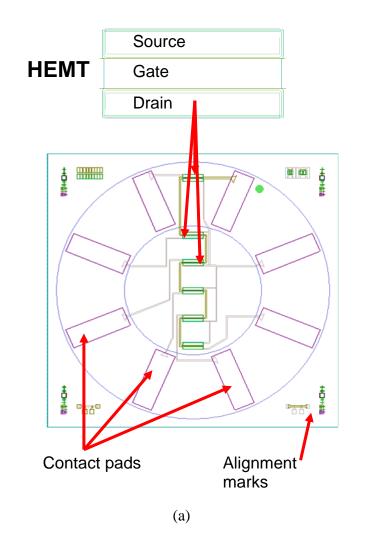

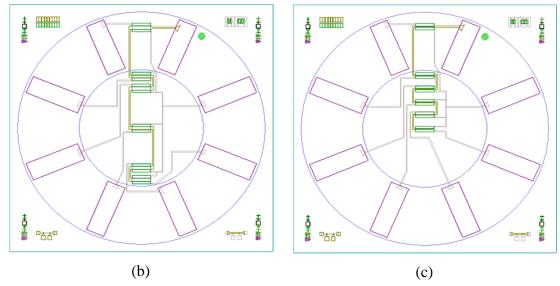

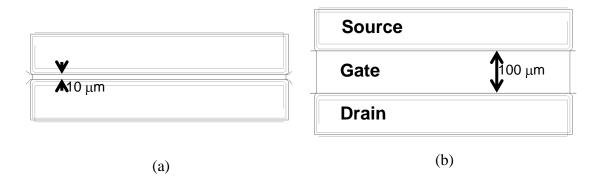

| 7.5 Design of the drumskin sensor mask set                                  | 241       |

| 7.6 Design of a high-pressure drumskin test rig                             | 245       |

| 7.7 Initial results from the drumskin sensor test rig                       | 249       |

| 7.8 Results from drumskin                                                   | 251       |

| 7.8.1 Temperature dependency                                                | 251       |

| 7.8.1.1 Removing Self-Heating                                               | 251       |

| 7.8.1.2 Heating the Sensor                                                  | 252       |

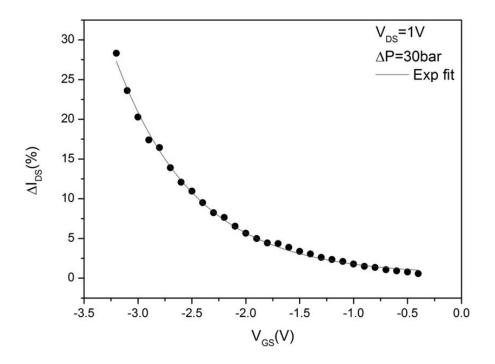

| 7.8.2 Static pressure dependency                                            | 253       |

| 7.8.3 Linearity of sensor response to pressure                              | 255       |

| 7.8.4 Addition of a Mechanical Probe                                        | 255       |

| 7.9 Concluding Remarks                                                      | 257       |

| 7.9.1 Comparison with other diaphragm sensors.                              | 258       |

| CHAPTER 8: PROJECT CONCLUSIONS AND FUTURE WORK.                             | 261       |

| 8.1 Thesis summary and overall conclusions from the project.                | 261       |

| 8.1.1 Measurements of the elastic properties of GaN with respect to temper  | ature 261 |

| 8.1.2 Development of a Si/PD substrate for use with GaN applications        | 261       |

| 8.1.3 ELOG templates for sensing applications                               | 263       |

| 8.1.4 GaN/sapphire diaphragm sensor                                         | 263       |

| 8.1.5 General outcomes of all experimental work in this PhD | 264  |

|-------------------------------------------------------------|------|

| 8.2 Future Work                                             | 265  |

| 8.2.1 Third generation ELOG sensor templates                | 265  |

| 8.2.2 GaN HEMTs on Si/PD substrates                         | 267  |

| 8.2.3. Diaphragm sensor                                     | 269  |

| REFERENCES                                                  | 272  |

| APPENDIX 1: MEETINGS, CONFERENCES AND PUBLICATIONS          | 293  |

| A1.1:                                                       | 296  |

| A1.2:                                                       | 306  |

| A1.3:                                                       | 311  |

| A1.4:                                                       | 316  |

| A1.5:                                                       | 321  |

| A1.6:                                                       | 330  |

| A1.7:                                                       | 332  |

| A1.8:                                                       | 336  |

| A1.9:                                                       | 338  |

| APPENDIX 2: EXAMPLE ANSYS CODE USED IN CHAPTERS 3, 4 AN     | ND 7 |

340

| Symbol          | Definition                 | SI unit           |

|-----------------|----------------------------|-------------------|

| а, с            | Lattice constants          | m                 |

| b               | Bow                        | m                 |

| С               | Capacitance                | F                 |

| С               | Uniform strain component   | -                 |

| C <sub>ij</sub> | Stiffness coefficients     | Pa                |

| CT              | Temperature coefficient    | $K^{-1}$          |

| d               | Diameter                   | m                 |

| D               | Electronic displacement    | C m <sup>-2</sup> |

| Ε               | Stiffness                  | Pa                |

| Е               | Strain                     | -                 |

| $\mathcal{E}_0$ | Permittivity of free space | $F m^{-1}$        |

| $\mathcal{E}_i$ | Permittivity               | F m <sup>-1</sup> |

# NOMENCLATURE.

| $e_{ij}$                 | Piezoelectric stress coefficients | $C m^{-1}$       |

|--------------------------|-----------------------------------|------------------|

| $E_{RT}$                 | Room temperature stiffness        | Pa               |

| G                        | Shear modulus                     | Pa               |

| Ι                        | Current                           | А                |

| $I_{DS}$                 | Drain-source current              | А                |

| <b>I</b> <sub>DSat</sub> | Drain-source saturation current   | А                |

| $I_{GS}$                 | Gate-source current               | А                |

| κ                        | Gauge factor                      | _                |

| М                        | Peeling moment                    | N m <sup>2</sup> |

| ν                        | Poisson's ratio                   | -                |

| R                        | Resistance                        | Ω                |

| r                        | Radius of curvature               | m <sup>-1</sup>  |

| σ, S                     | Stress                            | Ра               |

| $S_{ij}$                 | Compliance coefficients           | Pa <sup>-1</sup> |

| Т                                                        | Temperature                      | K   |

|----------------------------------------------------------|----------------------------------|-----|

| $t_b$                                                    | Bending axis                     | m   |

| $t_f$                                                    | Film thickness                   | m   |

| $t_s$                                                    | Substrate thickness              | m   |

| V                                                        | Voltage                          | V   |

| $V_{DS}$                                                 | Drain-source Voltage             | V   |

| <i>V<sub>DSat</sub></i>                                  | Drain-source saturation voltage  | V   |

| $V_{GS}$                                                 | Gate-source voltage              | V   |

| $\alpha$ , $\alpha$ <sub>a</sub> , $\alpha$ <sub>c</sub> | Coefficient of thermal expansion | K-1 |

| Name              | Definition                                      |

|-------------------|-------------------------------------------------|

| BIPEC             | Backside illuminated photo electrochemical etch |

| CE                | Cantilever epitaxy                              |

| CTE               | Coefficient of thermal expansion                |

| DMTA              | Dynamic mechanical thermal analysis             |

| EBL               | Electron beam lithography                       |

| ELOG, ELO,<br>LEO | Epitaxial layer overgrowth                      |

| FET               | Field effect transistor                         |

| FE                | Finite element                                  |

| FIB               | Focussed ion beam                               |

| HEMT              | High electron mobility transistor               |

| ICP               | Inductively coupled plasma                      |

| IPA               | Iso-propanol                                    |

| LED               | Light emitting diode                            |

# LIST OF DEFINITIONS.

| MORGaN | Materials for robust GaN                   |

|--------|--------------------------------------------|

| MIS    | metal-insulator-semiconductor              |

| MOCVD  | Metallo-organic chemical vapour deposition |

| MOVPE  | Metallo-organic vapour-phase epitaxy       |

| MEMS   | Micro-electromechanical systems            |

| NPE    | Nano-pendeo epitaxy                        |

| PECVD  | Plasma-enhanced chemical vapour deposition |

| PD     | Polycrystalline CVD diamond                |

| PEB    | Post exposure bake                         |

| PLOG   | Pulsed epitaxial layer overgrowth          |

| RIE    | Reactive ion etching                       |

| SEM    | Scanning electron microscopy               |

| SFB    | Silicon fusion bonding                     |

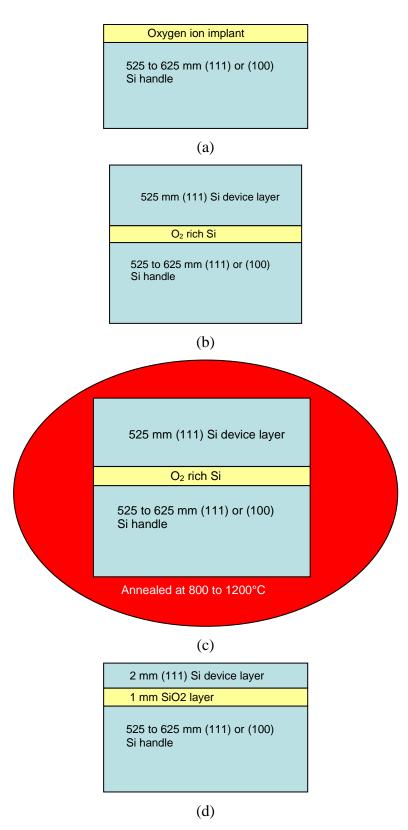

| SIMOX  | Silicon implantation of oxide              |

| SOI    | Silicon-on-insulator                       |

| TD    | Threading dislocation        |  |  |

|-------|------------------------------|--|--|

| III-V | Three-five semiconductor     |  |  |

| TMA   | Tri-methyl aluminium         |  |  |

| TMG   | Tri-methyl gallium           |  |  |

| TMI   | Tri-methyl indium            |  |  |

| 2DEG  | Two-dimensional electron gas |  |  |

| UV    | Ultra-violet                 |  |  |

#### **CHAPTER 1: MOTIVATION AND LITERATURE REVIEW**

#### **1.1 Introduction and Motivation**

#### 1.1.1 Introduction

The work to be undertaken as part of this PhD will be based on the design and fabrication of Gallium nitride (GaN)-based cantilever and membrane devices that can be used as a sensor at temperatures in excess of 300°C. The devices can potentially be used in areas such as space exploration [1], where present electronic devices degrade when exposed to extreme changes in temperature and large doses of radiation [1]. GaN-based sensors will suffer less mechanical degradation and can be used to measure pressure in extreme conditions [1].

GaN is an ideal material for a sensor in harsh environments since it is a robust material that is stable at temperatures up to 1000°C, has a wide band-gap of 3.6 eV [2] and a Young's modulus of ~288 GPa at room temperature [3]. Both cantilevers and membranes can based on GaN be used as strain gauges that respond to changes of pressure, temperature (see chapter 7) and stress. GaN is piezoelectric, which means that the material produces a charge when a strain is applied (the 'direct' piezoelectric effect) and an applied bias will result in the development of a strain in the material (the 'converse' piezoelectric effect) [4]. It is the piezoelectric properties of GaN that will allow strain on the device to be measured using either a metal-insulator-semiconductor (MIS) capacitor [4] or a high electron mobility transistor (HEMT) [2].

When a HEMT device is operating at high power, there are self-heating effects and this causes the electrical performance of the device to degrade [5]. This effect will also occur when a sensor is operating in high ambient temperatures. The most commonly used substrates for GaN growth are (111) silicon and sapphire, which are both relatively poor thermal conductors. The resulting heat gets trapped in the GaN surface, which reduces the channel conductivity and impairs the performance of the device (see chapter 7). GaN is now routinely grown on SiC substrates [6, 7], but these are very expensive (~\$760 for a 3 inch substrate in 2010 [8]) and have a thermal conductivity of 387 Wm<sup>-1</sup>K<sup>-1</sup> at room temperature [9], which although reasonable is

lower than that of diamond. The material with the highest thermal conductivity is diamond (4000 W m<sup>-1</sup>K<sup>-1</sup> at 20°C [10]), which can be produced straightforwardly using a chemical vapour deposition (CVD) process [11-13] and will be less expensive to produce than SiC.

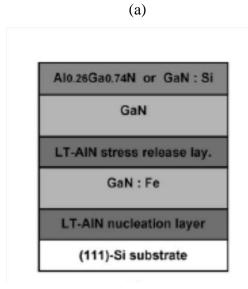

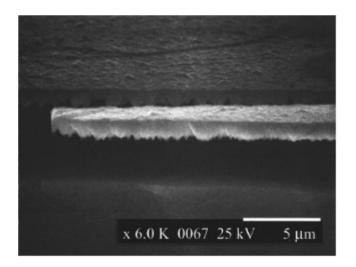

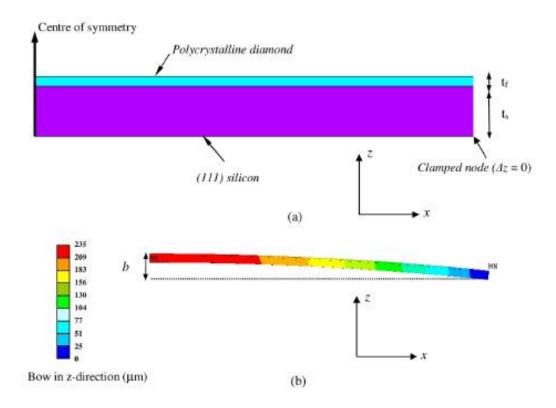

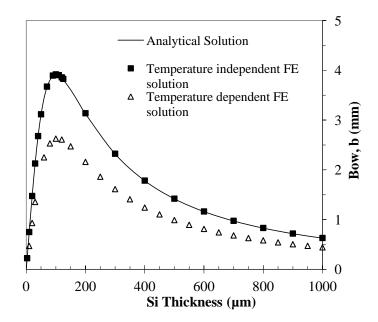

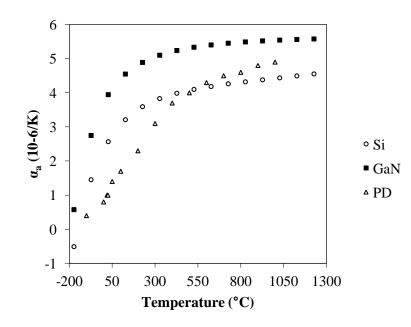

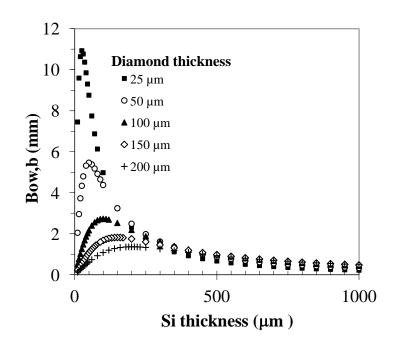

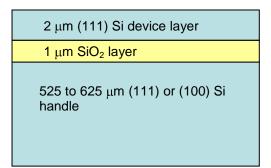

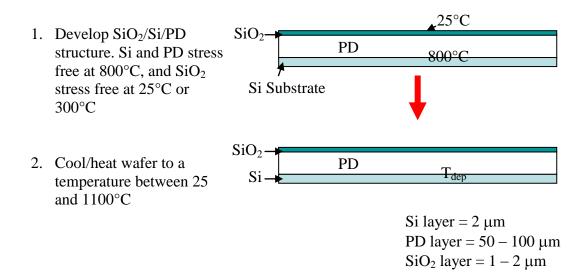

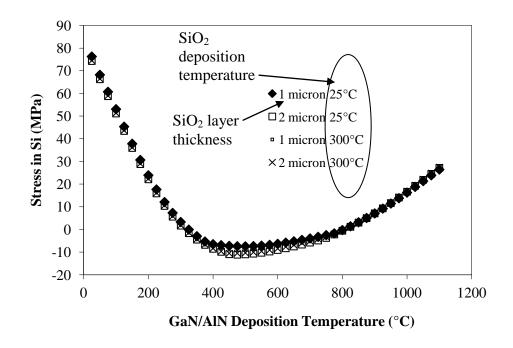

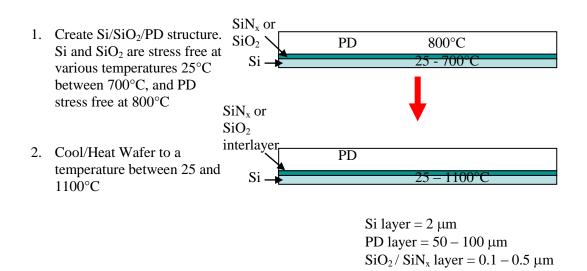

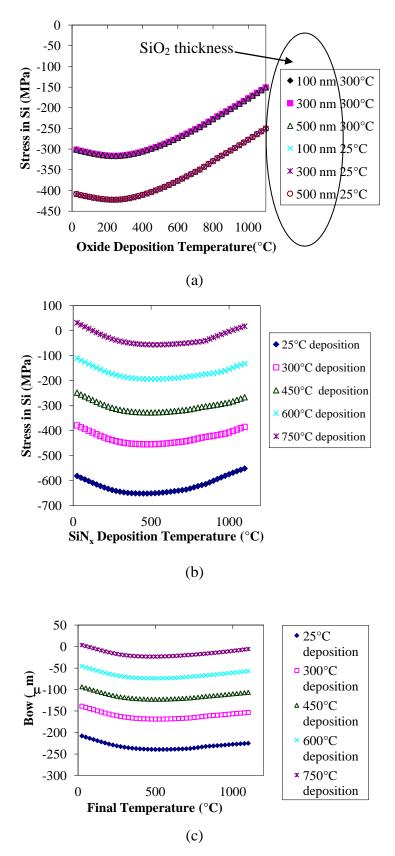

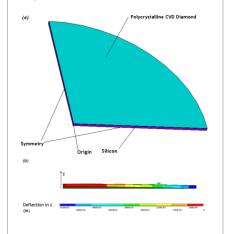

A (111) silicon (Si) / polycrystalline diamond (PD) composite substrate has been proposed as part of the Framework 7 (FP7) MORGaN (Materials for Robust Gallium Nitride) project [14, 15] and such a composite substrate has the potential to combine the high thermal conductivity of diamond with the epitaxial compatibility of GaN and (111) Si. We will see in the thesis that this composite substrate will consist of a ~ 2  $\mu$ m layer of Si and a ~ 50 to 100  $\mu$ m layer of PD. The PD will be synthesised on a bulk (111) Si wafer with a thickness of ~ 525  $\mu$ m and the Si will be subsequently lapped down to the desired thickness. However, due to thermal mismatch effects, the wafer becomes highly bowed and stressed during the lapping process. These issues and potential methods for creating a viable composite substrate are discussed in chapters 3 and 4.

#### 1.1.2 Motivation

This project concerns the effect of stress on GaN structures and their piezoelectric response in order to create a pressure sensor using either a field effect transistor (FET) or a high electron mobility transistor (HEMT) as a transducer. GaN and related III-V nitride materials, such as AlN and InN, are piezoelectric and semiconducting, hence suitable materials for creating strain sensors. GaN research is a large and varied research area, as discussed later in sections 1.2 to 1.5, meaning that this project can only concentrate on a few specific areas. These areas are the mechanical and piezoelectric behaviour of GaN and related substrate materials (Si, sapphire and PD are used as substrates in this project) when placed under mechanical and thermal stress. Additionally some knowledge of the workings of a GaN high electron mobility transistor (HEMT) is also needed so that they can be effectively utilised as sensing elements.

GaN also has a monocrystalline structure, rather than consisting of randomly orientated domains like PZT (lead zirconate titanate), which means that it does not require poling and this is an advantage for a strain sensor that potentially operates in environments that are difficult to access, such as in an oil well, jet engine or on a satellite. Theoretically [3] the elastic modulus of GaN shows little decrease with respect to temperature when heated to 625°C, meaning that GaN is potential sensing base material in what are defined in this project as 'harsh environments'. For the purpose of this thesis a 'harsh environment' is defined as an environment where the ambient temperature exceeds 300°C and the pressure is in the range of 10 to 60 bar. The sensors designed and discussed in this thesis are are intended for eventual use in these kind of environments

The objectives of this project are:

- Provide accurate finite element (FE) models using ANSYS that can be used to predict the behaviour of silicon/polycrystalline diamond (PD) composite substrates. These models will provide the MORGaN processing team with data that can be used to help overcome technical issues with these substrates.

- Have the Young's modulus of GaN measured up to the highest available temperature to verify that GaN maintains structural integrity. This will be done in this project using dynamic mechanical thermal analysis (DMTA) and the GaN samples will be sent to an external company for impulse excitation analysis to verify the DMTA measurements.

- Model, design and test, in conjunction with other MORGaN project partners, a GaN HEMT diaphragm sensor that has the potential to be used in harsh environments, verify that the sensor is sufficiently strain sensitive and follows trend behaviour predicted by the FE model. ANSYS will be used to provide predictions of the stress distribution and piezo-electric response of the sensor. This information will then be used to determine the position of the HEMT sensing elements at the design phase and the sensor testing will determine the accuracy of the model.

• Design templates that can be used by the in-house metallo-organic vapour phase epitaxy (MOVPE) expert to laterally overgrow GaN material, using an epitaxial lateral overgrowth (ELOG) method, which can be potentially used as a sensor beyond this project. After MOVPE growth, there will be an attempt to release the laterally overgrown material from the designed template using nanofabrication methods: creating free-standing structures that can be converted into strain sensors in the future.

#### 1.1.2 Thesis Structure

This thesis concerns the work undertaken developing novel substrates that are compatible with GaN growth and the development of new GaN-based pressure sensors for extreme environments. The work was undertaken as part of the MORGaN (Materials for Robust Gallium Nitride) project, which funded this PhD. The thesis consists of eight chapters, with the concluding chapter discussing future work and appendices at the end.

Chapter 1 consists of a literature review that shows the motivation of this project and the current state of the art of GaN sensing and substrate technology. The relative merits of current substrates and other examples of GaN sensors will be discussed. The shortcomings of the current technology in the literature will be determined and there will be an outline of how this thesis will improve on the current state of the art. The stiffness and piezoelectric coefficients of GaN and the substrate materials used in this project will be discussed and derived from first principles; these are very important quantities when modelling new substrates and sensors. There will also be a discussion of how some these properties will be measured experimentally as part of this project.

Chapter 2 is an additional review chapter that concerns the experimental techniques used in this project. Although there is a significant amount of modelling in this PhD, it is speculative unless it receives some validation. This chapter describes the methodology of the experimental techniques that have been used to validate the model. The details of how wafer bow, layer thicknesses and strains in a wafer are measured will be described in this chapter. Furthermore, the measurement of the stiffness of GaN, Si and sapphire at high temperature are discussed. Understanding how these materials behave at high temperatures is of high importance to this project and the design of extreme sensing devices. Finally, the nanofabrication techniques used to develop GaN sensors will also be discussed.

The development of a Si/PD composite substrate wafer will be the overriding topic of chapters 3 and 4. The potential of this substrate technology is high and is a key output of the MORGaN project. However there are many issues to overcome, such as delamination, cracking and excessive bow caused by thermal mismatch. Chapter 3 will consider the validation of the finite element (FE) model developed to examine this problem and the issues caused by the mismatch of the coefficients of thermal expansion (CTEs). Chapter 4 will discuss various methods for overcoming issues caused by CTE mismatch and diamond synthesis will be discussed, and the merits of these methods will be determined. The main method for overcoming Si/PD processing issues was to use silicon-on-insulator (SOI) wafers and this work will be discussed in detail in chapter 4. Potential solutions to these methods will also be discussed, as well as the viability of this technology.

The high temperature measurements of Si, GaN and sapphire will be discussed in chapter 5. These measurements were undertaken using dynamic mechanical thermal analysis (DMTA), which can measure the stiffness of a material up to 500°C, and impulse excitation at IMCE, which can measure the stiffness up to 1000°C. The stiffness of Si at high temperature is well-known in the literature and this data will be used to discuss the validity of using DMTA for these measurements. The stiffness of sapphire was then measured and there is a discussion of the results. Free-standing GaN wafers were laser cut, so that precise test pieces could be formed and the error in geometry was minimised. Understanding how GaN, Si and sapphire behave at high temperature is a requirement for extreme sensing.

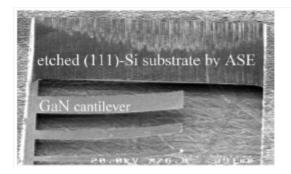

Chapter 6 details the progress in the production of a small GaN strain sensor templates fashioned from Epitaxial Layer Overgrowth (ELO or ELOG) material. ELOG material has a very low dislocation density, and therefore has superior electrical and mechanical properties [16]. This chapter will describe the design process, with fabricated photoelectric masks and any issues that manifested themselves during this stage. The process was iterative and multiple types of ELOG device were trialled, the merits of each type of device will be determined. The ELOG fabrication process will be discussed in detail, along with any associated technical issues.

Chapter 7 will describe the development of a GaN membrane pressure sensor known as the "drumskin" in the MORGaN project. This chapter begins by discussing the initial FE modelling of the concept, followed by the design of the sensor. The relative merits of all three different types of drumskin that were considered will be discussed. An experimental test rig for this sensor was then designed and built at Bath. The drumskin testing methodology will be outlined and the results will be discussed in detail. Finally, there will be a discussion of future possible improvements to this sensor.

The final chapter of the thesis will discuss concluding remarks. In these remarks the key results and novelty of the thesis will be outlined. There will be a discussion of potential future work that can result from this project. The thesis will then provide appendices and publications that have resulted from this PhD project after the main body of work. A review of the current state of GaN sensing technology will now be discussed.

#### **1.2 Applications of GaN**

The traditional use for GaN in the semiconductor industry is for blue-light emitting diodes (LEDs) for solid state lighting [17-19]. These LEDs emit light at a shorter wavelength than traditional red LEDs, increasing the memory capacity of a disk; these are used to read blu-ray disks [19]. This application is not important to this project because in order to make good-quality high-temperature strain gauges, the understanding of the thermal, physical and structural properties of GaN is more important. The strain gauge application has more in common with another common use for GaN, field-effect transistors (FETs) and high electron mobility transistors (HEMTs) in particular [6, 20].

A HEMT is also known as a heterojunction FET, where a heterojunction is the interface between two different solid-state materials. A HEMT works because at the

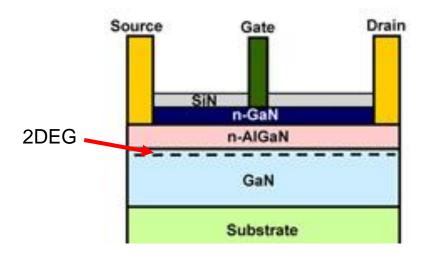

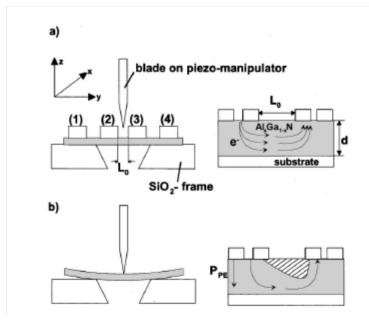

heterojunction, a 2D electron gas (2DEG) forms and this gives HEMTs high electron mobility. In the growth and fabrication of a GaN device, HEMTs are typically made by depositing a metallic alloy layer, such as AlGaN, on top of a GaN layer. A diagram of a generic GaN/AlGaN HEMT from [21] is shown in figure 1.1.

Figure 1.1 Schematic of a GaN / AlGaN HEMT [21].

A GaN-based HEMT generally looks similar to the HEMT in figure 1.1, although a InAlN layer is sometimes used in place of AlGaN due to the fact the it is lattice matched with GaN [22]. A HEMT has been proposed [23] as a potential sensor for measuring the piezoelectric and piezoresistive response to changes in stress applied to a MEMS GaN cantilever. The addition of the AlGaN layer also has the effect lowering the potential barrier of GaN, improving the semiconducting properties of the device and simplifying the process of fabricating contacts. The background theory of HEMTs will be briefly discussed in section 1.5. GaN is piezoelectric and piezoresistive, hence it is a potential for sensing applications. The following section will discuss the piezoelectric and piezoresistive properties of GaN.

### 1.3 Introduction to Piezoelectricity and Piezoresistivity

### 1.3.1 Piezoelectricity

A piezoelectric material exhibits time-varying dipole moments and voltages when subjected to time-varying mechanical stress [24]. Piezoelectric materials tend to be single crystalline or ceramic, with unsymmetrical crystal lattices and an even distribution of positive and negative charges. There are two types of piezoelectric effects the direct piezoelectric effect, where a strain applied to the material causes a potential, and the converse piezoelectric effect, where a potential causes mechanical strain in the material. GaN demonstrates both the direct and converse piezoelectric effect [4, 25].

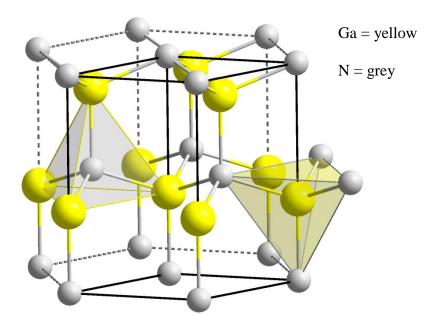

GaN is a binary compound in a wurtzite crystal structure, where wurtzite is a hexagonal crystal lattice system. Wurtzite crystals generally exhibit the piezoelectric effect [26] and GaN is no exception. Other examples of materials with a wurtzite crystal structure include other nitrides, such as Aluminium Nitride (AlN), Boron Nitride (BN) and Indium Nitride (InN), and sulphides such as CdS and ZnS [2]. The elements in a wurtzite lattice are bonded ionically and arranged in the lattice shown in figure 1.2.

Figure 1.2 Schematic of the Wurtzite Crystal Structure [27].

A piezoelectric material consists of numerous charges in a crystalline structure, with the positive and negative charges distributed throughout the crystal. In monocrystalline GaN all of the dipoles are naturally orientated in the same direction, unlike a ferroelectric material (such as lead zirconia titanate (PZT)) that consists of randomly orientated domains, and this means that GaN has the advantage of not requiring an external bias, a process known as 'poling'. Ferroelectric materials consist of randomly orientated piezoelectric domains that typically cancel each other out and require an external bias to align the domains in the same direction, making the material practical to use for piezoelectric applications.

When a piezoelectric material is placed under compressive strain, the dipoles are deformed, disturbing the charge symmetry, and this causes an electric charge separation across the crystal lattice. This charge separation causes an electric potential in response to the applied strain. In all piezoelectric materials, the piezoelectric effect is anisotropic in nature and its coefficients vary according to the direction along the crystal plane. Therefore, the piezoelectric strain and stiffness matrix coefficients need to be known for the purposes of modelling; this will be discussed in section 1.6.

#### 1.3.2 Piezoresistivity

As well as having piezoelectric properties, GaN also exhibits a small piezoresistive effect [28, 29]. The piezoresistive effect is a change in resistance due to the application of a mechanical stress to a material. Unlike the piezoelectric effect, the piezoresistive effect only changes the electrical resistance of the material and does not produce a potential. This basically means that the piezoresistive effect refers to a small perturbation in current with respect to a constant voltage when a mechanical stress is applied to the sensor. The piezoresistor is the most common piezoresistive device and is used for measuring strain in mechanical devices [29, 30]. One of the aims of this project is to design, build and characterise a microelectro-mechanical system (MEMS) device that uses the piezoelectric and/or piezoresistive properties of GaN to measure stress/strain changes in harsh environments.

The sensitivity to piezoresistivity and piezoelectricity in a device is defined by its gauge factor  $\kappa$  [30].

$$\kappa = \frac{dR/R}{\varepsilon} \tag{1.1}$$

Where dR is the change in resistance due to mechanical deformation, R is the initial resistance, and  $\varepsilon$  is the strain. An alternative to Equation (1.1) is to calculate the gauge factor using the applied strain and changes in capacitance [30]:

$$\kappa = \frac{\Delta C/C}{S_1} \tag{1.2}$$

Where C is the initial capacitance at zero strain,  $\Delta C$  is the change in capacitance, and S<sub>1</sub> is the applied strain [30]. The gauge factor is also a measure of the sensitivity of a device.

#### 1.3.3 Piezoelectric and piezoresistive measurements in the literature.

The piezoelectric and piezoresistive properties of GaN are difficult to measure because the charges dissipate over time after a static strain is applied [28]. It only takes approximately a second for most of the piezoelectric charges in GaN generated from an applied strain to dissipate [28] since the material is a semiconductor; the charges are eventually neutralised by free-carriers in the material and background extrinsic charges [28]. This is in contrast to conventional piezoelectric ceramics such as lead zirconate titanate (PZT) which are excellent insulators. Therefore, it is possible that GaN is better suited to sensing dynamic, rather than static environments. A dynamic gauge factor of 130 was measured for the GaN/sapphire sample in [28] when it was deformed longitudinally, which is four times greater than the gauge factor of SiC. These samples consisted of a  $3-5 \mu m$  layer of GaN epitaxially grown slightly off-axis from a (0001) sapphire substrate [28]. The GaN/sapphire sample also exhibited a small static gauge factor of four [28], suggesting that GaN is weakly piezoresistive and can be used as a static sensor in extreme environments in the absence of another suitable material. Further evidence in support of GaN being a viable static sensing material will be discussed in chapter 7. This small piezoresistive effect is caused by the electron donor energy being shifted closer to the conduction band by applying a stress [28].

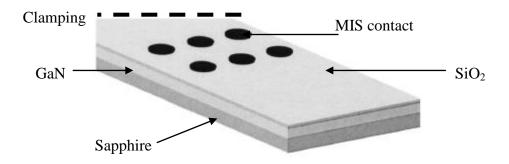

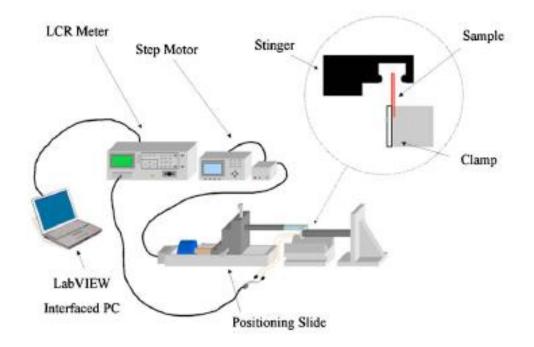

A method for measuring piezoelectric and piezoresistive effects and the gauge factor of GaN sensors is shown in figure 1.3, as described by Strittmatter [31] and in three papers by Tilak [30, 32, 33]. The basic process is to clamp a section of a GaN/substrate and use capacitive contacts for taking electrical measurements. In the cases of [30-33] the type of capacitive contacts are known as metal-insulatorsemiconductor (MIS) capacitors. Using equation (1.2), it is possible to measure the gauge factor of a GaN sensor and determine its piezoelectric and piezoresistive behaviour. Therefore a capacitor is a suitable sensing element for GaN, but it does have the drawback of needing to be typically 40 to50  $\mu$ m in gate length and 50  $\mu$ m in gate width [34-36] in order to retrieve a significant signal, which is a significant handicap when fabricating a MEMS sensor. The type of cantilever structure, shown in figure 1.3, can also be used to measure the piezoelectric coefficients of GaN, for which there are no agreed measurements in the literature; in addition to being a potential viable strain gauge device.

In reference [30], GaN-based strain gauges with GaN epitaxially grown on (111) Si and c-plane (0001) sapphire were fabricated. These relatively large cantilevers were 17 x 5 mm long, with a ~2 µm n-doped GaN layer deposited on the sapphire substrate; which is left unaltered and at its original thickness. When the substrate is sapphire, two MIS capacitive contacts were deposited directly onto a 2 µm thick ndoped GaN layer. When silicon was used as a substrate, a 20 nm AlGaN layer was grown on top of a 1 µm thick layer of GaN; the contacts were then fabricated on the AlGaN. As discussed earlier, the purpose of the n-type doping and the use of AlGaN in the respective cantilevers are to lower the potential barrier of GaN to improve the reliability of the capacitive contacts. Lowering the potential barrier means that it will take less energy for an electron to pass from the metallic contact to the conduction band in the AlGaN and vice versa. This means in the case of the GaN cantilevers in [30], the semiconductor component of the device is the GaN or GaN/AlGaN layer. An insulating layer of 100 nm SiO<sub>2</sub> was then deposited on the GaN/sapphire wafer, and 30 nm of the same material was deposited on the AlGaN/GaN/Si wafer to create a capacitive contact. A 30 nm layer of  $SiN_x$  was then deposited on both types of wafer, completing the insulator layer [30]. Two differing metal contacts were then deposited on the insulating layer [30].

**Figure 1.3** Schematic of the MIS diode cantilever used in Strittmatter *et al* [4]. The cantilevers described in [30] are similar.

For a MIS capacitor, one of the contacts has Ohmic current-voltage (IV) characteristics and the other contact has Schottky barrier characteristics. The main difference between the two types of barriers is that a Schottky barrier rectifies the current and an ohmic contact does not. This means that the I-V characteristic curve of an ohmic device is linear and symmetric, with the opposite being the case in a Schottky device. An Ohmic contact is defined as a metal-semiconductor contact that has a minimal resistance in relation to the total resistance of the semiconductor device [2]. Every semiconductor device requires at least two metal-semiconductor interfaces, so at least one good ohmic contact is required for the majority of semiconductor devices. For GaN-based devices, it is difficult to make good ohmic contacts because it has a wide band gap of 3.6 eV. This means that this band gap has to be lowered at the surface. Possible methods for doing this include heavily doping the GaN device layer, severely impacting on the performance of the device, or by creating heterojunctions by growing thin epitaxial layers of a metallic alloy such as AlGaN. Examples of both methods are contained in the literature [30], using both doping and epitaxial layers to help fabricate an ohmic contact. The two different types of devices in [32] use different levels of doping. Table 1.1 below shows the relative performances of the cantilever devices in [30] and [32].

| Data<br>Source | Structure                                                                    | Operating<br>Temperature | Gauge<br>Factor | Dimensions<br>(mm) |

|----------------|------------------------------------------------------------------------------|--------------------------|-----------------|--------------------|

|                |                                                                              | ( <b>K</b> )             |                 |                    |

| [30]           | AlGaN/GaN MIS                                                                | 298                      | 575             | 17 x 5             |

|                | capacitor (n-type doping $< 10^{16}$ cm <sup>-3</sup> )                      | 673                      | 361             |                    |

| [30]           | GaN MIS capacitor<br>(n-type doping                                          | 298                      | 75              | 17 x 5             |

| [32]           | $<10^{16} \text{ cm}^{-3}$ )<br>7 x 10 <sup>16</sup> cm <sup>-3</sup> n-type | 298                      | 167             | $8 \times 5$       |

| [32]           | • 1                                                                          |                          | 107             | 0 × J              |

|                | doped 2 µm thick<br>GaN MIS capacitor                                        | 523                      | 104             |                    |

| [32]           | $10^{18} \text{ cm}^{-3} \text{ n-type}$                                     | 298                      | 25              | $8 \times 5$       |

|                | doped 250 µm thick<br>GaN MIS capacitor                                      | 398                      | 17              |                    |

**Table 1.1** Gauge factors of different cantilever devices.

Table 1.1 shows that the cantilever with an AlGaN epitaxial layer has the largest gauge factor and is the most sensitive to changes in stress. All of the cantilevers in table 1.1 were designed to be used as capacitors that could be used to measure either the piezoelectric coefficients of GaN or the gauge factor of the device. The application of the cantilevers in [30] is for high temperature strain gauges, which is similar to the application of the devices in this PhD; although the cantilevers or membranes are likely to be smaller [23]. The AlGaN device performs well at 400°C (673K), indicating that the devices created during this PhD may also function well at similar temperatures. The ohmic contact fabricated for both types of cantilever in [30] was a stack of Ti/Al/Mo/Au with thicknesses of 10 nm/100 nm/50 nm/50 nm, and the Schottky gate was Ni (50 nm)/Au (300 nm). A 500 nm gold layer was finally deposited on both contacts to allow wires to be bonded.

A schematic from reference [33], in figure 1.4, shows a method employed for measuring the piezoelectric coefficients of GaN.

**Figure 1.4** Schematic of an experiment used in reference [33] to determine the piezoelectric coefficient of GaN.

It should be mentioned that to date, no evidence has been found for the high temperature testing of the piezoelectric properties of these types of devices. In [33] all of the measurements were carried out at room temperature.

#### 1.4 GaN HEMTs

#### 1.4.1 HEMT Terminology

GaN HEMTs are used as sensing elements for the sensor described in chapter 7 and in this literature review. To help with the interpretation of the results in this chapter, the basics of HEMT operation and terminology will be described in this section. The High Electron Mobility Transistor (HEMT), also known as a Heterojunction Field Effect Transistor (HFET). HEMTs are often used in modern electronics as they have high carrier concentrations and superior electron mobilities [2]. A HEMT belongs to the metal semiconductor field effect transistors (MESFET) group of field effect transistors (FETs). HEMTs are often used instead of Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) as they have high carrier concentrations and superior electron mobilities. At the interface between the semiconducting materials, known as a heterojunction, a 2D electron gas (2DEG) forms and this is the cause of the HEMT's high electron mobility [2].

In order to allow conduction in a semiconductor, it needs to be doped with impurities such as iron or silicon. Electrons tend to collide with the impurity atoms, slowing them down, and reducing both the efficiency and electron mobility of the device [2]. In the case of a simple GaN/AlGaN HEMT (figure 1.1), where the heterojunction consists of an n-doped epitaxial layer of AlGaN on top of a GaN layer with no deliberate dopants (unintentionally doped GaN is slightly n-doped due to the crystal growth process); the electrons produced in the n-AlGaN epitaxial layer will diffuse into the top of the GaN layer because a quantum well is created in its conduction band. If a heterojunction is allowed to reach chemical and thermal equilibrium, then the Fermi level of both materials aligns and this means that it is constant throughout the system. This means that electrons will leave some regions, causing depletion and

will accumulate in others in order to find equilibrium. The depletion and accumulation of electrons causes the bending of conduction and valence bands near the interface. In the case of a heterojunction between AlGaN and GaN, the band bending means that the electrons accumulate in a quantum well on the GaN conduction band near the AlGaN/GaN interface.

In practice, this quantum well exists as a thin layer between the n-AlGaN and GaN layers and is known as a 2DEG. Inside the 2DEG, there is a very high concentration of highly mobile electrons and the electrons can move quickly without colliding into any impurity atoms; the position of the 2DEG is marked in figure 1.1. Therefore, the HEMT overcomes the impurity collision problem because electrons can travel unhindered along the 2DEG: leading to very low resistivity in the device. Furthermore, the impurity concentration of a HEMT device has little impact on its performance.

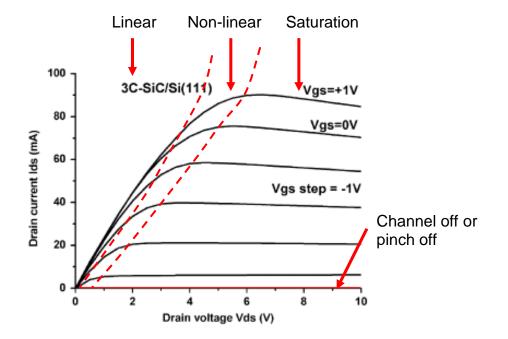

**Figure 1.5**  $I_{DS}$ - $V_{DS}$  of a AlGaN/GaN HEMT with a 3 x 150  $\mu$ m gate grown on a SiC substrate from [6].

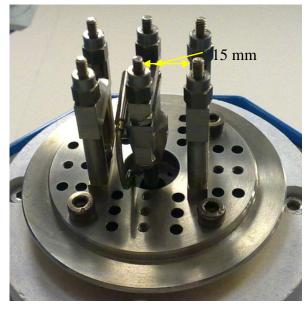

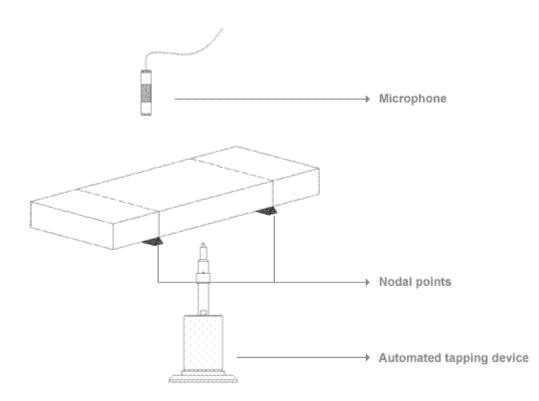

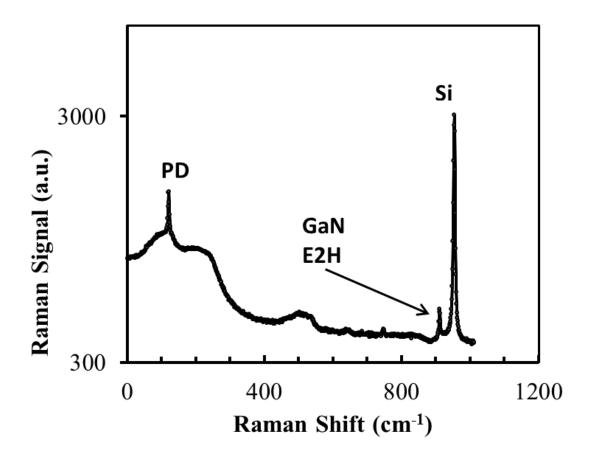

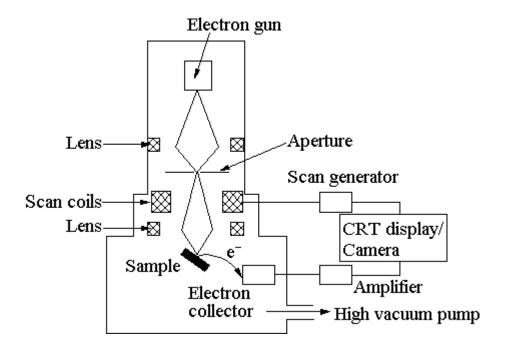

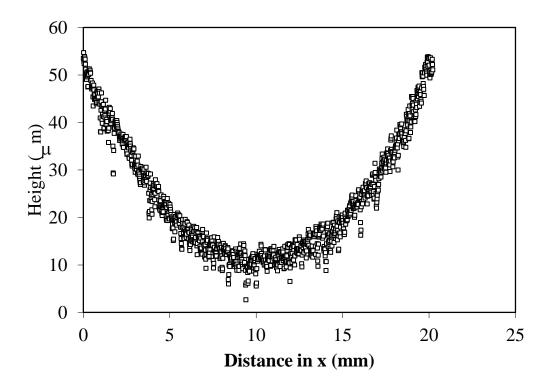

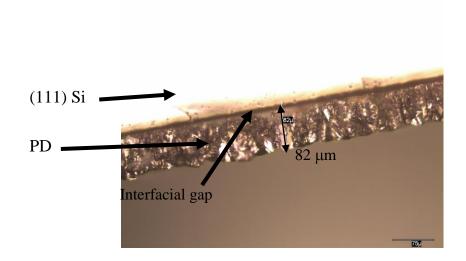

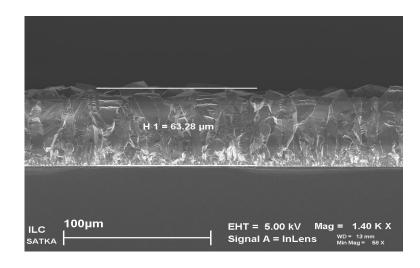

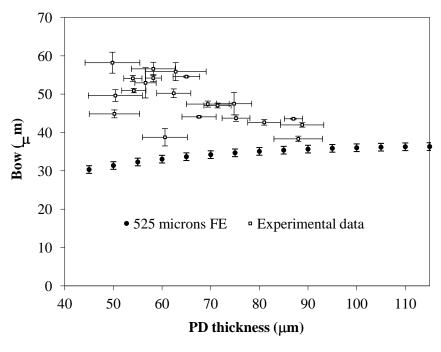

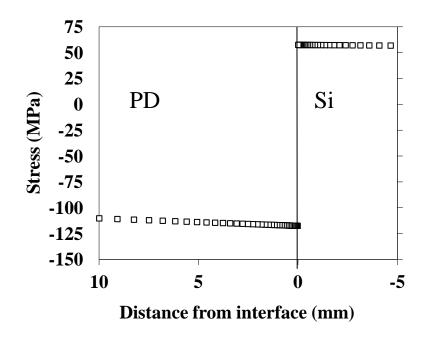

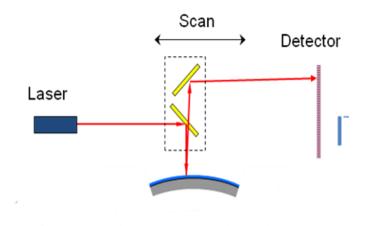

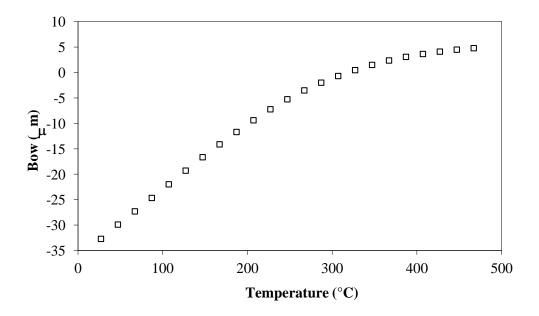

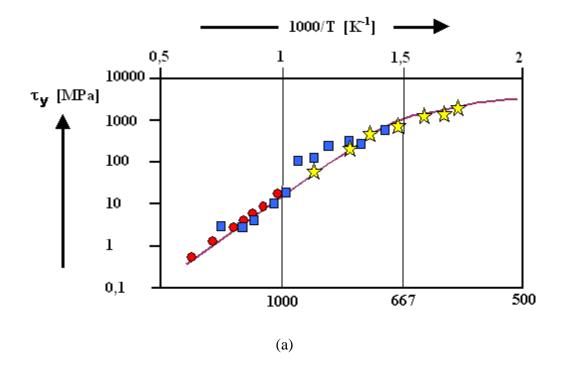

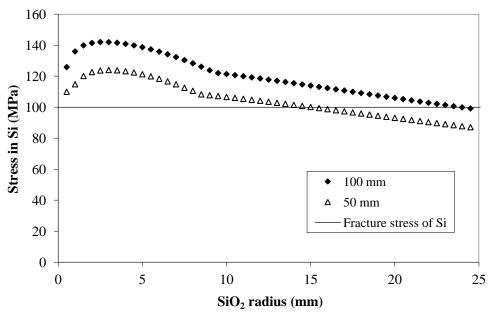

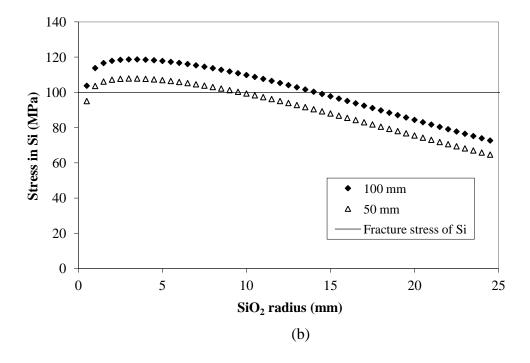

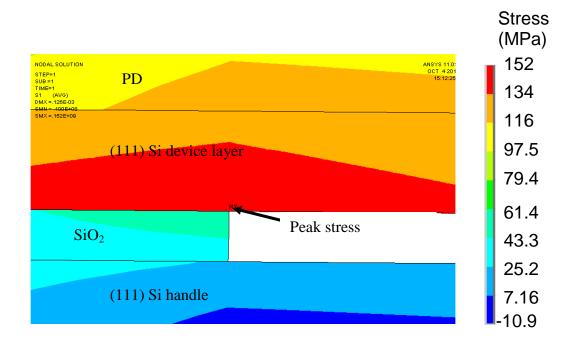

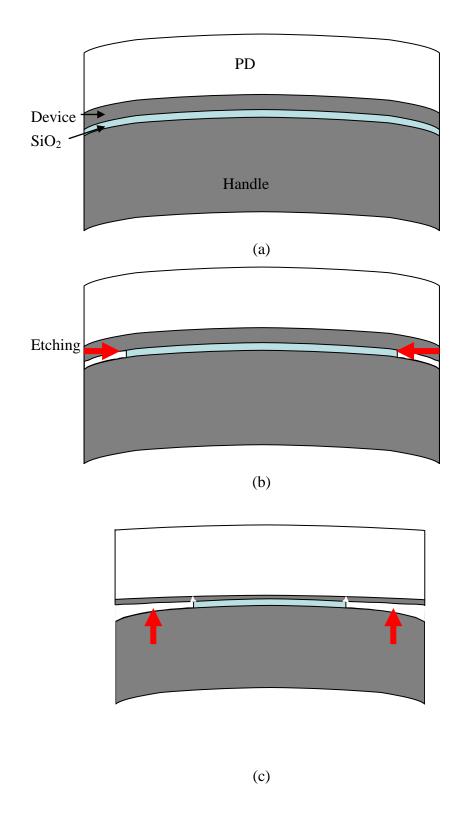

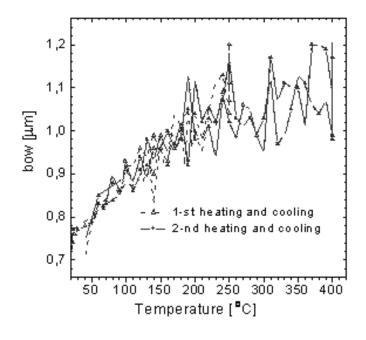

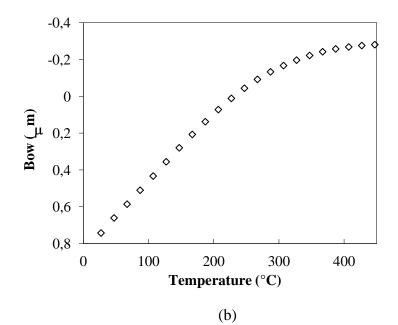

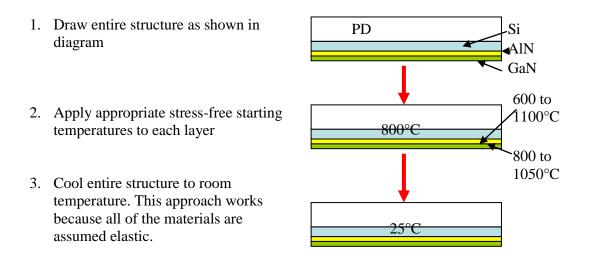

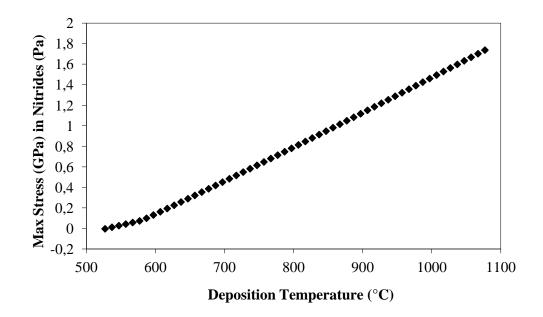

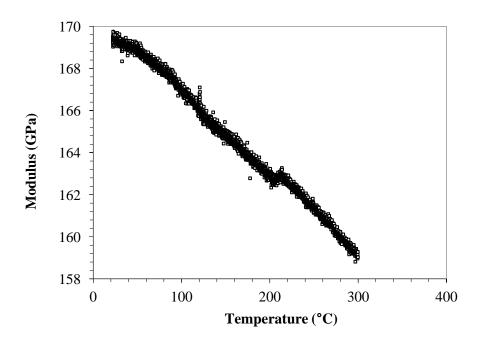

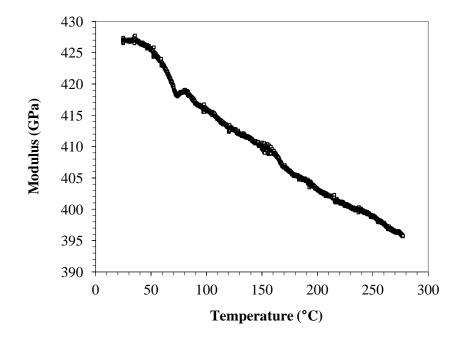

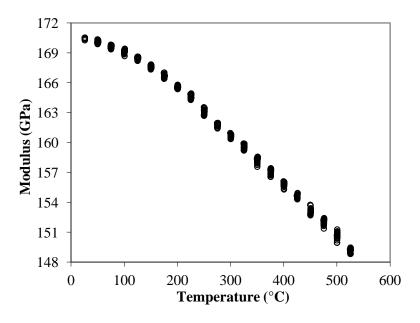

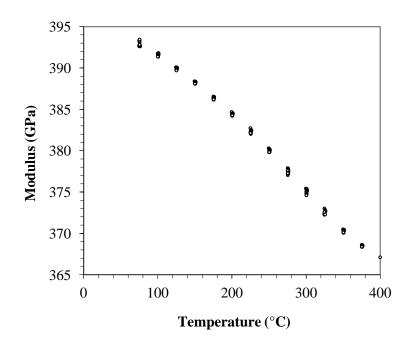

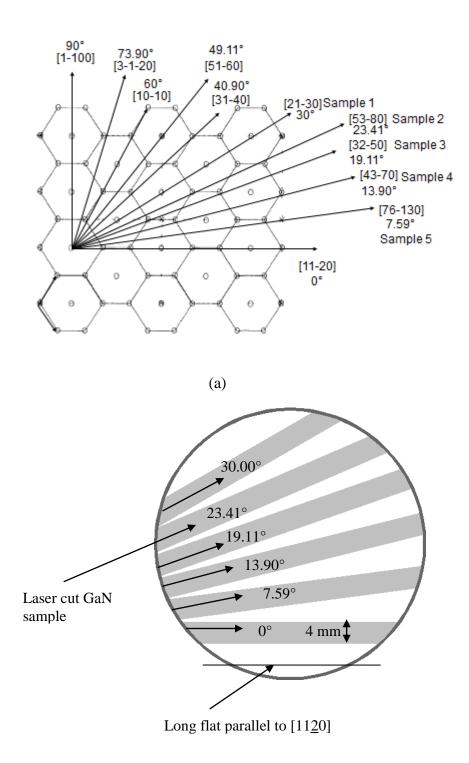

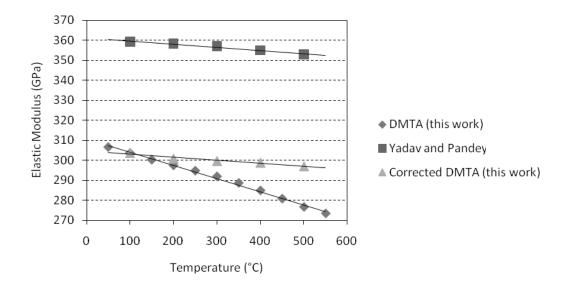

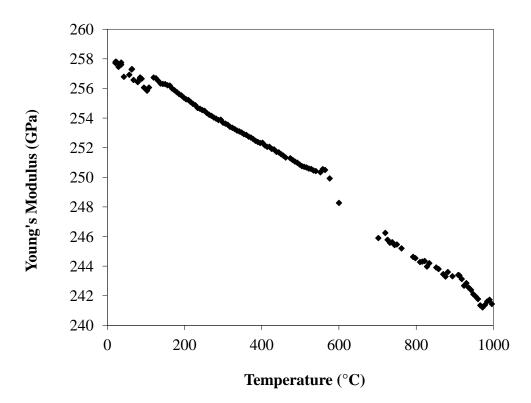

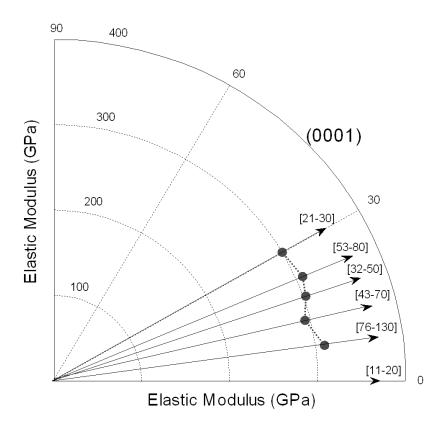

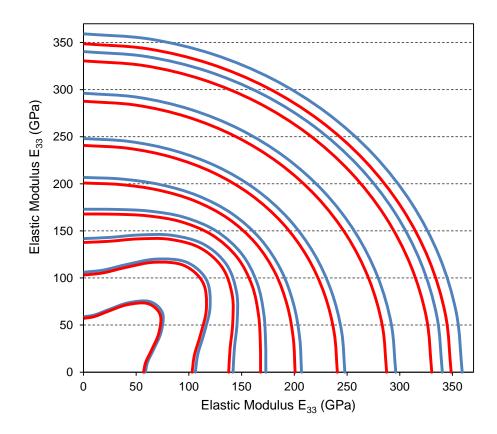

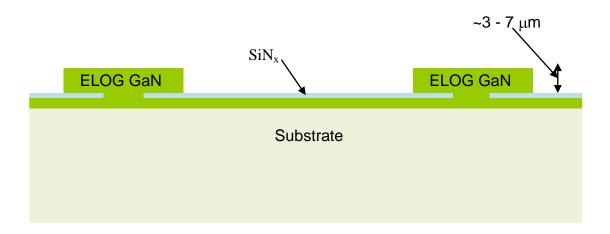

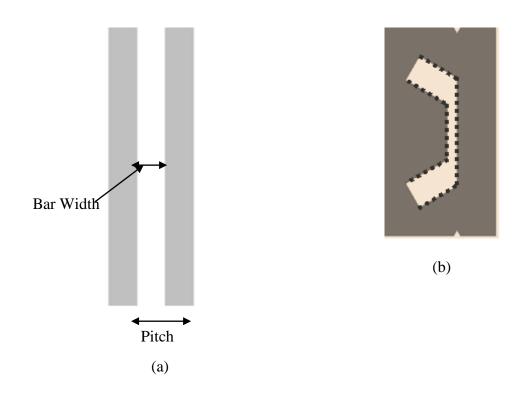

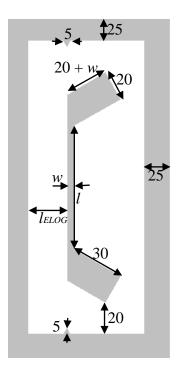

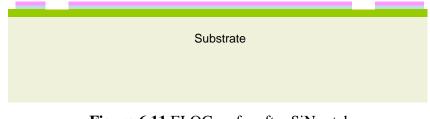

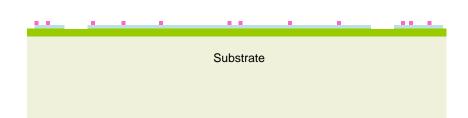

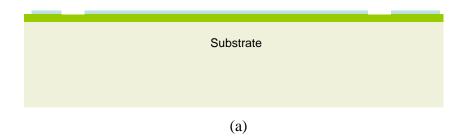

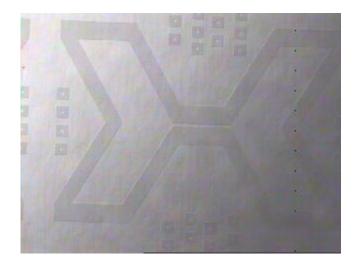

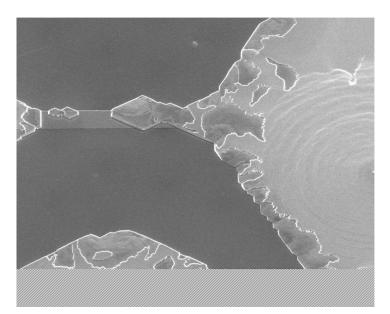

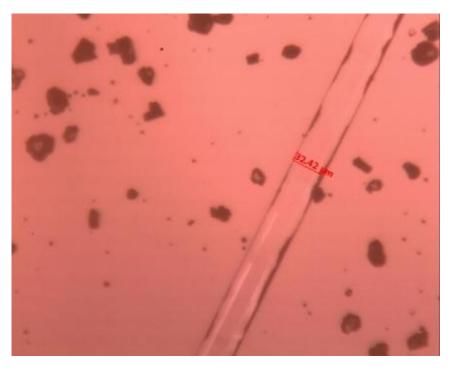

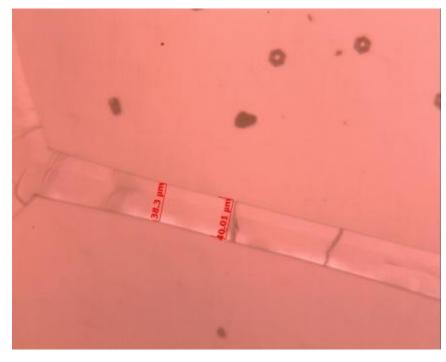

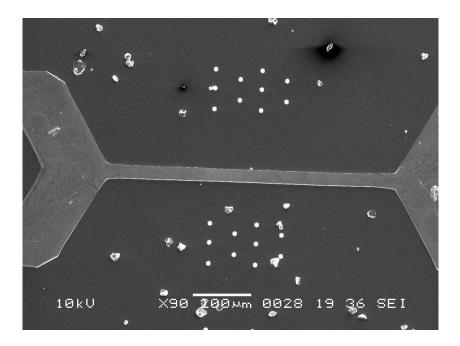

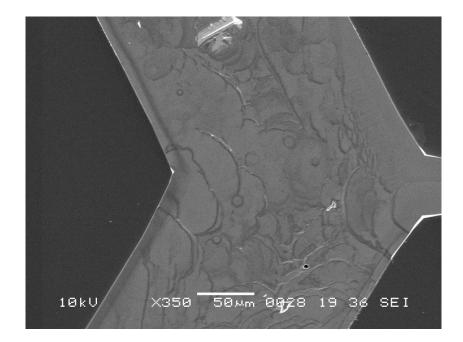

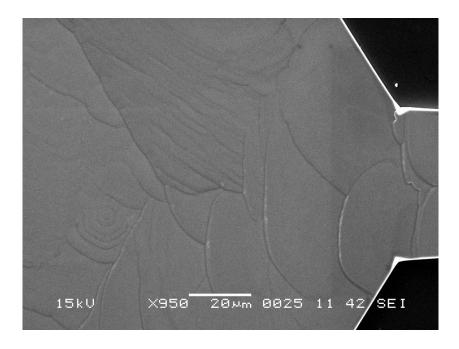

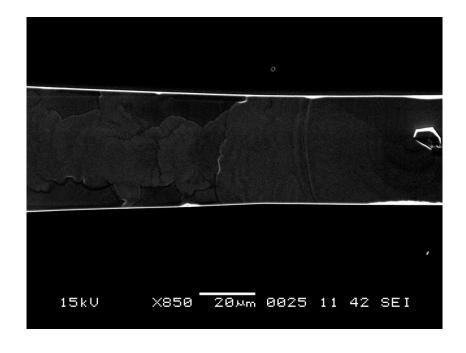

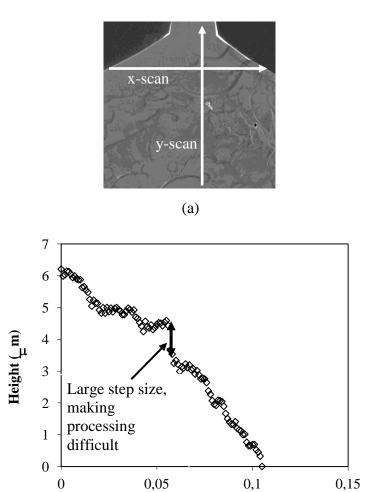

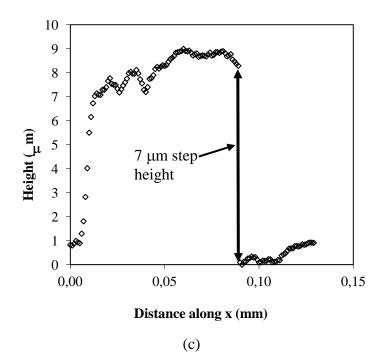

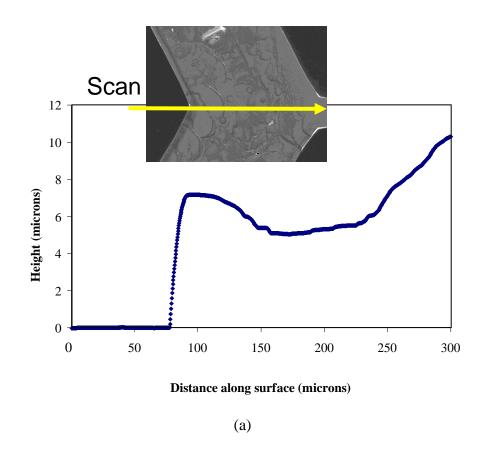

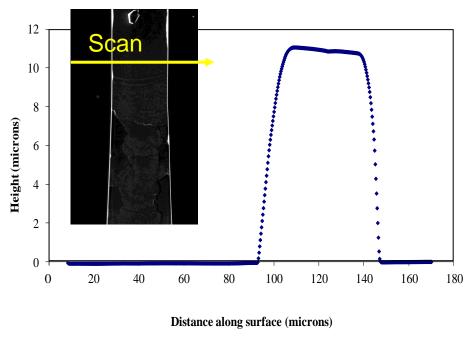

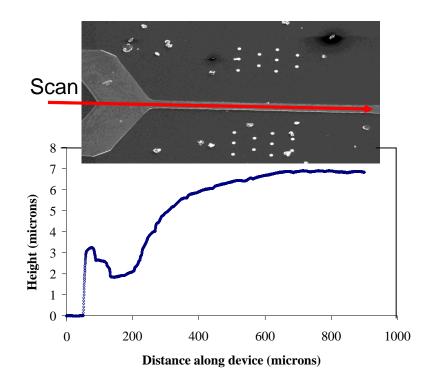

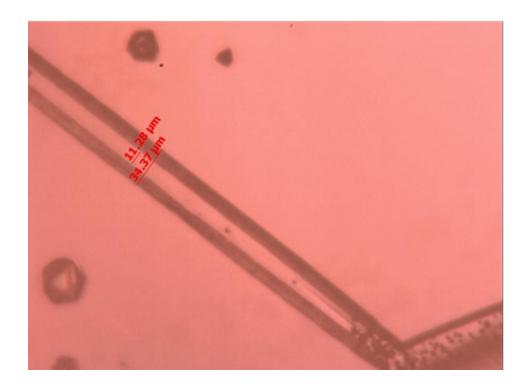

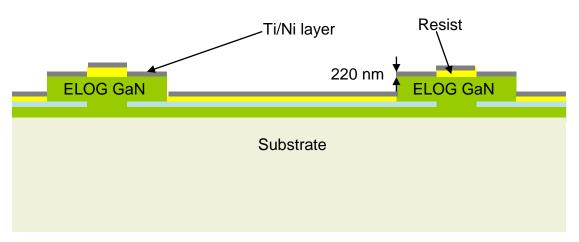

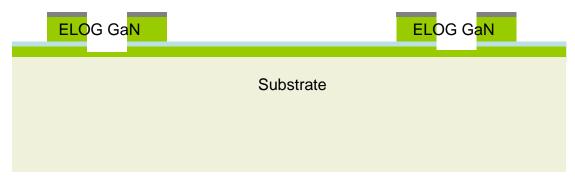

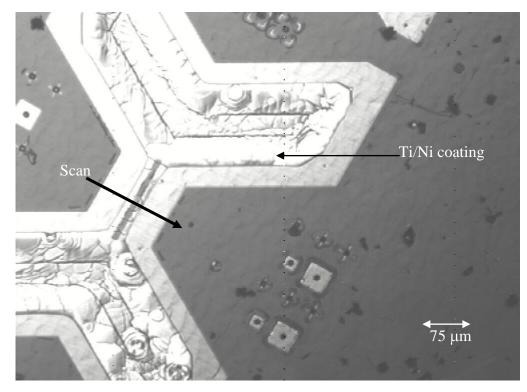

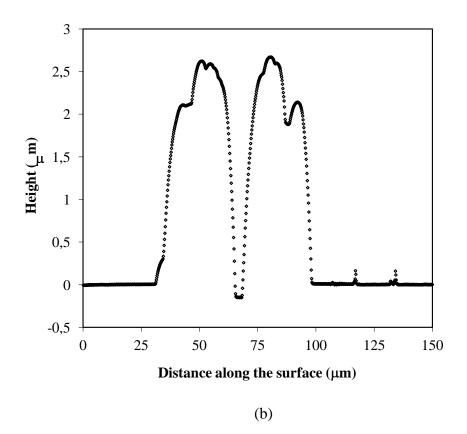

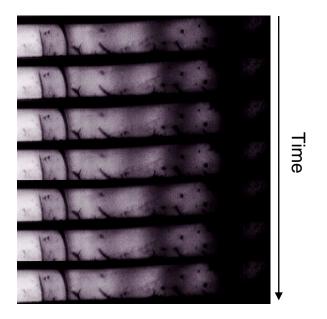

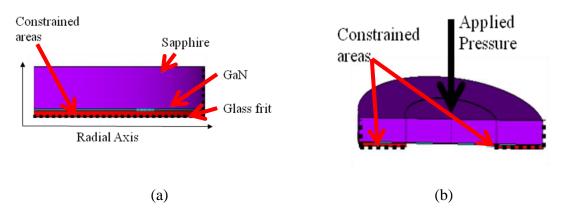

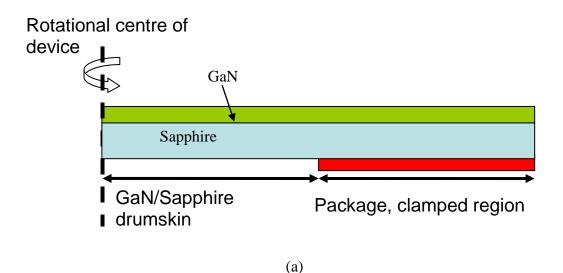

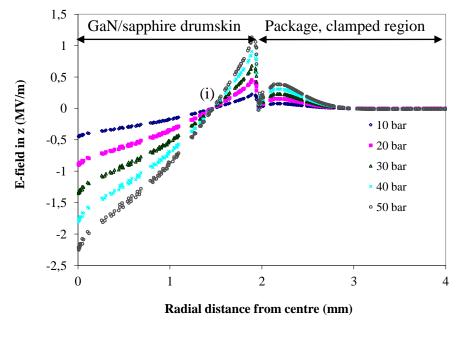

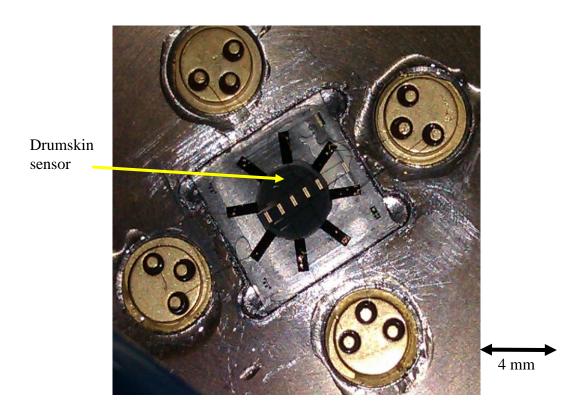

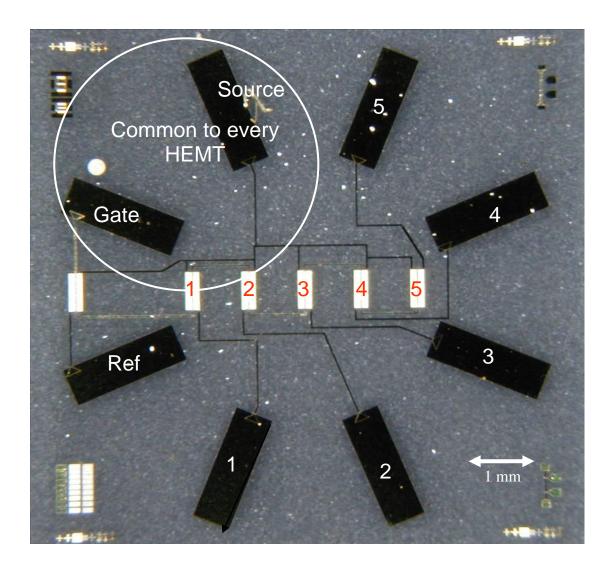

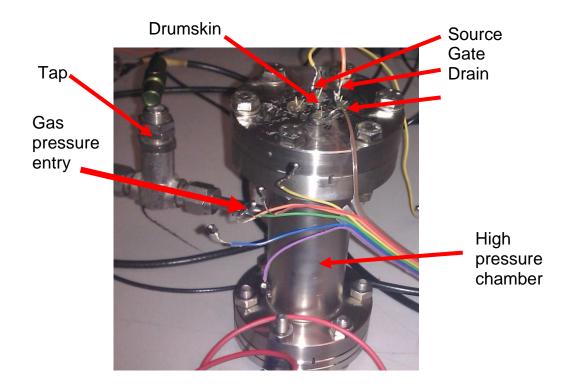

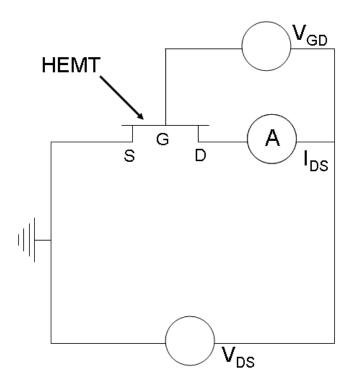

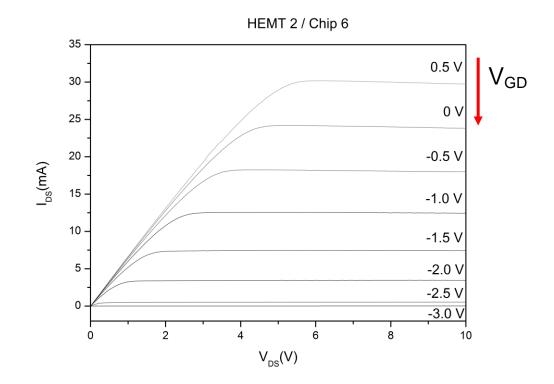

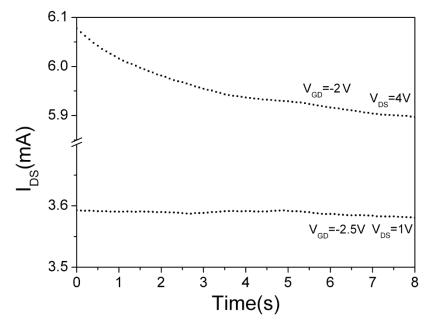

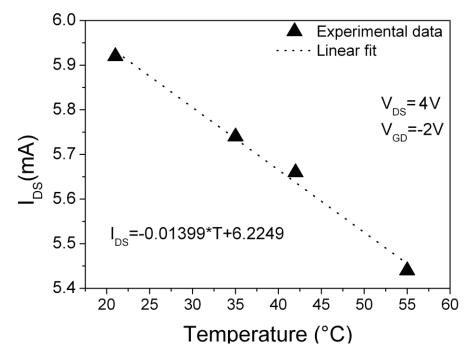

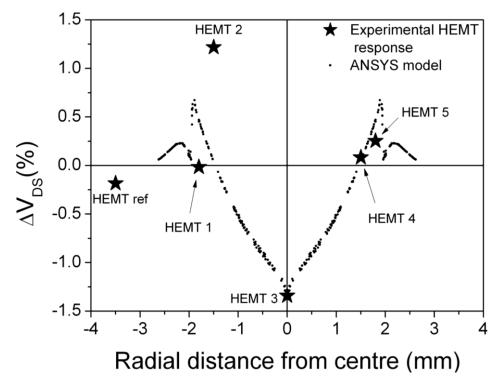

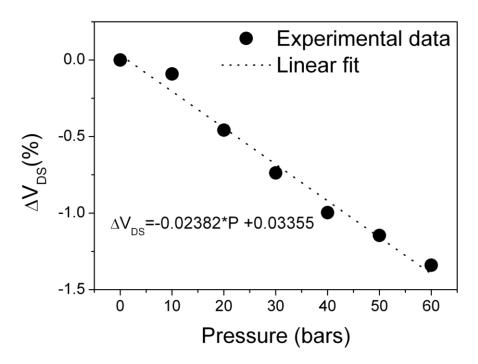

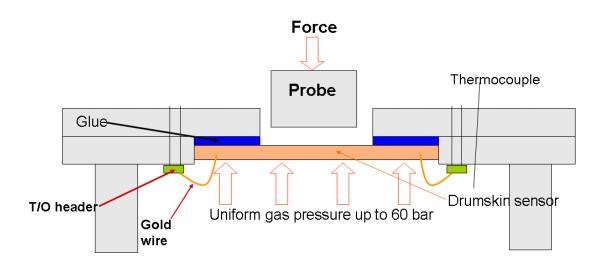

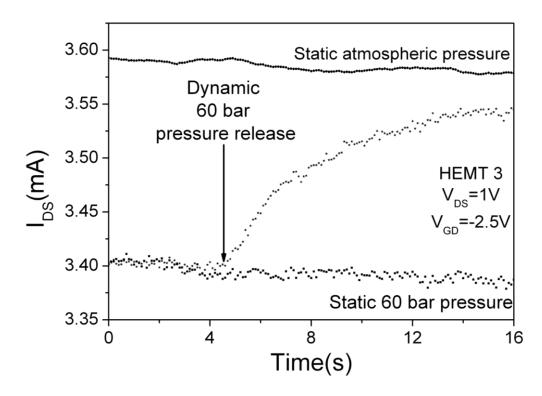

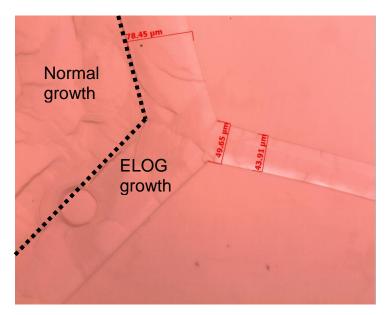

The IV curve shown in figure 1.5 is fairly typical for an AlGaN/GaN HEMT. Every  $I_{DS}$ - $V_{DS}$  curve shown for each respective  $V_{GS}$  firstly consists of a linear region, where