### Verilog-A compact modelling of SiC devices with Qucs-S, QucsStudio and MAPP/Octave FOSS tools

Mike Brinson<sup>1</sup>, mbrin72043@yahoo.co.uk.

$^1\mathrm{Centre}$  for Communications Technology, London Metropolitan University, UK

Presented at IEEE EDS DL Mini-Colloquium, Gdynia, Poland, 20 June 2018

#### An outline of compact device modelling tools implemented by FOSS tools:1

| Simulator      | Simulation and output<br>commands                                                                                                                                                                                                                                                       | Components/models                                                                                                                   | Modelling features                                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Berkeley SPICE | .OP, .DC, .TF, .AC, .TRAN, .NOISE.,<br>.DISTO, .PZ, .SENS, .SAVE, .PRINT,<br>.PLOT, .FOUR, .SUBCKTENDS<br>Berkeley Nutmeg simulation data<br>post processor.                                                                                                                            | R, C, L, M, S, W, V, I, T, LTRA, U, URC,<br>D, BJT, J, M, Z, B                                                                      | 1. Fully expanded circuits,<br>2. Subcircuits <sup>4</sup> , 3. Macromodels <sup>8</sup> ,<br>4. C compiled code models <sup>C</sup> . |

| Qucs           | DC, AC, transient, harmonic<br>balance <sup>0</sup> , Parameter sweep,<br>equations, S-parameter analysis,<br>Qucs and Octave post simulation<br>data processors. Noise analysis.<br>Optimization.                                                                                      | Similar to Berkely SPICE plus<br>RF component and device models,<br>VHDL and Verilog Digital models.                                | 1., 2. and 3. the same as SPICE,<br>4. EDD and RFEDD behavioural modelling<br>5. Verilog-A code models <sup>E</sup> .                  |

| QucsStudio     | DC, AC, transient, harmonic<br>balance (including large signal AC<br>and noise), equations, 5 parameter<br>analysis, ducs and Octave post<br>simulation data processors,<br>Parameter sweep, transient<br>shooting method periodic steady-<br>state simulation, Monte Carlo<br>analysis | Similar to Berkely SPICE plus<br>RF component and device models,<br>VHDL and Verilog Digital models.<br>Communication system models | 1., 2. and 3. the same as SPICE,<br>4. EDD and RFEDD behavioural modelling<br>5. Verilog-A and C++ code models <sup>E</sup> .          |

#### NOTES

- A : Linear and non-linear device models based on subcircuits.

- B: Linear and non-linear device models constructed from existing component models.

- C: SPICE C code model API.

- D: Incomplete single tone Harmonic Balance simulation feature.

- E : ADMS Verilog-A compact modelling feature with "Turn-key" capabilities.

### An outline of compact device modelling tools implemented by FOSS tools:2

#### NOTES:

- 1. Qucs-S allows the selection of the simulation engine to use.

- 2. Available simulation components depends on the simulation engine chosen.

- 3. Users may select either Qucs-S or Octave post-processing of simulator data.

# Qucs-S, QucsStudio and Xyce/MAPP/VAPP/VAlint Verilog-A Compact modelling tools

1. Qucs-S allows the selection of the simulation engine to use.

0 - X

- 2. Available simulation components depends on the simulation engine chosen.

- 3. Users may select either Qucs-S or Octave post-processing of simulator data.

- 4. Berkeley MAPP/VAPP and VaLint requires that Octave 4.0 or greater is installed.

Building compact device models: specify the physical properties of a device as a set of equations and parameters: introductory example - the static and dynamic device properties of a semiconductor diode

• This choice of device is deliberate because its properties are well known, making the operation of the modelling tools easier to follow and understand.

• (1) Non-linear static ld-Vd characteristics :

$$Id = IST2 \cdot (exp(Vd/(N \cdot Vt(T2)))) - 1.0) + GMIN \cdot Vd, \text{ where}$$

$$Vd = V(Anode, Cathode),$$

$$T1 = TNOM + 273.15,$$

$$T2 = TEMP + 273.15,$$

$$Vt(T2) = (k \cdot T2)/q,$$

$$IST2 = IS \cdot AREA \cdot (T2/T1)^{XTN/N} \cdot exp(-Eg(300)/Vt(T2)),$$

$$Eg(T) = Eg - (7.02e - 4 \cdot T \cdot T)/(1108.0 + T), \text{ here}$$

$$k \text{ is the Boltzmann constant and } q \text{ the elementary charge. Other physical}$$

$$parameters have their usual meaning: AREA = 1, N = 1, IS = 1e - 14,$$

$$XTI = 3.0, Eg = 1.16, TNOM = 26.85, TEMP = 26.85 \text{ and } GMIN = 1e - 9.$$

#### Building compact device models with Qucs-S: continued

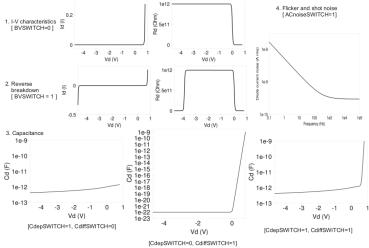

- (2) Reverse breakdown voltage : device model with Qucs-S Equation-Defined Devices (EDD)

K2 = 1.0/(N · Vt(T2)), K5 = N · Vt(T2), IBVEFF = IBV · AREA IDBV = -IST2 · (limexp(-BV · K2) 1.0), BVEFF = (IBVEFF > IDBV)?BV K5 · In(IBVEFF / IDBV) : BV, Id = -IST2 · (limexp(-(BVEFF Vd) · K2) 1.0 + BVEFF · K2), where the breakdown physical parameters have their usual meaning: BV = 4.5, and IBV = 1e 3.

- (3) Semiconductor diode depletion charge :  $Qdep = (Vd \ge 0.0)?CJ0T2 \cdot (Vd + P11 \cdot Vd \cdot Vd) : P6 \cdot (1 - (1 - Vd/JT2)^{P7}),$ where  $CJ0T2 = CJ0 \cdot AREA, P11 = M/(2 \cdot VJ), P6 = (CJ0T2 \cdot VJT2)/P7,$  P7 = 1 - M, and  $VJT2 = (T2 \cdot VJ)/T1 - 2 \cdot Vt(T2) \cdot ln(T2/T1)^{1.5} - ((T2 \cdot Eg(T1)/T1) - Eg(T2),$ where the depletion capacitor physical parameters have their usual meaning: CJ0 = 1e - 12, VJ = 1.0 and M = 0.5.

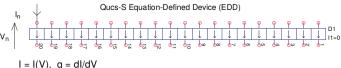

# Building compact device models with Qucs-S: compact device modelling with Equation-Defined Devices (EDD)

$\begin{array}{l} I = I(V), \ g = dI/dV \\ Q = Q(V,I), \ C = dQ/dV = \partial Q(V)/\partial V + \partial Q(I)/\partial I \cdot g, \ where \\ \text{the current flowing in branch } n \ \text{is } I_n = I(V_n) + d/dt(Q_n), \ \text{and } 1 <= n <= 20. \end{array}$

- EDD is a multiterminal nonlinear component with branch currents that can be functions of EDD branch voltage, and stored charge that can be a function of both EDD branch voltages and currents

- · EDD is similar, but more advanced to the SPICE 3f5 B type I or V controlled sources

- EDD can be combined with conventional circuit components and Qucs-S equation blocks when constructing compact device models and subcircuit macromodels

- EDD is an advanced component, allowing users to construct prototype experimental models from a set of

equations derived from physical device properties

- · EDD operator d/dt is undertaken internally by Qucs-S

- Qucs-S EDD can have a maximum of 20 two terminal branches

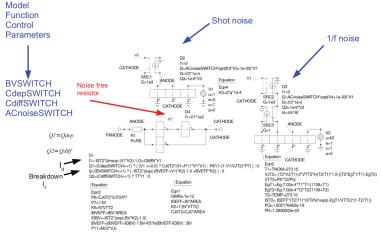

Building compact device models with Qucs-S: compact device modelling with Equation-Defined Devices (EDD). Diode static and dynamic models plus noise

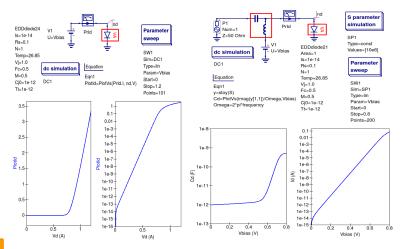

# Building compact device models with Qucs-S: compact device modelling with Equation-Defined Devices (EDD). Typical test data

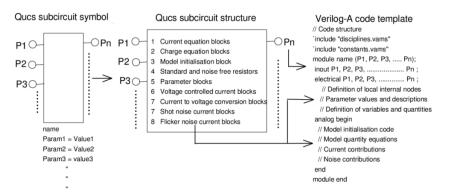

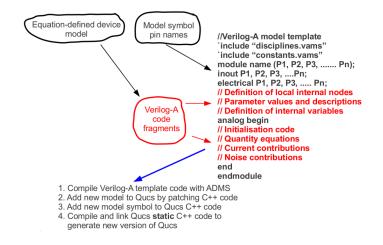

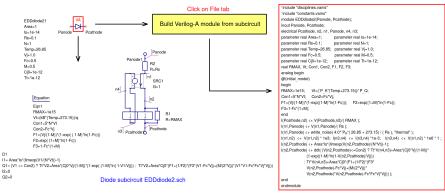

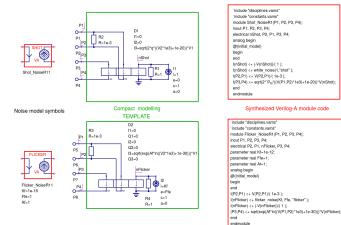

# Building compact device models with Qucs-S: generating Verilog-A compact device models

The following diagram illustrates the initial stage in the construction of a Ques Verilog-A compact device model.

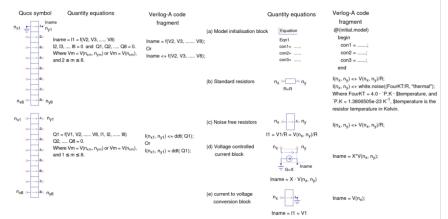

# Building compact device models with Qucs-S: relationships between schematic symbols and Verilog-A code fragments

#### Fundamental EDD blocks

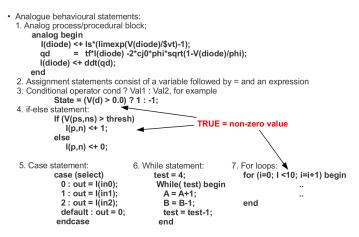

# Building compact device models with Qucs-S: MOT-ADMS - introduction to the basic available Verilog-A subset

#### The MOT-ADMS software is supplied with little documentation! These brief notes provide a basic introduction to the MOT-ADMS Verilog-A subset

- · Verilog-A is a case sensitive language

- Comments: single line comments start with *II*, block comments begin with *I\** and end with *\*I*

- Identifiers are sequences of letters, digits, dollar signs '\$' and the underscore '\_'; the first letter of an identifier must not be a digit

- MOT-ADMS version 2.30 keywords: parameter, aliasparameter, aliasparam, module, endmodule, function, endfunction, discipline, potential, flow, domain, ground, enddiscipline, nature, endnature, input, output, inout, branch, analog, begin, end, if, while, case, endcase, default, for, else, integer, real, string, from, exclude, inf, INF

- Compiler directives: `define,`undef, `ifdef, `else, `endif, `include

- · Data types: integers, reals and strings

- Predefined constants in "constants.vams": `M\_PI, `M\_TWO\_PI, `M\_PI\_2, `M\_PI\_4, `M\_1\_PI, `M\_2\_PI, `M\_2\_SQRTPI, `M\_E, `M\_LOG2E, `M\_LOG10E, `M\_LN2, `M\_LN10, `M\_SQRT2, `M\_SQRT1\_2, `P\_Q, `P\_C, `P\_K, `P\_H,`P\_EPS0, `P\_U0, `P\_CELSIUS0

- Variables are named objects that contain a value of a particular type. They are initialised to zero or unknown. They retain their value until changed by an assignment statement.

# Building compact device models with Qucs-S: MOT-ADMS - introduction to the basic available Verilog-A subset; continued

- Parameters are declared using statements of the form: parameter integer size=16; parameter real period = 1.0 from (0:inf); parameter integer dir = 1 from [-1:1] exclude 0;

- · Verilog-A natures and disciplines ae listed in file "disciplines.vams"

- · Port, net and node examples in Verilog-A:

module amp(out1, in1); input in1; output out1; electrical out1, in1;

- Branches declared with statement branch (n1,n2) b1;

- Signal access function examples: V(n2), I(n), V(b1), I(b1), V(n,m), I(n,m)

- Current contribution examples:

l(diode) <+ ls\*(limexp(V(diode)/\$vt)-1);

I(diode) <+ ddt(-2\*cj0\*phi\*sqrt(1-V(diode)/phi));

- MOT-ADMS allows an extensive range of Verilog-AMS operators and mathematical functions

- Environmental Functions: \$temperature, \$vt, \$strobe, \$finish, \$given, \$parameter\_given

- Analogue operators: @(initial\_step), @(final\_step), @(initial\_model), @(initial\_instance)

# Building compact device models with Qucs-S: MOT-ADMS - introduction to the basic available Verilog-A subset; continued

8. User defined functions and function calls.

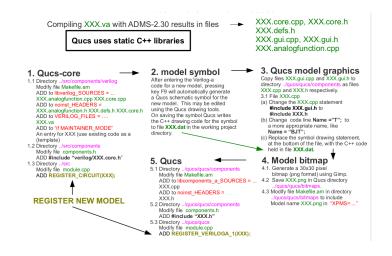

Building compact device models with Qucs-S: generating Verilog-A compact device models; the original Qucs user controlled construction of Verilog-A models using static C libraries

Building compact device models with Qucs: implementing Qucs Verilog-A compact device models with C++ patches; the model REGISTRATION process

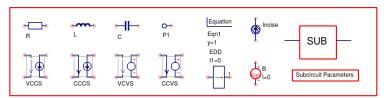

#### Introduction to the Qucs GPL Verilog-A module synthesizer: part I

- The Qucs-S-0.0.20 Verilog-A synthesizer is the latest version of this new open source ECAD tool.

- Generated synthesized Verilog-A code is basic and has to be optimized manually for speed, if required. However, it is expected that in the future its operation will improve as development of the synthesizer progresses.

- The synthesized Verilog-A code can be interchanged by Qucs, QucsStudio, Xyce and Berkeley MAPP/VAPP.

- Synthesized circuits and models can be constructed from the following Qucs-S/SPICE built in components:

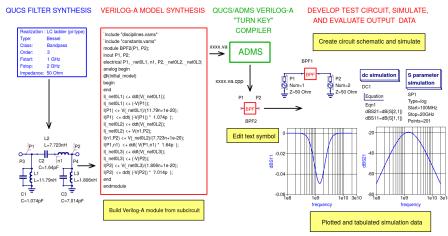

#### Introduction to the Qucs GPL Verilog-A module synthesizer: part II

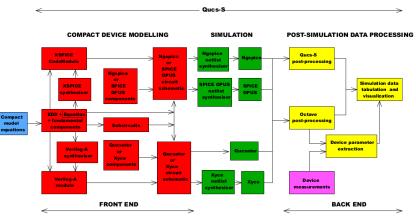

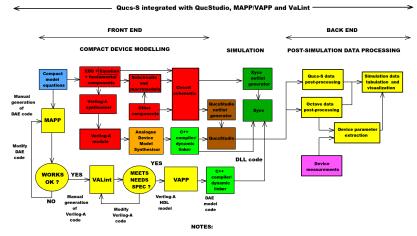

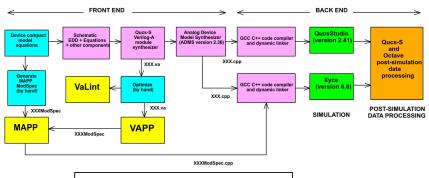

Data flow through the Qucs GPL compact device modelling tool set.

Synthesis of a SPICE like compact semiconductor diode model: static  $I_d$  and dynamic capacitance model plus synthesized Verilog-A module code.

D1

### Introduction to the Qucs GPL Verilog-A module synthesizer: part V

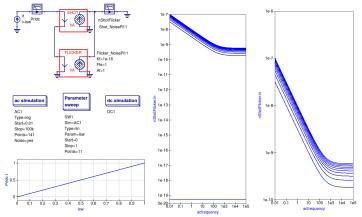

Synthesis of a SPICE like semiconductor diode model: simulated static and dynamic characteristics.

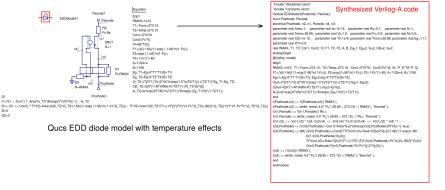

#### Verilog-A synthesis of a SPICE like semiconductor diode model: temperature effects

01

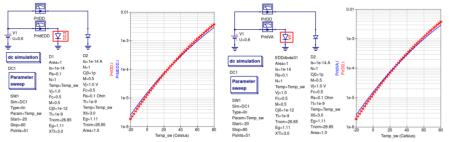

Verilog-A synthesis of a SPICE like semiconductor diode model: simulated  $I_d - V_d$  temperature effects.

Simulation data for Qucs EDD model and built-in diode model Simulation data for Verilog-A model and built-in diode model

Verilog-A synthesis of semiconductor device shot and flicker noise: EDD models and Verilog-A module code.

Verilog-A synthesis of semiconductor device shot and flicker noise: small signal AC domain simulation data.

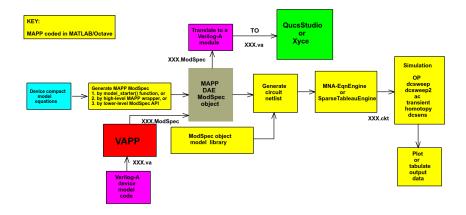

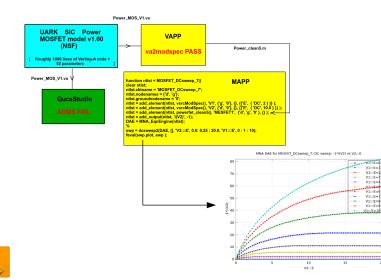

# Building SiC compact device models with Qucs-S, QucsStudio, MAPP/VAPP and Xyce: the model development tool kit

Qucs-S Integrated with QucsStudio, MAPP/VAPP and Xyce

MAPP : The Berkeley Model and Algorithm Prototyping Platform

VAPP : Verilog-A Parser and Processor

VaLint : NEEDS Verilog-A checker

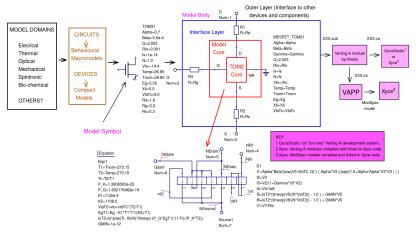

# Building SiC compact device models with Qucs-S, QucsStudio, MAPP/VAPP and Xyce: model structure

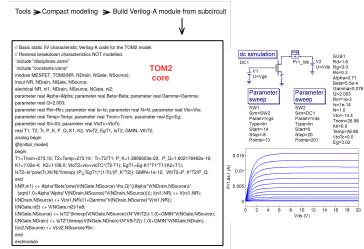

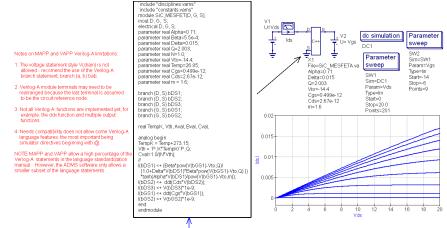

### Building SiC compact device models with Qucs-S, QucsStudio, MAPP/VAPP and Xyce: the development of a fundamental 4H-SiC MESFET "Triquint level 2 (TOM2)" model

en e

### Building SiC compact device models with Qucs-S, QucsStudio, MAPP/VAPP and Xyce: the development of a fundamental 4H-SiC MESFET "Triquint level 2 (TOM2)" model; improvements and limitations

- Improvements: extending, for example, the TOM2 model to improve I/V characteristics, include dynamic model charge properties, add thermal effects and electrical noise is straight forward provided model Verilog-A module code is written in the ADMS Verilog-A subset.

- Limitations: ADMS performance is limited by a number of features; 1. the generated backend differential code is very large leading to poor simulation times, 2. ADMS has node collapsing problems, 3. ADMS is written in XSLT making its code difficult to understand and maintain, 4. ADMS has no support for current branches and 5. very poor documentation.

- Industrial level compact Verilog-A device models are normally written in a much larger subset of Verilog-A, often resulting in model failure when compiled with ADMS.

- Future model development: For industrial grade compact modelling of electrical and multi-physics systems requires a reliable an much improved software tool - hence move Qucs-S compact model development to the Berkeley MAPP and VAPP tools. These have been under continuous development over the last six years as part of the NEEDS NonoHUB project and have been released under the open source GPL licence.

0 - X

### Building SiC compact device models with Qucs-S, QucsStudio, MAPP/VAPP and Xyce: Moving forward - merging MAPP/VAPP and XYCE within the Qucs-S framework

- The release of the advanced Xyce parallel circuit simulator under the GPL licence has made available to the wider compact modelling community a package with significant new simulation facilities.

- By combining the Xyce circuit simulator with the new Berkeley "Modelling and algorithm prototyping platform, under the GPL licence, the available compact modelling tool set has been "future proofed" for the foreseeable future.

- Release of the latest stable version of Qucs-S in October 2017 has triggered work on merging MAPP/VAPP (coupled with Xyce) within the Qucs-S framework.

- The remaining slides in this presentation report on the work done so far to achieve the merger of MAPP/VAPP and Xyce with Qucs-S. An indication of future plans are also introduced and a number of SiC modelling examples are outlined.

for a 4H-SiC MESFET l=lds where

A simplified circuit model

Here, Rds = Ras = 1/GMIN

Differential/Algebraic Equations (DAE)

#### MAPP ModSpec function

ids=lds+d/dt(Cds · Vds) +Vds · GMIN

ias=d/dt(Cas ·Vas) + Vas · GMIN.

$\mathsf{Ids} = (\beta \cdot (\mathsf{Vgs}\mathsf{-}\mathsf{Vto})^{\mathsf{Q}})/(1 + \delta \cdot \mathsf{Vds} \cdot \mathsf{be} \; \mathsf{Vdsta} \cdot (\mathsf{Vgs}\mathsf{-}\mathsf{Vto})^{\mathsf{Q}})) \cdot$ tanh( (g · Vds )/(Vds-Vto)<sup>m</sup> ).

and  $\alpha = 0.71$ ,  $\beta = 5.5e-4$ , Q = 2.003, Vto=-14.4, Cds=2.67e-12, Cqs=0.499e-12, m=1.6, GMIN=1e-9,

In general MAPP model branches, electrical systems, can be represented by

d/dt(q(v)) + f(v) + b(t) = 0

where, nonlinear functions q(v) and f(v) represent the charge andresistive parts of a branch, respectively, and b(t) is an external voltage or current input which is a function of time.

ModSpec files represent objects being modelled in a very general way which allows explicit and implicit formulation with specified inputs and outputs, supports internal unknown quantities and time-varying behaviour.

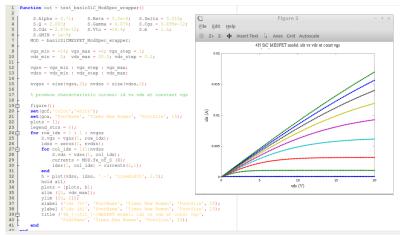

```

function MOD = basicSiCMESEET ModSpec wrapper()

MOD = ee.model();

MOD = add_to_ee_model(MOD, 'terminals', {'d', 'g', 's'});

MOD = add to ee model(MOD, 'explicit outs', {'igs', 'ids'});

MOD = add to ee model(MOD, 'params', {'Alpha', 0.71, 'Beta', 5.5e-4} );

MOD = add to ee model(MOD, 'params', {'Gamma', 0.076, 'Q', 2.003} );

MOD = add to ee model(MOD, 'params', ('Is', 1e-14, 'N', 1.0) );

MOD = add_to_ee_model(MOD, 'params', {'Vto', -14.4, 'Temp', 26.85} );

MOD = add to ee model(MOD, 'params', ('Cds', 2.67e-12, 'Cos', 0.499e-12) ):

MOD = add to ee model(MOD, 'params', {'m', 1.6, 'GMIN', 1e-9} );

MOD = add to ee model(MOD, 'f', @f);

MOD = add to ee model(MOD, 'g', (2g );

MOD = finish_ee_model(MOD);

unction fout = f(S)

v2struct(S):

Aval = (vgs-Vto)Q

Bval = (vgs-Vto)"

ids = ( Beta*Aval/(1.0+Gamma*vds*Beta*Aval) )*tanh(Alpha*vds/Bval) + vds*GMIN:

igs = ygs*GMIN:

fout = [ids; igs];

function gout = g($)

v2struct(S):

ods = Cds*vds

qgs = Cgs*vgs;

gout = [gds; ggs];

```

XU Yue-hang et al., Advanced SPICE- modelling 0f 4H-SiC MESFET's, Journal of Electronic Science and Technology of China, March 2007, Vol. 5 No. 1, pp. 62-65.

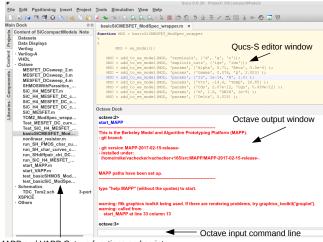

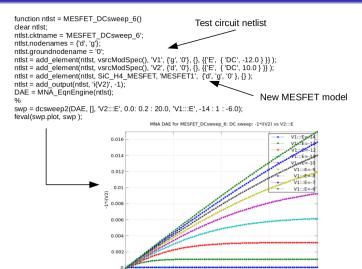

MAPP and VAPP Octave functions and scripts

32 / 40

Verilog-A module code derived from MAPP DAE model.

10

V2:::E

15

20

36 / 40

- Increased integration of Qucs-S with MAPP, VAPP and Xyce.

- Improvements in MAPP support: new component models, better tabular output data and Octave/MATLAB visualization.

- Implementation of Xyce compiled MNA DAE models: Integration of Xyce with MAPP, VAPP and Qucs-S via ModSpec-C++API.

# Verilog-A compact modelling of SiC devices with Qucs-S, QucsStudio and MAPP/Octave FOSS tools: download links

- Qucs-S: Download links The latest stable release is Qucs-0.0.20. It is based on stable release Qucs-0.0.19. Documentation can be found at readthedocs.io. Source tarball qucs-s-0.0.20.tar.gz at Github repository. Debian repository (32 and 64 bit), built with openSUSE OBS: Debian 9 "Stretch", Debian 8 "Jessy", Debian 7 "Wheezy", Ubuntu 14.04 and 16.04. RPM Packages (32 and 64 bit) for CentOS and Fedora-24, 25, and 26. Windows installer (Zipped EXE): qucs-s-0.0.20-setup.zip.

- Xyce: Download and documentation from https://xyce.sandia.gov/.

- MAPP/VAPP: Download from https://github.com/jaijeet/MAPP, see also http://draco.eecs.berkeley.edu/mapptiki/tiki-index.php.

- Octave: https://www.gnu.org/software/octave/.

## Verilog-A compact modelling of SiC devices with Qucs-S, QucsStudio and MAPP/Octave FOSS tools: references; part1 Qucs-S

- Jahn S., and Brinson M., Interactive compact device modelling using Qucs equation defined devices, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, September/October 2008, 21(5), pp 335-349, DOI:10.1002/jnm.676.

- Brinson M., and Jahn, Qucs: A GPL software package for circuit simulation, compact device modeling and circuit macromodeling from DC to RF and beyond, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, July/August 2009, 22(4), pp 207-319, DOI:10.1002/jnm.702.

- Mike Brinson and Michael Margraf, Verilog-A compact semiconductor device modelling and circuit macromodelling with the QucsStudio-ADMS Turn-Key modelling system, International journal of Microelectronics and Computer Science, Vol. 3, No. 1, pp. 32-40, Jan. 2012. ISSN 2080-8755

- Wladek Grabinski, Mike Brinson, Paolo Nenzi, Francesco Lannutti, Nikolaos Makris, Angelos Antonopoulos and Matthias Bucher, Open-source circuit simulation tools for RF compact semiconductor device modelling, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, Volume 27, Issue 5-6, September- December 2014, Pages: 761779, DOI:10.1002/jnm.1973.

- Mike Brinson and Vadim Kuznetsov, A new approach to compact semiconductor device modelling with Ques Verilog-A analogue module synthesis, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, Volume 29, Issue 6 November-December 2016, Pages 10701088, DOI: 10.1002/jnm.2166.

Mike Brinson and Vadim Kuznetsov, Extended behavioural device modelling and circuitsimulation with Qucs-S, International Journal of Electronics, Published online on 29 July 2017. http://dx.doi.org/10.1080/00207217.2017.1357764.

39 / 40

## Verilog-A compact modelling of SiC devices with Qucs-S, QucsStudio and MAPP/Octave FOSS tools: references; part2 Berkeley MAPP/VAPP

- MAPP: A Platform for Prototyping Algorithms and Models Quickly and Easily Tianshi Wang, Aadithya V. Karthik, Bichen Wu, and Jaijeet Roychowdhury (invited paper) in Proceedings of IEEE International Conference on Numerical Electromagnetic and Multiphysics Modeling and Optimization (NEMO), Aug 2015.

- Multiphysics Modelling and Simulation in Berkeley MAPP Tianshi Wang and Jaijeet Roychowdhury in Proceedings of IEEE International Conference on Numerical Electromagnetic and Multiphysics Modeling and Optimization (NEMO), July 2016.

- MAPP: The Berkeley Model and Algorithm Prototyping Platform Tianshi Wang, Aadithya V. Karthik, Bichen Wu, Jian Yao, and Jaijeet Roychowdhury (invited paper) in Proceedings of IEEE Custom Integrated Circuits Conference, Sept 2015.

- Modelling Optical Devices and Systems in MAPP Tianshi Wang and Jaijeet Roychowdhury EECS Department, University of California, Berkeley, Tech. Rep., UCB/EECS-2017-160, Oct 2017.

- Well-Posed Device Models for Electrical Circuit Simulation A. Gokcen Mahmutoglu, Tianshi Wang, Archit Gupta, and Jaijeet Roychowdhury NEEDS: Nano-Engineered Electronic Device Simulation Node Tech. Rep., Mar 2017.

- Further Qucs-S and MAPP/VAPP publications can be found at: 1. MOS-AK Association : http://www.mos-ak.org/, and 2. Nano-Engineered Electronic Device Simulation Node, https://nanohub.org/groups/needs/.