# UNIVERSITY OF THESSALY

## **DIPLOMA THESIS**

# Correlating Workload Behavior with Core Voltage Variability on Modern x86 Architectures with Machine Learning

Author:

Konstantinos KANELLIS

Supervisors: Christos D. Antonopoulos Spyros Lalis

A thesis submitted in fulfillment of the requirements for the degree of Diploma

in the

Computer Systems Laboratory (CSL)

Department of Electrical and Computer Engineering

"The statements of science are not of what is true and what is not true, but statements of what is known with different degrees of certainty."

Richard P. Feynman

#### ΠΑΝΕΠΙΣΤΗΜΙΟ ΘΕΣΣΑΛΙΑΣ

# Περίληψη

Τμήμα Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών

## Διπλωματική Εργασία

Συσχέτιση της συμπεριφοράς εφαρμογών με τη μεταβλητότητα τάσης πυρήνα σε σύγχρονες αρχιτεκτονικές **x86**, με χρήση μηχανικής μάθησης

## Κωνσταντίνος Κανελλής

Οι σύγχρονες αρχιτεκτονικές x86 είναι εξοπλισμένες με έναν καινούργιο μηχανισμό δυναμικής κλιμάκωσης της τάσης και της συχνότητας του επεξεργαστή (Dynamic Voltage Frequency Scaling - DVFS), που ονομάζεται SpeedShift. Ο μηχανισμός SpeedShift προσαρμόζει αυτόματα την τάση τροφοδοσίας του πυρήνα και την συχνότητα του επεξεργαστή, μέσω υπο-βοήθειας υλικού, βάσει των απαιτήσεων της τρέχουσας εφαρμογής. Στην παρούσα διπλωματική εργασία διερευνούμε και αξιοποιούμε τον μηχανισμό αυτό, παρατηρώντας την αλληλπίδραση μιας δυναμικής και χρονικά-μεταβαλλόμενης εφαρμογής με την αρχιτεκτονική πάνω στην οποία εκτελείται. Συλλέγοντας δεδομένα από γεγονότα που συμβαίνουν στην αρχιτεκτονική (hardware events), τα οποία καταγράφουν πως η συμπεριφορά μιας εφαρμογής επηρεάζει δομικά στοιχεία της αρχιτεκτονικής, εξερευνούμε την συσχέτιση τιμών τους με των τιμών της τάσης λειτουργία πυρήνα του επεξεργαστή, για ένα ευρύ φάσμα εφαρμογών. Στην συνέχεια εφαρμόζουμε διάφορους αλγορίθμους μηχανικής μάθησης για να εκτιμήσουμε την τιμή της τάσης λειτουργίας πυρήνα του επεξεργαστή σε οποιαδήποτε χρονική στιγμή. Παρατηρούμε πως κάνοντας χρήση νευρωνικών δίκτυων, τα οποία έχουν εκπαιδευτεί με βάση τους hardware events, πετυχαίνουμε μεγάλη ακρίβεια στις προβλέψεις μας. Εν τέλει, σχεδιάζουμε ένα καινοτόμο εργαλείο που ανιχνεύει και αναλύει αλλαγές μεταξύ των φάσεων εκτέλεσης μιας εφαρμογής, λαμβάνοντας υπόψην την τάσης λειτουργίας πυρήνα του επεξεργαστή, καθώς και μιας μετρικής κλιμακωσιμότητας της εφαρμογής (π.χ. παραγωγική συχνότητα επεξεργαστή), που παρέχεται από τον ίδιο. Το εργαλείο που αναπτύξαμε καταφέρνει να συσχετίσει τις παραπάνω τιμές με το κομμάτι του κώδικα εφαρμογής που εκτελείται, παίρνοντας μετρήσεις του μετρητή προγράμματος (program counter).  $\Delta$ είχνουμε ότι το εργαλείο μας είναι αρχετά αποδοτιχό στο να εντοπίζει τις φάσης μιας εχτελούμενης εφαρμοργής, ενώ η μεθοδολογία που ακολουθείται είναι λιγότερο επεμβατική στο σύστημά μας, η οποία και προκαλεί μονο την μισή επιβάρυνση συγκρίνόμενη με το καλύτερο διαθέσιμο εργαλείο.

### UNIVERSITY OF THESSALY

## Abstract

Department of Electrical and Computer Engineering

Diploma Thesis

# Correlating Workload Behavior with Core Voltage Variability on Modern x86 Architectures with Machine Learning

by Konstantinos KANELLIS

Modern x86 architectures are equipped with a new, hardware-assisted, Dynamic Frequency Voltage Scaling (DVFS) mechanism (i.e. SpeedShift). SpeedShift automatically adjusts the CPU core voltage and frequency values based on the application needs. In this Thesis, we explore and exploit this mechanism in an attempt to obtain useful runtime knowledge, by observing the interaction of the time-varying behavior of applications with the architecture. At first, we explore the correlation between profiled hardware events, which capture certain aspects of the application behavior, with CPU core voltage values, for a wide set of diverse workloads. Then, we leverage supervised machine learning to accurately estimate the CPU core voltage value at any time point, and we experiment with various models. We show that, by using neural networks, it is possible to achieve great accuracy, when the neural networks are trained on hardware events data. Finally, we design a novel online phase detection tool, which utilizes CPU core voltage and a workload scalability metric provided by the architecture itself (i.e. productive frequency), to detect program phase changes. The tool also exploits instruction pointer sampling in order to associate core voltage and productive frequency samples with application context. We show that our tool efficiently discovers program phases, while being less intrusive and having half the overhead compared with the state-of-the-art methodology.

# Acknowledgements

First and foremost, I would like to render my warmest thanks to my supervisor Prof. Christos D. Antonopoulos for giving me the chance to work on intriguing projects that were a perfect match for my interests. His patient guidance and availability were crucial to the completion of this thesis and allowed me to experience first-hand how research is conducted. I would also wish to express my gratitude to my advisor Prof. Spyros Lalis for his valuable comments and key suggestions throughout all stages of this work.

Additionally, I am more than thankful to the friends, old and new, for all the unforgettable moments we have lived together over the past five years. This place holds a special place in my heart because of you! Moreover, I appreciate all the help from the members of the CSL lab, who provided me with a friendly and fun work environment, and they were always there when I had all sorts of questions.

Finally, I would like to thank my family for their unconditional love, understanding and unwavering belief in me throughout all those years.

# **Contents**

| П  | ερίληψ | η       |                                    | ii  |

|----|--------|---------|------------------------------------|-----|

| A۱ | bstrac | et      |                                    | iii |

| A  | cknov  | wledge  | ments                              | iv  |

| 1  | Intr   | oductio | on                                 | 1   |

|    | 1.1    | Contr   | ibutions                           | 3   |

|    | 1.2    | Thesis  | Structure                          | 3   |

| 2  | Bacl   | kgroun  | d                                  | 5   |

|    | 2.1    | CPU I   | Power Management                   | 5   |

|    |        | 2.1.1   | Power consumption model            | 5   |

|    |        | 2.1.2   | Dynamic Voltage-Frequency Scaling  | 6   |

|    |        |         | P-States                           | 6   |

|    |        |         | C-States                           | 7   |

|    |        | 2.1.3   | Hardware-controlled P-states (HWP) | 7   |

|    |        | 2.1.4   | Performance Boosting Mechanisms    | 9   |

|    | 2.2    | Perf_   | events profiling tool              | 9   |

|    |        | 2.2.1   | Programmable core events           | 10  |

|    |        | 2.2.2   | Fixed-function events              | 12  |

|    |        | 2.2.3   | Shared socket-wide events          | 12  |

|    |        | 2.2.4   | Power-related and thermal events   | 13  |

| 3  | Exte   | nding   | perf_events                        | 14  |

|    | 3.1    | CPU o   | core voltage                       | 14  |

|    | 3.2    | Core I  | Frequency                          | 15  |

|    | 3.3    |         | active Performance                 | 15  |

|    | 3.4    | Proces  | ssor states (C-states)             | 16  |

|    | 3.5    | Variab  | ble Interval Measurements          | 17  |

| 4  | Cap    | turing  | Workload Behavior                  | 19  |

|    | 4.1    | Workl   | oad selection                      | 19  |

|    | 4.2    | Workl   | oad Profiling                      | 19  |

|    |        | 4.2.1   | <u> </u>                           | 19  |

|    |        | 122     | Parf events Sampling Interval      | 21  |

|   | 4.3  | Data Collection, Cl | leaning & Transformation                    | 22 |

|---|------|---------------------|---------------------------------------------|----|

|   |      | 4.3.1 High-Level    | Metrics (HLM) dataset                       | 23 |

|   |      | 4.3.2 All-Metrics   | (AM) Dataset                                | 25 |

|   | 4.4  | Data Cleaning       |                                             | 25 |

|   | 4.5  | Data Transforming   | 5                                           | 26 |

|   |      | 4.5.1 PMU-relate    | ed events                                   | 26 |

|   |      | 4.5.2 MSR-related   | d events                                    | 26 |

| 5 | Data | Analysis            |                                             | 28 |

|   | 5.1  | Data Visualization  |                                             | 28 |

|   |      | 5.1.1 Workload E    | Events Behavior                             | 28 |

|   |      | 5.1.2 Core Voltag   | ge Behavior                                 | 30 |

|   | 5.2  | Correlation Analys  | sis                                         | 32 |

|   |      | 5.2.1 Exploring L   | Linear Correlation                          | 32 |

|   |      | Pearson's P         | Product-Moment Coefficient                  | 32 |

|   |      | Core Voltag         | ge - Hardware Events Correlation            | 33 |

|   |      | 5.2.2 Exploring N   | Non-Linear correlation                      | 35 |

|   |      | Spearman's          | s Rank Correlation Coefficient              | 35 |

|   |      | Core Voltag         | ge - Hardware Events Correlation            | 35 |

|   |      | 5.2.3 Cross-work    | cload Correlation Coefficients Distribution | 37 |

| 6 | Esti | nating CPU Core V   | <sup>7</sup> oltage                         | 39 |

|   | 6.1  | Supervised Machin   | ne Learning Algorithms                      | 39 |

|   |      | 6.1.1 Linear Mod    | dels                                        | 40 |

|   |      | Lasso               |                                             | 41 |

|   |      | Elastic Net         |                                             | 41 |

|   |      | 6.1.2 Tree-based    | Methods                                     | 42 |

|   |      | Decision Tro        | ree (CART algorithm)                        | 42 |

|   |      | Random Fo           | prests                                      | 43 |

|   |      | 6.1.3 Artificial No | eural Networks                              | 43 |

|   |      | Multi-Layer         | r Perceptron                                | 46 |

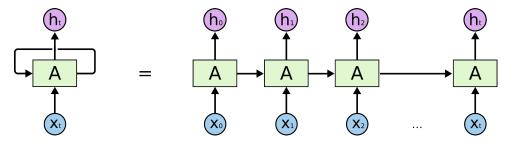

|   |      | Long Short-         | -Term Memory (LSTM) Networks                | 47 |

|   | 6.2  | Data Pre-processin  | ng                                          | 48 |

|   |      | 6.2.1 Data Balanc   | cing                                        | 48 |

|   |      | 6.2.2 Data Norma    | alization                                   | 49 |

|   | 6.3  | Model Parameters    |                                             | 49 |

|   |      | 6.3.1 Neural Net    | works                                       | 49 |

|   |      | Activation l        | Function                                    | 49 |

|   |      | Optimizatio         | on method                                   | 50 |

|   |      | Regularizat         | t <mark>ion</mark>                          | 50 |

|   | 6.4  | Model Evaluation    |                                             | 51 |

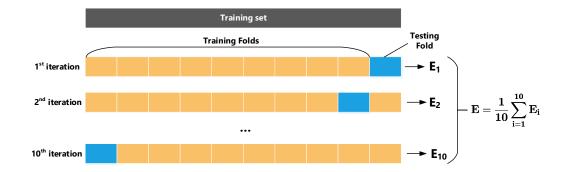

|   |      | 6.4.1 Cross-valid   | lation                                      | 51 |

|   |      | 6.4.2 Loss Functi   | ion                                         | 52 |

| vii |  |

|-----|--|

|     |  |

| 7  | Onl   | ine Pro | gram Phase Detection                      | 58 |

|----|-------|---------|-------------------------------------------|----|

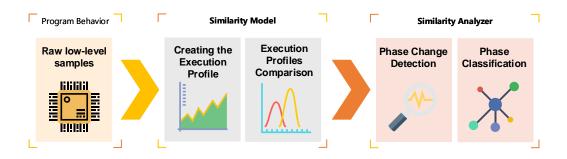

|    | 7.1   |         | ework                                     | 59 |

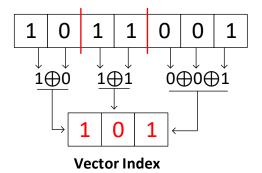

|    | 7.2   |         | tion Frequency Vectors                    |    |

|    | 7.3   |         | pproach                                   |    |

|    |       | 7.3.1   | Sampling                                  |    |

|    |       | 7.3.2   | Execution Profile                         | 62 |

|    |       | 7.3.3   | Histogram Similarity                      | 62 |

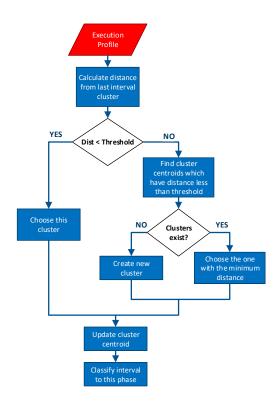

|    |       | 7.3.4   | Phase Change Detection and Classification | 65 |

|    | 7.4   | Integr  | ating application context                 | 66 |

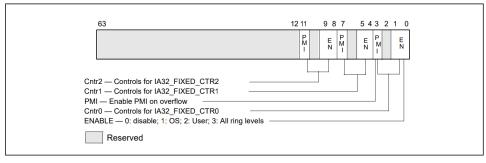

|    | 7.5   | Imple   | mentation                                 | 67 |

|    | 7.6   | Evalua  | ation                                     | 69 |

| 8  | Con   | clusior | 1S                                        | 73 |

| Bi | blioº | raphy   |                                           | 74 |

# **List of Figures**

| 2.1  | Figure 2.1a (left) shows intuitively the impact on the processor power consumption for various P-states. Figure 2.1b (right) shows which |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | HW components are powered-down for each C-state. [7]                                                                                     | 7  |

| 2.2  | Comparison of core voltage behavior between Skylake and Haswell                                                                          |    |

|      | architectures                                                                                                                            | 8  |

| 4.1  | Comparison of core voltage behavior for three representative SPEC2006                                                                    |    |

|      | workloads                                                                                                                                | 22 |

| 5.1  | Time-varying behavior of bzip2 hardware events                                                                                           | 29 |

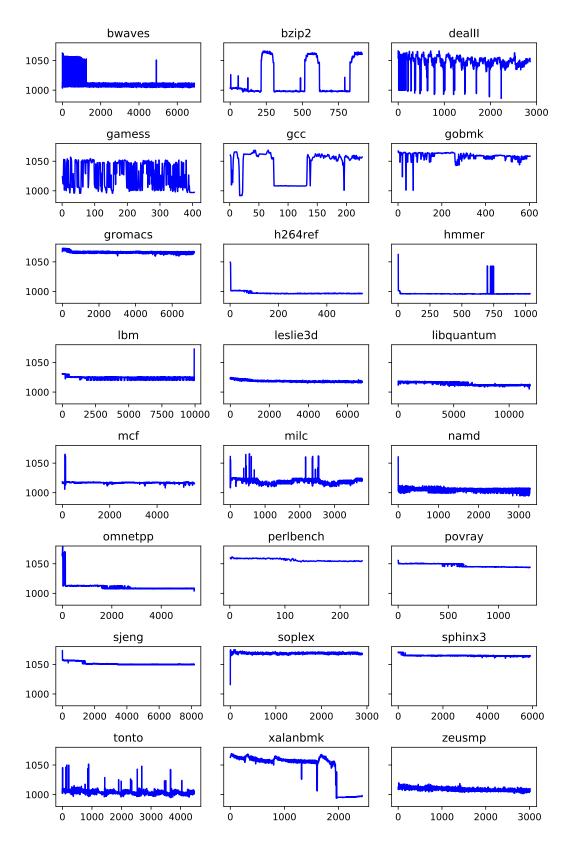

| 5.2  | Core voltage variability for each workload, over time                                                                                    | 31 |

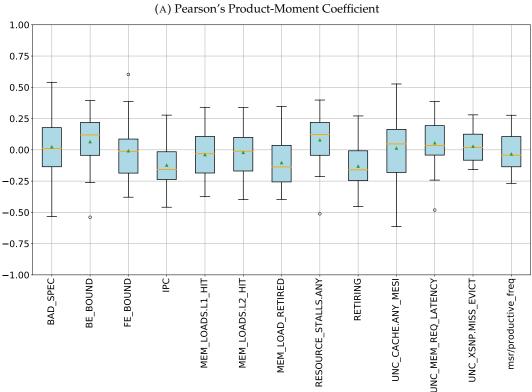

| 5.3  | Pearsons's <i>r</i> correlation coefficient for each hardware event and work-                                                            |    |

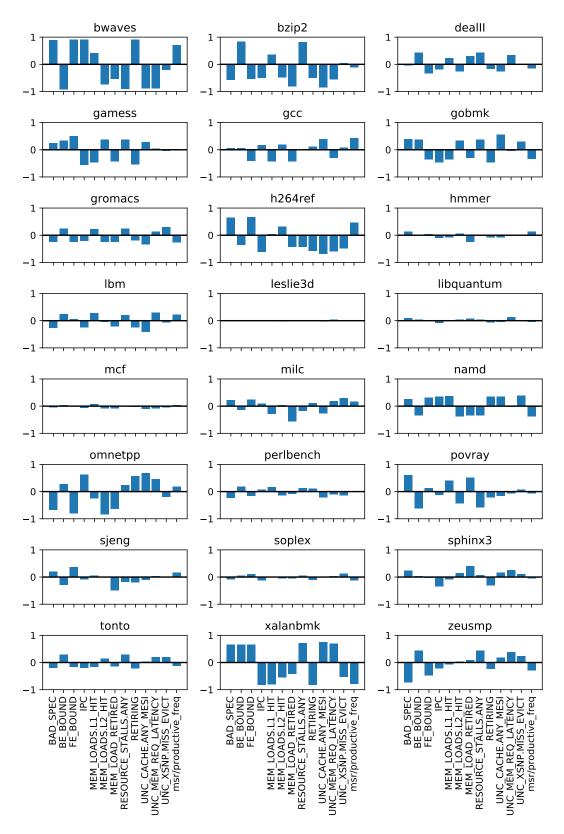

|      | load                                                                                                                                     | 34 |

| 5.4  | Spearman's $r_s$ correlation coefficient for each hardware event and work-                                                               |    |

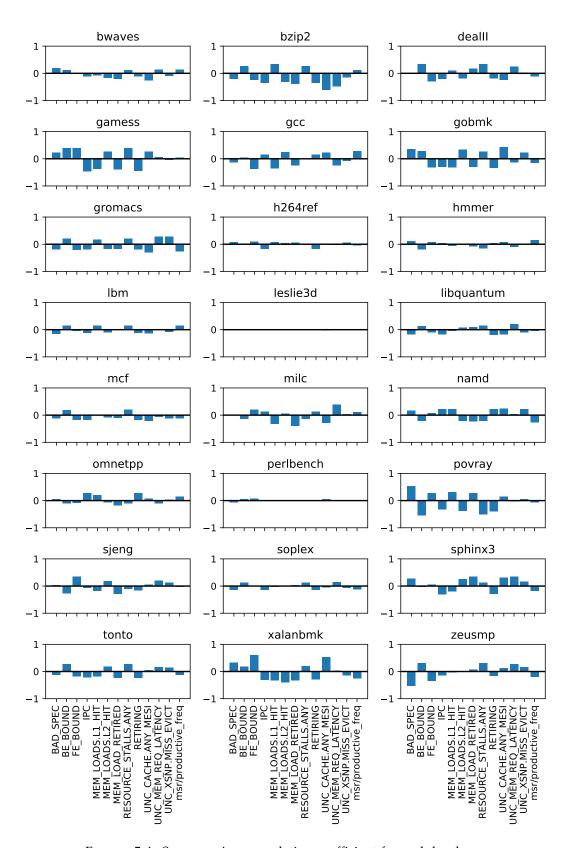

|      | load                                                                                                                                     | 36 |

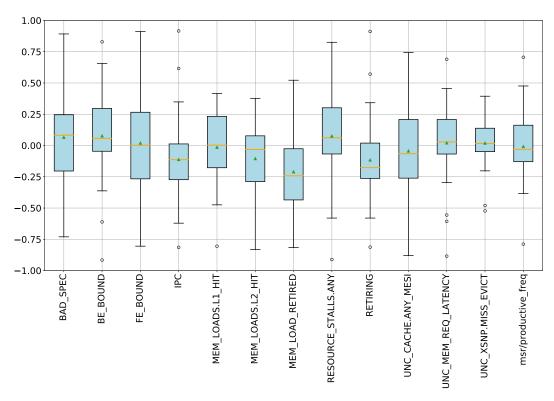

| 5.5  | Boxplots of the Linear (top) and Non-Linear (bottom) Correlation Co-                                                                     |    |

|      | efficient Distribution                                                                                                                   | 38 |

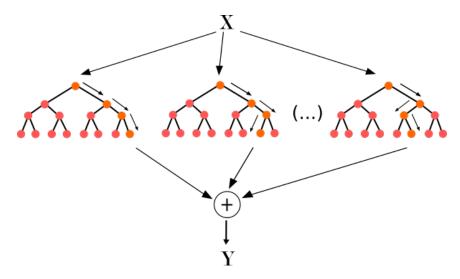

| 6.1  | Random Forest ML algorithm visualization                                                                                                 | 43 |

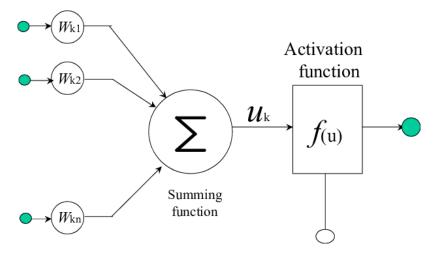

| 6.2  | Components of a neural network processing element                                                                                        | 44 |

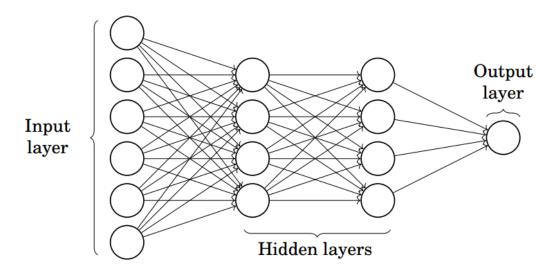

| 6.3  | Visualization of a multi-layer perceptron with two hidden layers                                                                         | 46 |

| 6.4  | Unrolled recurrent neural network                                                                                                        | 47 |

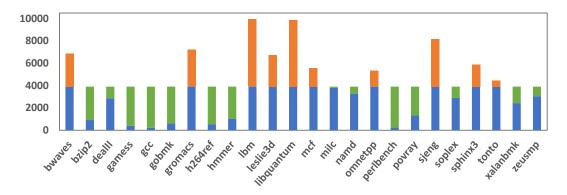

| 6.5  | Number of duplicated/dropped samples per workload. The green                                                                             |    |

|      | bars represent the number of duplicated samples, and the orange bars                                                                     |    |

|      | the number of dropped samples                                                                                                            | 48 |

| 6.6  | 10-Fold Cross-Validation Procedure Visualization                                                                                         | 51 |

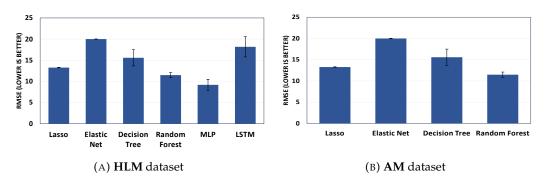

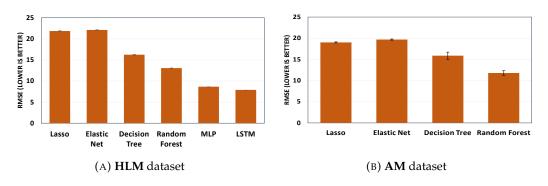

| 6.7  | Voltage estimation accuracy of ML models                                                                                                 | 52 |

| 6.8  | Voltage estimation accuracy of ML models                                                                                                 |    |

|      | (no power events)                                                                                                                        | 53 |

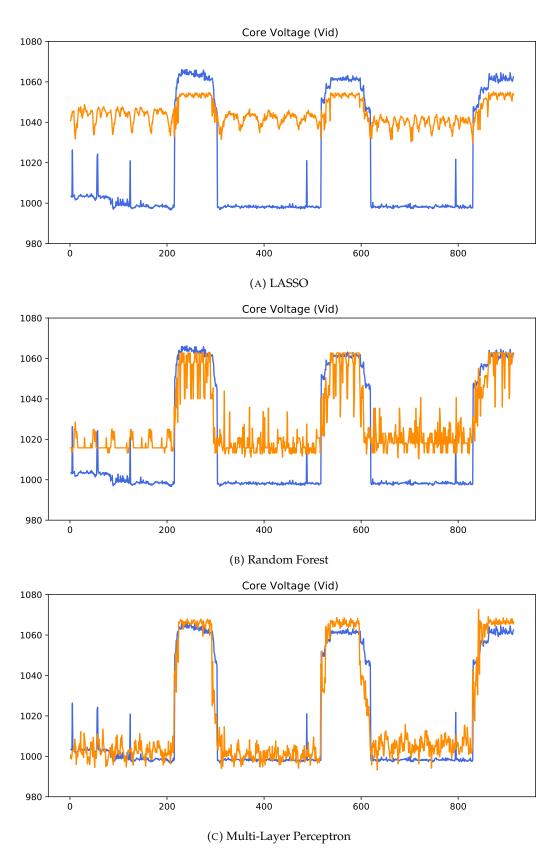

| 6.9  | Core voltage estimation of LASSO, Random Forest and MLP models                                                                           |    |

|      | on bzip2 workload                                                                                                                        | 54 |

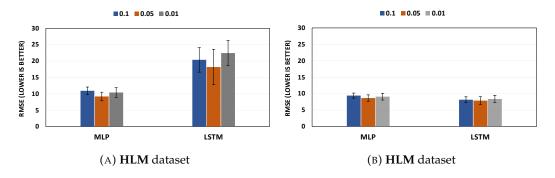

| 6.10 | MLP estimation error with various $L_2$ regularization term values for                                                                   |    |

|      | HLM dataset                                                                                                                              | 55 |

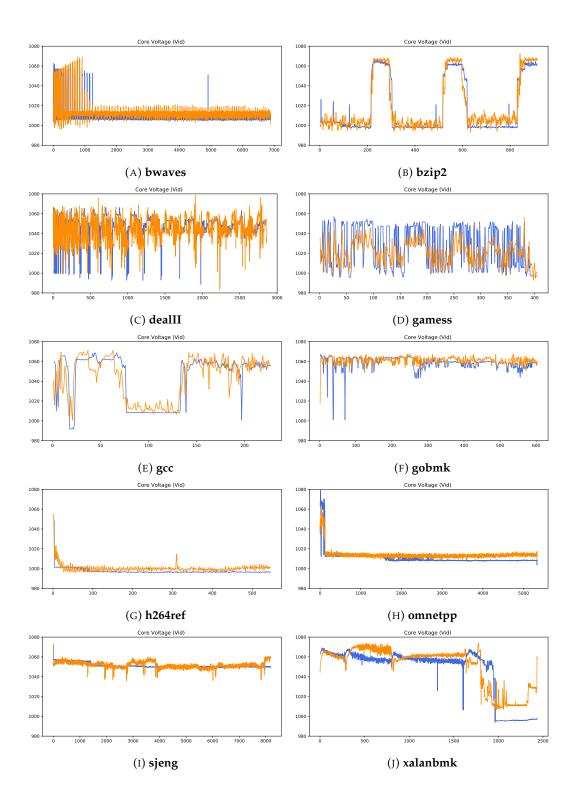

| 6.11 | Voltage estimations made by MLP model trained with $L_2 = 0.05$ , on        |    |

|------|-----------------------------------------------------------------------------|----|

|      | a subset of SPEC CPU2006. X-axis represents samples taken every             |    |

|      | 100ms, while y-axis is the core voltage value                               | 57 |

| 7.1  | Framework for detecting program phases                                      | 59 |

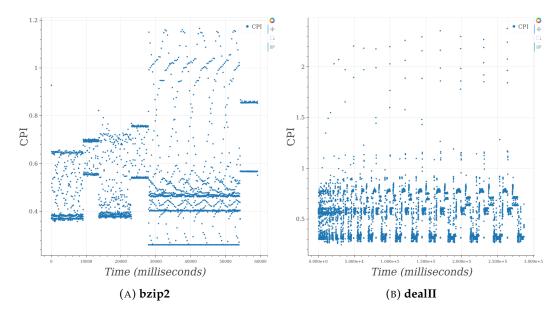

| 7.2  | CPI variability during execution of bzip2 and dealII workloads              | 60 |

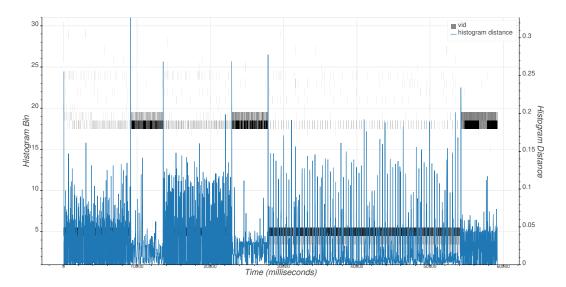

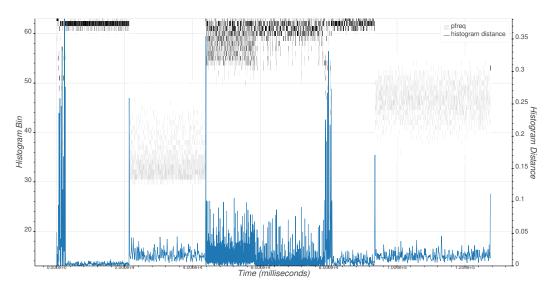

| 7.3  | Histogram dissimilarity values between consecutive interval. Fig-           |    |

|      | ure 7.3a shows the core voltage histograms for the bzip2 workload,          |    |

|      | while Figure 7.3b shows the productive frequency ones for the astar         |    |

|      | workload                                                                    | 64 |

| 7.4  | Phase classification algorithm                                              | 65 |

| 7.5  | Spatial-aware projection                                                    | 66 |

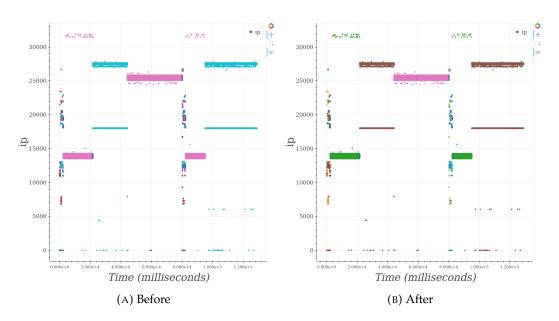

| 7.6  | Classification results before (left) and after (right) integrating applica- |    |

|      | tion context into the method, for astar. Same color denotes the same        |    |

|      | program phase                                                               | 67 |

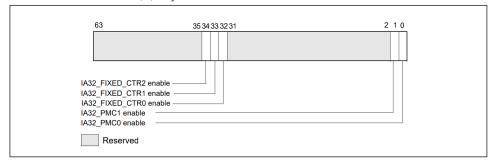

| 7.7  | Layout of MSRs used by the kernel module                                    | 68 |

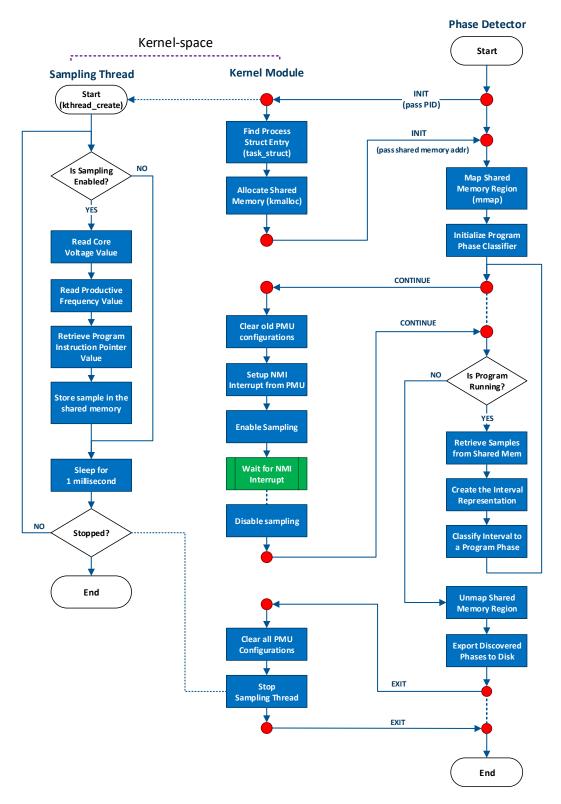

| 7.8  | Workflow of our online phase detection tool                                 | 70 |

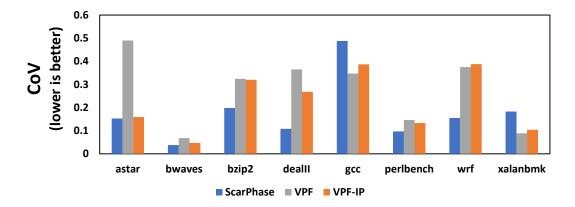

| 7.9  | Homogeneity comparison of program phases discovered                         | 71 |

|      |                                                                             |    |

# **List of Tables**

| 2.1 | Fixed-tunction events in the Skylake architecture                  | 12 |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Pre-defined power / thermal events by perf_events                  | 13 |

| 3.1 | List of registers used for extending perf_events                   | 18 |

| 4.1 | Subset of SPEC CPU2006 workloads used for profiling                | 20 |

| 4.2 | Specifications of the Skylake workstation                          | 21 |

| 4.3 | Total hardware events measured for the HLM dataset                 | 24 |

| 4.4 | Tranformation of gathered events for the <b>HLM dataset</b>        | 26 |

| 5.1 | Characterization of workloads based on the rapidness and intensity |    |

|     | of core voltage fluctuations                                       | 30 |

| 5.2 | Workload Characterization based on the Core Voltage-Performance    |    |

|     | Events Linear Correlation                                          | 33 |

| 7.1 | Core voltage and productive frequency histogram parameters         | 62 |

| 7.2 | Subset of SPEC_CPU2006 workloads used for phase detection          | 69 |

# Listings

| 2.1 | Output of perf list subcommand                                       | 11 |

|-----|----------------------------------------------------------------------|----|

| 3.1 | Sample function implementation in C that returns the core voltage in |    |

|     | millivolts, on SandyBridge (and later) processors                    | 15 |

| 3.2 | Sample function implementation in C that returns the C-states resi-  |    |

|     | dencies percentage on Skylake processors                             | 17 |

| 4.1 | System initial pre-profiling configuration script                    | 20 |

# Chapter 1

# Introduction

In the course of the past 40 years processors have became pipelined to increase the instruction throughput, got equipped with large multilevel caches to hide the memory latency and used advanced techniques (i.e. out-of-order execution) and superscalar designs to exploit Instruction Level Parallelism. These additions, along with the significant advances in semiconductor manufacturing techniques, resulted in tremendous performance improvements, which was generally considered as the limiting barrier at that time. More recently, and in the dawn of the post-*Dennard Scaling* [13] era, power efficiency became the primary concern for computer designers. The introduction of multicore processors partially managed to bypass the performance scaling limitations, while retaining the same power budget. However, the coupling of multiple processing cores on a single die, required the implementation of additional logic to ensure safe concurrent access to shared resources (e.g. Last Level Cache).

This rapid and irregular evolution of microprocessors, driven by the need for performance at first and power efficiency later, led to the development of robust, albeit very complicated architectures. Nonetheless, high-performance workloads should take full advantage of such computing platforms, avoiding at the same time, undesirable performance degradation often caused due to the poor utilization of some part of the processor pipeline (i.e. bottleneck). In addition, Operating Systems (OS) and CPU manufacturers design and implement dynamic software and hardware optimization mechanisms, which try to adjust the processor profile to the needs of the executed workload. However, in order to reach their full potential, these mechanisms need to accurately know the state of the architecture at any point.

Unsurprisingly, different applications have entirely different impact on the utilization of each hardware component. For example, matrix multiplication that consists of many integer (or floating point) operations is limited by the number of CPU arithmetic units. On the other hand, a linear search over a large array will be limited by the bandwidth (and latency) of either the caches or the main memory. Moreover, researchers have shown that large and complex applications consisting of thousands

of lines of code, exhibit time-varying behavior [58], which is attributed to the different code portion that is being executed. This behavior produces a distinct signature at run-time, which if traced and exploited correctly can lead to opportunities for further performance and power optimizations.

In order to get an insight of the effects of their applications on the micro-architecture, programmers use software profilers. A software profiler is a tool that monitors the run-time behavior of an application by gathering interesting program data and events. Examples of popular profilers are *perf\_events* [37], *PAPI* [61] and *Intel VTune* [29]. Most advanced tools (i.e. Intel Vtune) are able to even characterize the application, using for example the *Top-down Microarchitecture Analysis Method* [68] or find possible bandwidth limiting bounds in some architectural component, by applying the *Roofline model* [66].

Software profilers typically run on top of the application they want to monitor. They employ dedicated special-purpose registers, which are located in each CPU core. These registers are called hardware performance counters or Performance Monitoring Units (PMU). Each register can be used to store a specific information (i.e. count or address) from a wide range of low-level hardware events (e.g. branch mispredictions, cache misses, etc.). Periodically and as long as the application is running, the profiler samples these registers and stores their values. Once the application exits, the samples from these low-level raw events can then be combined to extract more useful high-level metrics (e.g. Instructions per Cycle – IPC).

Unfortunately, the use of performance counters restricts the characterization of the application behavior in specific hardware domains, which depend on the events chosen to be measured. Furthermore, it is not possible to record too many hardware events at the same time, as the number of PMUs in each core is limited. In addition, the inter-core contention on shared resources cannot be deciphered efficiently from single core events. One possible way to overcome the previous limitations and acquire a bird's eye view of the behavior of the executed application, is to use aggregated architectural metrics.

Modern x86 architectures, for example Intel Skylake (and later), are equipped with a new power management engine called SpeedShift [50]. SpeedShift is advertised as an autonomous hardware-assisted Dynamic Frequency Voltage Scaler (DVFS). The motivation behind this mechanism is the quicker system response to performance burst requests. Using internal metric collection and on-chip sensors, Speedshift adjusts the CPU frequency and voltage, without any intervention from the OS. It, also, constantly fine-tunes the voltage and frequency values trying to compromise between the energy consumption of the CPU package and the workload performance. Thus, there is an inherent relationship between the workload behavior impact on the architecture and the voltage and frequency values set by this mechanism, at any given time.

### 1.1 Contributions

This thesis focuses on exploring and exploiting the aforementioned relationship, in order to obtain useful runtime knowledge on the time-varying application interaction on the architecture. This knowledge can then be potentially used in conjunction with online decision-making systems in order to apply dynamic software or hardware optimizations.

The contributions from this exploration and exploitation are the following:

- We profile a large subset of SPEC CPU2006 [26] workloads, by sampling both hardware performance events and CPU core voltage and frequency values.

Then, we model those samples as time series and we explore both the linear and non-linear correlation between the two, using statistical methods.

- After having identified some correlation, we leverage supervised Machine Learning (ML) methods to make accurate estimations on the CPU core voltage value based on the values of hardware performance events. We experiment with different ML algorithms and we evaluate their performance.

- Finally, we design and implement an online program phase detection algorithm, which uses the CPU core voltage and frequency values to decide when a change in the program behavior has occurred. By comparing its accuracy and performance overhead with the state-of-the-art [54], we show that our tool accuracy is on par, while having negligible runtime overhead.

#### 1.2 Thesis Structure

The rest of this thesis is organized as follows:

Chapter 2 provides background on the evolution of CPU power management mechanisms and introduces the perf\_events profiling tool, which is capable of monitoring the behavior of an application using various hardware events.

Chapter 3 presents in details the modifications that we made to perf\_events, in order to extend its functionality for unsupported architectural events.

Chapter 4 describes the methodology we following to capture the application behavior, which ultimate led to the creation of two datasets. We explain the two different approaches we followed for selecting the appropriate hardware events, along with the post-collecting data cleaning and transformation processes.

Chapter 5 explores the linear and non-linear correlation between collected hardware events and core voltage values, for each individual workload. In addition, we characterize each workload based on its core voltage behavior.

Chapter 6 focuses on estimating the core voltage value using supervised machine learning models that were trained on specific hardware events . We experiment with diverse ML models and we evaluate their performance on two datasets.

Chapter 7 introduces a novel program phase detection and classification tool that makes use of core voltage and productive frequency values, to discover phase changes. Further, we employ unsupervised learning to efficiently classify different parts of the program execution to distinct phases.

Finally, Chapter 8 concludes this thesis by discussing our key findings and by presenting some directions for future work.

# **Chapter 2**

# Background

## 2.1 CPU Power Management

The physical barriers encountered in the CMOS transistor manufacturing technology, marked the end of low-cost performance scaling. Thus, the research community turned its interest in finding ways to minimize the energy consumption. Nowadays, the power management is an important concern in the design of CPUs. Modern CPUs integrate numerous different mechanisms aimed at maximizing power-savings while trying to minimize performance degradation.

In this section, we present the evolution and the inner-workings of power management techniques that have been implemented on the last few generations of Intel processors. Then, we give an overview of the set of the latest enhancements that constitute the SpeedShift technology, which we aim to exploit.

### 2.1.1 Power consumption model

The goal of the CPU power management mechanism is to reduce the power consumption of the processor. The CPU power consumption can be split in two parts: static power and dynamic (or switching) power, as follows:

$$P_{CPU} = P_{dyn} + P_{static}$$

where  $P_{static}$  is the power required just to keep the CPU on, and  $P_{dyn}$ , which reflects the consumption due to the activity of CPUs logic gates, and depends on the running workload. Dynamic power  $P_{dyn}$  is the dominant factor in this equation as it accounts for the majority of the CPU total power consumption. The dynamic power of CMOS transistors can be approximately modeled [43] as:

$$P_{dyn} = aCV^2 f$$

where *C* is the switching capacitance, *V* is the voltage, *f* is the frequency and *a* is the activity factor (i.e. average number of transistor switching events). The key takeaway here is that the CPU power consumption is proportional to the frequency, and to the square of the voltage. Thus, by lowering just the voltage it is possible to get significant power gains, without generally affecting the performance. This is not the case with frequency though, where lower values bring some power gains but often result in longer workload execution times.

## 2.1.2 Dynamic Voltage-Frequency Scaling

Before the CPUs were equipped with Dynamic Voltage-Frequency Scaling (DVFS) mechanisms, they used constant voltage and frequency operation points. These adaptive mechanisms allowed for opportunistic adjustments of both voltage and frequency, especially when the full computational power of the processor is temporarily not needed. In order to ensure the stability of the CPU, however, a change on the CPU frequency is accompanied with an appropriate CPU voltage change.

The Intel SpeedStep technology [51] released in 2002 (with the Prescott 6 series), and AMD Cool'n'Quiet in 2003, were the first DVFS implementations for consumer desktop processors. These mechanisms depend on the operating system to find the optimal power configuration, based on the current system load. This is achieved using CPU utilization statistics (i.e. APERF & MPERF registers) provided by x86 platform [39]. Then, the OS applies the optimal configuration using the Advanced Configuration and Power Interface (ACPI), which relies on the P-states and C-states (explained below). The above process is repeated periodically (every few 10s of milliseconds), as the CPU load can change continuously (e.g. new process is spawned, process switch to sleep state, etc.). In the Linux kernel, this mechanism is implemented under the cpufreq infrastructure [65].

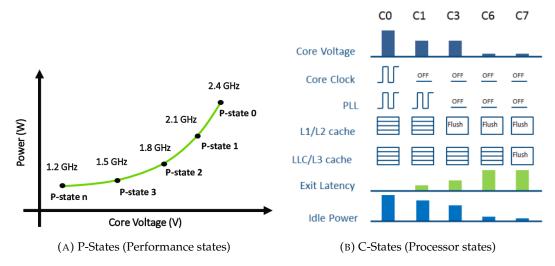

#### **P-States**

Depending on the current workload requirements, a CPU can operate at different discrete voltage-frequency levels called **P-States** (Performance States). Generally P0 is the highest state (i.e. maximum performance), while Pn is the lowest one (i.e. maximum power-saving). Each intermediate state (e.g. P1, P2 and so on) saves additional power, but at the same time adds an extra penalty to the CPU performance. Figure 2.1a shows graphically the impact of different P-states at the total power consumption of the CPU.

FIGURE 2.1: Figure 2.1a (left) shows intuitively the impact on the processor power consumption for various P-states. Figure 2.1b (right) shows which HW components are powered-down for each C-state.

#### **C-States**

In contrast to P-States, which are design to optimize power consumption under workload execution, C-states (Processor states) are used to reduce power consumption when the processor is in idle mode (i.e. nothing is executed). At a C-state (other than CO), unused hardware parts are powered down to save energy seeing that no workload needs them. Each CPU core can operate on a different C-state which brings further power savings for single-threaded workload. Figure 2.1b illustrates which hardware components are powered-down under each C-state. Finally, it is worth mentioning that P-states are relevant only in the presence of the CO state, as the core clock is active only in that state.

The latest microarchitectures (i.e SandyBridge/Haswell/Broadwell) brought additional power and performance improvements, as these DVFS technologies were further optimized (i.e. Enhanced Intel SpeedStep Technology). Moreover, the Linux kernel support was improved with the use of the smarter intel\_pstate governor [65].

#### 2.1.3 Hardware-controlled P-states (HWP)

Ever since the introduction of the aforementioned power management mechanisms, it was operating system role to detect a change in the system load and properly adjust the CPU frequency-voltage values (i.e. P-state). However, when transient workloads are spawned, which are in need of a rapid performance boost, the operating system response time granularity (10s of milliseconds) is limiting. Another issue is

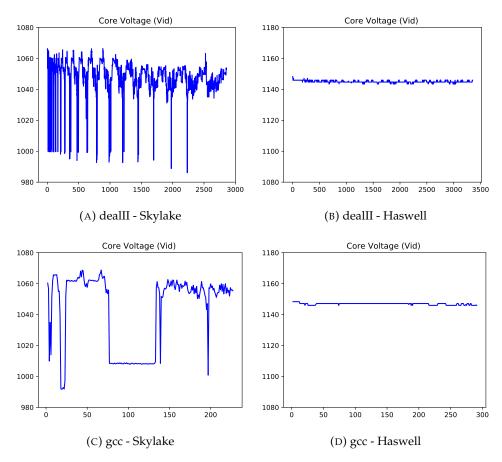

FIGURE 2.2: Comparison of core voltage behavior between Skylake and Haswell architectures

that the OS lacks the ability to make a direct observation of the workload microarchitectural behavior. In order to address these issues, a new set of power management technologies were implemented in the Skylake (and later) microprocessors.

This new technology, code-named SpeedShift, makes it possible to offload the frequency and voltage shifting from the operating system to a hardware micro-controller (i.e. Package Control Unit – PCU). PCU collects internal architectural statistics and monitors the power envelope of the CPU. Using the collected statistics and by computing and applying the optimal configuration every  $\sim 1$  millisecond, the processor manages to quickly adapt to bursty performance and power needs [19, 50].

SpeedShift is also capable by default, of instantaneous full-range frequency shifts. This means that it is possible for example to transition from P4 to P0 in a single step rather than making all the way through the P3, P2 and P1 states, until eventually reaching the desired P0 state. The operating system, however, can still change the default configuration of the mechanism to ensure a Quality of Service (QoS). This is typically achieved by specifying the minimum and the maximum processor operating frequency [30].

Figure 2.2 compares the core voltage behavior between the recent Skylake architecture, and the older Haswell one. Two workloads were profiled: gcc and dealII, which have shown significant core voltage variability on Skylake architectures. The x-axis represents the core voltage samples, which are taken every 5 milliseconds. Note that even though the two architectures have different core voltage operating point range, the plots have the same y-axis scale. It is obvious that the core voltage on the Haswell system is almost constant, with minor variations. This is not the case on the Skylake system, as the core voltage experiences very large fluctuations throughout the execution of the workload.

### 2.1.4 Performance Boosting Mechanisms

Apart from the power-saving mechanisms described in the previous paragraphs, there has been some research on integrating performance-boosting mechanisms on the processors, too. One such technology is Hyper-Threading (HTT) which basically allowed two threads to sometimes run simultaneously on a single core [41] (i.e. Simultaneous Multithreading – SMT). Because of superscalar design of x86 processors, it is possible to improve the parallelization of the computations by issuing individual instructions in the pipeline, with the restriction that they operate on separate data. Hyper-Threading exists on almost all modern desktop and server mid to high-end CPUs.

A more advanced mechanism, commonly found in some high-end processors, is Intel Turbo Boost Technology, which allows some cores to run faster than the rated clock frequency for a short time [33]. Typically, this mechanism takes action only when the cores are on the P0 state (i.e. maximum frequency) and within the power, current and thermal design specification limits. Without diving into the details, these mechanisms provide some additional P-states, called turbo P-states, which are used when it is considered safe.

For the scope of this thesis, we won't be focusing on these performance-oriented technologies.

## 2.2 Perf\_events profiling tool

In order to monitor the processor microarchitectural behavior, we extensively use an existing performance monitoring and analyzing tool called perf\_events, which is available in the Linux kernel since version 2.6.32 [37]. Perf\_events is capable (among other things) of statistical profiling of each core or of the entire system by providing a unified interface to the low-level Performance Monitoring Units (PMU). These units may differ from one architecture to another, as their specific implementation uses special-purpose hardware registers.

Perf\_events abstracts the implementation details and enables the hardware events reporting to the user-space. This is achieved by using a kernel component that performs and buffers the actual measurements and a user-space component, which periodically pulls and saves these measurements.

Perf\_events can be programmed to operate in two modes:

- **Counting mode**, which enables the counting of the occurrences of certain events e.g. executed instructions, L1 caches misses, inside a user-defined interval.

- **Sampling mode**, which periodically triggers interrupts after a user-defined number of occurrences of the given event.

Since we are not interested in locating individual events but getting aggregated values, we use the counting mode. Perf\_events provide this functionality with the perf\_stat subcommand.

Traditional hardware performance counters measure events inside a CPU core. Nevertheless, in modern Intel architectures there are a couple more mechanisms that provide access to package-wide measurements.

In the next paragraphs, we present a rough overview of each different type of hardware event.

## 2.2.1 Programmable core events

These are the most common events and usually refer to the programmable hardware performance events. These events can be monitored by properly programming the PMUs, which requires some writing to dedicated control registers. Fortunately, these low-level operations are abstracted by perf\_events. On x86 architectures, each CPU core has a distinct set of PMUs, thus it is possible to take per-core measurements.

Perf\_events holds a list of popular pre-defined events which usually refer to the high-level components of the processor architecture. It also presents them which user-friendly names instead of the actual (more compliacted ones). Listing 2.1 shows the output of the perf list subcommand. Typically, the hardware and hardware cache event types occupy a PMU, while the Kernel PMU events do not. However, this also depends on which hardware events are to be measured.

```

List of pre-defined events (to be used in -e):

branch-instructions OR branches

[Hardware event]

branch-misses

[Hardware event]

bus-cycles

[Hardware event]

cache-misses

[Hardware event]

cache-references

[Hardware event]

cpu-cycles OR cycles

[Hardware event]

instructions

[Hardware event]

ref-cycles

[Hardware event]

... <omitting software events> ...

L1-dcache-load-misses

[Hardware cache event]

L1-dcache-loads

[Hardware cache event]

L1-dcache-stores

[Hardware cache event]

L1-icache-load-misses

[Hardware cache event]

LLC-load-misses

[Hardware cache event]

LLC-loads

[Hardware cache event]

LLC-store-misses

[Hardware cache event]

LLC-stores

[Hardware cache event]

branch-load-misses

[Hardware cache event]

[Hardware cache event]

branch-loads

dTLB-load-misses

[Hardware cache event]

dTLB-loads

[Hardware cache event]

dTLB-store-misses

[Hardware cache event]

dTLB-stores

[Hardware cache event]

iTLB-load-misses

[Hardware cache event]

iTLB-loads

[Hardware cache event]

node-load-misses

[Hardware cache event]

node-loads

[Hardware cache event]

node-store-misses

[Hardware cache event]

node-stores

[Hardware cache event]

branch-instructions OR cpu/branch-instructions/ [Kernel PMU event]

branch-misses OR cpu/branch-misses/

[Kernel PMU event]

bus-cycles OR cpu/bus-cycles/

[Kernel PMU event]

cache-misses OR cpu/cache-misses/

[Kernel PMU event]

cache-references OR cpu/cache-references/

[Kernel PMU event]

cpu-cycles OR cpu/cpu-cycles/

[Kernel PMU event]

instructions OR cpu/instructions/

[Kernel PMU event]

mem-loads OR cpu/mem-loads/

[Kernel PMU event]

mem-stores OR cpu/mem-stores/

[Kernel PMU event]

cpu/topdown-fetch-bubbles/

[Kernel PMU event]

cpu/topdown-recovery-bubbles/

[Kernel PMU event]

cpu/topdown-slots-issued/

[Kernel PMU event]

cpu/topdown-slots-retired/

[Kernel PMU event]

cpu/topdown-total-slots/

[Kernel PMU event]

```

LISTING 2.1: Output of perf list subcommand

The number of the available hardware events is much higher though, and depends

| Perf_events Name         | Event Description                                  |  |

|--------------------------|----------------------------------------------------|--|

| Mnemonic Name            |                                                    |  |

| cpu/instructions         | Instructions retired from execution                |  |

| INST_RETIRED.ANY         | instructions retired from execution                |  |

| cpu/cycles               | Carolina with an other near in most in healt state |  |

| CPU_CLK_UNHALTED.THREAD  | Cycles when the core is not in halt state          |  |

| anylyof avaloa           | Counts the number of reference (i.e not            |  |

| cpu/ref-cycles           | affected by core frequency changes) cy-            |  |

| CPU_CLK_UNHALTED.REF_TSC | cles when the core is not in a halt state.         |  |

TABLE 2.1: Fixed-function events in the Skylake architecture

on the architecture generation. On the Skylake architecture, the actual number of such events is approximately 220 [31]. Perf\_events can program the PMUs to monitor any of these events by providing its (unique) event mnemonic name. Unfortunately, it is not possible to monitor all these events simultaneously, as the limited number of PMUs (per core) in Skylake architecture allows for the simultaneously monitoring of 4 events, or 8 if the Hyper-Threading technology is disabled.

#### 2.2.2 Fixed-function events

Fixed-function events, are per core performance events that do not occupy a PMU. In contrast to programmable counters, these are special registers, which have the very specific role of measuring a certain event. In general, these registers are updated internally by the CPU at constant intervals, and thus changing the event measured is not possible.

Table 2.1 lists the fixed-function events for the Skylake architecture. Note the generic nature of these events, as their value can be beneficial in any kind of performance or power analysis.

### 2.2.3 Shared socket-wide events

The shared socket-wide events, called from now on uncore events, measure events that occur outside the CPU cores. The uncore PMUs (or "boxes") can be programmed to measure the number of last level cache (i.e. L3 cache) misses, cache coherence protocol snoop events and main memory (i.e. RAM) cache line requests and many more [31]. There exist various types of "boxes", which are located in different parts of the architecture to allow for the effective profiling of the subsystems. For example, a C-box is dedicated to the last level cache metrics, the iMC refers to the integrated memory controller etc. More technical details related to uncore events, can be found in [63].

| Event Name / Register Name       | Event Description                      |

|----------------------------------|----------------------------------------|

| power/energy-pkg/                | The total amount of energy consumed by |

| MSR_PKG_ENERGY_STATUS            | the whole package / chip.              |

| power/energy-cores/              | The total amount of energy consumed    |

| MSR_PPO_ENERGY_STATUS            | only by the cores.                     |

| msr/thermal/ IA32_THERMAL_STATUS | Current core temperature               |

TABLE 2.2: Pre-defined power / thermal events by perf\_events

#### 2.2.4 Power-related and thermal events

In addition to the previous performance events, modern systems may provide on-CPU power and energy measurements. These are exposed via the Running Average Power Limit (RAPL) interface, which is available on certain Intel processors. Depending on the actual processor model, these might be just estimates, computed by math models, or actual power measurements, provided by on-chip sensors. RAPL events are divided among different components of the platform, to enable for finer control (e.g. package, CPU cores, DRAM controller etc.).

Perf\_events supports the RAPL interface since mainline version 3.14 [38]. Table 2.2 lists the relevant power and thermal events, provided by perf\_events for the Skylake architecture.

# **Chapter 3**

# Extending perf\_events

As it has been discussed in section 2.2, the run-time knowledge of the micro architecture can be obtained using mechanisms that employ dedicated hardware registers (i.e. PMUs). These registers are just a small part of a larger group of architecture-specific registers called Model-Specific Registers (MSR) [32]. The access to the majority of the registers, which are used by some already-established mechanism (i.e. RAPL, PMU) has already been abstracted by the specifications of the interface. However, there are more MSRs available which are not part of some interface, yet they can be read directly to extract more information.

Reading from or writing to an MSR is handled by the rdmsr and wrmsr commands. These are privileged instructions, however, and cannot be executed directly from the user-space. Thus, we make some modifications to the kernel component of perf\_events with the intention to include the measurement of events described below, which are not yet supported by the current versions <sup>1</sup>.

## 3.1 CPU core voltage

According to Intel Software Developer's Manual [32], which lists all the MSR for each processor generation, it is possible to read the CPU core voltage on SandyBridge (and later) architectures. This is achieved by reading the value in the IA32\_PERF\_STATUS MSR and then extracting the value of [32, 47] bits. Through experimentation we discovered that this register value is updated every  $\sim 1$  millisecond.

Listing 3.1 presents a sample C implementation that returns the core voltage value (in millivolts). Please note, however, that the CPU (i.e. package) provides just a single MSR register for all cores. Now, whether it is the case that each core has it is own voltage regulator, and thus may work on a different voltage level from each other, or all cores share the same regulator, is not currently documented. For the scope of this thesis, it is assumed that all cores are powered by the same core voltage.

<sup>&</sup>lt;sup>1</sup>These modifications were made by Panos Koutsovasilis

```

unsigned short read_core_voltage (int cpu_core) {

unsigned long long vid = rdmsr(cpu_core, MSR_IA32_PERF_STATUS);

vid = (vid >> 32) * 1000;

return ((unsigned short) vid >> 13);

}

```

LISTING 3.1: Sample function implementation in C that returns the core voltage in millivolts, on SandyBridge (and later) processors

## 3.2 Core Frequency

The current CPU core frequency can be calculated in Skylake architectures by taking readings of the following two MSRs:

- **IA32\_MPERF**, which increments with the **maximum** frequency (i.e. fixed clock rate), when the processor is in the C0 state.

- **IA32\_APERF**, which increments with the **actual/current** frequency (i.e. clock rate of execution), when the processor is in the C0 state.

Assuming the processor is not idle, the *APERF/MPERF* indicates the ratio of total cycles to constant-clock cycles (i.e. cycles that would had been executed if the processor was at the P0 state at the whole time). Thus, using the following formula:

$$FREQ_{CORE} = FREQ_{BASE} \times (\Delta APERF / \Delta MPERF)$$

it is possible to obtain the average core frequency over the last interval (as shown in [31] – paragraph 14.5.5). The CPU base frequency is a design-specific value and it is constant on the processor. So, the above formula can be translated to code by using the APERF and PFREQ values of the previous interval to calculate  $\Delta$  *APERF* and  $\Delta$  *MPERF*, respectively.

#### 3.3 Productive Performance

One new and very interesting metric, found only in Skylake (and later) architectures, is the so-called Productive Performance. As discussed in [31] on paragraph 14.4.5.1, it provides a quantitative metric to software of hardware's view of workload scalability. This can be defined as a rough estimation of the relationship between frequency and workload performance, to software.

The Productive Performance value can be obtained by reading the IA32\_PPERF MSR. This counter is increased only in "productive" cycles, where the hardware believes

that there is real progress to instruction execution. In other words, "productive" cycles are the ones that the core does not experience any activity stalls due to some dependency (e.g. waiting data from memory). So, in simple terms, productive performance refers to the extent of stalls compared to stall-free cycles within a time window [44].

Analogous to the core frequency case, the  $\Delta$  *PPERF*/  $\Delta$  *APERF* indicates the ratio of total cycles to the **productive** or **stall-free** ones (based on observations from the hardware itself). Having these in mind, we define a new metric, which we call Productive Frequency, as follows:

$$FREQ_{PROD} = FREQ_{BASE} \times (\Delta PPERF / \Delta APERF)$$

We can argue that  $FREQ_{PROD}$  is the (average) lowest possible frequency value that we could have set the core frequency to in the last interval, so it didn't had a negative impact on the workload performance. We will see later on section 7.3, that the productive frequency can be exploited for detecting phases of workload behavior.

## 3.4 Processor states (C-states)

The Skylake architecture provides several MSRs on each CPU core that can be used to measure how much time a core spends in some idle-state (i.e C-state). Each core has dedicated MSRs for the C3, C6 and C7 states. At every cycle the processor core increments one of these MSRs if it currently is in any of these states. An additional MSR, named time-stamp counter (TSC) that is increased every cycles, can be used to find the residency percentage. This is achieved by dividing the C3, C6 and C7 state value by the TSC value, as the latter is invariant of the core C-state:

$$RESIDENCY_{CX} = TICKS_{CX} / TICKS_{TSC}$$

, where  $CX \in \{C3, C6, C7\}$

Since the architecture does not provide dedicated MSRs that count the time spent on C0 and C1 states, these are computed with the help of MPERF MSR. More specifically, the C1 residency can be computed as follows:

$$RESIDENCY_{C1} = \left(TICKS_{TSC} - \sum_{s \in S} TICKS_s\right) \ / \ TICKS_{TSC}$$

where  $S = \{MPERF, C3, C6, C7\}$ . Finally, the C0 residency can be computed by subtracting all the other C-state residencies:

$$RESIDENCY_{C0} = 1.0 - \sum_{Cx \in CX} RESIDENCY_{Cx} , CX = \{C1, C3, C6, C7\}$$

Listing 3.2 shows a sample C code that calculates the C-states residencies using the method described above. A slight code addition can be observed when computing the cycle count (i.e ticks) of C1 residency. As the MSR values cannot be read simultaneously, but with a small delay, C1 ticks might end up with negative value. Therefore, an explicit check ensures that this will never happen.

```

void get_cx_residencies (int cpu_core, float* c0_perc, float* c1_perc,

float* c3_perc, float* c6_perc, float *c7_perc) {

unsigned long long mperf, c1, c3, c6, c7, tsc, cx_tick;

// Read Cx-states, MPERF & Timestamp counter ticks

mperf = rdmsr(cpu_core, IA32_MPERF);

c3 = rdmsr(cpu_core, MSR_CORE_C3_RESIDENCY);

c6 = rdmsr(cpu_core, MSR_CORE_C6_RESIDENCY);

c7 = rdmsr(cpu_core, MSR_CORE_C7_RESIDENCY);

tsc = rdmsr(cpu_core, IA32_TIME_STAMP_COUNTER);

// Calculate C1-state ticks

cx_ticks = c3 + c6 + c7;

c1_ticks = (mperf + cx_ticks <= tsc) ?</pre>

tsc - mperf - cx_ticks : 0;

cx_ticks += c1;

// CX residencies

*c1_perc = c1 / tsc;

*c3_perc = c3 / tsc;

*c6_perc = c6 / tsc;

*c7_perc = c7 / tsc;

*c0_perc = 1 - *c1_perc - *c3_perc - *c6_perc - *c7_perc;

```

LISTING 3.2: Sample function implementation in C that returns the C-states residencies percentage on Skylake processors

Table 3.1 summarizes the registers that were used for extending the perf\_events capabilities. It is possible for a single MSR to have multiple copies across every core or even every thread (i.e scope). For example, in the case of an MSR with core scope, each core has its own dedicated register. If a CPU has 4 cores, then 4 values can be extracted for the same event. Furthermore, the values on these registers are different as each core executes instructions independently from the others.

## 3.5 Variable Interval Measurements

The implementation of perf\_events reports the measurements of the hardware events at fixed intervals. However, in the course of our research, it was required to take measurements of MSR-related events in smaller intervals than PMU-related ones. Therefore, we modified the kernel component of perf\_events to enable for variable interval measurements among different events.

| Addr  | Description            | Scope   | Register Name           |

|-------|------------------------|---------|-------------------------|

| 0x198 | Core Voltage           | Package | IA32_PERF_STATUS        |

|       | (bits 47:32)           |         |                         |

| 0xE7  | Maximum Performance    | Thread  | IA32_MPERF              |

|       | Frequency Clock Count  |         |                         |

| 0xE8  | Actual Performance     | Thread  | IA32_APERF              |

|       | Frequency Clock Count  |         |                         |

| 0x64E | Productive Performance | Thread  | IA32_PPERF              |

|       | Count                  |         |                         |

| 0x10  | Time Stamp Counter     | Core    | IA32_TIME_STAMP_COUNTER |

|       | (TSC)                  |         |                         |

| 0x3FC | C3 Residency Counter   | Core    | MSR_CORE_C3_RESIDENCY   |

| 0x3FD | C6 Residency Counter   | Core    | MSR_CORE_C6_RESIDENCY   |

| 0x3FE | C7 Residency Counter   | Core    | MSR_CORE_C7_RESIDENCY   |

TABLE 3.1: List of registers used for extending perf\_events

This change was pretty straightforward, as the actual sampling is performed inside a big while loop that is executed at fixed time points. First, we reduced the time delay between two consecutive iterations, which correspond to MSR-related events measuring. Then, in order to measure the PMU-related events, we added logic that samples these only every k-th iteration. To summarize, MSR-related events are measured in each iteration, while PMU-related ones every k iterations. By properly defining k and the fixed time interval (in milliseconds) we can support all possibilities.

# Chapter 4

# **Capturing Workload Behavior**

### 4.1 Workload selection

In order to achieve a comprehensive analysis of the inner-workings of SpeedShift, we use a large subset of the SPEC CPU2006 [26] benchmarking suite. This suite consists of a wide range of CPU-intensive workloads, written in C, C++ or Fortran programming languages, which originate from real-world applications. Each workload may perform integer or floating-point operations and stresses different part the system's processor and memory subsystem.

Table 4.1 lists the workloads from the selected SPEC CPU2006 subset along with more information regarding their application domain.

## 4.2 Workload Profiling

### 4.2.1 System Specs & Setup

The workloads are profiled on a typical Intel Xeon workstation. Table 4.2 contains the full hardware and software specification of this system. Please note that the designated nominal supply voltage is the maximum possible, when there is full utilization of the CPU.

Before running the workloads, a bash script is run to perform the initial setup of the system. This setup / configuration script, the code of which is shown in Listing 4.1, does the following actions:

- It disables the NMI Watchdog, which conflicts with perf\_events when reading or writing the MSRs. If not disabled, it can lead to reduced accuracy.

- It loads the msr module to the kernel, using the modprobe command. This is necessary in order for the modified perf\_events version to be able to access the aforementioned MSRs.

| Name       | <b>Operation Type</b> | Language | Application Domain          |

|------------|-----------------------|----------|-----------------------------|

| bwaves     | Floating-Point        | Fortran  | Fluid Dynamics              |

| bzip2      | Integer               | C        | Compression                 |

| dealII     | Floating-Point        | C++      | Finite Element Analysis     |

| gamess     | Floating-Point        | Fortran  | Quantum Chemistry           |

| gcc        | Integer               | C        | C Compiler                  |

| gobmk      | Integer               | C        | AI / Go                     |

| gromacs    | Floating-Point        | C        | Molecular Dynamics          |

| h264ref    | Integer               | C        | Video Compression           |

| hmmer      | Integer               | C        | Search Gene Sequence        |

| lbm        | Floating-Point        | C        | Fluid Dynamics              |

| leslie3d   | Floating-Point        | Fortran  | Fluid Dynamics              |

| libquantum | Integer               | C        | Physics / Quantum Computing |

| mcf        | Integer               | C        | Combinatorial Optimization  |

| milc       | Floating-Point        | C        | Quantum Chromodynamics      |

| namd       | Floating-Point        | C++      | Molecular Dynamics          |

| omnetpp    | Integer               | C++      | Discrete Event Simulation   |

| perlbench  | Integer               | C        | Programming Language        |

| povray     | Floating-Point        | C++      | Image Ray-tracing           |

| sjeng      | Integer               | C        | AI / Chess                  |

| soplex     | Floating-Point        | C++      | Linear Programming Solver   |

| sphinx3    | Floating-Point        | C        | Speech Recognition          |

| tonto      | Floating-Point        | Fortran  | Quantum Chemistry           |

| xalancbmk  | Integer               | C++      | XML Processing              |

| zeusmp     | Floating-Point        | Fortran  | Physics / CFD               |

TABLE 4.1: Subset of SPEC CPU2006 workloads used for profiling

- It enables the SpeedShift technology on each core, by setting the least significant bit of the IA32\_PM\_ENABLE MSR.

- It locks the core frequency of all 4 cores to the fixed base frequency of the processor (i.e. 3GHz). This is achieved by writing at the IA32\_HWP\_REQUEST MSR (more details can be found in [31] on paragraph 14.4.4). The fixed frequency allows us to not worry about potential run-time changes across P-states but instead focusing on the voltage variation on a single one.

```

#!/bin/bash

echo 0 > /proc/sys/kernel/nmi_watchdog

sudo modprobe msr # Expose MSRs on user-space

sudo wrmsr -a 0x770 0x1 # Enable SpeedShift on each core

sudo wrmsr -a 0x774 0x19e0001e1e # Fix the core frequency to 3.0GHz

```

LISTING 4.1: System initial pre-profiling configuration script

In addition, we disable the Turbo Boost Technology to prevent any core from briefly switching to some turbo P-state. To further limit the interference from the operating system, we also disable the internal Intel P-state governor. This is achieved by selecting the acpi-cpufreq driver, instead of the default intel\_pstate one, which is

| Parameters                  | Values          |

|-----------------------------|-----------------|

| CPU                         | Xeon E3-1220 v5 |

| # of Cores / Threads        | 4 / 4           |

| CPU Base Freq.              | 3.00 GHz        |

| CPU Max Turbo Freq.         | 3.50 GHz        |

| L1 D-Cache                  | 32KB / core     |

| L1 I-Cache                  | 32KB / core     |

| L2 Cache                    | 256KB / core    |

| L3 Cache                    | 8 MB            |

| RAM Size                    | 8 GB            |

| RAM Type                    | DDR4 @ 2133 Mhz |

| Technology                  | 14nm            |

| Supply Voltage ( $V_{dd}$ ) | 1.15V           |

| Thermal Design Power        | 80 W            |

| Operating System            | Ubuntu 16.04    |

| Linux Kernel Version        | 4.10.17         |

TABLE 4.2: Specifications of the Skylake workstation

present in Linux kernel (details are available in [65]). After these steps, the full control of frequency and voltage operation points has been handed to the autonomous SpeedShift mechanism.

Finally, we launch one workload instance for every core, and we bind them to individual cores (using the taskset command), to be certain that they will not migrate among cores.

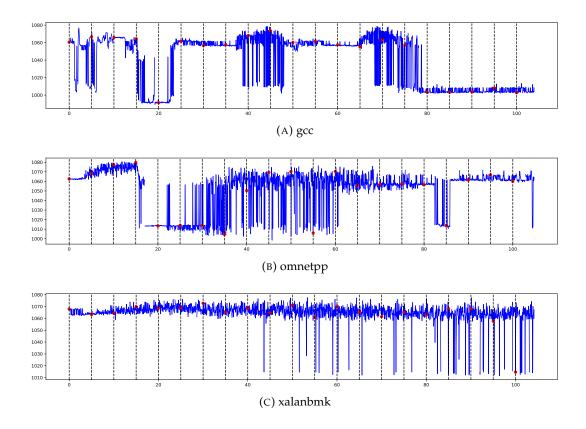

## 4.2.2 Perf\_events Sampling Interval

The sampling rate of the events measured greatly depends on their rate of change. Figure 4.1 shows how quickly the core voltage value changes in the first half second of the execution of three representative workloads (i.e. gcc, omnetpp, xalanbmk). Samples are taken every 5 milliseconds and the red dots indicate samples that are 100ms apart. Notice that while the "red" samples of xalanbmk workload are representative of overall core voltage behavior, this is not true for some parts of gcc and omnetpp execution.

Perf\_events supports the sampling of aggregated hardware events that are measured by the PMUs at different time intervals. The user can specify the desired time interval depending on her needs. In our case, we are interested in observing the relationship between hardware events and core voltage. As it has been shown though, core voltage may flunctuate very quickly. Therefore, the lowest possible sampling rate should be preferred, which is found to be **100 ms**. Lower values, produce a perf\_events warning message, stating that significant overhead might be introduced,

FIGURE 4.1: Comparison of core voltage behavior for three representative SPEC2006 workloads

mainly due to the time spent for the configuration of PMUs. Thus, we stay with 100 ms, which is applied for the core, uncore and fixed-function events / counters.

In contrast to PMU hardware events, the sampling of events that are measured using dedicated MSRs has no real overhead. Their values are updated internally by the CPU in constant intervals, regardless of the actions of the operating system. Since the only step in gathering these measurements is just reading an MSR (using the rdmsr instruction), the overhead is minimal as this call is done inside the kernel space (as described in Chapter 3) and does not require any expensive context switches. The selected sampling interval for these events is set to **5 ms**, and is applied for the power events, the core voltage, the core and productive frequency and the C-states residency events.

To summarize, for each PMU-related sample we obtain 20 MSR-related samples.

## 4.3 Data Collection, Cleaning & Transformation

In our evaluation system, we are able to measure just 8 core hardware events simultaneously, as this is the number of PMUs per core. This is a very limiting if we recall that the number of available hardware events is over 220. Keeping these in

mind, there are two approaches here: either we explicitly choose some high-level metrics that have previously been successfully used in other domains or we somehow manage to get measurements for the majority of events and then, by leveraging data mining and statistical methods, select which best describe the core voltage behavior. We experiment with both, as we create two separate datasets. The exact methodology followed is described in the next paragraphs.

## 4.3.1 High-Level Metrics (HLM) dataset

A lot of work has been done in power consumption estimation of modern processors, using hardware performance counters. Even though, one could argue that estimating power is the same as estimating voltage, we saw that this is not true, as voltage is an instantaneous event, in contrast to power which is an aggregated one. Nevertheless, researchers have suggested a variety of hardware events that span across multiple components of the architecture, as presented in [59] and [10].

A more thorough investigation of hardware events has been presented by the Top-Down Microarchitectural Analysis (TDMA) [68]. TDMA is a practical method for quickly characterizing a workload based on the performance bottlenecks, caused by stalls in the architectural level. It employs a hierarchical organization of event-based metrics, which measure the state of the micro-architectural entire spectrum. The first level of TDMA hierarchy consists of the following metrics:

- Front-end Bound, which denotes when the front-end part of the architecture undersupplies the back-end. The front-end contains the branch predictor and the instruction fetcher and decoder units.

- **Bad Speculation Bound**, which refers to time wasted due to incorrect speculations. The wasted time is due to branch miss-predictions and machine clears (i.e. pipeline flushes).

- **Retiring Bound**, which reflects the retiring rate of micro-ops / instructions from the arithmetic and floating-point units (both scalar and vectorized).

- Back-end Bound, which measures the stall count, which occurred due to lack

of required resources. This can be further split into memory bound, where execution is stalled due to data-cache misses, and core bound, where the stalling

reason is the overload of the Arithmetic Logic Unit (ALU).

Although TDMA aims at improving performance, which is not related directly to power behavior, there is close resemblance on the hardware events chosen by both studies. However, this events list does not explicitly include events that are targeting the behavior of both caches and main memory. Hence, to fill this gap we include

| Event Name                                 | Event Description                                                                                                                             |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Core Events                                |                                                                                                                                               |  |  |  |

| IDQ_UOPS_NOT_DELIVERED .CORE               | Uops not delivered to Resource Allocation Table (RAT) per thread when backend is not stalled                                                  |  |  |  |

| UOPS_ISSUED.ANY                            | Uops that RAT issues to Reservation Station (RS)                                                                                              |  |  |  |

| UOPS_RETIRED.RETIRE_SLOTS                  | Counts the retirement slots used                                                                                                              |  |  |  |

| INT_MISC.RECOVERY_CYCLES                   | Core cycles the allocator was stalled<br>due to recovery from earlier clear<br>event for this thread (e.g. mispredic-<br>tion or memory nuke) |  |  |  |

| RESOURCE_STALLS.ANY                        | Counts resource-related stall cycles                                                                                                          |  |  |  |

| MEM_LOAD_RETIRED.L1_HIT                    | Retired load instructions with L1 cache hits as data sources                                                                                  |  |  |  |

| MEM_LOAD_RETIRED.L2_HIT                    | Retired load instructions with L2 cache hits as data sources                                                                                  |  |  |  |

| MEM_INST_RETIRED.ALL_LOADS                 | All retired load instructions                                                                                                                 |  |  |  |

| Uncore Events                              |                                                                                                                                               |  |  |  |

| UNC_CBO_XSNP_RESPONSE .MISS_EVICTION       | A cross-core snoop resulted from L3<br>Eviction which misses in some processor core                                                           |  |  |  |

| UNC_CBO_CACHE_LOOKUP .ANY_MESI             | L3 Lookup any request that access cache and found line in MESI-state                                                                          |  |  |  |

| UNC_ARB_TRK_OCCUPANCY.ALL                  | Number of all Core entries outstanding for the memory controller                                                                              |  |  |  |

| UNC_ARB_TRK_REQUESTS.ALL                   | Total number of Core outgoing entries allocated. Accounts for Coherent and non-coherent traffic                                               |  |  |  |

| Fixed Events                               |                                                                                                                                               |  |  |  |

| cpu/cycles                                 | Core cycles when the thread is not in halt state                                                                                              |  |  |  |

| cpu/instructions                           | Instructions retired from execution                                                                                                           |  |  |  |

| Power Events                               |                                                                                                                                               |  |  |  |

| power/energy-pkg/                          | The total amount of energy consumed by the whole package/chip                                                                                 |  |  |  |

| power/energy-cores                         | The total amount of energy consumed only by the cores                                                                                         |  |  |  |

| Miscellaneous                              |                                                                                                                                               |  |  |  |

| msr/vid<br>msr/freq<br>msr/productive_freq | CPU Core voltage (in millivolts) CPU Core frequency (in MHz) Productive Frequency (in MHz)                                                    |  |  |  |

| msr/c0_residency                           | CPU Residency Percentage in C0 state                                                                                                          |  |  |  |

Table 4.3: Total hardware events measured for the HLM dataset

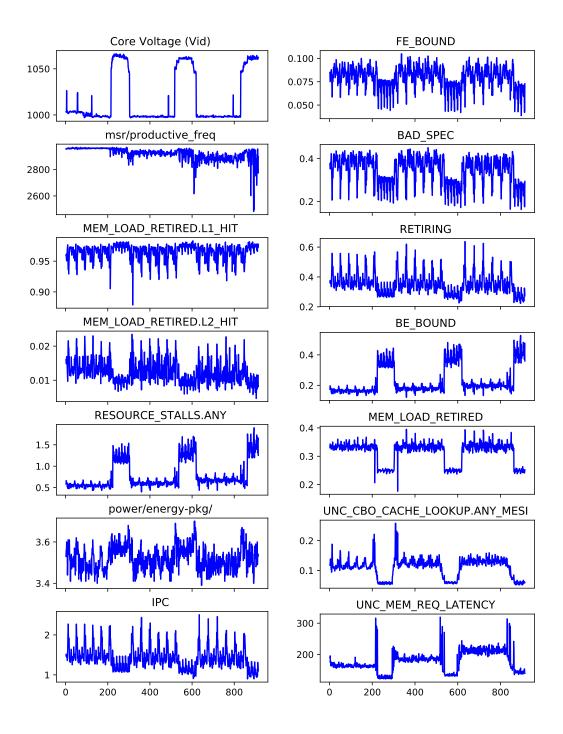

specific events that primarily focus on the power footprint of the different cache levels (i.e. L1, L2, LLC). Table 4.3 lists the hardware events measured by perf\_events, which are used for the construction of **HLM dataset**.

### 4.3.2 All-Metrics (AM) Dataset

Although the gathering of all hardware events is not feasible in as single run, many individual profiling runs can be performed. In order to profile  $\sim 220$  events, 28 distinct runs were required. The workload execution times were varying slightly, as different hardware event sets introduce different overhead. To adjust the unequal number of samples, a number of the last samples was dropped for each run so that each run had the same number of samples.

Multiple runs means that there are multiple values of each MSR event, as these are profiled for each run. Still, for constructing the final dataset, a single and hopefully representative value, should be selected. One option is to take the average of all values profiled. However, this average is a synthetic value, since it was not obtained from a direct measurement. Thus, we choose the median MSR value across the all runs, as it is the result of a real run.

# 4.4 Data Cleaning

Once the profiling data are collected and exported to .csv files by perf\_events, the data cleaning process is taking place to ensure that the acquired data are relevant and can be included in the final dataset. Data cleaning (or data cleansing) usually refers to removing incorrect or inaccurate samples obtained during the collection phase [67]. In our case, the following cleaning steps are performed:

- The samples with a **C0-state residency** value below 80% are discarded. The rationale behind this decision is that at this time interval, the processor is not "busy enough", and thus the aggregated hardware events values obtained cannot be directly compared against other intervals. Depending on the workload, this discards from 0.5% to 2% of the total samples collected.

- The samples having a core frequency value outside of the 2.95 − 3.05 GHz range are dropped as well. It has been observed that on some workloads there exist some sudden peaks on the core frequency value. As frequency changes may impact the core voltage as well, we want to make sure that our samples are consistent to the same voltage range. This step drops less that 0.5% of the samples for every workload.

The above steps are applied to both **HLM** and **AM** dataset samples.

| Metric Name               | Formula                                 |  |

|---------------------------|-----------------------------------------|--|

| Core Metrics              |                                         |  |

| Frontend Bound            | FetchBubbles / TotalSlots               |  |

| Bad Speculation           | (SlotsIssued – SlotsRetired + Recovery- |  |

|                           | Bubbles) / TotalSlots                   |  |

| Retiring                  | SlotsRetired / TotalSlots               |  |

| Backend Bound             | 1 – (Frontend Bound + Bad Speculation + |  |

|                           | Retiring)                               |  |

| Instructions Per Cycle    | Instr / Cycles                          |  |

| L1 Cache Hit Percentage   | MemHitL1 / MemLoadInstr                 |  |

| L2 Cache Hit Percentage   | MemHitL2 / MemLoadInstr                 |  |