ECCTD'01 - European Conference on Circuit Theory and Design, August 28-31, 2001, Espoo, Finland

# Analysis and Modeling of the Non-Linear Sampling Process in Switched-Current Circuits - Application to Bandpass Sigma-Delta Modulators

José M. de la Rosa, Belén Pérez-Verdú, Fernando Medeiro, Rocío del Río and Angel Rodríguez-Vázquez †

Abstract – This paper presents a precise model for the transient behaviour of Fully Differential (FD) SwItched-current (SI) memory cells placed at the front-end of high-speed A/D interfaces. This model allows us to analyze the main errors associated to the S/H process, namely: excess transfer-function delay and harmonic distortion. For the latter, the analysis is extended to BandPass  $\Sigma\Delta$  Modulators (BP- $\Sigma\Delta$ Ms) and a closed-form expression is derived for the third-order intermodulation distortion. Time-domain simulations and experimental measurements taken from a 0.8 $\mu$ m CMOS 4th-order BP- $\Sigma\Delta$ M silicon prototype validate our approach.

#### 1. Introduction

Nowadays the market of digital communication devices is rapidly expanding with the development of new services and applications. This trend, together with the continuous scaling of digital CMOS technologies, has motivated exploring analog design techniques compatible with standard, VLSI processes. This is the case of <u>SwItched-current</u> (SI) circuits, which taking advantage of current processing, are suitable for fast operation with low-power consumption and low-voltage supplies [1].

Up to now, the potential of the SI technique has been barely demonstrated through actual, practical circuits. Thus, in the case of  $\Sigma\Delta$  Modulators ( $\Sigma\Delta$ Ms), performances featured by reported SI silicon prototypes are well below those of Switched-Capacitor (SC) counterparts, even if the latter are realized in standard technologies without good passive capacitors. Such poorer performances are partly due to the larger influence of SI non-idealities, as well as to the incomplete modeling of their influence. Particularly, for BandPass  $\Sigma\Delta$ Ms (BP- $\Sigma\Delta$ Ms), and due to the necessity to cope with the frequency specifications required for modern digital wireless systems [2], Harmonic Distortion (HD) caused by non-linear dynamics becomes one of the dominant limiting factors.

Most attempts to model HD due to the non-linear transient assumed that the input signal is constant during the sampling phase[3][4]. However, this assumption does not apply to a memory cell placed at the front-end of BP- $\Sigma\Delta$ Ms. In this case, the input signal frequency is typically a quarter of the sampling frequency. Hence, large variations of the drain-source current will occur during the sampling phase, thus causing an additional HD which cannot be explained by an step-response.

The analysis of the HD of a SI memory cell with a continuous-time sinewave signal was analysed in [5]. In this paper, that analysis is extended to the case of BP- $\Sigma\Delta$ Ms. For this purpose, a precise model is described for a front-end Fully Differential (FD) memory cell. On the one hand, this model allows us to study the dominant non-ide-

†.Instituto de Microelectrónica de Sevilla, IMSE, CNM-CSIC. Ed. CNM-CICA, Av. Reina Mercedes s/n, 41012 Sevilla, SPAIN. E-mail: jrosa@imse.cnm.es, Phone: +34-955056666, FAX: +34-955056686.

alities associated to the sampling process, namely: excess transfer-function delay and harmonic distortion. On the other hand, it enables hierarchical systematic analysis of SI circuits composed of memory cells, such as BP- $\Sigma\Delta$ Ms. As a result, a closed-form expression is derived for the third-order intermodulation distortion. It is demonstrated that large HD levels are obtained even for a low settling error, as confirmed by experimental measurements taken from a 0.8 $\mu$ m CMOS 4th-order BP- $\Sigma\Delta$ M [6].

## 2. Modeling of front-end FD SI memory cells

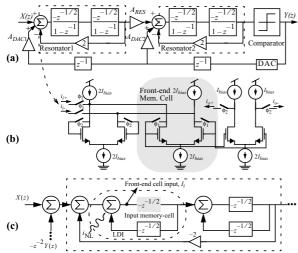

Fig. 1(a) shows a FD second-generation memory cell. In what follows, it will be assumed that the error associated to the transient response is the dominant limitation. Therefore, the effect of the charge injection error, and the finite output conductance, analysed elsewhere [1][7], will not be considered. Besides, in most practical cases the time constant formed by the drain-source capacitance and the switch-on resistance is much smaller than that due to the gate-source capacitance,  $C_{gs}$ , and the small-signal transconductance,  $g_{mQ}$ . In such a case, the behaviour of the cell during the sampling phase,  $\phi_1$ , can be modelled by the equivalent circuit in Fig.1(b). In this circuit, the large-signal behaviour is modelled by  $g_{m+}$  and  $g_{m-}$ , which represent the transconductances of  $M_{+,-}$  given by  $g_{m+,-} = g_{mQ} \sqrt{1 + m_{i+,-}}$ , where  $m_{i+,-} = i_{i+,-} / I_{bias}$ ,  $i_{i+,-} = \pm i_i / 2$ , and  $i_i$  is the input current [3].

Let us consider that  $i_i$  is a continuous-time sinewave of amplitude  $I_i$  and frequency  $f_i \cong f_s/4^{\ddagger}$ , with  $f_s$  being the sampling frequency. In this case,  $i_i$  will change during the sampling phase up to  $I_i/\sqrt{2}^{\dagger\dagger}$ , thus causing an additional error to that due to the incomplete settling error, which cannot be explained by analysing the step-response of the cell. For a better understanding of this phenomenon, we will consider first the linear analysis of Fig.1(b), with  $g_{m+}=g_{m-}=g_{mQ}$  and  $i_i(t)=I_i\sin(2\pi f_i t)$ . Thus, solving  $v_g$  for the initial condition,  $v_g(t_o)$ , yields:

$$v_{g}(t) = \begin{bmatrix} v_{g}(t_{o}) - \frac{i_{i}(t_{o})}{g_{mQ}} F_{t_{o}}(f_{i}) \end{bmatrix} e^{\frac{-(t-t_{o})}{\tau}} + \frac{i_{i}(t)F_{t}(f_{i})}{g_{mQ}}$$

(1)

$$v_{g}(t) = \begin{bmatrix} v_{g}(t_{o}) - \frac{i_{i}(t_{o})}{g_{mQ}} F_{t_{o}}(f_{i}) \end{bmatrix} e^{\frac{-(t-t_{o})}{\tau}} + \frac{i_{i}(t)F_{t}(f_{i})}{g_{mQ}}$$

(1)

$$v_{g}(t) = \begin{bmatrix} v_{g}(t_{o}) - \frac{i_{i}(t_{o})}{g_{mQ}} F_{t_{o}}(f_{i}) \end{bmatrix} e^{\frac{-(t-t_{o})}{\tau}} + \frac{i_{i}(t)F_{t}(f_{i})}{g_{mQ}}$$

(1)

**Figure 1.** Fully differential memory cell. a) Schematic. b) Equivalent circuit during the sampling phase.

‡.This is the typical case of a front-end memory cell in a BP- $\Sigma\Delta M$ . ††.The maximum signal variation during the sampling phase is given by:  $I_i |\sin[2\pi f_i(t+T_s/2)] - \sin[2\pi f_i t]|_{f_s=f_s/4} \le I_i/\sqrt{2}$ .

where

$$F_i(f_i) = \frac{1-2\pi f_i \tau \cot(2\pi f_i t)}{1+(2\pi f_i \tau)^2}$$

,  $\tau = C_{gs}/g_{mQ}$ .

Assuming that the memory switch becomes OFF at  $t_o = (n-1)T_s$  ( $T_s$  is the sampling period), it can be shown from (1) that the differential drain-source current at the end of the sampling phase,  $i_{d, n-1/2} = g_{mQ}v_{g, n-1/2}$  ; is given by:

$$i_{d, n-1/2}^{g, n-1/2} = i_{i, n-1/2} F_{n-1/2}(f_i) + F_{i_{d, n-1}} - i_{i, n-1} F_{n-1}(f_i) \epsilon_s$$

(2)

where  $\varepsilon_s = \exp[-T_s/(2\tau)]$  is the incomplete settling error and  $F_n(f_i) = F_{t=nT_s}(f_i)$ .

During the hold phase,  $i_d$  keeps constant at the value

During the hold phase,  $i_d^s$  keeps constant at the value reached at the end of the sampling phase and the cell delivers the output current,  $i_o$ . Thus, at the end of the hold phase  $nT_s$ , the output current is:

$$i_{o,n} = i_{o,n-1} \varepsilon_s - -[i_{i,n-1/2} F_{n-1/2}(f_i) - i_{i,n-1} F_{n-1}(f_i) \varepsilon_s]$$

(3)

The above expression can be simplified for two particular cases. On the one hand, consider us the case of stationary ( $f_iT_s \ll 1$ ) input signals, i.e,  $i_{i,n-1/2} \cong i_{i,n-1}$ . In this case,  $f_i \tau \ll 1$  and  $F_n(f_i) \to 1$ . Making these approximations in (3), results in the well-known finite difference equation of a memory cell degraded by  $\varepsilon_s$  [1].

On the other hand, considering a negligible settling error, i.e,  $\tau \ll T_s$ , and taking into account that  $i_{i,n} = I_i \sin(2\pi f_i n T_s)$ , it can be shown from (3) that:

$$i_{o,n} \simeq \frac{-I_i \sin[2\pi f_i (n - 1/2)T_s - a \tan(2\pi f_i \tau)]}{\sqrt{1 + (2\pi f_i \tau)^2}}$$

(4)

meaning that the overall transfer function of the cell is:

$$\frac{i_o(f)}{i_i(f)} = \frac{-\exp[-j\pi f_i T_s - j \operatorname{atan}(2\pi f_i \tau)]}{\sqrt{1 + (2\pi f_i \tau)^2}}$$

(5)

which can be seen as the cascade of two transfer functions: one of the Continuous-Time (CT) type, given by  $H_{\rm CT}(f)=1/(1+j2\pi f\tau)$ , and other one of the discrete-time type corresponding to the ideal transfer function of a memory cell,  $-z^{-1/2}$ . The former causes a transmission error which we will define as  $\varepsilon_{\rm CT}\equiv 2\pi f_i \tau$ . This error can severely degrade the performance of the memory cell even for  $\varepsilon_s\ll 1$  as will be shown in the next section.

In a more general case, i.e, for  $\varepsilon_{\rm CT} \neq 0$  and  $\varepsilon_s \neq 0$ ,  $i_d$  will evolve in time during the sampling phase from the previous memorized value to the new stationary state input current, degraded by  $H_{\rm CT}(f)$ . However, as a consequence of  $\varepsilon_s$ , that stationary state will not be reached at the end of the sampling phase, such that there will be an accumulation of two errors:  $\varepsilon_{\rm CT}$  and  $\varepsilon_s$ . The latter has been analysed elsewhere [1][3][4]. Here, we will focus on studying the main effects of  $\varepsilon_{\rm CT}$ .

#### 2.1 Excess transfer-function phase delay

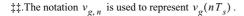

One of the main effects of  $\varepsilon_{\rm CT}$  is to increase the phase delay between  $i_i$  and  $i_o$ . This is illustrated in Fig.2(a) by showing an electrical simulation (HSPICE) of the cell in Fig. 1(a) with  $I_{bias} = 200 \mu {\rm A}$  and  $\tau \cong 7.7 {\rm ns}$  assuming a CT input signal of  $f_i \cong f_s/4$ . This figure plots  $v_g$  as a

**Figure 2.** Excess transfer-function phase delay caused by  $\varepsilon_{\rm CT}$  for a non-stationary input signal of  $f_i \cong f_s/4$ . a) HSPICE. b) Theoretical model.

function of  $i_i$  for three values of  $f_s$ . Comparing the resulting ellipses it can be concluded that the phase delay increases with  $f_s$  as a consequence of the increment of  $f_i \tau$ , i.e,  $\epsilon_{\rm CT}$ . This effect is predicted by the proposed model as Fig.2(b) illustrates. Besides, note that the ellipses become wider as  $\epsilon_{\rm CT}$  increases. This effect appears because  $f_i$  is not an exact submultiple of  $f_s$  — which is common in practice. Hence, since the number of sampling periods contained in an input period is not an integer, the sampled currents will vary from one input period to the next one.

Fig.3 illustrates the effect of changing  $f_i/f_s$  in memory cells with non-stationary input signals for  $\tau=7.7 \mathrm{ns}$  and  $f_s=10 \mathrm{MHz}$ , ( $\epsilon_s \!\cong\! 0.15\%$ ). Observe that the phase delay becomes larger as a consequence of increasing  $f_i \tau$ , i.e,  $\epsilon_{\mathrm{CT}}$ , not due to  $\epsilon_s$  (which is kept constant).

In the case of sampled-and-held input signals, the above-mentioned phenomenon appears but when  $\epsilon_s$  is greatly increased. This is illustrated in Fig.4 for a FD memory cell with  $I_{bias}=200\mu\mathrm{A}$ ,  $f_i{\,\cong\,}f_s/4$  and  $\tau=3.7\mathrm{ns}$ . Note that the cell starts to behave as if it had a non-stationary input signal when the settling error becomes large ( $f_s>50\mathrm{MHz}$ ), i.e, for  $T_s\to\tau$ , and the discrete-time approaches the continuous-time.

#### 2.2 Harmonic distortion due to non-linear S/H

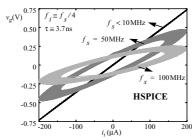

Another consequence of non-stationary input signals is the increase of the HD as compared to the case of stationary signals. This is illustrated in Fig.5 by comparing the

**Figure 3.** Effect of varying  $f_i$  on the transfer-function delay for  $\tau = 7.7$ ns and  $f_s = 10$ MHz ( $\varepsilon_s \approx 0.15\%$ ).

**Figure 4.** Excess transfer-function phase delay caused by  $\varepsilon_s$  for a sampled-and-held input signal of  $f_i \cong f_s/4$ .

simulated (HSPICE) output spectra of the cell in Fig.1(a) (with  $I_{bias} = 100 \mu A$ ,  $I_i = I_{bias}/2$ ,  $f_i = f_s/16$ ,  $g_{mQ} = 268 \mu A/V$ ,  $C_{gs} = 1 \text{pF}$  and  $f_s = 1 \text{MHz}$ ), corresponding to both a sampled-and-held and a continuous-time input tone. It is clear that the latter presents much more HD  $(HD_3 = -89 \,\mathrm{dB})$  than the former  $(HD_3 = -127 dB)$ . However, in both cases the settling error is negligible ( $\tau = 3.7$ ns and  $T_s = 1 \mu s$ ), meaning that the extra HD is caused by the non-linear sampling process. This phenomenon can be analysed by solving the non-linear circuit shown in Fig.1(b) for an sinewave input. A rigorous study will require using the Volterra series method as we demonstrated in [7]. However this method involves a tedious mathematical analysis and is difficult to extend to other SI circuits of higher hierarchy such as  $\Sigma\Delta Ms$ . Instead, we can find a similar solution – but involving a more simple analysis – by replacing  $g_{mQ}$  in (3) with  $g_{m+}$ . Making this respectively in each branch of the FD cell, the output current can be approximated by:

$$i_{o,n} \cong -i_{i,n-1/2} \varphi_{n-1/2}(m_{i,n-1/2}) + + [i_{i,n-1} \varphi_{n-1}(m_{i,n-1/2}) + i_{o,n-1}] \Psi(m_{i,n-1/2})$$

(6)

where  $\varphi_n(m_i) =$

$$= \frac{\frac{1}{2} - \pi f_i \tau \frac{\cot(2\pi f_i n T_s)}{\sqrt{1 + m_i}}}{1 + \frac{(2\pi f_i \tau)^2}{1 + m_i}} + \frac{\frac{1}{2} - \pi f_i \tau \frac{\cot(2\pi f_i n T_s)}{\sqrt{1 - m_i}}}{1 + \frac{(2\pi f_i \tau)^2}{1 - m_i}}$$

(7)

and  $\Psi(m_i) =$

$$= \frac{1}{2} \left( \exp \left[ \frac{-T_s}{2\tau} \sqrt{1 + m_i} \right] + \exp \left[ \frac{-T_s}{2\tau} \sqrt{1 - m_i} \right] \right)$$

(8)

To obtain a closed-form expression of  $HD_3$ , we have performed a Taylor series expansion of (7) and (8) for  $m_i \ll 1$ , giving:

$$\varphi_n(i_i) \cong \xi_1 + \xi_2 i_i^2 \qquad \Psi(i_i) \cong \varepsilon_s + \varepsilon_{s2} i_i^2 \qquad (9)$$

**Figure 5.** Output spectra of a FD memory cell with a (a) non-stationary and (b) stationary input tone of  $f_i = f_s/16$ .

where

$$\xi_1 = [1 - 2\pi f_i \tau \cot(2\pi f_i n T_s)]/(1 + (2\pi f_i \tau)^2)$$

$\xi_2 = -6\pi f_i \tau \cot(2\pi f_i n T_s)/(32I_{bias}^2)$

and  $\varepsilon_{s2} = \varepsilon_s [T_s/(2\tau)][1 + T_s/(2\tau)]/(32I_{bias}^2)$ . Substituting (9) into (6), it can be shown that the non-linear term appearing at the output of the cell is:

$$i_{\text{NL},n} \cong i_{i,n-1/2}^{2} [(\xi_{2} \varepsilon_{s} + \xi_{1} \varepsilon_{s2}) i_{i,n-1} + \varepsilon_{s2} i_{o,n-1}] - (10)$$

$$-\xi_{2} i_{i,n-1/2}^{3}$$

Approximating  $i_o$  by its first-order harmonic and performing a Fourier series expansion of (10) it can be derived that the amplitude of the third-order harmonic is:

$$A_{3H} = \frac{(3 - 3\varepsilon_s - 32\varepsilon_{s2}I_{bias}^2)\pi f_i \tau}{64I_{bias}^2} I_i^3 = \frac{3\pi f_i \tau I_i^3}{64I_{bias}^2}$$

(11)

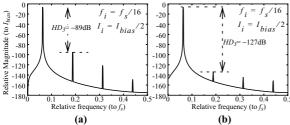

which agrees with HSPICE simulations as illustrated in Fig.6 by representing  $HD_3$  (  $\equiv A_{3H}/I_i$ ) vs.  $f_i/f_s$  for  $I_{bias}=100\mu\mathrm{A}$ ,  $g_{mQ}=268\mu\mathrm{A/V}$ ,  $C_{gs}=1\mathrm{pF}$ ,  $I_i=I_{bias}/2$ , and different values of  $f_s$ .

It is important to mention that the model described here is valid not only for analysing the HD of a single memory cell as in [5], but also to perform precise time-domain behavioural simulations of any FD SI circuit based on memory cells [7][8]. We will take advantage of this fact to obtain the effect of non-linear  $\epsilon_{CT}$  on the HD of BP- $\Sigma\Delta Ms$ .

### 3. Harmonic distortion of FD SI BP-ΣΔMs

Fig.7(a) shows the block diagram of the 4th-order BP-ΣΔM under study, with  $A_{DAC2}=2A_{DAC1}A_{RES}$ , which has been obtained by applying a  $z^{-1}\rightarrow -z^{-2}$  to a 2nd-order lowpass ΣΔM [2]. Because of this transformation, the original integrators become resonators with a transfer function  $z^{-a}/(1+z^{-2})$ , where  $0 < a \le 2$ . This function can be realized by several filter structures [2]. The resonators of Fig.7(a) are based on LD Integrators (LDI's), which can be realized using FD SI memory cells as shown in Fig.7(b). This structure is advantageous as compared to the others because it remains stable under changes in the loop coefficients [7]. For the analysis of the HD caused by non-linear  $\varepsilon_{CT}$ , the following considerations have been taken into account:

- •The HD referred to the modulator input is equal to the HD referred to the modulator output because the signal transfer function (Y(z)/X(z)) is unity in the signal band.

- •The quantization error, modelled as an additive white noise source [2], does not contribute to HD.

- •For  $\varepsilon_s \ll 1$ , the HD will be dominated by the non-linear  $\varepsilon_{CT}$  of the cell connected at the input node (see Fig.7(b)).

**Figure 6.**  $HD_3$  vs.  $f_i/f_s$  due to non-linear  $\varepsilon_{CT}$ .

**Figure 7.** Fourth-order BP- $\Sigma\Delta M$ . a) Block diagram. b) FD SI LDI-loop resonator. c) Block diagram for obtaining  $I_i$ .

Taking into account the above considerations, to calculate the third-order harmonic at the output of the modulator it is necessary to express  $I_i$  as a function of the modulator input amplitude,  $|X|=A_\chi$ . The analysis of Fig.7(c) gives:

$$I_i \cong A_x | (1 - z^{-1})^2 (1 + z^{-1}) | \Big|_{z = e^{j2\pi f_i T_s}} \cong 2\sqrt{2}A_x$$

(12)

where  $f_i \cong f_s/4$  has been assumed.

Substituting (12) into (11) and dividing by  $A_x$  it can be shown that the third-order intermodulation distortion,  $IM_3^{\dagger\dagger\dagger}$ , at the output of the BP- $\Sigma\Delta M$  is:

$$IM_3 \cong \frac{9}{8\sqrt{2}n_h^2} \pi f_s \tau \left(\frac{A_x}{I_{DAC}}\right)^2 \tag{13}$$

where  $n_b = I_{bias}/I_{DAC}$  , and  $I_{DAC}$  is the DAC output current.

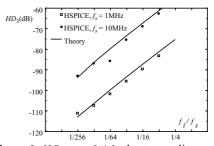

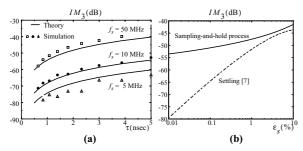

This analysis has been validated by time-domain simulation using the behavioural simulator for SI circuits reported in [8]. Fig.8(a) compares (13) with simulations by plotting  $IM_3$  vs.  $\tau$  for different values of  $f_s$ ,  $n_b=4$  and  $A_x/I_{DAC}=1/2$ . The theoretical model accurately predicts the simulation results except for some cases where a maximum error of 4dB occurs. In these cases a more exact analysis using the Volterra series method should be used.

**Figure 8.**  $IM_3$  due to the non-linear sampling. a)  $IM_3$  vs.  $\tau$ . b) Comparison with  $IM_3$  due to non-linear  $\varepsilon_s$  [7].

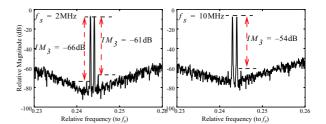

**Figure 9.** Experimental output spectra for different  $f_s$ .

To conclude this study, Fig.8(b) compares  $IM_3$  caused by the non-linear  $\varepsilon_s$  [7] and  $\varepsilon_{\rm CT}$  for  $f_s=10{\rm MHz}$  and  $A_x/I_{DAC}=1/2$ . Note that, for  $\varepsilon_s>3\%$ , both expressions approximately converge. However, for practical designs, i.e, for  $\varepsilon_s<0.1\%$ ,  $IM_3$  due to  $\varepsilon_{\rm CT}$  dominates, limiting the performance of SI BP- $\Sigma\Delta$ Ms unless a front-end S/H circuit will be used. This fact has been confirmed by experimental results from a 0.8 $\mu$ m CMOS 4th-order BP- $\Sigma\Delta$ M [6]. Fig.9 shows two measured output spectra for  $A_x/I_{DAC}=0.42$  when clocked at  $f_s=2{\rm MHz}$  and  $f_s=10{\rm MHz}$ , obtaining  $IM_3=-61{\rm dB}$  and  $-54{\rm dB}$  respectively. In this case,  $g_{mQ}=360\mu{\rm A/V}$  and  $C_{gs}=2.8{\rm pF}$  ( $\varepsilon_s=0.16\%$  at  $f_s=10{\rm MHz}$ ), which according to (13) gives  $IM_3=-64{\rm dB}$  and  $IM_3=-55{\rm dB}$  respectively.

#### 4. Conclusions

The effect of non-linear S/H process on SI circuits has been studied in detail. A model for FD memory cells placed at the front-end of A/D interfaces has been described. The analysis, validated by HSPICE, explains the main errors associated to the non-linear S/H, namely: excess phase delay and HD. For the latter, a closed-form expression has been derived for  $IM_3$  at the output of BP- $\Sigma\Delta$ Ms, which as confirmed by experimental results, constitutes the main source of HD in practical designs.

## References

- C.Toumazou, J.B.Hughes, and N.C. Battersby (Editors): "Switched-Currents: An Analogue Technique for Digital Technology", London: Peter Peregrinus Ltd., 1993.

- [2] S.R. Norsworthy, R. Schreier, G.C. Temes: "Delta-Sigma Converters. Theory, Design and Simulation", New York, IEEE Press, 1997.

- [3] P.J. Crawley and G.W. Roberts: "Predicting Harmonic Distortion in Switched-Current Memory Circuits", *IEEE Trans. Circuits and Systems II*, pp. 73-86, February 1994.

- [4] M.Helfenstein and G. Moschytz: "Distortion Analysis of Switched-Current Circuits", Proc. 1998 IEEE Int. Symp. Circuits and Systems (ISCAS), pp. 29-32.

- [5] J.M. Martins and V.F. Dias: "Harmonic Distortion in SI Cells: Settling and Clock Fall-Time Effects", Proc. of 1998 Design of Integrated Circuits and Systems Conference (DCIS), pp. 292-297.

- [6] J.M. de la Rosa, B. Pérez-Verdú, R. del Río and A. Rodríguez-Vázquez: "A CMOS 0.8μm Transistor-Only 1.63MHz Switched-Current Bandpass ΣΔ Modulator for AM Signal A/D Conversion", *IEEE Journal of Solid-State Circuits*, pp. 1220-1226, August 2000.

- [7] J.M. de la Rosa: "Modeling and Design of Switched-Current Bandpass ΣΔ Modulators for Digital Communication Systems", Ph.D. Dissertation, Univ. of Seville, December 2000.

- [8] J.M. de la Rosa, A. Kaiser and B. Pérez-Verdú: "Interactive Verification of Switched-Current Sigma-Delta Modulators", Proc. of 1998 IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 2.157-2.160.

<sup>†††.</sup> $IM_s \equiv 3HD_3$  is a more appropriate parameter for characterizing HD in BP- $\Sigma\Delta$ Ms.