# A Thesis Submitted for the Degree of PhD at the University of Warwick

# **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/110580/

# **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# On the implementation of P-RAM algorithms on feasible SIMD computers

A thesis submitted

for the degree of Doctor of Philosophy

by

RIDHA ZIANI

Department of Computer Science

University of Warwick

August 1992

# ACKNOWLEDGMENTS

I wish to express my gratitude to Dr. Alan Gibbons for his supervision, guidance and patience during the years I spent at Warwick.

I also would like to thank the members of the Computer Science Department for all the assistance I had and the Algerian government for financial support.

Finally, I am grateful to my family, to Janette and to many of my friends for all the moral support I had during the years.

#### DECLARATION

This is a thesis submitted to the University of Warwick in support of my application for admission to the degree of Doctor of Philosophy. It contains the account of my own work performed in the Department of Computer Science of the University of Warwick under the general supervision of Dr. Alan Gibbons. No part of it has been submitted in support of an application for another degree or qualification of this or any other institution of learning. The work described in this thesis is the result of my own independent research except where specifically acknowledged in the text.

Parts of this work have been presented or appeared as follows:

- (i) Techniques for the efficient implementation of some P-RAM algorithms on the Meshconnected computer, 5<sup>th</sup> British Colloquium on Theoretical Computer Science, Royal Holloway and Bedford New College, London University, Egham, April 1989.

- (ii) The Balanced binary tree technique on Mesh-connected computers, Information Processing letters 37, January 1991, 101-109.

# On the implementation of P-RAM algorithms on feasible SIMD computers

#### ABSTRACT

The P.BAM model of computation has proved to be a very useful theoretical model for exploiting and extracting inherent parallelism in problems and thus for designing parallel algorithms. Therefore, it becomes very important to examine whether results obtained for such a model can be translated onto machines considered to be more realistic in the face of current technological constraints.

In this thesis, we show how the implementation of many techniques and algorithms designed for the P-RAM can be achieved on the feasible SIMD class of computers.

The first investigation concerns classes of problems solvable on the P-RAM model using the recursive techniques of compression, tree contraction and 'divide and conquer'. For such problems, specific methods are emphasised to achieve efficient implementations on some SIMD architectures. Problems such as list ranking, polynomial and expression evaluation are shown to have efficient solutions on the 2-dimensional mesh-connected computer.

The balanced binary tree technique is widely employed to solve many problems in the P-RAM model. By proposing an implicit embedding of the binary tree of size n on a  $(\sqrt{n} \times \sqrt{n})$  mesh-connected computer (contrary to using the usual H-tree approach which requires a mesh of size  $\approx (2\sqrt{n} \times 2\sqrt{n})$ ), we show that many of the problems solvable using this technique can be efficiently implementable on this architecture. Two efficient  $O(\sqrt{n})$  algorithms for solving the bracket matching problem are presented. Consequently, the problems of expression evaluation (where the expression is given in an array form), evaluating algebraic expressions with a carrier of constant bounded size and parsing expressions of both bracket and input driven languages are all shown to have efficient solutions on the 2-dimensional mesh-connected computer.

Dealing with non-tree structured computations we show that the Eulerian tour problem for a given graph with m edges and maximum vertex degree d can be solved in  $O(d\sqrt{m})$  parallel time on the 2-dimensional mesh-connected computer.

A way to increase the processor utilisation on the 2-dimensional mesh-connected computer is also presented. The method suggested consists of pipelining sets of iteratively solvable problems each of which at each step of its execution uses only a fraction of available PE's.

The techniques and subproblems investigated in this thesis are of such commonality in the design of parallel algorithms that they could be usefully implemented as a library of resource on feasible markines.

# Contents

| Des | igning | algorithms for parallel computer       |      |    |   |    |    |    |    |     |         |  | 5  |

|-----|--------|----------------------------------------|------|----|---|----|----|----|----|-----|---------|--|----|

| 1.1 | Introd | uction ,                               | -    |    |   |    |    |    |    |     | <br>    |  | 5  |

| 1.2 | Machi  | ne Models of parallel computation      |      |    |   |    |    |    |    |     | <br>    |  | 8  |

|     | 1.2.1  | Flynn's classification                 | , .  |    |   |    |    |    |    |     | <br>. , |  | 8  |

|     | 1.2.2  | Schwartz's classification              |      |    |   |    |    |    |    | -   | <br>    |  | 10 |

|     | 1.2.3  | The SIMD class of computers            | ٠.   |    |   |    |    |    |    |     | <br>    |  | 10 |

| 1.3 | Comp   | exity theory of parallel computation . |      |    |   |    |    |    |    |     | <br>    |  | 20 |

|     | 1.3.1  | Limits of parallel models of computat  | tion |    |   |    |    |    |    |     |         |  | 21 |

|     | 1.3.2  | The NC class of problems               |      |    |   |    |    |    |    |     |         |  | 23 |

| Tec | hnique | s for efficient problem solving on     | SI   | MI | D | co | mj | рu | te | era |         |  | 25 |

| 2.1 | Introd | uction                                 |      |    |   |    |    |    |    |     | . ,     |  | 25 |

| 2.2 | The b  | alanced binary tree method             |      |    |   |    |    |    |    |     |         |  | 26 |

| 2.3 | The co | muression technique                    |      |    |   |    |    |    |    |     |         |  | 28 |

| 2.4                                                      | The tree contraction technique                                    | 29 |  |  |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|

| 2.5                                                      | The 'divide and conquer' technique                                | 29 |  |  |  |  |  |  |  |  |

| 2.6                                                      | The doubling technique                                            | 30 |  |  |  |  |  |  |  |  |

| 2.7                                                      | Efficient data distribution                                       | 31 |  |  |  |  |  |  |  |  |

| 2.8                                                      | Non-conventional input schemes                                    | 35 |  |  |  |  |  |  |  |  |

| 2.9                                                      | Graph emheddings                                                  | 37 |  |  |  |  |  |  |  |  |

| 2.10                                                     | Augmenting architectures                                          | 40 |  |  |  |  |  |  |  |  |

| Tools for efficient problem solving on SIMD computers 42 |                                                                   |    |  |  |  |  |  |  |  |  |

| 3.1                                                      | Introduction                                                      | 42 |  |  |  |  |  |  |  |  |

| 3.2                                                      | Sorting on SIMD computers                                         | 45 |  |  |  |  |  |  |  |  |

| 3.3                                                      | Routing on SIMD computers                                         | 46 |  |  |  |  |  |  |  |  |

|                                                          | 3.3.1 The routing problem                                         | 4  |  |  |  |  |  |  |  |  |

|                                                          | 3.3.2 Simulation of P-RAM's                                       | 4  |  |  |  |  |  |  |  |  |

|                                                          | 3.3.3 Deterministic routing on feasible architectures             | 41 |  |  |  |  |  |  |  |  |

|                                                          | 3.3.4 Randomised routing                                          | 5: |  |  |  |  |  |  |  |  |

| 3.4                                                      | Prefix sums                                                       | 5  |  |  |  |  |  |  |  |  |

|                                                          | 3.4.1 Implementation of the P-RAM prefix computation algorithm on |    |  |  |  |  |  |  |  |  |

|                                                          | the 2-dimensional mesh-connected computer                         | 5  |  |  |  |  |  |  |  |  |

| 3.5                                                      | The Euler tour technique                                          | 5  |  |  |  |  |  |  |  |  |

|   |     | 3.5.1 Implementation of the Euler tour technique                      | OU |

|---|-----|-----------------------------------------------------------------------|----|

|   | 3.6 | The ear decomposition technique                                       | 61 |

|   | Con | npression, tree contraction and 'divide and conquer' on feasible      |    |

| I | MD  | computers                                                             | 63 |

|   | 4.1 | Introduction                                                          | 63 |

|   | 4.2 | A simple case                                                         | 64 |

|   |     | 4.2.1 Naive implementation                                            | 66 |

|   |     | 4.2.2 Some improved results                                           | 67 |

|   | 4.3 | Generalisations                                                       | 70 |

|   | 4.4 | Enlarging the class of problems efficiently solvable on feasible SIMD |    |

|   |     | computers                                                             | 75 |

|   |     | 4.4.1 Solving the list ranking problem                                | 80 |

|   | 4.5 | Solving the dynamic expression evaluation problem                     | 83 |

|   | 4.6 | Improving the processor utilisation                                   | 81 |

| 5 | Th  | e balanced binary technique on feasible SIMD computers                | 94 |

|   | 5.1 | Introduction                                                          | 9- |

|   | 5.2 | Implicit representation of the balanced binary tree                   | 9  |

|   | 5.3 | Elementary examples                                                   | 10 |

|   |     | 5.3.1 Partial sums computation                                        | 10 |

|   |        | 5.3.2 Subsequence ranking                                 | 104   |

|---|--------|-----------------------------------------------------------|-------|

|   | 5.4    | Solving the bracket matching problem                      | 106   |

|   | 5.5    | Another solution to the bracket matching problem          | 115   |

| 8 | Fine   | ding Euler tours on feasible SIMD computers               | 120   |

|   | 6.1    | Introduction                                              | 120   |

|   | 6.2    | Eulerian property of graphs                               | . 121 |

|   | 6.3    | Parallel approaches to solve the Eulerian circuit problem | . 122 |

|   |        | 6.3.1 Outline of algorithm 1                              | . 12: |

|   |        | 6.3.2 Outline of algorithm 2                              | . 124 |

|   | 6.4    | Algorithm on MCC <sup>2</sup>                             | . 12  |

|   |        | 6.4.1 Detailed description:                               | . 12  |

| 7 | Co     | nclusions                                                 | 13    |

| В | liblia | graphy                                                    | 14    |

# Chapter 1

# Designing algorithms for parallel computers

# 1.1 Introduction

Unlike serial computation where a more unified approach is taken in the design and analysis of algorithms, the situation in parallel computing is quite different. To say the least, the variety of parallel algorithms that exist, do not all fit in a general framework (see, e.g. [GR88], [A85], [A89], [U84]) since the intricacies brought to light by the idea of making a collection of processors cooperate to achieve a task, are not fully understood.

Amongst many issues the notions of organisation and nature of the parallel models of computation have been a dividing factor in the community of algorithmic researchers. Those who are motivated by mere intellectual challenge have taken many liberties regarding the feasibility factor of parallel machines. In contrast, those who have been motivated by the desire of making full use of current available parallel computers are being more realistic regarding the technological limits. In this respect, parallel machines can be separated into two broad categories, namely the abstract or ideal models and the more realistic or feasible ones.

Parallel algorithms differ from their sequential counterparts in the approach used in their design. The different ways for proceeding to solve a problem on a parallel machine are to parallelise a sequential algorithm, to adapt a parallel solution from one machine to another or simply to design a new solution right from scratch.

Benefiting from previous work by trying to detect and exploit any inherent parallelism in an existing sequential algorithm is a task that has proved not to be easy. Many elegant sequential solutions to some problems have been found very hard to parallelise, they include problems such as depth first search [V91], the Eulerian circuit problem [AIS84] or simply the very old problem of finding the great common divisor of two natural numbers [H87].

The second alternative which is to implement or readapt a parallel algorithm initially designed to run on a different model is very appealing. However, practice has shown that it has many drawbacks if some issues such as inter-processor communications are not properly handled.

When there is no possibility to follow the above paths then the last resort is

to invent a new parallel algorithm right from scratch.

This thesis follows the second approach. It will be shown that many algorithms designed for an ideal model such as the P-RAM (using a predefined amount of time and resources) can be implemented on more feasible machines within realistic bounds. This is mainly achieved as follows:

- by adapting the algorithmic techniques used in the design of these P-RAM algorithms.

- by implementing some basic and widely used P-RAM tools incorporated in these algorithms.

The algorithmic techniques treated in this thesis are introduced in chapter 2 along with techniques of a different nature which also share the goal of facilitating the design of parallel algorithms. In chapter 3 we present a set of tools or library candidate routines which include widely used simple P-RAM algorithms and utilities as well as routines that are essential to use in a realistic parallel setting.

But prior to this, the rest of this chapter is devoted to the different models of parallel computation concentrating mainly on the SIMD class of computers. The differences that exist amongst them as well as the ways in which they relate to each other are highlighted. It will also present the limits of these parallel models by introducing a few notions from parallel complexity theory.

# 1.2 Machine Models of parallel computation

In the field of parallel algorithmic design, researchers and problem solvers have used several models of computation, ranging models such as the sorting network of the three Hungarians Ajtai, Komlos and Szemerdi [AKS83] to the various machines that are now commercially available like the highly publicised Connection Machine [Hi85]. The differences between these lie essentially in their structure on the one hand and on their behaviour or the way in which they handle data on the other. As it will be seen later, these factors allow a clear distinction to be made between what is by today's technological standards a theoretical model in contrast to what is called a practical or realistic model. This abundance of models has pushed for their categorisation or classification under different criteria. In the literature many different such classifications exist. We have retained the two most commonly used ones and from which the terminology of this thesis is borrowed. They are the classifications of Flynn [F66] and Schwartz [S80].

### 1.2.1 Flynn's classification

The earliest and most used classification of parallel models of computation, based on the notion of synchronicity and the number of data and instruction streams handled in parallel, is due to Flynn [F66] who distinguishes four classes of machine as follows:

SISD (Single Instruction stream, Single Data stream) class. Machines in this class are those performing one instruction at a time on one set of data. The traditional sequential computers belong to this class.

- 2. SIMD (Single Instruction stream, Multiple Data stream) class. This class contains the parallel machines that allow the simultaneous execution of one instruction on possibly different sets of data. A so-called enable/disable mask (e.g. an if then block) selects the processing elements that are allowed to execute operations on their assigned data. The ICL/DAP (Distributed Array Processor), The ILLIAC IV, the Burroughs PEPE and the Goodyear Aerospace MPP are examples of computers that belong to this class [HB85].

- 3. MISD (Multiple Instruction stream, Single Data stream). This category which has received very little attention except in domains such as signal and image processing (computer vision) comprises machines that perform multiple sets of instructions on a single stream of data [A89].

- 4. MIMD (Multiple Instruction stream, Multiple Data stream) class. This class, which is considered as the most general and most powerful class of machines, includes those performing different sets of instructions on different sets of data. An MIMD computer is either synchronous or asynchronous. In the former case all processing elements perform each successive set of instructions simultaneously, whereas in the latter, the processors run independently and wait only if information from other processors is needed. An example of an asynchronous MIMD machine is the Denelcor/HEP (Heterogeneous Element Processor) [HB85].

### 1.2.2 Schwartz's classification

Schwartz [S80] classifies parallel computers according to the method in which information is passed amongst the processors; an issue which is of crucial importance in parallel computing environments. He calls a paracomputer, a parallel computer whose processors can have simultaneous access to a shared common memory and thus who can communicate in constant time. Whereas a parallel computer where each processor has its own memory and where inter-processor communication is achieved only via a fixed interconnection network is referred to as an ultracomputer.

## 1.2.3 The SIMD class of computers

The focus of this thesis is on the SIMD class which consists of the two categories of paracomputers and ultracomputers where PE's operate synchronously in a lock-step fashion. That is, the PE's are synchronised to perform the the same function at the same time. The next sections look at the standard paracomputer or shared memory model of computation (the P-RAM) as well as widely used interconnections networks that have characterised ultracomputers in general.

#### 1.3.2.2 The P-RAM model of computation

The most popular model amongst parallel algorithms designers is the P-RAM (Parallel Random-Access Machine) model introduced by Fortune and Willie [F78]. This model is much liked because of its simplicity and great power to express

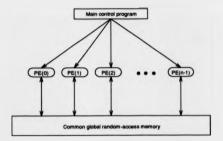

Figure 1.1: The P-RAM diagram

parallelism. A P-RAM is a collection of n processors (throughout the thesis, the abbreviation PE will be used to denote a processing element and PE(i) will denote the processor with index i) indexed from 0 to n-1 which synchronously execute the same program (through the central main control) and which communicate via a common random access global memory. Each processor is a RAM (Random Access Machine [AHU74]) capable of executing standard operations in constant time. Figure 1.1 schematically shows the P-RAM model.

The P-RAM model neglects the hardware limitations that an actual parallel computer would impose, particularly arising from how the processors are connected. It implicitly assumes that all different connections between processors and memory locations exist and thus communication takes constant time. Such an assumption is unrealistic due to the impracticality of wiring processor to memory when the number of processors and the size of the memory are large. However

this does not alter the fact that the P-RAM is a very powerful model for the design of parallel algorithms in general and explicitly employs the parallelism of problems.

Variations of the P-RAM model exist, which are based on protocols for reading and writing information from the global memory. Whether a model will allow or prohibit concurrent reads (many PE's trying to read the same memory location) or concurrent writes (many PE's trying to modify the contents of the same memory location), affects its strength. Consequently three subclasses of the P-RAM model are distinguished in order of increasing strength:

- (i) Exclusive-Read, Exclusive-Write (EREW) P-RAM. In this model no two processors are simultaneously allowed to read from or write into the same memory location.

- (ii) Concurrent-Read, Exclusive Write (CREW) P-RAM. Many processors are allowed to synchronously read from the same memory location, but no concurrent writes are allowed.

- (iii) Concurrent-Read, Concurrent-Write (CRCW) P-RAM. Both multiple read and multiple-write are allowed.

Writing conflicts of the CRCW are resolved by setting arbitration rules among contending processors. Some commonly employed resolution methods are:

(a) All processors writing into the same memory location must write the same value. If such a rule is adopted, then the model is called a Common model.

- (b) Any processor involved in a writing conflict may succeed and a task performed by the model must work correctly regardless of which one succeeds.

A model where this rule is chosen is called an Arbitrary model.

- (c) The minimum indexed processor in a conflict. If this rule is carried out then the model is called a Priority model.

The following [Ha91] illustrates the relative strengths of the variations of the P-RAM model:

$$EREW \le CREW \le Common \le Arbitrary \le Priority$$

#### 1.3.2.2 Feasible SIMD models

By a feasible or practical model of computation, it is meant (in contrast to the P-RAM model) a machine that can be constructed using current technology.

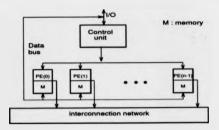

A feasible SIMD computer (as shown in figure 1.2) consists of n processing elements (indexed from 0 to n-1) all of which are under the control of on control unit (CU) and communicating through an interconnection network. Each PE has its own working registers and memory (M). The CU has also its own memory for the storage of programs which can be loaded from an external source. The function of the CU is to determine where the instructions should be executed and subsequently bradcasted to the appropriate PE's. All the PE's perform the same function synchronously in a lok-step step fashion under the command of the CU.

Data is loaded into the PE's from external sources via a data bus or via the CU.

Figure 1.2: The diagram of a feasible SIMD computer

PE's may be active or disabled for executing a given operation [HB85]. Data exchanges among the PE's are achieved via the interconnection network which is also under the control of the CU.

Feasibility of machine models of parallel computation also depends on the number of links from each PE in the network being bounded by a manageable integer (i.e. constant or at most growing logarithmically with the size of the network) and the maximum path length within an architecture being small enough to allow fast communications. These two quantities are often referred to as the degree (d) and diameter (D) of the architecture. A simple block diagram for an SIMD computer is shown in figure 1.2.

Different network topologies lead to different SIMD architectures in respect to the parameters diameter and degree. In what follows we present a catalogue of networks referring occasionally to PE's as nodes of a graph (the interconnection network).

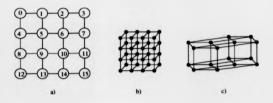

Figure 1.3: 2. 3 and 4-dimesional meshes

a) The Mesh-Connected Computer (MCC) family. The mesh-connected class of computers has received wide attention in the literature merely because of the fact that one of the first commercialised parallel computers, the ILLIAC IV had a mesh structure. In general such a structure may be thought of as a collection of n PE's logically arranged in a q-dimensional array  $A(n_{q-1}, n_{q-2}, ..., n_0)$ , where  $n_i$  is the number of PE's in the i<sup>th</sup> dimension and  $n = n_{q-1} \times n_{q-2} \times n_{q-2}$ ...  $\times$   $n_0$ . The PE at location  $A(i_{q-1},...,i_0)$  is connected to the PE's at location  $A(i_{q-1}, \dots i_{j\pm 1}, \dots, i_0), \ 0 \le j < q$ , provided they exist. Varying the sizes of the dimensions of a mesh obviously modifies the diameter (D) of the architecture which is given by the simple formulae  $D=\sum_{q=1}^n(n_{q-1}-1)$  and the degree d which is bounded by 2q. When all the dimensions have the same size,  $D = q(n^{1/q} - 1)$ . Figure 1.3.(a) shows a  $(4 \times 4)$  MCC where the processors are indexed according to a natural order i.e. from left to right, top to bottom. Other indexing schemes for the 2-dimensional MCC (MCC will represent a q-dimensional mesh) will be seen in later sections. Figures 1.3.b and 1.3.c show respectively  $(4 \times 4 \times 2)$  and  $(2 \times 2 \times 2 \times 2)$  meshes.

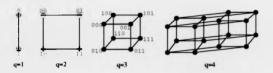

Figure 1.4: 1, 23 and 4-dimensional hypercubes

- b) The Cube-Connected Computer (CCC) or hypercube family. The hypercube topology is one of the most common structures adopted for many recent parallel computers such as (for instance) the famous Connection Machine mentioned earlier [Hi85], [TW91]. A hypercube or CCC of dimension q is a machine with  $N=2^q$  PE's each having a distinct label or index  $i \in \{0...N-1\}$  such that links exist only between the PE's having the binary representation of their indices differ in exactly one position. Formally PE(i) with the binary representation of i being  $i_{q-1} \dots i_{0+1}$  is connected to the q PE's with the binary indices equal to  $i_{q-1} \dots i_{0+1}$ , where  $c(i_b)$  is the complement of  $i_b$  and  $0 \le b < q$ . The degree and diameter of the hypercube architecture are both equal to  $\log N = q$  (all logarithms used in thesis are of base 2). The recursive construction of a hypercube of dimension q from 2 hypercubes of dimension q-1 is shown in figure 1.4 for the hypercubes of dimensions 2, 3 and 4.

- e) The perfect shuffle and the deBruijn family of networks. Another architecture having the desired property of small degree and diameter is the perfect shuffle network. Like the hypercube, the perfect shuffle computer (PSC) or shuffle exchange network of dimension g has  $N = 2^g$  PE's. Each processor whose index is

Figure 1.5: A shuffle-exchange network with 8 processors

connected to the three processors PE(j), PE(shuffle(i)) and PE(unshuffle(i)). The operations shuffle (cyclic left shift) and unshuffle (cyclic right shift) are defined on i as follows: if the binary representation of i is  $i_{p-1}i_{p-2}...i_1i_0$ , then  $shuffle(i) = i_{p-2}...i_1i_0i_{p-1}$  and  $unshuffle(i) = i_0i_{p-1}...i_1$ . PE(j) denotes the PE whose index j differs from i only in the least significant bit. The connections PE(i) to PE(j) are called exchange connections and the remaining are referred to as shuffle connections. A PSC has constant vertex degree d=3 and its diameter is  $2\log N-1$ . Figure 1.5. shows a shuffle-exchange network with q=3.

A deBruijn network is similar to the shuffle-exchange network except that the exchange connections are replaced by the so-called 'exchange-shuffle' connections. This last type of connection links PE(i) to PE(j) if and only if the binary representation of i and shuffle(j) differ in their least significant bit [L92]. A deBruijn network has d=4 and  $D=\log N$  as shown in figure 1.6 for such a network with q=3.

d) The Tree Structured Computer (TSC) family. Trees are an important tool in structuring computations in both the sequential and parallel domains and

Figure 1.6: A deBruijn network with 8 processors

Figure 1.7: A tree network with 15 processors

therefore it is natural that they have been proposed as useful networks, at least for some applications. A tree structured network is a collection of  $N=2^p-1$  PE's forming a complete binary tree with p levels numbered 0 to p-1. The PE at level i is connected to its parent at level i+1 (except when it is the root) and to its two children at level i-1 (except when it is a leaf). The degree of the tree architecture is obviously bounded by 3 and its diameter is  $2 \log (N+1)$ . A (15 PE) TCC is illustrated in figure 1.7.

e) Other networks. Other networks commonly encountered are considered to be variations or enhanced versions of some of the architectures mentioned above. For instance the cube connected cycles computer and the butterfly network can be regarded as hypercubes with a fixed number of connections for every PE. The cube connected cycles computer is a hypercube where each of the 27 processors.

Figure 1.8: A cube-connected cycles network with 24 processors

Figure 1.9: A butterfly network with 32 processors

is replaced by a cycle of q PE's, hence it has  $n=q2^{\circ}$ . The diameter of the architecture is  $2\log n$  and the degree is 3. Figure 1.8 illustrates such an architecture for q=3.

The butterfly network of dimension q has  $n=(q+1)2^q$  processors organised in (q+1) ranks numbered from 0 to q and each having  $2^q$  PE's. The diameter of the architecture is  $2\log n$  and the maximum degree is 4. Figure 1.9 shows a butterfly of dimension 3.

Finally, other networks in the same vein are the X-tree computer shown in

Figure 1.10: The X-tree and double rooted binary tree networks

figure 1.10 (a) with 3 levels, and the double rooted binary tree structured computer shown (with 4 levels) in figure 1.10 (b) which are regarded to be variations of the Tree Structured Computer. Some additional networks appear under the headings of future sections.

For the sake of comprehending the limits of parallel models of computation in general, we review a few notions in complexity theory.

# 1.3 Complexity theory of parallel computation

Bearing in mind the impact that complexity theory has had in sequential computation, a similar theory in the parallel field has proved essential. This section outlines aspects of that theory relevant to algorithmic design which lead to an understanding of the theoretical limits of parallel models of computation as well as providing important tools for assessing parallel computation itself.

## 1.3.1 Limits of parallel models of computation

Limits for parallel computation can be derived on different bases. On an upper level, these limits are in strict relation with the nature of the problems to be solved. That is, problems could be classified in terms of computations, between two extremes. On the one hand, there are those whose computations could be entirely fragmented into independent tasks and thus are well suited to be executed in parallel constant time. On the other hand, there are those that are basically sequential in nature and remain hardly parallelisable even if unbounded parallel execution is available.

Regarding intractability, the question whether parallelism can be used to solve intractable (NP hard) problems in reasonable (polynomial) parallel time is pertinent. On sequential models of computation, NP hard problems have polynomial time solutions if nondeterminism is used [Ka86]. Emulating the strategy of guessing by using sufficient numbers of PE's on parallel machines, will also lead to what seems to be reasonable parallel time solutions even for the NP-complete problems. Nevertheless if that seems to indicate that intractability is removed by using parallelism, we note that in order to obtain such solutions, the number of PE's needed becomes impractical since computation trees will have exponential path lengths.

For problems that are conjectured to have no reasonable sequential solutions, the question whether these problems have reasonable parallel solutions is still open. This is shown by a key concept in parallel complexity theory which is the so-called parallel computation thesis, see, e.g. ([G82], [CKS81]). This thesis states that 'time bounded parallel machines are polynomially related to space bounded sequential machines'. In other words this implies that if a problem is solved sequentially using a certain amount of space, say S(n) for inputs of length n, then it can be solved in parallel in time that is no worse than  $S(n)^{O(1)}$  (i.e. polynomial in S(n)), this is symbolically written: Sequential-PSPACE = Parallel-PTIME. Thus our question is simply reduced to whether the class PSPACE contains problems that can be proved not to have polynomial time sequential solutions.

Other limits that can be derived are those considering technological constraints on certain models of computation. Using Schwartz's terminology [S80], it is an obvious fact that an ultracomputer can never solve a problem faster than a paracomputer due to communication overheads. However, an ultracomputer could match the performance of a paracomputer in terms of time complexity for the solution of a given problem, if the communication pattern is good enough. As a consequence any theoretical upper limits derived for ultracomputers hold for paracomputers and conversely for the lower limits.

On an ultracomputer the performance of an algorithm may depend on the relationship between the quantity (n) of data handled and the number (p) of PE's available (This problem is often ignored on paracomputers because of the allowance of unbounded parallelism). In real applications one could be faced with the problem of having fewer PE's than data items (n > p).

In contrast there is the rare situation where one has to solve a problem with

fewer data items than the PE's available. In this case the processors that could have been idle may be used to speed up calculations. For instance Nassimi and Sahni have shown (see [S80]) that  $n^{1-\delta}$  numbers can be sorted in  $O(\delta^{-1} \log n)$  time on an n-processor ultracomputer despite the fact that n elements are sorted in  $O(\log^{\delta} n)$  time.

For some problems the first situation (as it will be seen in more detail) can be adopted to achieve optimal speedups. For example, to compute the sum or product of n integers, a straightforward way could be to structure the computation in a a binary tree form by assigning one integer to every PE at the lowest level of the tree. Using such mappings these type of computations can be achieved in  $O(\log n)$  due to inter-processor communication as we go up along the tree. This blind version of a sequential linear time algorithm is considered as not fast enough and can be much improved by distributing data more efficiently.

#### 1.3.2 The NC class of problems

The major reason for introducing parallelism in problem solving on computers is unarguably to reduce running times. It is in accordance with this exigence that the class Parallel-PTIME (the class of problems solvable in parallel polynomial time) cannot really be considered as a good standard for specifying efficient solutions.

Consequently, another norm to characterize efficiency in parallel environments

was put forward. This norm conveys a main objective namely the achievement

of sublinear running times for solving a wide range of problems. Solutions are regarded as efficient only if they are achieved in polylogarithmic time and using a polynomial number of processors. The problems solvable within these limits belong to the class NC. NC is an acronym for Nick (Pippenger)'s Class.

Many problems that belong to class P are also known to belong to NC. Multiplication, division, sorting and other very well known problems have all been solved in polylogarithmic  $O(\log^{O(1)} n)$  parallel time (see for example [GR88], where various problems are treated).

Unfortunately, and as for the case of problems in NP for which no polynomial time sequential algorithms have yet been found, some problems in P seem to be very difficult to solve in polylogarithmic parallel time. A problem of this kind is finding the greatest common divisor (gcd) of two integers. Although Euclid found a polynomial time 'sequential' algorithm for it 2300 years ago, no one has yet managed to find a way to speed up the computations involved [H87].

This implies the fact that problems in P cannot all be claimed to belong to NC, whereas the opposite is true, implying (although no concrete proof exists) that the classes P and NC are distinct.

# Chapter 2

# Techniques for efficient problem solving on SIMD computers

# 2.1 Introduction

The advent of parallel computers, whether theoretical or practical has led to the emergence of new techniques and paradigms for solving problems with the goal of achieving optimal and/or efficient bounds defined by many criteria. Efficiency bounds depend on the computational environment. Within the P-RAM model, the class NC defines efficiency. For shared memory models, the network diameter provides a natural lower bound on computation time. For instance on a  $(\sqrt{n} \times \sqrt{n})$  mesh, a useful definition of an efficient algorithm is an algorithm that runs in  $O(\sqrt{n})$  parallel time for a problem of size n. For the hypercube family and networks of diameter =  $O(\log n)$ , algorithms are efficient if they run in  $O(\log n)$

time. For our purposes we will also define an algorithm to be nearly efficient if it runs within a  $\log^k n$  (for some integer k) of the diameter of an architecture.

Moreover, a parallel algorithm is called optimal ([GR88], [KR91]) if the product  $P = \text{(parallel running time} \times \text{number of PE's used)}$  is a linear function of the input size or equal to the running time of the best sequential algorithm that solves the same problem.

Our goal in this chapter is to describe a set of techniques that differ in nature and to highlight for some the issues related to their future use in later chapters. At first, emphasis will be put on those which are qualified as algorithmic techniques such as the balanced binary tree, the doubling technique and others. Most of these rely extensively on the tree structure which in parallel computation appears in many facets. Then techniques that help tackle or incorporate solutions to the important issue of communication overheads are presented. These appear under the headings efficient data distribution and non-conventional input schemes. Finally, the technique of embedding structures (such as trees) on interconnection networks and that of hardware enhancing are introduced.

# 2.2 The balanced binary tree method

Although chapter 5 is almost entirely devoted to the balanced binary tree method on feasible SIMD computers to solve many problems efficiently, the aim of this section is to present it in a P-RAM context. Issues related to the implementation of alsorithms where this method is applied on more feasible machines (the same is valid for all the algorithmic methods) are highlighted.

This method makes use of a constructed balanced binary tree. Internal nodes store the result of subproblems with the root corresponding to the global problem. Solutions to problems structured in this way are found in a bottom-up fashion with those at the same level of the tree being computed (combined) in parallel. For instance problems involving the computations of quantities such as  $A(0) \oplus A(1) \oplus A(n-2) \oplus \ldots \oplus A(n-1)$  over an array  $[A(0), \ldots, (n-1)]$  where  $\oplus$  is a binary associative operator and n is a power of two (otherwise a minimum number of neutral dummy elements are added) are best achieved using this method [GR88].

On a P-RAM the above quantity is computed in  $O(\log n)$  parallel time with a maximum number of n/2 processors (using A(1) to store the final result) by executing the following:

$$\begin{aligned} d &\leftarrow (n-1)/2 \\ \text{repeat until } d &= 0 \\ \text{begin} \\ \text{for all } j : 0 &\leq j \leq d \text{ in parallel do} \\ A(j) &\leftarrow A(2j) \oplus A(2j+1) \\ d &\leftarrow (d-1)/2 \end{aligned}$$

end

Some algorithms might use the balanced binary tree technique just to compute some partial results. The implementation or design of such algorithms on feasible SIMD computers will undoubtedly depend in the first place on the nature of the computations to be performed after the construction of the tree. These computations requiring a resident constructed tree in the architecture will have a variety of data exchanges requirements (as will be seen in later chapters). Thus necessitating the application of other techniques to satisfy these requirements in the best possible way.

# 2.3 The compression technique

The aim of using the compression technique is to recursively reduce a set of entities acted upon by a factor of 2 by performing required computations. In its simplest manifestation this technique is applied to data structures such as, for instance, arrays where two entries can be compressed into a single one. This is in some cases equivalent to the use of the balanced binary tree method. But the non-trivial power of compression is highlighted in many graph algorithms where it is referred to as the vertex collapse technique. Amongst these are the ones that find the connected components of a graph where the strategy is to reduce sets of vertices into supervertices (see [QD84]). On a P-RAM, compression usually leads to  $O(\log n)$  solutions because of the absence of communications overheads. But on distributed memory machines such as feasible SIMD computers where data is spread across the network, this is not always implemented in a straightforward fashion. Chapter 4 is partly devoted to the use of the compression technique on feasible SIMD computers where various problems are treated.

# 2.4 The tree contraction technique

The tree contraction technique was initially designed to evaluate arithmetic expression given in a tree form [MR85], [GR88], but since then it has found a much wider applicability [KR91]. This technique is that of shrinking a binary rooted tree with an irregular height by recursively computing internal nodes. If a tree of size n has height  $\log n$ , then this method is equivalent to the compression technique. In chapter 4 we show that a P-RAM expression evaluation algorithm (using this method) can be efficiently implemented on some feasible computers.

# 2.5 The 'divide and conquer' technique

The way of proceeding when using the very well known technique of 'divide and conquer' ([AHU74], [GR88], [K85]) is to divide a given global problem into a number of independent subproblems and then to solve these in a recursive manner. The depth of the recursion is an important factor when adopting this technique as it determines the parallel running time for solving the overall problem.

At any level of the recursion the solution to anyone problem is found independently (from problems on the same level) by combining solutions to its subproblems. On a P-RAM, if subproblems have each a size which is at least a fixed proportion of the problem they compose, then the depth is logarithmic.

Formally, the divide and conquer strategy has the following recursive structure. Given a problem P: If P is decomposable into smaller problems

#### then

Divide P into two or more parts  $(P_1, P_2, \dots, P_n)$

# In parallel

Solve Pr

Solve Pa

\*\*\*

Solve Pn

Combine the partial solutions to obtain a solution to P

# else

solve P directly.

The use of the divide and conquer technique on feasible SIMD machines is also treated in chapter 4 (along with compression and tree contraction) since all the algorithmic techniques presented are not entirely disjoint.

# 2.6 The doubling technique

The doubling technique is usually applied to data structures such as 1-dimensional arrays and lists. A necessary definition before briefly describing this technique is that of the distance between two elements in these data structures. In a 1 dimensional array this distance may be thought of as the difference between the indices of two elements and in a list of it represents the number of pointer jumps

from one element to another.

The doubling technique proceeds by a recursive application of the required calculation to all elements over a certain distance (in the data structure) from each individual element. This distance is doubled at each iteration. For arrays or lists of length  $n=2^k$ , a P-RAM computation using the doubling technique will be completed for each element after  $k=\log n$  stages. The implementation of the doubling technique for performing some computations such as ranking the elements of a list on computers such as the  $MCC^2$  is also treated in chapter 4.

# 2.7 Efficient data distribution

Data distribution can have a significant effect on the amount of execution time of parallel algorithms since adopting the right data distribution has proved to improve on communication costs and consequently on execution times. Data distribution is affected by the number of PE's available or the mapping of data items to PE's at the start of a computation. Although unbounded parallelism is allowed, it is often the case that on P-RAM's fewer PE's than data items are used to solve a problem and this within the same time complexity as if it was to be solved with a number of PE's equal to the input size.

A typical example on which this way of proceeding is best illustrated is the computation of quantities such as  $Q = A(1) \oplus A(2) \oplus A(3) \oplus \ldots \oplus A(n)$  over an array  $A = [A(1), \ldots, A(n)]$  by the use of the balanced binary tree. As seen earlier a P-RAM algorithm can compute this quantity in  $O(\log n)$  parallel time

with p ≤ n/2 PE's.

The idea behind reducing the number of processors comes from the fact that at each iteration of our algorithm (equivalent of climbing the balanced binary tree) the number of PE's used is reduced by a factor of 2 making a high proportion of them become idle. One way to reduce such an effect is that p < n/2 PE's can be used and still lead to an  $O(\log n)$  solution. The strategy is to partition the n elements of the given array into p groups (every PE will be in charge of 1 group) where p-1 of them will contain  $\lceil n/p \rceil$  elements and the remaining group will only contain  $(n-(p-1)\lceil n/p \rceil)$  elements. All the p PE's in parallel then compute a quantity similar to Q within their assigned group in a sequential manner. For any group the maximum number of computations of the type  $A(i) \oplus A(j)$  is bounded by  $\lceil n/p \rceil - 1$  implying that the problem of computing quantities such as Q (of size n) could be reduced to a problem of size p in  $\lceil n/p \rceil - 1$  time units. This newly created problem is then solved using the balanced binary tree method in  $O(\log p)$  parallel time.

Thus, the overall computation of Q can be achieved in  $\lceil n/p \rceil - 1 + \log p$  parallel time using p < n/2 processors. If  $p = n/\log n$ , then this is done in an optimal fashion. A more general approach to this problem is the application of Brent's theorem which states that if an algorithm A has a parallel running time of t and if A involves a total number of l computations, then A can be implemented using p processors in O(l/p + t) time. [GR88] contains a simple proof of Brent's theorem.

Incidentally this same approach is sometimes forced to be adopted in real par-

allel environments and has proved to be extremely useful as it drastically reduces inter-processor communication [AL81]. For example the cost of external sorting is very expensive and thus one would have to adapt existing sorting algorithms (based on element per PE) and to assume the availability of enough memory space to store a reasonable amount of data. A typical example is the k-fold bitonic sort algorithm of Hsiao and Shen [HS85] who adapt Batcher's bitonic sort [B75] on the  $MCC^2$  to sort sequences containing more elements than the number of PE's available.

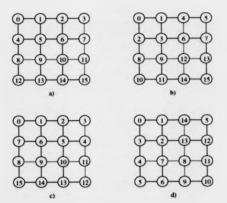

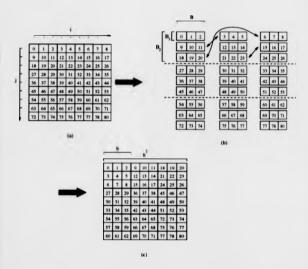

In the case of a one-to-one mapping of input data items to the PE's of a parallel computer, we consider such a mapping to be efficient if it allows the design of efficient algorithms. On a P-RAM we do not need to worry as on this model all mappings are equivalent with regard to communication costs. However, on machines such as the  $MCC^2$ , this issue is sometimes fundamentally important in the design of efficient algorithms. The PE's of a  $(\sqrt{n} \times \sqrt{n})$   $MCC^2$  can be indexed according to many indexing schemes which are one-to-one mappings from the coordinate space  $\{0, 1, ..., \sqrt{n}\} \times \{0, 1, ..., \sqrt{n}\}$  onto the index space  $\{0, 1, ..., n-1\}$  each baving properties that makes it suitable for particular applications. Figure 2.1 shows the four most popular indexing schemes of a  $MCC^2$ .

The row-major indexing or identity indexing (Figure 2.1.a) which is based on a top to bottom, right to left ordering seems to be the most natural way of indexing the PE's of a mesh but appears only to be suitable for computations with very low inter-processor communication [MS88] such as for instance, the

Figure 2.1

very simple problem of adding n numbers. Problems with high inter-processor communication such as sorting do not perform well on the  $MCC^2$  with such an indexing. The algorithm in [O75] requires  $O(\sqrt{n}\log n)$  parallel time to sort a sequence of length n due to such an indexing.

Another indexing which has received much attention due to its properties is the shuffled row major indexing (Figure 2.1.b). Such an indexing which is based on the recursive division of the PE's of the mesh into quadrants can be useful in designing algorithms based on the 'divide and conquer' strategy and thus involving a great deal of communication between PE's.

Two other indexing schemes to be used on a mesh are the snake-like order and

the proximity order (Figures 2.1.c and 2.1.d). The former which has the property that successively indexed PE's are adjacent has also proved to be very useful. For instance, Schnorr and Shamir [SS86] use such an indexing to design a very simple efficient algorithm for sorting on the (MIMD)  $MCC^2$ . The latter indexing combines the advantages of some of the other indexings and is based on space filling curves. Like the shuffled row major order, this indexing recursively divides the mesh into quadrants and like the snake-like order, successively indexed PE's are adjacent. Miller and Stout [MS89] use such an indexing to design efficient algorithms for a wide range of problems in computational geometry.

In later chapters when trying to solve a variety of problems, other advantages and shortcomings of indexing schemes such as the ones described in this section will be highlighted.

# 2.8 Non-conventional input schemes

Another way for easing difficulties such as communication overheads when solving problems on feasible parallel computers is to use non conventional input schemes. In these schemes no data is stored in the PE's memory at the start of a computation but is rather input gradually maintaining a balance between communication and computation.

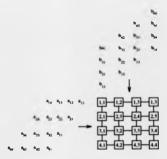

A very simple algorithm to use such a scheme is the algorithm of Guibas et al. [GKT79] to compute the transitive closure of a directed graph. In this algorithm (Boolean) matrix multiplication is achieved in  $O(\sqrt{n})$  parallel time

Figure 2.2

(for two  $(\sqrt{n} \times \sqrt{n})$  matrices on a  $MCC^2$  with  $(\sqrt{n} \times \sqrt{n})$  PE's) by the use of a skewed input scheme as shown in Figure 2.2 (for two matrices denoted A and B). At each step of the computation, matrix A is pushed one step to the right and matrix B is pushed one step down, and each PE (identified in this case by its geometric coordinates (i,j)) multiplies the values it receives  $(a_{ij}$  and  $b_{ij})$  and adds the result to an accumulator. After precisely  $2\sqrt{n} - 1$  steps every PE(i,j) will contain the required value  $(\sum_{k=1}^{n} a_{ik}b_{kj})$ .

Amongst other algorithms that use a similar kind of input scheme and which can be regarded as a sort of data pipelining, is the  $O(\sqrt{n})$  algorithm of Maggs and Plotkin [MP88] for finding the minimum-cost spanning tree of an n-vertex undirected graph on a  $(\sqrt{n} \times \sqrt{n})$   $MCC^2$ .

# 2.9 Graph embeddings

Another general approach for efficient problem solving is the embedding of structures such as graphs (in particular trees) in interconnection networks. Such embeddings are of a great interest in simulation studies. For example, embedding trees in some interconnection networks may efficiently simulate a P-RAM algorithm based on such structures. Moreover, inter-mapping of topologies on which interconnection networks are based would provide a view on how efficiently a particular network might simulate another [U84].

In graph theoretical terms, an embedding of a graph G (called the guest graph) into another graph H (called the host graph) is a mapping of the edges of G into paths of H such that each vertex of G maps to a single vertex of H. The quality of an embedding is usually measured by three parameters:

- a) dilation which is equal to the maximum length of any path in the host graph to which an edge of the guest graph is mapped.

- b) expansion which is the ratio of the number of nodes of the host to the number of nodes in the guest.

- c) congestion which is the maximum number of paths (mappings of the guest graph) using any edge of the host graph.

Considering only embeddings where at most one node of the guest is associated

Figure 2.3

with any single node of the host and labeling the dilation, the expansion and congestion respectively as d, e, and c, we note for instance from [Gi91] that the double rooted binary tree embeds in the hypercube (with the same size n) with d=1, e=1 and c=1, and that any mesh with n nodes whose dimensions are each a power of two is a subgraph of its optimum hypercube. By optimum hypercube, we mean the smallest possible hypercube with n' nodes such  $n \le n'$  Ullman [U84] describes embeddings of complete binary trees and other graphs in a VLSI context.

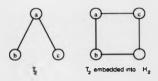

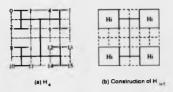

In what follows we describe how the complete binary tree  $T_n$  (of height n) with  $2^n - 1$  nodes can be optimally embedded in the hypercube of dimension n with  $2^n$  nodes (denoted  $H_n$ ) following Wu's method [W85]. For n = 1, it is trivial to see that  $T_1$  can be embedded in the hypercube of dimension 0 ( $H_0$ ). For n > 1 there is no embedding of  $T_n$  into the hypercube  $H_n$  with d (dilation) = 1 unless n = 2. Thus,  $T_2$  can be embedded in the 2-dimensional hypercube with d = 1 and c = 1 as shown in figure 2.3.

From [W85], a complete binary tree of height n > 2 can be embedded into a hypercube of dimension n + 1 ( $H_{n+1}$ ) with d = 1 and into a hypercube  $H_n$  with d=2. The second claim is proved by showing first that there exists no embedding with dilation = 1 and by stating two properties that the embedding with dilation = 2 must satisfy to finally prove by induction that these properties hold for all values of n. These properties are called the cost2 Property and the Free Neighbor Property.

- 1) Cost2 Property: If A is the root of T<sub>n</sub> and L and R are respectively the roots of its left and right subtrees, then the distance between the vertices that A and L are mapped to in the n-dimensional hypercube H<sub>d</sub> is 2 while that between the vertices that A and R are mapped to is 1.

- 2) Free Neighbor Property: The only free (no vertex of the hinary tree is mapped onto it) node in the hypercube is a neighbour to the node to which the root of T<sub>n</sub> is mapped.

From an embedding with d=2 of a binary tree  $T_{n-1}$  into a hypercube of n-1 dimensions  $(H_{n-1})$  that verifies the two above stated properties, Wu [W85] obtains an embedding of  $T_n$  with d=2 into the n-dimensional hypercube  $H_n$  that will also verify these properties by the following construction.

i) Embed the left subtree of T<sub>n</sub> into 0H<sub>n-1</sub> (0H<sub>n-1</sub> denotes the dimension n - 1 of H<sub>n</sub> comprised by the vertices (PE's) whose most significant bit is 0). Let 0A be the vertex in H<sub>n</sub> to which the root of the left subtree is mapped to and let 0B be its free neighbour.

ii) Embed the right subtree of  $T_n$  into  $1H_{n-1}$   $(1H_{n-1}$  denotes the dimension n-1 of  $H_n$  formed by the vertices (PE's) whose most significant bit is 1). Let 1A be the vertex in  $H_n$  to which the root of the right subtree is mapped to and let 1B be its free neighbour.

# iii) Map the root of Hn to the vertex (PE) 1B.

Again we have given a flavor of the technique of embedding graphs because we rely on such a technique to show (in chapter 5) that it is important in the efficient implementation of other techniques (such as the balanced binary tree) on feasible SIMD computers.

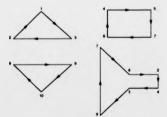

# 2.10 Augmenting architectures

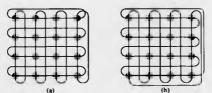

Another technique for speeding up applications on parallel computers is the addition of extra hardware or features to a particular architecture. This consists of adding extra simple connections between PE's, extra PE's and connections or buses for conveying data in a faster fashion. The issue of adding extra connection to an architecture is best illustrated on the 2-dimensional mesh connected computer which can be enhanced by the so-called 'wrap-around' (figure 2.4(a)) or 'toroidal' (figure 2.4(b)) connections [HB85]. Unfortunately this type of enhancement will only help reduce time complexity terms (for certain problems) by constant factors due to the fact that it only speeds up communications by offering shortcuts within the architecture. In the case of the MCC<sup>2</sup> with 'wrap-around'

Figure 2.4

connections the diameter is halved. The addition of extra connections might add to the properties of an architecture. In chapter 4, we show that an augmented perfect-shuffle computer can support some P-RAM algorithms in a hetter way than its non-augmented counterpart.

Augmenting architectures by means of extra processing elements can also be illustrated on previously mentioned architectures. The 'Cube-Connected Cycles' computer proposed by Preparata and Villeumin [PV81] can in a way be regarded as opting for augmenting the cube-connected or hypercube computer by means of extra processing elements. They showed that if every PE in a CCC is replaced by a cycle consisting of a fixed number of PE's, then the result is a very powerful interconnection network. The same thing could be said about the q-dimensional Mesh Connected Computer which can be considered as the superimposition of q 2-dimensional MCC's, a structure that has attracted many by its topological simplicity.

# Chapter 3

# Tools for efficient problem solving on SIMD computers

#### 3.1 Introduction

The continually growing body of parallel algorithms has undoubtedly highlighted the importance of many paradigms. In the previous chapter we described a variety of techniques ranging from algorithmic to hardware enhancing. Our purpose here is to review some primary algorithms (or library candidate routines) and other utilities that have proved very useful in the design of parallel algorithms.

A logical consequence of identifying such primary algorithms and utilities is the establishment of a structural consistency amongst parallel algorithms, at least for those that relate to a common domain. Vishkin [Vi91] illustrates such a concept very elegantly by compiling different structures for many types of problems and by stressing the usefulness of many simple algorithms and utilities.

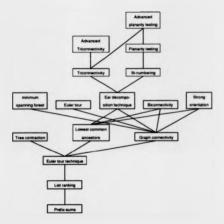

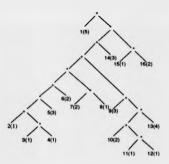

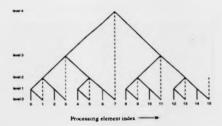

For instance, for some list, tree and graph problems, the structure compiled (of which an extract is shown in figure 3.1) is for problems whose solutions on the P-RAM model of computation are known to be in NC. This structure shows that solutions to problems or utilities higher in the diagram incorporate solutions to problems or utilities lower in the diagram. As an example the solution to the prefix sums problem (bottom of figure 3.1) is a key subroutine in the solution to the list ranking problem which is itself a key subroutine used the utility called the Euler tour technique. Further up, this structure shows that the technique of tree contraction or the problems of finding the lowest common ancestors (lca's) and graph connectivity make use of the Euler technique.

On feasible interconnection networks, Vishkin's structure [Vi91] holds from a relational point of view. That is, one can always solve any problem as on the P-RAM model of computation using the same primary algorithms and utilities but with modified time complexities. For instance on the  $MCC^2$  (with a diameter of  $2\sqrt{n}$ ) it will take at least  $O(\sqrt{n})$  time to solve each problem in figure 3.1. Communication overheads are closely responsible for this lower bound on this computation time. Solutions to the communication or routing problem must be therefore included in such a structure because assumptions about the execution of algorithms on interconnection networks becomes worthless without their inclusion. Another important problem related to the communication problem and which should also be included in such a structure is sorting.

Figure 3.1: List, tree and graph problems linkage

In what follows, along with sorting and communication strategies on feasible machines we look at a set of primary algorithms and utilities that have greatly facilitated the design of algorithms on the P-RAM model. These are the prefix computation problem, the Euler tour technique and the ear decomposition technique.

#### 3.2 Sorting on SIMD computers

Sorting on a parallel computer with n PE's, is the problem of reordering a set of n keys so that at the end of the computation the  $i^{th}$  smallest key is stored at the  $i^{th}$  PE. Understandably it is one of the problems that has attracted a lot of interest within the community of parallel algorithms researchers. This has led to numerous solutions on various models of parallel computation which range from the implementation of known sequential sorting algorithms to a variety of new concepts (see for instance [A85]).

For the P-RAM model of computation, many sorting algorithms have been proposed (see for example [C86], [BH82], [SV81] and [P78]). The latest result is the  $O(\log n)$  (optimal) algorithm of Cole [C86] to sort a sequence of n items using n processors. Implementing P-RAM sorting algorithms or designing new ones on many realistic machines within optimal bounds has often been prohibited by the high inter-processor communication requirements of the sorting problem.

Instead solutions based on circuit comparators such that of Batcher [B68] have been proposed for feasible SIMD machines. For instance Nassimi and Sahni

[NS78] and Thompson and Kung [TK77] mapped Batcher's bitonic sort in  $O(\sqrt{n})$ on the q-dimensional mesh-connected computer. Similarly it was implemented on n PE's architectures such as the hypercube [RS90], the perfect-shuffle [S71] and the cube-connected cycles architectures [PV81] in  $O(\log^2 n)$  parallel time.

Unlike the case for the MCC, the question of sorting on these architectures in times proportional to their diameters (i.e  $O(\log n)$ ) is still open. More recently Cypher and Plaxton [CP90] obtained an  $O(\log n(\log \log n)^4)$  for sorting a sequence of n elements on an n-PE's hypercube.

# 3.3 Routing on SIMD computers

A major problem in parallel computing on distributed memory machines is how to organise communication through the interconnection network for data exchanges between the processors. Frequently, the cost of routing is the dominating term in the time required to solve a problem on such machines. Amongst others, the algorithm of Thompson and Kung [TK77] for sorting a sequence of n numbers on a  $(\sqrt{n} \times \sqrt{n})$  mesh connected computer, where the PE's are indexed according to the shuffled row major order, uses only  $O(\log n)$  comparison steps but has  $O(\sqrt{n})$  routing steps. Solving the routing problem also arises when trying to simulate particular operations of a machine such as the P-RAM on more realistic machines.

#### 3.3.1 The routing problem

Depending on the application, routing on a parallel computer can occur in different forms as defined by Ullman [U84]:

Permutation routing occurs when each PE requests access to the memory of another distinct PE. Partial routing occurs when each PE of a proper subset uniquely accesses a memory location. In many-one routing each PE requests an access to some memory and many PE's may request access to the same memory. As some requests could be nullified, this form of routing is seen as a generalisation of Partial routing.

Formally the routing problem on an n PE's parallel (distributed memory) model of computation could be stated as follows: Each PE with index  $i \in I = [0..n-1]$ , initially contains an address  $a(i) \in \{0, 1, ..., n-1\} \cup \emptyset$  of another destination PE. The communication requirement to satisfy depends on the specification of the elements of the set A:

It is a permutation routing iff:  $\forall i, j (i \neq j) \in I$  we have  $a(i) \neq a(j) \neq \emptyset$ . It is a partial routing iff:  $\forall i, j (i \neq j) \in I$  we have  $a(i) \neq a(j)$  provided  $a(i) \neq \emptyset$ .  $a(j) \neq \emptyset$  and it is a many-one routing iff:  $\forall i \in I$  we have  $a(i) \neq \emptyset$ .

#### 3.3.2 Simulation of P-RAM's

Finding solutions to the routing problem in its various forms on distributed memory machines allows the simulation of read and write operations of ideal parallel computers such as the P-RAM. For instance, solutions to permutation routing can simulate the EREW P-RAM since it does not allow either concurrent reads nor concurrent writes. The more powerful CRCW can be simulated by a solution to the many-one form of routing on condition that arbitration rules are set to resolve writing conflicts [U84].

Moreover, there are two ways for solving all forms of the routing problem. The first is to proceed deterministically and the second is to use randomness. The difference between the two methods lies in the way of choosing intermediate PE's when messages are routed. The next two sections outline solutions from both methods. Having to deal with the SIMD class of computers, we are therefore restricted to the instance of the problem where all the requests made by the processors are done in a synchronous fashion.

#### 3.3.3 Deterministic routing on feasible architectures

In deterministic routing, a message is wholly directed from a source PE to a target PE via other PE's chosen deterministically.

Permutation routing can be reduced to sorting and therefore messages can be routed using compare-exchange and near-neighbour routing operations. It has efficient deterministic solutions on many architectures. On the 2-dimensional MCC, the algorithms of Nassimi and Sahni [NS81] and Thompson and Kung [TK77] that run in  $O(\sqrt{n})$  parallel time for n-items permutations serve our purpose. Further algorithms that also perform the same task in the same time order have been designed to improve on the constant factor of the leading complexity term [SS86]. On architectures such as the (n PE's) CCC or PSC, the results of [RS90], [S71] reported in the previous section for solving the n-items permutations achieve our goal on these machines but only in  $O(\log^4 n)$  parallel time. The desired complexity is of course  $O(\log n)$  which is proportional to the diameters of such architectures, but the only known method is to use randomness.

In the following section, an outline of a deterministic solution to the many-one form of the routing problem is presented. Moreover, such a solution encompasses solutions to all the other forms. The algorithm which is extensively used in this thesis as a library routing procedure on the  $MCC^2$  is due to Nassimi and Sahni [NS81]. It achieves the goal of running, within a constant factor of the optimum time of  $2\sqrt{n}$ . This algorithm was also designed for machines such as cube connected (CCC) and perfect shuffle (PSC) computers and runs in  $O(\log^2 n)$  on such networks of size n. The  $O(\log n)$  (probabilistic) algorithms of Valiant and Brebner [VB81] (section 3.3.4) and Aleliunas [Al82] are rather preferred for these architectures to execute partial or permutation routing.

#### Nassimi and Sahni's routing algorithm

The algorithm of Nassimi and Sahni [NS81] allows the simulation of concurrent read and write operations of the P-RAM model of computation on more realistic machines by the use of the techniques of compacting and replicating data.

Nassimi and Sahni [NS81] identify the routing problem in two forms. The

first is called the Random Access Read (RAR) and occurs when a PE wishes to acquire a data item from another PE, not necessarily a direct neighbour. The second is called the Random Access Write (RAW), and occurs when a PE wants to send (transmit) a data item to another processor.

RAR and RAW require some well defined subalgorithms (procedures) called sort, rank, concentrate, distribute and generalise. These, manipulate records containing data to be routed as well as other routing information. They can be briefly described as follows:

Sort This procedure simply sorts a sequence of records (G(i)'s) held by the PE's of the MCC in non-decreasing order on the key target which is the address to which data is to be sent to, or read from. If H(i) is the key target then after an application of **sort**, records will be rearranged so that:

$$H(i) \le H(i+1), \ 0 \le i \le N-1 \ (N : total number of PE's)$$

Again, Nassimi and Sahni's [NS79] and Thompson and Kung's [TK77] sorting algorithms are amongst the known algorithms to achieve this task in a strict SIMD context.

Rank The objective of rank is to assign to each selected record held by a PE a rank which is the number of selected records held by other PE's having a smaller index. A record is selected if it is held by the PE with the highest index amongst the (sorted) set of PE's requesting the same address. Suppose we

have the following set of records:  $(a, b, e, e^*, a, a^*, e^*, f^*)$  (a starred value denotes a selected record), then the output of rank is (-, -, -, 0, -, 1, -, 2, 3)

Concentrate The main goal of procedure concentrate is to displace the ranked records to the PE's whose indices equal the ranks computed in the previous step. Let  $G(i_r)$   $(0 \le r \le j < N)$  be a set of records initially stored in PE $(i_r)$  and assume that these records have been ranked so that  $H(i_r) = r$ . A concentrate results in record  $G(i_r)$  being moved to PE(r).

**Distribute** Distribute is the inverse of procedure concentrate. Its purpose is to move records to the PE's whose indices equal the addresses carried by these records. Let G(i)  $(0 \le i \le i < N)$  be a set of records with G(i) in PE(i). Let H(i)  $(0 \le i \le j)$  be a set of destinations such that H(i) < H(i+1)  $(0 \le i \le j)$ . Distribute routes G(i) to PE(H(i))  $(0 \le i \le j)$ .

Generalise The purpose of generalise is to copy (replicate) a record held by a PE with an index equal to the rank of this record into all the PE's whose indexes are less or equal to the address carried by this record. let G(i) ( $0 \le i \le j < N$ ) be stored in PE(i). Each record has a field H such that  $0 \le H(0) \le H(1) \le \ldots \le H(j) \le N-1$  and  $H(i) = \infty$  j < i < N. Generalise makes copies of record G(i) in PE(H(i-1) + 1) through PE(H(i))  $0 \le i \le j$ . H(-1) = 0.

An RAR (simulating concurrent reads) is performed using (in order) sort, rank, concentrate, distribute, concentrate, generalise and finally sort. The RAW problem (simulating concurrent writes) is simpler to deal with than

the RAR. When no two PE's are sending data to the same PE then sort followed

by distribute will achieve our purpose. In the event where many PE's have the

same target PE, two cases are distinguished: Either only one PE is made to

succeed and thus, an arbitration rule among contending PE's has to be set, or

all requests to write are to be honored which results in compacting data from all

PE's. In both cases, the ordered sequence of subalgorithms to perform is sort,

rank, concentrate and distribute with the difference that dissimilar records

are manipulated for each case.

With all factors considered (including d which is the maximum number of data items to be written into any one PE), the overall time complexity of executing RAR's and RAW's on a q-dimensional MCC is respectively  $O(q^2n^{1/q})$  and  $O(q^2n^{1/q}+dqn^{1/q})$ . For an n PE's PSC or CCC, the time complexity of performing a RAR is  $O(\log^2 n)$  and it mounts up to  $O(\log^2 n+d\log n)$  for executing a RAW.

#### 3.3.4 Randomised routing

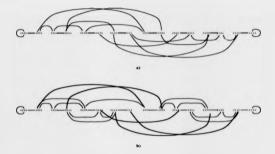

In randomised routing data is forwarded between a source PE and a target PE via intermediate PE's chosen at random. The algorithm of Valiant [V80] was the first algorithm to realise partial and permutation routing on a cube connected computer (CCC) with n processors in only  $O(\log n)$  parallel time. It performs well on other interconnections also [VB81]. The strategy employed is a two-

phase strategy and consists of first sending data from each PE (involved in the communication requirement) to another PE chc..en randomly and then to send the data to their true destinations.

#### Valiant and Brebner's routing algorithm

A high level description of this algorithm can be stated in two steps as follows:

- 1. For each PE(i) that wishes to send a data item (packet) to another PE(j), select randomly another index k by picking each of the n bits in the binary representation of k to be 0 or 1, independently, each with probability 1/2 and following a left-to-right routing strategy send (transmit) the data item to PE(k). In the i<sup>th</sup> step of a left to right strategy the data is routed so as to to correct the i<sup>th</sup> bit (from the left) of the current address of each datum compared with its destination. In case of competition for a wire (connection) to leave a PE, packets are queued and transmitted one at each step. The priority is given to the packet with the farthest destination.

- The packet, say from PE(i) having reached PE(k), is given again a left-toright route to its true destination PE(j) in a similar manner.

The time complexity of Valiant and Brebner's algorithm is  $O(\log n)$  with overwhelming probability for both the PSC and CCC architectures with n PE's. More precisely Valiant [V80] has shown that for the hypercube with n PE's the probability that messages will take more than  $8\log n$  time to be routed is less than (0.74<sup>log n</sup>). This probability converges towards zero exponentially with the dimension of the architecture.

#### 3.4 Prefix sums

The prefix sums or prefix computation problem is an important problem in various fields (see e.g. [Ki90]. For ease of description the problem is described as follows [GR88]: Given an associative binary operator  $\odot$  (e.g.  $min, max, +, \times$ ) and an array  $[A(1), A(2), \ldots, A(2n-1)]$ , compute  $A(n), A(n) \odot A(n+1), A(n) \odot A(n+1)$ , O(n+1) is store intermediate results.

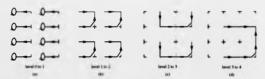

We describe below a P-RAM algorithm which uses the balanced binary tree method and runs in  $O(\log n)$  time with n PE's. The leaves of the tree initially contain the values  $(A(n), A(n+1), \dots, A(2n-1))$ . An auxiliary vector B is also needed to store intermediate and final results.

There are two phases in the computation. The first consists of constructing the balanced binary tree. This takes  $\log n$  steps after which, every non-leaf node contains  $(value(ls) \odot value(rs)$  (ls: left son, rs: right son). Results are stored in locations A(1) through A(n-1). This phase is described as follows:

for

$$k=(\log n)-1$$

step  $-1$  to  $0$  for all  $j,2^k\leq j\leq 2^{k+1}-1$  in parallel do

$$A(j) \leftarrow A(2j)\odot A(2j+1)$$

Figure 3.2: Prefix computation on a P.RAM