# On Multicast in Asynchronous Networks-on-Chip: Techniques, Architectures, and FPGA Implementation

## Kshitij Bhardwaj

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

## **ABSTRACT**

# On Multicast in Asynchronous Networks-on-Chip: Techniques, Architectures, and FPGA Implementation

## Kshitij Bhardwaj

In this era of exascale computing, conventional synchronous design techniques are facing unprecedented challenges. The consumer electronics market is replete with many-core systems in the range of 16 cores to thousands of cores on chip, integrating multi-billion transistors. However, with this ever increasing complexity, the traditional design approaches are facing key issues such as increasing chip power, process variability, aging, thermal problems, and scalability.

An alternative paradigm that has gained significant interest in the last decade is asynchronous design. Asynchronous designs have several potential advantages: they are naturally *energy proportional*, burning power only when active, do not require complex clock distribution, are robust to different forms of variability, and provide ease of composability for heterogeneous platforms.

Networks-on-chip (NoCs) is an interconnect paradigm that has been introduced to deal with the ever-increasing system complexity. NoCs provide a distributed, scalable, and efficient interconnect solution for today's many-core systems. Moreover, NoCs are a natural match with asynchronous design techniques, as they separate communication infrastructure and timing from the computational elements. To this end, globally-asynchronous locally-synchronous (GALS) systems that interconnect multiple processing cores, operating at different clock speeds, using an asynchronous NoC, have gained significant interest.

While asynchronous NoCs have several advantages, they also face a key challenge of supporting new types of traffic patterns. Once such pattern is *multicast communication*, where a source sends packets to arbitrary number of destinations. Multicast is not only common in parallel computing, such as for cache coherency, but also for emerging areas such as neuromorphic computing. This important capability has been largely missing from asynchronous NoCs.

This thesis introduces several efficient multicast solutions for these interconnects. In particular,

techniques, and network architectures are introduced to support high-performance and low-power multicast. Two leading network topologies are the focus: a variant mesh-of-trees (MoT) and a 2D mesh. In addition, for a more realistic implementation and analysis, as well as significantly advancing the field of asynchronous NoCs, this thesis also targets synthesis of these NoCs on commercial FPGAs. While there has been significant advances in FPGA technologies, there has been only limited research on implementing asynchronous NoCs on FPGAs. To this end, a systematic computeraided design (CAD) methodology has been introduced to efficiently and safely map asynchronous NoCs on FPGAs. Overall, this thesis makes the following three contributions.

The first contribution is a multicast solution for a variant MoT network topology. This topology consists of simple low-radix switches, and has been used in high-performance computing platforms. A novel *local speculation* technique is introduced, where a subset of the network's switches are speculative that *always broadcast* every packet. These switches are very simple and have high performance. Speculative switches are surrounded by non-speculative ones that route packets based on their destinations and also throttle any redundant copies created by the former. This hybrid network architecture achieved significant performance and power benefits over other multicast approaches.

The second contribution is a multicast solution for a 2D-mesh topology, which is more complex with higher-radix switches and also is more commonly used. A novel *continuous-time replication strategy* is introduced to optimize the critical multi-way forking operation of a multicast transmission. In this technique, a multicast packet is first stored in an input port of a switch, from where it is sent through distinct output ports towards different destinations concurrently, at each output's own rate and in continuous time. This strategy is shown to have significant latency and energy benefits over an approach that performs multicast using multiple distinct serial unicasts to each destination.

Finally, a systematic CAD methodology is introduced to synthesize asynchronous NoCs on commercial FPGAs. A two-fold goal is targeted: correctness and high performance. For ease of implementation, only existing FPGA synthesis tools are used. Moreover, since asynchronous NoCs involve special asynchronous components, a comprehensive guide is introduced to map these elements correctly and efficiently. Two asynchronous NoC switches are synthesized using the proposed approach on a leading *Xilinx FPGA in 28 nm:* one that only handles unicast, and the other that also supports multicast. Both showed significant energy benefits with some performance gains over a state-of-the-art synchronous switch.

# **Table of Contents**

| Li | List of Figures |               |                                                           | vi |

|----|-----------------|---------------|-----------------------------------------------------------|----|

| Li | st of T         | <b>Fables</b> |                                                           | X  |

| 1  | Intr            | ntroduction   |                                                           | 1  |

|    | 1.1             | Synch         | ronous Design: Challenges                                 | 3  |

|    | 1.2             | Async         | hronous Design: An Alternative Paradigm                   | 5  |

|    |                 | 1.2.1         | Advantages of Asynchronous Design                         | 5  |

|    |                 | 1.2.2         | Challenges with Asynchronous Design                       | 6  |

|    |                 | 1.2.3         | History and Overview of Recent Success                    | 7  |

|    | 1.3             | Netwo         | orks-on-Chip: An Introduction                             | 10 |

|    |                 | 1.3.1         | NoCs: Motivation, Basics, and Advantages                  | 10 |

|    |                 | 1.3.2         | Advances in Synchronous NoCs                              | 12 |

|    |                 | 1.3.3         | Advances in Asynchronous NoCs                             | 14 |

|    | 1.4             | Multic        | east Communication and its Applications                   | 16 |

|    | 1.5             | FPGA          | s: Architecture, and Applications                         | 18 |

|    |                 | 1.5.1         | FPGA Architecture                                         | 18 |

|    |                 | 1.5.2         | FPGA Applications                                         | 20 |

|    | 1.6             | Resear        | rch Focus                                                 | 20 |

|    |                 | 1.6.1         | Challenges with Supporting Multicast in Asynchronous NoCs | 21 |

|    |                 | 1.6.2         | Challenges with Implementing Asynchronous NoCs on FPGAs   | 22 |

|    | 1.7             | Contri        | bution of Thesis                                          | 22 |

|    | 1.8             | Organ         | ization of Thesis                                         | 24 |

| 2 | Bacl | kground | l: Asynchronous Design                                                   | 26 |

|---|------|---------|--------------------------------------------------------------------------|----|

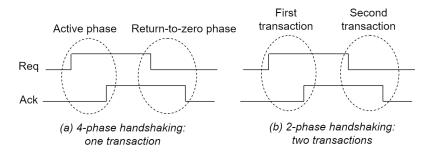

|   | 2.1  | Handsl  | haking Protocols                                                         | 26 |

|   |      | 2.1.1   | Four-Phase Protocol                                                      | 27 |

|   |      | 2.1.2   | Two-Phase Protocol                                                       | 27 |

|   |      | 2.1.3   | Trade-Offs                                                               | 28 |

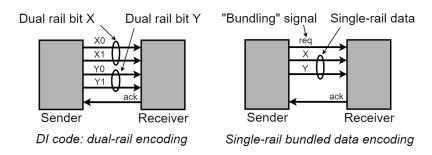

|   | 2.2  | Data E  | incoding Schemes                                                         | 28 |

|   |      | 2.2.1   | Delay-Insensitive (DI) Codes                                             | 28 |

|   |      | 2.2.2   | Single-Rail Bundled Data                                                 | 29 |

|   |      | 2.2.3   | Trade-Offs                                                               | 29 |

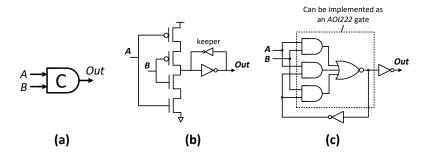

|   | 2.3  | Specia  | l Asynchronous Components                                                | 30 |

|   |      | 2.3.1   | The C-Element                                                            | 30 |

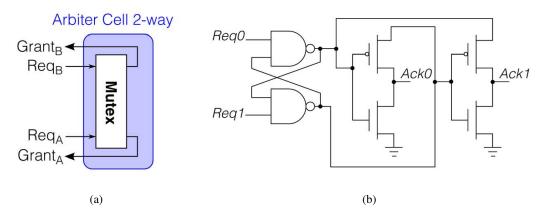

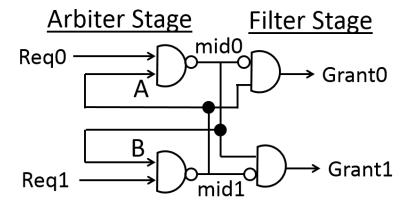

|   |      | 2.3.2   | The Mutex                                                                | 31 |

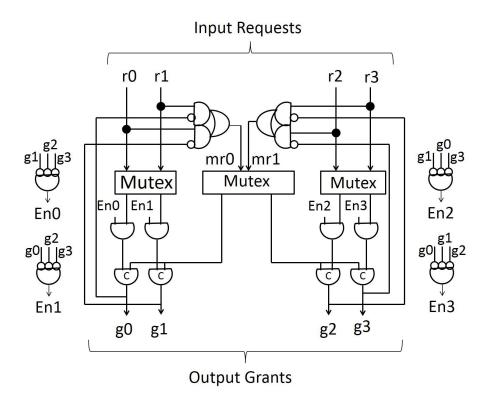

|   |      | 2.3.3   | The N-Way Arbiters                                                       | 32 |

|   | 2.4  | Mouse   | trap Pipelines                                                           | 34 |

|   |      | 2.4.1   | Mousetrap Structure                                                      | 34 |

|   |      | 2.4.2   | Mousetrap Operation                                                      | 34 |

|   |      | 2.4.3   | Timing Constraints                                                       | 35 |

|   | 2.5  | Mixed   | -Timing Interfaces                                                       | 35 |

| 3 | Bacl | kground | l: Networks-on-Chip                                                      | 38 |

|   | 3.1  | Netwo   | rk Topologies                                                            | 38 |

|   |      | 3.1.1   | A Variant MoT Topology                                                   | 39 |

|   |      | 3.1.2   | A 2D-Mesh Topology                                                       | 40 |

|   | 3.2  | Routin  | g Algorithms                                                             | 41 |

|   |      | 3.2.1   | Deterministic Routing                                                    | 42 |

|   |      | 3.2.2   | Oblivious Routing                                                        | 42 |

|   |      | 3.2.3   | Adaptive Routing                                                         | 42 |

|   | 3.3  | Packet  | Encoding Schemes                                                         | 43 |

|   | 3.4  | Synchi  | conous Unicast Router: Micro-Architectures and Performance Optimizations | 44 |

|   |      | 3.4.1   | A Traditional 5-Cycle Router                                             | 44 |

|   |      | 3 4 2   | Recent Single-Cycle Routers                                              | 45 |

|   |     | 3.4.3    | Extreme Bypassing in Single Cycle Using SMART NoCs     | 46 |

|---|-----|----------|--------------------------------------------------------|----|

|   | 3.5 | Multic   | ast Techniques and Related Work                        | 47 |

|   |     | 3.5.1    | Techniques                                             | 47 |

|   |     | 3.5.2    | Related Work                                           | 48 |

|   | 3.6 | Leadir   | ng Synchronous Multicast NoCs                          | 49 |

|   |     | 3.6.1    | Multicast Using Single-Cycle Routers                   | 49 |

|   |     | 3.6.2    | Multicast Using SMART NoCs                             | 49 |

| 4 | A L | ocal Spo | eculation Approach for Multicast in Mesh-of-Trees NoCs | 52 |

|   | 4.1 | Introdu  | action                                                 | 52 |

|   | 4.2 | Baseli   | ne Asynchronous NoC                                    | 53 |

|   |     | 4.2.1    | Fanout Node                                            | 55 |

|   |     | 4.2.2    | Fanin Node                                             | 56 |

|   |     | 4.2.3    | Results                                                | 57 |

|   |     | 4.2.4    | Baseline for the New Multicast Research                | 57 |

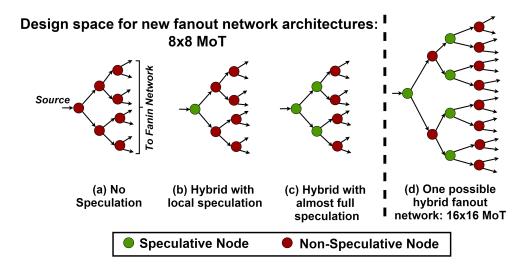

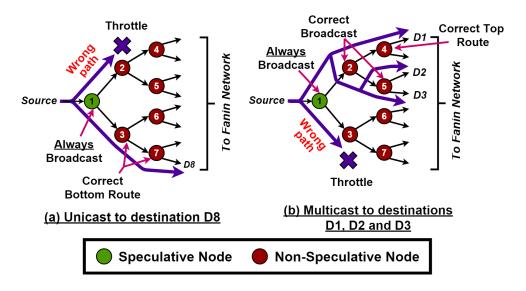

|   | 4.3 | Propos   | sed Multicast Approaches                               | 58 |

|   |     | 4.3.1    | Simple Tree-Based Multicast                            | 58 |

|   |     | 4.3.2    | Local Speculation-Based Multicast                      | 59 |

|   |     | 4.3.3    | Protocol Optimizations                                 | 61 |

|   |     | 4.3.4    | Target Parallel Multicast Networks                     | 62 |

|   | 4.4 | Propos   | sed Fanout Node Designs                                | 62 |

|   |     | 4.4.1    | Unoptimized Speculative Fanout Node                    | 62 |

|   |     | 4.4.2    | Unoptimized Non-Speculative Fanout Node                | 64 |

|   |     | 4.4.3    | Optimized Speculative Fanout Node                      | 68 |

|   |     | 4.4.4    | Optimized Non-Speculative Fanout Node                  | 71 |

|   | 4.5 | Experi   | mental Results                                         | 76 |

|   |     | 4.5.1    | Experimental Framework                                 | 76 |

|   |     | 4.5.2    | Node- and Network-Level Results                        | 78 |

|   | 4.6 | Conclu   | isions                                                 | 84 |

| 5 | A C  | ontinuo   | us-Time Replication Strategy for Multicast in 2D-Mesh NoCs               | 85  |

|---|------|-----------|--------------------------------------------------------------------------|-----|

|   | 5.1  | Introdu   | nction                                                                   | 85  |

|   | 5.2  | Baselin   | ne Asynchronous NoC                                                      | 86  |

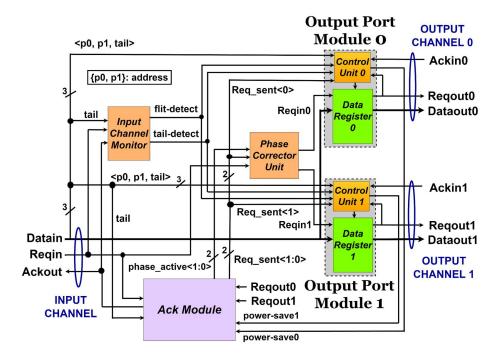

|   |      | 5.2.1     | The Baseline NoC Without VCs                                             | 87  |

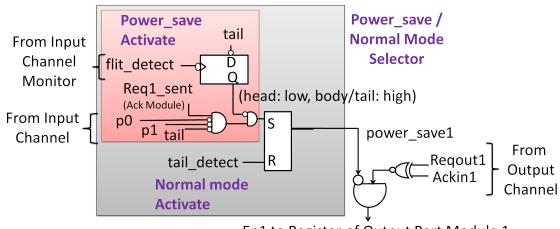

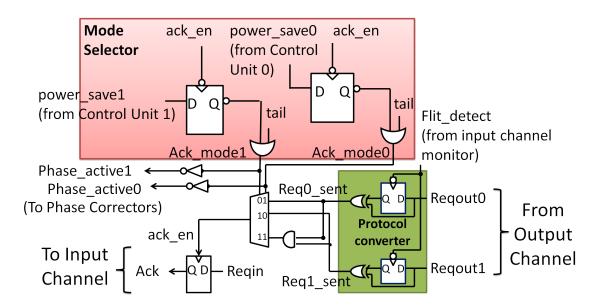

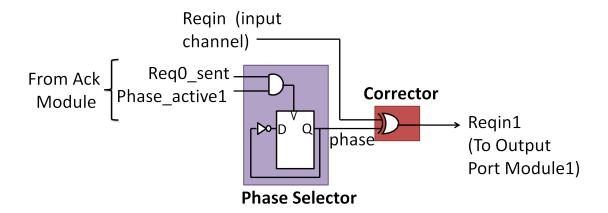

|   |      | 5.2.2     | Industrial Extension of the Baseline NoC to VCs                          | 92  |

|   | 5.3  | New M     | Iulticast Approach                                                       | 96  |

|   |      | 5.3.1     | Tree-Based Parallel Multicast                                            | 96  |

|   |      | 5.3.2     | Continuous-Time Replication Strategy                                     | 97  |

|   |      | 5.3.3     | Route Computation and Buffering Policy                                   | 98  |

|   |      | 5.3.4     | Simulation of Multicast Routing                                          | 99  |

|   |      | 5.3.5     | Resource-Dependent Deadlock Avoidance                                    | 101 |

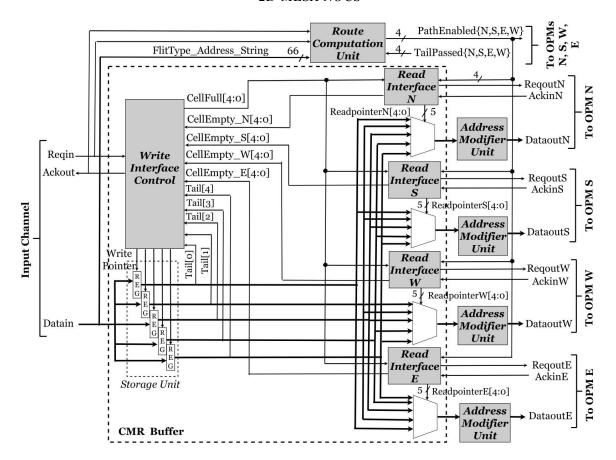

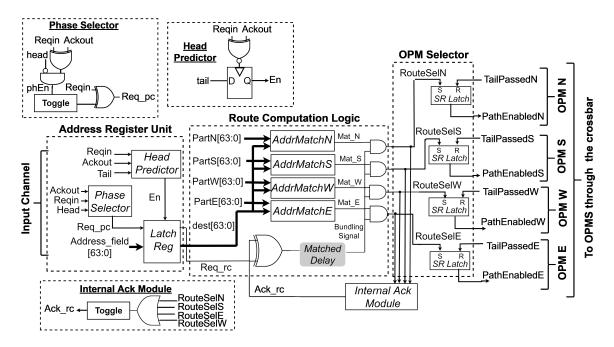

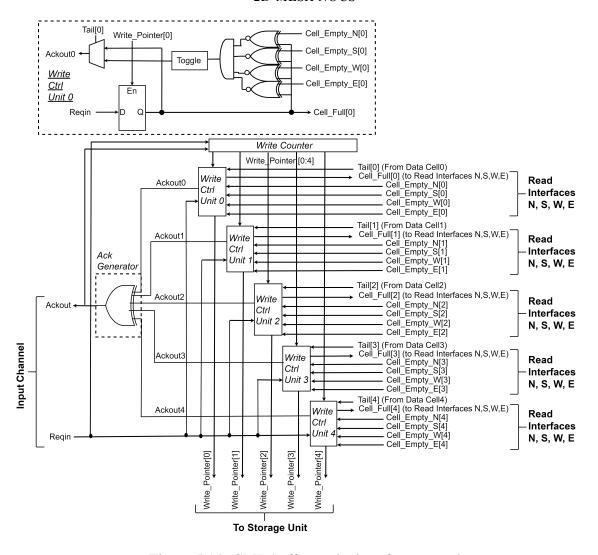

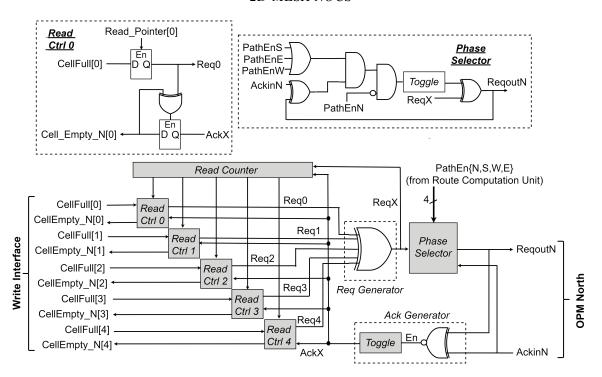

|   | 5.4  | Design    | Details: New Input Port Module (IPM)                                     | 104 |

|   |      | 5.4.1     | IPM Structure and Operation                                              | 104 |

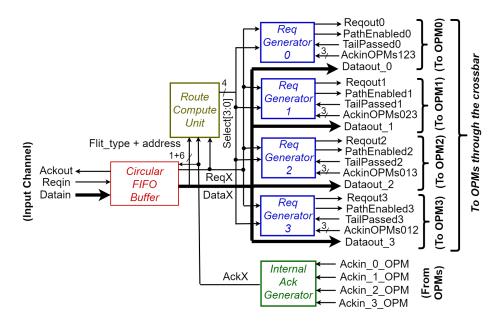

|   |      | 5.4.2     | Route Computation Unit (RCU)                                             | 106 |

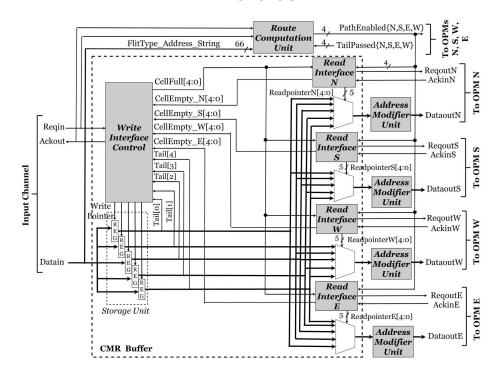

|   |      | 5.4.3     | CMR Buffer                                                               | 107 |

|   |      | 5.4.4     | Address Modifier Unit (AMU)                                              | 111 |

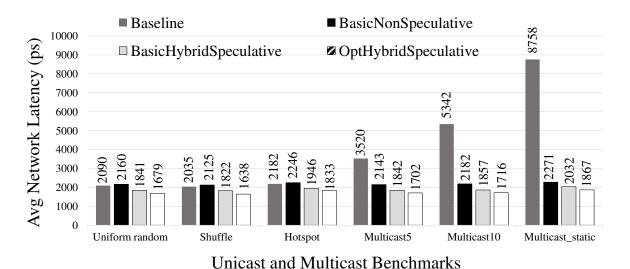

|   | 5.5  | Experi    | mental Setup and Node-level Results                                      | 112 |

|   |      | 5.5.1     | Experimental Framework                                                   | 112 |

|   |      | 5.5.2     | Node-Level Results                                                       | 114 |

|   | 5.6  | Networ    | rk-level results                                                         | 117 |

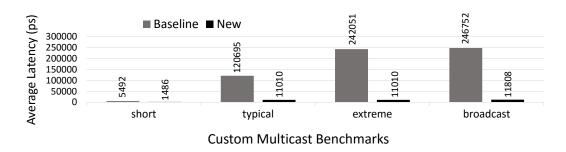

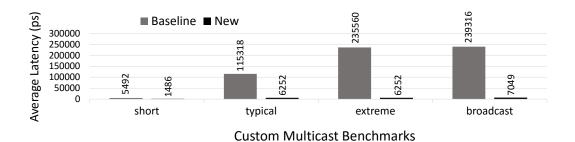

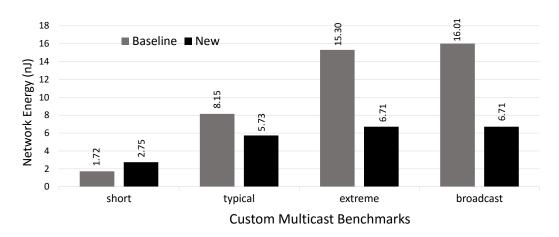

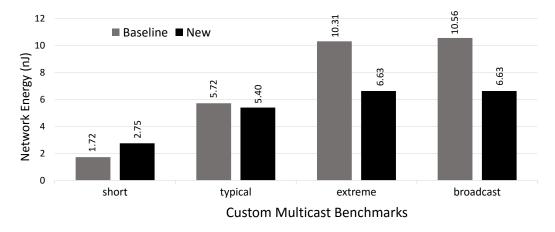

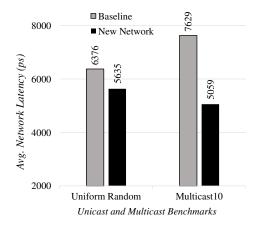

|   |      | 5.6.1     | Multi-Flit Network-Level Results                                         | 118 |

|   |      | 5.6.2     | Single-Flit Network-Level Results                                        | 127 |

|   |      | 5.6.3     | Analytical comparison with state-of-the-art synchronous multicast NoCs . | 128 |

|   | 5.7  | Conclu    | isions                                                                   | 131 |

| 6 | Synt | thesizing | g Asynchronous NoCs on FPGAs: a Systematic Methodology                   | 133 |

|   | 6.1  | Introdu   | action                                                                   | 133 |

|   | 6.2  | Implen    | nenting Asynchronous Circuits on FPGAs: Related Work                     | 135 |

|   | 6.3  | Mouse     | trap Pipeline and Timing Requirements of Bundled-Data Circuits: A Brief  |     |

|   |      | Backgr    | ound                                                                     | 136 |

|   |      | 6.3.1     | Mousetrap Pipeline                                                       | 136 |

|    |                             | 6.3.2  | Timing Requirements of Bundled-Data Circuits                   | 137 |

|----|-----------------------------|--------|----------------------------------------------------------------|-----|

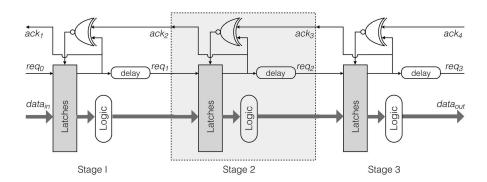

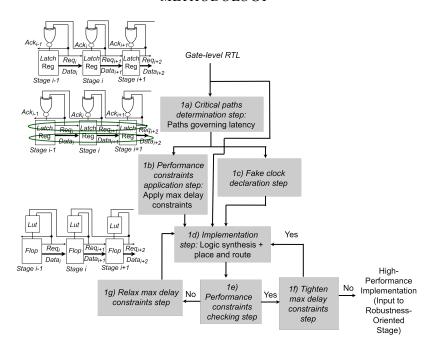

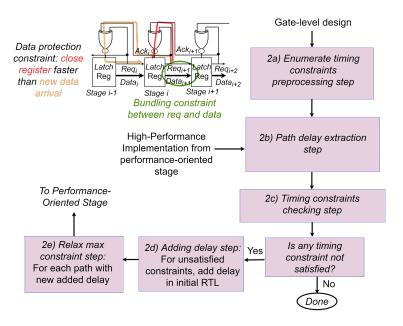

|    | 6.4                         | A CAI  | O Methodology for Bundled-Data Asynchronous Circuits           | 137 |

|    |                             | 6.4.1  | Tool Flow                                                      | 137 |

|    |                             | 6.4.2  | Validation Approach                                            | 142 |

|    |                             | 6.4.3  | Tool Flow Illustration: A Mousetrap Pipeline                   | 142 |

|    | 6.5                         | Synthe | sis of Special Asynchronous Components on FPGAs                | 145 |

|    |                             | 6.5.1  | C-Element                                                      | 145 |

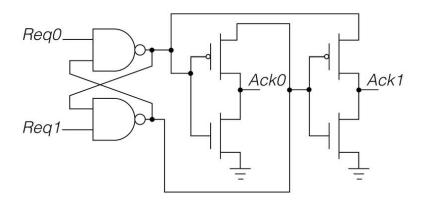

|    |                             | 6.5.2  | Mutex                                                          | 147 |

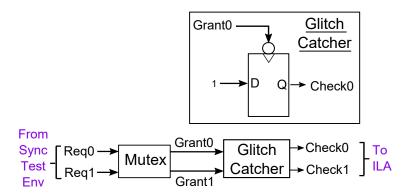

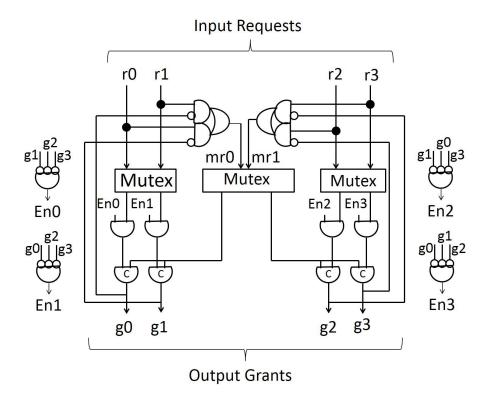

|    |                             | 6.5.3  | 4-Input Arbiter                                                | 152 |

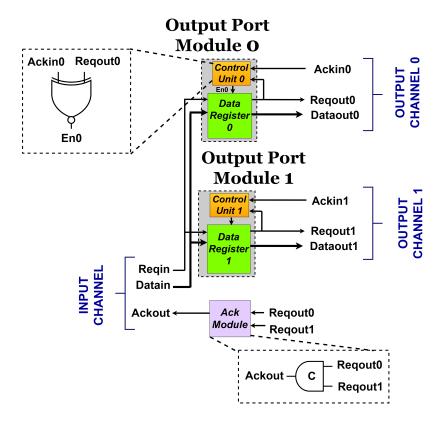

|    | 6.6                         | Case S | tudy: Asynchronous NoC Routers                                 | 154 |

|    |                             | 6.6.1  | A Brief Recap: Unicast-Only and Multicast Asynchronous Routers | 154 |

|    |                             | 6.6.2  | Implementing Asynchronous Routers on FPGAs                     | 156 |

|    | 6.7                         | Experi | mental Results                                                 | 158 |

|    |                             | 6.7.1  | Experimental Setup                                             | 159 |

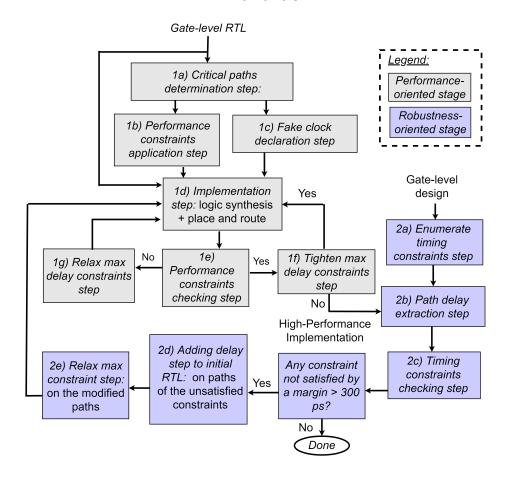

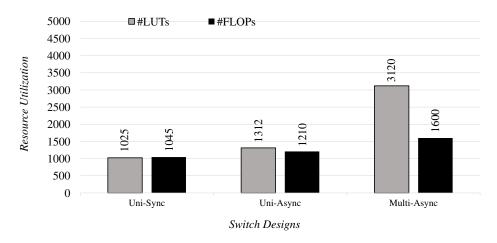

|    |                             | 6.7.2  | Results                                                        | 159 |

|    | 6.8                         | Conclu | asions                                                         | 163 |

| 7  | Conclusions and Future Work |        |                                                                | 165 |

|    | 7.1                         | Conclu | isions                                                         | 165 |

|    | 7.2                         | Future | Work                                                           | 168 |

| ъ. |                             | ,      |                                                                | 170 |

| ВI | bliogi                      | rapny  |                                                                | 168 |

# **List of Figures**

| 1.1 | A typical synchronous system                                                  | 3  |

|-----|-------------------------------------------------------------------------------|----|

| 1.2 | An asynchronous system                                                        | 5  |

| 1.3 | A GALS system                                                                 | 9  |

| 1.4 | Network-on-chip structure                                                     | 12 |

| 1.5 | Xilinx 7 Series FPGA block view [86]                                          | 19 |

| 1.6 | FPGA programmable logic fabric                                                | 20 |

| 2.1 | A typical asynchronous communication                                          | 27 |

| 2.2 | Two common handshaking protocols                                              | 27 |

| 2.3 | Two widely-used data encoding schemes                                         | 29 |

| 2.4 | The C-element: (a) symbol, (b) a transistor-level design, and (c) a standard- |    |

|     | cell based design                                                             | 30 |

| 2.5 | Mutex: (a) block-level view, (b) design details [147]                         | 31 |

| 2.6 | A 4-input arbiter [135]                                                       | 33 |

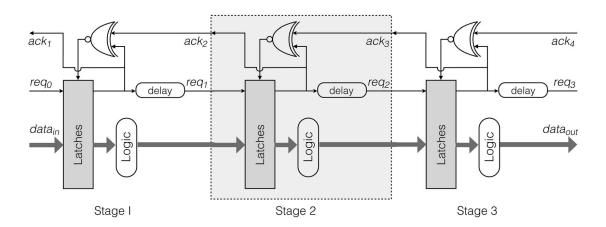

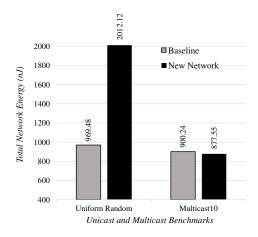

| 2.7 | A 3-stage Mousetrap pipeline [171]                                            | 34 |

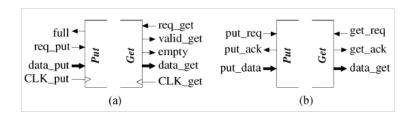

| 2.8 | Put/get interfaces for mixed-timing FIFOs: (a) synchronous interfaces, (b)    |    |

|     | asynchronous interfaces [29]                                                  | 36 |

| 2.9 | Basic <i>sync-sync</i> FIFO architecture [29]                                 | 37 |

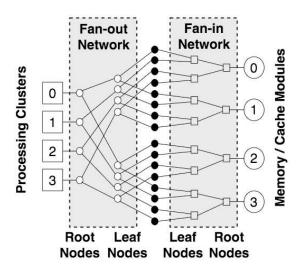

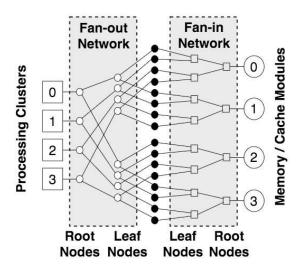

| 3.1 | Original $4 \times 4$ MoT topology [6]                                        | 39 |

| 3.2 | A variant mesh-of-trees (MoT) topology, connecting processors to memory       |    |

|     | modules [7]                                                                   | 40 |

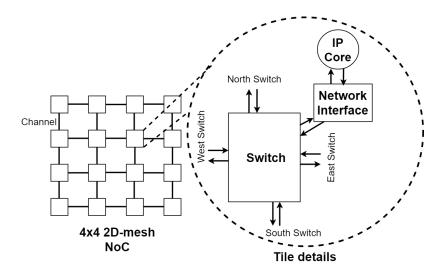

| 3.3 | A 2D-mesh topology and the details of its nodes                               | 41 |

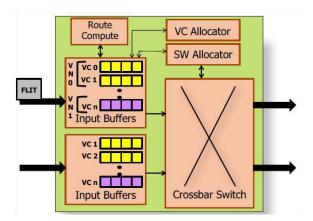

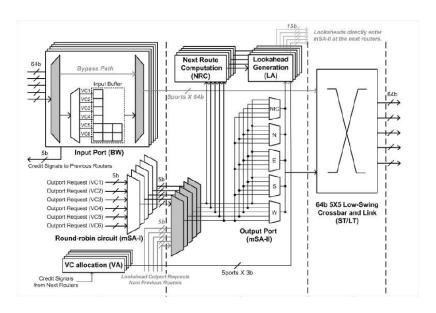

| 3.4  | A traditional 5-cycle router micro-architecture [103]                         | 45 |

|------|-------------------------------------------------------------------------------|----|

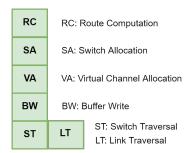

| 3.5  | Pipeline stages in single-cycle routers                                       | 46 |

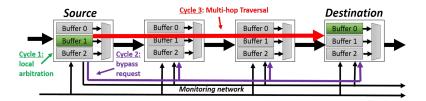

| 3.6  | A SMART NoC structure and operation                                           | 47 |

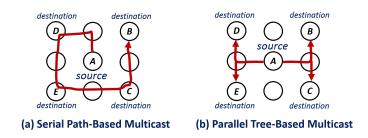

| 3.7  | Multicast techniques: (a) path-based, (b) tree-based                          | 48 |

| 3.8  | A single-cycle multicast router architecture [149]                            | 50 |

| 4.1  | Variant mesh-of-trees (MoT): connecting processors to memory modules          | 54 |

| 4.2  | Baseline fanout node                                                          | 55 |

| 4.3  | Baseline fanin node                                                           | 56 |

| 4.4  | New fanout network architectures: (a)-(c) full range for 8x8 MoT, (d) One     |    |

|      | possible hybrid network for 16x16 MoT                                         | 59 |

| 4.5  | Hybrid network: unicast/multicast simulations                                 | 60 |

| 4.6  | Unoptimized speculative fanout node                                           | 63 |

| 4.7  | Unoptimized non-speculative fanout node                                       | 65 |

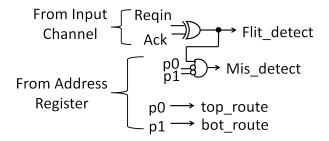

| 4.8  | Unoptimized non-speculative fanout node: Input Channel Monitor and Con-       |    |

|      | trol Unit details                                                             | 67 |

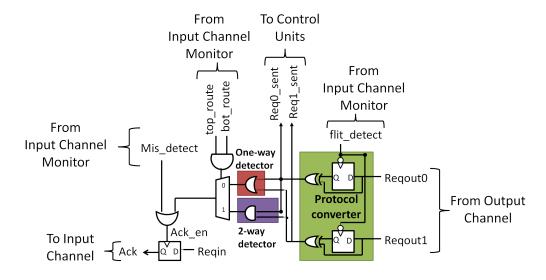

| 4.9  | Unoptimized non-speculative fanout node: Ack Module details                   | 67 |

| 4.10 | Optimized speculative fanout node                                             | 70 |

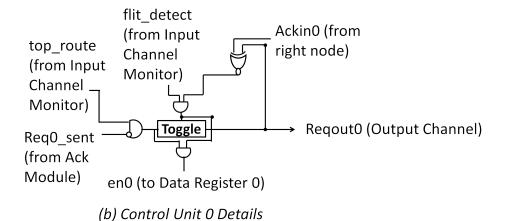

| 4.11 | Optimized speculative fanout node: control unit details                       | 72 |

| 4.12 | Optimized speculative fanout node: Ack Module details                         | 72 |

| 4.13 | Optimized speculative fanout node: Input Channel Monitor and Phase Cor-       |    |

|      | rector details                                                                | 73 |

| 4.14 | Optimized non-speculative fanout node                                         | 74 |

| 4.15 | Optimized non-speculative fanout node: Control Unit details                   | 75 |

| 4.16 | Optimized non-speculative fanout node: Phase Corrector details                | 76 |

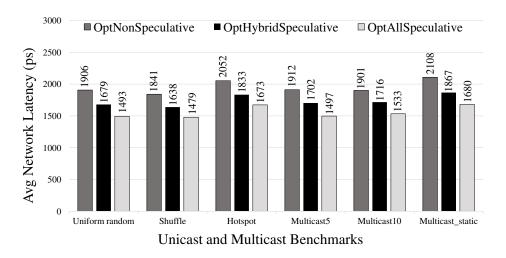

| 4.17 | Contribution trajectory: network latency at 25% saturation load of respective |    |

|      | networks                                                                      | 79 |

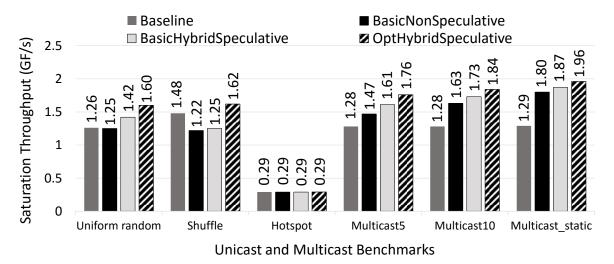

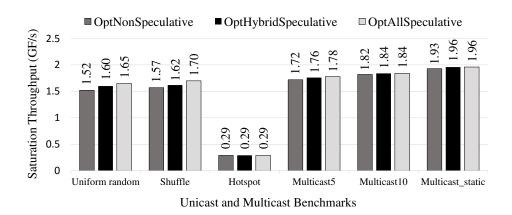

| 4.18 | Contribution trajectory: saturated throughput                                 | 80 |

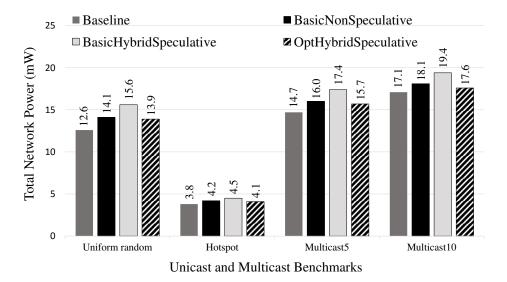

| 4.19 | Contribution trajectory: total network power                                  | 82 |

| 4.20 | Architectural design space exploration: network latency at 25% saturation     |    |

|      | load of respective networks                                                   | 83 |

| 4.21 | Architectural design space exploration: saturated throughput                   | 83  |

|------|--------------------------------------------------------------------------------|-----|

| 4.22 | Architectural design space exploration: total network power                    | 83  |

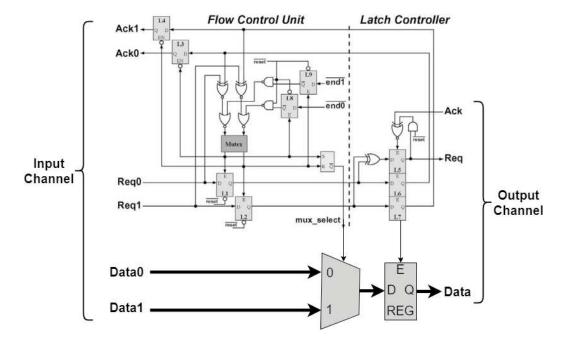

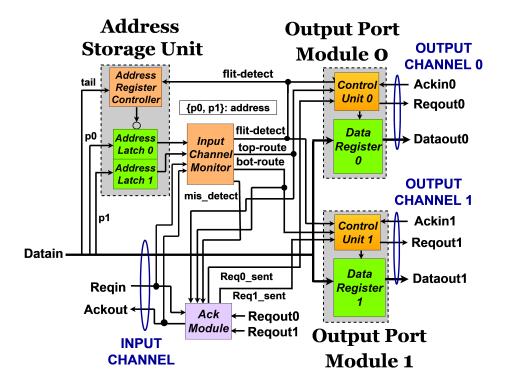

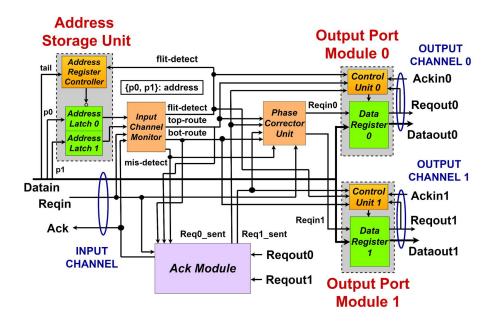

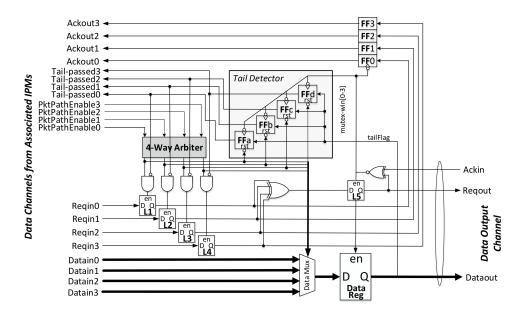

| 5.1  | Baseline IPM micro-architecture                                                | 88  |

| 5.2  | Baseline circular FIFO                                                         | 89  |

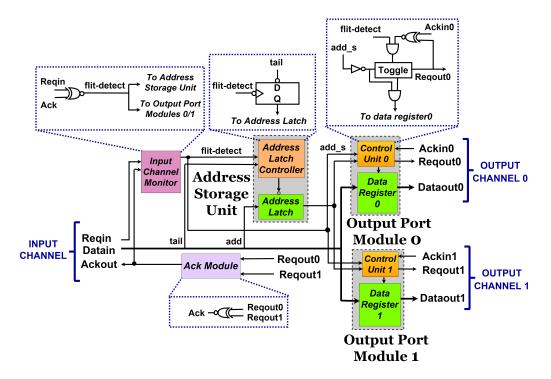

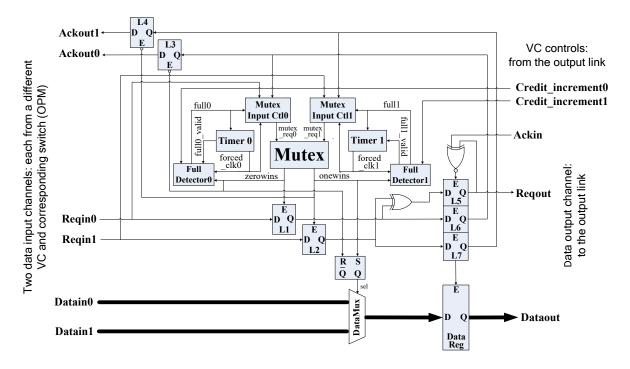

| 5.3  | Baseline OPM micro-architecture                                                | 90  |

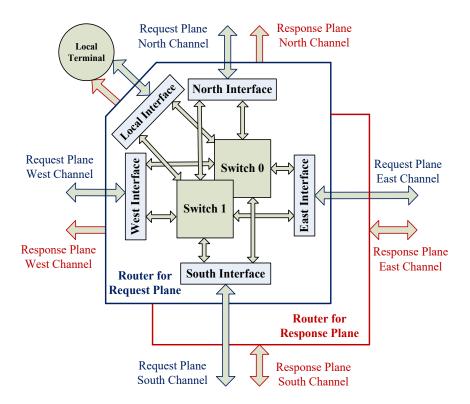

| 5.4  | Node structure for double-plane baseline asynchronous router                   | 93  |

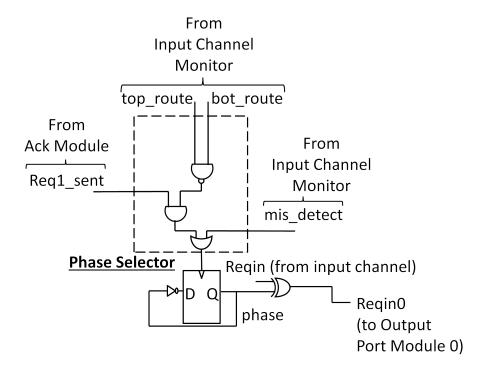

| 5.5  | VC control for an output channel interface                                     | 94  |

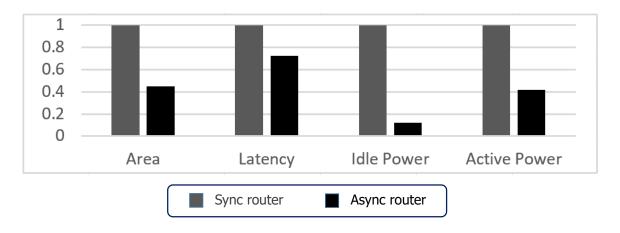

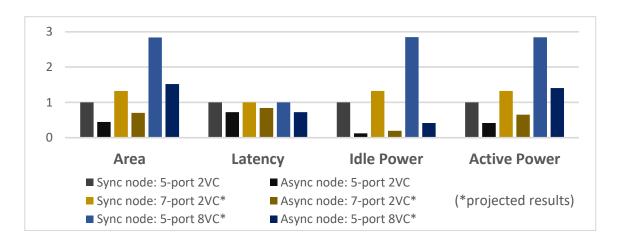

| 5.6  | Baseline asynchronous vs. synchronous router: basic comparison for 2 VCs       | 96  |

| 5.7  | Asynchronous vs. synchronous router: projected results                         | 96  |

| 5.8  | New router architecture and tree-based multicast operation                     | 97  |

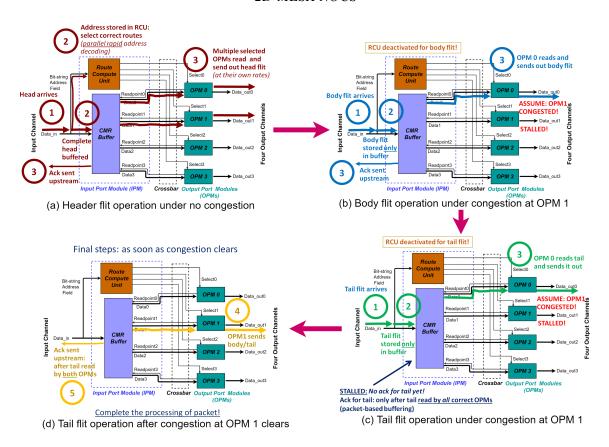

| 5.9  | Continuous-time replication strategy operation for a 3-flit packet: highlight- |     |

|      | ing interesting aspects of parallel route computation, independent read oper-  |     |

|      | ations, and packet-based buffering                                             | 100 |

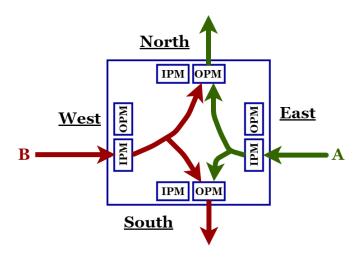

| 5.10 | Cyclic dependency between multicast packets                                    | 102 |

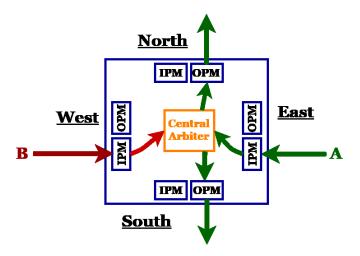

| 5.11 | Centralized arbitration: an alternative approach to avoid resource-dependent   |     |

|      | deadlocks for multicast                                                        | 103 |

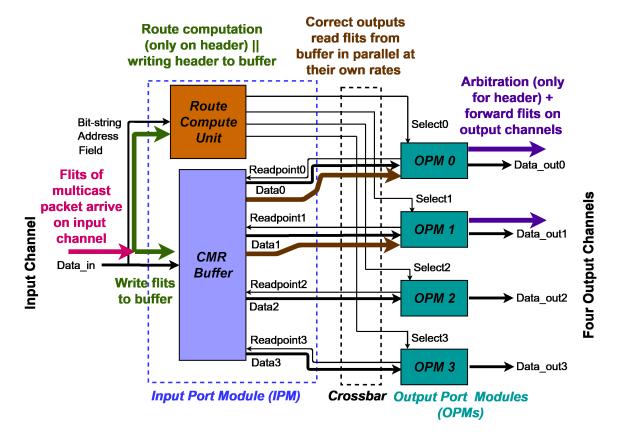

| 5.12 | New IPM micro-architecture with CMR buffer                                     | 105 |

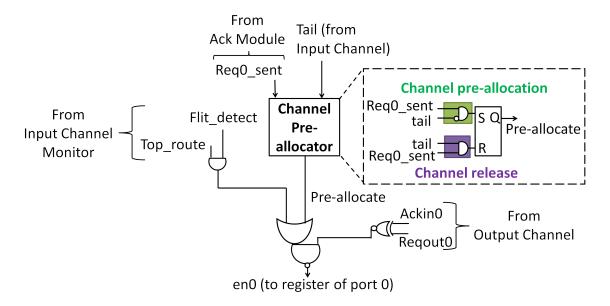

| 5.13 | New route computation unit architecture                                        | 106 |

| 5.14 | CMR buffer: write interface control                                            | 109 |

| 5.15 | CMR buffer: read interface control                                             | 111 |

| 5.16 | Address modifier unit (AMU)                                                    | 112 |

| 5.17 | Node-level energy results for different unicast and multicast transmission     |     |

|      | scenarios                                                                      | 116 |

| 5.18 | Network latency for unicast and mixed unicast/multicast benchmarks at 25%      |     |

|      | saturation load of baseline                                                    | 119 |

| 5.19 | Unicast network latency at varying injection loads                             | 120 |

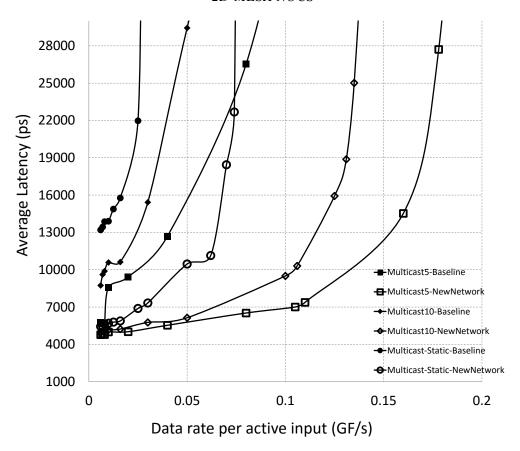

| 5.20 | Mixed unicast/multicast latency at varying injection loads                     | 121 |

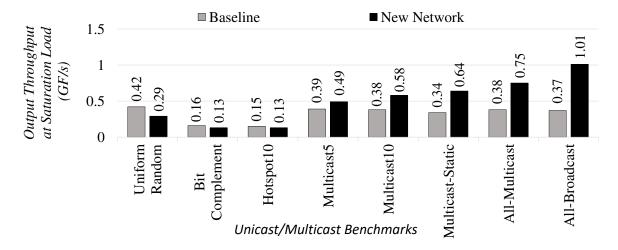

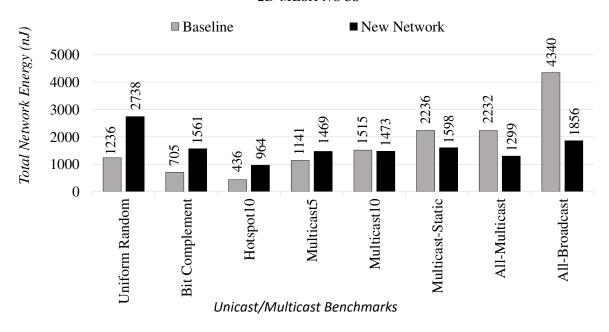

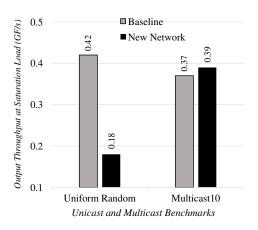

| 5.21 | Output throughput at saturation load                                           | 124 |

| 5.22 | Total network energy results measured at 25% saturation load of $\it baseline$ | 125 |

| 5 23 | Isolated multicast case study: network latency for corner source               | 125 |

| 5.24 | Isolated multicast case study: network latency for center source                | 126 |

|------|---------------------------------------------------------------------------------|-----|

| 5.25 | Isolated multicast case study: network energy for corner source                 | 126 |

| 5.26 | Isolated multicast case study: network energy for center source                 | 126 |

| 5.27 | Network latency for single-flit traffic at $25\%$ saturation load of $baseline$ | 128 |

| 5.28 | Saturation throughput for single-flit traffic                                   | 128 |

| 5.29 | Total network energy for single-flit traffic at 25% saturation load of baseline | 129 |

| 6.1  | A 3-stage Mousetrap pipeline                                                    | 137 |

| 6.2  | Tool flow for implementing bundled-data asynchronous circuits on FPGAs .        | 141 |

| 6.3  | Illustrating the proposed tool flow of performance-oriented stage on a Mouse-   |     |

|      | trap pipeline example                                                           | 143 |

| 6.4  | Illustrating the proposed tool flow of robustness-oriented stage on a Mouse-    |     |

|      | trap pipeline example                                                           | 144 |

| 6.5  | C-element: Standard-cell designs and FPGA mappings                              | 146 |

| 6.6  | The analog mutex                                                                | 147 |

| 6.7  | The digital standard-cell mutex                                                 | 149 |

| 6.8  | Validation setup for mapped mutex                                               | 152 |

| 6.9  | A 4-input arbiter                                                               | 153 |

| 6.10 | Asynchronous unicast router input port module                                   | 155 |

| 6.11 | Asynchronous unicast/multicast router output port module                        | 156 |

| 6.12 | Asynchronous multicast router input port module                                 | 157 |

| 6.13 | Resource utilization for the three switch designs                               | 160 |

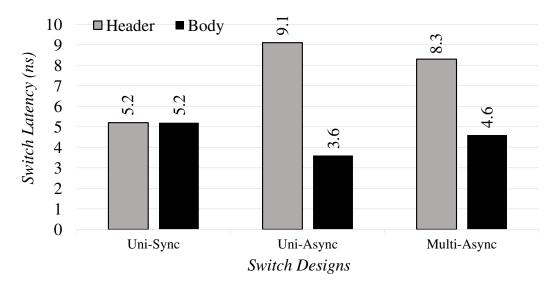

| 6.14 | Switch latency for the header and body flits                                    | 161 |

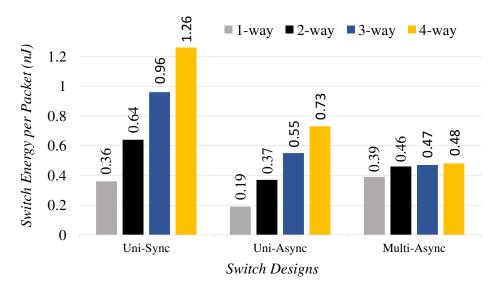

| 6.15 | Switch energy per packet for different unicast and multicast transmissions .    | 162 |

# **List of Tables**

| 4.1 | Node-level area and latency comparisons                                      | 79  |

|-----|------------------------------------------------------------------------------|-----|

| 5.1 | Node-level area and latency comparisons                                      | 115 |

| 5.2 | Zero-load latency for all-multicast and all-broadcast                        | 120 |

| 5.3 | Minimum, average, and maximum multicast delivery time for different bench-   |     |

|     | marks, averaged over the total number of multicast packets injected for each |     |

|     | henchmark                                                                    | 122 |

# Acknowledgments

I would like to thank many people who have helped me throughout my PhD at Columbia and have made this thesis possible.

First, I would like to thank my advisor and mentor, Steven Nowick, for his guidance and support. I admire Steve's way of conducting research, which he has taught me during my Ph.D.: understanding the fundamentals of a research problem, defining the problem in the simplest possible ways, performing a careful review of the relevant literature, and then coming up with systematic new solutions. Steve has also helped me improve my presentation skills. While new and interesting research ideas are important, presenting them clearly and simply, when writing a paper or giving a talk, is also critical. Steve is an excellent teacher and I have learned a lot from him, both by taking his classes and as his teaching assistant. Thanks Steve for patiently guiding me and making me a better researcher.

I would like to thank other members of my dissertation committee – Simha Sethumadhavan, Luca Carloni, Mingoo Seok and Gennette Gill – for their time, insightful feedback and valuable comments. During my Ph.D., I have approached Simha, Luca and Mingoo several times with my research-related questions, and they were always happy to answer them. I also enjoyed excellent classes from both Simha and Luca that helped me develop solid background in computer architecture and system design. I also had an excellent opportunity to collaborate with Luca on my final project of synthesizing asynchronous NoCs on FPGAs, and his guidance was very helpful.

I would like to thank Ram Krishnamurthy for giving me an opportunity to work at Intel Labs for a 3-month internship. During this time, I enjoyed working with other members of his team: Gregory Chen, Himanshu Kaul, Huseyin Sumbul, Phil Knag, and Raghavan Kumar. The internship was a success and we jointly filed for a US patent on my work.

I also had the pleasure of interning at Cadence Design Systems under the expert guidance of Ping-Sheng Tseng. At Cadence, I enjoyed working with Ping's team: Cheoljoo Jeong (a former student of Steve), Paraminder Sahai, and Rajiv Roy.

I would like to thank my colleagues in the Computer Systems Lab at Columbia. I am thankful for their support and for all the interesting discussions: Weiwei Jiang, Paolo Mantovani, Kanad Sinha, Emilio Cota, Andrea Lottarini, Davide Giri, Tom Repetti, Richard Townsend, Luca Piccolboni, and Yipeng Huang. I really enjoyed working with Paolo on my final FPGA project. I always enjoyed the delicious Indian lunches with Kanad at Doaba Deli!

This thesis would not have been possible without the support from my family. My brother, Kartikeya, a fellow Ph.D. student at CMU and an excellent researcher, was always there to support me and put a smile on my face. Thanks for introducing me to several awesome restaurants of Pittsburgh. My wife, Prachi, also a Ph.D. student at BU, who constantly motivated me. Her love and support have been very valuable and helped me through some difficult times. A special thanks to my parents-in-law and my brother-in-law, who are always there for me.

Finally, none of this would have been possible without my parents' unparalleled guidance, love and blessings. They are always a great source of inspiration and encouragement. My father's interesting stories from his own Ph.D. years motivated me, and his words energized me. My mother's care and affection have always been there, and her cooking was very helpful! Thanks mom and dad!

I would also like to acknowledge some miscellaneous things that played important roles. Since I commuted a lot during my Ph.D., a special thanks to Metro-North for making my train travel (between Poughkeepsie and NYC) a relaxing commute, albeit a slow one. Merritt parkway for some high-speed driving experiences between Boston and NYC. I am also thankful to the hilarious British comedy TV shows - I could rely on them after a long day. Last but not the least, several grants have made this research possible: NSF Grant No. CCF-1527796 and NSF Grant No. CCF-1219013.

This thesis is dedicated to:

My late grandfather, an eminent scholar.

# Chapter 1

## Introduction

We are in the age of exascale computing [131]. Shrinking transistor sizes have led to ultra-scale integration with the number of transistors on a single chip in the multi-billion range. Intel recently revealed its behemoth 72-core chip called *Knights Landing*, to be used in supercomputers [141]. The consumer market is already replete with many-core processors, ranging from 16 cores to almost thousand cores on chip. Examples include AMD 16-core Opteron 6000, Intel 24-core Xeon-E7, Intel 80-core Xeon Phi, and graphic processors such as AMD FirePro and Nvidia Titan X that have 2500-3500 GPU cores. However, given the ever-increasing scale of integration, conventional design approaches are facing unprecedented challenges: process variability, aging, chip power and thermal challenges, and scalability issues [147].

In the last two decades, asynchronous, or a hybrid mix of asynchronous and synchronous design approaches, has emerged as an alternative paradigm to address the challenges faced by the conventional synchronous or centralized clock-based approaches. Asynchronous designs are naturally *energy proportional*, where they burn dynamic power only when active. These systems also do not require complex clock distribution, are highly modular and support 'object-oriented' design style with ease of composability, and are very robust to process- and environment-induced variability [147]. Asynchronous design is gaining visibility in not just general-purpose processors and embedded systems, but are also suitable for the emerging areas of neuromorphic computing, quantum cellular automata, energy harvesting, and systems used in space missions [147], [148].

Another concept that has seen significant recent interest is networks-on-chip (NoCs), that have effectively replaced traditional bus-based interconnects in today's complex many-core systems.

NoCs have several advantages over the conventional interconnects such as buses or point-to-point networks [22]: (i) they provide a distributed architecture, which can be shared by multiple traffic flows in parallel leading to high performance; (ii) NoCs support modularity by separating communication from computation, thus allowing easy integration of processing cores, possibly operating at different rates; (iii) NoCs are more scalable, where their effective bandwidth scales with size, unlike buses; and (iv) they are also more cost-effective than point-to-point interconnects, which can have large area/power overheads.

In recent years, there has been significant research on combining asynchronous design with networks-on-chip [66], [83], [89], [96], [185]. Asynchronous NoCs can be used not only to interconnect components in a fully-asynchronous system but also for globally-synchronous locally-synchronous (GALS) systems, where synchronous components can be running at different speeds. Asynchronous NoCs are promising due to their several advantages in terms of no clock distribution, no clock switching power, and ease of integration of heterogeneous processing elements.

While asynchronous NoCs provide several advantages, they also face a key challenge of supporting new types of traffic patterns. These NoCs must be able to support communication requirements of advanced parallel computer architectures, new interconnect technologies, such as wireless and photonics, and traffic due to emerging computing paradigms, e.g. neuromorphic computing. One important class is multicast, i.e. 1-to-many communication, which has recently seen growing interest [15].

While there is significant research on supporting multicast in synchronous NoCs [81], [88], [149] [164], [193], this capability has been largely missing from asynchronous NoCs. The aim of this thesis is to significantly advance the field of asynchronous NoCs by designing efficient multicast solutions that (i) exploit potential advantages of asynchronous NoCs in terms of low area/energy footprint while maintaining high performance, and (ii) introduce novel multicast paradigms that are unique to asynchronous, which can lead to lightweight NoC designs. To this end, new multicast strategies are introduced for two leading NoC topologies: simpler variant mesh-of-trees, and more complex but common 2D mesh. To the best of our knowledge, these are the first general-purpose asynchronous NoCs to support parallel multicast.

Additionally, for a more realistic analysis and evaluation, and also to advance the field of asynchronous NoCs, this thesis targets synthesis of these NoCs on commercial field-programmable gate

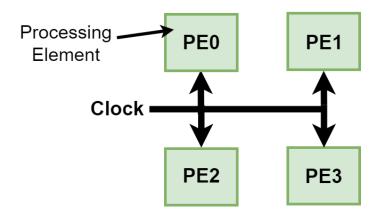

Figure 1.1: A typical synchronous system

arrays (FPGAs). Modern FPGAs not only include standard programmable logic but also consist of multiple cores, accelerators, GPUs and memories. These FPGAs have gained significant importance in hardware-assisted acceleration [151]. Even though there has been major advancement in FPGAs, there has been only limited research on mapping asynchronous NoCs to these devices. *To this end, this thesis proposes the first systematic CAD methodology to efficiently synthesize asynchronous NoCs on commercial FPGAs*. The target is a challenging two-fold goal of not only correctness but also high performance. Only the existing synchronous FPGA synthesis tools are used for ease of implementation. This methodology will enable efficient implementation of asynchronous NoCs on FPGAs to help with their deployment in accelerating real-world applications.

## 1.1 Synchronous Design: Challenges

Digital systems most commonly use the synchronous design style. In such systems, usually all computing elements communicate with each other using a global clock as shown in Figure 1.1. The clock is used to validate computations, which are performed during a clock cycle, and must be complete by the end of the current cycle. This discrete-time operation greatly simplifies the implementation and verification of digital systems.

The use of global clock in synchronous systems leads to a simple solution but also faces numerous challenges. Modern chips are highly-complex, can integrate thousands of computing cores, accelerators and memories, that perform different functionalities, and have distinct performance and power requirements. Designing such large-scale heterogeneous systems poses major challenges for

the globally-synchronous design paradigm, as discussed below.

Clock distribution. Designing a robust clock distribution network for today's highly-complex systems is a major challenge [174]. A single clock distributed to a large chip can suffer from static and dynamic uncertainties, such as skew and jitter, respectively. The generated clock period must include appropriate margins to account for these uncertainties, which can increase as the chip size grows, leading to performance degradations. This problem is further exacerbated when high clock frequencies (upwards of 3 GHz) are used. Moreover, physical design of a global clock distribution network for such chips is also an arduous task, and can have its own challenges.

Clock power dissipation. Modern processor clock frequencies can no longer exceed 3-4 GHz as power consumption has hit a so-called *power wall* [129]. The switching energy of the clock network, even when the system is idle, can lead to significant power dissipation: almost 25-30% of a synchronous chip's power is due to the clock distribution network [173]. Clock power is a major issue for consumer electronics and embedded systems such as smart phones, where it directly impacts the battery life [73]. While techniques such as clock gating can be used to 'turn off' the clock for the inactive components [155], they can also incur extra overhead due to the complex clock-gating circuitry. In particular, clock gating can be applied at two levels: coarse-grain, where entire clock network can be shut down or fine-grain, where individual flip-flops can be selectively enabled or disabled. The former is partially effective when only a portion of the entire chip, connected to the same clock tree, is active [16]. The latter requires adding clock-gating logic at the leaves of a clock network, which has its own challenges pertaining to physical design [87].

**Worst-case performance.** The operating clock rate of a synchronous system is determined by its slowest component, and are therefore bound to worst-case performance. These systems cannot easily exploit the variation in data-dependent computation times to achieve higher performance.

Interfacing with heterogeneous components. There is a big push towards heterogeneous systems, for applications such as Internet-of-Things (IoT), consisting of different accelerators, cores, and memories. These components usually operate at different clock rates, and will therefore require complex synchronizers for interfacing between the different clock domains, which can lead to extra power, performance and area overheads.

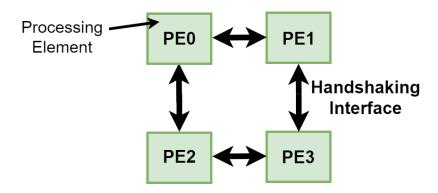

Figure 1.2: An asynchronous system

### 1.2 Asynchronous Design: An Alternative Paradigm

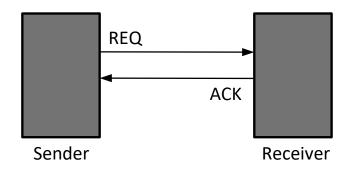

To address the challenges of the conventional synchronous designs, this thesis targets an alternative design style: asynchronous or clockless design. Figure 1.2 shows a high-level view of an asynchronous system, where the processing elements communicate with each other using local handshaking channels. In the absence of a global clock, these components are free to operate at different speeds.

Asynchronous designs exhibit several potential advantages over the conventional synchronous designs, which have led to a recent surge in the use of asynchronous circuits for various industrial applications. However, these designs also have their own unique challenges that must be addressed by the research community to make asynchronous more mainstream.

#### 1.2.1 Advantages of Asynchronous Design

Asynchronous circuits can exhibit several potential advantages over synchronous in terms of lower power, higher performance, better scalability and design reuse.

**Potential lower power.** The absence of a clock and the associated clocking circuitry can lead to significant power savings for the asynchronous designs. Asynchronous circuits are also *energy proportional*, where they burn dynamic power only when active [147]. In contrast, as highlighted earlier, synchronous designs consume power even when inactive due to switching of the clock; clock gating can be used to inactivate modules that are not being used, but it can have its own limitations and overheads.

**Potentially higher average-case performance.** Unlike synchronous, performance of asynchronous systems is not limited by its slowest component, rather it is determined by an average of the operating speeds of different components, which can potentially lead to overall higher performance.

Better scalability and design reuse. Asynchronous systems exhibit high composability, where a larger complex system can be built using a simple aggregation of smaller components. In contrast, adding new modules to a synchronous system requires re-designing clocking networks. In addition some of these components might not be compatible with the target clock frequency, and therefore need to be re-designed as well. These issues do not exist for asynchronous systems. Recently, several large-scale industrial fully-asynchronous or GALS systems have been introduced that exhibit this ease of integration: Intel's asynchronous Ethernet switch [45], STMicroelectronics' P2012 [11], IBM's TrueNorth [2], and Intel's Loihi neuromorphic chip [117].

#### 1.2.2 Challenges with Asynchronous Design

Even though the asynchronous approach has the above advantages, there are some major challenges associated with these designs that must be addressed: hazard-free operation, the lack of CAD tool support, and testing of asynchronous circuits.

**Hazard-free designs.** In synchronous designs, freedom from hazards is usually not a requirement as long as the result of a computation becomes stable before the start of the next clock cycle. However, in asynchronous designs, since there is no clock, freedom from hazards is therefore a requirement to achieve glitch-free operation. Freedom from hazards must be guaranteed at different levels of the synthesis flow: from two-level/multi-level logic minimization to technology mapping [148].

Lack of CAD support. While small asynchronous designs can be synthesized manually, larger designs will require automation for faster time-to-market, targeting both correctness and efficiency. There is a two-fold goal for developing automated tool flows for asynchronous circuits [148]: (i) these flows must be compatible with the existing synchronous languages and CAD tools, and (ii) new specification languages need to be developed, which can capture the asynchronous-specific aspects: absence of clock, fine-grain concurrency, and distributed synchronization.

Testability of asynchronous circuits. Testing of asynchronous circuits faces unique challenges compared to synchronous designs [148]. A typical testing procedure for synchronous designs, called *single-stepped approach*, involves pausing or slowing down the system, and checking the internal states by comparing with the 'golden' results. However, this testing approach is not possible for asynchronous designs due to the absence of a global clock. In addition, the testing tools for asynchronous designs should not only check for functional correctness but also for hazards, which adds further complications.

#### 1.2.3 History and Overview of Recent Success

There has been a large amount of work in addressing various challenges of asynchronous design as well as exploiting its advantages to develop highly-efficient systems. This section presents a brief history of asynchronous designs, followed by an overview of the research on hazard-free logic synthesis, CAD flows, asynchronous processors, GALS systems, and various commercial applications of asynchronous designs.

Brief history. The early years between 1950s to 1970s mostly saw advent of the classical asynchronous theory by Unger [187], and Muller [143], as well as the use of asynchronous design in many commercial processors (Iliac, Iliac II, Atlas, MU-5) and in LDS-1 graphics system. The mid 1970s to early 1980s did not see much advancement in asynchronous designs and was a period of reduced activity. However, the mid 1980s to late 1990s was a "coming-of-age" era for asynchronous with significant new developments: correct and efficient methodologies for asynchronous controllers [9], [37], [60], [146] and pipeline designs [61], [114], [203], the first academic asynchronous processors from Caltech [124], and University of Manchester [65], and initial commercial uptake by Philips Semiconductor for low-power consumer products [63]. In the modern era, from early 2000s, there has been a surge of recent activity: new CAD tool development [8], [116]; asynchronous networks-on-chip [23], [66], [185]; asynchronous FPGAs [183]; industrial uptake such as from STMicroelectronics [11] and Intel [45]; and applications, for example, emerging areas of neuromorphic computing [2], [46], sensor networks [55], and energy harvesting [34].

**Hazard-free logic synthesis.** Two widely-used methods for the specification and synthesis of hazard-free asynchronous controllers have been proposed: burst-mode (BM) [145], and Petri-net based [38]. BM is effectively an asynchronous state machine, where state transitions are event-

driven: once an "input burst" of one or more signal transitions arrives, the dependent output changes, and the machine advances to the next state. Although a BM specification can leverage existing synchronous approaches for synthesis, it requires a simple hold time requirement, also known as *generalized fundamental mode* timing requirement: no new input burst may arrive until the machine has stabilized from the previous burst. On the other hand, a Petri-net based method uses a directed bipartite graph, in which the nodes represent transitions (i.e. events that may occur) and places (i.e. conditions). Petri-net based controllers only use a quasi-delay insensitive (QDI) timing assumption, which requires that at each wire fanout point, the forked wires have roughly the same delay. Alternatively, *NULL Convention Logic (NCL)*, introduced by Karl Fant, targeted a unified synthesis of both control and datapath, where synchronous netlists are translated to asynchronous threshold gates, such as m-of-n gates [116].

Synthesis CAD flows. Several CAD flows have been developed for asynchronous circuits. The earliest is the *Caltech Synthesis Method* from Alain Martin's group [123], followed by Philips' *Tangram Compiler*, which was used for development of 80C51 microcontrollers, that had several applications with one of most prominent one being for smart card applications [14]. In addition, several automated tool flows have been developed for NCL-based systems, from as early as 2000 [116] to more recent ones [139]. Multiple pipeline optimization frameworks have also been proposed, which use techniques such as slack matching and loop unrolling. One of these pipeline optimization flows is *Proteus*, from 2011, which has been used in the development of Intel's Ethernet switch [8], [45]. Also, around the same period as Proteus, *Tiempo* was introduced, which uses high-level transaction-level modeling (TLM) of SystemVerilog, for specification entry, and then compiles it to a gate-level netlist, followed by synthesizing to layout using commercial synchronous tools [160].

**Asynchronous processors.** The first modern asynchronous 16-bit RISC processor was developed at Caltech by Martin's group in 1988 [124]. In 1993, another influential processor, Amulet 1, was designed at University of Manchester, which is an asynchronous version of the ARM processors [65]. Since then, there have been several processors that have advanced the field with new pipeline optimizations, cache and memory design, exception handling, speculative operation [148]: TITAC-1/2 [179], Amulet2e and Amulet3i [65], and MiniMIPS [125].

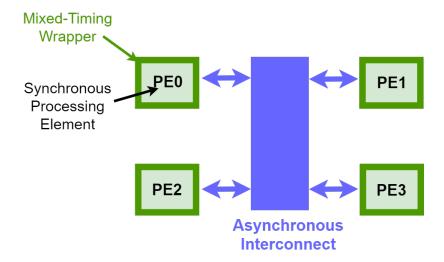

**GALS systems.** An alternative to fully-asynchronous systems are globally-asynchronous locally-synchronous (GALS) systems. An example GALS system is shown in Figure 1.3, where syn-

Figure 1.3: A GALS system

chronous computing elements, operating at different clock frequencies, are connected using an asynchronous interconnection network. For correct synchronization between synchronous and asynchronous components, mixed-timing wrappers are required at the sync-async boundaries. The GALS approach eliminates the use of global clock for the entire chip [107], [147], [182].

**Commercial applications.** Asynchronous designs have been used in several industrial applications.

Philips Semiconductors (now NXP) developed an asynchronous 80C51 microcontroller in the late 1990s to early 2000s [63]. This microcontroller showed 3-4× lower power as well as lower electromagnetic interference (EMI) noise than its commercial synchronous version. This combined advantage led to the use of these controllers in wide-range of consumer electronics, such as pagers, cell phones, smart cards and digital IDs.

Asynchronous design has also made in-roads in FPGA development. Achronix Semiconductor introduced the Speedster 22i family of FPGAs in the mid 2000s [183]. These high-performance FPGAs used fine-grain bit-level pipelining, and could operate at 1.5 GHz in 22 nm technology.

Intel acquired the asynchronous startup Fulcrum Microsystems in 2011 to develop its industry-leading FM5000/6000 series Ethernet switch chips [45]. This switch supports a 40 Gigabit Ethernet using a fully-asynchronous high-speed crossbar, providing a maximum of 640 Gbps bandwidth with high energy efficiency.

Asynchronous design has also seen an increasing interest in brain-inspired neuromorphic computers, from both IBM [2] and Intel [46], aiming to achieve the high efficiency of the biological brain. These computers follow a non-Von-Neumann architecture, where neurons are the main computing elements, with closely-coupled memories, and these neurons are connected to each other using synapses, modeled as the interconnection framework of the computer. IBM's *TrueNorth* is 5.4 billion transistor neuromorphic GALS chip, which connects 4096 synchronous cores, modeling 1 million neurons and 256 million synapses using a fully-asynchronous NoC. Intel's *Loihi* is a fully-asynchronous 2.1 billion transistors system, comprising 128 cores, each modeling 1024 neurons.

### 1.3 Networks-on-Chip: An Introduction

Networks-on-Chip (NoCs) are becoming the de facto standard of communication for many-core systems, and are the focus of this thesis. This section presents the motivation behind the rise of NoCs, its basics and advantages, and recent advances in synchronous as well as asynchronous NoCs.

#### 1.3.1 NoCs: Motivation, Basics, and Advantages

System performance and power depend not only on computing efficiency but are also governed by the communication efficacy of the on-chip interconnects [122]. In particular, on-chip interconnects have become the limiting factor to achieve high performance and low power for today's many-core systems due to two reasons: (i) cores for these systems operate on different clock frequencies, and a reliable and efficient interconnect is required to manage interaction between these different timing domains; and (ii) with technology scaling, computational elements and memories have become faster and more energy-efficient but the performance and power of the interconnects has not scaled down. Given these reasons, it is important to consider designing efficient on-chip communication framework as a first-class research problem.

Traditional global buses are often not suitable for today's large-scale many-core processors [122]. In bus-based interconnects, a single bus is shared between multiple processors, graphics cards, memory modules, and accelerators, which is not scalable as the number of units increase, both in terms of performance and power. Due to the centralized architecture, buses have limited support for handling multiple communication flows in parallel. To start a transmission, a sender first requests access to

the bus. Since, there can be multiple senders active at one time, arbitration is performed and the bus access is granted to the winner. The winner then broadcasts messages on the bus, which are received by all 'slave' units but are accepted only by the intended receiver, and ignored by the others. Such bus-wide broadcasts can have significant power overheads.

Another conventional interconnect is the point-to-point interconnect. These interconnects use dedicated wires connecting each source-destination pair, e.g. a crossbar. This network can lead to high performance but at a cost of significant power and area overheads, and may not scale well with large networks. These interconnects also suffer from significant physical design issues, where routing of these large number of dedicated wires is an arduous task.

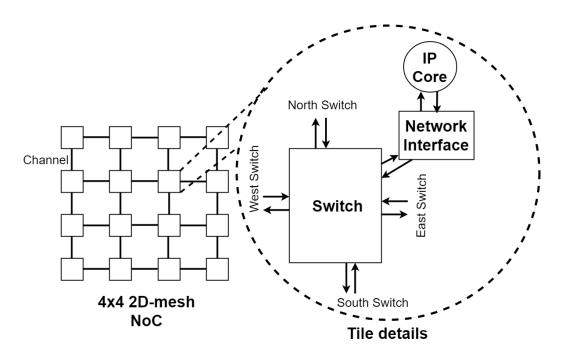

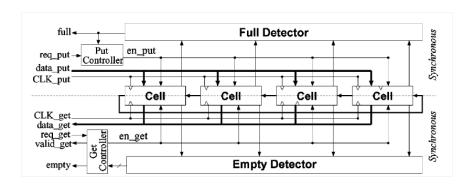

As shown in Figure 1.4, NoC provides a distributed communication infrastructure, consisting of switches and channels. Each processing element (PE) is connected to the switch through a network interface (or NI), and the switches are in turn connected to each other using channels or links. The switches and channels are organized in a fixed structure called a topology, which can be of different types, e.g. mesh, torus, ring, etc. [122]. During a transmission, the PE sends a message to the NI, which performs packetization, and converts the message into multiple packets, which are sent to the attached switch. The switches use an underlying routing algorithm to determine the path for routing the packets to the destination switch, traversing intermediate channels. The destination switch sends the received packets to the NI, which converts them back to messages, compatible to the formats used by the PEs, and sends them to the destination PE. In cases where the PEs are operating at a different clock rate than the NoC, the NIs may also use mixed-timing interfaces to synchronize between the NoC and the PEs.

NoCs have several advantages over the traditional interconnects:

- High performance and energy efficiency. NoCs provide a shared communication infrastructure, which can be utilized by many traffic flows at the same time. This parallel and distributed operation leads to high performance, without utilizing extra dedicated wiring resources, hence with minimum area and power overheads.

- Scalability and reliability. The aggregated bandwidth of the NoCs scales with the network size. In contrast, bandwidth is limited in traditional global buses, which is shared by all the attached units and suffers when the number of units increase. Further, NoCs have regular ar-

Figure 1.4: Network-on-chip structure

chitectures, with short wires that have controlled and predictable electrical properties, leading to a more reliable operation compared to global long wires.

• Modularity and ease of integration. NoCs support modularity by separating communication from computation. They also facilitate design reuse where optimized standard IPs can be simply plugged in, considerably decreasing the design efforts and allowing faster testing and validation, hence improving the overall design cycle.

#### 1.3.2 Advances in Synchronous NoCs

The synchronous design style is the most common approach used for NoCs. The earliest synchronous NoCs were seen in the early 2000s [12], [40], [72], [76], [197]. Since then, there has been much advancement in this field.

**Topologies.** Many different network topologies have been used, as well as new ones proposed for NoCs. The most common topologies are: mesh [70], [132], torus [204], ring [93], and trees [72]. Some high-radix topologies are also proposed for high-performance computing, such as Dragonfly [99].

**Routing Algorithms.** There has been significant research on routing algorithms for NoCs. There are two main categories: *deterministic*, where the path taken by a packet is fixed statically [79], [93], [177], [204], and *adaptive routing*, where a packet can dynamically select the best path based on network state such as congestion [69], [72], [80], [132].

**Guaranteed service.** NoCs also play a critical role in systems with hard real time deadlines in order to deliver packets on time. Such systems require NoCs to support guaranteed service (GS) and multiple service levels [70], [93], [132].

**Power and performance optimization.** Several power and performance optimization techniques have been introduced for NoCs. To minimize power, novel router architectures have been proposed [192], and techniques such as dynamic voltage and frequency scaling (DVFS) have been used to select the best *V,F* settings depending on channel utilization [169]. To improve performance, optimization techniques such as speculation [150], prediction [127] and bypassing or lookahead [149] have been used within routers. Recently, SMART NoCs were introduced that use *extreme bypassing*, where multiple routers on the correct path are bypassed by a packet in a single clock cycle [104].

**Support for new traffic patterns.** There has also been significant recent research to support communication patterns common in parallel computing application, such as cache coherency, and emerging areas of deep neural network architectures. These patterns involve multicast (1-to-many) and aggregation (many-to-1) traffic. Several approaches have been proposed to support these patterns while simultaneously achieving high performance with low overheads [106], [81], [88], [106], [193].

**Reliability.** Fault tolerance and reliability are major concerns for NoCs as feature sizes keep scaling down [22]. Fault-tolerant routing algorithms that route around the faulty components have been introduced [59], [156], [209], some of which can tolerate any number of faults as long as good connections exist [156]. Defect-tolerant router architectures have also been proposed that use error detection codes such as CRC and redundant hardware to improve reliability [36].

**Real chips and prototypes.** Synchronous NoCs have been used in several academic and industrial chips, which are large-scale, involve many processors, and are used for different applications. Some of the academic prototypes include: TRIPS [71], where a NoC replaced the traditional bus for the applications of operand networks, and more recent 36-core SCORPIO [47] with a mesh-based

NoC to support a scalable snoopy cache coherence protocol. Some of the industrial systems using NoCs are from Tilera [10], Intel [189], and IBM [208].

Emerging technologies. Recently, several high-performance NoCs using emerging technologies such as 3D, wireless, and photonics have been proposed. A 3D chip stacks multiple device layers, connected using vertical interfaces such as Through-Silicon Vias (TSVs) [44]. New 3D NoCs have been proposed to connect processing elements in these chips. These NoCs have many advantages: lower network diameter leading to potentially high performance, reduction in total wiring cost, and higher packing density [43], [92], [186]. In addition, wireless NoCs have been proposed that add high-speed wireless links on top of a conventional wired NoC to create a *small world* effect of bringing far nodes closer, significantly improving performance [49]. Such hybrid wireless/wired NoCs use different wireless technologies, e.g., mm-wave or surface wave [49], [95]. Similarly, photonics NoCs have been introduced that exploit *wavelength-division multiplexing (WDM)* to send multiple packet streams in parallel, using different wavelengths, on a single channel, at speed of light, leading to very high performance [119], [168].

#### 1.3.3 Advances in Asynchronous NoCs

Even though synchronous NoCs are mainstream, they can still incur significant power and performance overheads, making asynchronous NoCs a promising alternative.

Asynchronous NoCs can be used to connect synchronous components, forming globally-asynchronous locally-synchronous (GALS) systems, or can be used in fully-asynchronous systems. The use of asynchronous NoCs eliminates global clock management, and the associated overheads of clock skew, clock power or any clock-gating circuitry. Given the promise of asynchronous NoCs, there has been much research in this area in the last decade, including industrial advancements and use of these NoCs in emerging areas of neuromorphic computing, as described below.

General asynchronous NoC research. A number of research challenges for asynchronous NoCs have been targeted. To achieve quality of service (QoS), asynchronous NoCs have been proposed that provide guaranteed service and multiple levels of services, in addition to best effort traffic [23], [51], [162]. There has been important research on improving fault-tolerance and reliability of asynchronous NoCs [84], [176], [205] with some works focusing on developing efficient asynchronous NoCs that also mitigate effects of process variation [56], [142]. Automated tool flows

have also been proposed for asynchronous NoCs that guarantee not only correctness but also lead to high-performance implementation [66], [134], [184]. Interestingly, a recent asynchronous NoC that supports time division multiplexing (TDM) was proposed [96]; TDM is usually performed in a synchronous setting, since the use of clock helps provide a time reference. In addition, space division multiplexing (SDM) has also been used for asynchronous NoCs [206]. Further, virtual channels (VCs) have been added to asynchronous NoCs without significant overheads in terms of area and power [51], [136]. Multiple recent works target latency optimization of asynchronous NoCs using a low-overhead bypassing technique, where the routers on the path of a packet are informed in advance of the arrival so they can pre-allocate the resources, and the packet is then simply fast forwarded through the routers after arrival [57], [90]. Finally, there also has been recent interest in using asynchronous NoCs for 3D technology [190], as well as for vision applications [163].

**Industrial comparisons with synchronous NoCs.** Recently, there have been asynchronous and GALS NoCs developed at STMicroelectronics, Intel and AMD, which have been shown to be more efficient than their synchronous counterparts.

A GALS system called P2012 from STMicroelectronics uses a fully-asynchronous NoC to connect highly-customizable accelerators [11]. This system comprises 4 clusters, each consisting of 16 synchronous processors. The system delivers a performance of 80 GOPS but consuming only 2W power. Compared to recent Quadro and Nvidia commercial GPUs, P2012 achieves significantly better performance per unit area and performance per unit power.

Intel Labs proposed a hybrid packet/circuit-switched NoC, fabricated in advanced 22 nm tri-gate CMOS technology [30]. This NoC supports two modes: normal synchronous packet-switched, and a *source-synchronous* circuit-switched mode. The latter mode is actually an asynchronous circuit-switched implementation, which was shown to achieve 2.7× better network throughput and a 93% reduction in latency, compared to the synchronous packet-switched mode.

A recent asynchronous NoC router, developed jointly by AMD research and Asynchronous Circuits Lab of Columbia University, showed 55% less area and 28% reduction in latency in a head-to-head comparison with a state-of-the-art synchronous router used in high-end AMD processors [89]. Both the routers were synthesized in advanced 14 nm FinFET technology, and used two virtual channels. Similar improvements were also estimated for this asynchronous router with 8 VCs.

Neuromorphic computing. Neuromorphic computing is an emerging area of brain-inspired

computers that target brain-like high performance and power efficiency. These systems have billions of computing elements, each following a non-Von Neumann architecture with a closely-coupled local memory. The neurons, in these systems, are implemented by computing elements, either using digital design [2] or analog [13], while the communication between neurons (or synapses) are implemented using an interconnect. Interestingly, asynchronous NoCs are often used as these interconnection networks, connecting billions of synchronous neural cores, forming a substantial GALS system. Neuromorphic computing fits the asynchronous paradigm because of the event-driven communication between neurons, and can utilize the various benefits of asynchronous NoCs in terms of scalability, low power, and ease-of-integration.

On of the first examples of a neuromorphic computer is *SpiNNaker* (*Spiking Neural Network Architecture*), developed at University of Manchester [62]. Spinnaker is a massively-parallel system, where 1 million neurons are modeled in software using synchronous ARM9 cores, which are connected using an asynchronous communication infrastructure. This system achieves burns only 50 mJ of energy when processing a 1024 by 1024 image, compared to 1.5 J for a GPU-based system.

TrueNorth from IBM is a recent example, which is a 5.4-billion transistor neuromorphic chip [2]. TrueNorth is also a GALS system with 4096 synchronous neurosynaptic cores, modeling 1 million neurons and 256 million synapses, connected using a fully-asynchronous NoC. This chip only consumes 63 mW of power while processing a  $400\times240$  video input. TrueNorth is also being used for other applications such as face recognition.

Very recently, Intel announced the *Loihi neuromorphic chip*, which is a fully-asynchronous 2.1-billion transistor system [46], [117]. This chip comprises of 128 neural cores, modeling 1024 neurons each, and consuming only 25 pJ energy per operation at 1 V supply. These cores are connected using a 8×4 asynchronous mesh NoC. Loihi is the first system to support on-chip learning.

## 1.4 Multicast Communication and its Applications

While NoCs have several benefits, they also face a key challenge of supporting new types of traffic patterns. Modern NoCs must be able to support communication requirements of advanced parallel architectures. One such important class of traffic is multicast, i.e. 1-to-many communication, which has seen a growing interest recently [15]. Even though there has been significant research on sup-

porting multicast in synchronous NoCs, this capability has been largely missing from asynchronous NoCs, despite the numerous applications of multicast as described below. This thesis focuses on supporting high-performance multicast in asynchronous NoCs while maintaining low overheads.

Multicast communication is defined as sending the same packet from one source to an arbitrary number of destinations. There are three main domains where this traffic pattern is common: (i) parallel computing applications, (ii) new interconnect technologies, and (iii) emerging NoC applications.

Multicast has been widely used in parallel computing domain for three main applications: *cache coherence protocols, shared operand networks*, and *barrier synchronization* [88]. In cache coherence, multicast can be used to send write invalidates to multiple processors in directory-based protocols. There are also multicast [21] and broadcast-based [126] snoopy cache coherence protocols. In shared operand networks such as RAW [181], TRIPS [166], Wavescalar [178], multicast can be used to deliver operands to multiple instructions. Also, barrier synchronization can be performed using multicast, crucial for message passing based shared memory systems. This approach is useful in bringing a set of processors to a known global phase before proceeding to a new phase of computation. In this case, a barrier-sync packet indicating thread synchronization is multicast/broadcast to all the participating processors [175]. Therefore, given these important applications, the NoCs for these advanced parallel architectures must support efficient multicast.

Multicast is also gaining importance with new technologies replacing the traditional electrical wires in NoCs. Emerging interconnect paradigms such as nanophotonics, wireless, and 3D integration have seen recent interest [26], [49], [168], [202]. Multicast and broadcast are inherent forms of communication used in radio frequency (RF) [28], [27], [94] wireless [49], [50], [111], photonics [33], [133], [201], and CDMA technologies [112], [153], [195]. Supporting lightweight, and power-performance efficient multicast in these emerging NoCs is an active area of research [94]. There is also interesting research in handling multicast in 3D NoCs [54].

Finally, 1-to-many (multicast) and 1-to-all (broadcast) communication patterns are also common in emerging areas of neuromorphic computing [2], [46] [130], [138], [144], and computational genomics [24]. A significant portion (sometimes 100%) of spiking neural networks (SNNs) [188] or deep neural networks (DNNs) [32], [109], traffic is multicast/broadcast, where a neuron communicates with several other neurons. Similarly, broadcast patterns are common for genomic applications

such as sequence analysis and parallel sequence alignment [24]. NoCs designed for these emerging applications must be able to support multicast and broadcast efficiently. Recently, asynchronous NoCs have also been used to handle communication requirements of hardware implementations of SNNs [130]. However, an efficient multicast capability has been entirely missing from general-purpose asynchronous NoCs.

### 1.5 FPGAs: Architecture, and Applications

In the last decade, research and development in the field of reconfigurable computing has led to FPGAs becoming more mainstream and being deployed as SoCs for variety of applications. Modern FPGAs not only consist of the standard programmable logic fabric but also a processing system comprising multiple cores, GPUs, accelerators, and memories [151], [161]. The combination of programmability with a high-performance processing unit enables efficient implementation of large-scale systems, targeting different applications, at low cost, low power, and achieving fast time-to-market.

FPGAs have come a long way from the production of the first Xilinx FPGA in 1985, which could support 1000 ASIC gates to Xilinx's latest Zynq Ultrascale+ FPGA, which supports up to 6.2 million ASIC gates. Since 1999, there has been a major push towards integrating processors and memories with the programmable logic: from a single core to multi-core homogeneous and heterogeneous systems with different processors targeting specialized tasks and supporting different operating systems [151]. However, given the advancement in this field, there has been only limited research on implementing asynchronous circuits on FPGAs. This thesis takes on this challenge of safely and optimally implementing asynchronous NoCs on the modern FPGAs.

Before discussing the implementation of asynchronous NoCs on FPGAs, it is important to first understand the basic architecture of an FPGA, and the recent trends of its different applications.

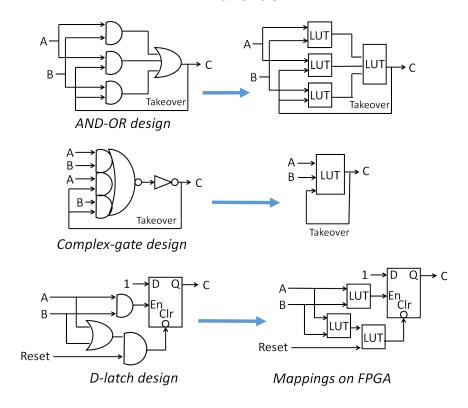

#### 1.5.1 FPGA Architecture

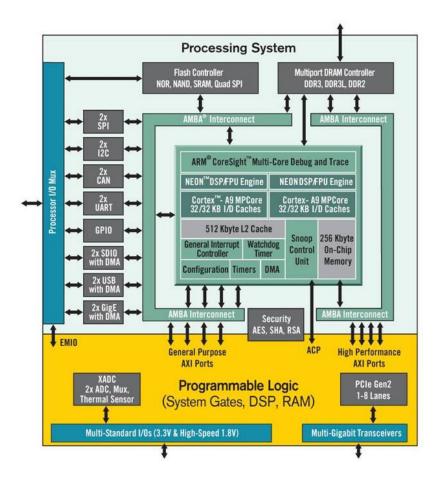

Figure 1.5 shows the high-level architecture of a Xilinx 7 series FPGA, such as Zynq 7000, Kintex 7, and Virtex 7 [20]. There are two main components: a processing system, and a programmable logic fabric.

Figure 1.5: Xilinx 7 Series FPGA block view [86]

The processing system consists of an advanced processor subsystem with dual-core ARM Cortex-A9 CPUs, L1/L2 caches, on-chip memory, and other useful units such as DMA and interrupt controller. Other important components of the processing system are the flash controller, multi-port DRAM controller that supports DDR2 and DDR3, and a rich set of standard I/O peripherals. This system connects to the programmable logic fabric using a high-performance low-latency AXI-based interconnect that can enable 16 parallel DMA channels and a functional bandwidth of over 300 MB/s.

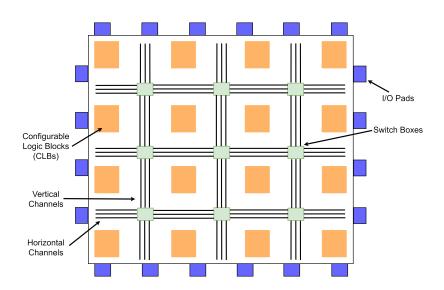

The structure of a programmable logic fabric is shown in Figure 1.6 [98]. It uses an island-style architecture with two main components: configurable logic blocks (CLBs) and an underlying programmable interconnect, connecting the CLBs. The CLBs consist of configurable one-to-five input look-up tables (LUTs) that can implement different logic functions, and flip-flops for storage

Figure 1.6: FPGA programmable logic fabric

purposes. The programmable interconnect consists of switch boxes, and horizontal and vertical channels. The switch boxes mainly consist of multiplexers that can be configured, as well as buffers to drive the wires of the channels.

### 1.5.2 FPGA Applications

Due to the advancement in FPGA technology, these devices are being deployed for several industrial applications [151], [161]. Some of the important ones are [161]: to develop efficient digital signal processing systems, implementing vision applications in FPGA for aerial vehicles such as UAVs, and in automative systems for vehicle velocity estimation, etc. With the ever-increasing interest in machine learning algorithms, FPGAs are also being used for hardware-assisted acceleration of these algorithms: prominent examples are at Microsoft, where FPGAs are being used to accelerate the Bing search engine [3], [25]. Additionally, other applications of FPGAs include: developing security circuits such as PUFs [91], as well as for big-data analytics acceleration [191].

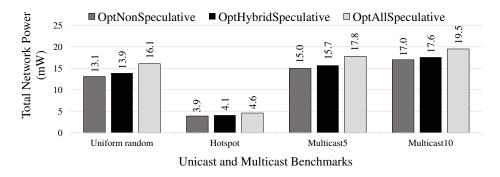

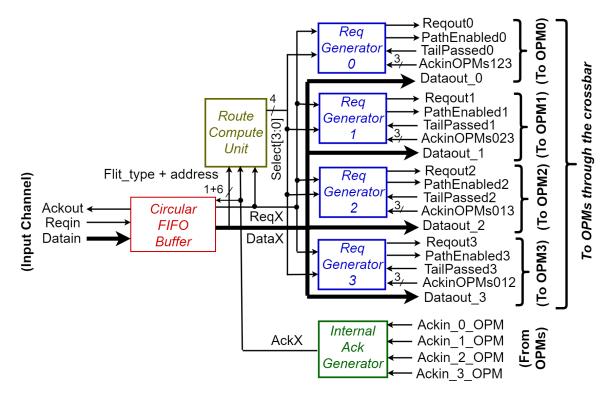

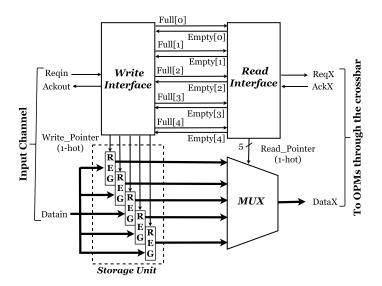

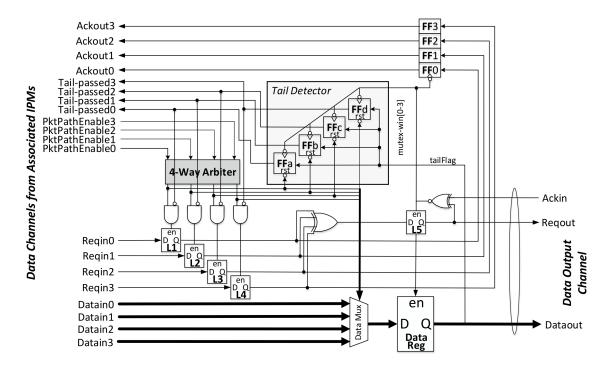

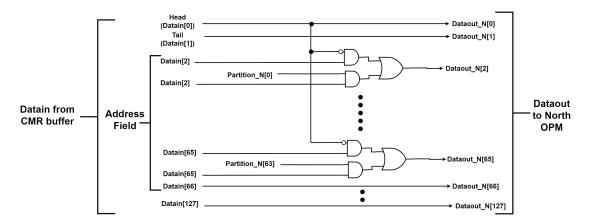

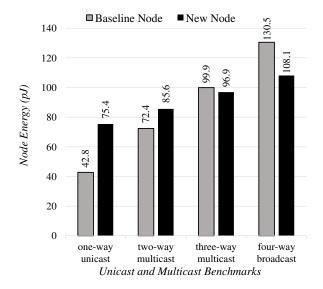

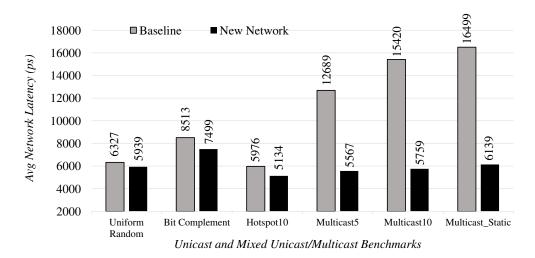

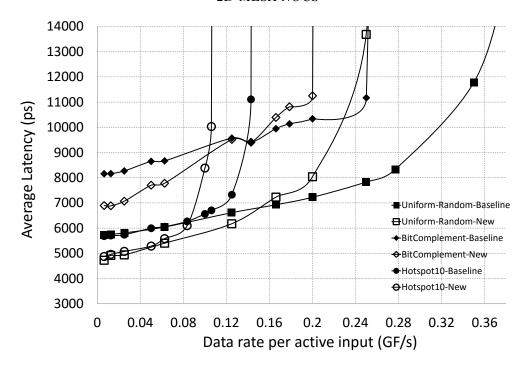

### 1.6 Research Focus