# Transfer printing of photonic nanostructures to silicon integrated circuits

Charalambos Klitis<sup>1</sup>, Benoit Guilhabert<sup>2</sup>, John McPhillimy<sup>2</sup>, Stuart May<sup>1</sup>, Ningh Zhang<sup>1</sup>, Michael J. Strain<sup>2</sup>, Marc Sorel<sup>1</sup>

> School of Engineering, University of Glasgow, Oakfield Avenue, Glasgow, G12 8LT, UK

> Institute of Photonics, Dept. of Physics, University of Strathclyde, Glasgow G1 1RD, UK Corresponding author email address: charalambos.klitis@glasgow.ac.uk

**Abstract:** Optical systems require the integration of technologies fabricated on different materials. We use a transfer printing technique to integrate pre-processed III-V, polymer and silicon membrane devices onto passive optical circuits with nano-metric positional accuracy. **OCIS codes:** (230.3120) Integrated optics devices; (040.6040) Silicon; (130.6622)

## 1. Introduction

One of the main advantages of silicon photonics is its compatibility with CMOS technology, which provides a wellestablished route for large volume and low cost manufacturing [1]. For this reason, silicon photonics has been widely taken up by industry [2] as a volume production platform for next generation telecommunications, sensing and computing. However, the silicon photonic toolkit lacks a number of key capabilities, such as efficient electrooptic modulation and light generation. Thus far, this has been a significant barrier to the creation of truly integrated chip-scale photonics. Chip-scale bonding of separate pre-fabricated III-V devices on silicon-on-insulator (SOI) chips [3] is of great industrial interest as it allows for the individual components to be fabricated and optimised in their respective foundries. Amongst the various techniques proposed, transfer printing (TP) is gaining popularity as it offers scalability as well as sub-micro scale alignment. Recent TP demonstrators include the integration of III-V lasers, Ge detectors [4], nano-lasers [5] and quantum emitters [6] on an SOI platform.

If robust fabrication techniques of membranes are coupled to nano-metric placement accuracy, TP offers a promising route to complex hybrid integration platforms that can fully exploit the vertical dimension. In this work, we present a TP assembly technique with nano-metric accuracy that is used to demonstrate dual-layer silicon photonic devices, vertically coupled polymer waveguides and AlGaAs microdisks integrated on an SOI chip.

## 2. Nano-metre alignment accuracy transfer printing

In the TP technique, fully fabricated membrane devices are detached from their native substrate and transferred to a host substrate using a highly accurate pick-and-place tool (Fig.1). The use of device membranes has a number of key advantages, including mechanical flexibility of the membrane, allowing for high optical quality bonding of transferred devices to non-native substrates and the potential to reuse the valuable III-V substrate after processing.

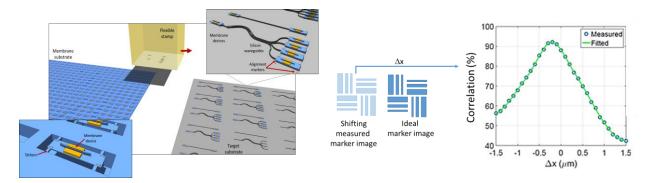

Fig. 1: (left) Schematic vision of the Transfer Printing (TP) method. Individual III-V membrane devices are detached from their native substrate using a flexible stamp in the TP tool. Computer vision alignment allows the deposition of these devices onto pre-fabricated photonics chips. (right) Schematic of the registration marker cross-correlation technique and measured registration mark cross-correlation with reference grid. The peak of the fitted curve indicates the stage displacement in one dimension required for alignment

Crucially, it has been demonstrated that this technique can transfer a large number of membranes devices simultaneously, paving the way for scalable integration of photonic circuits. In order to integrate waveguide devices

on separate, vertically coupled layers, the printing process must demonstrate positional accuracy in the sub-100nm range. Using computer vision optical microscopy techniques, we have developed a layer to layer alignment process allowing the direct integration of waveguide devices. Absolute positional accuracy is measured by referencing the imaged marker against a predefined ideal position. The marker image is captured as a function of displacement between the imaging system and the translational stage on which the sample is mounted. Each image is cross-correlated with the ideal marker image stored in memory, as illustrated in Fig.1.

## 4. Membrane devices to SOI integrated circuits

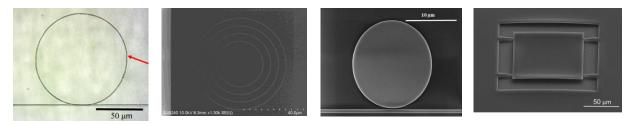

To show the flexibility and the alignment accuracy of the technique a number of different membrane devices were fabricated and transferred to a host photonic chip. (i) SU8 polymer waveguides vertically coupled to a ring resonator (Fig.2a) (ii) Silicon membranes containing concentric rings with sidewall gratings coupled to SOI bus waveguides for the simultaneous emission of vertical and concentric vortex beams (Fig.2b). (iii) AlGaAs microdisks coupled to a silicon bus waveguide for efficient non-linear applications (Fig. 2c). In all of these examples, the membranes were formed by removing the underlying cladding layer and were kept suspended to the chip via thin mechanical supports (Fig. 2d). Suspended membranes were detached from their native substrate using a polymeric micro-stamp and then transferred to the host substrate using a differential adhesion method.

Fig. 2: SEM and optical images of (a) Vertically coupled polymer ring resonator fabricated by printing the ring layer onto the bus waveguide layer; (b) Concentric microring resonators in silicon with sidewall gratings; (c) A transferred AlGaAs micro-disk next to a prefabricate Si waveguide; (d) A silicon membrane with mechanical supports

## 4. Conclusions

In this work we present a number of integrated photonic chips fabricated by hybrid device micro-assembly that show the versatility of the transfer printing technique. Using computer vision optical microscopy techniques, we demonstrated alignment accuracy as good as 100 nm, which enables the integration of highly confining optical waveguides with sub-micrometer cross sections.

#### 5. Acknowledgments

This work was supported by the Engineering and Physical Sciences Research Council through the *Cornerstone* (EP/L021129/1) and *Parallel Heterogeneous Integration of III-V Devices on Silicon Photonic Chips* (EP/P013570/1).

#### 6. References

[1] L Pavesi. Will silicon be the photonic material of the third millennium? Journal of Physics: Condensed Matter, 15(26) (2003)

[2] Rickman, A. The commercialization of silicon photonics. Nat. Photonics 8, 579-582 (2014).

[3] Yang, S. et al. A single adiabatic microring-based laser in 220 nm silicon-on-insulator. Opt. Express 22(1), (2014).

[4] J. Justice, et al. Wafer-scale integration of group III-V lasers on silicon using transfer printing of epitaxial layers, Nature Photon., vol. 6, no. 9, pp. 610–614, 2012.

[5] D. Jevtics et al. Integration of Semiconductor Nanowire Lasers with Polymeric Waveguide Devices on a Mechanically Flexible Substrate, *Nano Lett.*, 2017, *17* (10)

[6] A. W. Elshaari *et al.*, "On-chip single photon filtering and multiplexing in hybrid quantum photonic circuits," *Nat. Commun.*, vol. 8, no. 1, p. 379, 2017.