# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Chen, Qianqiao

Title:

Exploring hardware support for resource management in the data centre

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

#### Take down policy

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

· Your contact details

Bibliographic details for the item, including a URL

• An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Exploring hardware support for resource management in the data centre

By

QIANQIAO CHEN

Department of Electric and Electronic Engineering UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements of the degree of DOCTOR OF PHILOSOPHY in the Faculty of Electric and Electronic Engineering.

May 2018

Word count: Approximately 22000

ABSTRACT

he management of data centre resources has become important as their size, complexity, and power consumption are increasing. Efficient resource utilisation helps reduce the construction and maintenance costs of data centres. Using that background as a starting point, this thesis explores hardware support that increases the efficiency of resources in data centres.

Either optimising existing data centre architectures or establishing new data centre architectures has a strong requirement on the data centre network. Therefore, this thesis establishes a network interface equipped with the new OptoPHY optical transceiver. The feasibility and quality of an optical transceiver when it is combined with a server board are evaluated by comparing it with a traditional SFP+ transceiver.

The reconfigurable FPGA platforms have a great potential to reduce power consumption and maintenance costs due to their high-volume programmable parallel processing features. Therefore, this thesis tries to explore the management of FPGA resources in a data centre environment.

Based on partial reconfiguration technology, an architecture that would virtualise the FPGA platforms is proposed and implemented. Resources on the FPGA chip are partitioned into several regions. Furthermore, an interconnect system is implemented to share I/Os with all of the regions and enable communication between regions.

When several FPGA platforms are combined for pipelined stream processing, it is difficult to perform function reconfiguration over multiple FPGA platforms that have a short downtime. That is because it is hard to predict the network delay of reconfiguration requests sent from a centralised manager. Therefore, a new network protocol is proposed, and the associated protocol processor is implemented to synchronise the reconfigurations of related FPGA platforms.

#### **DEDICATION AND ACKNOWLEDGEMENTS**

would like to thank my supervisors, Dr. Georgios Zervas and Dr. Jose Nunez-Yanez, who have helped me with their guidance, supervision, and constructive comments. My PhD has been an amazing experience, and I sincerely thank them for the tremendous academic support they have given me.

I would also like to thank my colleagues Vaibhawa Mishra, Hui Yuan, and Adaranijo Peters. I have had plenty of helpful discussions with them at various stages of my studies.

I would like to thank my parents. Their love and affection have been the sources of motivation and encouragement for my studies. I would also like to thank all my friends for supporting and encouraging me with their best wishes.

### **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

# TABLE OF CONTENTS

|                |       | Pa                      | age  |  |  |  |  |  |  |

|----------------|-------|-------------------------|------|--|--|--|--|--|--|

| List of Tables |       |                         |      |  |  |  |  |  |  |

| Li             | st of | Figures                 | xiii |  |  |  |  |  |  |

| 1              | Intr  | oduction                | 1    |  |  |  |  |  |  |

|                | 1.1   | Motivation              | 1    |  |  |  |  |  |  |

|                | 1.2   | Goals                   | 4    |  |  |  |  |  |  |

|                | 1.3   | Thesis outline          | 4    |  |  |  |  |  |  |

|                | 1.4   | Main contributions      | 5    |  |  |  |  |  |  |

|                | 1.5   | Publications            | 6    |  |  |  |  |  |  |

| 2              | Lite  | rature review           | 9    |  |  |  |  |  |  |

|                | 2.1   | Introduction            | 9    |  |  |  |  |  |  |

|                | 2.2   | Resource virtualization | 12   |  |  |  |  |  |  |

|                |       | 2.2.1 Prediction        | 13   |  |  |  |  |  |  |

|                |       | 2.2.2 Allocation        | 14   |  |  |  |  |  |  |

|                |       | 2.2.3 Migration         | 15   |  |  |  |  |  |  |

|                |       | 2.2.4 Summary           | 16   |  |  |  |  |  |  |

|                | 2.3   | Resource disaggregation | 17   |  |  |  |  |  |  |

|                |       | 2.3.1 Software support  | 17   |  |  |  |  |  |  |

|                |       | 2.3.2 Hardware support  | 18   |  |  |  |  |  |  |

|                |       | 2.3.3 The dRedBox       | 19   |  |  |  |  |  |  |

|                |       | 2.3.4 Summary           | 20   |  |  |  |  |  |  |

# TABLE OF CONTENTS

|   | 2.4 | Management of FPGA resources                                   | 21 |

|---|-----|----------------------------------------------------------------|----|

|   |     | 2.4.1 Virtualisation of FPGA resources                         | 22 |

|   |     | 2.4.2 Disaggregation of FPGA resources                         | 26 |

|   | 2.5 | Summary                                                        | 29 |

| 3 | Hig | h performance network interface for resource disaggregation    | 31 |

|   | 3.1 | Introduction                                                   | 31 |

|   | 3.2 | Motivation                                                     | 33 |

|   | 3.3 | Experiment                                                     | 34 |

|   |     | 3.3.1 Testbed set up                                           | 34 |

|   |     | 3.3.2 Technology and skill                                     | 36 |

|   | 3.4 | Result                                                         | 40 |

|   |     | 3.4.1 Optical transceiver result                               | 40 |

|   |     | 3.4.2 Optical switch result                                    | 40 |

|   |     | 3.4.3 Ethernet layer result                                    | 43 |

|   | 3.5 | Limitation                                                     | 43 |

|   |     | 3.5.1 Summary                                                  | 45 |

|   | 3.6 | Conclusion                                                     | 46 |

| 4 | The | virtualisation of reconfigurable FPGA resources                | 47 |

|   | 4.1 | Introduction                                                   | 47 |

|   | 4.2 | Background                                                     | 49 |

|   | 4.3 | Architecture Overview                                          | 53 |

|   | 4.4 | Evaluation of the interconnect                                 | 56 |

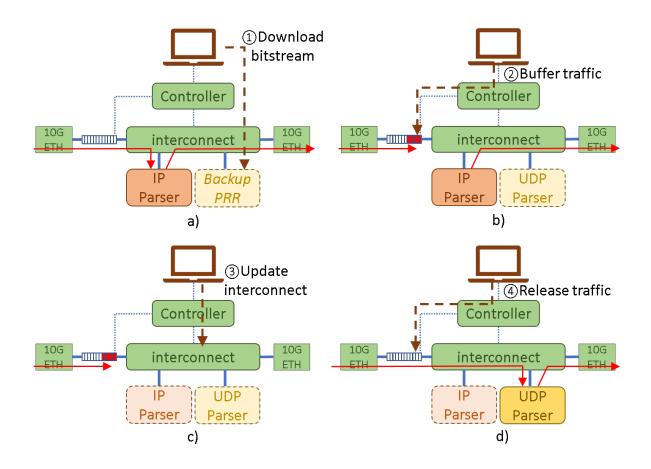

|   | 4.5 | Reconfiguration Process                                        | 60 |

|   | 4.6 | Experiment and Demonstration                                   | 64 |

|   | 4.7 | Conclusion                                                     | 68 |

|   |     |                                                                |    |

| 5 | Syn | chronizing the reconfiguration on disaggregated FPGA resources | 71 |

# TABLE OF CONTENTS

| Bi | Bibliography 9 |                 |    |  |  |  |  |  |  |  |

|----|----------------|-----------------|----|--|--|--|--|--|--|--|

|    | 6.3            | Future work     | 96 |  |  |  |  |  |  |  |

|    | 6.2            | Lessons learned | 96 |  |  |  |  |  |  |  |

|    | 6.1            | Achievement     | 95 |  |  |  |  |  |  |  |

| 6  | Conclusion     |                 |    |  |  |  |  |  |  |  |

|    | 5.7            | Conclusion      | 90 |  |  |  |  |  |  |  |

|    | 5.6            | Experiment      | 87 |  |  |  |  |  |  |  |

|    | 5.5            | Evaluation      | 83 |  |  |  |  |  |  |  |

|    | 5.4            | Implementation  | 78 |  |  |  |  |  |  |  |

|    | 5.3            | Motivation      | 74 |  |  |  |  |  |  |  |

|    | 5.2            | Background      | 72 |  |  |  |  |  |  |  |

# Bibliography

# LIST OF TABLES

| TABLE |                                                                              |      |  |  |  |

|-------|------------------------------------------------------------------------------|------|--|--|--|

| 3.1   | The resource utilisation of the protocol processor                           | 33   |  |  |  |

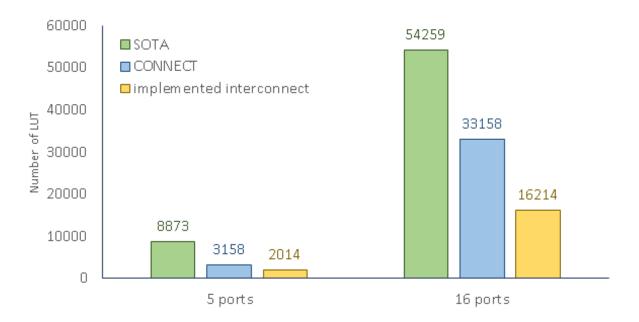

| 4.1   | The comparison between SOTA, CONNECT and the implemented interconnect system | n 60 |  |  |  |

| 4.2   | Resource Utilization and Partial Bitfile Size                                | 63   |  |  |  |

| 4.3   | Resource Utilization                                                         | 65   |  |  |  |

| 5.1   | The resource utilisation of the protocol processor                           | 87   |  |  |  |

# LIST OF FIGURES

# FIGURE

# Page

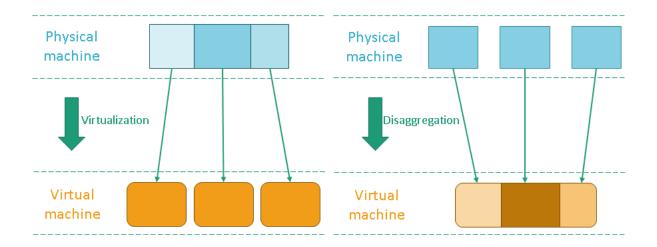

| 2.1  | The resource virtualisation and disaggregation of data center.                 | 11 |

|------|--------------------------------------------------------------------------------|----|

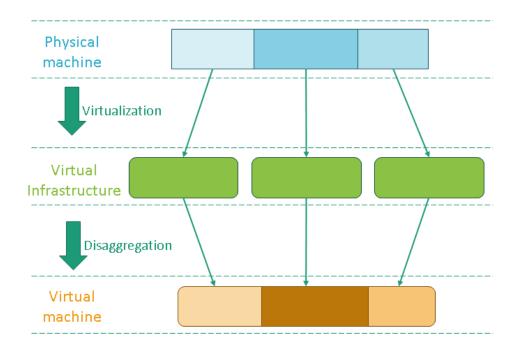

| 2.2  | The combined utilization of virtualisation and disaggregation.                 | 12 |

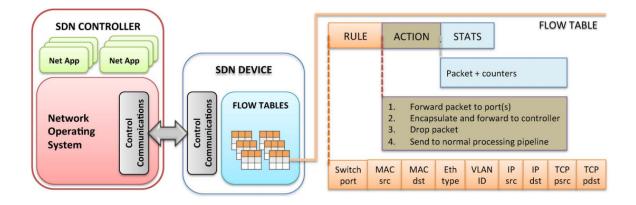

| 2.3  | The overall concept of software-defined network.                               | 19 |

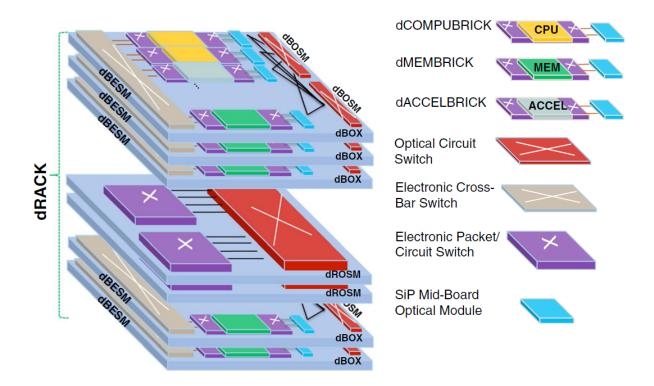

| 2.4  | The structure of the dRedBox data center resource disaggregation system        | 21 |

| 2.5  | The basic architecture of the system                                           | 24 |

| 2.6  | The design principle of the virtualization system of FPGA resources.           | 25 |

| 2.7  | The disaggregation system for FPGA devices                                     | 27 |

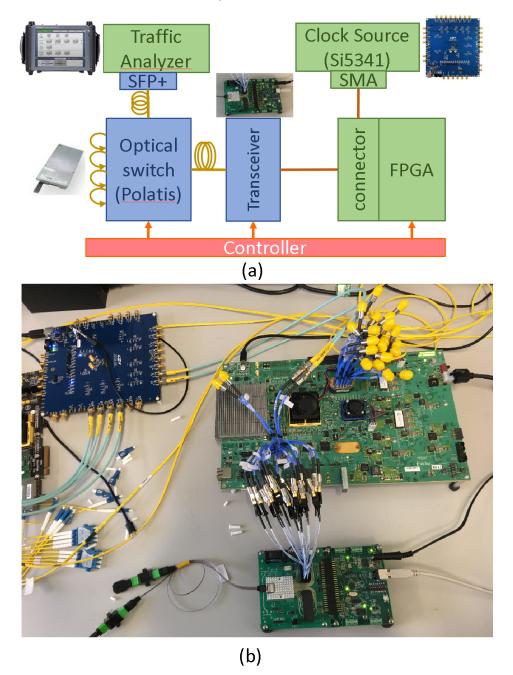

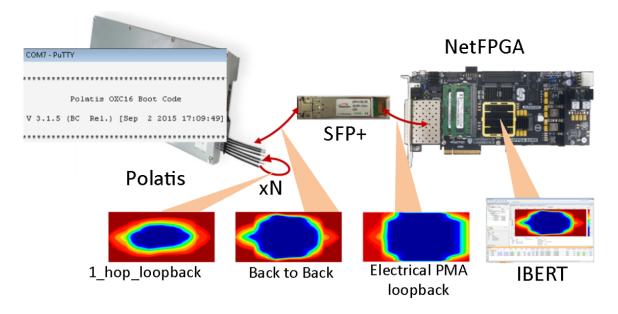

| 3.1  | The testbed set up of the OptoPHY transceiver.                                 | 35 |

| 3.2  | The testbed set up of the SFP+ transceiver                                     | 36 |

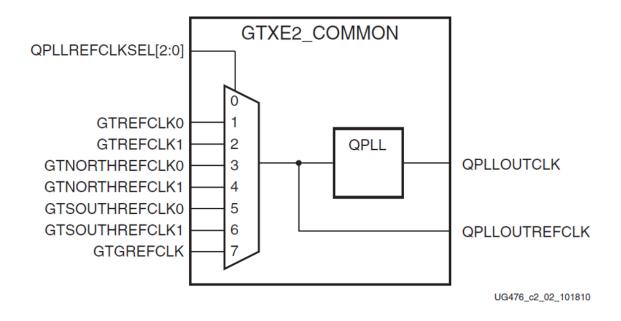

| 3.3  | The clock structure of the Xilinx gigabit transceiver.                         | 38 |

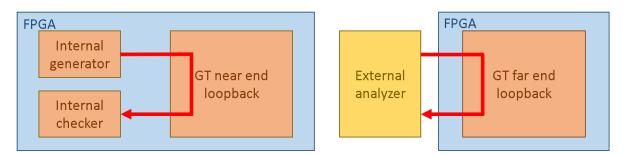

| 3.4  | The loopback mode in the Xilinx IBERT                                          | 39 |

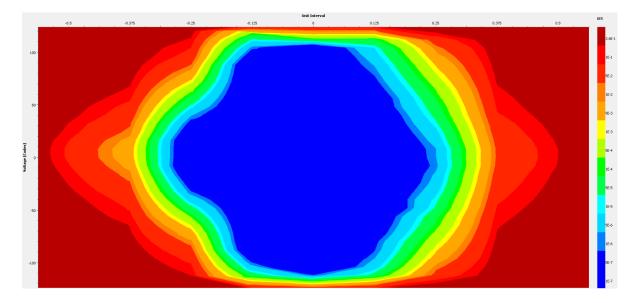

| 3.5  | A typical eye diagram collected by the IBERT.                                  | 39 |

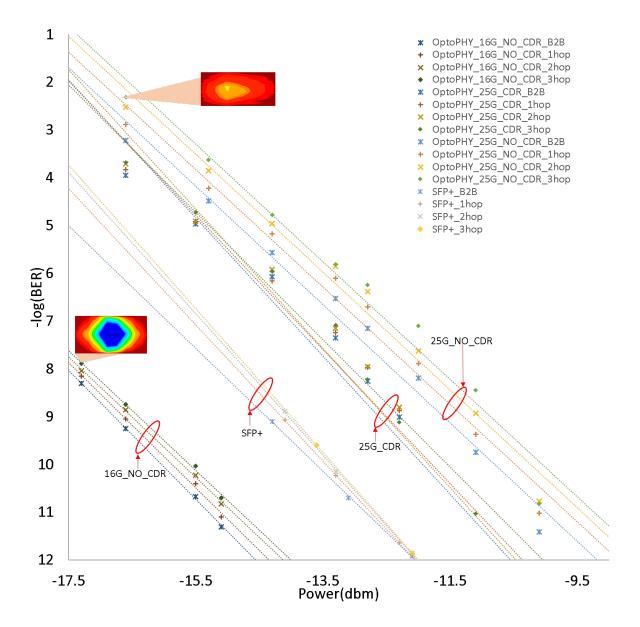

| 3.6  | The bit error rate of the OptoPHY and SFP+ optical transceiver                 | 41 |

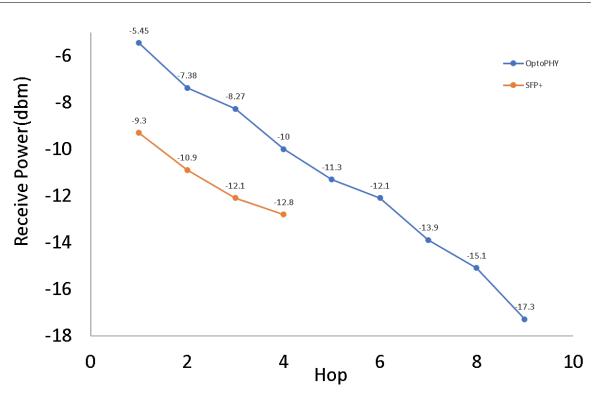

| 3.7  | The loss of power of the optical switch                                        | 42 |

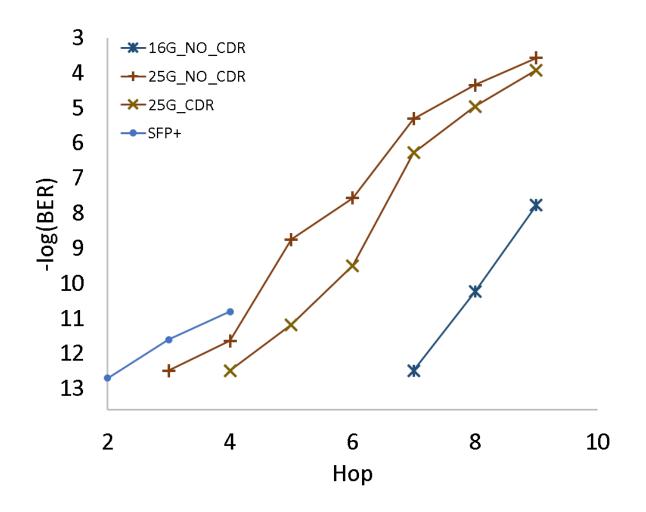

| 3.8  | The relationship between the hops and the BER.                                 | 43 |

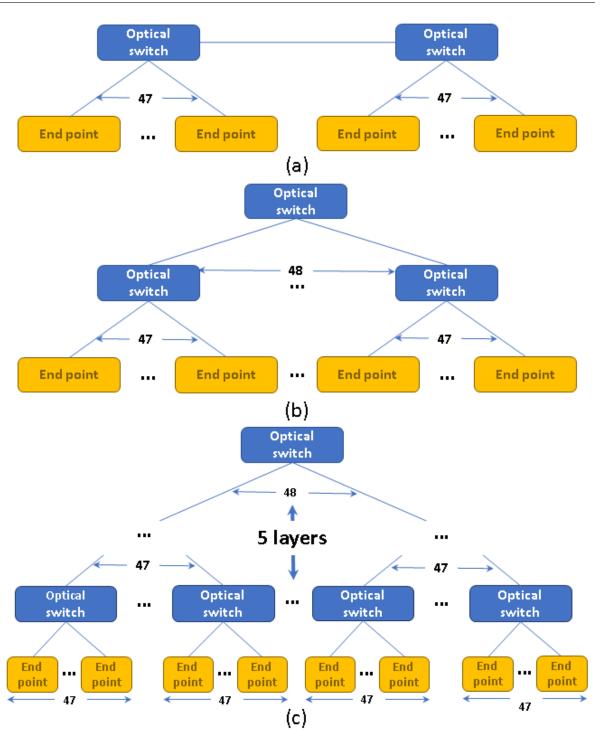

| 3.9  | The scalability of a multi-tier network.                                       | 44 |

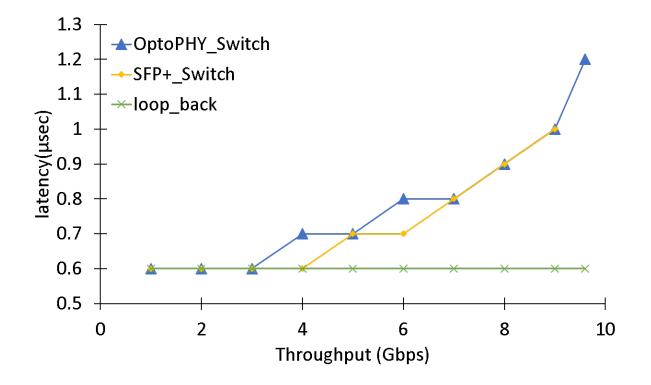

| 3.10 | The measured latency at the Ethernet layer.                                    | 45 |

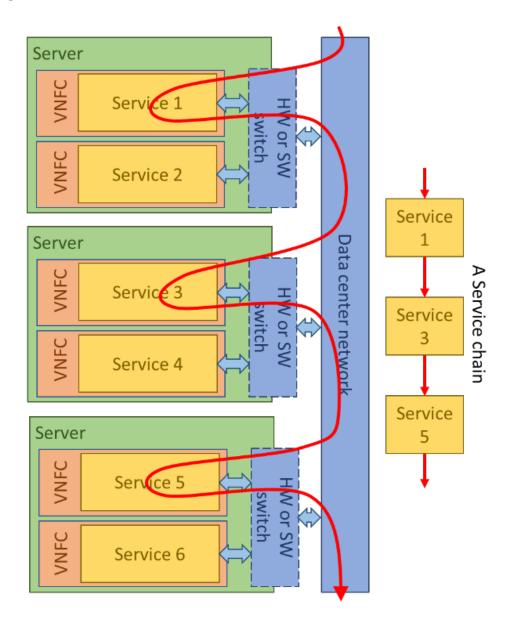

| 4.1  | A typical infrastructure of NFV and the service chain.                         | 50 |

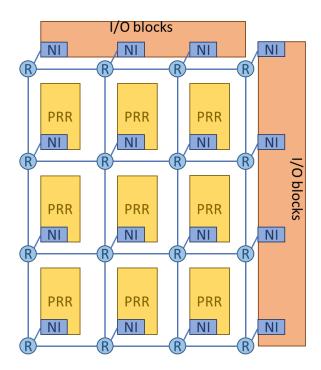

| 4.2  | A typical NoC based architecture for FPGA vidtualisation.                      | 52 |

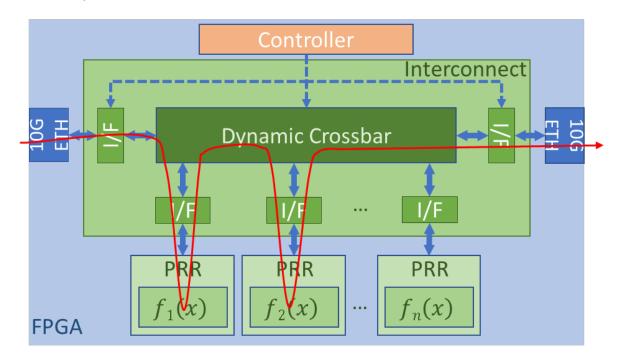

| 4.3  | The overview of the proposed FPGA virtualization architecture for NFV platform | 54 |

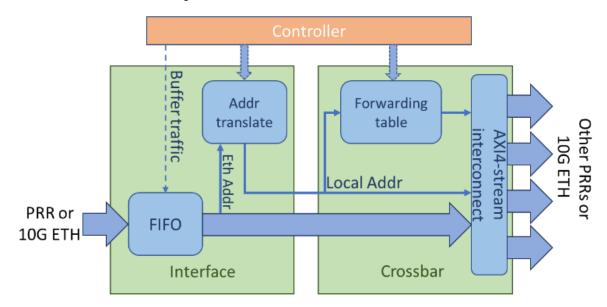

| 4.4  | The detailed structure of the interface and dynamic crossbar of the interconnect               | 55       |

|------|------------------------------------------------------------------------------------------------|----------|

| 4.5  | The LUT resource utilisation of CONNECT, SOTA and the interconnect system                      |          |

|      | implemented                                                                                    | 57       |

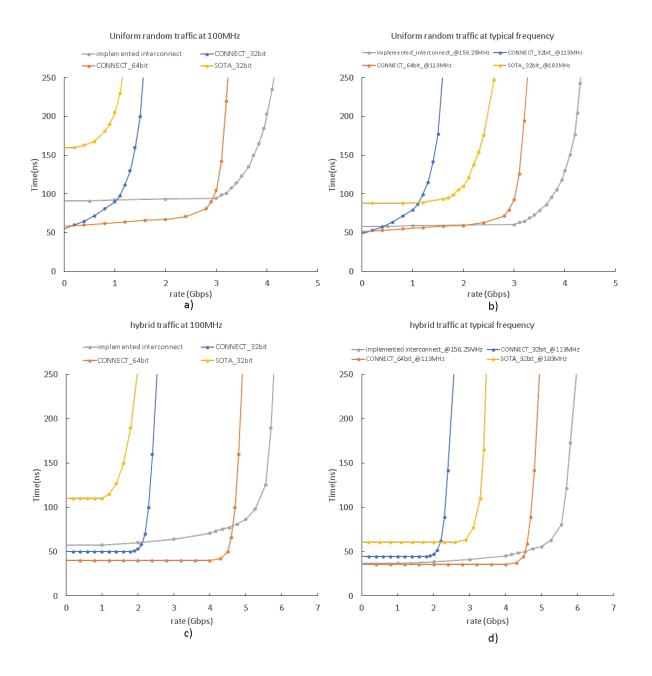

| 4.6  | The pattern for the static part of the hybrid traffic.                                         | 58       |

| 4.7  | The comparison between the implemented interconnect system and the existing SOTA               |          |

|      | and CONNECT interconnect.                                                                      | 59       |

| 4.8  | The proposed reconfiguration process that supports function reconfiguration in real            |          |

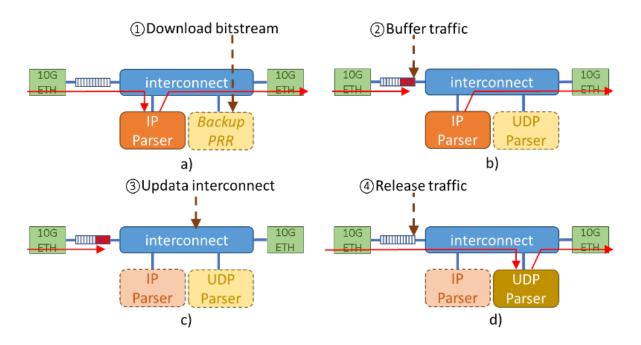

|      | time                                                                                           | 62       |

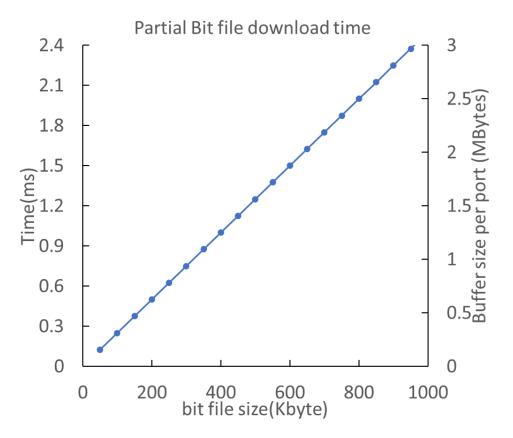

| 4.9  | Time and buffer needed for packet loss free partial bitfile download                           | 63       |

| 4.10 | Time and buffer needed for packet loss free NoC Update time.                                   | 64       |

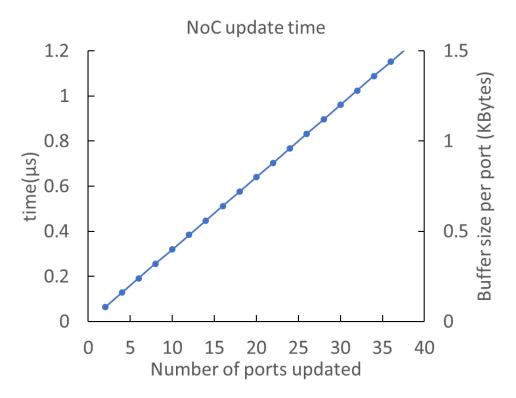

| 4.11 | The experiment set up at 156.25MHz and 200MHz                                                  | 66       |

| 4.12 | The demonstrated reconfiguration process.                                                      | 67       |

| 4.13 | Network function virtualization in data centers.                                               | 68       |

| 5.1  | Reconfiguration of FPGA functions on single chip and in data centers.                          | 75       |

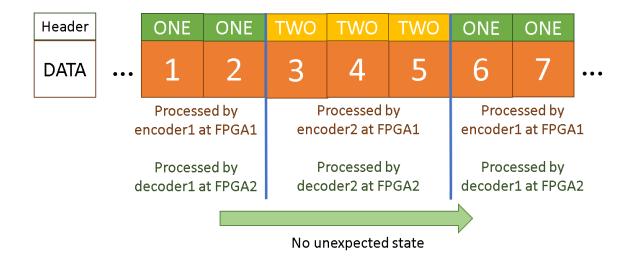

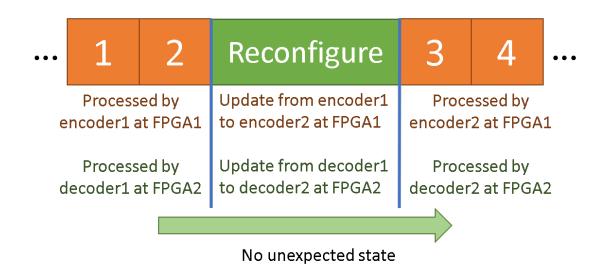

| 5.2  | An example for network-wide coherent function reconfiguration.                                 | 76       |

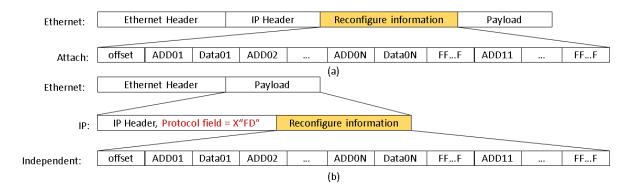

| 5.3  | The first method: the reconfigure information is attached to every packet as headers.          | 77       |

| 5.4  | The second method: the reconfiguration is encapsulated in an independent packet                | ••<br>77 |

|      |                                                                                                |          |

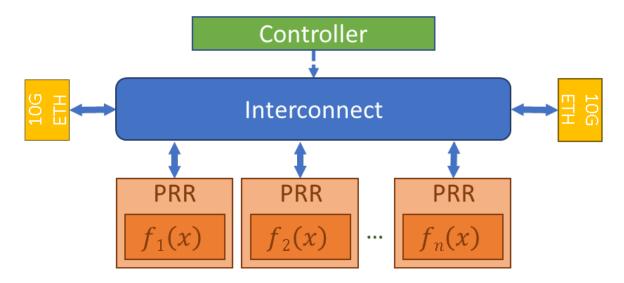

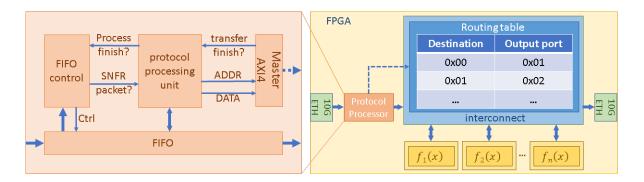

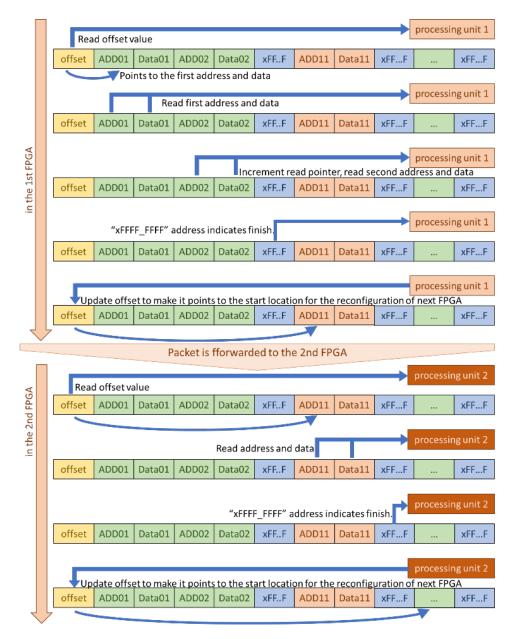

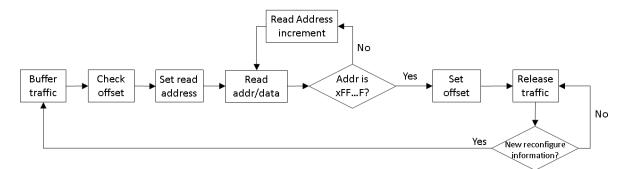

| 5.5  | The overview architecture of the reconfigurable platform.                                      | 78       |

| 5.6  | The testbed set up of the OptoPHY transceiver.                                                 | 79       |

| 5.7  | The location and architecture of the protocol processor                                        | 80       |

| 5.8  | The protocol for both method.                                                                  | 81       |

| 5.9  | The brief description of the behaviour of the protocol processing unit. $\ldots$               | 82       |

| 5.10 | The state machine of the protocol processing unit                                              | 83       |

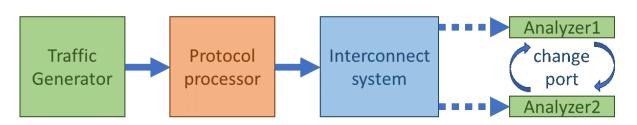

| 5.11 | The simulation set up to compare the proposed two methods. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 84       |

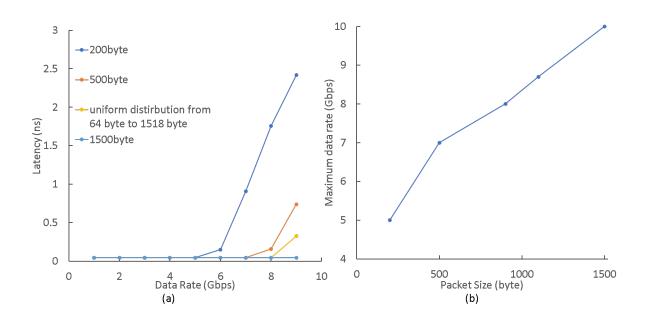

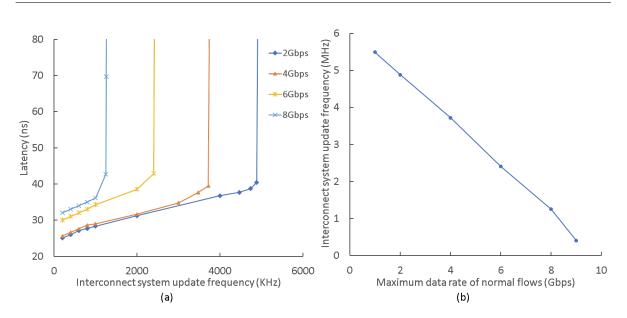

| 5.12 | Simulation result for the first method                                                         | 85       |

| 5.13 | The simulation result for the second method                                                    | 86       |

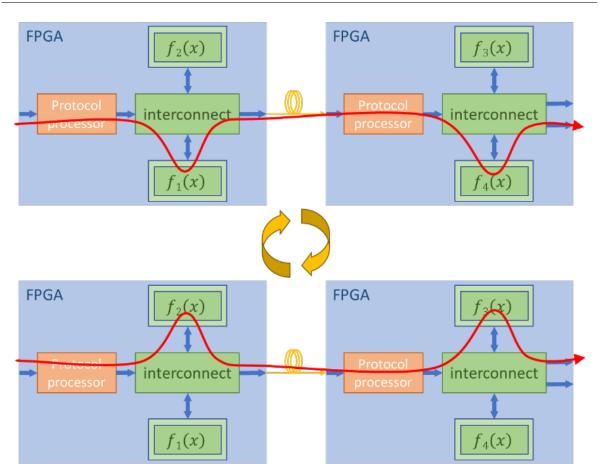

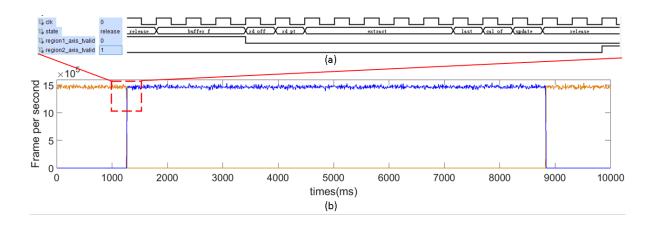

| 5.14 | The demonstrated reconfiguration process.                                                      | 88       |

| 5.15 | The captured reconfiguration process                                                           | 89       |

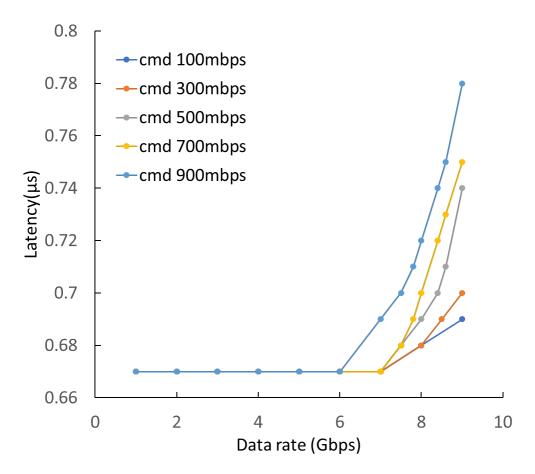

| 5 16 | The latency | v influence | of the | protocol | nrocessing  |      |     |     |     |     |     |   |     |     |   |     |   | 89 |

|------|-------------|-------------|--------|----------|-------------|------|-----|-----|-----|-----|-----|---|-----|-----|---|-----|---|----|

| 0.10 | The fatence | ymmuchec    | or unc |          | processing. | <br> | • • | • • | • • | • • | • • | • | • • | • • | • | • • | • | 00 |

#### **INTRODUCTION**

#### 1.1 Motivation

The information technology (IT) industry has experienced exponential growth since its birth in the previous century to become one of the most remarkable industries in today's world. Cloud computing is shaping the way IT solutions are designed and purchased because of its potential to reduce operating costs and management overheads. Many companies are moving their IT infrastructure from public data centres and are starting to build private data centres. Consequently, the requirement on computing resource such as CPU, memories and storage is rapidly growing with the ever-growing workload of data centres.

Due to the diverse and dynamic demand from tenants, the resource utilisation found in data centres has become inefficient. Studies show that from June 2009 to May 2011, the average utilisation of CPUs, memory , and discs on thousands of randomly selected data centre servers was 17.76%, 77.93% and 75.25% respectively [1]. While the covariance was 1.02%, 0.3% and 0.32% respectively. Another study on resource utilisation of the Google Cluster Trace over a period of 29 days reports that the mean CPU utilisation is less than 60% and the mean memory utilization is less than 50% [2]. The allocated CPU resources to a task equals the peak requirement (70% of a server), although the CPU requirement of a task is 40% most of the time. According to these

#### CHAPTER 1. INTRODUCTION

surveys, data center operators tends to allocate resource according to the peak resource usage of a task or a request. And the reason is that current data center architecture cannot support smooth resource reallocation during the runtime of a task.

The inefficient resource utilisation in a data centre results in increasing economic pressure for a firm. It is reported that in 2015, more than 400,000 data centres in China alone were consuming about 1.5% of national electricity supply [3] [4]. In the U.S., consumption in 2014 reached 70 TWh, about 1.8% of total supply [5]. Energy consumption caused by the inefficient resource utilisation also increases the operating costs for data centre operators. Furthermore, it is predicted that densely populated data centres may arouse environmental problems due to their tremendous energy consumption [6]. To optimise resource utilisation, research and technologies to better manage the fast-growing data centre resources are proposed. For example, the resource virtualisation propose methods to share a single physical platforms to multiple users, and the resource disaggregation suggests to combine distributed platforms to build a complete computing system. In order to increase the resource efficiency of data center, this paper focus on developing methods and platforms to deliver high bandwidth flexible network stream processing.

Servers in data centres act as the main containers of computing resources. Cloud applications are deployed on servers in the form of computing resources requests. Operations within each server are organized automatically by local operating systems, while operations between servers require an additional data centre manager. In other words, operations between servers are more complex and have a weaker performance than operations within servers. To avoid operations between servers as much as possible, data centre operators usually abstract the resource management in data centres into a bin pack problem where cloud requests are packed by servers in a best-fit way. In other words, data centre operators are developing additional algorithms and building additional control layers in resource management to overcome the low performance of operations between servers. Difficulties in operations between servers come from hardware restrictions. Networks within a server only need to connect a limited number of endpoints, while networks between servers (data centre network) ideally need to connect countless endpoints. Compared to networks within servers, data centre networks have stronger performance requirements. Therefore, this thesis explores the network interface to increase the performance of data centre networks and build a data centre resource with fewer boundaries caused by servers.

On the other hand, heterogeneous data centers, which contains a set of accelerators for graphic processing and reconfigurable processing, have been suggested. Reconfigurable devices are able to deliver application-specific higher performance functions compared to general purpose processors. At the same time, they are more flexible than other application-specific integrated circuits. These advantages of reconfigurable FPGA resources help reduce power consumption and increase the performance of data centres. However, the reconfiguration feature also provides flexibilities in the control of reconfigurable devices, which introduces more challenges for the management of reconfigurable resources.

The reconfigurable FPGA resources are often treated as a piece of memory that is attached to general purpose processors since existing resource management methods such as virtualisation can be adopted. However, parallel high-volume stream processing is a key feature of FPGA resources. Data movement through the processors will affect this feature as the memory-mapped interfaces between processors and FPGA resources limit the total performance. Therefore, this thesis will try to develop a system that virtualises and manages FPGA resources independently without involving data movement through memory-mapped interfaces.

Apart from data movement, the function reconfiguration on multiple devices also needs to be concerned with the management of reconfigurable FPGA resources. Existing solutions that reconfigure functions on multiple FPGAs follow a deploy-and-run manner. Only when all the associated FPGA devices are properly configured can the newly-deployed function begin processing. As the downtime of every reconfiguration is relatively long, it is hard to perform function reconfiguration at a very high frequency. This is also because most of the time will be consumed by function reconfiguration rather than data processing. Therefore, this thesis will try to come up with a new reconfiguration manner to reduce downtime and to enable reconfiguration at higher frequencies.

# 1.2 Goals

In summary, the purpose of this thesis is to explore and develop hardware systems that help increase the resource efficiency in data centres. This thesis aims to propose hardware systems that increase the performance of data centre networks, as well as to proposes methods that introduce reconfiguration FPGA resources in data centres. The goals of this thesis are listed as follows:

- Introduce the development of resource management in data centres, including virtualisation and disaggregation of computing resources.

- Develop hardware systems that increase the performance of data centre networks and help break the limits of servers.

- Design systems to efficiently manage stream processing in reconfigurable FPGA resources at a low performance cost.

- Explore methods to control the reconfiguration of multiple FPGA resources in data centres.

# 1.3 Thesis outline

Chapter 2 reviews the literature on data centre resource management. According to the purpose, this thesis classifies the management method into two types: virtualisation and disaggregation. Virtualisation tries to partition resources on a single physical machine and share the resources with multiple tenants. Meanwhile, disaggregation aims to combine resources on multiple platforms into a complete system. Specifically, the virtualisation and disaggregation of FPGA resources are reviewed. Methods that manage FPGA resources in a data centre environment are introduced.

The burden of the scale-up of data centres mainly falls on the network. Increasing the performance of existing data centres and developing new data centre architectures both require a powerful high bandwidth network. Therefore in chapter 3, a high bandwidth network interface for the server is set up. Equipped with advanced optical transceivers, the network interface is

able to deliver a higher bandwidth at lower power costs and a lower footprint. The bit error rate of an optical transceiver is collected and is compared with the that of a traditional SFP+ transceiver. Furthermore, the interface is tested in the environment of an optical data centre network by attaching it to an optical switch.

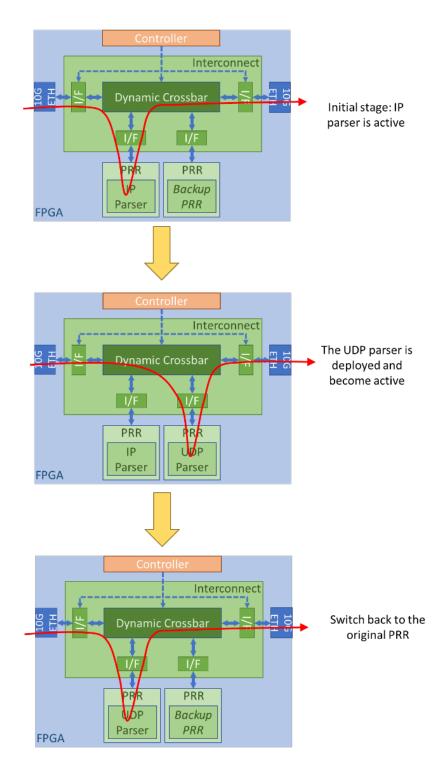

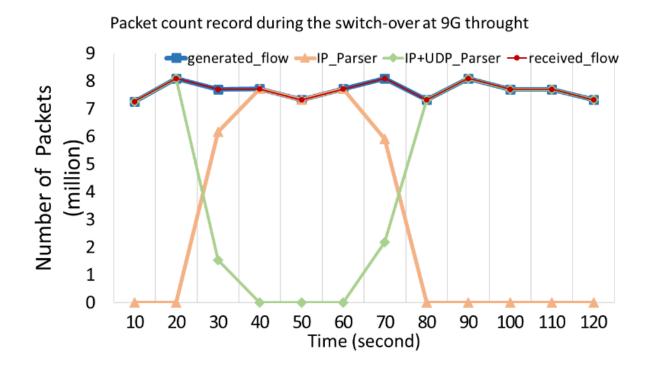

The virtualisation of reconfigurable FPGA resources is explored in chapter 4. Based on partial reconfiguration technology, resources on an FPGA platform are partitioned and distributed to different users. By establishing interconnect structures , the I/Os such as Ethernet ports are shared by reconfigurable regions and enable communication with off-chip networks. As an example, this thesis demonstrates the use of cases in the virtualized FPGA platform in the area of network function virtualisation to deliver high-performance flexible network functions.

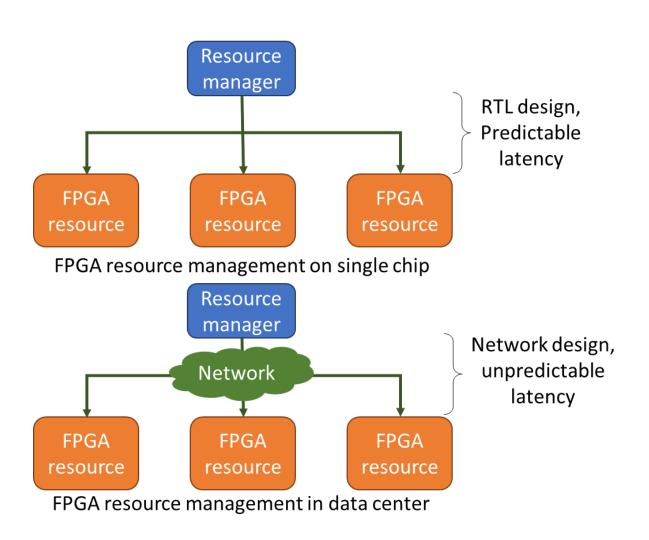

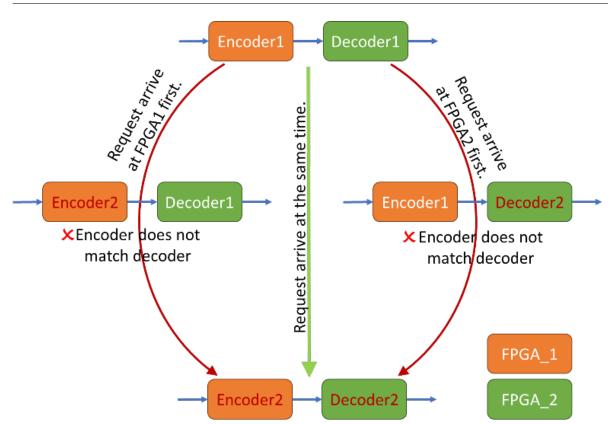

Chapter 5 explores the disaggregation of reconfigurable FPGA resources. A common method to manage and combine FPGA resources is to send a configuration request to each FPGA device from a centralised controller. However, as network latency is not predictable, it takes time to deploy functions resulting in downtime during the runtime reconfiguration. Therefore, in chapter 5, a new network protocol is suggested to spread configuration requests through the data centre. The protocol is able to synchronise the reconfiguration on pipelined stream processing over multiple FPGA resources.

Chapter 6 states the conclusion of the thesis and summarises the work that was done.

#### **1.4 Main contributions**

This thesis explores hardware systems that support resource management in data centres. This work also proposes methods that both increase the performance of data centre networks and those that introduce reconfigurable FPGA resources in data centres. The main contributions are summarised as follows:

- Combine an OptoPHY optical transceiver with FPGA devices to establish a high-bandwidth network interface at a low PCB footprint cost.

- Compare OptoPHY with a traditional SFP+ optical transceiver.

- Set up the optical switch to emulate the optical data centre network.

- Implement a system to virtualise the FPGA platform. The feature of high-volume stream processing can be kept in the said system.

- Establish an on-chip interconnect system to switch traffic based on the Ethernet address.

- Propose a process to enable reconfiguration with a low downtime.

- Design and implement a method and an associated network protocol to synchronise the reconfiguration over multiple FPGAs.

- A network protocol to synchronise reconfiguration is designed.

- The associated protocol processor is implemented.

- The high-frequency reconfiguration over multiple FPGA devices is demonstrated.

# **1.5 Publications**

All the work is done with the help of my colleagues Vaibhawa Mishra, Hui Yuan, Adaranijo Peters, Peter De Dobbelaere, Michael Enrico, and Nick Parsons, as well as my supervisors, Jose Nunez-Yanez and Georgios Zervas. The contribution is supported by a number of academic papers:

Q. Chen, V. Mishra, N. Parsons, and G. Zervas, "Hardware programmable network function service chain on optical rack-scale data centers," in 2017 Optical Fiber Communications Conference and Exhibition (OFC), 2017.

Q. Chen, V. Mishra, and G. Zervas, "Reconfigurable computing for network function virtualization: A protocol independent switch," in 2016 International Conference on ReConFigurable Computing and FPGAs (ReConFig), 2016.

Q. Chen, V. Mishra, and G. Zervas, "Synchronizing reconfiguration of coherent functions on

disaggregated FPGA resources," in 2017 International Conference on ReConFigurable Computing and FPGAs (ReConFig), 2017.

Q. Chen, V. Mishra, G. Zervas, "SiP-enabled FPGA Network Interface for Programmable Access to Disaggregated Data Centre Resources", OSA Asia Communications and Photonics Conference, Nov 2017

Q. Chen, V. Mishra, J. Nunez-Yanez, and G. Zervas, "Reconfigurable Network Stream Processing on Virtualized FPGA Resources," International Journal of Reconfigurable Computing, vol. 2018, Article ID 8785903, 11 pages, 2018. doi:10.1155/2018/8785903

V. Mishra, Q. Chen, and G. Zervas, "REoN: A protocol for reliable software-defined FPGA partial reconfiguration over network," in 2016 International Conference on ReConFigurable Computing and FPGAs (ReConFig), 2016, pp. 1–7.

G. Zervas, V. Mishra, Q. Chen, "Network, Compute and Storage Function Programmability and Virtualization: An FPGA-based Disaggregated System", OSA Asia Communications and Photonics Conference, Nov 2016

G. Zervas et al., "Disaggregated compute, memory and network systems: A new era for optical data centre architectures," in 2017 Optical Fiber Communications Conference and Exhibition (OFC), 2017, pp. 1–3.

G. Zervas, H. Yuan, A. Saljoghei, Q. Chen, and V. Mishra, "Optically disaggregated data centers with minimal remote memory latency: Technologies, architectures, and resource allocation [invited]," IEEE/OSA Journal of Optical Communications and Networking, vol. 10, no. 2, pp. A270–A285, Feb 2018.

K. Katrinis et al., "On interconnecting and orchestrating components in disaggregated data

#### CHAPTER 1. INTRODUCTION

centers: The dReDBox project vision," in 2016 European Conference on Networks and Communications (EuCNC), 2016, pp. 235–239.

K. Katrinis et al., "Rack-scale disaggregated cloud data centers: The dReDBox project vision," in 2016 Design, Automation Test in Europe Conference Exhibition (DATE), 2016, pp. 690–695.

#### LITERATURE REVIEW

# 2.1 Introduction

Virtualisation is widely adopted to manage computing resources. It partitions resources on a single physical machine and shares them with multiple tenants by providing each tenant with an independent interface. Recent research also shows interest in the disaggregation of data centre resources. Although there is no final conclusion on the definition of resource disaggregation, this thesis defines disaggregation as technologies that combine resources on multiple platforms into a single complete computing system. The research on the management of data centre resources is reviewed in this chapter. Existing technologies on resource virtualisation are discussed. The new disaggregation concept is then introduced.

The resource virtualisation originates from the instruction-by-instruction simulation of a computing system on a different system. At the very beginning (in the middle of 1960s), virtualisation was often used by programmers who were working on a more general-purpose computer but were at the same time developing software for a new special-purpose computer which was under construction. They likely began by writing a simulator for the new computer on other available machines. Programmers were soon aware that it is possible to run a number of copies of the simulator at the same time and build a time-sharing system that supports multiple users [7].

Since then, virtualisation has evolved into the most common technology to manage computing resources. It is able to decouple the software from the physical hardware platform by delivering a diverse virtual environment to its client applications. Moreover, it can also divide the physical machine by (a) time-sharing the CPU resources and (b) partitioning the storage resources [8].

Being another technology that manages data centre resources, resource disaggregation recently attracted the attention of researchers. It originates from the concept of virtual storage [9]. Computer architecture designers have found that it is difficult to integrate large amounts of storage inside the chip. Hence, they started to use external storage and designed mechanisms to automatically swap the data in the external storage with the data in the internal storage. This approach enables the hierarchy storage systems. Based on observations of imbalance density growth of different on-board resources (e.g. CPU, memory, discs), there are reports that the relative low-density on-board memory limits the overall performance of a computer system [10].

On the other hand, data centres (previously known as multicomputers) whose performances are scalable with the number of computer resources have evolved out of the research [11]. Specifically, heterogeneous servers equipped with additional specific resources were widely adopted in data centres. Meanwhile, mechanisms which enable access to remote memory are proposed [12]. Heterogeneous servers in data centres have become the solution to the imbalance in the density of different on-board resources. Access to the remote memory was initially organised by the communication between local and remote processors. However, to reduce access latency and bypass the remote processors, remote direct memory access (RDMA) is proposed. The heterogeneous servers and RDMA have evolved into today's data centre resource disaggregation.

The disaggregation enables the independent scale-up of different types of resources by combining computing resources found on physically distributed platforms into a computing system. With resource disaggregation, data centre operators can upgrade different resources independently. Resource disaggregation also enables multiplex resources beyond the edge of the board at the scale of a data centre, which can potentially increase the efficiency of resource utilisation.

Both the virtualisation and disaggregation aim to project an illusion of machine interfaces.

FIGURE 2.1. The resource virtualisation and disaggregation of data centres.

However, different methods are adopted by the two concepts to achieve their goal. Virtualisation tries to isolate computing resources on a single physical machine to form multiple machine interfaces. Ideally, when using one of the interfaces, the user cannot feel the existence of other interfaces. On the other hand, disaggregation attempts to combine computing resources on multiple physical machines to build an interface out of a single machine. The user of the interface should not feel the location or distribution of the physical resources. In summary, as shown in Figure 2.1, virtualisation talks about how to transform a single physical machine into an illusion of multiple single machines, whereas disaggregation discusses how to combine multiple physical machines to deliver the illusion of a single machine.

While the virtualisation and disaggregation are independent concepts, they can create a powerful solution to the resource inefficiency of data centres when combined together as shown in Figure 2.3. The virtualisation technology is able to divide computing resource into finegrained virtual infrastructure. With disaggregation, it becomes possible to interconnect these infrastructure into on demand systems. Consequently, the combination of virtualisation and disaggregation helps to get every piece of data centre resource involved in the cloud computing.

This chapter reviews the associated technology for the resource virtualisation and disaggregation. The rest of this chapter is arranged as follows: in section 2.2, the virtualisation technology is reviewed. Section 2.3 introduces the disaggregation of data centre resources. Especially, the

FIGURE 2.2. The combined utilization of virtualisation and disaggregation.

virtualisation and disaggregation of FPGA resources is reviewed in section 2.4. And section 2.5 summarises this chapter.

# 2.2 Resource virtualization

Virtualisation is the most important technology in resource management of data centres. It divides a physical machine into multiple independent virtual machines by introducing a virtual machine monitor or hypervisor on top of the hardware platforms. Each virtual machine ideally executes its own operating system and applications without affecting others. Resource management based on virtualisation usually includes three steps: prediction, allocation, and migration. These three steps will be introduced in this section.

As the workloads of data centres fluctuate over time, the allocation of resources appropriate for a particular time slot may become inefficient in another time. As the following resource allocation algorithm and virtual machine migration may take a long time, it is hard to deploy applications immediately. Therefore, the prediction of a data centre's workload is essential in the management of its resources.

#### 2.2.1 Prediction

Jheng et. al. [13] find that the virtual machine (VM) workload has a strong periodicity, so they predict the workload by tracing the historical workload of each VM in the data centre. Some researchers notice that not all VMs observe the same workload pattern, thus they try to classify the VMs. Khan et. al. decompose applications into multiple components and each component is served by a set of VMs [14]. Algorithms are applied separately to VM sets that serve different components to predict the workload more accurately. Similarly, Chen classifies the VMs based on the tenant and finds that workloads from the same tenant are similar [15]. However, Bobroff states that not all the VMs' workloads are predictable, i.e., some VMs' workloads either lack periodicity or experience random changes over time [16]. Some scholars have put forward more advanced models. For example, Kashifuddin adopts the chaotic theory in the prediction of resource utilization [17], while Zhen's research utilises the Exponentially Weighted Moving Average (EWMA) model [18].

Although some scholars have suggested various models, predicting the workload of shortrunning tasks is still complicated and takes time. In contrast, long-running tasks show a periodic feature and are more predictable. Consequently, most workload predictions are only applicable in a relatively static scenario. For a dynamic data centre, it is hard for the prediction algorithm to come up with an accurate result on time.

Apart from monitoring resource utilisation, methods based on the trace of incoming requests are also suggested. For example, Vercauteren et. al. [19] trace the number of requests in web servers that randomly fluctuate over the short-term but exhibit periodic patterns in a diurnal cycle. Fang et. al. [20] have applied the ARIMA model to predict the short-term workload based on observing the number of requests. Unlike the resource utilisation of VMs, the number of incoming requests are easier to predict. However, it is difficult to map the incoming requests to the actual workload. These requests on the target hardware platforms need to be tested in advance, which needs additional effort. The interference between collocated requests has also not been considered, which may complicate the prediction of workloads.

In summary, short-term workloads are challenging to predict. If the data centre is running applications with very dynamic hardware resource requests, the prediction may become inaccu-

rate. As the input of the allocation, large prediction errors may mislead the following steps of resource management.

#### 2.2.2 Allocation

After predicting the workloads, algorithms are required to allocate resources to the incoming applications. Allocation algorithms are responsible for placing VMs into servers with efficient resource utilisation (minimum active physical machines and maximum resource utilisation on each server).

The placement of VMs is abstracted into a bin-pack problem in [21] [22] as follows:

- Givens: (1) An N number of VMs and the resource demand of each VM. (2) The resource capacity of each server.

- Obtain: The location of each VM.

- Objective: Reduce the number of active servers.

- Constraints: (1) Each VM is placed on only one server. (2) the utilization does not exceed the capacity of all servers

Many algorithms exist to solve the bin-packing problem such as Best Fit, First Fit, etc. But the results of the model heavily depend on the preciseness of the prediction, as any random events are not taken into account. To solve this problem, Jin et al. [23] classify the resource demands by VMs into static and dynamic parts. The static demands are treated as a constant value, while the dynamic demands are formulated as a random number of normal distributions. Moreover, an additional constraint is added to the aforementioned bin-packing problem: for each VM resource demand, the under-provision probability should be less than a threshold.

Considering the placement of VMs as a bin-packing problem results in the relocation of all the VMs. Consequently, the migration of VMs takes a very long time because most VMs need to be migrated in every time slot. Therefore, in order to reduce the number of instances of migration, some research suggests a method that can be applied in real time. Most real-time algorithms try to rearrange VMs from high-load servers to low load servers one-by-one. The low-load servers are ordered based on a specific standard. The movement of VMs is performed starting from the lowest load server on the list, and it continues until the list of high-load servers is exhausted [24]. This method, however, needs to traverse all type of resources on every server to find a suitable low-load server, which takes a long time. Therefore, the load of the server is abstracted into a load indicator function to enable these algorithms in real-time allocation. However, it is hard to come up with an accurate function to indicate the thorough load of a server.

In summary, because of the heterogeneous servers and the resource demands of VMs, the allocation algorithms often need to compare between huge tables with multiple columns. As it often takes a long time to finish the comparison, having accurate allocation algorithms in real time becomes difficult. Most allocation algorithms assume that it is impossible to divide a VM into multiple parts and locate them on different servers. That is the main reason why they try to compare the VM resource demand tables and server resource capacity tables to find a suitable placement of VMs. As a result, investigating how to enable distributed VM leads to the concept of resource disaggregation. The technology of resource disaggregation makes the distribution of VM possible and helps create faster VM allocations.

#### 2.2.3 Migration

After allocation algorithms, the data centre should be able to evolve into a better optimised state. Instead of fixing VMs on the server where they were created, VM migration enables the movement of VMs from one server to another based on the allocation result.

The general idea of VM migration is to copy memory from the source server to the destination server and keep the function of the VM running as smoothly as possible. For example, while the memory is moving, the performance of the VMs should not be affected and there should be less downtime. It needs to be pointed out that, if the VM keeps functioning during the migration to reduce migration downtime, there will be differences between the source memory and the copied memory, as the source memory might be updated when the copied memory data is moving. These differences between source and destination should be handled while VM migration is going on. During the migration process, the original memory data is copied first to the destination server. Then the newly-dirtied data is iteratively transferred to the destination. When the iteration reaches a specific threshold, the source VM will be stopped. The remaining dirtied data will then be packed and transferred to the destination server together. Finally, the VM in the destination server will be activated.

Many technologies are adopted to accelerate the VM migration. For example, to reduce the network traffic, some research suggests compressing data in the memory before the transmission, as the memory pages have strong regularity [25]. These methods need to make a trade-off between computing performance and migration performance, as compression needs additional computing. High-speed connection technologies can also accelerate the VM migration by providing a dedicated bandwidth and specific remote direct memory access functions.

VM migration and technologies associated with it explore the handling of memories on a remote server. These technologies not only enhance the resource virtualisation by accelerating the migration process but also enlighten the concept of resource disaggregation. Instead of accessing remote memory for a short time during the iteration of transferring dirty memory data in the migration, it is also possible to keep accessing remote memory during a VM's lifespan. However, this approach has stronger requirements on the performance of the network.

#### 2.2.4 Summary

Virtualisation technology is reviewed in this section. Virtualisation can be divided into three steps: workload prediction, resource allocation, and VM migration. It is difficult to predict the short-term workload of data centres with dynamic applications. As it is unable to distribute a single VM on multiple servers, the allocation algorithms need to handle huge tables that record different types of available server resources to find a suitable place for a VM. The VM migration technology explores methods that handle remote memories which become key enablers of resource disaggregation.

# 2.3 Resource disaggregation

To better utilise data centre resources, the concept of resource disaggregation is proposed. Instead of tightly binding all types of resources (processors, memories, etc.) on a single board, resource disaggregation tries to connect computing resources located on separated boards into a system. Ideally, as the location of the resources (local or remote) does not affect the performance of the resulting system, it would be able to equip a board with a unique type of resource. This feature can potentially contribute to the operation and upgrading of data centres, as different types of resource are managed and scaled independently. However, as it is impossible to avoid the overhead introduced by the interconnect system, performance penalty of resource disaggregation becomes a fact of life. As a result, combining distributed resources into a system at a low performance cost becomes the key question in resource disaggregation.

#### 2.3.1 Software support

To demonstrate the concept of resource disaggregation, a software solution of the resource disaggregation is suggested as an initial step. Regardless of performance, with the software solution, executing an application on disaggregated resources is possible.

Software systems for memory disaggregation are first implemented. Lim et al. [10] implement a software prototype with a processor and a remote memory blade linked by PCIe. Instead of a point-to-point system, a PCIe switch is adopted in [10] to extend the prototype into a manyto-many system. Apart from PCIe, the FaRM [26] presents a scalable system where servers are interconnected by RDMA over Converged Ethernet (RoCE) [27]. Then, a complete OS level solution [28] is proposed as a further step to resource disaggregation.

The software solution aims to provide an efficient system to manage local and remote memory. It enables the cloud application developer to design and run their program on a resourcedisaggregated environment. However, due to the overhead from the interconnect, applications that run in the resource-disaggregated environment suffer poor performance, while software solutions contribute little to performance improvement [29].

### 2.3.2 Hardware support

As the main overhead cost comes from the interconnected system, a data centre network becomes the key element to reduce the performance penalty from resource disaggregation. As the traffic previously existing within a server is moved to the external network, bandwidth and latency become a key requirement in resource disaggregation [30]. Since various additional protocols such as RDMA are often introduced to support disaggregation, the flexibility of a network is also another important element.

Optical networks have become a promising solution to address the challenges in resource disaggregation due to their high network capacity and low energy consumption [31]. Advanced photonic technologies also enable switching at the optical domain, which eliminates the latency and energy introduced by electrical switches [32]. However, the advanced photonic technologies often need specialised optical interfaces. These optical interfaces may introduce challenges in the board design of the servers as they often require additional power and footprint. Therefore, to be compatible with the advanced optical network, Chapter 2 proposes new network interfaces that consider bandwidth density and footprint size.

Due to the non-availability of an optical buffer solution, the packet-level processing of a data centre network is based on electronic devices. Recent research on packet-level network processing focuses on increasing the flexibility of the network to make it easier to manage, upgrade, and evolve. As a consequence, a software-defined network (SDN) is proposed [33].

The SDN tries to decouple the control and data plane of the network. The infrastructure of SDN is shown in figure, there are two elements, the controllers and the data plane devices. The data plane devices is a hardware or software element specialized for traffic forwarding, while the controller is a software element executed by a commodity hardware platform. A SDN device is based on a pipelined of flow forwarding tables with the following entries: a) a matching rule; b) actions to be executed after packet matching and c) counters that record statistics of packet matching. In the SDN devices, a path through a sequence of flow tables defines how packets should be processed. The possible actions performed on packets includes: 1) forward the packet to output ports; 2) forward the packet to the controller; 3) drop the packet and 4) forward the packet to a specific flow table.

FIGURE 2.3. The overall concept of software-defined network. [33]

The control and management on the distributed data plane of network is centralized in the SDN. Although the SDN suggests a software control plane only, the software data plane is also implemented as a complement to the SDN concept. In data centres, software network switches are often adopted to forward data between virtual machines in the same sever.

Theses software applications on network control and data plane implicates the concept of network function virtualization (NFV). In the NFV, network functions are treated as software applications that run in the operating system. So virtualization technology can be applied to virtualize the network resource. The NFV inherited many advantages from SDN. For example, network services can be deployed easily in NFV. The NFV also has its own advantages such as sharing physical network resources to multiple tenants of data centres.

Although running software network applications increases the flexibility of a network, general purpose processors may limit the performance of these network functions especially on the data plane. An FPGA, as a reconfigurable device, becomes an outstanding hardware platform to keep both the flexibility and performance. In Chapter 4, a virtualise system is implemented on the FPGA platform to deliver a flexible high-performance network function.

### 2.3.3 The dRedBox

The dRedBox research project is one of the ongoing research projects which investigates resource disaggregation [34]. It aims to deliver a customisable data centre architecture by introducing

advanced technologies in optical networks to eliminate the effect from the boundaries of the server board.

The architecture of the resource disaggregation architecture in dRedBox is shown in figure 2.4 [35]. The disaggregated racks (dRack) contain many disaggregated boxes (dBoxes). Each dBox includes a set of pluggable disaggregated bricks (dBrick) equipped with a specific computing resource. Each dBrick can support unique types of resources such as general purpose processors, memories, or accelerators of a specific application. All dBricks are able to have a direct connection to other dBricks through electronic or optical switches. The optical circuit switches mainly connect dBricks located on different dBoxes, while the electronic crossbar switch is responsible for the connection between dBricks on the same dBox.

Apart from the main computing resource, as the glue logic between dBricks and dBoxes, each dBrick is also equipped with a reconfigurable system to deliver on-demand high-performance network functions such as network interfacing and network switching. For example, the reconfigurable system needs to provide RDMA protocols when it is interfacing processors with memories and IP protocols when interfacing processors with end users. In Chapter 3, a reconfigurable system to deliver on-demand network functions is implemented and will be adopted as the glue logic between the dBrick and dBoxes.

Each dBrick is also equipped with an onboard optical transceiver. To minimise the footprint size and power consumption while increasing bandwidth, an optical transceiver based on advanced silicon photonic technology is tested in Chapter 2. The adopted optical transceivers and the optical switches enable a scalable, transparent dBrick-to-dBrick interconnect system with ultra-low latency and high bandwidth.

#### 2.3.4 Summary

The data centre resource disaggregation is reviewed in this section. Software solutions are first proposed to enable the concept of resource disaggregation. They mainly focus on the management of the data in remote memory. Most software solutions have a strong requirement on the network. Therefore, a high-performance data centre network is established by introducing advanced interconnect technologies. To increase bandwidth, the optical network is introduced. The SDN

FIGURE 2.4. The structure of the dRedBox data centre resource disaggregation system.[35]

and NFV are also introduced to increase the flexibility of the network.

## 2.4 Management of FPGA resources

The FPGA devices have been adopted in data centres as reconfigurable resources. Due to their extreme customisation feature, FPGA devices are widely adopted to support high-performance applications that need non-recurring hardware accelerators. Two types of usage of FPGA resources can be observed in the data centre. Firstly, the FPGA performs as a kind of equipment to enable data centre such as network switches or accelerators of specific processes. The second is as a kind of general computing resource which should be delivered to end users directly.

Similar to the memory, the management of FPGA resources is also based on virtualisation and disaggregation. FPGA resources should be isolated and shared properly in virtualisation, while it should be able to combine distributed FPGA resources to compose an on-demand system in disaggregation. Unlike the memory, however, functions deployed on the FPGA resources are sensitive to their physical location. In other words, inappropriate places and routes may result in failed timing in the FPGA while the location of the program in the memory does not make any difference.

Therefore, additional architecture is required to reduce the effect of the location when managing FPGA resources. In this section, architectures or systems of virtualisation and disaggregate FPGA resources are reviewed.

### 2.4.1 Virtualisation of FPGA resources

FPGA resources should be isolated and shared by multiple tenants in virtualisation. Partial reconfiguration becomes a key enabler of virtualisation of FPGA resources, as it is able to configure a part of the FPGA while it keeps the rest working [36].

The initial effort for partial reconfiguration is reported in [37]. It tries to modify the bit width of multipliers. Because there are overlap in the logic used by several version of multipliers, researches tries to propose methods to only configure the non-overlapping part of the design to reduce the reconfiguration time. Although tools are developed to identify the overlap parts of the circuit and set the reconfiguration parts automatically [38], companies finally develop tools to make FPGA designers to predefine reconfiguration circuits manually. Also the interface between static and dynamic regions should be predefined and is not reconfigurable at run time because it is made through fixed-location LUT.

Apart from hardware implementation, swapping circuits at run time requires software management. This software needs to consider the size of the reconfigurable region, the performance improvement and the overhead to perform the reconfiguration [39]. The sequence of reconfiguration can also be optimized to reduce the overall application latency. The operating system level design to support for placing portions of an application in FPGA then appeared [40]. The FPGA is treated as a co-processor and its reconfiguration are scheduled as software threads of execution [41].

A number of cloud applications has shown benefits of using partial reconfiguration. For example, [42] shows using partial reconfiguration to update the sorting algorithm for large data sets can accelerate the overall data sorting. The partial reconfiguration also helps to develop network applications for protocol and packet filtering modules in network virtualization [43]. It is also used to accelerate SQL database query operations in [44] and FPGA can be reconfigured in milliseconds to enhance performance.

With partial reconfiguration technology, it would be able to partition FPGA resources into many regions and change the function of each region based on requests from users. However, there are two limitations in the partial reconfiguration technology that need to be considered in the virtualisation architecture. First, instead of allocating in runtime, reconfigurable regions should be pre-set in the design's early stages. Secondly, whatever functions are plugged in, the interface (the number and direction of pins) of reconfigurable regions must not change.

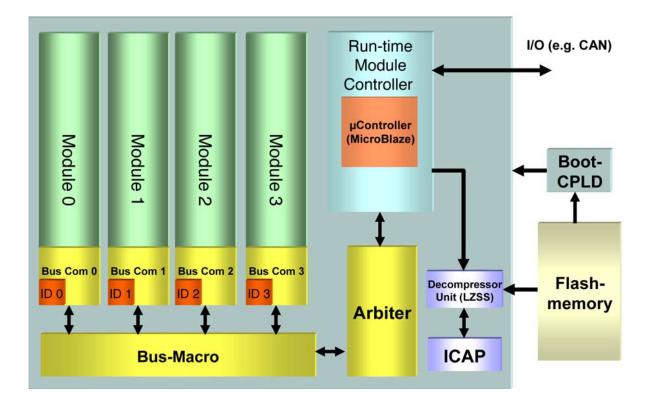

The basic architecture to virtualise the FPGA resources is suggested in [45] as shown in Figure 2.5. The run-time module controller acts as the orchestrator of the complete system. The bus is connected with the controller through the arbiter. The arbiter is responsible for controlling the data flow. Functional modules can share data with each other through the bus. A standard interface module named Bus Com is proposed to ensure that every partial reconfigurable module has a uniform interface towards the static region. The partial reconfiguration is performed in the internal configuration access port (ICAP) on the lower-right side of Figure 2.5. The compressed partial bit stream is loaded from the flash memory and pushed to the ICAP after decompression.

By using partial reconfiguration, FPGA resources are partitioned into several regions, and each of the regions can perform different functions independently without affecting another. In addition, a bus structure is applied to enable data transfer between reconfigurable and static regions. The bus structure defines a uniform interface for the reconfigurable regions. Additionally, it also shares resources in the static region such as controllers and I/Os to all reconfigurable regions.

This architecture was originally adopted in an automotive system to deliver functions such as cabin control and rear-view mirror control. The system includes four reconfigurable regions, and the bus is designed for acknowledgement instead of data movement. As it suggests a dynamic architecture that can deliver on-demand FPGA functions, this architecture has been utilised in many fields which need a reconfigurable high-performance system. The basic architecture has been modified as well according to the feature of different applications. For example, this

FIGURE 2.5. The basic architecture of the system suggested in [45].

architecture is adopted for video processing in [46]. Two processors are included in the system. One of them is for control of the reconfigurable system, while another one is for the software support of video processing. A memory-mapped bus is also used for data movements between plugged-in modules.

Apart from video processing, the architecture in Figure 2.5 is also used in the processing of network traffic. Because of its stream processing feature, this architecture is able to deliver a high bandwidth and dynamic data plane in recent flexible network architecture technologies [47]. For example, [47] attaches the network interface to the interconnect system and implements partially reconfigurable hardware routers. A bus that supports a 1-Gbps throughput is implemented. Software routers are also deployed in the processor to run as a complementary system during the partial reconfiguration.

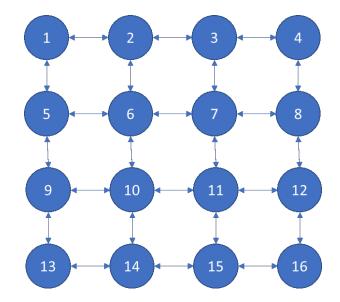

Much research has been done to enhance the architecture in Figure 2.5 while applying it in different domains. A network-on-chip system is deployed in [48]. As the timing requirement between reconfigurable regions is released, the network-on-chip helps support more reconfigurable regions and finer-grained partition on the FPGA resources. [49] also suggests allocation algorithms that properly place the reconfigurable regions. The algorithm is able to automatically determine a suitable size and location for each region, and timing constraints in the interconnect system are also considered. [50] and [51] also propose algorithms in the control system that schedule the reconfigurable function in real-time. As these schedule algorithms avoid manually downloading partial bitstreams, they further virtualise the FPGA resources in a time-sharing way.

FIGURE 2.6. The design principle of the virtualisation system of FPGA resources summarised in [52].

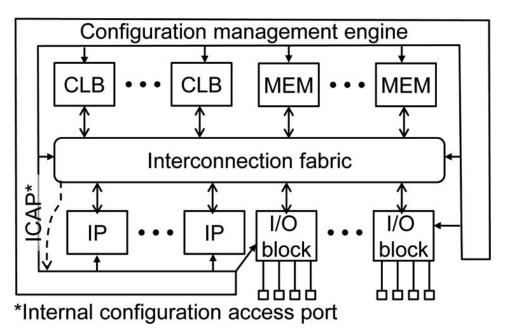

Although the basic architecture becomes complicated after contributions from many functional domains, [52] has summarised the generic design principle of the reconfigurable architecture. As shown in Figure 2.6, three elements should be included:

• Functional blocks

These functional blocks are able to partition the FPGA resource according to the deployed functions. These functions and their associated FPGA resources should be shared with users after virtualisation.

• Configurable interconnection

The interconnect system shares data between functional blocks and the external world. It shares routing resources to multiple functional block connections. Shared data is registered and arbitrated in the interconnect system to ease the timing requirement. Therefore, it can reduce the location effects of the functional blocks.

Configuration Management Engine

This engine orchestrates the complete system. It updates the port-map of the interconnection and triggers the reconfiguration of functional blocks. It also interfaces the entire FPGA system to the software part.

FPGA resources can be virtualised by following these elements, as they can be managed in a way similar to virtual memory [53]. Based on these principles, a system that virtualises FPGA resources is established and introduced in Chapter 4. In addition, network stream processing functions can be deployed on the virtualised FPGA platform to demonstrate advanced network technologies such as network function virtualisation.

### 2.4.2 Disaggregation of FPGA resources

When cloud applications are disaggregated and deployed on distributed resources, a virtual platform that combines multiple resources is often delivered. This section reviews research and technologies that combine distributed FPGA resources into a single virtual joint platform.

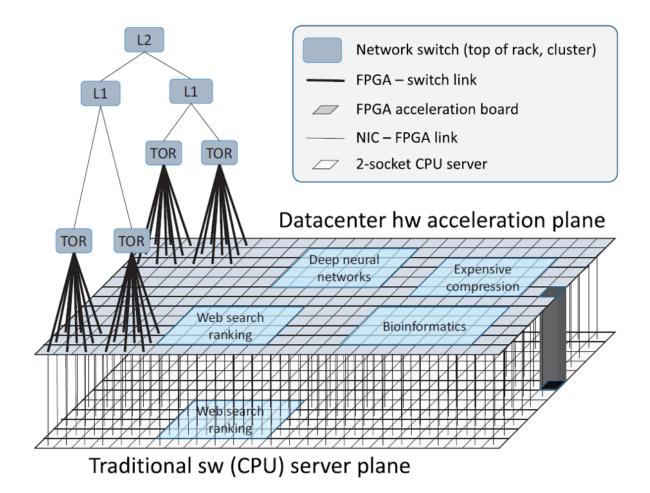

In [54] and [55], an architecture that attempts to integrate distributed FPGA resources is proposed to support the Bing web search engine. As shown in Figure 2.7, there are two planes in the architecture: a CPU server plane and a hardware acceleration plane. Links between the two planes are enabled by both a Gen3 PCIe interface and a 40-Gbps Ethernet connection. Internal Ethernet links also exist inside each plane. Cloud applications can be distributed on both planes (web search ranking in Figure 2.7). They can also be found on a single plane but with multiple boards (others in the Figure 2.7). This section classifies research in combining FPGA resources based on two types of systems: a)systems that combine FPGA resources through processors. b)systems that combine FPGA resources directly through networks.

FIGURE 2.7. The disaggregation system for FPGA devices suggested in [55].

In systems that combine FPGA resources through processors, FPGA resources act as complementary accelerators that are attached to general purpose processors. The hardware support of this kind of system is based on the system-on-chip technology or PCIe interfaces. The Xilinx SoC adopts memory-mapped AXI interface for communication between a processing system and programmable logic. The PCIe interfaces are also memory-mapped systems. Therefore, from the perspective of a processing unit, programmable logic can be accessed as a piece of memory.

Consequently, the software support offered by the resource disaggregation through processors tries to apply traditional methods to efficiently manage memories. In [56], the FPGA resources are integrated with the Openstack. The system is mainly designed for stream processing. The data communication between processors and each reconfigurable regions is enabled by a standard memory-mapped interface. A basic library to access control registers or to move memory data in the reconfigurable regions is developed. The Openstack is also adopted in the IBM FPGA cloud system [57]. In addition, IBM developed a hardware scheduler system to reconfigure the FPGA inside the Openstack scheduler. Other than Openstack, a management system designed specifically for FPGA resources called RC3E is proposed in [58]. Functions in the centralised hypervisor system such as job scheduler, compute nodes manager, and user interfaces are developed. The cloud-wide FPGA design that includes HLS is also introduced in RC3E [59].

As the FPGA is considered as an accelerator beside general purpose processors, FPGA resources are accessed in a memory-mapped way in the disaggregation system that combines resource through processors. Mechanisms and architecture in standard data centre resource management solutions can still be utilised by changing the interface from DDR or SATA to PCIe or AXI. However, high-bandwidth heterogeneous parallel processing is one of the features of FPGA resources that stands out the most. In the system combine resources through processors, data moving between FPGA resources have to go through memory-mapped interfaces (between processor and FPGA), which extremely limits the performance of the final combined FPGA systems. Therefore, disaggregation solutions that combine FPGA resources directly through networks are also required.

In systems that combine FPGA resources directly through networks, similar to the disaggregation of memory, the optical network is also adopted. For example, in the Bing search engine, a 40-Gbps QSFP interface is established to enable direct communications with other FPGAs [60]. A lightweight transport layer network processor is also developed. It reduces the latency by eliminating the packet reorder features in a standard TCP/IP network. Another attempt comes from IBM [61]. Standard layer 2 and layer 3 protocols are implemented. Furthermore, memory that is attached to the FPGA is also partitioned and allocated to each reconfigurable region by introducing a hardware memory manager [62]. In addition to the development of a fundamental structure on a single FPGA, [63] tries to establish a global management system that combines multiple FPGA devices by introducing the service chains concept from network function virtualisation. It aims to deploy pipelined functions for stream processing (instead of memory-mapped processing). Technologies in programmable networks such as OpenFlow are utilised to guide data streams to on-demand FPGAs in a specific order.

The FPGA, as a flexible resource, needs runtime configuration. The configuration (update control registers or download bitstream) on multiple FPGA devices is performed through vertical systems in most research. For example, in the BORPH [64] system, the configuration of a control register is triggered by a central controller and through an on-board bus. The BORPH is designed for configuration on multiple FPGA devices but within the board [65]. The network-wide configuration is often integrated with existing data centre management systems that are triggered by a central orchestrator as reviewed in the vertical FPGA resource disaggregation system. During the configuration, as the FPGA blocks that will be updated cannot function, the data flow should be buffered. As a result, the process on data flow between FPGA resources involves waiting - from sending a configuration request to receiving a configuration success response which can last for at least several microseconds. To reduce the configuration time on multiple FPGA resources, this thesis introduces a new configuration method in Chapter 5. The configuration is triggered by network packets through a horizontal resource disaggregation system instead of a vertical system.

## 2.5 Summary

This chapter has reviewed the research and technologies involving managing data centre resources. Data centre resource management can be classified into two categories (virtualisation and disaggregation) based on the purpose. Virtualisation aims at properly partitioning a single physical platform into multiple virtual environments, while disaggregation attempts to combine distributed resources into a complete system.

The development from virtualisation to disaggregation is then reviewed. In the virtualisation of data centre resources, there are three steps: prediction, allocation, and migration. It is difficult to predict short-term resource utilisation in most algorithms. This inaccuracy may affect the result of the following steps, especially when the resource requirements of cloud applications are highly dynamic. In the allocation, most algorithms assume that only local memory is accessible. Therefore, they try to find out an optimised virtual machine placement that balances the utilisation of all types of computing resources (CPU clock cycles or memory) on each server. After the initial allocation, the process of migration is performed in the runtime of applications. During the migration process, researchers try to synchronise the memory of the source and destination servers for a certain period. This process hints at the key technology of memory disaggregation (accessing the remote memory). To support memory disaggregation, software solutions are first suggested. However, researchers find that a high-bandwidth low-latency connection is required to make the remote storage act like a piece of memory. Therefore, an optical networks is suggested as it is able to provide direct point-to-point low-latency connections. The bandwidth of an optical network depends on the integration of optical transceivers, where the footprint and power consumption of the optical transceivers should be taken into consideration. Therefore, Chapter 3 establishes a network interface where high-bandwidth optical transceivers are integrated with small footprint and power consumption.

The virtualisation and disaggregation of FPGA resources were introduced in Section 2.4. The virtualisation of FPGA resources can be based on the architecture that is shown in Figure 2.5. It can be summarised as a set of functional blocks that are linked by a configurable interconnect system. Based on this design principle, this thesis establishes a virtualisation system of FPGA resources which will be introduced in Chapter 4. The disaggregation of FPGA resources is then reviewed. It can be classified into vertical and horizontal systems. Vertical systems aim to develop a centralised resource manager that abstracts and simplifies the configuration (including updated registers and download bitstreams). The horizontal system attempts to develop boundless links between each FPGA device. In Chapter 5, in lieu of vertical configuration, a network protocol and associated processor that delivers horizontal configuration with a low downtime is developed.

## HIGH PERFORMANCE NETWORK INTERFACE FOR RESOURCE DISAGGREGATION

## 3.1 Introduction

In response to the growing data centre workload, in addition to buying more racks and servers, improving the data centre architecture is also suggested. For example, instead of CPU-centric architecture, the Hewlett Packard company suggests server racks with massive stores of dense, energy-efficient memory which are dedicated to providing storage services. To efficiently make use of data centre resources, resource disaggregation is also suggested in the dRedBox project [66].

The greatest burden of the scale-up of data centres falls on the network. Current data centres may consist of hundreds of thousands of servers arranged in a hierarchical tree-based structure [67]. All servers should be able to communicate with others through high-performance connections. Recent research findings suggest that over 70% of data exchange traffic remains within the data centre for intra-data centre communications [68].

Furthermore, new data centre architectures also have a strong requirement with the network. As [69] suggests, servers with high-density computing resource occupy more capacity in the data centre network. A high-performance network also acts as a key enabler of data centre resource

# CHAPTER 3. HIGH PERFORMANCE NETWORK INTERFACE FOR RESOURCE DISAGGREGATION

disaggregation, as communication that was previously contained within a server is now provided by the external network [70].

Optical networks have a high potential to meet the requirements of recent large-scale data centres or new data centre architectures. Although fibre consumes much less energy than copper cable, high-bandwidth optical transceivers remain power-hungry modules on the server [32]. Current commercial off-the-shelf servers only include one or two SFP+ cages for a 10-Gbps interface. However, advanced data centre architecture requires a more powerful interface to establish high-bandwidth and low-latency connections between a large number of endpoints to support newer data centre architecture.

Optical transceivers with advanced photonic technologies have been invented to support highcapacity networks, efficient energy consumption, and coordination with fast electronic devices. In this chapter, a prototype network interface is developed to support data centre resource disaggregation. The contribution of this chapter is outlined as follows:

- Under the new network interface, recent optical transceivers based on silicon photonic technology are combined with FPGA devices.

- Related equipment, experiment, and skills which are used to combine the optical transceiver with the FPGA are introduced.

- By connecting the new implemented network interface with the optical switch, the prototype of a pure optical data center network is established.

- Based on the prototype of the pure optical network, the feasibility of data centre resource disaggregation is also evaluated.

The rest of this chapter is organized as follows. Section 3.2 introduces the motivation for using advanced optical transceivers in the developed network interface. Section 3.3 introduces the experiment to combine the transceiver with the FPGA and build the network interface. Section 3.3 introduces the experiment set-up. Section 3.4 presents the result of the experiment and analyses the feasibility of resource disaggregation. Section 3.6 provides a conclusion for this chapter.

## 3.2 Motivation

Two elements of optical transceivers can physically limit the bandwidth of a server's network interface: energy consumption and footprint dimension.

The data centre needs a large amount of power to function. Google reports that they continuously draw 260 megawatts of power to run their data centres [71]. Energy efficiency becomes a significant parameter of a data centre due to its economic and performance impact. Power bills become the most important expense of a data centre. On the other hand, techniques that reduce electricity usage of data centres also tend to reduce performance. As such, it points to a complex trade-off between energy consumption and performance. More optical transceivers are often included in the servers to support higher bandwidths. However, more optical transceivers integrated into the servers increase the servers' energy consumption.

Another restriction of optical transceivers involves the dimension of the footprint. Recent silicon fabrication with nanometre-scale accuracy has the ability to integrate large amounts of computing resources into the server. An increasing number of optical transceivers are necessary to support high bandwidth inter-server communication between these resources. The footprint dimension of the transceiver becomes important in order to include high-density optical transceivers on the server board.