# Switched-Capacitor RF Receivers for High Interferer Tolerance

### Yang Xu

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

2018

©2017

Yang Xu

All Rights Reserved

### **Abstract**

# Switched-Capacitor RF Receivers for High Interferer Tolerance

### Yang Xu

The demand for broadband wireless communication is growing rapidly, requiring more spectrum resources. However, spectrum usage is inefficient today because different frequency bands are allocated for different communication standards and most of the bands are not highly occupied.

Cognitive radio systems with dynamic spectrum access improve spectrum efficiency, but they require wideband tunable receiver hardware. In such a system, a preselect filter is required for the RF receiver front end, because an out-of-band (OB) interferer can block the front end or cause distortion, desensitizing the receiver. In a conventional solution, off-chip passive filters, such as surface-acoustic-wave (SAW) filters, are used to reject the OB interferer. However, such passive filters are hardly tunable, have large area, and are very expensive. On-chip, high-selectivity, linearly tunable RF filters are, therefore, a hot topic in RF front-end research. Switched-capacitor (SC) RF filters, such as N-path filters, feature good linearity and tunability, making them good candidates for tunable RF filters. However, N-path filters have some drawbacks: notably, a poor harmonic response and limited close-by blocker tolerance.

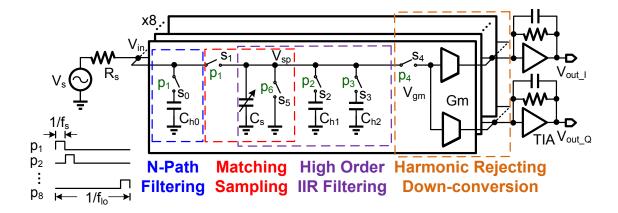

This thesis presents the design and implementation of several interferer-tolerant receivers based

on SC technology. We present an RF receiver with a harmonic-rejecting N-path filter to improve the harmonic response of the N-path bandpass filter. It features tunable narrowband filtering and high attenuation of the third- and fifth-order LO harmonics at the LNA output, which improves the blocker tolerance at LO harmonics. The 0.2–1 GHz RF receiver is implemented in a 65 nm CMOS process. The blocker 1 dB compression point (B1dB) is  $-2.4\,\mathrm{dBm}$  at a 20 MHz offset, and remains high at the third- and fifth-order LO harmonics. The LNA's reverse isolation helps keep the LO emission below  $-90\,\mathrm{dBm}$ . A two-stage harmonic-rejection approach offers a  $> 51\,\mathrm{dB}$  harmonic-rejection ratio at the third- and fifth-order LO harmonics without calibration.

To improve tolerance for close-by blockers, we further present an SC RF receiver achieving high-order, tunable, highly linear RF filtering. We implement RF input impedance matching, N-path filtering, high-order discrete-time infinite-impulse response (IIR) filtering and down-conversion using only switches and capacitors in a 0.1–0.7 GHz prototype with tunable center frequency, programmable filter order, and very high tolerance for OB blockers. The 40 nm CMOS receiver consumes 38.5–76.5 mA, achieves 40 dB gain, 24 dBm OB IIP3, 14.7 dBm B1dB for a 30 MHz blocker offset, 6.8–9.7 dB noise figure, and > 66 dB calibrated harmonic rejection ratio.

The key drawback of our earlier SC receiver is the relatively high theoretical lower limit of the noise figure. To improve the noise performance, we developed a 0.1–0.6 GHz chopping SC RF receiver with an integrated blocker detector. We achieve RF impedance matching, high-order OB interferer filtering, and flicker-noise chopping with passive SC circuits only. The 34–80 mW 65 nm receiver achieves 35 dB gain, 4.6–9 dB NF, 31 dBm OB-IIP3, and 15 dBm B1dB. The 0.2 mW

integrated blocker detector detects large OB blockers with only a  $1\,\mu s$  response time. The filter order can be adapted to blocker power with the blocker detector.

# **Contents**

| L  | St 01 1 | rigules                                                         | ,   |

|----|---------|-----------------------------------------------------------------|-----|

| Li | st of T | <b>Fables</b>                                                   | xiv |

| 1  | Intr    | oduction                                                        | 1   |

|    | 1.1     | Evolution of Wireless Communications                            | 1   |

|    | 1.2     | Evolution of CMOS RF Receiver Front Ends                        | ۷   |

|    | 1.3     | Motivation                                                      | Ć   |

|    | 1.4     | Organization of the Thesis                                      | 8   |

| 2  | Revi    | iew of Switched-Capacitor Techniques for RF Receiver Design     | 10  |

|    | 2.1     | Active DT Filters                                               | 11  |

|    | 2.2     | Passive DT Filters                                              | 13  |

|    | 2.3     | RF N-Path Filters                                               | 15  |

|    | 2.4     | Thesis Overview                                                 | 16  |

| 3  | Bloc    | eker-Tolerant Receiver with Harmonic-Rejecting N-Path Filtering | 18  |

|   | 3.1  | Introdu | action                                                               | 18 |

|---|------|---------|----------------------------------------------------------------------|----|

|   | 3.2  | Harmo   | onic-rejecting N-path filter                                         | 20 |

|   |      | 3.2.1   | Harmonic response, harmonic folding, and harmonic down-conversion in |    |

|   |      |         | a differential N-path filter                                         | 22 |

|   |      | 3.2.2   | Analysis of the harmonic-rejecting N-path filter                     | 24 |

|   |      | 3.2.3   | Second-order effects                                                 | 29 |

|   | 3.3  | RF rec  | eiver with harmonic rejecting N-path filter                          | 32 |

|   |      | 3.3.1   | RF front-end architecture                                            | 32 |

|   |      | 3.3.2   | Circuit implementation                                               | 33 |

|   |      | 3.3.3   | Improvement of out-of-band linearity                                 | 35 |

|   |      | 3.3.4   | Noise analysis                                                       | 36 |

|   | 3.4  | Experi  | mental Results and Comparison                                        | 40 |

|   | 3.5  | Conclu  | isions                                                               | 47 |

| 4 | Swit | tched-C | apacitor RF Receiver with Programmable High-Order Filtering          | 48 |

|   | 4.1  | Introdu | action                                                               | 48 |

|   | 4.2  | Switch  | ned-Capacitor RF Front End Concept and Analysis                      | 51 |

|   |      | 4.2.1   | Basic Concept                                                        | 51 |

|   |      | 4.2.2   | Core Switched-Capacitor RF Front End without Filtering               | 53 |

|   |      | 4.2.3   | Programmable High-Order DT IIR Filter                                | 61 |

|   |      | 4.2.4   | Noise Analysis                                                       | 63 |

|   |      | 4.2.5   | Out-of-Band Blocker Linearity Analysis                               | 68 |

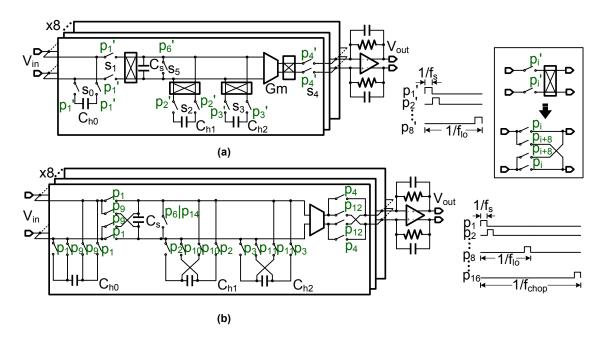

|   |     | 4.2.6    | Switched-Capacitor Front End with N-path filter                        | 70  |

|---|-----|----------|------------------------------------------------------------------------|-----|

|   | 4.3 | Impler   | mentation of the RF Front End                                          | 71  |

|   | 4.4 | Measu    | rement Results                                                         | 76  |

|   | 4.5 | Conclu   | asions                                                                 | 85  |

|   | 4.6 | Appen    | dix                                                                    | 85  |

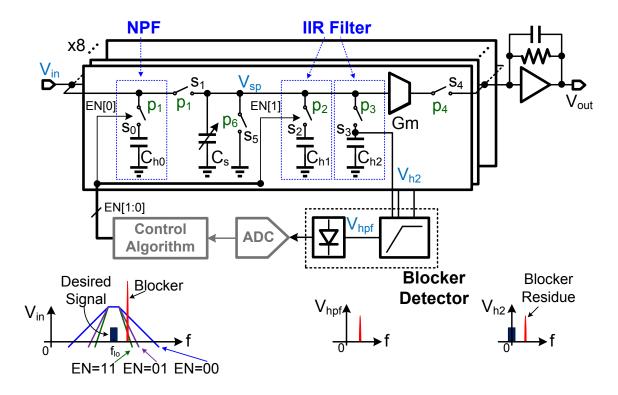

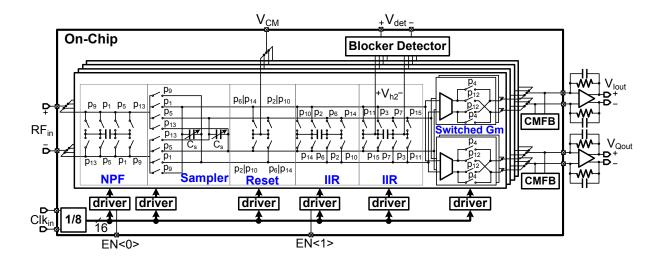

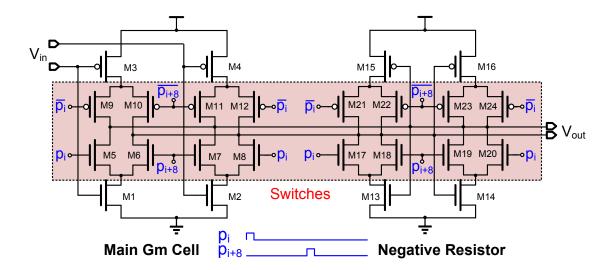

| 5 | Cho | pping S  | witched-Capacitor Receiver with Integrated Blocker Detection           | 88  |

|   | 5.1 | Introd   | action                                                                 | 88  |

|   | 5.2 | Chopp    | ing Switched-Capacitor RF Receiver Design                              | 89  |

|   |     | 5.2.1    | Switched-Capacitor Receiver                                            | 90  |

|   |     | 5.2.2    | Improving Noise Performance of the Passive Switched-Capacitor RF Front |     |

|   |     |          | End                                                                    | 91  |

|   |     | 5.2.3    | The Chopping Switched-Capacitor RF Receiver Architecture               | 94  |

|   | 5.3 | Progra   | mmable Blocker Filtering and Blocker Detection                         | 97  |

|   | 5.4 | RF Re    | ceiver Circuit Implementation                                          | 99  |

|   |     | 5.4.1    | RF Receiver Circuit Architecture                                       | 99  |

|   |     | 5.4.2    | Baseband Circuit                                                       | 102 |

|   |     | 5.4.3    | Blocker detection circuit                                              | 104 |

|   | 5.5 | Measu    | rement Results                                                         | 105 |

|   | 5.6 | Conclu   | asions                                                                 | 114 |

| 6 | Ana | lysis of | Passive Gain Techniques for Switched-Capacitor Receivers               | 115 |

| Bil | bliogr | aphy     |                                                     | 133   |

|-----|--------|----------|-----------------------------------------------------|-------|

| 7   | Con    | clusions | 5                                                   | 128   |

|     | 6.5    | Conclu   | isions                                              | . 127 |

|     | 6.4    | Simula   | ation Results                                       | . 126 |

|     |        | 6.3.2    | Sampling Capacitor Linearization                    | . 123 |

|     |        | 6.3.1    | Noise Analysis                                      | . 123 |

|     | 6.3    | Switch   | ed-Capacitor Receiver with Parametric Amplification | . 120 |

|     |        | 6.2.3    | Simulation Results                                  | . 120 |

|     |        | 6.2.2    | Noise Limitation                                    | . 117 |

|     |        | 6.2.1    | Capacitor-Stacking Concept                          | . 116 |

|     | 6.2    | Capaci   | tor-Stacking Switched-Capacitor Receiver            | . 116 |

|     | 6.1    | Introdu  | action                                              | . 115 |

# **List of Figures**

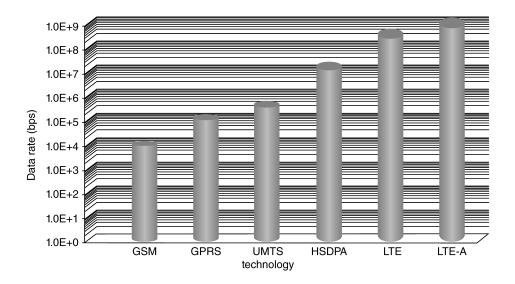

| 1.1 | Data rates of cellular communications [1]                                           | 2  |

|-----|-------------------------------------------------------------------------------------|----|

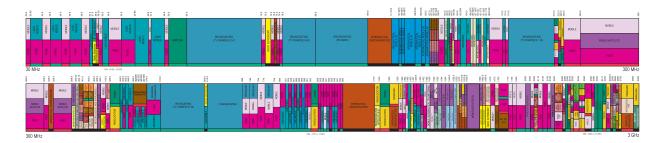

| 1.2 | United States frequency allocation chart (30 MHz–3 GHz) [2]                         | 2  |

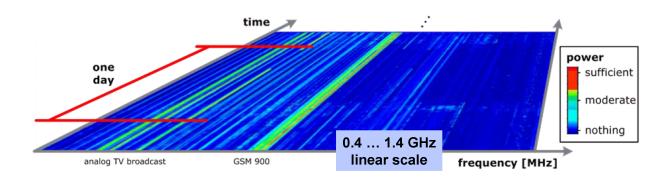

| 1.3 | Measured radio spectrum during a day [3]                                            | 2  |

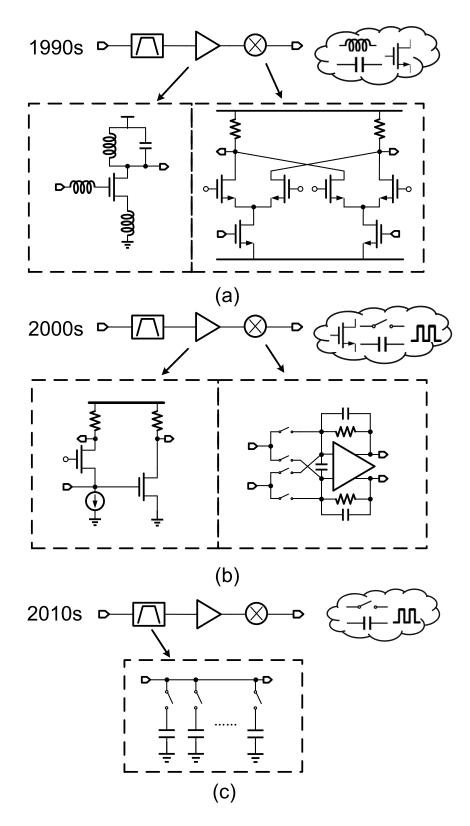

| 1.4 | (a) In the 1990s, inductor-degenerated LNAs and active mixers were the popu-        |    |

|     | lar RF front-end circuit. (b) In the 2000s, wideband LNAs (e.g., noise-canceling    |    |

|     | LNAs) and passive mixers became popular, thanks to faster transistors. (c) In the   |    |

|     | 2010s, switch-based RF circuits (e.g., the N-path filter) further improved receiver |    |

|     | performance with advanced CMOS process                                              | 5  |

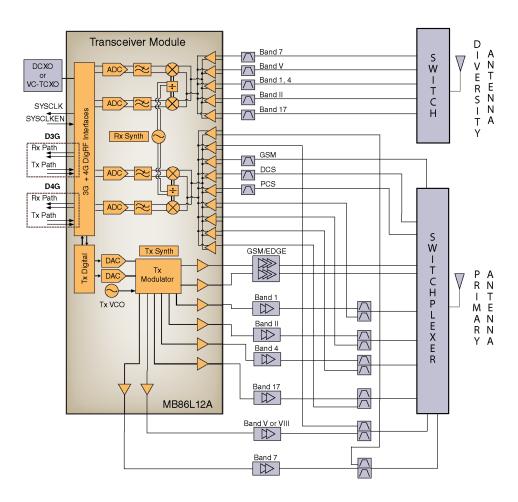

| 1.5 | Block diagram of a multiband LTE transceiver [4]                                    | 7  |

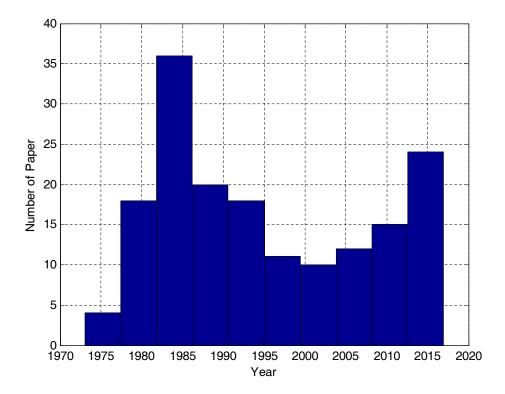

| 2.1 | Trend of switched-capacitor publications in JSSC (1970s–Feb. 2017)                  | 11 |

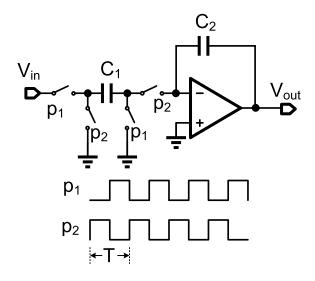

| 2.2 | Active switched-capacitor filter.                                                   | 12 |

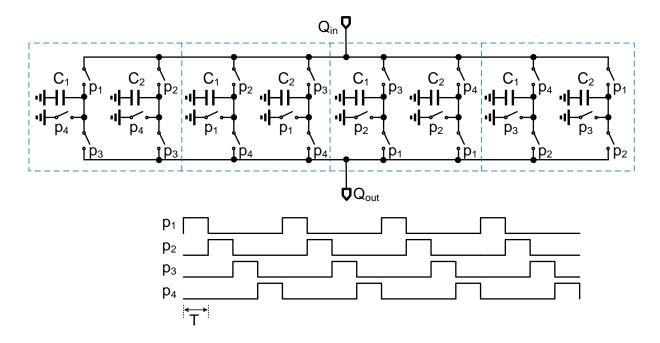

| 2.3 | Passive switched-capacitor finite impulse response filter                           | 13 |

| 2.4 | Passive switched-capacitor infinite impulse response filter                         | 14 |

| 2.5 | (a) Schematic and (b) frequency response of the N-path bandpass filter              | 16 |

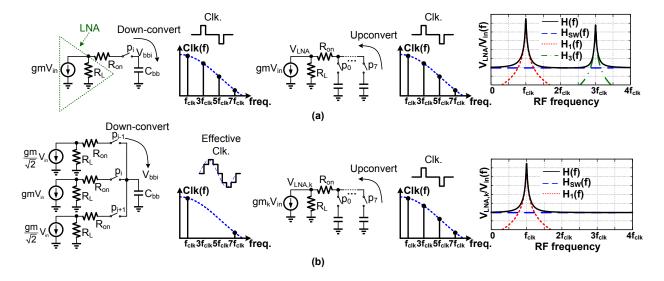

| 3.1 | (a) Conventional N-path filter. (b) Conventional N-path filter with LNA. (c) Pro-                         |    |

|-----|-----------------------------------------------------------------------------------------------------------|----|

|     | posed harmonic rejecting N-path filter with LNA                                                           | 20 |

| 3.2 | Simulated harmonic response (top row), harmonic folding (middle row), and har-                            |    |

|     | monic down-conversion (bottom row) in 4-path filter (left column), 8-path filter                          |    |

|     | (middle column) and proposed harmonic-rejecting 8-path filter (right column) for                          |    |

|     | a 0.2 GHz clock frequency.                                                                                | 21 |

| 3.3 | A simplified model for the harmonic response analysis for a differential NPF at                           |    |

|     | the output of the LNA; the LNA is modeled with a Norton equivalent (a) For a                              |    |

|     | conventional 8-path filter, the signals at $f_{\text{clk}}$ and $3f_{\text{clk}}$ are down-converted then |    |

|     | up-converted to RF input resulting in harmonic responses. (b) In the proposed                             |    |

|     | harmonic-rejecting 8-path filter, the harmonic down-conversion from $3f_{clk}$ is re-                     |    |

|     | jected by the effective LO, and the harmonic responses are improved. (Note that                           |    |

|     | the gain and bandwidth of the HR-8PF is different from conventional 8PF)                                  | 24 |

| 3.4 | (a) A differential harmonic rejecting N-path filter with non-overlapping clocks. (b)                      |    |

|     | An equivalent circuit of the LNA with a switch. (c) For one baseband capacitor,                           |    |

|     | the currents from all the LNAs generate the baseband voltage $V_{bb,i}.\ (d)$ All the                     |    |

|     | baseband voltages are up-converted to the LNA output                                                      | 25 |

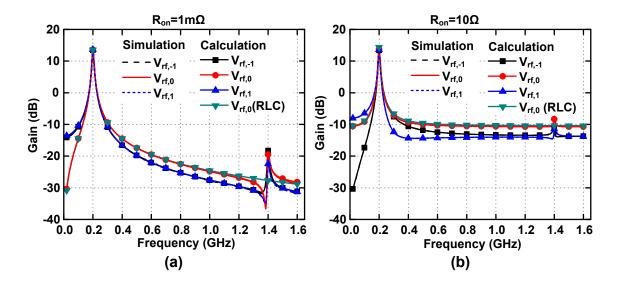

| 3.5 | The calculated (using (3.9)) and simulated transfer function of the HR-8PF with                           |    |

|     | an $R_{on}$ of (a) 1 m $\!\Omega$ and (b) 10 $\!\Omega$                                                   | 28 |

| 3.6 | Architecture of the blocker tolerant RF receiver                                                          | 32 |

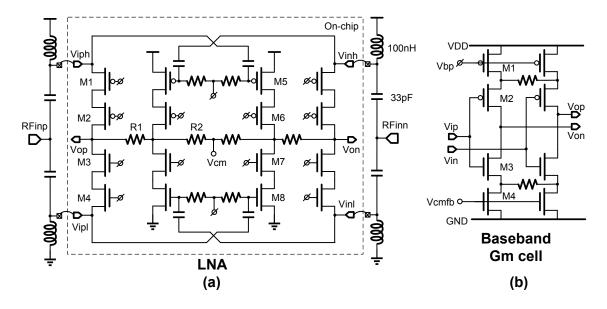

| 3.7 | Schematic of (a) LNA and (b) baseband Gm cell                                                             | 34 |

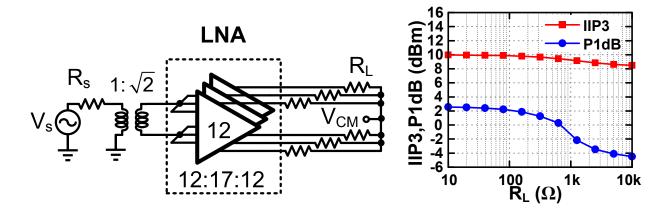

| 3.8  | Transistor simulated IIP3 and B1dB versus LNA load impedance for the LNA with                 |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | a gm factor of 17                                                                             | 36 |

| 3.9  | (a) Simplified model of the noise-cancelling LNA. (b) Noise cancelling in a har-              |    |

|      | monic rejection mixer.                                                                        | 37 |

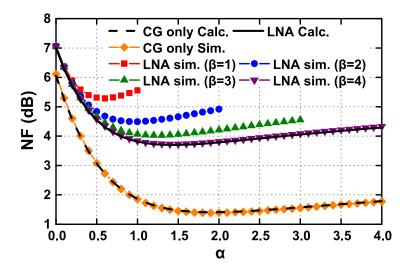

| 3.10 | Calculated and behavioral-level simulated front-end noise figure with noisy LNA               |    |

|      | versus factor $\alpha$                                                                        | 40 |

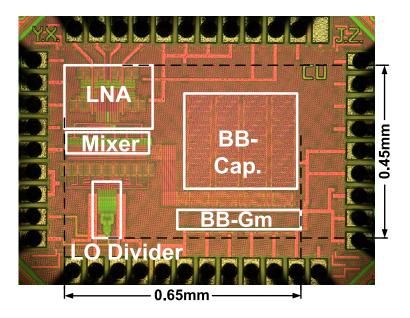

| 3.11 | Chip photo                                                                                    | 41 |

| 3.12 | LNA transfer function measured at RFtest for LO frequencies swept from 0.2 to                 |    |

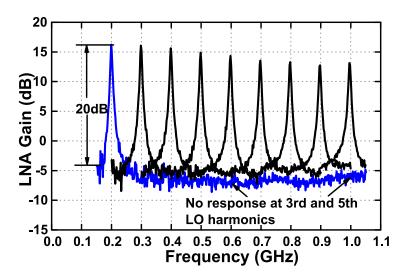

|      | 1GHz with a 0.1GHz step                                                                       | 41 |

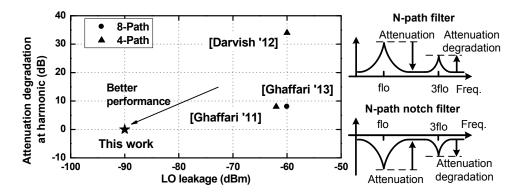

| 3.13 | Harmonic attenuation performance compared with other N-path filters                           | 42 |

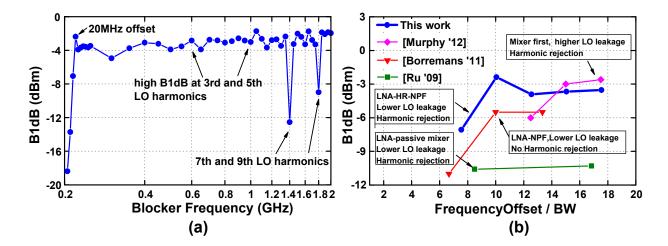

| 3.14 | (a) Measured blocker 1dB compression point (B1dB) versus blocker frequency                    |    |

|      | for an LO frequency of 0.2GHz. (b)B1dB versus relative blocker frequency offset               |    |

|      | compared with other blocker tolerant RXs                                                      | 43 |

| 3.15 | Measured out-of-band IIP3 for the OB signal located at 20MHz offset and 3 <sup>rd</sup> order |    |

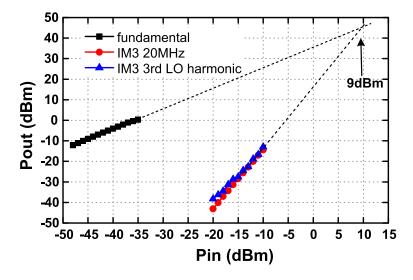

|      | LO harmonic.                                                                                  | 43 |

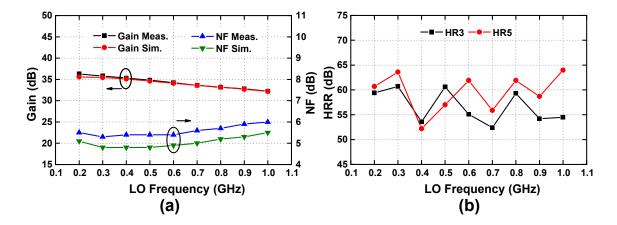

| 3.16 | (a) Measured and simulated conversion gain and noise figure, (b) measured har-                |    |

|      | monic rejection ratio versus LO frequencies                                                   | 44 |

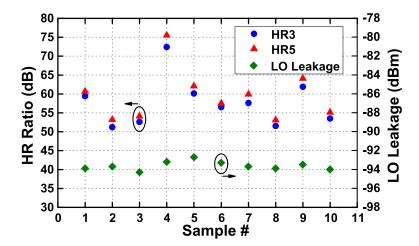

| 3.17 | Measured harmonic rejection ratio with a 0.2 GHz LO and LO leakage with 1 GHz                 |    |

|      | LO for 10 samples                                                                             | 45 |

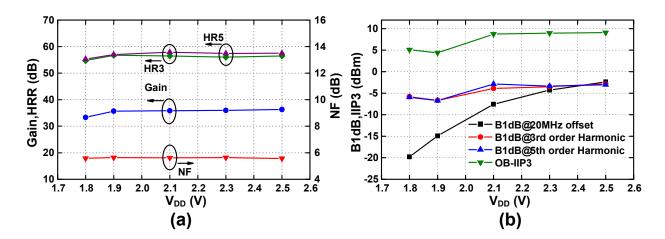

| 3.18 | (a) Gain, noise figure, harmonic rejection ratio and (b) OB-IIP3, OB-B1dB versus              |    |

|      | V <sub>DD</sub> measurement with a 0.2 GHz LO                                                 | 46 |

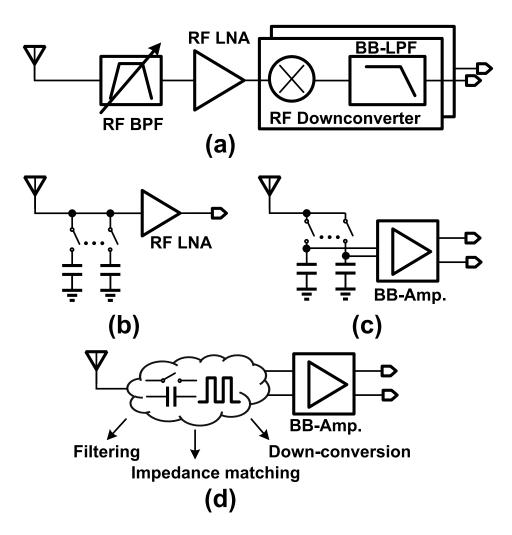

| 4.1 | (a) Wideband receiver with an off-chip RF bandpass filter. (b) A wideband re-                 |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | ceiver with an N-path filer at the RF input. (c) A mixer-first receiver. (d) Pro-             |    |

|     | posed switched-capacitor receiver with filtering, impedance matching and down-                |    |

|     | conversion performed with switches and capacitors only                                        | 50 |

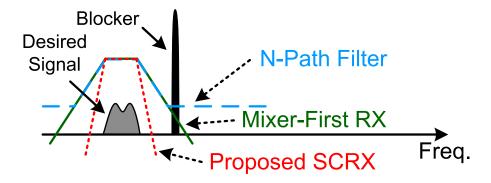

| 4.2 | Equivalent RF filtering before the nonlinear active circuits of an N-path filter, a           |    |

|     | mixer-first receiver, and the proposed switched-capacitor receiver                            | 51 |

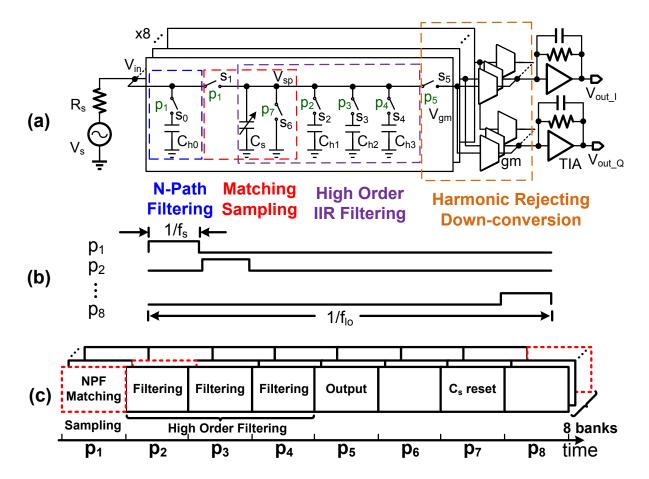

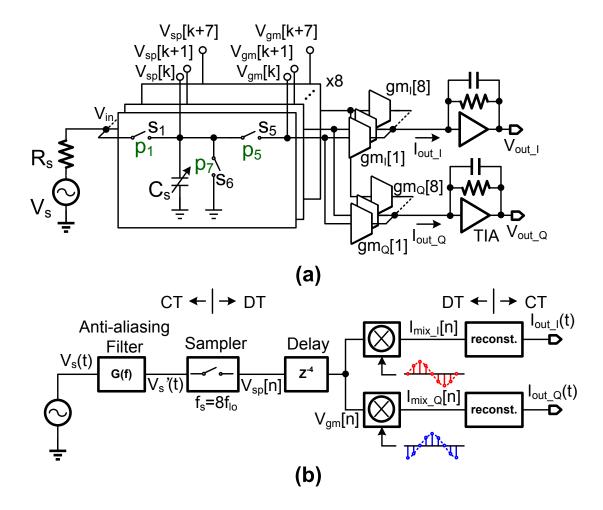

| 4.3 | (a) Simplified architecture of a single-ended SC receiver. (b) clock wave form. (c)           |    |

|     | Operation of the SC receiver                                                                  | 52 |

| 4.4 | (a) Simplified RF SC receiver without filtering. (b) Model of the SC receiver                 | 54 |

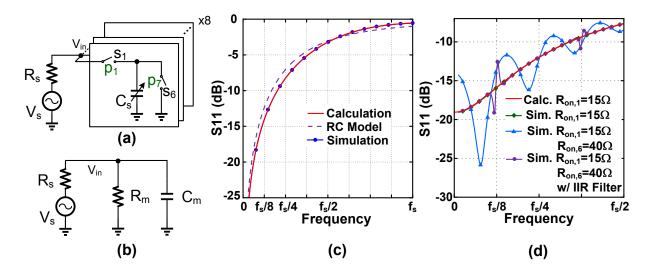

| 4.5 | (a) Switched-capacitor impedance-matching circuit. (b) RC model of the impedance-             |    |

|     | matching circuit. (c) Calculated and simulated $S_{11}$ with ideal switches. (d) Calcu-       |    |

|     | lated and simulated $S_{11}$ with finite $R_{on}$ and the differential IIR filter loading the |    |

|     | circuits                                                                                      | 55 |

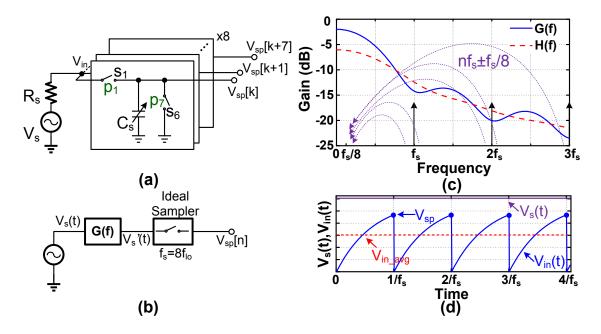

| 4.6 | (a) Sampling circuit. (b) Model of the sampling circuit. (c) Calculated transfer              |    |

|     | function of the CT antialiasing filter $G(f)$ . (d) Simulated input voltage transient         |    |

|     | wave form for a DC (0 Hz) source voltage                                                      | 58 |

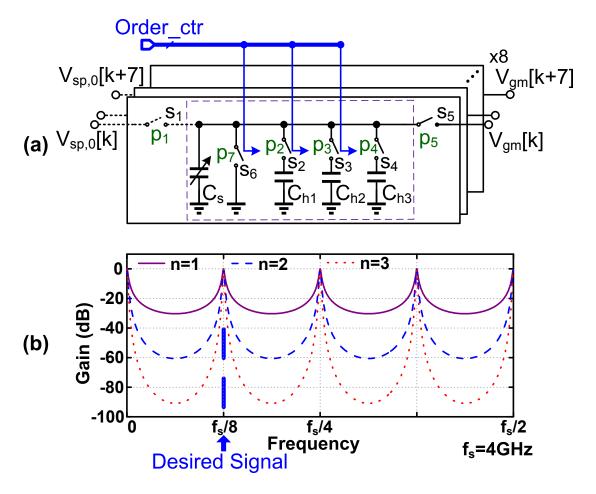

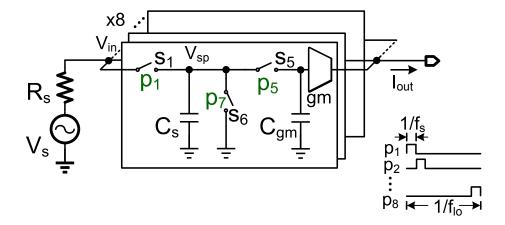

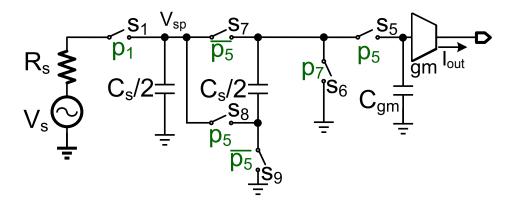

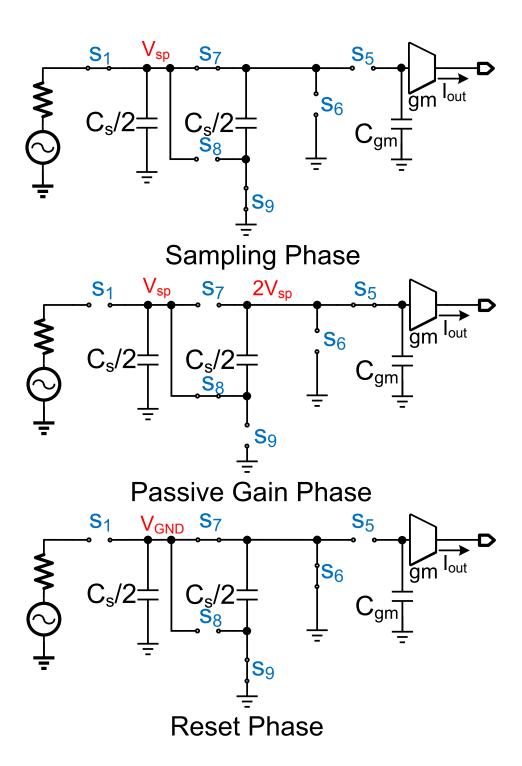

| 4.7 | (a) Schematic of the IIR filter with programmable order. (b) Calculated transfer              |    |

|     | function of the IIR filter for $f_s=4\text{GHz}, C_s=3.15\text{pF}$ , and $C_h=50\text{pF}.$  | 61 |

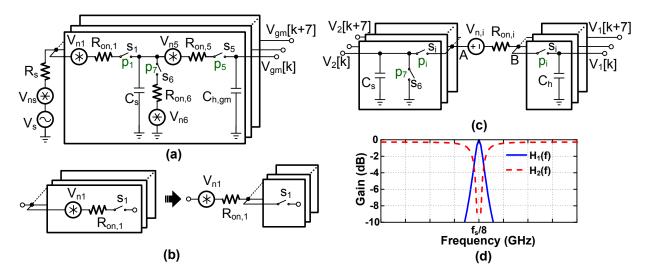

| 4.8  | (a) Noise sources in the switched-capacitor receiver with filtering. (b) All the noise                       |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

|      | sources of the s <sub>1</sub> swithes can be merged into a single noise source. (c) Simplified               |    |

|      | schematic for the noise analysis of s2 to s5. (d) Calculated transfer function of                            |    |

|      | voltage source $V_{n,i}$ in (c) to the capacitors $C_h$ $(H_1(f))$ and $C_s$ $(H_2(f)). \ . \ . \ . \ . \ .$ | 63 |

| 4.9  | Model to calculate the propagation of the noise of the source and switches through                           |    |

|      | the switched-capacitor receiver                                                                              | 64 |

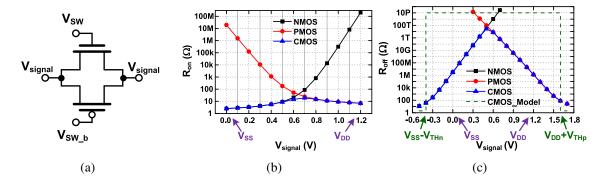

| 4.10 | (a) Schematic of the CMOS switch, the sizes of the NMOS and PMOS transistors                                 |    |

|      | are the same (W/L = $150 \mu\text{m}/40 \text{nm}$ ). (b) Simulated R <sub>on</sub> of NMOS, PMOS and        |    |

|      | CMOS switches versus signal voltage. (c) Simulated $R_{\text{off}}$ of NMOS, PMOS and                        |    |

|      | CMOS switches versus signal voltage                                                                          | 66 |

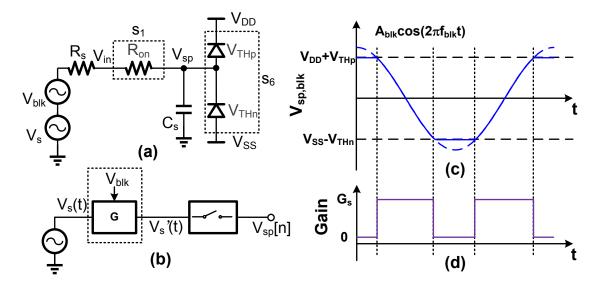

| 4.11 | (a) Simplified sampler schematic when the input signal is sampled on $C_s$ . (b) Sam-                        |    |

|      | pler model with blocker. (c) Sampled blocker voltage versus time. (d) Small signal                           |    |

|      | gain versus time.                                                                                            | 67 |

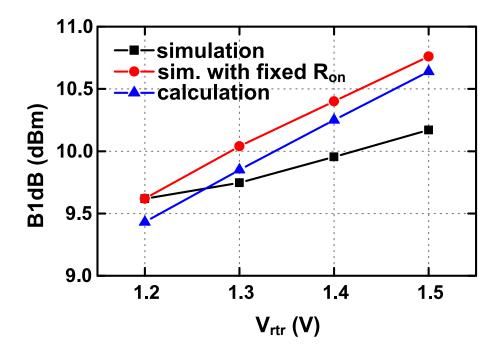

| 4.12 | Calculated and simulated 1 dB compression point (B1dB) versus rail-to-rail volt-                             |    |

|      | age of the differential SCRX with a 100 MHz LO frequency and 30 MHz blocker                                  |    |

|      | frequency offset; real MOS transistors are used in the simulation and the input bias                         |    |

|      | voltage is the midpoint of the rail-to-rail voltage.                                                         | 67 |

| 4.13 | Schematic of the switched-capacitor RF receiver                                                              | 71 |

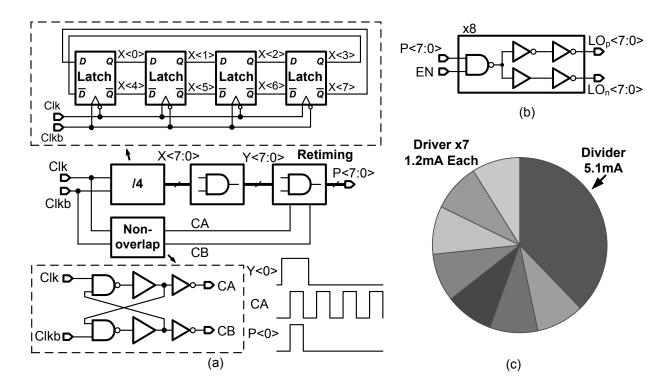

| 4.14 | (a) Block diagram of (a) the clock divider and (b) the clock driver circuits. (c)                            |    |

|      | Current consumption breakdown of the clock generator for a 0.2 GHz LO frequency.                             | 73 |

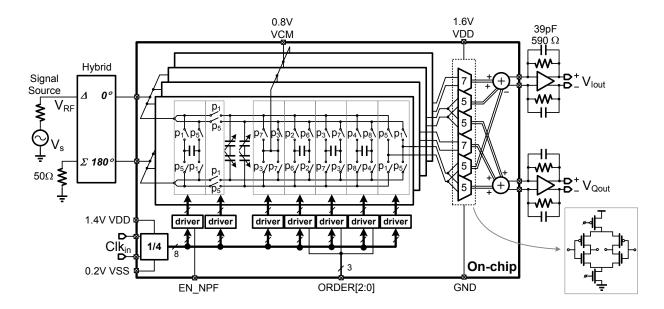

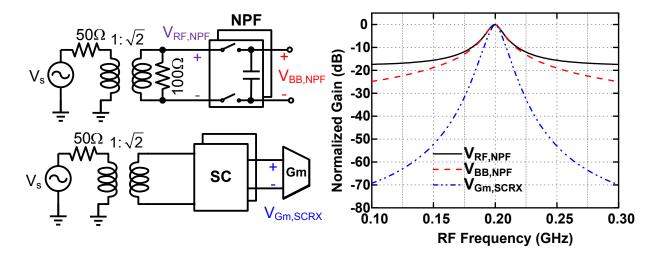

| 4.15 | Transistor-level simulation of the gain/conversion gain at node $V_{RF,NPF}$ , $V_{BB,NPF}$ ,           |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | $V_{\text{Gm,SCRX}}$ for a 0.2GHz LO frequency. All the transfer curves are normalized for              |    |

|      | equal in-band gain of 0 dB. $V_{RF,NPF}$ , $V_{BB,NPF}$ , and $V_{Gm,SCRX}$ are the nodes before        |    |

|      | non-linear active circuits in RF NPF, mixer-first receiver, and the proposed SCRX                       |    |

|      | respectively as shown in Fig. 4.1(b)(c)(d)                                                              | 74 |

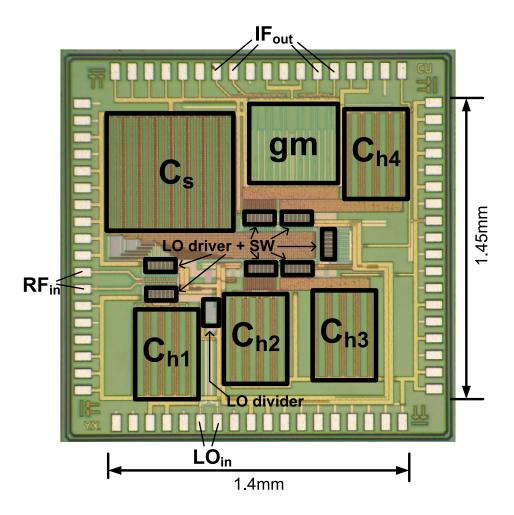

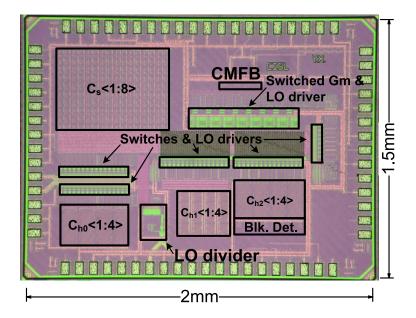

| 4.16 | Chip photo                                                                                              | 75 |

| 4.17 | Measured differential-mode $S_{11}$ for LO frequencies ranging from 0.1 to 0.7 GHz                      |    |

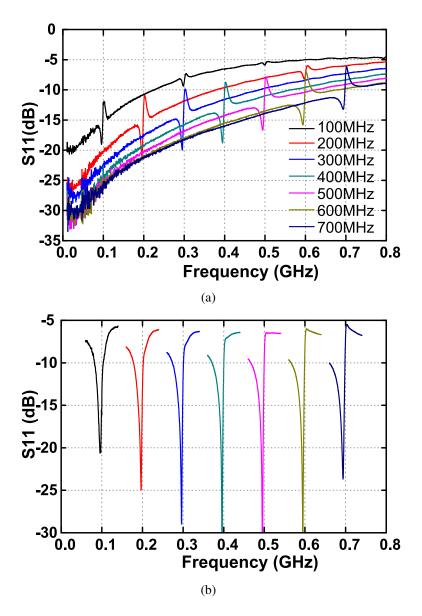

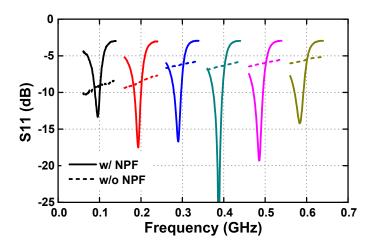

|      | with a 0.1 GHz step: (a) $S_{11}$ without the N-path filter; (b) $S_{11}$ with the N-path filter.       | 77 |

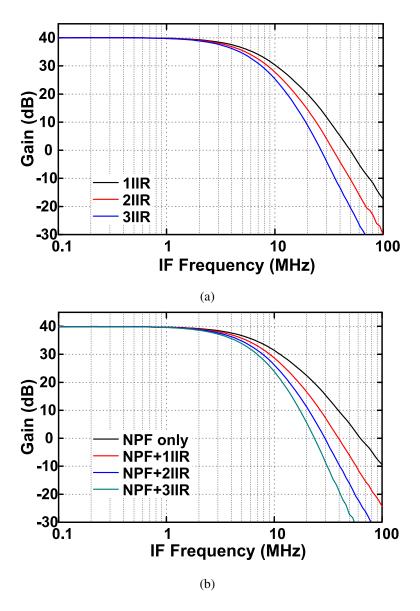

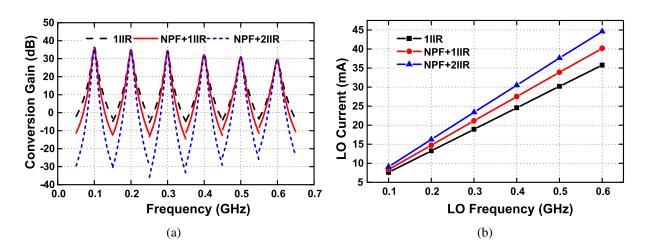

| 4.18 | Measured conversion gain $V_{\text{Iout}}/V_{\text{RF}}$ with different filter configurations for an LO |    |

|      | frequency of 0.2 GHz: (a) Conversion gain without the N-path filter; (b) Conver-                        |    |

|      | sion gain with the N-path filter                                                                        | 78 |

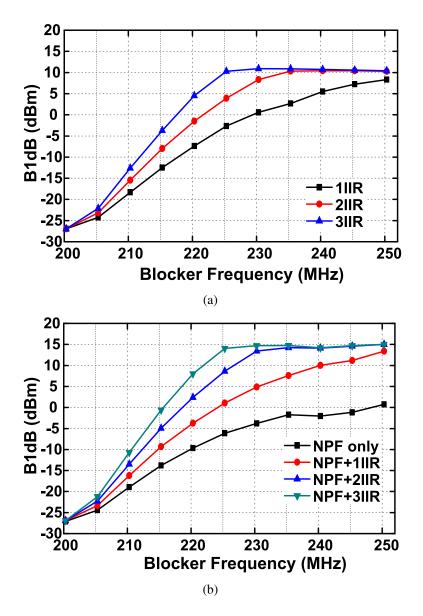

| 4.19 | Measured B1dB versus blocker frequency for an LO frequency of 0.2 GHz: (a)                              |    |

|      | B1dB without the N-path filter; (b) B1dB with the N-path filter                                         | 80 |

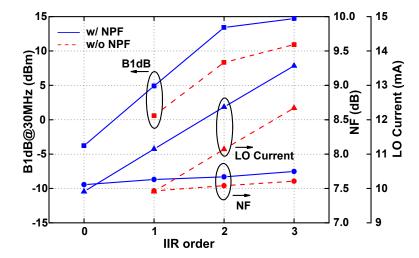

| 4.20 | Measured B1dB at a 30 MHz frequency offset, noise figure, LO current consump-                           |    |

|      | tion versus filter order for a LO frequency of 0.2 GHz                                                  | 81 |

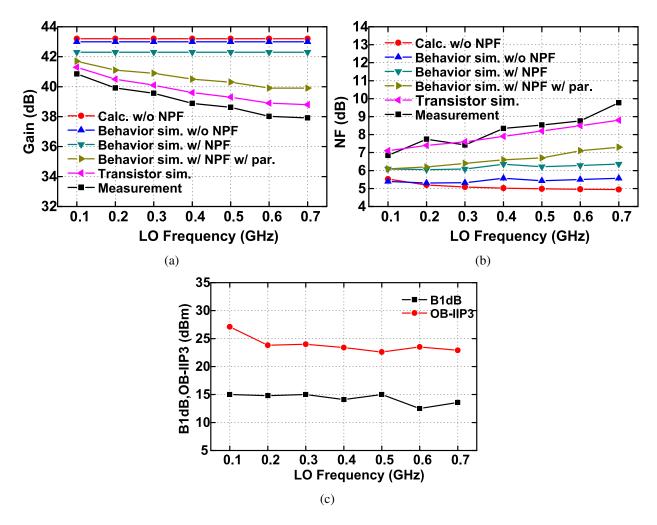

| 4.21 | The (a) conversion gain $V_{Iout}/(V_s/2)$ , (b) NF, and (c) B1dB and OB-IIP3 across                    |    |

|      | LO frequency; in all cases 3rd-order IIR filtering is used; results are shown for                       |    |

|      | calculations using the differential version of (4.7) and (4.15), behavioral-level sim-                  |    |

|      | ulations (without NPF; with NPF, with and without the parasitic capacitance and                         |    |

|      | non-ideal clock), transistor-level simulations with NPF, and measurements with NPF.                     | 82 |

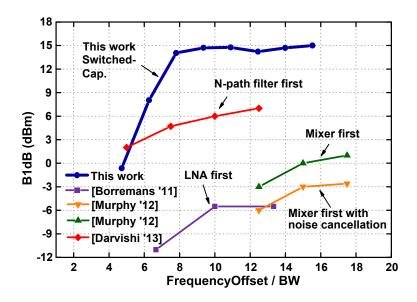

| 4.22 | Comparison with other blocker-tolerant RF receivers of their B1dB versus relative            |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | blocker frequency offset                                                                     | 83 |

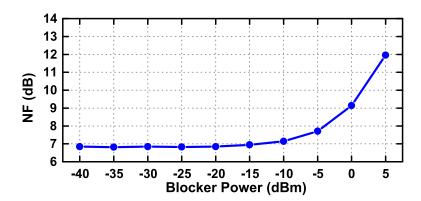

| 4.23 | Measured noise figure versus blocker power with a 0.13GHz continuous-wave                    |    |

|      | blocker for a LO frequency of 0.1GHz                                                         | 83 |

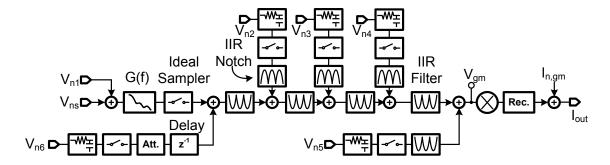

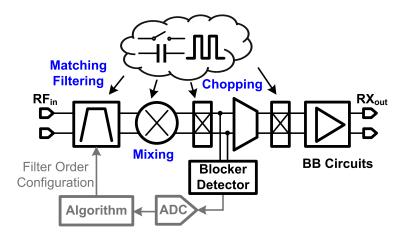

| 5.1  | Proposed chopping switched-capacitor RF receiver with blocker detection                      | 89 |

| 5.2  | Simplified architecture of the switched-capacitor receiver                                   | 90 |

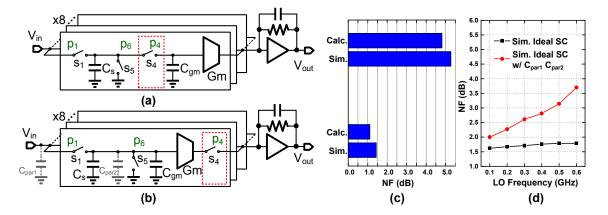

| 5.3  | (a) Switched-capacitor RF receiver without filtering [5]. (b) Proposed approach to           |    |

|      | improve the noise figure by relocating output switch s4 after the baseband transcon-         |    |

|      | ductor Gm. (c) Calculated and behavioral-level simulated noise figure of both ar-            |    |

|      | chitectures. (d) Simulated noise figure versus LO frequency.                                 | 91 |

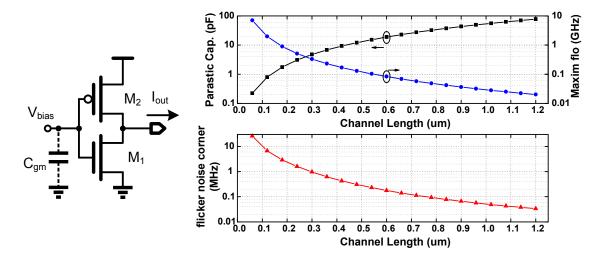

| 5.4  | Simulated Gm parasitic capacitance, flicker-noise corner, and maximum $f_{\text{LO}}$ of the |    |

|      | switched-capacitor receiver versus transistor length for a 100 mS inverter-based             |    |

|      | Gm in 65 nm CMOS                                                                             | 92 |

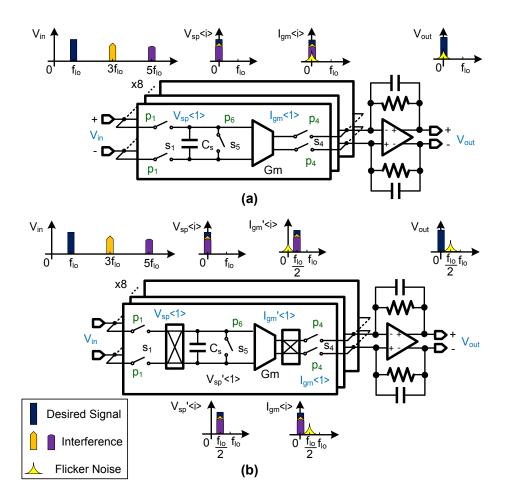

| 5.5  | (a) Modified differential switched-capacitor receiver with improved noise perfor-            |    |

|      | mance; (b) proposed modified switched-capacitor receiver including chopping                  | 95 |

| 5.6  | (a) Architecture of the proposed chopping switched-capacitor RF receiver with                |    |

|      | high-order filtering; (b) Implementation with the chopper merged into the switched-          |    |

|      | capacitor circuits                                                                           | 96 |

| 5.7  | Block diagram of the switched-capacitor RF receiver with RF blocker power de-                |    |

|      | tector                                                                                       | 97 |

| 5.8  | Schematic of the chopping switched-capacitor RF receiver                                     | 99 |

| 5.9  | Schematic of the baseband switched Gm cell                                                            |

|------|-------------------------------------------------------------------------------------------------------|

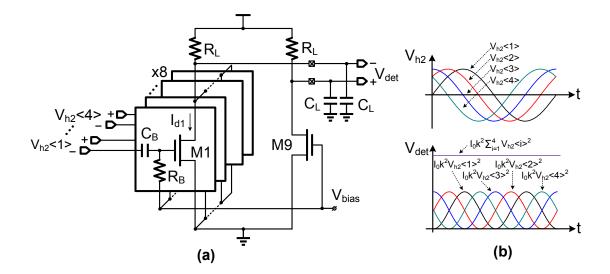

| 5.10 | (a) Schematic of the blocker detector. (b) Input and output waveforms of the blocker                  |

|      | detector                                                                                              |

| 5.11 | Chip photo                                                                                            |

| 5.12 | Measured differential-mode $S_{11}$ for LO frequencies ranging from $0.1\ to\ 0.6\ GHz$               |

|      | with a 0.1G Hz step with and without the N-path filter                                                |

| 5.13 | Measured (a) conversion gain $V_{\text{Iout}}/V_{\text{RF}}$ ; (b) LO current versus RF frequency for |

|      | LO frequencies ranging from 0.1 to 0.6 GHz with a 0.1 GHz step and for different                      |

|      | filter configurations                                                                                 |

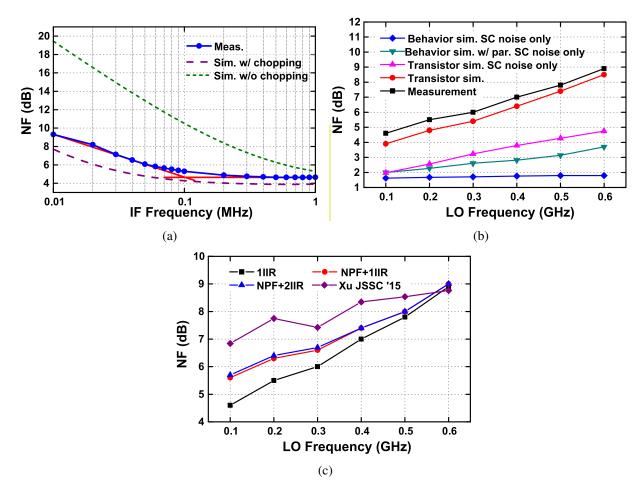

| 5.14 | (a) Measured and simulated NF versus IF frequency for an LO frequency of 0.1 GHz                      |

|      | with first-order IIR filtering; (b) Measured and simulated NF versus LO frequency                     |

|      | for the receiver with first-order IIR filter; (c) Measured NF across LO frequency                     |

|      | compared with earlier switched-capacitor receiver                                                     |

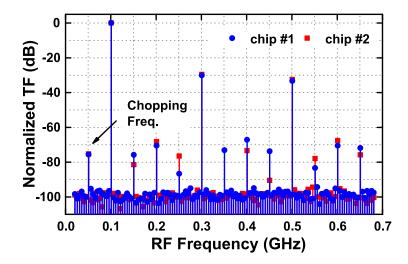

| 5.15 | Measured wideband transfer function for an LO frequency of 0.1 GHz 108                                |

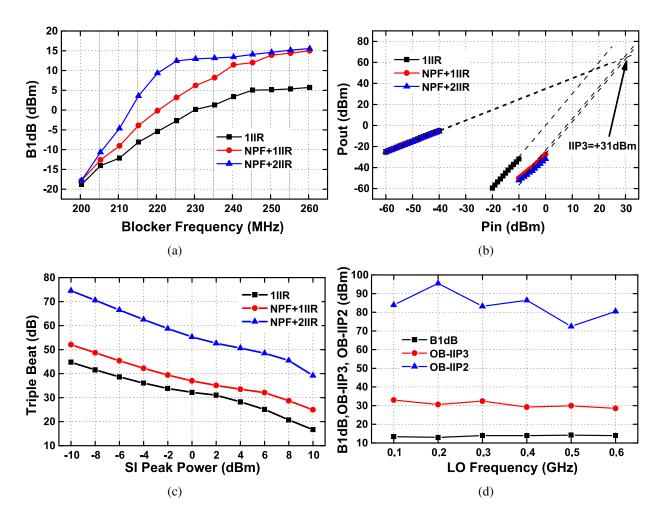

| 5.16 | (a) Measured blocker 1dB compression point versus blocker frequency; (b) out-if-                      |

|      | band IIP3; and (c) triple beat versus two-tone SI peak power for an LO frequency                      |

|      | of 0.2 GHz with different filter configurations; (d) measured B1dB, OB-IIP3, OB-                      |

|      | IIP2 for LO frequencies stepped between 0.1 and 0.6 GHz                                               |

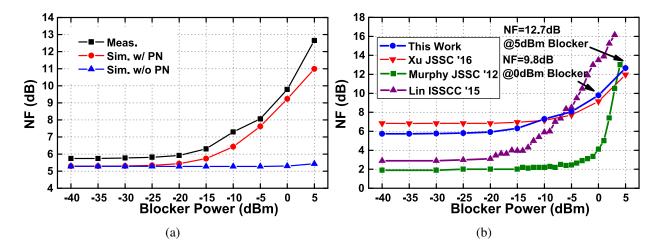

| 5.17 | (a) Measured and simulated blocker noise with blocker at 30MHz for a 0.1 GHz                          |

|      | LO. (b) Measured blocker noise figure compared with other blocker tolerant re-                        |

|      | ceivers                                                                                               |

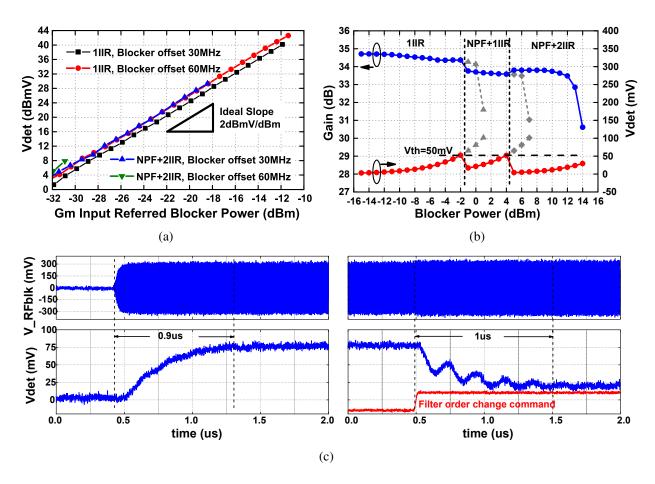

| 5.18 | (a) Measured blocker-detector output voltage versus Gm input-referred blocker       |

|------|-------------------------------------------------------------------------------------|

|      | power for different filter orders and blocker offset frequencies. (b) Measured con- |

|      | version gain versus blocker power with adaptive filter order for a 0.2 GHz LO and   |

|      | 30 MHz blocker offset. (c) The blocker-detector transient response                  |

| 6.1  | Core circuits of a switched-capacitor receiver                                      |

| 6.2  | SC bank #1 of the capacitor-stacking SCRX core circuits                             |

| 6.3  | Operation of a capacitor-stacking SCRX                                              |

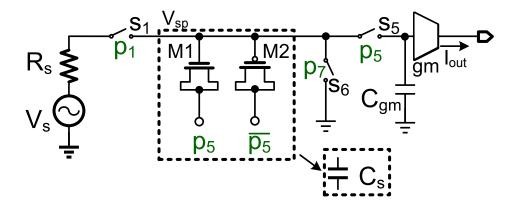

| 6.4  | SC bank #1 of the parametric SCRX core circuits                                     |

| 6.5  | Operation of the parametric SCRX                                                    |

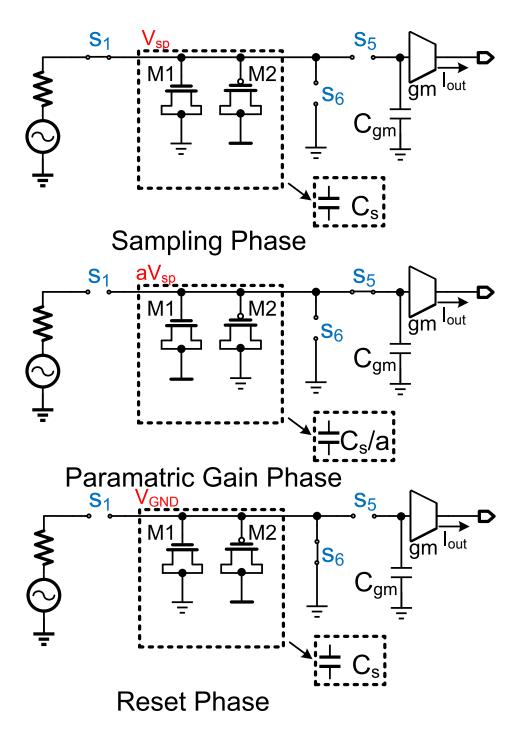

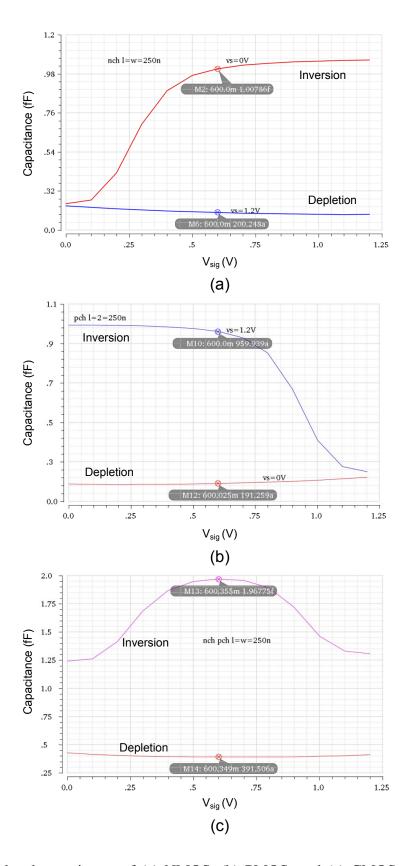

| 6.6  | Linearization of sampling capacitance in parametric amplification                   |

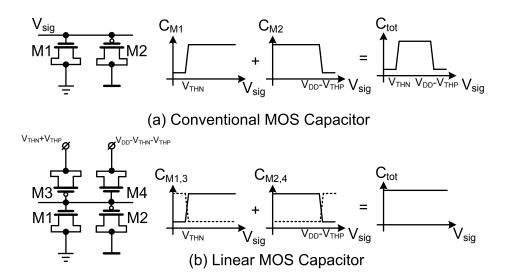

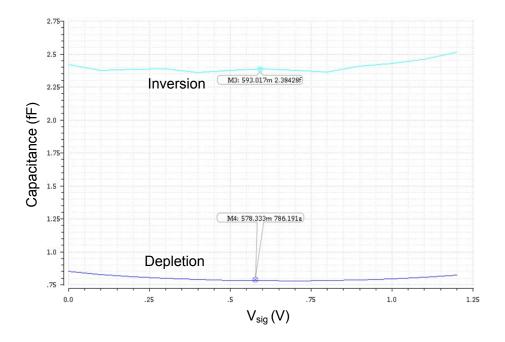

| 6.7  | Simulated capacitance of (a) NMOS, (b) PMOS, and (c) CMOS capacitors versus         |

|      | input voltage                                                                       |

| 6.8  | Simulated capacitance of the linearized CMOS capacitor versus input voltage 126     |

# **List of Tables**

| 3.1 | Breakdown of the transistor-level simulated noise contribution           |

|-----|--------------------------------------------------------------------------|

| 3.2 | Comparison with the state of the art                                     |

| 4.1 | Comparison with the state of the art                                     |

| 5.1 | Comparison with the state of the art                                     |

| 6.1 | Comparison of SCRX without and with capacitor stacking                   |

| 6.2 | Comparison of SCRX with CMOS capacitor and linearized CMOS capacitor 127 |

### Acknowledgments

This dissertation could not have been completed without the great support that I have received from so many people over the years. I wish to offer my most heartfelt thanks to the following people.

First of all, I would like to express my sincere appreciation to my advisor Professor Peter Kinget for his guidance. He has been actively interested in my work and has always been available to provide valuable advice. I thank him for providing me with the opportunity to work with a talented team of researchers. I also thank my committee members: Prof. Yannis Tsividis, Prof. Charles Zukowski, Prof. Kaushik Sengupta, and Dr. Tony Montalvo for their invaluable time, comments and feedback.

I would give my thanks to Wei Family Private Foundation, DARPA, as well as Department of Electrical Engineering for my financial funding, and UMC for chip fabrication donation. I also wish to express my appreciation to Professor Harish Krishnaswamy for technical discussions, and Bob Melville for measurement support.

I am grateful to all my colleagues, past and current of the Columbia Integrated System Laboratory. It has been an honor working with Karthik Tripurari, Baradwaj Vigraham, Jayanth Kuppambatti, Chun-Wei Hsu, Rabia Tugce Yazicigil, Chengrui Le, Jianxun Zhu, Teng Yang, Tanbir Haque, Sarthak Kalani, Daniel de Godoy Peixoto, Shravan Nagam, Scott Newton, Matt Bajor, Vivek Mangal, Yudong Zhang, Meng Wang, Xiang Li, Branislav Jovanovic, Michael Whalen, Mengxi Lin, Jian Lu, Sagar Vaze, Damla Dimlioglu, Manoj Gupta, Guoxiang Hang, Suhas Rao, Ning Guo, Yu Chen, Tao Mai, Linxiao Zhang, and Tsung-Hao (Jeffrey) Chuang.

Most of all, I would like to sincerely thank for the love, support, and encouragement from my families, my parents and my wife Ni Xu. Without their love and understanding, I would not be able to pursue my PhD and this work would never have come into existence.

## Chapter 1

### Introduction

#### 1.1 Evolution of Wireless Communications

The demand for wireless communications has grown very quickly [1], and this high-speed communication has significantly changed people's lifestyle. Fig. 1.1 shows the data rates of different cellular standards. In 1991, when the Global Systems for Mobile (GSM) communications was released, the data rate was 9.6 kbps and only supported voice and short-message services. Twenty-six years later, the data rate of Long-Term Evolution-Advanced (LTE-A) is 1 Gbps, which is more than 100,000 times faster than GSM. Today, people can use a smartphone to watch online videos using LTE. Apart from cellular communication, other wireless connectivity systems (such as WLAN/WiFi, Bluetooth, RFID, NFC, and ZigBee) and the Global Navigation Satellite System (GNSS; as well as GPS, GLONASS, and BeiDou) also play a significant role in our daily lives.

One of the bottlenecks to achieving a high data rate in wireless communication is inefficient

Figure 1.1: Data rates of cellular communications [1].

Figure 1.2: United States frequency allocation chart (30 MHz–3 GHz) [2].

Figure 1.3: Measured radio spectrum during a day [3].

frequency allocation. In the United States, the radio spectrum is regulated by the Federal Communications Commission (FCC) and the National Telecommunications and Information Administration (NTIA). Fig. 1.2 [2] shows the frequency allocation from 30 MHz to 3 GHz. Different standards are allocated in different frequency bands. However, if we measure the radio spectrum during a day [3] (Fig. 1.3), we can find some bands are very busy (e.g., GSM) while some bands are almost unused. The radio spectrum is a costly and limited natural resource. However, the current static frequency allocation leads to low spectrum-use efficiency. Going forward, dynamic frequency allocation can make the spectrum use more efficient.

Cognitive radio (CR) technology [6] was proposed to achieve dynamic spectrum access. CR is a wireless architecture in which a communication system does not operate in a fixed assigned band. Rather, each device automatically finds an appropriate empty band for its communication. There are two main methods for the secondary, cognitive, user to avoid interfering with primary or licensed users. The first is to use spectrum sensing [7], which uses a spectrum detector to sense the primary user's frequency band. The second to use a geolocation database [8]. The database system protects the primary users, ensuring that any interference is below acceptable thresholds, and enables the secondary users to access unused frequency bands. CR must be reconfigurable to adapt its RF center frequency and bandwidth to the available spectrum. Therefore, tunable receiver hardware is a key CR component.

Recently, the unlicensed devices have been allowed to operate on TV white spaces (TVWS), frequencies in the TV bands in areas where they are not used by licensed services [9]. The migration from analog TV to digital TV has freed up several VHF and UHF bands (48 MHz–860 MHz)

due to the high spectral efficiency of digital TV. Many wireless standards based on the CR concept are emerging for TVWS communications, including IEEE 802.22 [10], 802.11af [11], and 802.15.4m [12]. IEEE 802.22 provides long-range (30 km) connectivity in rural areas to build wireless regional area networks (WRAN). IEEE 802.11af is a WiFi-like wireless local area network (WLAN). IEEE 802.15.4m is a low-data-rate wireless personal area network (WPAN) suitable for the Internet of Things (IoT) and machine-to-machine (M2M) communications.

#### 1.2 Evolution of CMOS RF Receiver Front Ends

In the early 1990s, RF receiver front ends were mainly implemented in bipolar processes with standalone circuit building blocks. The development of the CMOS RF technique [13] in the mid-1990s dramatically improved the scale of integration and reduced the cost of RF receivers. Process scaling and circuit innovation were the two main engines driving the evolution of the CMOS RF receiver front end.

In first-phase integrated CMOS RF receivers [14–16] (Fig. 1.4(a)), inductor-degenerated LNA and CMOS Gilbert-cell-based mixers were the most popular circuit typologies in micron-scale process. Inductor-degenerated LNAs achieved a good noise figure and provided RF gain. However, it required bulky on-chip or off-chip inductors and had a narrow bandwidth. The CMOS Gilbert cell also had limited linearity.

With better CMOS process, the parasitic capacitance of the MOS transistors was reduced, so that the transistors could operate at higher frequencies. In the 2000s, inductorless LNAs with smaller area and wide RF bandwidth became more popular. These were implemented with resis-

**Figure 1.4:** (a) In the 1990s, inductor-degenerated LNAs and active mixers were the popular RF front-end circuit. (b) In the 2000s, wideband LNAs (e.g., noise-canceling LNAs) and passive mixers became popular, thanks to faster transistors. (c) In the 2010s, switch-based RF circuits (e.g., the N-path filter) further improved receiver performance with advanced CMOS process.

tive feedback [17, 18] and innovated noise-canceling techniques [19, 20]. With faster transistors, the switch-based passive mixer [21] offered better linearity (Fig. 1.4(b)). However, without the narrowband resonance tank, the wideband LNA had limited out-of-band (OB) linearity.

In recent years (Fig. 1.4(c)), more switch-based RF techniques have appeared due to the better switch performance with advanced process. N-path bandpass filters [22–26] and mixer-first receivers [27–31] use the switches to achieve better OB linearity with tunable center frequency. My research focuses on further investigating how to use advanced CMOS process to improve receiver performance.

#### 1.3 Motivation

To receive a narrowband signal with wide tuning range, a wideband tunable receiver is the key block in CR to achieve dynamic spectrum access. The wideband receiver front end needs to achieve a tunable center frequency, low noise, and OB interference tolerance. High OB interference tolerance is the key challenge in receiver design.

In the commercial receiver, which also needs to support different RF bands, OB interference tolerance is achieved with multiple off-chip filters. Fig. 1.5 shows the block diagram of a multiband 2G/3G/4G LTE transceiver [4]. On the receiver side, different bands can share the synthesizer, down-convert, and baseband circuits. However, dedicated off-chip filters and LNAs are used for different bands. The high-Q off-chip filter for a certain center frequency can strongly attenuate the OB interfere to relax the RF front end's linearity requirements.

In CR systems, the goal is to replace high-quality fixed off-chip RF filters with tunable RF

Figure 1.5: Block diagram of a multiband LTE transceiver [4].

filtering to realize an interference-tolerant tunable RF receiver front end. RF MEMS filters have been proposed to achieve the off-chip high-quality tunable filters, but they suffer from a limited tuning range, in-band loss and large size [32]. Conventional on-chip RF filters, such as LC [33] and  $G_m$ -C [34], suffer from either a low quality (Q) factor, small tuning range, or limited linearity [25]. Without wide-tuning, high-Q, linear filters, wideband receivers suffer from the impact of the large continuous-wave (CW) close-by blockers that saturate the RF front end and desensitize the receiver. Even if the interferer power is not large enough to block the desired signal, the intermodulation and cross-modulation caused by the OB interferer in FDD, along with coexistence scenarios, can degrade the signal-to-noise ratio.

Switched-capacitor (SC) RF filters, such as N-path filters implemented in CMOS, offer tunable high-quality filtering [22, 23, 26, 35–37] to improve OB linearity. Furthermore, the SC approach benefits from process scaling, which provides faster switches and a lower power clock generator [38]. In this thesis, we use the SC technique to overcome the drawbacks of conventional SC RF filters, such as harmonic response and limited filter order.

### 1.4 Organization of the Thesis

Chapter 2 summarize the SC techniques used in RF receivers. Chapter 3 proposes an RF front end with a harmonic-rejecting N-path filter. This front end mitigates the N-path filter's harmonic-response issue and features tunable narrowband filtering and high attenuation of the third- and fifth-order LO harmonics at the LNA output, improving the blocker tolerance at LO harmonics. Chapters 4, 5, and 6 introduce the SC RF front ends, achieving equivalent high-order, tunable,

highly linear RF filtering to improve the OB blocker tolerance. RF input impedance matching, N-path filtering, high-order discrete-time infinite-impulse response (IIR) filtering, and down conversion are implemented using only switches and capacitors. The basic SC RF front end is proposed in Chapter 4 achieving rail-to-rail blocker tolerance. Two different methods to improve the noise performance of the SCRX are proposed in Chapters 5 and 6 using chopping techniques and passive gain. Chapter 7 concludes.

## Chapter 2

## **Review of Switched-Capacitor Techniques**

# for RF Receiver Design

Thanks to the simple switches and high impedance nodes of the CMOS process, SC circuits can be easily implemented and play a key role in analog signal processing. Fig. 2.1 shows the trend of SC papers published in the *Journal of Solid-State Circuits* (JSSC) since the 1970s. It was a hot topic in 1980s. Most of the basic SC structures were developed (e.g., active SC filters [39–41], N-path filters [42–44]) at that time. In recent years, SC research is trending up because, with advanced CMOS process, SC applications have expanded to RF front ends such as RF N-path bandpass filter [23–26] and SC RF power amplifier–transmitters [45–48].

In RF receivers, SC techniques are used to implement filters eliminating large undesired signals and relaxing the dynamic-range requirements of subsequent circuits [49–53]. Compared with other analog filters such as active-RC and  $G_m$ -C filters, the corner frequencies of SC filters are well

Figure 2.1: Trend of switched-capacitor publications in JSSC (1970s–Feb. 2017).

controlled and less sensitive to PVT variations since they are set by the capacitor ratio and can be programmed by the tunable capacitor banks. Active discrete-time (DT) filters, passive DT filters, and N-path filters are the three popular blocks used in RF receivers.

### 2.1 Active DT Filters

Active DT SC filters can be used as baseband filters in an RF receiver. Fig. 2.2 shows a simple active SC filter. The switches can be implemented by MOS transistors and driven by nonoverlapping clocks. The input voltage is sampled on  $C_1$  in  $p_1$ , and the charge on  $C_1$  is transferred to  $C_2$  in  $p_2$ .

**Figure 2.2:** Active switched-capacitor filter.

Assuming the opamp has infinite gain, the filter's transfer function can be written as

$$H(z) = \frac{V_{\text{out}}(z)}{V_{\text{in}}(z)} = \frac{C_1}{C_2} \cdot \frac{z^{-1}}{1 - z^{-1}}.$$

(2.1)

With an active opamp, any type of filter can be synthesized [54]. The key drawback of the active DT SC filter is that the opamp mainly limits its performance. Considering the finite gain of the opamp, the filter's transfer function is

$$H(z) = \frac{V_{\text{out}}(z)}{V_{\text{in}}(z)} = \frac{C_1}{C_2} \cdot \frac{\frac{C_2 A}{C_2 (1+A) + C_1} z^{-1}}{1 - \frac{C_2 (1+A)}{C_2 (1+A) + C_1} z^{-1}},$$

(2.2)

where A is the opamp gain. Opamp gain drops at high frequencies due to finite bandwidth, which increases the filter's gain and phase errors. The opamp's unity-gain frequency sets the active DT SC circuit's upper-limit clock rate. The clock frequency must be less than 1/5 of the opamp unity-gain frequency to keep the effects of finite opamp bandwidth negligible [55]. The bandwidth of the

**Figure 2.3:** Passive switched-capacitor finite impulse response filter.

active DT SC filter is less than half the clock frequency and therefore limited to tens of megahertz.

Due to the limited clock frequency, active DT filters are always placed at the latter stages of the SC filter chain [56], and decimation is required to reduce the active filter's clock rate.

#### 2.2 Passive DT Filters

Lacking the active opamp, passive DT SC filters simply rely on charge sharing to achieve the charge transfer. Passive SC filters' operation frequency is not limited by the opamp unity-gain bandwidth and can take full advantage of CMOS process scaling. There are two types of passive DT filters, finite impulse response (FIR) and infinite impulse response (IIR). More complex filters can be built from these basic structures.

An FIR filter is achieved by summing the delayed and weighted input signal. The capacitor can

Figure 2.4: Passive switched-capacitor infinite impulse response filter.

be considered as a charge memory, and the SC circuit is a perfect delay cell with the weighting achieved by scaling the capacitors. Fig. 2.3 shows a time-interleaved, first-order FIR filter. The input charge is sampled on  $C_1$  and  $C_2$  in  $p_1$ . Each capacitor stores a charge of  $C_iQ_{in}/(C_1+C_2)$ . In  $p_3$ , the capacitors sampling at  $p_1$  and  $p_2$  are connected to the output. Thus, the output signal is

$$Q_{\text{out}}(z) = \frac{C_2 + C_1 z^{-1}}{C_1 + C_2} z^{-1} Q_{\text{in}}(z).$$

(2.3)

The capacitors are reset to ground after the output is formed to prepare for the input sampling in next cycle. The input charge is consecutively sampled on the four SC banks. High-order FIR filter can be achieved by using more capacitor banks.

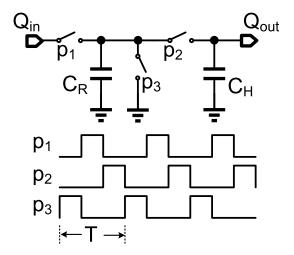

The IIR filter uses the input signal and past output signals to obtain the current output value, requiring less memory than the FIR filter to achieve the same filter selectivity. Fig. 2.4 shows a first-order IIR filter. In contrast to the FIR filter,  $C_{\rm H}$  is not reset each cycle, so it can store the past

output charge. The output signal is

$$Q_{\text{out}}(z) = \frac{1 - \alpha}{1 - \alpha z^{-1}} z^{-1} Q_{\text{in}}(z), \tag{2.4}$$

where  $\alpha = C_{\rm H}/(C_{\rm R}+C_{\rm H})$ . High-order IIR filters can be achieved by rotating the charge among several history capacitors [57].

The passive SC filter also has some drawbacks. In contrast to active filters, it may not be able to synthesize every type of filter [57], and it is hard to achieve signal gain to suppress the noise of the next stage. Most passive SC filters are used as baseband filters and driven by transconductance  $(G_m)$  cells, which makes the filter linearity limited by  $G_m$ .

#### 2.3 RF N-Path Filters

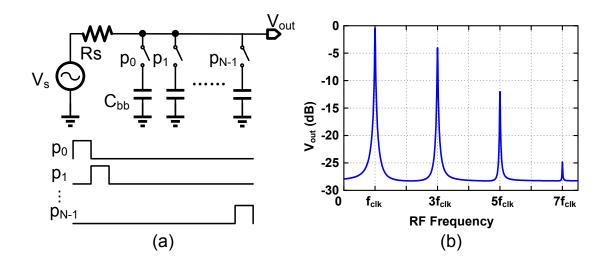

The N-path bandpass filter [22,58] has recently been popular in RF front-end design [23,26,35–37] because it provides narrowband filtering with a tunable center frequency. Fig. 2.5(a) shows a N-path filter with N SC banks. Each switch is driven by a nonoverlapping clock. The RF signal is first down-converted to baseband and filtered by  $C_{\rm bb}$ . It is then up-converted back to its original frequency. N-path filters feature narrow bandwidth, tunable center frequency and good linearity. The bandwidth depends on the RC constant at the baseband frequency. Achieving narrowband low-pass filtering is much easier than narrowband bandpass filtering. The center frequency is set by the clock frequency, achieving a large tuning range. Since the N-path filter can be directly connected to the RF input, linearity is limited only by the switches, and high linearity can be achieved.

Figure 2.5: (a) Schematic and (b) frequency response of the N-path bandpass filter.

Although the N-path filter is a good candidate for high-selectivity tunable RF bandpass filtering, it has drawbacks: harmonic response, limited filter order, and poor OB attenuation. Fig. 2.5(b) shows a differential N-path filter's frequency response (N=8). The desired center frequency is  $f_{\rm clk}$ . The N-path filter has harmonic responses at  $3f_{\rm clk}$ ,  $5f_{\rm clk}$ , and  $7f_{\rm clk}$  because the signals around those frequencies are down-converted by the clock harmonics and up-converted back to RF. The OB attenuation is limited to a certain number due to finite switch resistance. The first-order RC filter at baseband limits the N-path filter roll-off. A high-order active N-path filter [26] improves OB attenuation and filter order. However, the filter order before the active circuits is still low, making the linearity at close-by frequency is still limited by the active circuits.

#### 2.4 Thesis Overview

We present several techniques to improve the performance of SC-based RF filtering. Chapter 3 focuses on eliminating the N-path filter harmonic responses for better band selection. Chapters

4–5 present passive DT SC filter to achieve linear, high-order RF filtering. These chapters address such key challenges as linearity limitations, RF impedance matching, and noise performance.

# **Chapter 3**

# **Blocker-Tolerant Receiver with**

# **Harmonic-Rejecting N-Path Filtering**

## 3.1 Introduction

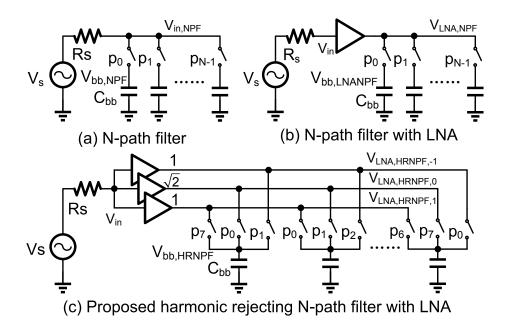

The switched capacitor-based N-path filter (NPF) [22–26] offers a high Q factor, large tuning range, and good linearity, and is a good candidate for on-chip blocker filtering. When using N-path filtering at the RF input (Fig. 3.1(a)), the RF N-path bandpass filters [23,25,26] and the mixer-first receivers [27,28] directly attenuate the OB blocker at the input resulting in an excellent blocker tolerance; however, for systems where there are strict emission limits, LO leakage can be a potential problem. Also, large capacitors are required to achieve narrow-band filtering due to the relatively small source impedance. Since the OB attenuation at the RF input node ( $V_{in}$  in Fig. 3.1(a)) is limited to the ratio of  $R_{on}/(R_{on}+R_s)$ , where  $R_{on}$  is the switch-on resistance, small  $R_{on}$  is also

required. These filters further exhibit spurious responses [23] at the harmonics of the LO signal which result in poor OB linearity. Preceding the NPF with an active LNA (Fig. 3.1(b)) [35,36] offers reverse isolation and reduces the LO leakage. Also, the LNA output impedance is larger than the 50  $\Omega$  source resistance, which reduces the capacitor sizes and relaxes the switch R<sub>on</sub> requirement. However, those receivers still have harmonic responses at the LNA output which reduce the blocker tolerance for blocking signals close to the LO harmonic frequencies. Various harmonicrejection mixing techniques [36, 59-62] have been proposed. Using harmonic recombination in baseband [36] achieves a good harmonic rejection ratio (HRR), but the harmonic attenuation at the LNA output is not improved. The current-driven passive mixer and two-stage harmonic rejection approach in [59] shows high HRR and good OB linearity. However, it offers only a moderate blocker 1 dB compression point (B1dB) at low blocker offset frequencies. The harmonic-rejection TIAs proposed in [62] reduce the harmonic down-conversion after the baseband TIA for mixer-first receivers and current-driven mixers, though the harmonic down-conversion before the TIA cannot be eliminated using this technique. In [63] a bandpass filter without 3<sup>rd</sup> harmonic response was proposed and its operation and performance was evaluated in simulation. However, that approach cannot suppress the harmonic response before the recombination.

We propose a harmonic-rejecting N-path filter (HR-NPF) which reduces the harmonic responses at the 3<sup>rd</sup> and 5<sup>th</sup> LO harmonics (Fig. 3.1(c)) [64]. The active LNA provides a lower than -90 dBm LO leakage and high source impedance for the NPF. The harmonic responses are strongly attenuated by the HR-NPF, which improves the LNA blocker tolerance at LO harmonic frequencies. A receiver front-end prototype using the HR-NPF achieves a -2.4 dBm B1dB at only a

**Figure 3.1:** (a) Conventional N-path filter. (b) Conventional N-path filter with LNA. (c) Proposed harmonic rejecting N-path filter with LNA

20 MHz blocker frequency offset, and the B1dB remains high at LO harmonics. The HR-NPF also offers additional harmonic rejection for the down-conversion to achieve the two-stage harmonic rejection with >51 dB HRR at the 3<sup>rd</sup> and 5<sup>th</sup> LO harmonics without calibration.

The concept and analysis of the HR-NPF are developed in Section 3.2. The RF receiver with an HR-NPF and the circuit implementation are described in Section 3.3. Section 3.4 provides the measurement results, and conclusions are presented in Section 3.5.

# 3.2 Harmonic-rejecting N-path filter

An NPF is a continuous-time switched-capacitor bandpass filter driven by N-phase 1/N-duty-cycle nonoverlapping clocks, which is well analyzed in [23–25]. Due to the time-varying nature of the

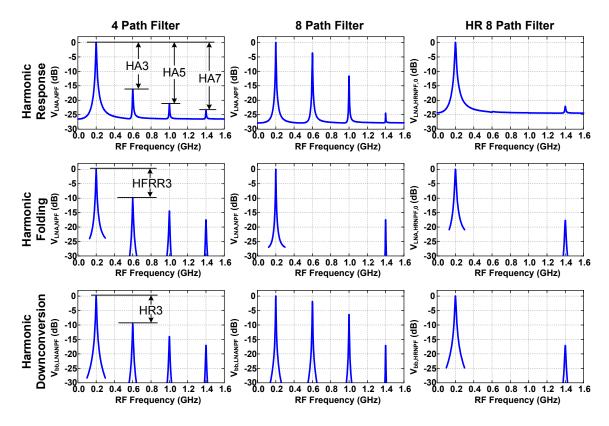

**Figure 3.2:** Simulated harmonic response (top row), harmonic folding (middle row), and harmonic down-conversion (bottom row) in 4-path filter (left column), 8-path filter (middle column) and proposed harmonic-rejecting 8-path filter (right column) for a 0.2 GHz clock frequency.

NPF, there are several frequency translation issues in the NPF compared to the linear-time-invariant (LTI) filter. Using a differential architecture helps to mitigate the issues due to even order harmonic. In this section, we first discuss the harmonic folding, harmonic response, and harmonic down-conversion in a differential NPF, then show the analysis of the HR-NPF.

# 3.2.1 Harmonic response, harmonic folding, and harmonic down-conversion in a differential N-path filter

Fig. 3.2 shows the simulated harmonic response, harmonic folding and harmonic down-conversion of differential NPF with LNA (Fig. 3.1(b)) and proposed HR-NPF with LNA (Fig. 3.1(c)) for a  $250 \Omega$  LNA output resistor, a  $10 \Omega$  switch on-resistor, an  $80 \,\mathrm{pF}$  baseband capacitor, and a  $0.2 \,\mathrm{GHz}$  clock frequency. These effects in an NPF are well analyzed in [24]. Considering the signal at LNA output, the harmonic response is the bandpass filtering function around the clock harmonics (top row in Fig. 3.2). The harmonic attenuation (HA) is the ratio of the gain at desired signal frequency to the gain at clock harmonics. The HA of an NPF is

$$HA_{i} = \frac{sinc^{2}\left(\frac{\pi}{N}\right)}{sinc^{2}\left(\frac{i\pi}{N}\right)}, \ (i = odd), \tag{3.1}$$

where i is the order of clock harmonic, N is the number of paths in the NPF, and sinc(x) = sin(x)/x. Low HA degrades the blocker tolerance at the clock harmonics.

The folding of unwanted signals from clock harmonics to the desired signal band at the LNA output is called harmonic folding (middle row in Fig. 3.2). The harmonic folding rejection ratio (HFRR) is the gain ratio of desired RF signal to the signal folded from clock harmonics, which is

$$HFRR_{i} = \frac{sinc\left(\frac{\pi}{N}\right)}{sinc\left(\frac{i\pi}{N}\right)}, \ (i = kN - 1, k \in \mathbf{Z}). \tag{3.2}$$

Since the RF signal is down-converted to the baseband capacitor, the NPF can also be used

as a down-converter. The down-converting of unwanted RF signals at clock harmonics is called harmonic down-conversion, which reduces the SNR for the desired signal. Also, the blockers at clock harmonics can be amplified, and saturate the baseband circuits. The harmonic-rejection ratio (HRR) is the ratio of the conversion gain for the desired signal to that for the signals at clock harmonics, which is

$$HRR_i = \frac{sinc\left(\frac{\pi}{N}\right)}{sinc\left(\frac{i\pi}{N}\right)}, \ (i = odd).$$

(3.3)

In the NPF, harmonic folding can be reduced by using more paths. Compared to a 4-path filter, in an 8-path, the harmonic folding from the 3<sup>rd</sup> and 5<sup>th</sup> clock harmonics filter is reduced (Fig. 3.2); however, the harmonic response is worse than that of a 4-path filter. The HA3 of an 8-path filter is only around 4 dB which is much higher than the 19 dB HA3 in a 4-path filter, and can reduce the blocker tolerance at that clock harmonic. Moreover, the HR3 of an 8-path filter is only 2 dB which is worse than the 10 dB HR3 in a 4-path filter.

In our proposed harmonic-rejecting 8-path filter (right column in Fig. 3.1), the harmonic folding is improved by employing more paths, and the harmonic response and the harmonic down-conversion are also improved. For a wideband receiver with a frequency range of 0.2-1 GHz, the HR-8PF improves the blocker tolerance at clock harmonics across the whole frequency range, since the 7<sup>th</sup> order harmonic for the lowest clock frequency 0.2 GHz is 1.4 GHz which is out of the desired input frequency range.

**Figure 3.3:** A simplified model for the harmonic response analysis for a differential NPF at the output of the LNA; the LNA is modeled with a Norton equivalent (a) For a conventional 8-path filter, the signals at  $f_{clk}$  and  $3f_{clk}$  are down-converted then up-converted to RF input resulting in harmonic responses. (b) In the proposed harmonic-rejecting 8-path filter, the harmonic down-conversion from  $3f_{clk}$  is rejected by the effective LO, and the harmonic responses are improved. (Note that the gain and bandwidth of the HR-8PF is different from conventional 8PF)

## 3.2.2 Analysis of the harmonic-rejecting N-path filter

Fig. 3.3 shows the simplified operation of the NPF and the proposed HR-NPF. In a conventional 8-path filter with an LNA, the RF signal is first down-converted to the baseband capacitors, then up-converted back to the LNA output as shown in Fig. 3.3(a). The total frequency response consists of transfer functions due to the fundamental of the clock  $H_1(f)$ ,  $3^{rd}$  order harmonic of the clock  $H_3(f)$ , and finite on-resistance  $H_{SW}(f)$ . In the proposed HR-8-path filter, the  $3^{rd}$  order clock harmonic is rejected during down-conversion by combining the outputs of 3 LNAs with scaled transconductance (Fig. 3.3(b)). Thus the filter transfer function due to the  $3^{rd}$  order clock harmonic  $(H_3(f))$  is removed, and the harmonic attenuation is limited only by switch  $R_{on}$ .

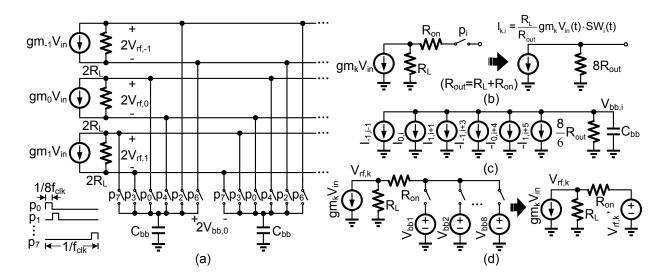

To calculate the transfer function of the HR-NPF, we use the similar approach in [26]. Fig. 3.4(a)

**Figure 3.4:** (a) A differential harmonic rejecting N-path filter with non-overlapping clocks. (b) An equivalent circuit of the LNA with a switch. (c) For one baseband capacitor, the currents from all the LNAs generate the baseband voltage  $V_{bb,i}$ . (d) All the baseband voltages are up-converted to the LNA output.

shows a differential harmonic-rejecting 8-path filter (HR-8PF). The switches driven by  $p_i$  and  $p_{i+4}$  share the same baseband capacitor to eliminate the even-order harmonic responses [24]. To analyze the transfer function  $V_{rf,k}/V_{in}$ , the LNAs are modeled as transconductors (Gms) with finite output impedance and  $gm_k = gm \cdot cos(k\pi/4)$  ( $k = \{-1,0,1\}$ ), while the switches are modeled as ideal switches with finite on-resistance. We first find the baseband voltage on one capacitor  $C_{bb}$ , then calculate the LNA output voltage using the superposition of  $V_{in}$  and  $V_{bb,k}$ .

The Gm with one switch can be modeled as a time-varying Gm with finite output resistance as shown in Fig. 3.4(b) [26] since in each time slot only one switch is turned on for each Gm. Since the switching function  $SW_i$  is

$$SW_i(t) = \sum_{n = -\infty}^{+\infty} a_n e^{-j\frac{n\pi}{4}i} e^{jn\omega_{clk}t},$$

(3.4)

where  $a_n = sinc(n\pi/8)/8 \cdot exp(-jn\pi/8)$ , the equivalent Gm current with one switch (Fig.3.4(b)) in frequency domain can be written as

$$I_{k,i}(\omega) = \frac{R_L}{R_{out}} g m_k \sum_{n=-\infty}^{+\infty} a_n e^{-j\frac{n\pi}{4}i} V_{in}(\omega - n\omega_{clk}), \qquad (3.5)$$

where  $R_{out}=R_L+R_{on}$ . The RF current is down-converted to the baseband by the  $n^{th}$  clock harmonic. The load resistor is  $8\cdot R_{out}$ , since the duty cycle of the clock is 1/8. For each  $C_{bb}$ , the current from 6 Gms are summed up and generate the baseband voltage  $V_{bb,i}$  shown in Fig. 3.4(c). The load resistor is  $8/6\cdot R_{out}$ . The baseband voltage is:

$$V_{bb,i}(\omega) = [I_{-1,i-1}(\omega) + I_{0,i}(\omega) + I_{1,i+1}(\omega) - I_{-1,i+3}(\omega) - I_{0,i+4}(\omega) - I_{1,k+5}(\omega)] \cdot Z_{bb}(\omega), \quad (3.6)$$

where  $Z_{bb}$  is the equivalent baseband impedance, which is  $R_{bb}/(1+j\omega R_{bb}C_{bb})$  ( $R_{bb}=4R_{out}/3$ ). The down-conversion from even order,  $3^{rd}$ , and  $5^{th}$  order clock harmonic frequencies are rejected since the Gms are scaled to the ratio of  $0:1:\sqrt{2}:1:0:-1:-\sqrt{2}:-1$  in the different time intervals as in a harmonic rejection mixer. Since  $gm_k=gm\cdot\cos(k\pi/4)$ , the baseband voltage can be derived as:

$$V_{bb,i}(\omega) = \sum_{n=-\infty}^{+\infty} 4a_n e^{-j\frac{n\pi}{4}i} \frac{R_L}{R_{out}} gmV_{in}(\omega - n\omega_{clk}) Z_{bb}(\omega), \ (n = 8l \pm 1, \ l \in \mathbf{Z}).$$

(3.7)

The output voltages of three LNAs can be considered as a superposition of the input Gm and the

up-converted  $V_{bb,i}$  (Fig. 3.4(d)). The up-converted part  $V_{rf,k}^{\prime}$  is

$$V'_{rf,k}(\omega) = \sum_{m=-\infty}^{+\infty} \sum_{n=-\infty}^{+\infty} 32a_m a_n \frac{R_L}{R_{out}} gm V_{in}(\omega - (m+n)\omega_{clk}) Z_{bb}(\omega - m\omega_{clk}) e^{j\frac{n\pi}{4}k},$$

$$(m+n=8q, m=odd, n=8l\pm 1, l, q \in \mathbf{Z}).$$

$$(3.8)$$

The desired signal frequency is  $\omega_{clk} + \omega_{bb}$ , so only the signals from  $(1-8q)\omega_{clk} + \omega_{bb}$  will be folded into desired signal band. Since the 3<sup>rd</sup> and 5<sup>th</sup> clock harmonics are rejected during down-conversion, the HR-8PF doesn't have those harmonic responses. Ignoring the harmonic folding, the transfer functions for the k<sup>th</sup> LNA can be written as:

$$\frac{V_{rf,k}(\omega)}{V_{in}(\omega)} = \cos\left(\frac{k\pi}{4}\right) gmR_{on} ||R_L + \left(\frac{R_L}{R_{out}}\right)^2 \sum_{m=-\infty}^{+\infty} 32|a_m|^2 gmZ_{bb}(\omega - m\omega_{clk}) e^{-j\frac{m\pi}{4}k},$$

$$(m = 8l \pm 1, l \in \mathbf{Z}).$$

(3.9)

The transfer function only has bandpass filtering around  $(8l\pm1)\omega_{clk}$ ; the  $3^{rd}$  and  $5^{th}$  clock harmonic responses are rejected. Assuming the LNA output resistance is much larger than the switch on-resistance  $(R_L\gg R_{on})$ , the bandwidth of the bandpass transfer function is  $3/(2\pi R_L C_{bb})$ , the in-band (IB) gain is  $128/3 \cdot |a_1|^2 gm R_L$  and the OB gain is  $\sin(k\pi/4) gm R_{on}$ . Although the Gms in the three LNA branches are different, The IB gain of all the three branches are the same since the gain is determined by the up-converted voltage  $V'_{rf,k}$  and for each branch the  $V'_{rf,k}$  has the same amplitude but a different phase shift. Compared with an NPF directly connected to the RF input, to achieve the same baseband bandwidth with the LNA, a smaller capacitor can be used result-

**Figure 3.5:** The calculated (using (3.9)) and simulated transfer function of the HR-8PF with an  $R_{on}$  of (a)  $1 \text{ m}\Omega$  and (b)  $10 \Omega$ .

ing in a smaller chip area, since the LNA  $R_L$  is much larger than the  $50\,\Omega$  RF source impedance. Additionally, larger OB attenuation can be achieved due to a larger  $R_L/R_{on}$  ratio.

The HR-NPF can be modeled as an RLC tank in series with  $R_{on}$  as conventional NPF [23]. The equivalent RLC values are:  $R_m = 32|a_1|^2R_{bb}$ ,  $C_m = C_{bb}/64|a_1|^2$ ,  $L_m = 1/(C_m\omega_{clk}^2)$ . Fig. 3.5(a) shows the calculated and behavioral-level simulated transfer function of the three LNA outputs (Fig. 3.3(a)) as well as the RLC model for the middle LNA branch. The switches are driven by a 200MHz 8-phase non-overlapping clock, and gm=30 mS,  $R_L$ =250  $\Omega$ ,  $R_{on}$ =1m  $\Omega$ ,  $C_{bb}$ =80 pF. The simulated transfer function matches the calculation using (3.9) very well. The frequency response of the HR-8PF is very close to an RLC filter and the center frequency is tunable. The difference of the different LNA outputs is caused by the phase shift in the up-converted voltage  $V'_{rf\,k}$ .

To compare the HR-8PF (Fig. 3.1(c)) with a conventional 8PF (Fig. 3.1(b)), we assume that they have the same total LNA transconductance  $gm_{LNA}$ , that the LNA/sub-LNA load resistors of

8PF and HR-8PF are that  $R_{L,LNA}$  and  $3R_{L,LNA}$  respectively, that the baseband capacitors are  $C_{bb}$ , that the OB attenuation of the HR-8PF middle branch and 8PF are the same, and  $R_{L,LNA}\gg R_{on}$ . The sub-LNA in the middle branch of the HR-8PF has a gm of  $gm_{LNA}/(1+\sqrt{2})$ , thus the gain and  $R_{on}$  of HR-8PF are  $2/(1+\sqrt{2})$  and  $1/(1+\sqrt{2})$  times that of the 8PF respectively. The bandwidth of the HR-8PF is the same as 8PF. The LNA power of the two filters are the same since the have the same gm. Assuming the clock generator power is proportional to the total switch capacitance and the capacitance of a switch is proportional to  $1/R_{on}$ , the clock generator power of the HR-NPF is  $3/(1+\sqrt{2})$  times that of the 8PF.

#### 3.2.3 Second-order effects

#### Finite switch on-resistance

The finite switch on-resistance limits the OB attenuation of the HR-NPF. The HR-8PF OB attenuation can be derived as  $20\log(128|a_1|^2R_L/[3R_{on}\sin(k\pi/4)])$  for the  $k^{th}$  LNA branch from (3.9). Fig. 3.5(b) shows the calculated and simulated transfer function of the HR-8PF with  $R_{on}$ =10  $\Omega$ . The transfer curve of the LNA branch #-1 skews to the right while that of the LNA branch #1 skews to the left at low frequency offset due to the phase shift in the up-converted voltage  $V'_{rf}$ . At larger frequency offset, the OB attenuation of those two branches is limited by the switch  $R_{on}$  as expected.

#### Parasitic capacitors

In a real circuit, the LNA and switches have parasitic capacitors. The switch capacitor at the baseband side can be considered a part of  $C_{bb}$ . The parasitic capacitor at the output of the LNA will shift the filter center frequency and increase the in-band loss as discussed in [26].

#### Mismatch between the branches

In an ideal HR-8PF, no RF currents around the  $3^{rd}$  and  $5^{th}$  clock harmonics are down-converted to the baseband capacitors, and the harmonic responses are fully eliminated. However, in a real circuit, the cancellation of the harmonic components of the effective clock is limited by the gain and phase errors between the three branches. The finite  $R_{on}$  also limits the harmonic attenuation. Defining  $HA'_{HR}$  as the harmonic attenuation ( $1\sigma$ ) of the HR-8PF due to harmonic mixing and using the derivation in [59],  $HA3'_{HR}$  and  $HA5'_{HR}$  of a HR-8PF can be written as:

$$HA3'_{HR} = 3 \frac{\sin^2\left(\frac{\pi}{8}\right)}{\sin^2\left(\frac{3\pi}{8}\right)} \left[ \left(\frac{\sigma_A}{12}\right)^2 + \left(\frac{\sigma_\phi}{4}\right)^2 \right]^{-1/2}$$

$$HA5'_{HR} = 5 \frac{\sin^2\left(\frac{\pi}{8}\right)}{\sin^2\left(\frac{5\pi}{8}\right)} \left[ \left(\frac{\sigma_A}{20}\right)^2 + \left(\frac{\sigma_\phi}{4}\right)^2 \right]^{-1/2}$$

(3.10)

where  $\sigma_A$  and  $\sigma_{\phi}$  are the standard deviations of gain and phase errors. The HA3 $^\prime_{HR}$  is 30 dB for a  $\sigma_A = 10\%$  and  $\sigma_{\phi} = 3^\circ$ , which is better than the HA3 caused by a  $10\,\Omega$  R $_{on}$  and a  $250\,\Omega$  R $_{L}$  (around 25 dB). Thus, the OB attenuation at  $3^{rd}$  and  $5^{th}$  order clock harmonics is mainly limited by the finite switch R $_{on}$  and can be as good as for other OB frequencies.

#### Clock leakage

Generally, for an RF receiver, the asymmetric baseband circuit DC offset and charge coupling mainly generate the clock leakage [65]. Considering the circuit in Fig. 3.1(b) as a differential RF receiver with an 8-phase mixer, for the receivers using baseband trans-impedance amplifier (TIA), the TIA input DC offset can be up-converted to  $8f_{clk}$  and its harmonics by the switches. However, if the DC offsets of each  $V_{bb}$  are not symmetric or the clock signal has mismatch, the clock leakage will appear at  $f_{clk}$ . The clock charge injection is caused by the parasitic capacitor between the clock trace and the RF trace. It generates clock coupling due to the asymmetric parasitic capacitor or the clock signal mismatch.

In this work, the baseband capacitors are connected to the gate of Gm cells, and the Gm is biased by the LNA outputs. Thus, the DC offset of the Gm cell input is much smaller than TIA. To reduce the clock charge injection, the clock traces should not overlap with the RF traces in the layout, thereby reducing the parasitic capacitance.

The reverse isolation of the LNA also helps to reduce the clock leakage. For the receivers using feedback LNA, the clock leakage is limited to around -80 dBm [66], since the feedback path limits the LNA reverse isolation. In this work, noise canceling LNA is used, and a cascode device helps to improve the reverse isolation.

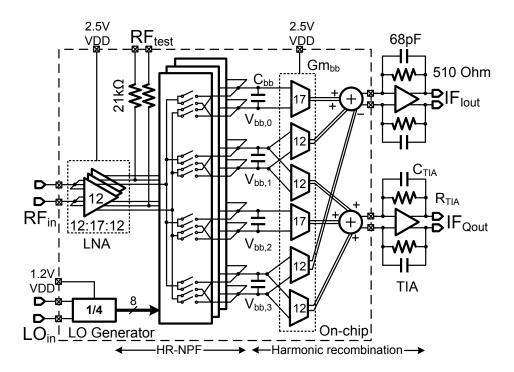

Figure 3.6: Architecture of the blocker tolerant RF receiver

# 3.3 RF receiver with harmonic rejecting N-path filter

#### 3.3.1 RF front-end architecture

The architecture of the RF front-end prototype IC (Fig. 3.6) consists of a broadband LNA with HR-NPF, baseband Gms, and an LO generator. All the switches in the HR-NPF are driven by 8-phase nonoverlapping LO signals as the clock. The HR-NPF provides bandpass filtering with reduced harmonic responses at LNA outputs. Also, the RF signal is down-converted to the baseband capacitors in the HR-NPF with harmonic rejection. Since the down-converted voltage  $V_{bb,i}$  has a phase shift  $exp(-jn\pi i/4)$  for the  $n^{th}$  order LO down-conversion, the baseband Gms combine the baseband voltages with the gm factor of  $sin(i\pi/4)$  to realize a two-stage harmonic rejection architecture [59] and form in-phase and quadrature currents that drive off-chip TIAs. The conversion

gain of the receiver is

$$CG = \frac{V_{IF}}{V_{in}} = \frac{\left(V_{bb,i-1}/\sqrt{2} + V_{bb,i} + V_{bb,i+1}/\sqrt{2}\right)gm_{bb}R_{TIA}}{V_{in}}$$

$$= \frac{4}{3}sinc\left(\frac{\pi}{8}\right)gmR_{L}gm_{bb}R_{TIA},$$

(3.11)

where gm is the transconductance of the LNA and gm<sub>bb</sub> is the transconductance of baseband Gm both with a gm factor of 1,  $R_L$  is the LNA load resistance, and  $R_{TIA}$  is the feedback resistance in the TIA. The ideal 1:  $\sin(\pi/4)$  gm ratio is approximated as 17:12 in the LNA and baseband Gms. Generally the HRR of a receiver is limited by the gain error of the Gm and the LO phase error. In the two-stage harmonic rejection approach the overall relative gain error is the product of the relative errors for the LNA and baseband Gms [59]. The gain error is negligible and the HRR is limited by the LO phase error, so that a high HRR can be achieved. Compared with HRR calibration techniques [36], two-stage harmonic rejection can achieve high HR3 and HR5 simultaneously. The HRR further helps to reduce the mixer noise figure thanks to the reduction of noise folding.

## 3.3.2 Circuit implementation

Fig. 3.7(a) shows the schematic of the fully differential LNA which is split into 3 sections with relative sizes of 12:17:12. All sections are joined together at the inputs.  $M_1 - M_4$  is a current-reuse common-gate (CG) stage and  $M_5 - M_8$  is a current-reuse common-source (CS) stage. The total gm of the CG stage is 20 mS to achieve the 50  $\Omega$  impedance matching at each input. Current re-use improves the current efficiency and the gm ratio of the CS and CG branches is 4:1 to achieve a low noise figure. The CG stages are biased with off-chip inductors to avoid the noise contribution

Figure 3.7: Schematic of (a) LNA and (b) baseband Gm cell

of an active current-source bias. The load resistor ratio is  $R_1:R_2=3:1$  and  $R_1+R_2$  is around 472  $\Omega$ . The output common mode is maintained at  $V_{DD}/2$  with an external regulator. The supply can vary from 1.8 V to 2.5 V and the cascode transistors guarantee a voltage drop smaller than 1V across each device at 2.5 V so that thin-oxide transistors can be used. The baseband capacitors  $C_{bb}$  (Fig. 3.6) have an effective 60 pF singled-ended capacitance and are realized with differential MIM capacitors and single-ended MOS capacitors.

The differential baseband Gm (Fig. 3.7(b)) also uses current-reuse and can operate from 1.8 V to 2.5 V.  $M_2$  and  $M_3$  are the input transistors with resistive source degeneration to improve linearity.  $M_1$  is a PMOS current source, while a common-mode feedback (CMFB) circuit drives the NMOS current source transistor  $M_4$  to maintain the output common mode voltage at  $V_{DD}/2$ . To ensure the common mode voltage tracks  $V_{DD}/2$  during power up, a soft-start LDO is used, and the LDO output ramp speed is lower than the speed of the CMFB circuit.

The LNA, switches, and Gm cells are DC coupled  $^1$  (Fig. 3.6) to achieve higher OB linearity at low RF frequencies as in [36]. The DC coupling sets the source/drain voltage of the switch transistors to the LNA and Gm common mode, i.e.  $V_{DD}/2$ , which can be as high as 1.25 V. The NMOS switch transistors are placed in a deep N-well and their body and source are connected together to keep source, drain, and body at the same DC voltage. The  $1.2\,V_{pp}$  LO signal is AC coupled to the gates of the switches, and the gate bias voltage is  $V_{DD}/2$ . The voltage drop across all transistor terminal pairs is then not larger than the supply voltage (1.2 V) of the LO signal, and thin-oxide switch transistors can be used. The on-resistance of each switch is around  $14\,\Omega$ .

#### 3.3.3 Improvement of out-of-band linearity

The HR-NPF improves the OB linearity of the receiver since it has low OB gain before the base-band circuit and it reduces the voltage swing at the LNA output to improve the LNA linearity. The cascade IIP3 for a receiver is  $1/A_{IIP3,tot}^2 = 1/A_{IIP3,LNA}^2 + G_{LNA}^2/A_{IIP3,BB}^2$  [67]. For the IB linearity, the baseband circuit is the bottleneck due to the large LNA gain. With the HR-NPF, the OB gain at the baseband capacitor is already reduced (Fig. 3.6), and the harmonic down-conversion from  $3^{rd}$  and  $5^{th}$  order LO harmonics is also rejected, thus the baseband circuit will not limit the OB linearity, so that the LNA linearity becomes the bottleneck. The low OB impedance of the HR-NPF also helps to improve the LNA output linearity. Fig. 3.8 shows the transistor-level simulated IIP3 and P1dB versus load impedance for the LNA in Fig. 3.7(a). The LNA is driven by a port with a  $1:\sqrt{2}$  balun, and the linearity is measured at the differential outputs of the LNA branch with a gm factor

<sup>&</sup>lt;sup>1</sup>However when using DC coupling, the LNA IM2 products and flicker noise may leak to into baseband circuits.

**Figure 3.8:** Transistor simulated IIP3 and B1dB versus LNA load impedance for the LNA with a gm factor of 17.

of 17. The small signal linearity (IIP3) and the large signal linearity (P1dB) are both improved with lower LNA load impedance as shown in Fig. 3.8(b). The P1dB improves more than the IIP3 with lower impedance since the LNA output will be clipped with a large input signal and high voltage.

## 3.3.4 Noise analysis

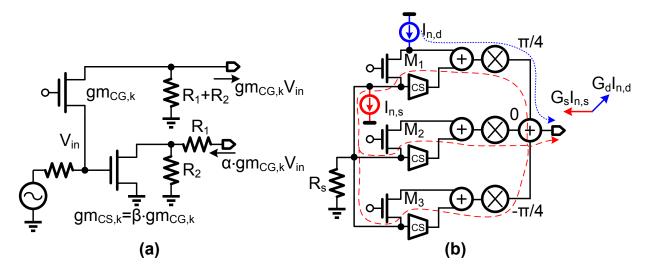

Noise-cancelling LNAs (NC-LNA) [19, 20] are widely used to achieve a low noise by cancelling the noise from their common-gate (CG) transistor. However, if we split the NC-LNA into several branches to achieve the harmonic rejection, the CG noise cannot be fully canceled. In this section we analyze the NC-LNA (Fig. 3.7(a)) in the harmonic rejection receiver (Fig. 3.6). The simplified circuit of the  $k^{th}$  branch of the LNA is shown as Fig. 3.9(a).  $gm_{CG,k}$  and  $gm_{CS,k}$  are the transconductances of the CG and common-source (CS) branchs, and

$$gm_{CG,k} = \frac{gm_{CG} \cdot \cos(k\pi/4)}{\sum_{i=-1}^{1} \cos(i\pi/4)}, gm_{CS,k} = \beta gm_{CG,k}.$$

(3.12)

**Figure 3.9:** (a) Simplified model of the noise-cancelling LNA. (b) Noise cancelling in a harmonic rejection mixer.

The output currents of these two branches are  $gm_{CG,k}V_{in}$  and  $\alpha gm_{CG,k}V_{in}$ , where  $\alpha=\beta R_2/(R_1+R_2)$ . Thus, the conversion gain can be written as

$$CG = \frac{2}{3} \cdot sinc(\frac{\pi}{8})(1+\alpha)\eta_{gm} \cdot gm_{CG}R_Lgm_{bb}R_{TIA}, \qquad (3.13)$$