# ${\it Combined~C-V/I-V~and~RTN~CMOS~Variability} \\ {\it Characterization~Using~An~On-Chip~Measurement~System}$

Simeon Dimitrov Realov

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

2012

©2012

Simeon Dimitrov Realov

All Rights Reserved

## Abstract

# Combined C-V/I-V and RTN CMOS Variability Characterization Using An On-Chip Measurement System

## Simeon Dimitrov Realov

With the number of transistors integrated into a single integrated circuit (IC) crossing the one-billion mark and complementary metal-oxide-semiconductor (CMOS) technology scaling pushing device dimensions ever-so-close to atomic scales, variability in transistor performance is becoming the dominant constraint in modern-day CMOS IC design. Developing novel approaches for device characterization, which allow a detailed study of electrical transistor characteristics across large statistical sample sets, is crucial for the proper identification, characterization, and modeling of different physical sources of device variability. On-chip characterization methodologies have the potential to address all of these issues by enabling the characterization of large statistical device sample sets, while also allowing for high measurement quality and throughput.

In this work, a fully-integrated system for on-chip combined capacitance-voltage (C-V) and current-voltage (I-V) characterization of a large integrated test transistor array implemented in a 45-nm bulk CMOS process is presented. On-chip I-V characterization is implemented using a four-point Kelvin measurement technique with 12-bit sub-10 nA current measurement resolution, 10-bit sub-1 mV voltage measurement resolution, and sampling speeds on the order of 100 kHz. C-V characterization is performed using a novel leakage- and parasitics-insensitive charge-based capacitance measurement (CBCM) technique with atto-Farad resolution.

The on-chip system is employed in developing a comprehensive CMOS transistor variability characterization methodology, studying both random and systematic sources of quasi-static device variability. For the first time, combined C-V/I-V characterization of circuit-representative devices is demonstrated and used to extract variations in the underlying physical parameters of the device. Additionally, the fast current sampling capabilities of the system are used for the characterization of random telegraph noise (RTN) in small area devices. An automated methodology for the extraction of RTN parameters is developed, and the statistics of RTN are studied across device type, bias, and geometry.

## Contents

| List of | Figur  | es                                   | iv   |

|---------|--------|--------------------------------------|------|

| List of | `Table | ${f s}$                              | vii  |

| Ackno   | wledgr | nents                                | viii |

| Chapt   | er 1 I | Introduction                         | 1    |

| 1.1     | Thesis | s Outline                            | 2    |

| Chapt   | er 2 I | Background                           | 4    |

| 2.1     | Introd | luction                              | 4    |

| 2.2     | CMO    | S Basics                             | 4    |

|         | 2.2.1  | CMOS Technology                      | 4    |

|         | 2.2.2  | The Appeal of CMOS                   | 5    |

| 2.3     | CMO    | S Variability                        | 8    |

|         | 2.3.1  | Historical Perspective               | 9    |

|         | 2.3.2  | Impact of CMOS Variability           | 10   |

|         | 2.3.3  | Classification of CMOS Variability   | 10   |

|         | 2.3.4  | Sources of Systematic Variability    | 11   |

|         | 2.3.5  | Sources of Random Variability        | 11   |

|         | 2.3.6  | Modeling Random Variability          | 16   |

| 2.4     | Metho  | ods for Variability Characterization | 17   |

|         | 2.4.1  | Ring Oscillators                     | 18   |

|        | 2.4.2  | Device Simulation and Imaging Techniques | 19 |

|--------|--------|------------------------------------------|----|

|        | 2.4.3  | Electrical Device Characterization       | 21 |

|        | 2.4.4  | Proposed Approach                        | 23 |

| Chapte | er 3 ( | On-Chip Characterization System          | 25 |

| 3.1    | Introd | uction                                   | 25 |

| 3.2    | System | n Overview                               | 25 |

| 3.3    | On-Cl  | nip Switching Matrix and DUT array       | 28 |

|        | 3.3.1  | DUT Array                                | 28 |

|        | 3.3.2  | Switch Design                            | 30 |

| 3.4    | Biasin | g DAC                                    | 32 |

| 3.5    | Measu  | rement Unit                              | 34 |

|        | 3.5.1  | Integrator Core                          | 37 |

|        | 3.5.2  | Current-Mode ADC                         | 44 |

|        | 3.5.3  | Voltage-Mode ADC                         | 47 |

|        | 3.5.4  | Analog Buffers                           | 49 |

| 3.6    | Test C | Chip                                     | 49 |

| 3.7    | Measu  | rement Setup                             | 50 |

| 3.8    | Conclu | usion                                    | 52 |

| Chapte | er 4 ( | Combined C-V/I-V Characterization        | 54 |

| 4.1    | Introd | uction                                   | 54 |

| 4.2    | Measu  | rement Techniques                        | 54 |

|        | 4.2.1  | I-V Measurements                         | 55 |

|        | 4.2.2  | C-V Measurements                         | 58 |

| 4.3    | Measu  | rement Results                           | 67 |

|        | 4.3.1  | Raw C-V/I-V Measurements                 | 67 |

|        | 4.3.2  | Parameter Extraction                     | 68 |

|        | 4.3.3  | $L_{eff}$ Extraction from C-V Data       | 69 |

|         | 4.3.4  | Analysis of Random Variability                                    | 73  |

|---------|--------|-------------------------------------------------------------------|-----|

|         | 4.3.5  | Analysis of Systematic Variability                                | 82  |

| 4.4     | Concl  | usion                                                             | 83  |

| Chapto  | er 5 I | Random Telegraph Noise Characterization                           | 86  |

| 5.1     | Introd | luction                                                           | 86  |

| 5.2     | Overv  | iew of RTN in Semiconductors                                      | 86  |

|         | 5.2.1  | Historical Perspective                                            | 87  |

|         | 5.2.2  | Source of RTN: Mobility vs. Carrier Density Modulation            | 88  |

|         | 5.2.3  | Multi-level RTN                                                   | 89  |

|         | 5.2.4  | Scaling Trends                                                    | 89  |

| 5.3     | Measu  | rement and Characterization of RTN                                | 90  |

|         | 5.3.1  | Measurement Approach                                              | 90  |

|         | 5.3.2  | Measurement Setup                                                 | 92  |

|         | 5.3.3  | Parameter extraction                                              | 94  |

| 5.4     | Statis | tical Modeling of RTN                                             | 105 |

|         | 5.4.1  | Statistics of Number of Traps, $N_T$                              | 107 |

|         | 5.4.2  | Statistics of Single-Trap Amplitude Fluctuations, $\Delta V_{th}$ | 110 |

|         | 5.4.3  | Complex CDF Model for Overall RTN Fluctuations                    | 115 |

| 5.5     | Concl  | usion                                                             | 120 |

| Chapte  | er 6 ( | Conclusion                                                        | 121 |

| 6.1     | Summ   | nary of contributions                                             | 121 |

| 6.2     | Future | e Work                                                            | 123 |

| Bibliog | graphy |                                                                   | 124 |

## List of Figures

| 2.1  | Cross-section of NMOS and PMOS devices                        | 5  |

|------|---------------------------------------------------------------|----|

| 2.2  | Moore's law                                                   | 7  |

| 2.3  | Line-edge roughness as source of variability in advanced CMOS | 14 |

| 2.4  | Mobility enhancement through channel stress in advanced CMOS  | 15 |

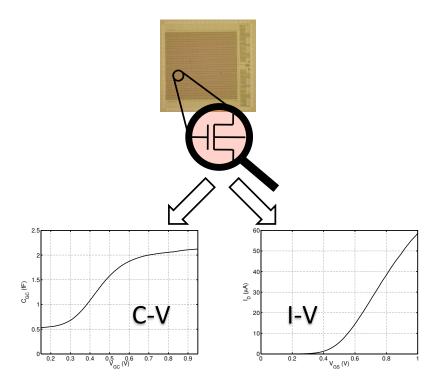

| 2.5  | Combined C-V/I-V characterization methodology                 | 23 |

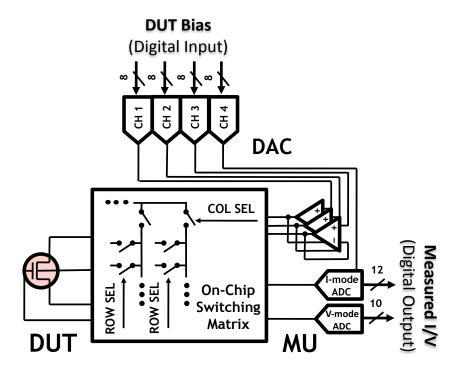

| 3.1  | On-chip characterization system schematic                     | 26 |

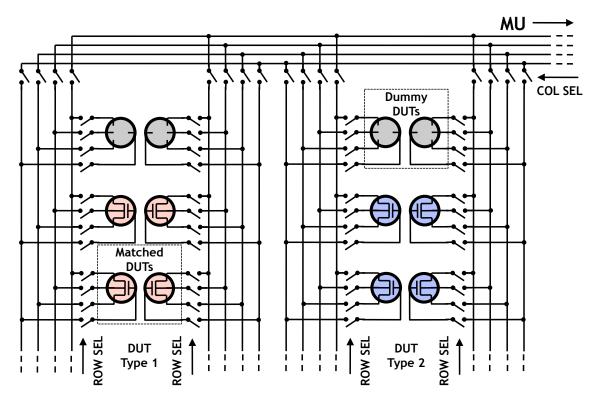

| 3.2  | DUT array schematic                                           | 29 |

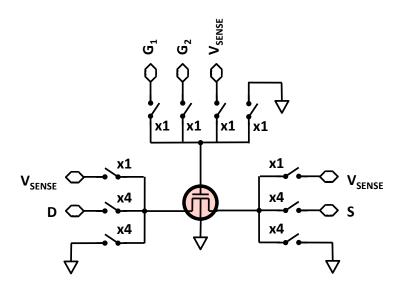

| 3.3  | DUT cell schematic                                            | 29 |

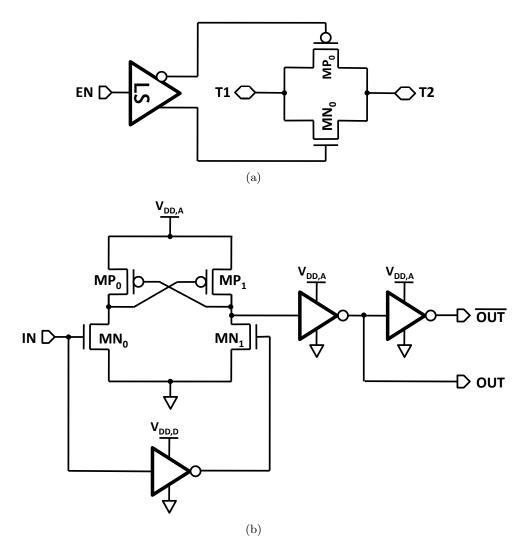

| 3.4  | CMOS transmission gate and positive-feedback level-shifter    | 31 |

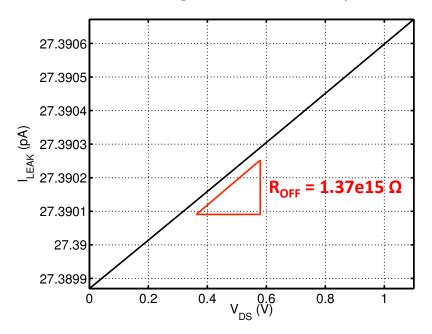

| 3.5  | Switch off-resistance simulation result                       | 32 |

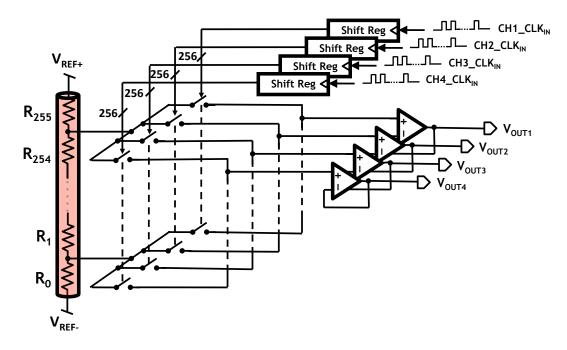

| 3.6  | Four-channel R-string DAC schematic                           | 33 |

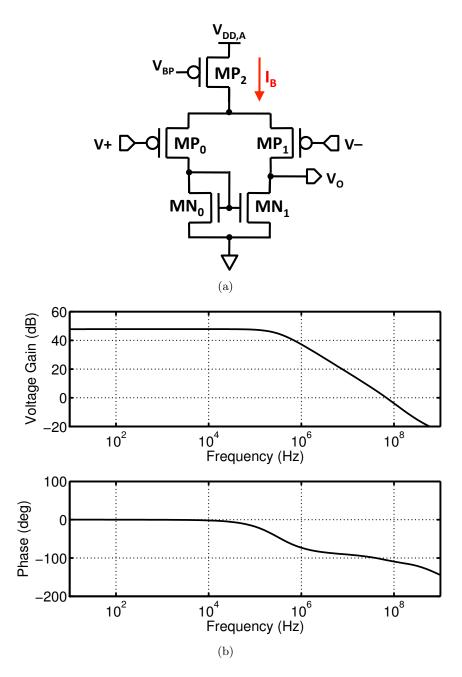

| 3.7  | DAC buffer schematic and simulation                           | 35 |

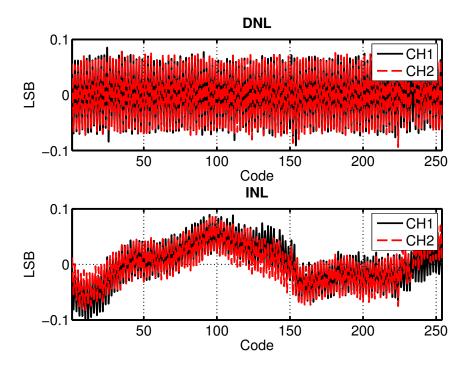

| 3.8  | DAC DNL/INL measurements                                      | 36 |

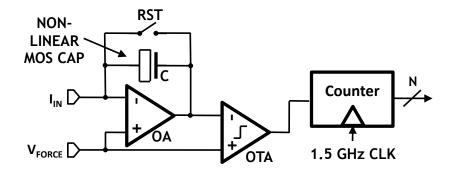

| 3.9  | Dual-slope integrator core schematic                          | 37 |

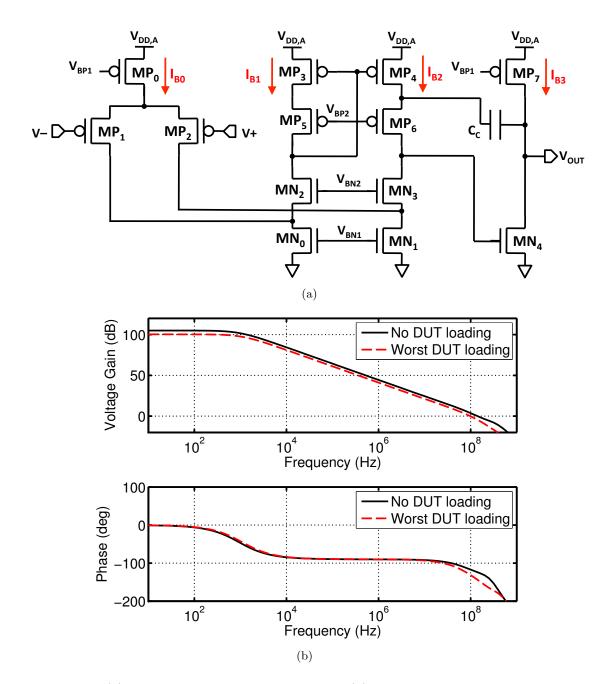

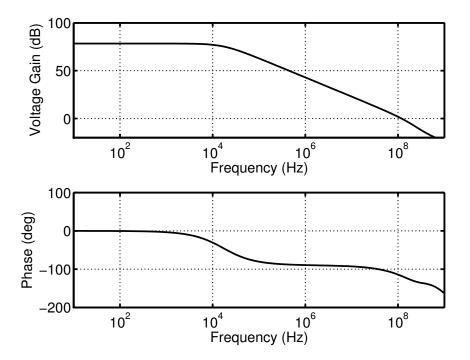

| 3.10 | Two-stage op-amp schematic and simulation result              | 39 |

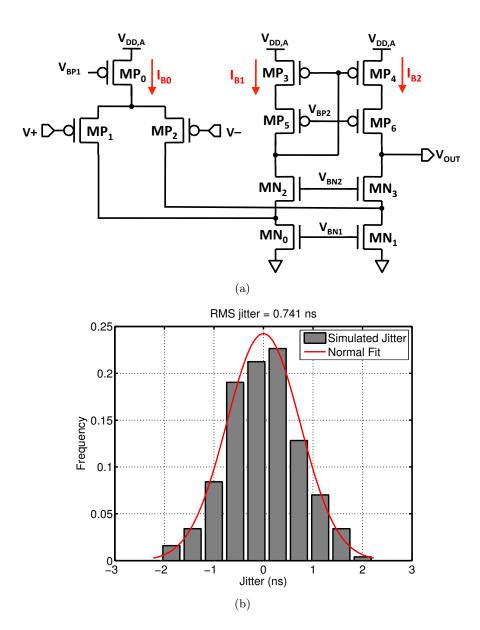

| 3.11 | Comparator schematic and simulation result                    | 42 |

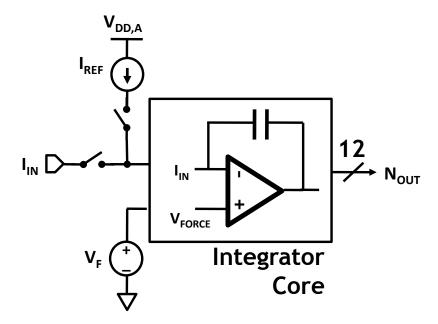

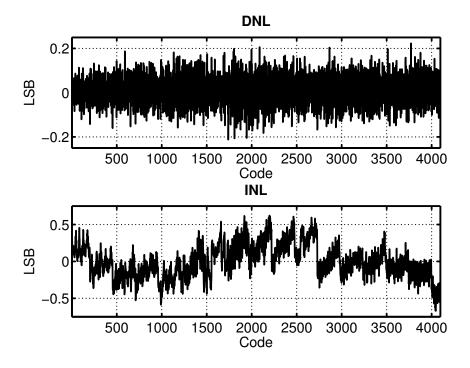

| 3.12 | Current-mode ADC schematic                                    | 44 |

| 3.13 | Current-mode ADC DNL/INL measurement                          | 46 |

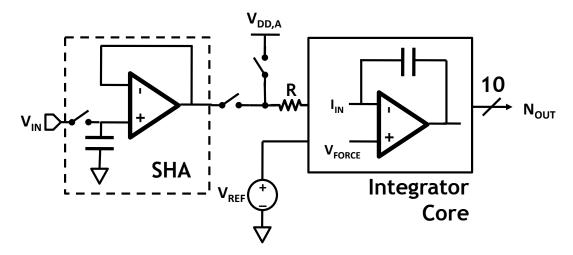

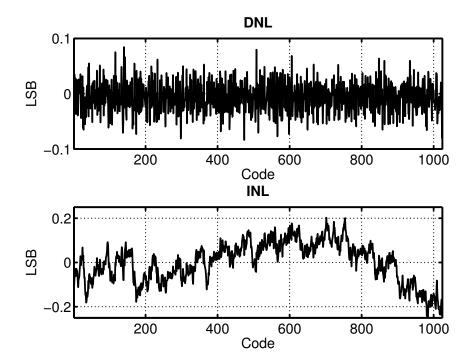

| 3.14 | Voltage-mode ADC schematic                                    | 47 |

| 3.15 | Voltage-mode ADC DNL/INL measurement                          | 48 |

| 3.16 | OTA buffer simulation result                                             | 50 |

|------|--------------------------------------------------------------------------|----|

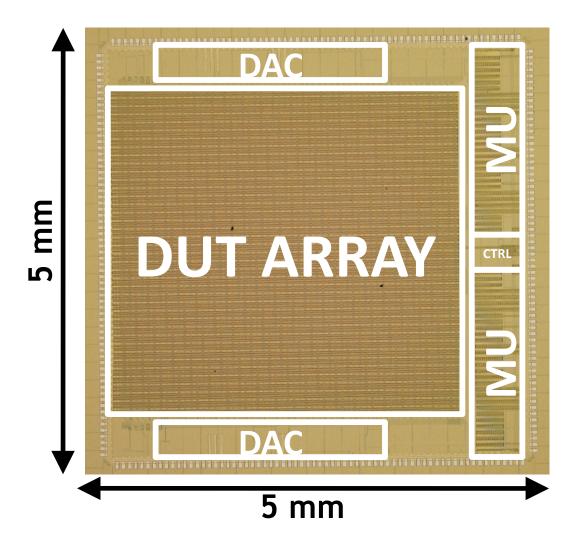

| 3.17 | Test chip micrograph                                                     | 51 |

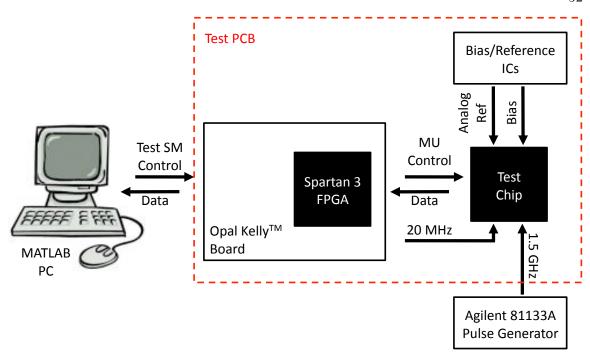

| 3.18 | Measurement setup                                                        | 52 |

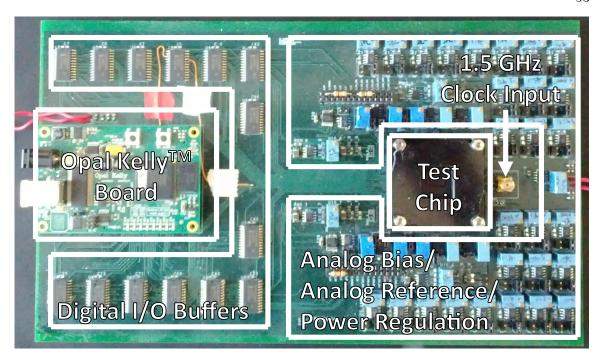

| 3.19 | Test PCB                                                                 | 53 |

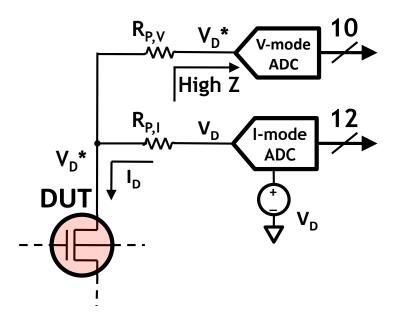

| 4.1  | On-chip Kelvin sensing measurement technique                             | 55 |

| 4.2  | Accurate I-V extraction using linear interpolation                       | 56 |

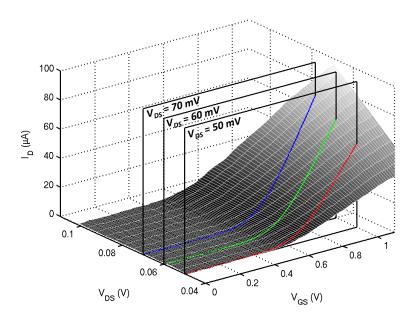

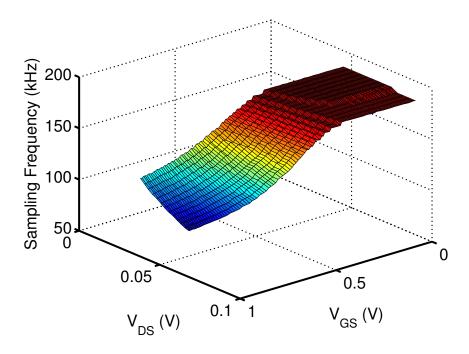

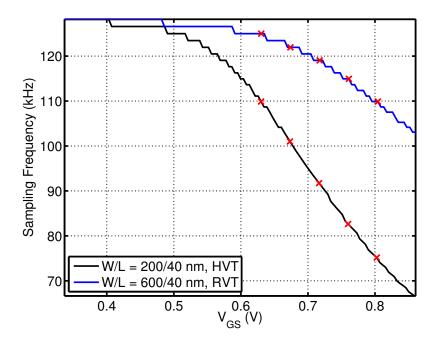

| 4.3  | Signal-strength-optimized sampling frequency                             | 58 |

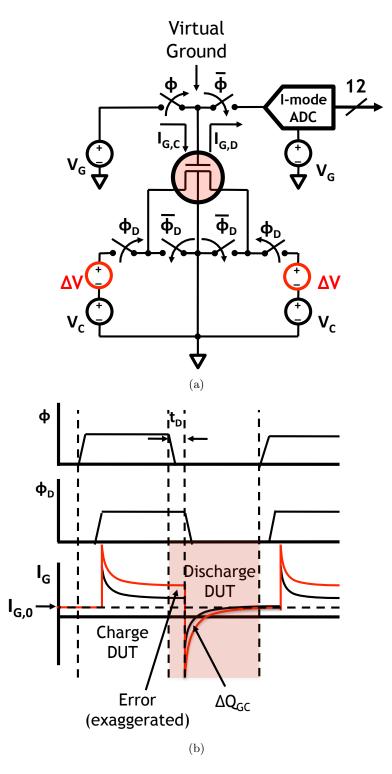

| 4.4  | CBCM technique for accurate C-V characterization                         | 60 |

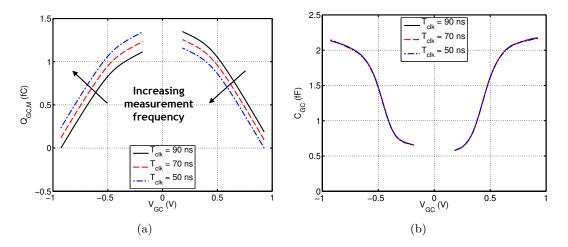

| 4.5  | Insensitivity of CBCM technique to measurement frequency                 | 62 |

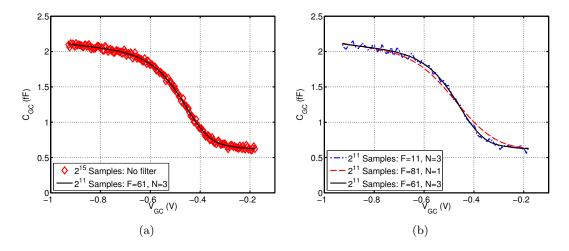

| 4.6  | Use of Savitzky-Golay digital filter for C-V data post-processing        | 64 |

| 4.7  | Suppression of $1/f$ noise in oversampled C-V measurements               | 65 |

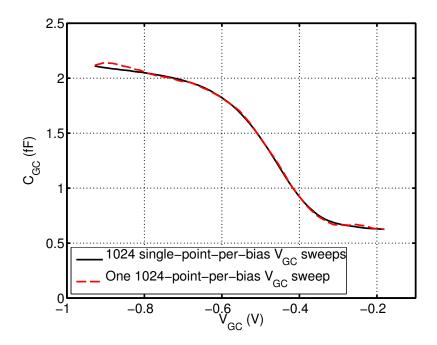

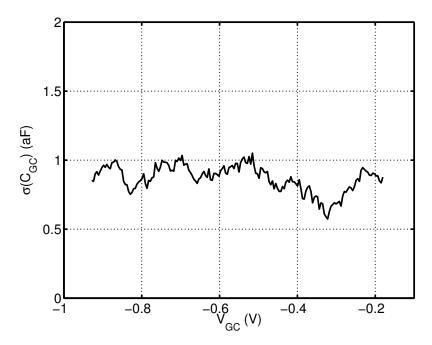

| 4.8  | C-V measurement noise floor                                              | 66 |

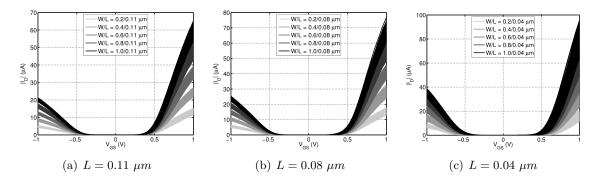

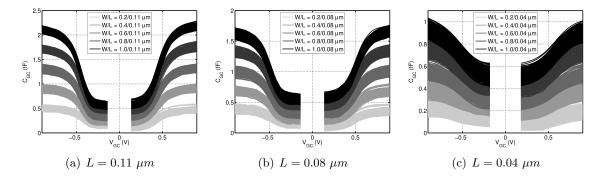

| 4.9  | PMOS and NMOS I-V measurement data                                       | 67 |

| 4.10 | PMOS and NMOS C-V measurement data                                       | 67 |

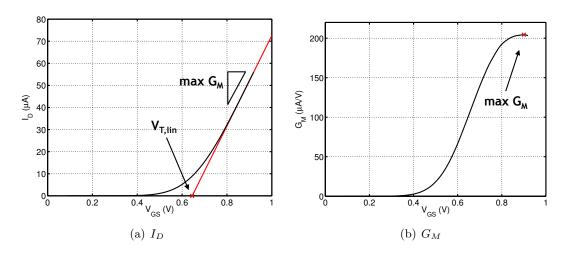

| 4.11 | I-V parameter extraction                                                 | 68 |

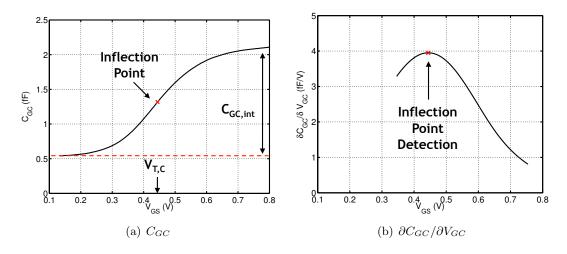

| 4.12 | C-V parameter extraction                                                 | 69 |

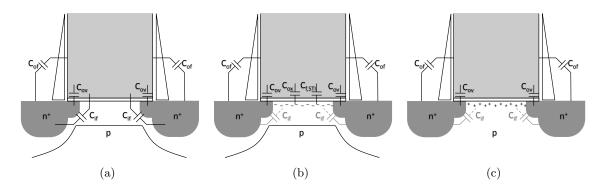

| 4.13 | Components of $C_{GC}$ at different gate bias                            | 71 |

| 4.14 | Measurement of $C_{if}$                                                  | 73 |

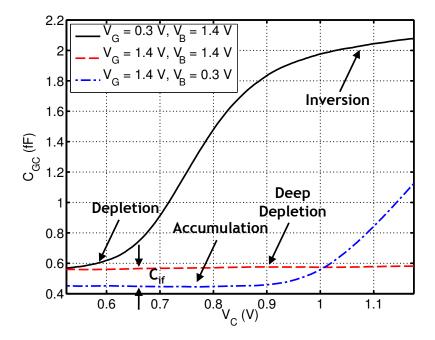

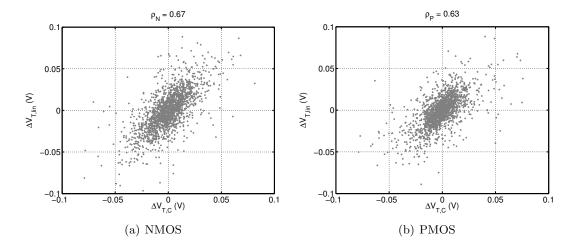

| 4.15 | Extraction of $C'_{ox}, C'_{f,STI}$ , and $\Delta L$ from $C^*_{GC,int}$ | 74 |

| 4.16 | Pelgrom plot of $\sigma_{\Delta V_{T,lin}}$ for NMOS and PMOS devices    | 75 |

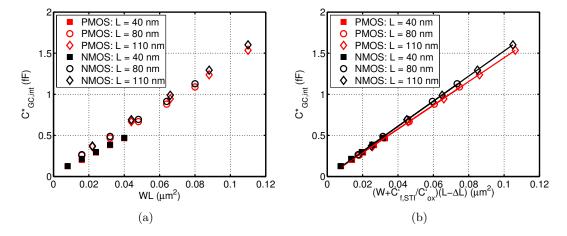

| 4.17 | Correlation between $V_{T,C}$ and $V_{T,lin}$                            | 77 |

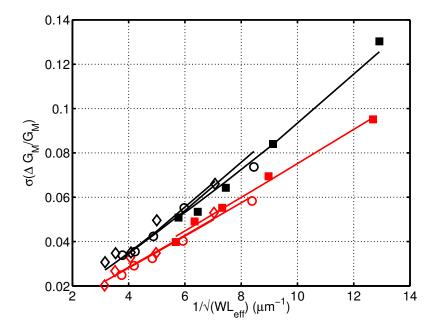

| 4.18 | Pelgrom plot of $\sigma_{\Delta G_M/G_M}$ for NMOS and PMOS devices      | 79 |

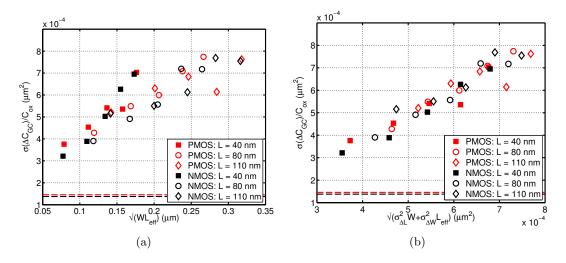

| 4.19 | Extracted random variability in $C_{GC,int}$                             | 81 |

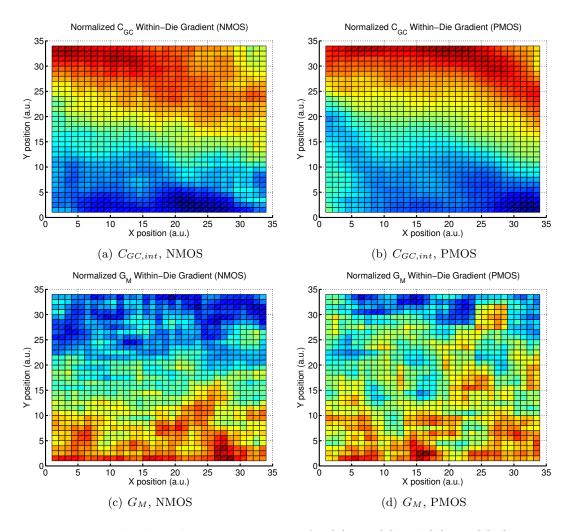

| 4.20 | Systematic variability in $C_{GC,int}$ and $G_M$ measured across the die | 84 |

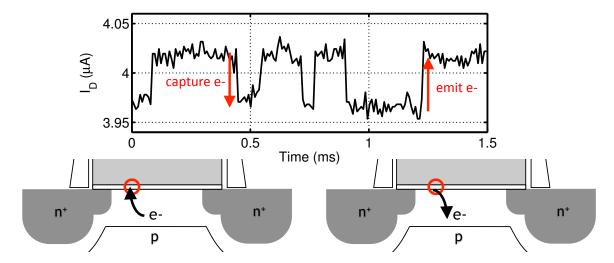

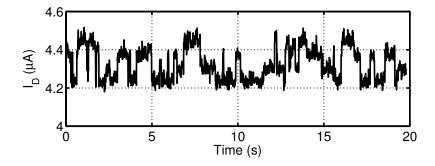

| 5.1  | Measured two-level RTN waveform                                          | 87 |

| 5.2  | Measured multi-level RTN waveform                                        | 89 |

| 5.3  | Asynchronous sampling of RTN                                             | 93 |

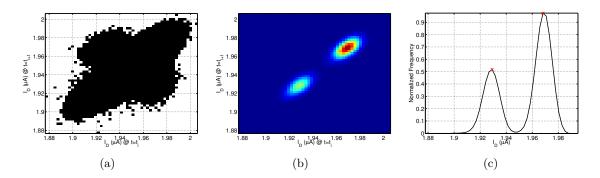

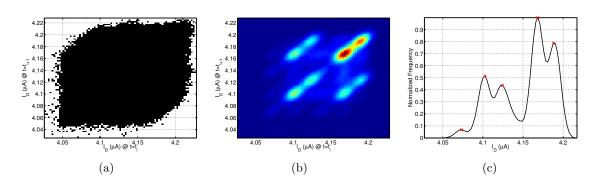

| 5.4  | TLP analysis of single-trap RTN signal                                                  | 95  |

|------|-----------------------------------------------------------------------------------------|-----|

| 5.5  | TLP analysis of triple-trap RTN signal with eight observed levels                       | 95  |

| 5.6  | TLP analysis of triple-trap RTN signal with five observed levels                        | 95  |

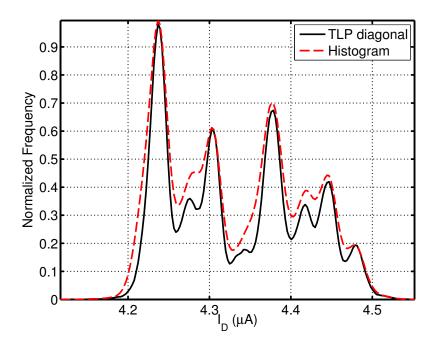

| 5.7  | Comparison between enhanced TLP diagonal and RTN histogram $\ \ldots \ \ldots$          | 98  |

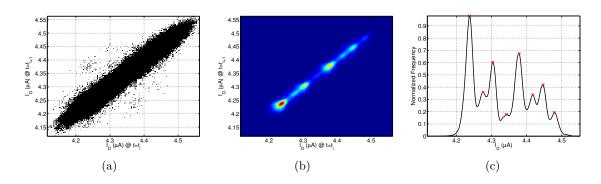

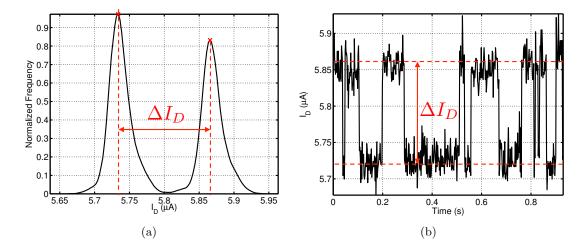

| 5.8  | Extraction of $\Delta I_D$ from single-trap RTN                                         | 99  |

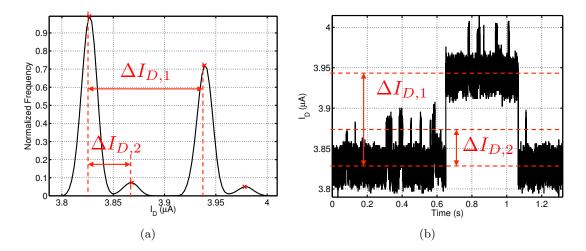

| 5.9  | Extraction of $\Delta I_D$ from multi-trap RTN                                          | 100 |

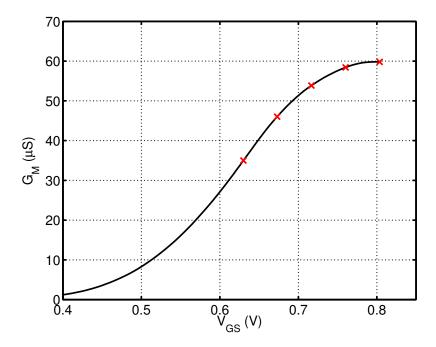

| 5.10 | $G_M$ extraction at different RTN measurement $V_{GS}$ bias levels                      | 101 |

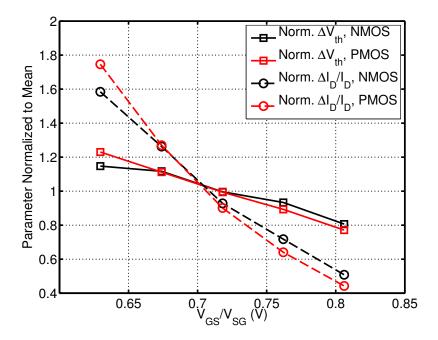

| 5.11 | Comparison between RTN modeled as $\frac{\Delta I_D}{I_D}$ and $\Delta V_{th}$          | 102 |

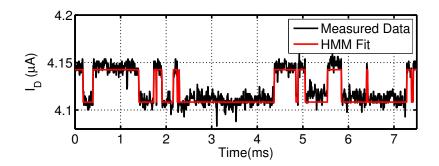

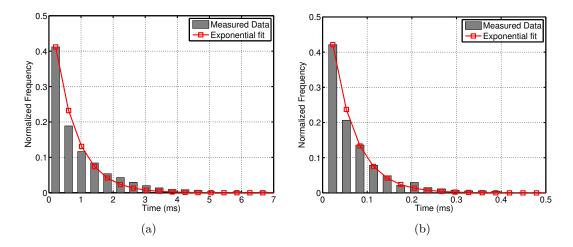

| 5.12 | Ideal RTN waveform extracted using HMM analysis                                         | 104 |

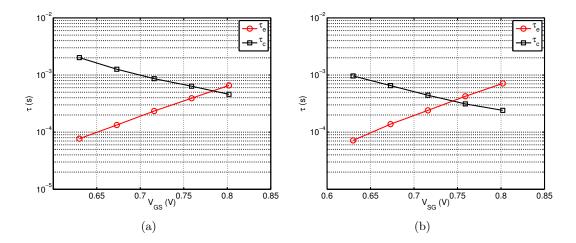

| 5.13 | Extraction of characteristic RTN capture/emission times                                 | 104 |

| 5.14 | Bistable RTN traps                                                                      | 106 |

| 5.15 | Neutral RTN trap                                                                        | 106 |

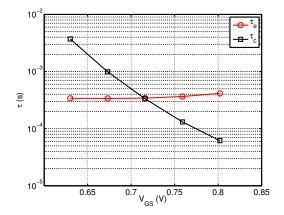

| 5.16 | Poisson distribution of $N_T$                                                           | 108 |

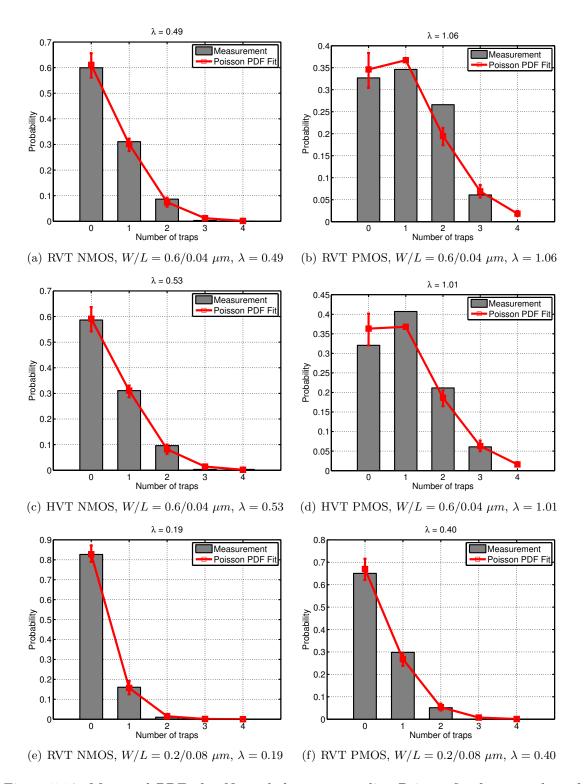

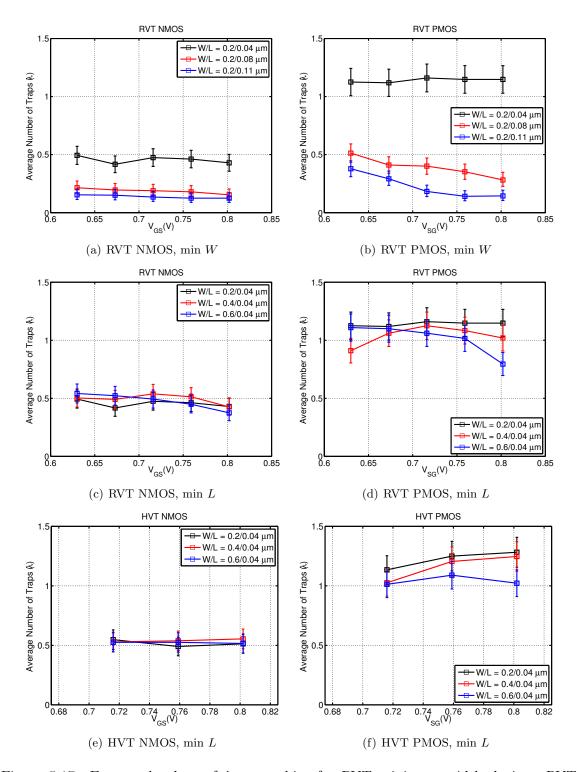

| 5.17 | Extracted values for $\lambda$ across bias                                              | 109 |

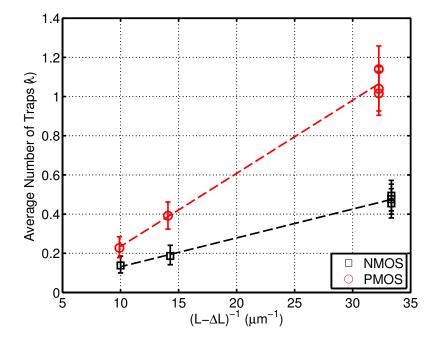

| 5.18 | $\lambda$ as a function of $1/(L-\Delta L)$                                             | 110 |

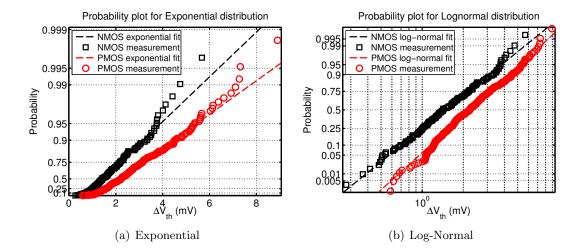

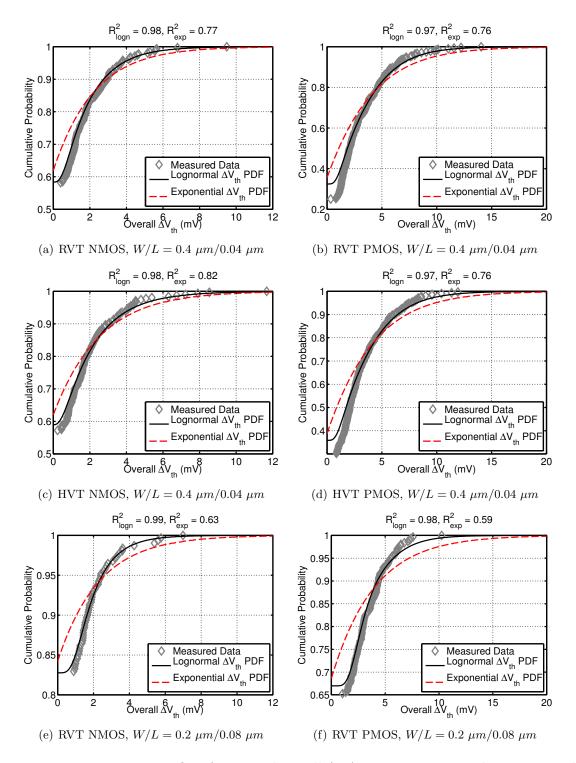

| 5.19 | Exponential vs. log-normal fit for $\Delta V_{th}$ PDFs                                 | 112 |

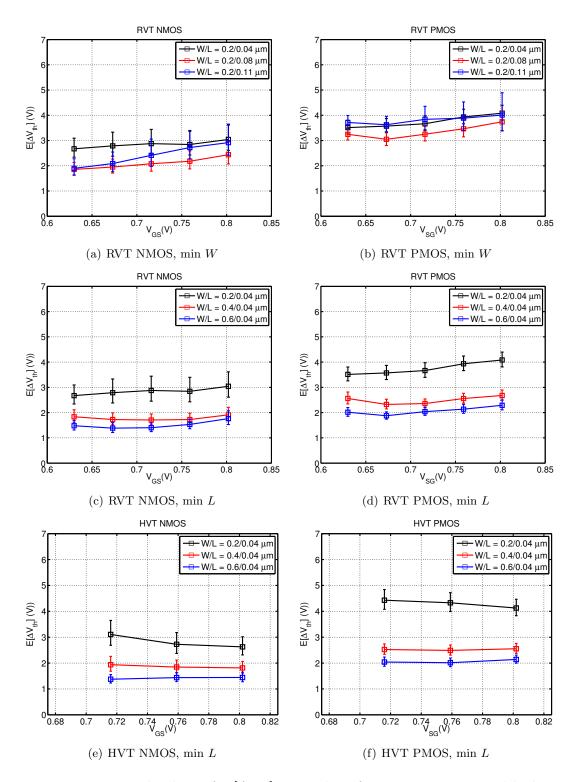

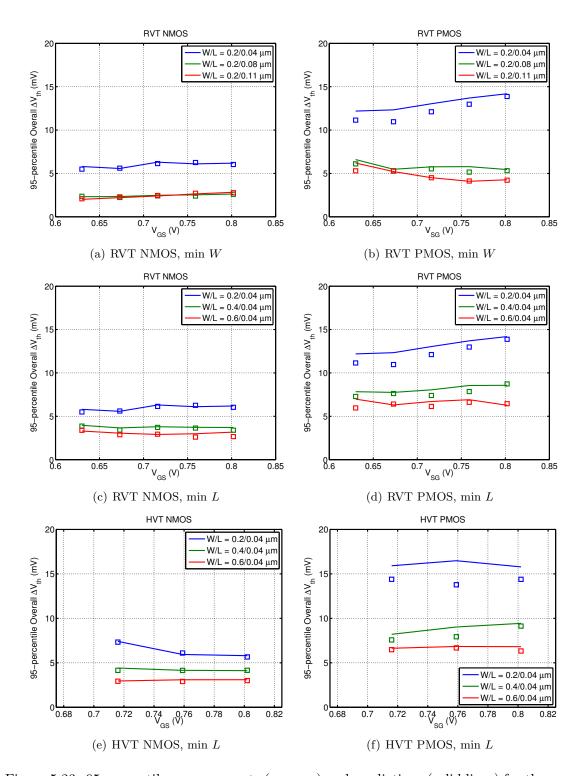

| 5.20 | Extracted values for $\Delta V_{th}$ across bias                                        | 114 |

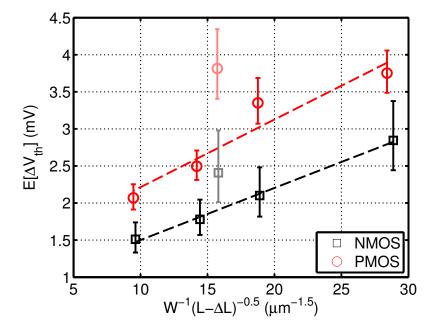

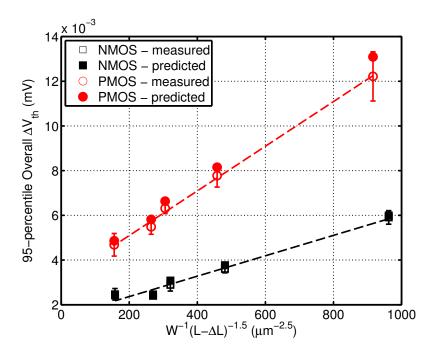

| 5.21 | $\Delta V_{th}$ as a function of $W^{-1}(L-\Delta L)^{-0.5}$                            | 115 |

| 5.22 | Comparison between measured and modeled overall RTN amplitude CDFs .                    | 117 |

| 5.23 | Measured and modeled 95-percentile overall RTN amplitude                                | 118 |

| 5.24 | Overall RTN amplitude, $\Delta V_{th}^*$ , as a function of $W^{-1}(L-\Delta L)^{-1.5}$ | 119 |

## List of Tables

| 2.1 | Dennard Constant Field Scaling [7]                                                       | 8  |

|-----|------------------------------------------------------------------------------------------|----|

| 3.1 | Level-Shifter Design Table                                                               | 32 |

| 3.2 | DAC Buffer Design Table                                                                  | 34 |

| 3.3 | Op-amp Design Table                                                                      | 40 |

| 3.4 | Comparator Design Table                                                                  | 43 |

|     |                                                                                          |    |

| 4.1 | Extracted Values of $\Delta L$ , $C'_{f,STI}$ , and $C'_{ox}$                            | 73 |

| 4.2 | Extracted Values of $A_{\Delta L}$ , $A_{\Delta W}$ , and $A_{\Delta k/k}$ from Eq. 4.21 | 78 |

| 4.3 | Extracted Values of $A_{\Lambda L}$ and $A_{\Lambda W}$ from Eq. 4.25                    | 81 |

## Acknowledgments

First and foremost, I would like to acknowledge the mentorship and support of my doctoral research adviser, Professor Kenneth Shepard, without whom none of this would have been possible. Ken is the reason why I chose to come to Columbia, and working with him over the years has been a pleasure and a privilege. He was always a reliable source of technical insight, and in spite of his overwhelmingly busy schedule, always made sure to set aside time to guide me through the rough patches. Ken provided me with every resource I ever required, whether it was access to cutting-edge manufacturing technology, CAD tools, test equipment, or lab space, and while it may seem trivial, this freedom has really made a difference in my work. At the end of the day, Ken is without a doubt the one person who has influenced me the most in my career up to this point, for which I will always be grateful.

I would also like to acknowledge the mentorship of Dr. Stanislav Polonsky, whom I worked with closely during my summers at the IBM T. J. Watson research center. Stas has been a great role model, a reliable source of technical expertise, and a good friend. Thanks to him, I gained exposure to the real-world aspects of the work I have been doing, which shaped my research efforts and helped me make my work more relevant.

The other members of my thesis committee also deserve a special mention. Professor Yannis Tsividis, Professor Luca Carloni, and Professor Charle Zukowski set aside time to examine my work and give me valuable feedback, for which I am thankful. I am fortunate to have had faculty with such vast expertise serve on my committee and contribute to my work.

My fellow graduate students have been another great resource during my time at

Columbia. Whether it was technical discussions, or practical help in the lab, each and every one of them has helped me in some way. Paul Pan was instrumental in helping me tape-out the test chip and deserves my gratitude and praise for that. He offered me a helping hand when I really needed it, and without him, I would have been hard-pressed to submit a working design in time to meet the deadline. Additionally, I would like to thank Jacob Rosenstein for his help in the lab and useful technical discussions. I would also like to specifically mention Matthew Jonhston and Ryan Field, who always contributed to technical discussions, sometimes in non-academic settings at odd hours of the night, and proved to be great friends outside of work as well. Additionally, Noah Sturcken, Jared Roseman, Inanc Meric, Sebastian Sorgenfrei, and Peter Levine have all contributed to my work in some way or another over the years, and have become good friends and colleges that I hope to remain in contact with in the future. Besides Ken, I have to say that the students in the group have been the best resource available to me throughout the years, and the quality of my work would not have been the same without their continual input.

Last, but not least, I would like to thank my family - my mom, Sonya, my dad, Dimitar, and my brother, Christo, for all of their support throughout the years. When things got rough, and inevitably, they always do in one's graduate school career, my family was always there for me. Without their support and constant encouragement, I would have never completed an undertaking of this magnitude.

## Chapter 1

## Introduction

Complementary metal-oxide-semiconductor (CMOS) technology is undoubtedly the dominant integrated circuit (IC) technology of today. In large part, the assent of CMOS can be attributed to the scalability of MOS transistors, which has persisted at an exponential rate for over five decades. However, as critical device dimensions are approaching atomic scales, issues associated with device variability are rapidly becoming a bottleneck across the entire design stack.

In order to adequately manage transistor variability in advanced CMOS technology nodes, novel comprehensive methodologies for variability characterization have to be established. Measurement techniques, which enable the fast and detailed characterization of large statistical device sample sets, are needed for this purpose.

On-chip integration of large addressable device-under-test (DUT) arrays and the associated characterization circuitry has the potential to address all of these issues. In this work, an on-chip characterization system for capacitance -voltage (C-V) and current-voltage (I-V) characterization of circuit-representative devices implemented in a 45-nm bulk CMOS process is introduced. The system is used to identify quasi-static sources of random and systematic device variability through a novel combined C-V/I-V characterization methodology. Random telegraph noise (RTN) is small-area devices is also studied with an emphasis on developing an automated methodology for the analysis of RTN waveforms, and

a comprehensive statistical model for the prediction of overall RTN amplitude is developed.

## 1.1 Thesis Outline

Chapter 2 begins by establishing the background for this work. A brief historical overview of CMOS circuits is presented, followed by a discussion of CMOS variability, including different approaches to modeling and characterizing variability. In this context, the on-chip combined C-V/I-V characterization approach is introduced.

Chapter 3 gives a description of the design of the on-chip combined C-V/I-V characterization system. Overall system design is discussed with an emphasis on full on-chip integration and design modularity. Implementation of the different circuit blocks in a 45-nm bulk CMOS process is described, and functionality is verified using simulation and measurement results. An experimental measurement setup is introduced.

Chapter 4 describes measurement techniques for combined on-chip C-V/I-V characterization. Accurate four-point Kelvin I-V measurements are demonstrated. A leakage-and parasitics-insensitive charge-based capacitance measurement (CBCM) technique with atto-Farad measurement resolution is presented. Combined C-V/I-V measurements are performed on large statistical sample sets of devices using the on-chip characterization system. Different electrical parameters are extracted, and the variability in these parameters is studied across device geometry. Specific emphasis is placed on using the combined information from C-V and I-V characterization to uncover the physical sources of variability in the quasi-static device characteristics. Sources of both random and systematic nature are examined.

Chapter 5 demonstrates another application of the on-chip device characterization system, where the rapid I-V measurement capability is used for time-domain characterization of RTN in small-area devices. An automated approach for the extraction of different RTN parameters from measured data is developed, and parameter statistics across bias, geometry, and device polarity are examined. Based on gathered data, an empirical statistical model for the modeling of overall RTN amplitude fluctuations is extracted and verified

across the sample range.

Chapter 6 concludes. The original contributions made in this work are summarized, and the resulting peer-review publications are presented. Future research directions are outlined.

## Chapter 2

## Background

## 2.1 Introduction

Chapter 2 serves to place the presented work in appropriate technical context. The origins and basics of CMOS integrated circuits are discussed, and the continual push driving device scaling is examined. CMOS transistor variability is presented as a major challenge in integrated circuit design. After establishing a brief historical perspective, different classifications and sources of variability are described, along with their impact on transistor characteristics and overall circuit performance. Basic approaches to modeling variability in transistor parameters are outlined. Different methods for measuring and characterizing device variability are discussed, with an emphasis on their comparative advantages and disadvantages. The proposed on-chip combined C-V/I-V variability characterization system is introduced in light of its advantages over current variability characterization methodologies.

## 2.2 CMOS Basics

## 2.2.1 CMOS Technology

Complementary metal-oxide-semiconductor (CMOS) technology is the dominant technology used today for the implementation of integrated circuits (ICs), ranging from digital memory and microprocessors to highly-integrated mixed-signal systems-on-chip (SOCs).

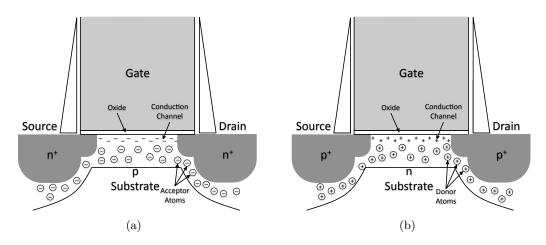

The complementary nature of CMOS technology is derived from the availability of both p-type (PMOS) and n-type (NMOS) field-effect transistors (FETs) as the fundamental circuit building blocks. An FET is a four-terminal semiconductor device, which uses an electric field applied through a gate terminal to induce a conduction channel in a doped semiconductor substrate, thus establishing an electrical contact between a source and a drain terminal doped with dopant atoms of the opposite polarity; a fourth terminal, referred to as the body terminal, is used to set the substrate potential. The majority carrier in an FET device refers to the type of carrier which transfers charge through the channel of the device. In NMOS transistors the majority carriers are negatively-charged electrons and in PMOS transistors the majority carriers are positively charged holes. PMOS devices are typically used as charging devices, and NMOS devices are typically used as discharging devices in the implementation of digital circuits. Basic representations of NMOS and PMOS transistor cross sections are shown in Fig.2.1.

Figure 2.1: Cross-section of (a) an NMOS device and (b) a PMOS device; the devices are shown with the channel fully inverted.

## 2.2.2 The Appeal of CMOS

The concept of a field-effect transistor was originally introduced by Lilienfeld in 1926 [1], but it wasn't until 1960 that Kahng from Bell Labs demonstrated the first operational MOS device [2]. The appearance of the first MOS transistors coincided with the introduction of

the concept of a monolithic integrated circuit, first patented by Noyce in 1959 [3]. While both NMOS and PMOS transistors were conceived early on, the idea of combining the two types of device polarities in order to achieve minimal standby power in a digital circuit implementation was introduced in 1963 by Wanlass and Sah [4]. The ability to limit power consumption to only power required for the charging and discharging of load capacitances during switching events is one of the primary appeals of CMOS technology.

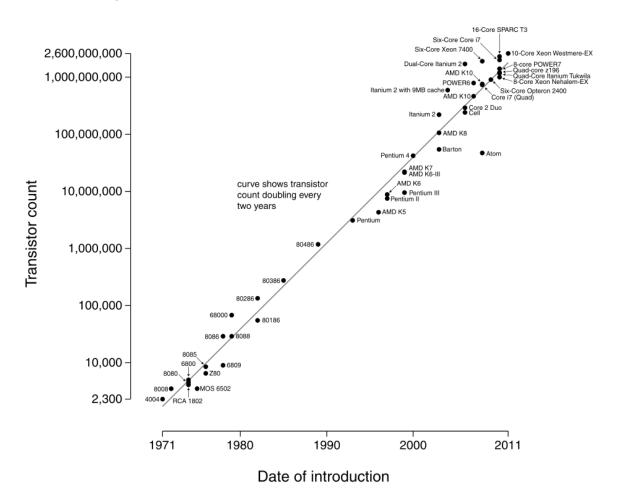

In 1965, Moore published his seminal paper, "Cramming More Components Onto Integrated Circuits" [5], which for the first time introduced the concept of technology scaling, and established what is commonly referred to as Moore's Law. Moore's Law states that the number of components integrated in a single IC will increase exponentially, doubling approximately every two years. While often labeled as a self-fulfilling prophecy, the push for continual scaling has been the driving force behind the explosive expansion of the semiconductor industry, making IC design one of the major global economic engines for the past five decades. It is interesting to note that Moore's prediction was not based on a technical argument, but rather on an economic one, stating that the reason for the exponential increase in the number of integrated components is based on the premise that higher integration leads to a correspondingly lower cost per device, keeping the cost of the IC relatively constant, while simultaneously increasing the available functionality at an exponential rate. As such, Moore's genius is perhaps not so much in noticing the technical possibilities for scaling, as much as in perceiving the ultimate economic driving force behind ever higher levels of integration. Amazingly, the IC industry has kept up with the exponential growth predicted by Moore to present day (Fig.2.2).

The technical path toward the realization of Moore's Law was in large part outlined by Dennard in 1974, when he introduced the concept of constant-field scaling [7]. The theory of constant-field scaling proposes that if MOSFETs are scaled in a manner, such that the magnitude of the electric fields that govern transistor operation remains constant, then a proportional gain in circuit performance can be expected, while at the same time a quadratic reduction of power per circuit operation is achieved, resulting in constant power density per

## Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 2.2: Moore's Law as demonstrated by the continual exponential growth of number of transistors integrated in a single IC up to present day [6].

Table 2.1: Dennard Constant Field Scaling [7]

| Device or Circuit Parameter           | Scaling Factor |

|---------------------------------------|----------------|

| Device dimension $t_{ox}$ , $L$ , $W$ | 1/k            |

| Doping concentration, $N_a$           | k              |

| Voltage, $V$                          | 1/k            |

| Current, I                            | 1/k            |

| Capacitance, $\epsilon A/t_{ox}$      | 1/k            |

| Delay time/circuit, $CV/I$            | 1/k            |

| Power dissipation/circuit $VI$        | $1/k^2$        |

| Power density, $VI/A$                 | 1              |

unit area. This type of scaling can be accomplished by reducing all of the physical device dimensions by a scaling factor, k, reducing all voltages (including the threshold voltage) by k, and increasing the doping concentration by k. The overall scaling trends proposed by Dennard are shown in Table 2.1. By and large, it is this notion of constant field scaling which cleared the way for the realization of Moore's law, and ultimately made CMOS technology the prevailing IC technology of today. However, strictly adhering to Dennard's scaling rules as described in [7] has proven difficult in recent years, mainly due to an inability to scale the threshold voltage of the device as the parameter approaches fundamental limits set by the laws of thermodynamics. Other scaling schemes, such as constant-voltage scaling and quasiconstant-voltage scaling [8], have been proposed in an attempt to circumvent this issue, and the general drive to scale the dimensions of the device with each new technology node, resulting in an overall exponential decrease in device dimensions over time, has remained true to this day.

## 2.3 CMOS Variability

While device scaling has many desirable properties, such as improved circuit performance and decreased cost per transistor, maintaining the scaling trajectory predicted by Moore's law is becoming increasingly difficult. Many factors contribute to this problem; however, variability in device performance is arguably the most difficult to overcome. In fact, Moore

[5] identifies issues related to yield as the major limiting factor in achieving ever higher levels of integration. Every manufacturing process is fundamentally limited by quality and reliability concerns, and after a certain point, trying to integrate more devices into a single IC results in decreased yield, and consequently, a higher price per working part. Problems associated with variability are particularly nefarious, since as device dimensions scale beyond the wavelength of light used for patterning and approach atomic dimensions, controlling device behavior with increasing precision becomes tremendously challenging. Different effects traced to the discrete and quantum nature of charge and the inability to accurately define device dimensions begin to dominate transistor behavior. At the same time, increasing levels of integration, with hundreds of millions and even billions of devices integrated on the same die in modern-day digital microprocessors [9,10], require ever tighter control of device parameters in order to ensure that if not all, then at least most of the devices integrated in a single die behave in a predictable manner that does not compromise the functionality of the underlying product.

## 2.3.1 Historical Perspective

Issues related to device variability have always been a central theme in semiconductor manufacturing. While variability may be perceived by many as an emerging concern in modern-day sub-100-nm CMOS technologies, it has in fact been a well-studied and carefully monitored quantity starting from the earliest days of CMOS design. Shockley is one of the first to examine the phenomenon of semiconductor device variation in his study of the random fluctuations in the breakdown voltage of p-n junctions [11]. His work is later extended by Keyes [12] to explain the effect of dopant fluctuations on the performance of FETs. Traditionally, fluctuations in the threshold voltage have been the primary source of device performance variability, and as such, have been most closely studied. However, as scaling trends have continued to progress over the years, many additional sources of device variability have been identified, and as the complexity of integrated circuits has grown, so has the sophistication in characterizing, modeling and measuring device variability.

## 2.3.2 Impact of CMOS Variability

The effect of device variability on the performance of digital logic circuits is primarily expressed in terms of overall variability in delay and power consumption. Both quantities are a function of the current-driving and capacitive characteristics of the device, with delay being proportional to capacitance and inversely proportional to current, active power consumption being directly proportional to capacitance, and static power consumption being directly proportional to leakage current. Therefore, in order to be able to examine the true impact of device variability, the effects of variability in both the current-voltage (I-V) and capacitance-voltage (C-V) characteristics of the device must be studied. As is discussed below, most work focuses on either studying overall variations in delay, or variations in the I-V characteristics of the device, whereas the impact of C-V variability, especially at circuit-representative geometries, is largely ignored. More importantly, there has been no work showing the relationship between variability in the C-V and I-V characteristics of the device, which are ultimately based on many of the same physical device properties, and are expected to show correlation.

## 2.3.3 Classification of CMOS Variability

The sources of device variability in a CMOS process can generally be classified as static and dynamic [13]. Dynamic sources of variability are manifested as either gradual changes in device characteristics over time, most notably bias-temperature instability (BTI) effects leading to shifts in the effective threshold voltage of a device,  $V_{th}$ , [14–16], or noise, and in particular, low-frequency random telegraph noise (RTN). RTN is the result of trapping and de-trapping of discrete charges at the channel/oxide interface of the device, and is generally modeled as sudden quantized jumps in  $V_{th}$  giving rise to corresponding fluctuations in the channel conductance [17]. This type of noise is mainly associated with small-area devices, and is closely related to the aforementioned BTI effects [18], as well as 1/f noise [19]. The measurement, characterization, and modeling of RTN as a source of device variability are a primary focus of this work and are discussed in detail in Chapter 5.

Static device variability refers to variability in the electrical characteristics of the transistor as a result of uncertainties in the manufacturing process, and can be either random or systematic [20]. Random variability is defined in terms of mismatch between nominally identical devices situated in immediate proximity to one another and is generally caused by random fluctuations in the underlying physical characteristics of the device. On the other hand, systematic variations manifest themselves as well-defined gradients across the die, known as within-die (WID) variations, gradients across the wafer, known as die-to-die (D2D) variations, and differences between mean parameter values across wafers, known as wafer-to-wafer (W2W) variations. By definition, systematic variability can be traced to a deterministic source. In terms of static variability, this work focuses on the measurement and characterization of random variations as well as within-die (WID) systematic variations.

## 2.3.4 Sources of Systematic Variability

Systematic variability is generally caused by fluctuations in different parameters of the manufacturing process. Issues related to pattern density [21, 22], channel stress [23–25], mask misalignment [26], and across-wafer gradients due to rapid thermal anneal [13], are amongst many reported. Identifying the actual sources of systematic variability can be challenging without intimate knowledge of the manufacturing process, and as such, is not a central focus of this work. However, measured gradients in electrical parameters can still be mapped to systematic variations in the physical properties of the device, as is shown in Chapter 4. Identifying the physical causes of systematic variation is critical in determining the underlying source.

## 2.3.5 Sources of Random Variability

There are a number of physical factors that contribute to random variability in the electrical characteristics of an FET. The general tendency dictated by Moore's law is that the variance of these physical parameters should scale proportionally to device dimensions, in order to keep yields at acceptable levels. However, as the critical dimensions of CMOS transistors

scale close to and beyond fundamental physical dimensions, such as atomic dimensions or the wavelength of light used for patterning, the task of keeping variability at bay is becoming ever more challenging. There are a number of physical sources of random device variability that manifest as variability in the electrical properties of the transistor, both in terms of its C-V and I-V characteristics. Four of the most dominant sources are introduced below.

#### Random dopant fluctuation

Random dopant fluctuation (RDF) refers to variations in the number of dopant atoms in a device, which arise from the inability to precisely distribute a given concentration of dopant atoms throughout the channel of the transistor. Due to the aggressive scaling in device dimensions, the total number of dopant atoms per device is rapidly diminishing, reaching values on the order of 100 in a 45-nm process [27]. As a result, even single-atom fluctuations can have an appreciable effect on  $V_{th}$ , and the impact of RDF accounts for upwards of 60% of the threshold voltage variability [20]. The effects of RDF are expected only to worsen with new technology nodes, as the relative variation in threshold voltage begins to creep up [28]. This is one of the main reasons why supply voltages in recent technology nodes have not scaled according to the principles of constant-field scaling. In order to find a long term solution to this problem, different device topologies involving undoped or lightly-doped silicon are investigated [29, 30].

RDF mainly has an impact on the threshold voltage,  $V_{th}$ , although some influence on the effective carrier mobility,  $\mu_{eff}$ , can also be expected due to Coulomb scattering [31]. The Coulomb interaction between mutually-repellant carriers and dopants in the channel limits the effective mobility of the carriers. As the uncertainty in the number and distribution of dopant atoms in the channel grows, so does the corresponding uncertainty in the effective carrier mobility.

Variations in  $V_{th}$  can be expected to have an effect on both the I-V and the C-V characteristics of the device, and variations in  $\mu_{eff}$  have an effect only on the current-driving characteristics of the device. In general, the effect of RDF on  $V_{th}$  is dominant,

whereas  $\mu_{eff}$  is expected to be more sensitive to variations in other process parameters, namely mechanical stress in the channel [32], as discussed below.

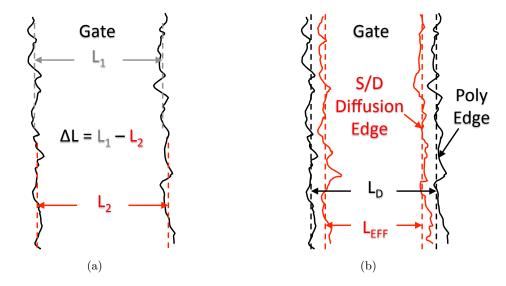

#### Line-edge roughness

Line-edge roughness (LER) is another major source of variation in modern-day CMOS processes [13,27,33]. LER results from statistical variation in the number of photons incident on the sample during lithographical exposure, and the absorption rate, chemical reactivity, and molecular composition of the photoresist [13]. Roughness along the edges of the gate can be expected to result in variability in the effective dimensions of the device, as shown in Fig. 2.3.

Since the length, L, of the device is generally considerably smaller than the width, W, LER is expected to couple into the I-V characteristics of the device mainly as an effect due to a variation in L. The impact on the drain current,  $I_D$ , is established through the inverse relationship between  $I_D$  and L, as well as through second-order effects on  $V_{th}$ . In terms of its impact on the capacitance of the device, LER is expected to influence the variability in the gate capacitance through the proportional relationship between the gate area, given by the product of W and L, and the intrinsic gate-to-channel capacitance,  $C_{GC,int}$ .

While discussing the effects of LER on device variability, it is important to note than maintaining a scaling trend in the variability of the critical dimensions (CD) of the device is crucial to continual scaling. As a result, much effort is put into maintaining these trends, as is discussed in [27], where it is shown that the variability in CD is very closely monitored and scales at the same rate as the technology nodes, at least down to the 45-nm node. As a result, one would not expect to see a tremendous impact of LER on device performance at 45-nm, in contrast to RDF, for instance. However, being able to monitor and characterize the variations in CD is still of great interest in terms of ensuring that these scaling trends are maintained [34].

Figure 2.3: (a) An example of different effective lengths across different areas of the same poly-silicon gate due to LER, and (b) difference between LER of the gate and of the source-drain edges, which actually define the effective length of the device - the two quantities are highly correlated, but not the same.

#### Channel stress fluctuations

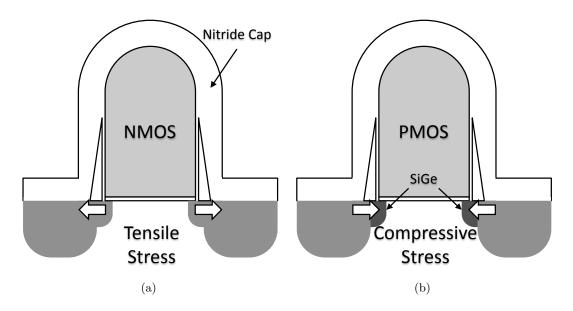

Channel stress has a fundamental impact on carrier mobility, a phenomenon widely exploited in modern-day CMOS devices in order to overcome the increasing degradation of carrier mobility caused by channel impurity scattering [35]. Due to the difference in charge carriers, NMOS devices have to be subjected to tensile stress and PMOS devices have to be subjected to compressive stress in order to enhance the effective channel mobility. While application of stress as a mobility enhancement technique is common to both device polarities, the mechanisms for producing the two distinct types of stress are different. In particular, nitride capping layers over the NMOS devices give rise to tensile stress, while embedded SiGe source/drain epitaxial layers give rise to compressive stress in the PMOS channels, as shown in Fig. 2.4. As a result, mobility variations due to stress can be expected to be different for each device type, as the controllability of the two types of stress would be different based on the two different stressing techniques used.

Stress-induced variability is most often considered as a source of systematic variability, where the stress caused by the device environment deterministically causes a change in

Figure 2.4: Application of channel stress for mobility enhancement: (a) tensile stress in an NMOS device using of a nitride capping layer, and (b) compressive stress in a PMOS device using a SiGe diffusion implant.

performance [23–25]. However, random variations in stress are also expected to contribute to random variations in  $\mu_{eff}$  [32,36,37]. In terms of the effects on the electrical characteristics of the device, variations in stress have a significant effect on the I-V characteristics through modulation of the channel mobility. However, in terms of the C-V characteristics of the device, carrier mobility, and consequently, channel stress, are expected to have no notable impact.

#### Interface roughness and defects

As the oxide thickness,  $t_{ox}$ , scales down to atomic levels, reaching as low as 2.4 nm in a 45-nm CMOS process, oxide roughness of one or two atomic layers can have a significant impact on device characteristics [38]. Variations in  $t_{ox}$  have a direct impact on the oxide capacitance per unit area,  $C'_{ox}$ , and as such, affect both the C-V and I-V characteristics of the device. Additionally, gate leakage is extremely sensitive to variations in  $t_{ox}$ . Due to this sensitivity, it is expected that  $t_{ox}$  is a variable, which is extremely-well controlled, both in terms of growth of the epitaxial layers, as well as post-processing using chemical-mechanical polishing (CMP) [27]. Due to the increased sensitivity to variations in the

oxide thickness, modern-day CMOS technologies are moving towards high-k dielectric gate materials, which enable scaling of the gate capacitance while maintaining a larger physical dielectric thickness.

Regardless of the type of dielectric used, defects in the channel-oxide interface are bound to occur, giving rise to interface trap states and the associated random telegraph noise (RTN). As mentioned above, RTN is a considerable source of dynamic variability in device performance and is discussed in more detail in Chapter 5.

### 2.3.6 Modeling Random Variability

Pelgrom [39] makes the observation that the variance of device parameters scales inversely with the device area based on general principles regarding the spacial averaging of random variables across device area. This idea is fundamental, in that it points to the need to consistently scale variability in device parameters with each new technology node in par with the reduction in device area, in order to maintain acceptable yield levels. Of course, as mentioned earlier, maintaing high yield is fundamental to the formulation of Moore's law in its original form, where scaling is expressed in terms of cost per transistor. The two results from Pelgrom's work quoted most often are the relationships regarding the scaling of the variability in the random mismatch of threshold voltage,  $\Delta V_{th}$ , and the relative current factor,  $\Delta \beta/\beta$ , which are given by

$$\sigma_{\Delta V_{th}}^2 \propto \frac{1}{WL} \tag{2.1}$$

and

$$\sigma_{\Delta\beta/\beta}^2 \propto \frac{1}{WL},$$

(2.2)

where  $\beta = \mu_{eff} C'_{ox} W/L$ .

Drennan [40] expands on the idea by distinguishing between physical device characteristics and electrical model parameters, and stipulating that the physical parameters, such as oxide thickness, doping, device dimensions, carrier mobility, etc. are the ones that average away with increase in the physical dimensions of the device. However, more than one physical parameter can have an impact on any given electrical parameter, and for accu-

rate modeling of variability, the variance of each physical parameter has to be propagated to the variance of the electrical parameter. In particular, the variance,  $\sigma_e^2$ , of an electrical parameter, e, can be expressed in terms of the variance,  $\sigma_{p_i}^2$ , of all physical parameters,  $p_i$ , and the electrical parameter's sensitivity to them, as given by

$$\sigma_e^2 = \sum_i \left(\frac{\partial e}{\partial p_i}\right)^2 \sigma_{p_i}^2(W, L). \tag{2.3}$$

More notably, Drennan also points out that while most physical parameters indeed average out over area, with

$$\sigma_{p_i}^2 \propto \frac{1}{WL},\tag{2.4}$$

the fluctuations in device length, L, and width, W, caused by line-edge roughness (LER), do not. Instead,

$$\sigma_{\Delta L}^2 \propto \frac{1}{W} \tag{2.5}$$

and

$$\sigma_{\Delta W}^2 \propto \frac{1}{L}.\tag{2.6}$$

This sort of analysis is also present in Pelgrom's work, where the author consideres the effect of  $\sigma_{\Delta L}$  and  $\sigma_{\Delta W}$  on  $\sigma_{\Delta \beta/\beta}^2$ , but ultimately argues that variability due to LER can be neglected if the dimensions W and L are large enough.

Pelgrom scaling and propagation of variance (POV) form the basis for most rudimentary variability modeling used in design, and are the primary variability models considered in this work.

## 2.4 Methods for Variability Characterization

Different techniques for variability measurement and characterization have been proposed to enable the monitoring and analysis of device variability and its impact on circuit performance. In general, when measuring device variability, a few important characterization parameters must be considered. The ability to measure large sample sets in order to extract the tails of statistical distributions with a high level of confidence is critical. Therefore,

characterization methodologies which allow high degrees of integration are preferred. Measuring large sample sets requires fast measurement acquisition times, which also makes highly integrated approaches appealing. On the other hand, if the physical sources of variability are to be identified, detailed measurements of different device characteristics need to be performed, preferably on the same device sample set. Measurement techniques which enable this are generally implemented using off-chip characterization equipment, making them time consuming and unsuitable for characterization of large device sample sets.

In this section, different popular variability characterization techniques are examined with respect to their ability to meet the specifications described above. While each has its own specific advantages, none of the popularly used techniques manage to satisfy all of the desired criteria. Consequently, a novel variability characterization methodology is proposed, which enables both rapid and detailed device characterization of large statistical sample sets.

### 2.4.1 Ring Oscillators

Ring oscillators (RO) and other delay-based characterization methods are widely employed in research and industry as tools for circuit and device variability measurement [41–47]. They offer a highly integrated approach to variability characterization, where variability in the delay of simple circuits (inverters or other standard gates) is measured through the means of measuring variability in the RO frequency of oscillation - a measurement, which can be done in a purely digital fashion. Such measurements can be performed rapidly and in large volumes. In an RO with N number of stages, the delay of a single stage,  $t_D$ , is related to the frequency of oscillation,  $f_{osc}$ , according to

$$t_D = \frac{1}{2N f_{osc}}. (2.7)$$

The delay metric,  $t_D$ , is arguably one of the most important metrics characterizing digital circuit performance, and it incorporates variations in both the current-driving and capacitive characteristics of the underlying devices.

However, there are significant drawbacks to RO characterization as well. As gate delay decreases with new technology nodes, generating a characteristic frequency,  $f_{osc}$ , that

is low enough to be accurately sampled necessitates RO structures with a large number of stages, especially if the frequency is not measured on-chip. This results in decreased measurement sensitivity, as the ratio of the standard deviation to the mean of the measured oscillation period,  $T_{osc}$ , decreases with increasing N, as given by

$$\frac{\sigma(T_{osc})}{\mu(T_{osc})} = \frac{\sqrt{2N}}{2N} \frac{\sigma(t_D)}{\mu(t_D)}.$$

(2.8)

More importantly, RO measurements integrate together all possible sources of variation into a single metric, making it impossible to determine the individual contribution of different sources of variability. In some cases, this issue can be addressed by comparing measurement results from ROs comprised of similar but different device structures, as reported in [41,48], and then assigning the relative difference in measured frequency to the differences in circuit and device topologies. However, such an approach still fails to distinguish between effects due to I-V and C-V variability.

Overall, the popularity of ROs stems from the ease of characterization they offer, the ability to integrate them alongside functional circuitry, and the direct observation of variation in the delay metric. They can be very useful as general purpose variability monitors, but do not give sufficient information about the underlying physical sources of device variability.

#### 2.4.2 Device Simulation and Imaging Techniques

On the opposite side of the spectrum from ROs lie a different set of variability characterization techniques, which depend on atomistic device modeling and imaging. In terms of using device simulations to model atomistic effects that lead to variability in different electrical device parameters, Asenov and his students have demonstrated a wide array of applications. They have used atomically correct device simulations based on their Glasgow simulation engine to study variability in both I-V and C-V device behavior at small geometries due to random dopant fluctuations, line-edge roughness, channel stress, and channel/oxide interface traps [33, 37, 49–54].

An atomistic device simulation methodology is well-suited for studying the impact different physical sources of variability have on electrical device characteristics. Also, given enough computational power, a Monte-Carlo approach can be used to gather a large number of statistical samples as needed to accurately extract different parameter distributions. However, simulated results have the disadvantage of predicting only phenomena incorporated in the model, and in general, the complexity of a real device can never truly be captured by any model, no matter how complex. Therefore, while atomistic device simulation is an indispensable tool in the detailed study of the relationship between the physical sources of device variability and their electrical manifestations, a methodology that is based on measurements of actual devices is still needed.

In addition to atomically correct device modeling, different device imagining techniques can also be used to directly observe physical sources of variability. As an example, scanning electron microscopy (SEM) can be used in the study of line-edge roughness by top-down imaging of transistor gates and digital extraction of gate contours from the SEM image [33, 55]. Such a technique is appealing in terms of studying in detail the different physical aspects of LER, such as the autocorrelation of the edge roughness, but is rather time consuming and taking a large number of samples is impractical. Moreover, as shown in Fig. 2.3, the LER associated with the poly gate is not the actual parameter of interest; instead, the LER associated with the source/drain diffusion edges is what affects variability in the electrical device characteristics.

In addition to SEM imaging, a new technique named laser-assisted atom probe to-mography (APT) has been used to generate 3-D images of individual dopant atoms in a MOSFET structure, giving a much more informative view of the physical characteristics of the device [56,57]. This technique is geared towards studying how atomic-scale phenomena contribute to device variability, but similarly to all other imaging techniques, it is impractical in terms of overall variability characterization due to the inability to collect a large number of samples over a wide device parameter space.

#### 2.4.3 Electrical Device Characterization

Perhaps the most robust way of characterizing the variability in MOSFETs is through electrical measurements. Direct measurements give the best indication of the variability in the electrostatic properties of the device, which is ultimately what gives rise to the variability in circuit performance. At the same time, methodical electrical characterization employing different I-V and C-V measurements can give a good insight into the actual physical sources of device variability through established relationships between physical device characteristics and electrical device properties. Depending on the level of integration and measurement functionality, direct device characterization can provide detailed measurements of large statistical device sets at acceptable rates, and can potentially result in a variability characterization methodology which offers a balance between detail, accuracy, sample size, and measurement throughput.

Most direct characterization approaches applied to variability measurements focus on the I-V characteristics of the device. This is primarily due to the fact that dc currents are easy to measure and most aspects of variability are reflected it the I-V characteristic of the transistor. I-V variability characterization comes in three different levels of test circuit integration. The first level is the traditional direct probing approach, which involves routing individual pads to each of the terminals of the device under test (DUT) [22, 30, 58, 59]. Even if small probe pads are used, this approach still results in small statistical sample sets and is generally not applicable to large-scale variability studies. Additionally, off-chip current measurements of low current signals can be slow due to the need to charge the large parasitic capacitances associated with the measurement probes, cables, and equipment at every sampling step.

In order to enable the study of large statistical DUT sample sets, different array-based characterization approaches have been employed [60–65]; these approaches are able to achieve much higher DUT density as a result of the reduction of the number of probe pads. However, issues related to sub-optimal sampling rates due to the large parasitics associated with taking measurements off-chip still remain.

Recent work attempts to address these issues by integrating the analog measurement circuitry on-chip, alongside a large addressable DUT array [48,66]. This approach overcomes many of the disadvantages associated with direct electrical measurements, in that it allows large device sample sets to be characterized at fast sampling speeds, while also offering a digital measurement output and removing the need for analog measurement equipment. However, the on-chip characterization system designs described in [48,66] still require sweeping an analog input in order to perform voltage sweep measurements, and are limited to I-V characterization only.

In terms of studying the variability in the C-V characteristics of FETs, few results can be found in the literature referring to modern-day CMOS capacitor characterization. Charge-based capacitance measurements (CBCM) have been successfully employed to perform atto-Farad resolution back-end-of-line (BEOL) characterization [67,68]. More recently, CBCM approaches have been successfully applied in front-end-of-line (FEOL) characterization to characterize the voltage-dependent capacitance of MOS transistors with sub-femto-Farad resolution [69,70]. However, most work focuses not on variability, but rather on using high-accuracy C-V measurements of individual devices for parameter extraction.

When referring to capacitance variability measurements, two recent publications stand out. One is the work by Polonsky et. al. [71], where a variation of CBCM called quadrature-voltage capacitance measurement (QVCM) specifically designed to overcome C-V characterization limitations due to gate leakage through the DUT is used to characterize an array of devices in a 45-nm SOI CMOS process. However, while sub-femto-Farad resolution C-V measurements of circuit-representative devices is indeed demonstrated, the statistical sample set measured consists of only 11 DUTs and the measurements from only one set of devices at circuit-representative dimensions is presented. The other example of CMOS C-V variability measurements is by Tsuji et. al. [72], where CBCM is once again used to measure C-V curves of devices with different dimensions in statistical sample sets of 24 DUTs and even some Pelgrom variability analysis of MOSFET capacitance is reported. It should be noted, however, that this work, while published in 2011, reports results from a

seemingly older technology node, with the smallest length of devices measured set at 0.12  $\mu m$ . Presumably, gate leakage is not an issue at this technology node, which greatly simplifies C-V characterization. In both instances, only the DUT arrays and the supporting CBCM switching circuitry are integrated on chip, with all measurements performed off-chip at CBCM measurement frequencies of 1 MHz or below.

## 2.4.4 Proposed Approach

Figure 2.5: An illustration of the proposed combined C-V/I-V characterization approach; C-V and I-V characteristics for the same circuit-representative device are measured.

The CMOS variability characterization methodology proposed in this work is based on an on-chip electrical characterization approach where both the C-V and the I-V characteristics of the device are extracted simultaneously, as illustrated in Fig. 2.5. Such an approach enables complete quasi-static device characterization, allowing for the correlation between the variability in the two characteristics to be studied. This will be shown to be useful with regards to extracting information about the underlying physical phenomena responsible for the measured variability in the electrical characteristics of the device.

An on-chip system for combined C-V/I-V characterization with a digital I/O interface is designed and implemented in a 45-nm bulk CMOS process, alongside a large addressable DUT array. Complete measurement system integration aims at improving measurement throughput as need for large-volume data acquisition. Moreover, on-chip integration makes high-frequency current measurements possible at low signal levels, enabling the characterization of random telegraph noise (RTN), in addition to quasi-static C-V and I-V characterization. Large statistical sample sets of different DUT types spanning a number of design parameters are available for characterization. All studied devices have circuit-representative dimensions, allowing accurate variability measurements at relevant device sizes. A novel CBCM characterization technique with atto-Farad measurement resolution is developed for the purpose of C-V characterization of small-area DUTs. To the author's knowledge, this is the first time when such a comprehensive electrical device characterization system has been implemented at such high levels of integration, and the only published work to date presenting results on combined C-V/I-V variability characterization of large sample sets at an advanced technology node. The proposed approach addresses issues related to sample set size and measurement throughput through complete on-chip integration, as well as issues related to measurement detail and ability to identify physical sources of device variability through combined C-V/I-V characterization.

# Chapter 3

# On-Chip Characterization System

#### 3.1 Introduction

Chapter 3 details the design of the on-chip variability characterization system and its individual components. The chapter begins by introducing a top-level system overview. Emphasis in placed on complete system integration and component modularity. The design of each of three main system components – addressable device-under-test (DUT) array, biasing digital-to-analog converted (DAC), and measurement unit (MU) – is described in detail. Simulation results and characterization measurements are included where applicable. Overall, the system is demonstrated to have all of the desired characteristics, including full on-chip integration of measurement and stimulus circuitry, complete digital I/O interface, and high-resolution current and voltage characterization capabilities. System implementation in a 45-nm bulk CMOS process and the associated experimental measurement setup are presented.

## 3.2 System Overview

Fig. 3.1 shows a simplified top-level schematic of the on-chip characterization system. The system consists of three major blocks – an on-chip switching matrix, used to individually address transistors from the device-under-test (DUT) array, a four-channel digital-to-analog

Figure 3.1: A simplified top-level schematic of the on-chip characterization system.

converter (DAC), used to supply each of the four DUT terminal bias voltages, and a measurement unit (MU), which consists of a current- and voltage-mode analog-to-digital converters (ADCs), used to perform accurate on-chip current-voltage (I-V) and charged-based capacitance-voltage (C-V) characterization. The system can be configured to characterize both NMOS as well as PMOS devices by adjusting the analog references and internal controls to account for opposite current polarities.

The design of the on-chip measurement system is based on complete on-chip integration of the entire MOSFET characterization infrastructure. The system has a digital-in/digital-out measurement interface, making it compatible with a purely digital test flow. Any need for accurate and expensive bench-top measurement equipment is completely removed. The only analog signals going to the chip are dc current and voltage reference signals as required by the DAC and ADCs, as well as dc currents for biasing on-chip analog circuits. As far as the author is aware, this is the highest level of integration achieved in any published system for on-chip device characterization. As discussed in Chapter 2,

achieving high levels of on-chip measurement integration not only removes the need for an analog signal interface, but also has the potential to greatly improve measurement throughput, which is an important parameter of any characterization setup, especially when large sample volume is considered.

One potential benefit of complete on-chip integration is the ability to design each of the individual system components according to specific characterization needs. However, this particular system is designed with generality in mind, and can in fact be used for a variety of electrical measurements on large statistical device sample sets. This flexibility is demonstrated by applying the characterization system in the context of both combined C-V/I-V dc measurements and random telegraph noise (RTN) time domain measurements, with the potential for many more experiments still there. The generality of the proposed characterization methodology is one of its main appeals, and it should be noted that the described approach can be extended to I-V and C-V variability characterization of other front-end-of-line (FEOL) components, as well as back-end-of-line (BEOL) components with very little overhead.

The on-chip characterization system is designed with maximum process compatibility in mind. Although there are a number of analog circuit blocks integrated on chip, no special analog devices or process options are used in the design of these blocks. Instead, basic thick-oxide I/O transistors are used to implement all analog functionality. These devices can be operated at 2.0 V supply, allowing for the necessarily voltage headroom to bias the digital DUTs at voltages of up to 1.1 V. Additionally, these devices have a minimum length of 0.44  $\mu m$ , which results in a comparatively larger intrinsic gain, due to the lack of various short-channel effects, at the expense of reduced intrinsic speed. Since the sampling rates of interest are below 1 MHz, the reduced speed is not an issue, whereas the increased gain is essential for accurate analog-to-digital conversion.

The design is highly modular and individual circuit blocks are reused whenever possible. While this may not be the most efficient design approach, power efficiency and, to a lesser degree, area efficiency are not of significant concern in this particular design.

Instead, a more fundamental design goal is to simplify the porting of the characterization system to new technology nodes. This is accomplished in a highly-modular design, as ultimately only a small number of sensitive analog blocks have to be redesigned in the new process. Using thick-oxide devices helps in this regard as well, since these devices tend to remain largely unchanged from one technology node to the next, further reducing the necessary redesign effort.

### 3.3 On-Chip Switching Matrix and DUT array

#### 3.3.1 DUT Array

A simplified representation of the integrated DUT array and the accompanying switching matrix is shown in Fig. 3.2. Column-select and row-select signals from one-hot shift registers are used to sequentially address individual DUTs from the array. The DUT array spans 40 rows of DUTs across 56 columns. Each column contains 39 identical DUTs, in addition to one empty array cell used as a null reference. Two neighboring columns contain matched DUTs of the same type, as indicated in Fig. 3.2, allowing any gradients along the height of the DUT column to be cancelled out differentially. Overall, the measurement sample set consists of 28 different DUT types with devices spanning different lengths, widths, threshold voltages, and environments, with a statistical set size of 78 DUTs per DUT type. Two test arrays containing NMOS and PMOS DUTs are weaved parallel to one another, sharing many of the global digital control signals, but with completely electrically isolated analog signal paths and dedicated on-chip characterization systems.

A detailed view of the individual DUT cell and the associated switches is shown in Fig. 3.3. The relative sizing of the switches is indicated on the schematic. Each terminal can be connected to a voltage sense path, which is ultimately routed to the integrated voltage-mode ADC. Since this is a high impedance sense path, minimum size switches are used. The source and drain terminals have dedicated switches used to contact the device during measurement. Since the current measurement path is a low-impedance path, larger switches

Figure 3.2: A simplified schematic of the DUT array and associated on-chip switching matrix.

Figure 3.3: A simplified schematic of an NMOS DUT cell and the associated switches; different size switches are used depending on weather the switches connect to a high- or a low-impedance signal path.

are used. On the gate side, there are two switches, either one of which can be used to provide the gate bias. The need for two identical switches is described in detail in Chapter 4, where the charge-based capacitance measurement (CBCM) technique is discussed. Since the gate presents a high-impedance, minimum-size switches are used. Each terminal also has a path that allows it to be tied to ground. The source and drain terminals have to be discharged during the CBCM C-V characterization. Additionally, the gate terminal is tied to ground when the cell is not selected, in order to reduce leakage during an I-V measurement. In the case of an NMOS DUT, the body is tied to ground since the body potential is set by the shared substrate potential. In the case of a PMOS DUT, since each DUT has a dedicated N-well associated with it, the body can also be biased through a set of switches identical to those at the gate (not shown). Apart from this, the only other difference between the NMOS and the PMOS DUT cell is that the PMOS DUT cell enables all terminals to be shorted to the analog supply,  $V_{DD,A}$ , rather than ground, as needed by the opposite polarity C-V measurement.

#### 3.3.2 Switch Design

Switches in the array are implemented using thick-oxide CMOS transmission gates, offering low leakage in the off state and and allowing high voltage swings. The schematic of a transmission gate switch is shown in Fig. 3.4(a). The NMOS and PMOS transistors are identically sized with  $W/L = 3.9 \ \mu m/0.44 \ \mu m$  for a unit switch with a nominal on-resistance of approximately 500  $\Omega$ . In order to decrease the on-resistance of switches in low-impedance paths, the width of the transistors is proportionally increased. Equal NMOS and PMOS sizing tends to keep the resistance of the switch relatively constant over the entire bias range [73]. Since all digital control signals on-chip are generated and distributed using 1.1 V native-oxide devices, a level-shifter circuit is used to transition between 1.1 V ( $V_{DD,D}$ ) and 2.0 V ( $V_{DD,A}$ ) logic levels. A standard positive-feedback topology is used for the level shifter (Fig. 3.4(b)), which amplifies the digital logic signals and generates complimentary outputs as needed for the CMOS transmission gate. Each analog switch has a dedicated

level-shifter.

Figure 3.4: (a) Transmission gate implementation of analog switch; (b) a positive-feedback level-shifter used to step-up 1.1 V ( $V_{DD,D}$ ) digital control signals to 2.0 V ( $V_{DD,A}$ ) analog levels; Table 3.2 gives sizing for the transistors in the positive-feedback latch.

In order to be able to integrate a large number of DUTs in a single DUT array, it is essential that the switches in the on-chip switching matrix provide enough isolation between DUTs. To achieve the best isolation, the source and drain terminals of all DUTs but the one being measured are disconnected from the measurement circuitry, and their gates are connected to either ground or  $V_{DD,D}$ , depending on weather an NMOS or a PMOS DUT is measured, respectively. The series combination of the two disconnected switches and the DUT biased in its off state results in very high impedance. Fig. 3.5 shows a simulation for

Table 3.1: Level-Shifter Design Table

| Component   | Value                                                                                             |  |  |

|-------------|---------------------------------------------------------------------------------------------------|--|--|

| $MP_0/MP_1$ | $0.8~\mu m/0.44~\mu m$                                                                            |  |  |

| $MN_0/MN_1$ | $\left  \hspace{0.1cm} 3.9 \hspace{0.1cm} \mu m/0.44 \hspace{0.1cm} \mu m \hspace{0.1cm} \right $ |  |  |

the parasitic current due to a large DUT in the off-state corrupting an I-V measurement, with the associated drain-to-source voltage swept between 0 and 1.1 V. While there is a somewhat appreciable leakage of about 27 pA, most of this leakage is not due to the swept potential and can be nulled during a calibration step using the empty DUT cell present in each column. The actual measured parasitic resistance of the DUT in the off state is shown to be  $R_{OFF} = 1.37 \times 10^{15} \Omega$ . Such a high off-resistance essentially means that the density

Figure 3.5: A simulation showing the excellent isolation of a DUT placed in the off state.

of the DUT array is limited only by area considerations and more complex array structures aimed at reducing switch leakage, such as the one presented in [63], are not necessary.

# 3.4 Biasing DAC

The four-channel resistor-string DAC shown in Fig. 3.6 is used to provide each of four DUT terminal bias voltages. The four DAC channels share the same resistor string reference,

Figure 3.6: Four-channel R-string DAC with one-hot shift register control used for generating DUT bias voltages.

keeping the overall DAC area footprint small. Each channel has 256 different output levels, resulting in eight-bit precision. The control of the DAC outputs is implemented using four independent one-hot bi-directional shift registers. This unorthodox control scheme is ideally suited for generating voltage sweeps, as needed for I-V and C-V characterization, while also keeping the control circuitry simple and compact as compared to a decoder-based approach.

The unit resistor of the resistor string is implemented using a poly-silicon resistor with a nominal resistance of 67.5  $\Omega$ . The resistance value is chosen such that when all four channels are simultaneously switched to mid-code, which results in the worst RC charging time constant, the resistor string output settles to five time constants within 0.5  $\mu s$ , resulting in a maximum DAC frequency of 2 MHz. The operating frequency of the DAC is designed to be one order of magnitude higher than the sampling frequency of the analog-to-digital converters, which can be as high as 200 kHz in the desired range of operation. As a result, biasing the device at each measurement step does not factor significantly into the overall characterization time.

Each of the four DAC channels is buffered using a single-stage load-stabilized analog

voltage buffer. The transistor-level schematic of the DAC buffer is shown in Fig. 3.7(a). Similarly to all other analog circuitry in this system, the voltage buffers are implemented using high-voltage thick-oxide devices. The simulated open-loop response of the buffer driving a 10.0 pF capacitive load is shown in Fig. 3.7(b). The buffer has an open-loop gain of 47.9 dB, a gain-bandwidth product (GBP) of 76.5 MHz, and a phase margin of 74.6 deg.

The measured differential non-linearity (DNL) and integral non-linearity (INL) of the DAC are shown in Fig. 3.8. Only two of the channels characteristics are plotted for clarity; measured performance of the other two channels is similar. The DAC reference voltages,  $V_{REF+}$  and  $V_{REF-}$ , are set to 1.4 V and 0.3 V, respectively, resulting in a least significant bit nominally set to  $V_{LSB}=4.3~mV$ . As expected, the resistor-string DAC offers excellent DNL performance, with absolute maximum DNL and INL of less than 0.1  $V_{LSB}$ . While all terminal voltages are measured at the point of application making absolute DAC accuracy non-essential, as discussed in Chapter 4, it is still desirable to have a monotonic DAC, especially in the context of C-V measurements, where the differential of the applied voltage factors in. A DNL of less than 1.0  $V_{LSB}$  guarantees such monotonicity. The non-linearity of the converter is mainly caused by mismatches in the shared resistor string, which is made evident by the similarity of the INL plots for the two channels.

Table 3.2: DAC Buffer Design Table