# **Energy-Efficient Time-Based Encoders and Digital Signal Processors in Continuous Time**

## **Sharvil Patil**

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

2017

©2017

Sharvil Patil

All Rights Reserved

## **Abstract**

# **Energy-Efficient Time-Based Encoders and Digital Signal Processors in Continuous Time**

## Sharvil Patil

Continuous-time (CT) data conversion and continuous-time digital signal processing (DSP) are an interesting alternative to conventional methods of signal conversion and processing. This alternative proposes time-based encoding that may not suffer from aliasing; shows superior spectral properties (e.g. no quantization noise floor); and enables time-based, event-driven, flexible signal processing using digital circuits, thus scaling well with technology. Despite these interesting features, this approach has so far been limited by the CT encoder, due to both its relatively poor energy efficiency and the constraints it imposes on the subsequent CT DSP. In this thesis, we present three principles that address these limitations and help improve the CT ADC/DSP system.

First, an adaptive-resolution encoding scheme that achieves first-order reconstruction with simple circuitry is proposed. It is shown that for certain signals, the scheme can significantly reduce the number of samples generated per unit of time for a given accuracy compared to schemes based on zero-order-hold reconstruction, thus promising to lead to low dynamic power dissipation at the system level.

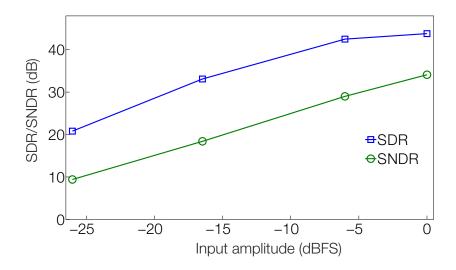

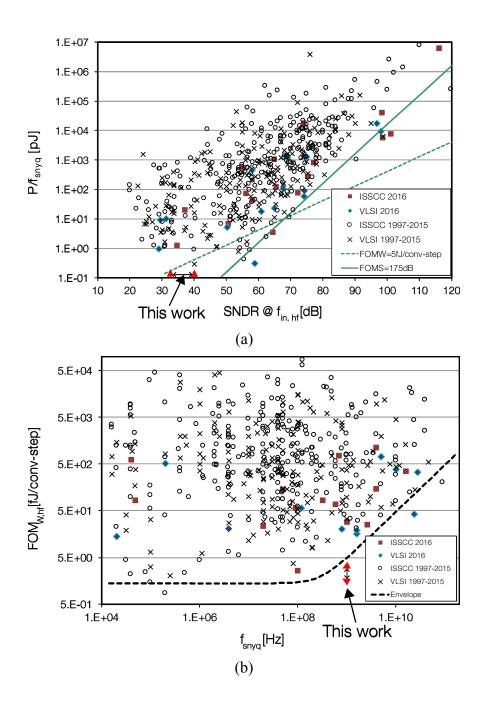

Presented next is a novel time-based CT ADC architecture, and associated encoding scheme, that allows a compact, energy-efficient circuit implementation, and achieves first-order quantization error spectral shaping. The design of a test chip, implemented in a 0.65-V 28-nm FDSOI process, that includes this CT ADC and a 10-tap programmable FIR CT DSP to process its output is described. The system achieves 32 dB - 42 dB SNDR over a 10 MHz - 50 MHz bandwidth, occupies 0.093 mm², and dissipates 15  $\mu$ W-163  $\mu$ W as the input amplitude goes from zero to full scale.

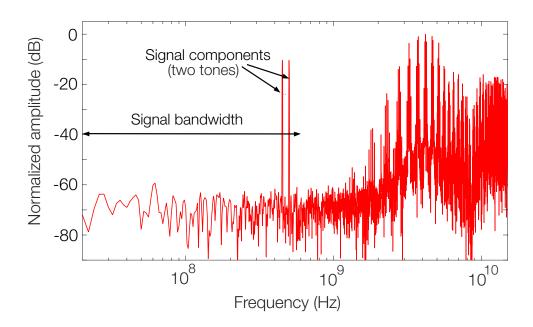

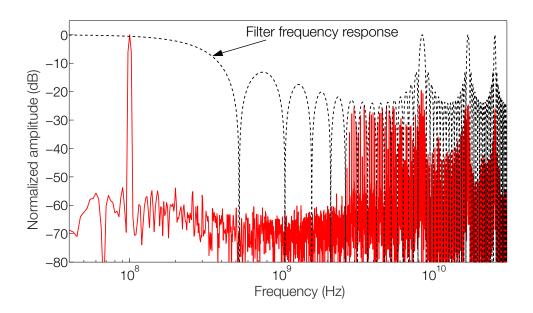

Finally, an investigation into the possibility of CT encoding using voltage-controlled oscillators is undertaken, and it leads to a CT ADC/DSP system architecture composed primarily of asynchronous digital delays. The latter makes the system highly digital and technology-scaling-friendly and, hence, is particularly attractive from the point of view of technology migration. The design of a test chip, where this delay-based CT ADC/DSP system architecture is used to implement a 16-tap programmable FIR filter, in a 1.2-V 28-nm FDSOI process, is described. Simulations show that the system will achieve a 33 dB – 40 dB SNDR over a 600 MHz bandwidth, while dissipating 4 mW.

## **Contents**

| L              | List of Figures |                                                                    |    |

|----------------|-----------------|--------------------------------------------------------------------|----|

| List of Tables |                 | xv                                                                 |    |

| 1              | Intro           | duction                                                            | 1  |

|                | 1.1             | Signal Processors and Processing Domains                           | 1  |

|                | 1.2             | Continuous-Time Data Conversion and DSP                            | 3  |

|                |                 | 1.2.1 CT ADC                                                       | 4  |

|                |                 | 1.2.2 CT DSP                                                       | 9  |

|                |                 | 1.2.3 Considerations for Low Power and Area in a CT ADC/DSP System | 14 |

|                | 1.3             | Thesis Goals and Organization                                      | 20 |

| 2              | Adap            | tive Derivative Level-Crossing Sampling                            | 23 |

|                | 2.1             | Introduction                                                       | 23 |

|                | 2.2             | Derivative Level-Crossing Sampling                                 | 26 |

|                | 2.3             | Companded DLCS                                                     | 29 |

|                | 2.4             | Adaptive-Resolution (AR) DLCS                                      | 29 |

|                |                 | 2.4.1 System Description                                           | 29 |

|                |                 | 2.4.2 System Design Procedure                                      | 31 |

|                | 2.5             | SER Comparison                                                     | 32 |

|   | 2.6        | Sample Generation Rate and Figure of Merit                              | 33 |

|---|------------|-------------------------------------------------------------------------|----|

|   |            | 2.6.1 FOM Definition                                                    | 33 |

|   |            | 2.6.2 Simulation Results                                                | 34 |

|   | 2.7        | Practical Considerations.                                               | 36 |

|   | 2.8        | Conclusions                                                             | 37 |

| 3 | An Eı      | rror-Shaping Alias-Free CT ADC/DSP/DAC System                           | 38 |

|   | 3.1        | Introduction                                                            | 38 |

|   | 3.2        | Overview of Existing Medium-Resolution CT ADC Architectures             | 40 |

|   | 3.3        | Proposed CT ADC Architecture                                            | 42 |

|   |            | 3.3.1 Operation                                                         | 42 |

|   |            | 3.3.2 Model                                                             | 44 |

|   |            | 3.3.3 Design Considerations                                             | 47 |

|   |            | 3.3.4 CT ADC Integrated Implementation                                  | 50 |

|   |            | 3.3.5 Measurement Results                                               | 57 |

|   |            | 3.3.6 Comparison of CT ADC with the State of the Art                    | 64 |

|   | 3.4        | CT DSP                                                                  | 67 |

|   |            | 3.4.1 Integrated Implementation                                         | 71 |

|   |            | 3.4.2 Simulation Results                                                | 85 |

|   |            | 3.4.3 Comparison with the State of the Art                              | 90 |

|   | 3.5        | Conclusions                                                             | 91 |

| 4 | Conti      | nuous-Time Data Conversion and DSP Using Voltage-Controlled Oscillators | 92 |

|   | <i>1</i> 1 | Introduction                                                            | 02 |

| 4.2   | Pulse Width Modulation Using a VCO                | 94  |

|-------|---------------------------------------------------|-----|

|       | 4.2.1 System Architecture                         | 96  |

|       | 4.2.2 Simulation Results                          | 99  |

|       | 4.2.3 Non-Idealities and Practical Considerations | 104 |

|       | 4.2.4 Conclusions                                 | 107 |

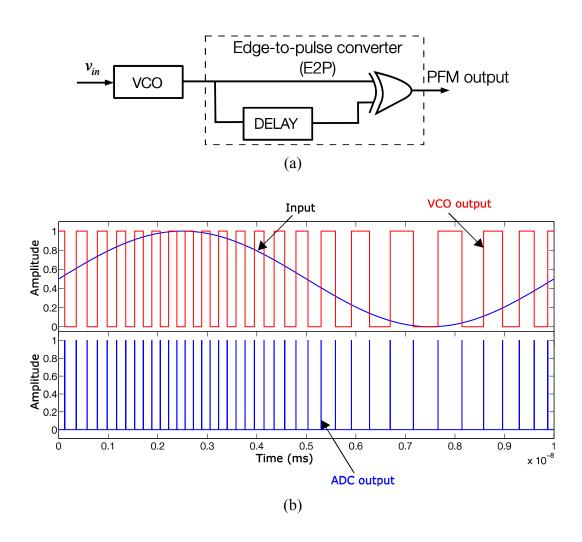

| 4.3   | Pulse Frequency Modulation Using a VCO            | 107 |

|       | 4.3.1 System Architecture                         | 108 |

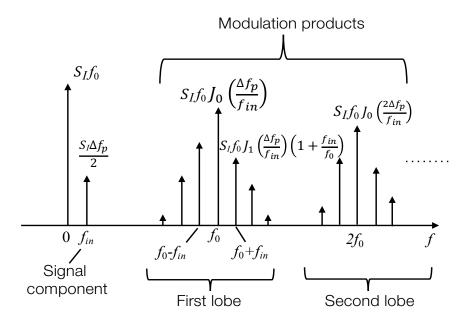

|       | 4.3.2 System Model and Spectral Description       | 112 |

|       | 4.3.3 Simulation Results                          | 121 |

|       | 4.3.4 Practical Considerations.                   | 126 |

|       | 4.3.5 Conclusions                                 | 128 |

| 4.4   | 4 Chapter Summary                                 | 128 |

| 5 A I | Delay-Based CT ADC/DSP/DAC System                 | 129 |

| 5.1   | I Introduction                                    | 129 |

| 5.2   | 2 Top-level Architecture                          | 130 |

|       | 5.2.1 Choice of Tap Delay, τ                      | 132 |

|       | 5.2.2 PFM Encoder Architecture                    | 134 |

| 5.3   | 3 Integrated Implementation                       | 141 |

|       | 5.3.1 Specifications and Targets                  | 141 |

|       | 5.3.2 Delay Cell Design for Delay Line            | 144 |

|       | 5.3.3 Delay Cell Design for the ADC               | 150 |

|       | 5.3.4 MDAC Design                                 | 160 |

|       |                                                   |     |

|      |      | 5.3.6 System-Level Simulation Results and Comparisons | 169 |

|------|------|-------------------------------------------------------|-----|

| 5.   | .4   | Conclusions                                           | 178 |

| 6 C  | onc  | lusions                                               | 179 |

| 6.   | .1   | Thesis Contributions                                  | 179 |

| 6.   | .2   | Suggestions for Future Work                           | 180 |

| Bibl | liog | raphy                                                 | 186 |

# **List of Figures**

| 1.1. Signal processing alternatives based on signal domains                            | 2                          |

|----------------------------------------------------------------------------------------|----------------------------|

| 1.2. A typical CT DSP signal processing chain.                                         | 3                          |

| 1.3. Level-crossing sampling: When an input crosses a level, the digital out           | put transitions to a code  |

| that corresponds to that level.                                                        | 4                          |

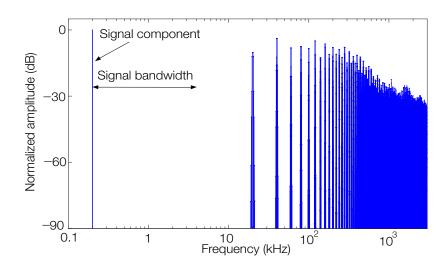

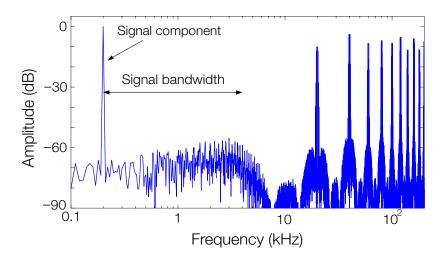

| 1.4. Spectral comparison between DT and CT ADCs [1]. For sinusoidal inp                | outs, CT ADCs produce      |

| only harmonic distortion in the output spectrum, whereas DT ADC                        | s additionally alias the   |

| distortion components, thereby creating "quantization noise floor"                     | 6                          |

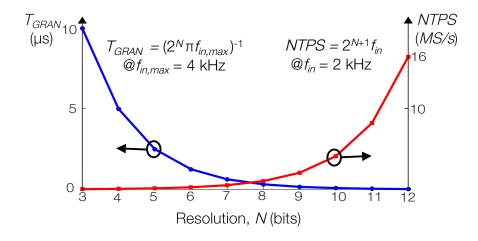

| 1.5. An example plot showing the exponential worsening of $NTPS$ and $T_{GR}$          | RAN with LCS quantizer     |

| resolution                                                                             | 8                          |

| 1.6. The CT DSP that follows the CT ADC uses a transversal structure to in             | mplement an FIR filter.    |

|                                                                                        | 9                          |

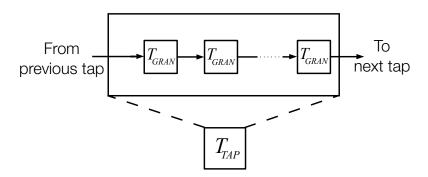

| 1.7. To preserve timing details, each tap delay, $T_{TAP}$ , is implemented as a       | a cascade of unit delay    |

| cells, each with a delay of $T_{GRAN}$                                                 | 10                         |

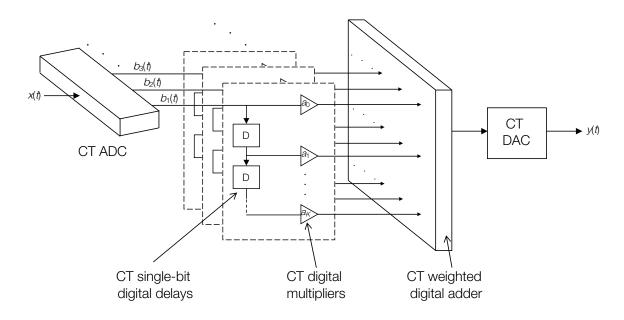

| 1.8. System-level view of the CT ADC/DSP/DAC system from Ref. [17]                     | 11                         |

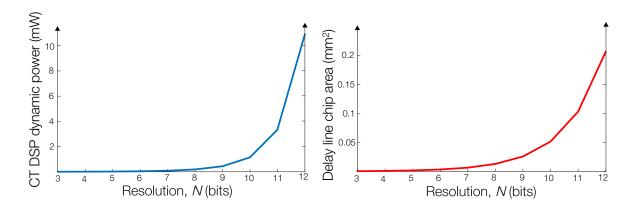

| 1.9. Dynamic power dissipation and delay line chip area of an 8-tap FIR (              | CT DSP with $T_{TAP} = 25$ |

| $μ$ s and for $f_{in}$ = 2 kHz, estimated using (1.1) and (1.2), using typical $μ$     | numbers obtained from      |

| Ref. [16]: $E_{Del} = 50$ fJ, $E_{Arithmetic} = 150$ pJ, $A_{Del} = 20 \mu \text{m}^2$ | 13                         |

| 1.1( | D. Diagram depicting design considerations for achieving low power in a CT DSP system 13             |

|------|------------------------------------------------------------------------------------------------------|

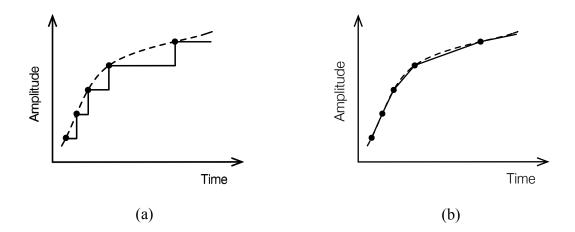

| 2.1. | Comparison of (a) zero-order and (b) first-order reconstruction.                                     |

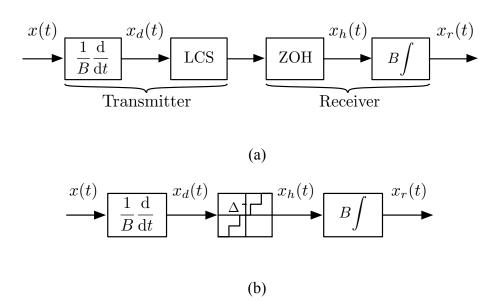

| 2.2. | Principle of derivative level-crossing sampling scheme: (a) actual scheme in a communication         |

|      | system; (b) conceptually equivalent system for analysis purposes                                     |

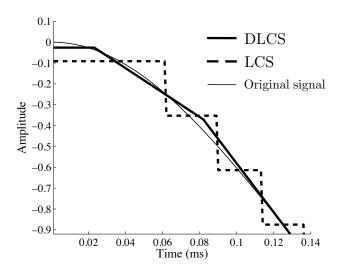

| 2.3. | Blow-up of DLCS (first-order) and LCS (zero-order) reconstruction for a full-scale sinusoida         |

|      | input signal at 2 kHz. 26                                                                            |

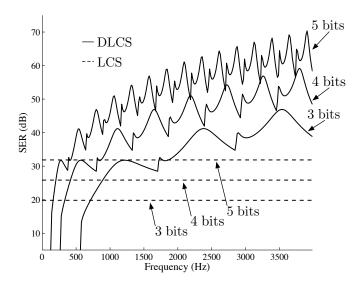

| 2.4. | Signal-to-error ratio (SER) for full-scale sinusoids using DLCS reconstruction; dashed lines         |

|      | correspond to the LCS SER: 6.02 <i>N</i> +1.76 dB for <i>N</i> bits of resolution.                   |

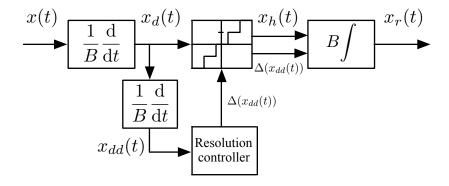

| 2.5. | Adaptive-resolution derivative level-crossing sampling and reconstruction principle                  |

|      | $\Delta(xdd(t))$ denotes the variable quantization step size, which depends on the value of $xdd(t)$ |

|      | 30                                                                                                   |

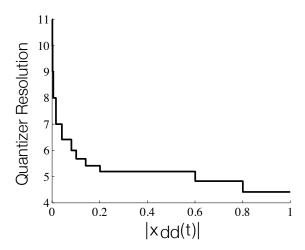

| 2.6. | Quantizer resolution versus the magnitude of the second derivative of the input for the system       |

|      | depicted in Fig. 2.5. We consider full-scale sinusoids from 0 to 4 kHz                               |

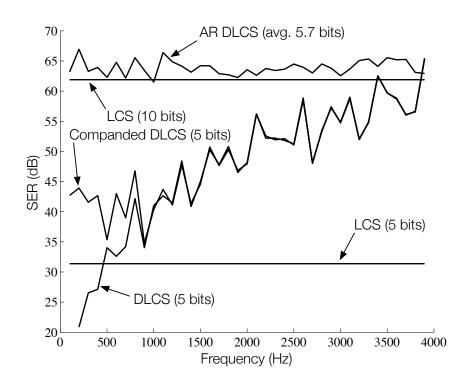

| 2.7. | Signal-to-error ratio (SER) for DLCS, companded DLCS, AR DLCS—where quantize                         |

|      | resolution varies from 4.5 to 11 bits with an average resolution of around 5.7 bits—, and LCS        |

|      | for full-scale sinusoidal inputs.                                                                    |

| 3.1. | Processing alternatives based on signal domain type in the ULP RX system context 39                  |

| 3.2. | The asynchronous delta modulator architecture used in prior work                                     |

| 3.3. | Proposed CT ADC architecture. 42                                                                     |

| 3.4. | Example waveforms of the differential input, output and some key internal signals 43                 |

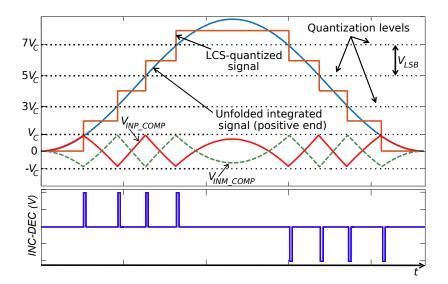

| 3.5. | Illustrating the development of a model for the ADC of Fig. 3.3, with a sinusoidal input (not           |

|------|---------------------------------------------------------------------------------------------------------|

|      | shown). The two upper waveforms are fictitious ones (see text). The ADC generates pulses                |

|      | at instants where the LCS-quantized version of the unfolded integrated signal makes step-               |

|      | transitions. 45                                                                                         |

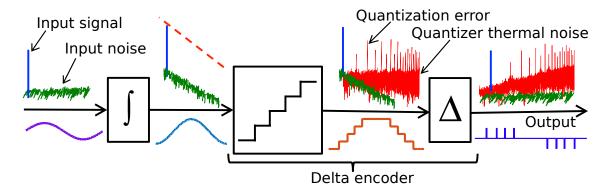

| 3.6. | The proposed ADC is modeled as a cascade of an integrator, a level-crossing sampling                    |

|      | quantizer, and a $\Delta$ block (which behaves like a differentiator). The input signal and input noise |

|      | components pass through an integrator-differentiator cascade and come out without                       |

|      | frequency shaping. The quantizer adds quantization error and thermal noise, which are first-            |

|      | order shaped by the differentiator transfer function of the $\Delta$ block. Time waveforms are shown    |

|      | below the corresponding spectra                                                                         |

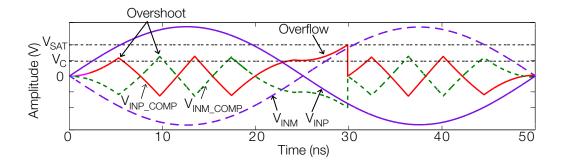

| 3.7. | Example showing overshoots and an overflow situation when the integrator input changes                  |

|      | sign while its output has exceeded the comparison window set by $V_C$ . A crossing of $V_{SAT}$ is      |

|      | detected and integrator outputs are reset. 48                                                           |

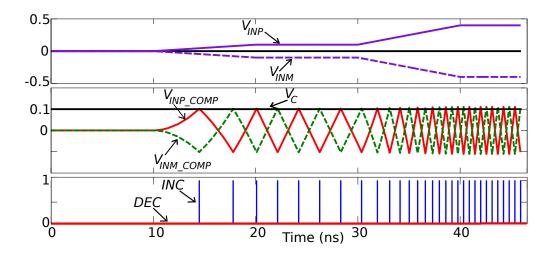

| 3.8. | The output token rate of the ADC increases in proportion to the input signal amplitude. A               |

|      | higher amplitude results in faster integration, and hence, a higher rate of threshold crossings.        |

|      | The polarity of the output (INC/DEC) depends on that of the input                                       |

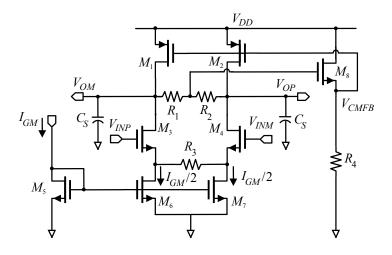

| 3.9. | Transconductor $(G_m)$ - $C$ integrator circuit. 51                                                     |

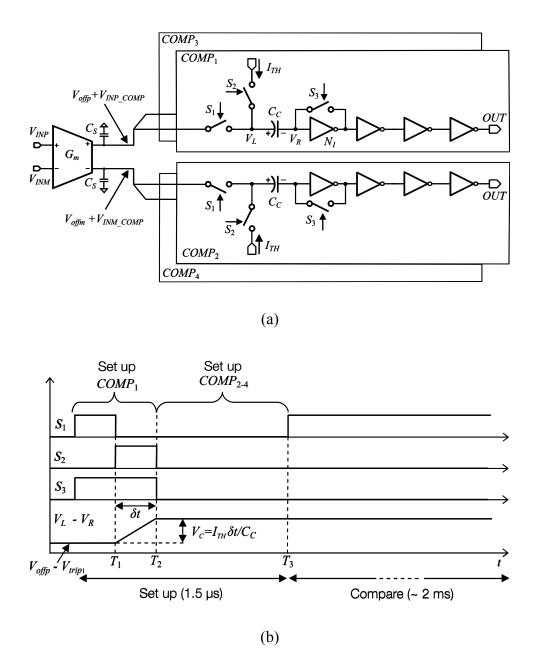

| 3.10 | . (a) Threshold setting scheme with the comparator architecture. (b) Waveforms illustrating             |

|      | the threshold setting mechanism. 52                                                                     |

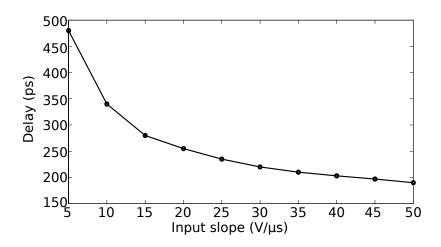

| 3.11 | . The comparator delay drops as the slope of its input increases                                        |

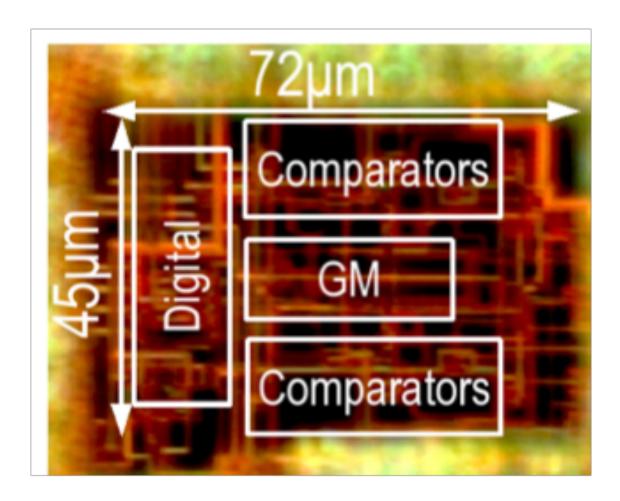

| 3 12 | CT ADC chip micrograph 57                                                                               |

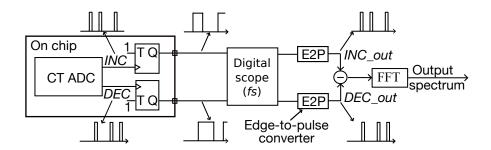

| 3.13. Output extraction and reconstruction. The output spectrum is obtained by performing an FF                 |

|-----------------------------------------------------------------------------------------------------------------|

| on the difference between <i>INC_out</i> and <i>DEC_out</i> signals.                                            |

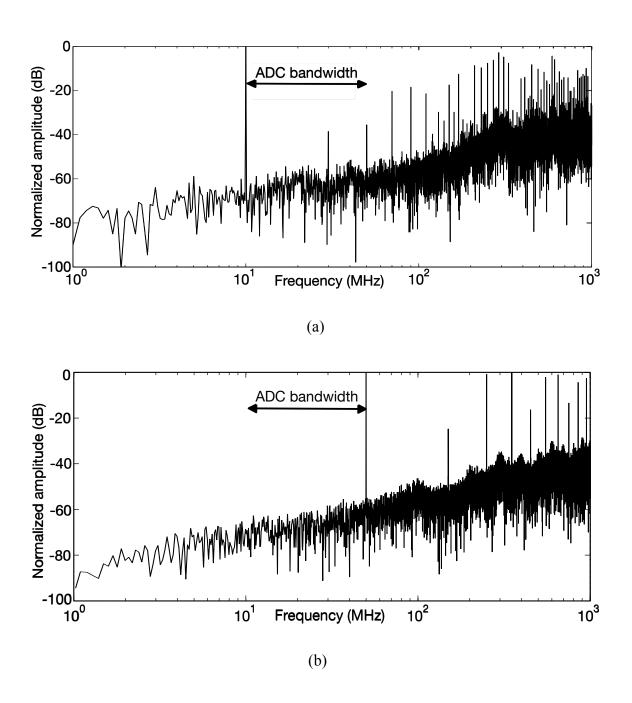

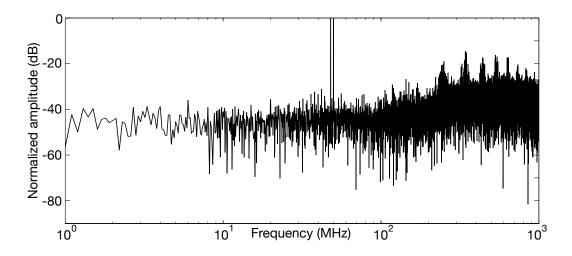

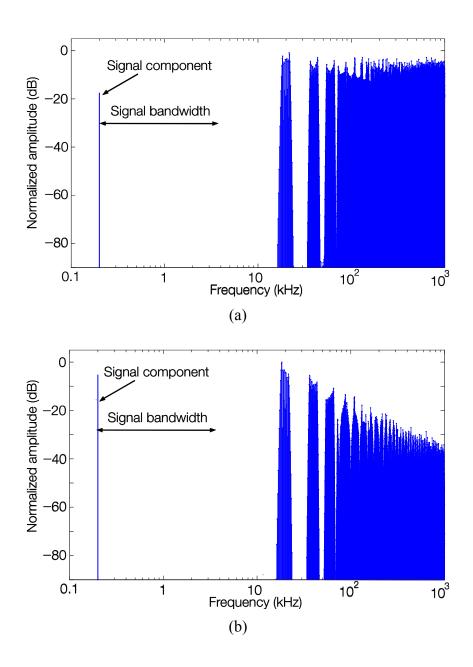

| 3.14. Measured output spectra for -3 dBFS single-tone inputs at (a) 10 MHz and (b) 50 MHz, wit                  |

| $V_C = 80$ mV and $I_{GM} = 4$ $\mu$ A. It contains the signal component and its first-order-shape              |

| harmonics5                                                                                                      |

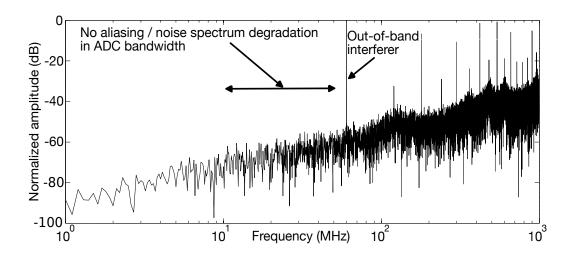

| 3.15. An out-of-band test tone at 60 MHz does not result in any degradation due to aliasing of                  |

| increased noise ( $V_C = 80 \text{ mV}$ and $I_{GM} = 4 \mu\text{A}$ ).                                         |

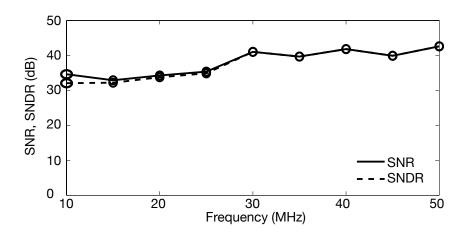

| 3.16. Plot of single-tone SNR/SNDR versus input frequency. The input amplitude is -3 dBFS, an                   |

| $V_C = 80 \text{ mV} \text{ and } I_{GM} = 4  \mu\text{A}.$                                                     |

| 3.17. Two-tone output spectrum; the input tones are at 48 MHz and 50 MHz; $V_C = 80$ mV and $I_{GL}$            |

| = $4 \mu A$ . The output consists of signal components and IM products. The low-frequency nois                  |

| floor does not show first-order shaping, and is attributed to the input noise from the two-ton                  |

| signal generator, which was different from the one used for single-tone tests                                   |

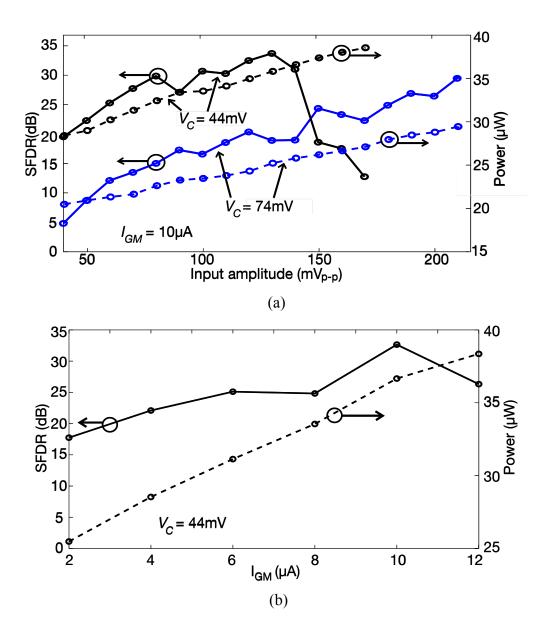

| 3.18. SFDR measurements for a two-tone input with two tones at 48 MHz and 50 MHz. $V_C$ and                     |

| $I_{GM}$ are changed from their nominal values to demonstrate programmability. (a) SFDR and                     |

| power dissipation vs. the input amplitude for different $V_C$ values with $I_{GM} = 10 \mu A$ ; (b) SFDI        |

| and power dissipation for different values of $I_{GM}$ with $V_C = 44$ mV and a 130 mV <sub>p-p</sub> input. 6. |

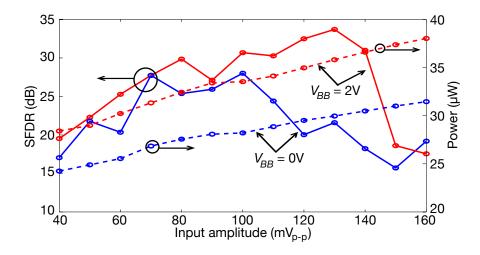

| 3.19. Effect of back-bias ( $V_{BB}$ ) used for digital circuits on ADC performance. A higher back-bia          |

| lowers delay and offers better linearity at the expense of power dissipation. Test set up is th                 |

| same as that used to generate Fig. 3.18(a), but with different values of $V_{BB}$ ( $V_{BB}$ is the absolute    |

| value of the back-gate bias, the latter being positive for NMOS and negative for PMOS) 6.                       |

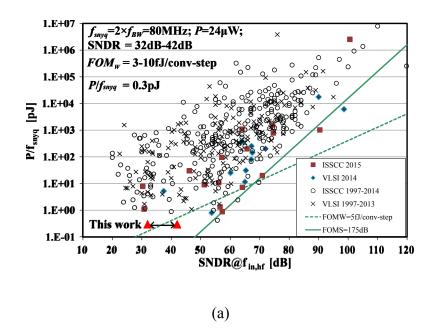

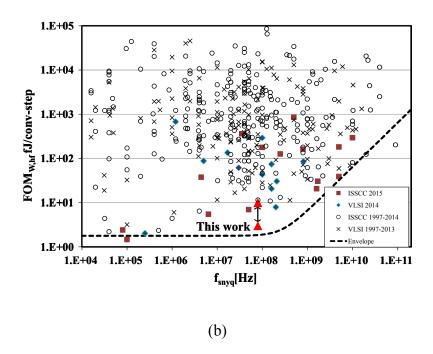

| 3.20 | . Comparison of the presented CT ADC with state-of-the-art ADCs in the Murmann survey                                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | w.r.t. (a) energy per conversion; and (b) Walden figure of merit                                                                                                                                        |

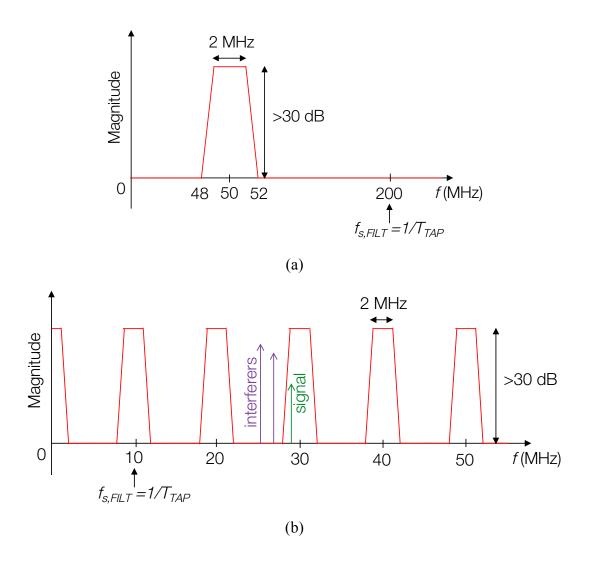

| 3.21 | . (a) Specifications for the desired filter frequency response with an example center frequency                                                                                                         |

|      | of 50 MHz and an $f_{s,FILT}$ of 200 MHz; (b) frequency response of (a) for an $f_{s,FILT}$ of 10 MHz.                                                                                                  |

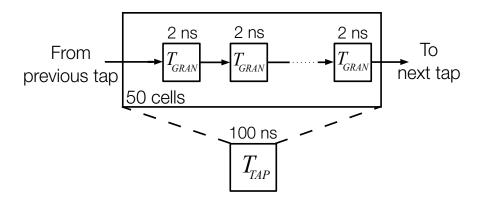

| 3.22 | . For a minimum intersample time, $T_{GRAN}$ , of 2 ns, each tap delay, $T_{TAP}$ , of 100 ns is                                                                                                        |

|      | implemented using a cascade of 50 2-ns digital delay cells                                                                                                                                              |

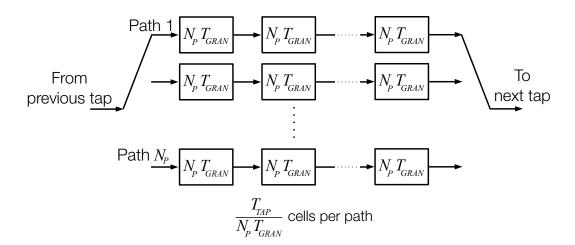

| 3.23 | . A tap delay in a parallelized delay line with $N_P$ parallel paths. Each path of the tap delay is implemented as a cascade of delay cells, each with a delay of $N_P T_{GRAN}$ . The input to the tap |

|      | is connected to one path at a time and circulated in a round-robin fashion                                                                                                                              |

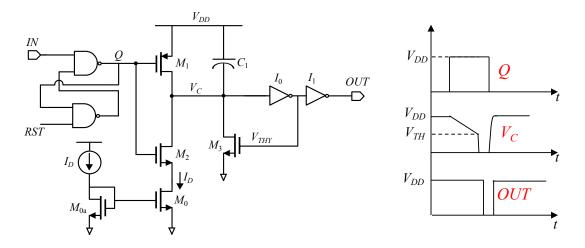

| 3.24 | . Principle of the delay cell presented in Ref. [25] along with example time waveforms 75                                                                                                               |

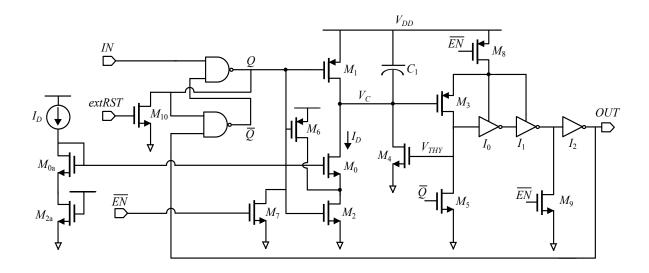

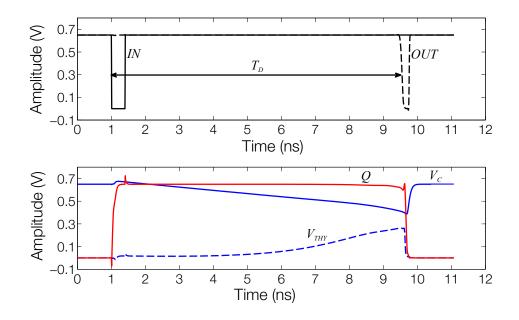

| 3.25 | . Architecture of the delay cell used in the proposed CT DSP                                                                                                                                            |

| 3.26 | . Time waveforms for some key signals in the delay cell in Fig. 3.25                                                                                                                                    |

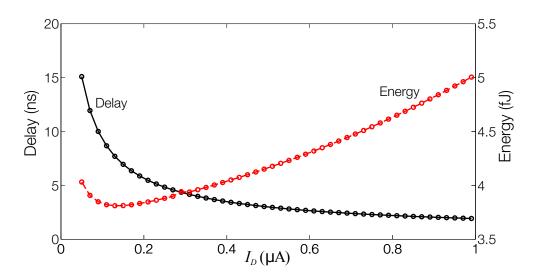

| 3.27 | . Plot of the delay and energy/operation versus the charging current, $I_D$ , for the delay cell in                                                                                                     |

|      | Fig. 3.25                                                                                                                                                                                               |

| 3.28 | One path (of the 5) in a delay tap along with the additional calibration circuitry: 2 10-ns (coarse) delay cells, 5 1-ns (fine) delay cells, and multiplexers for programmability 80                    |

| 3.29 | . Schematic of the arithmetic unit (multipliers and adder) [50]                                                                                                                                         |

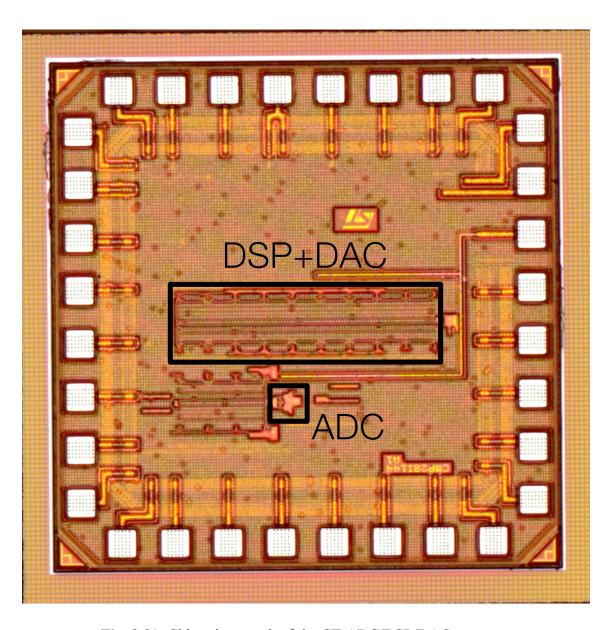

| 3.30 | . Chip micrograph of the CT ADC/DSP/DAC system                                                                                                                                                          |

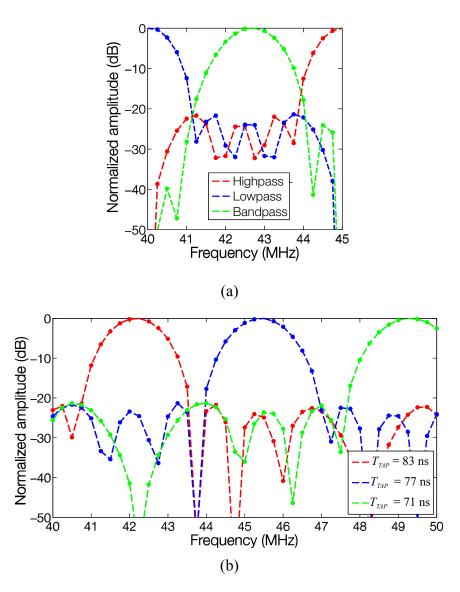

| 3.31 | . The CT DSP is configured in simulations to implement different frequency responses (a) by                                                                                                             |

|      | changing tap coefficients, $c_{0.9}$ ; and (b) by tuning the tap delay, $T_{TAP}$                                                                                                                       |

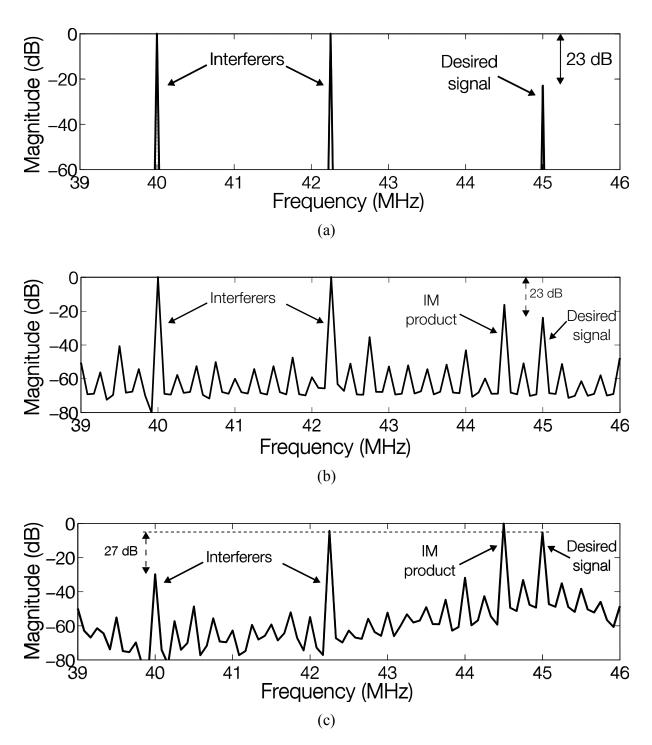

| 3.32 | . Interferer rejection using the CT/ADC/DSP/DAC system: (a) Input spectrum, with a weak       |

|------|-----------------------------------------------------------------------------------------------|

|      | signal and strong interfering components; (b) spectrum at the CT ADC output; and (c) that at  |

|      | the CT DSP output. 87                                                                         |

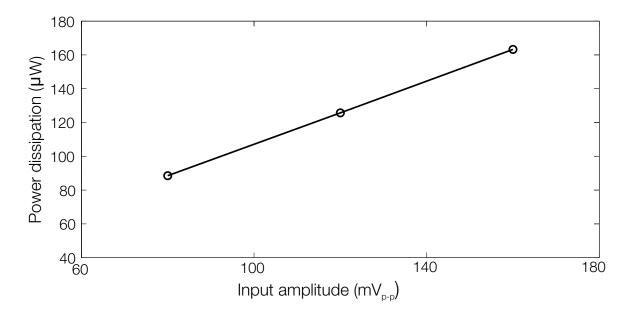

| 3.33 | . Power dissipation of the entire CT ADC/DSP/DAC system, configured as a bandpass filter      |

|      | with a passband center frequency of 50 MHz, versus input amplitude for a single-tone input    |

|      | at 50 MHz                                                                                     |

|      |                                                                                               |

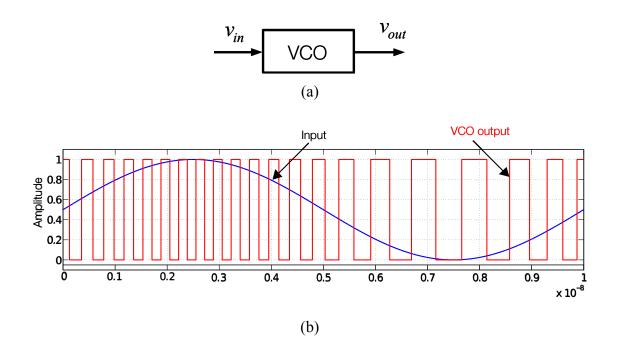

| 4.1. | (a) A general VCO; and (b) its terminal waveforms                                             |

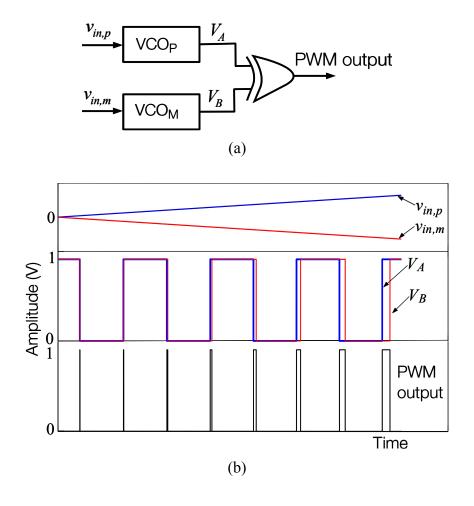

| 4.2. | (a) Pseudo-differential voltage-controlled oscillators implementing an analog integrator; (b) |

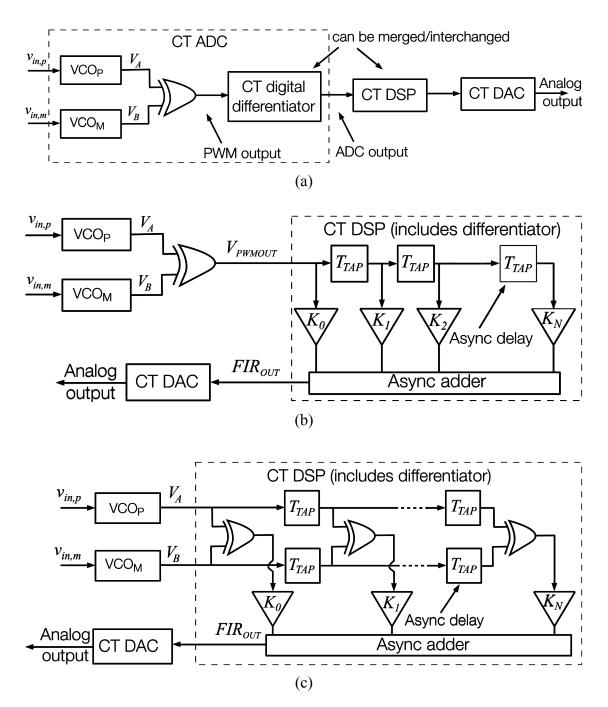

|      | example waveforms. 94                                                                         |

| 4.3. | CT ADC/DSP/DAC systems based on pseudo-differential VCOs: (a) general system; (b)             |

|      | general system with details of CT DSP block; (c) practical CT DSP implementation for          |

|      | avoiding very narrow pulses. 97                                                               |

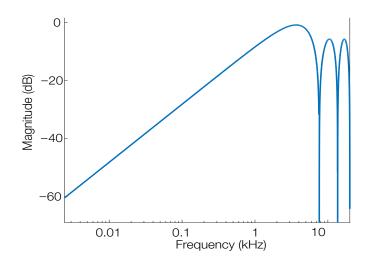

| 4.4. | Differentiator transfer function                                                              |

| 4.5. | Spectrum of the output of the VCO-based PWM encoder (post differentiation) for a full-scale   |

|      | single-tone input at 200 Hz. 100                                                              |

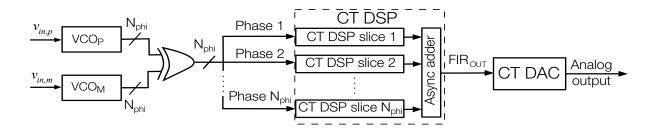

| 4.6. | System implementation for multiphase operation—each DSP slice has the CT DSP                  |

|      | architecture shown in Fig. 4.3(c).                                                            |

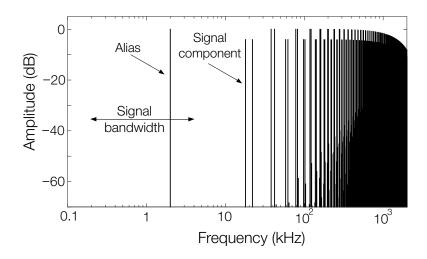

| 4.7. | Example spectrum demonstrating aliasing in the proposed system                                |

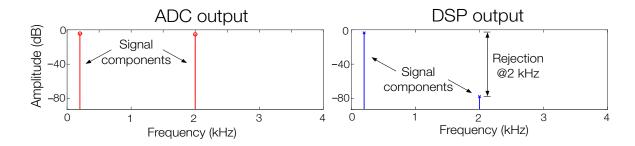

| 4.8. | Spectrum of the output of the proposed ADC and that of the following DSP for a two ton                                                            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|      | input with two tones at 200 Hz and 2 kHz. The DSP is a 67 <sup>th</sup> -order low-pass FIR filter wit                                            |

|      | an <i>f</i> <sub>-3dB</sub> of 500 Hz                                                                                                             |

| 4.9. | Output spectrum from Fig. 4.5 repeated with 4-kHz-bandlimited (voltage) white noise adde                                                          |

|      | at the input of the VCOs. 10                                                                                                                      |

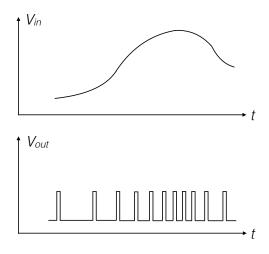

| 4.10 | An example of pulse frequency modulation. 10                                                                                                      |

| 4.11 | (a) A VCO-based PFM encoder with (b) example waveforms                                                                                            |

| 4.12 | A typical output spectrum of a pulse-frequency modulated signal. The componer                                                                     |

|      | magnitudes are from the expression in (4.6)                                                                                                       |

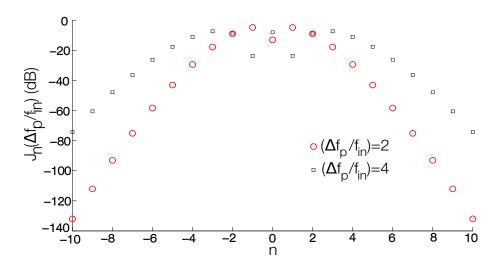

| 4.13 | Plot of $J_n(\frac{\Delta fp}{f_{in}})$ (in dB) versus n for two different values of $(\frac{\Delta fp}{f_{in}})$ ; the higher the latter's value |

|      | the slower the fall in the value of the Bessel function w.r.t. n                                                                                  |

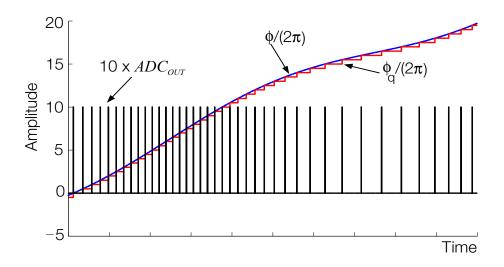

| 4.14 | Example waveforms to demonstrate the phase-domain model of the PFM encoder. The                                                                   |

|      | encoder output is amplified by 10× for better visibility                                                                                          |

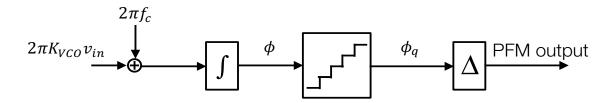

| 4.15 | The PFM encoder is modeled as one that integrates the input signal with an offset to generate                                                     |

|      | the phase signal of (4.13), then quantizes this signal, and produces a pulse at every step of the                                                 |

|      | quantized signal. The latter operation is achieved through the $\Delta$ block                                                                     |

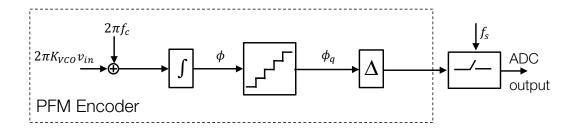

| 4.16 | A DT VCO ADC can be modeled as a cascade of a PFM encoder and a clocked sample                                                                    |

|      |                                                                                                                                                   |

| 4.17 | Spectra of the PFM-encoded output for a single-tone input at 200 Hz with the output (a) i                                                         |

|      | impulse-form and (b) with $T_{PW} = 40 \mu s$ .                                                                                                   |

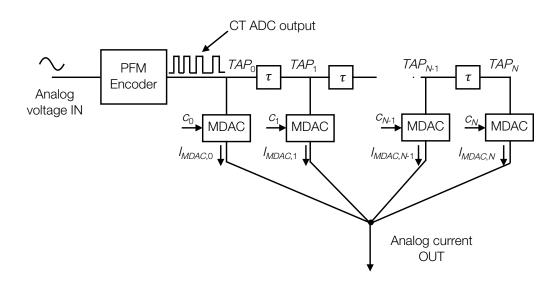

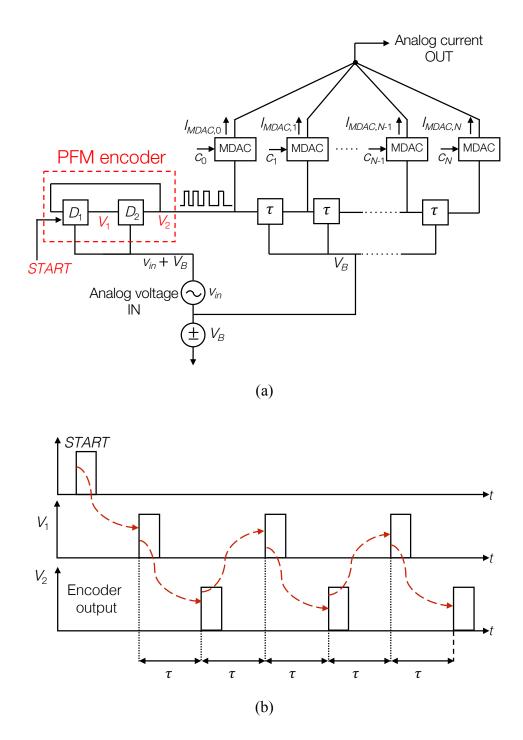

| 5.1. | Top-level architecture of the PFM-encoder-based CT ADC/DSP/DAC system. The PFM                       |

|------|------------------------------------------------------------------------------------------------------|

|      | encoder produces a 1-bit pulse train at its output, and the CT DSP delays it along a tapped          |

|      | delay line composed of asynchronous delays (labelled $\tau$ ). The multiplying DAC (MDAC             |

|      | multiplies the pulses at each tap output with a coefficient $c_i$ and outputs a proportional current |

|      | The output currents of all MDACs are summed by shorting their outputs together and                   |

|      | connecting to a low-impedance node                                                                   |

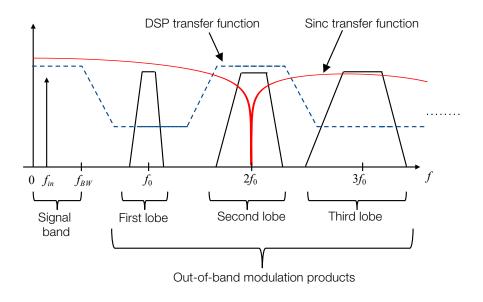

| 5.2. | The out-of-band modulation products are rejected using a combination of the CT DSP transfer          |

|      | function and the sinc transfer function created by using a non-zero pulse width for the PFM          |

|      | output                                                                                               |

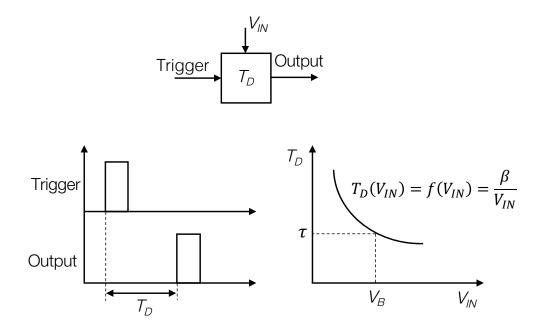

| 5.3. | The asynchronous digital delay cell; example time waveforms; and its $T_D(V_{IN})$ characteristic    |

|      | When input equals $V_B$ the delay of the cell is $\tau$ .                                            |

| 5.4. | (a) A PFM encoder made out of two asynchronous digital delays identical to the ones in the           |

|      | following CT DSP (also shown); and (b) example waveforms at the PFM encoder terminals                |

|      | following a <i>START</i> signal trigger                                                              |

| 5.5. | Parallelized version of the PFM-encoder-based CT ADC/DSP/DAC system from Fig. 5.4(a)                 |

|      |                                                                                                      |

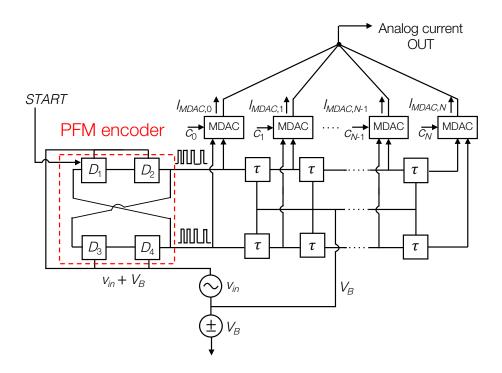

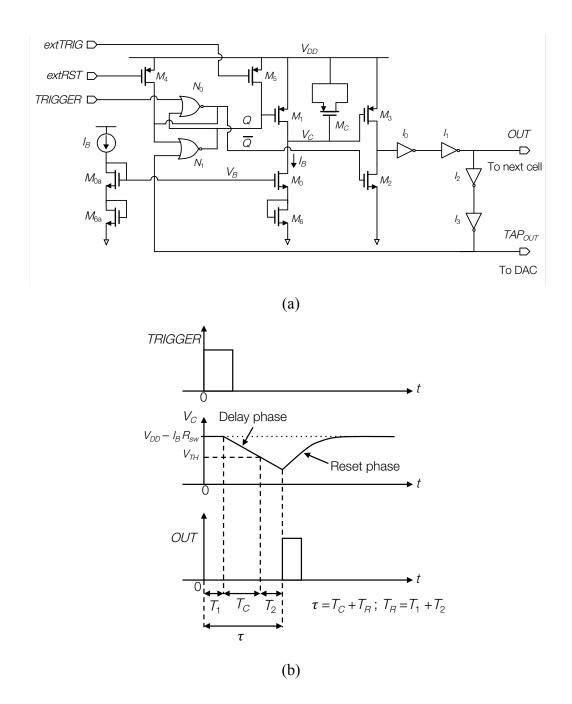

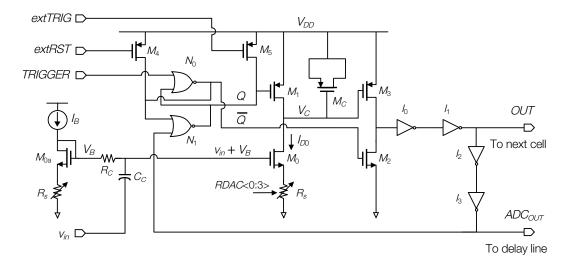

| 5.6. | (a) Architecture of the delay cell used in the delay line; and (b) time waveforms depicting          |

|      | operation. 145                                                                                       |

| 5.7. | Architecture of the delay cell used in the ADC150                                                    |

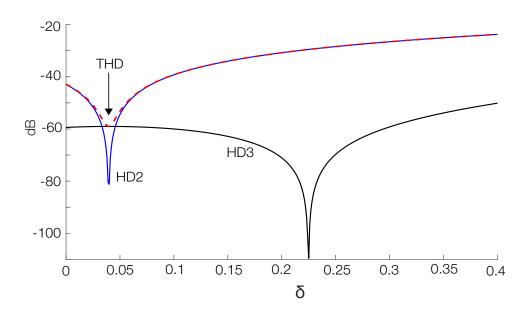

| 5.8. | Plot of HD2, HD3, and THD versus δ                                                                   |

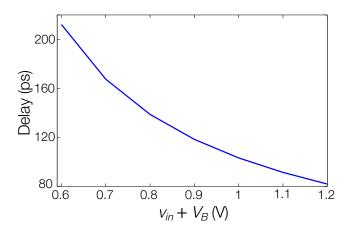

| 5.9. | Plot of delay of the asynchronous delay cell in the ADC versus input voltage, $v_{in} + V_{B}$ 159   |

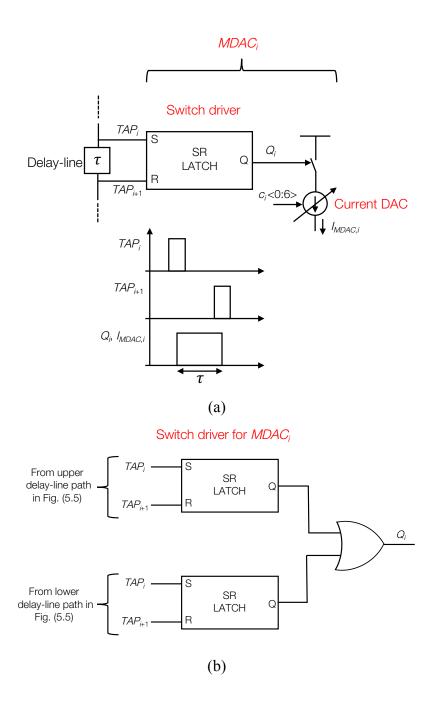

| 5.10 | . (a) The switch driver for $MDAC_i$ is made of an SR latch, which is set by $TAP_i$ and reset by        |

|------|----------------------------------------------------------------------------------------------------------|

|      | $TAP_{i+1}$ ; its resulting output, $Q_i$ , then controls the switches of the 7-bit current DAC. (b) For |

|      | the two-path delay line structure, each $MDAC_i$ has two SR-latches, whose outputs are                   |

|      | combined using an OR gate to generate the final control output $Q_i$                                     |

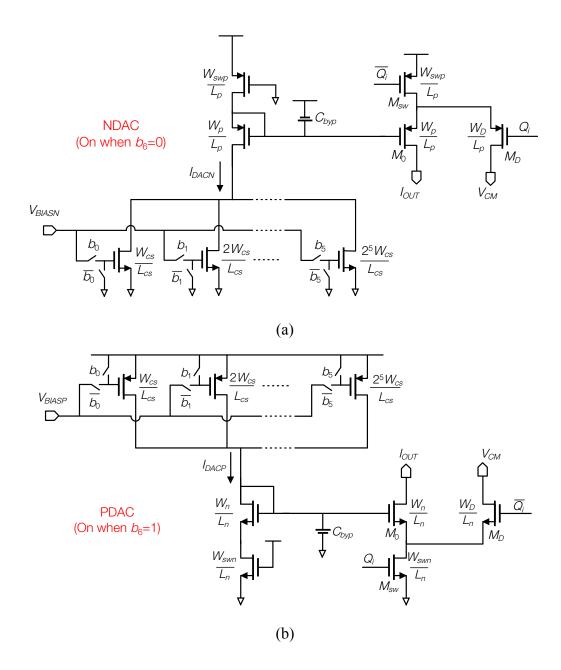

| 5.11 | . Current-mode (a) NMOS DAC (NDAC) and (b) PMOS DAC (PDAC), 6-bit each, together                         |

|      | implement a 7-bit DAC. Both DACs can never be on at the same time                                        |

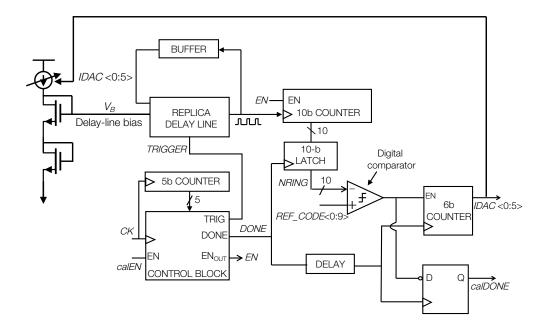

| 5.12 | . Calibration loop for calibrating the delay of the cells in the delay line                              |

| 5.13 | . Calibration loop for calibrating $V_{Rs}$                                                              |

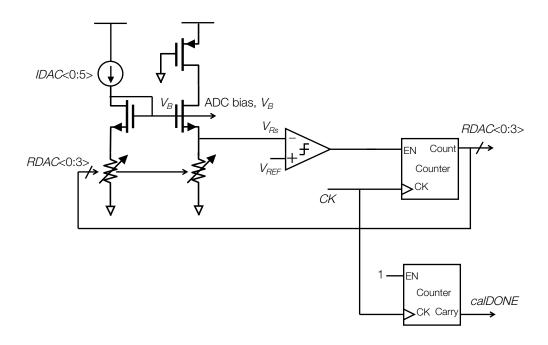

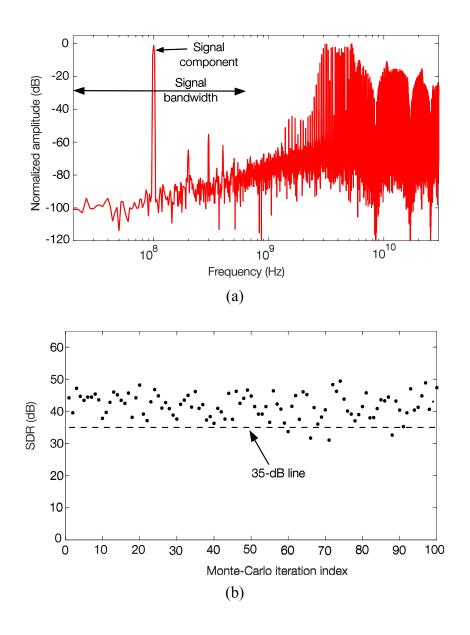

| 5.14 | . (a) ADC output spectrum obtained from a noiseless transient simulation for a full-scale                |

|      | single-tone input at 100 MHz. (b) SDR vs. iteration number for a Monte-Carlo simulation.                 |

|      |                                                                                                          |

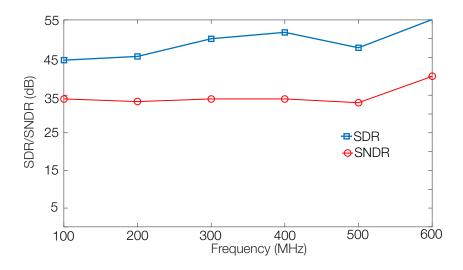

| 5.15 | . Plot of in-band SDR and SNDR of the PFM encoder output versus single-tone input                        |

|      | frequency                                                                                                |

| 5.16 | . Plot of in-band SDR and SNDR of the PFM encoder output versus input amplitude for a                    |

|      | single-tone input at 100 MHz.                                                                            |

| 5.17 | . ADC output spectrum for a two-tone input with two equal-amplitude tones at 450 MHz and                 |

|      | 500 MHz obtained from a transient noise simulation. 173                                                  |

| 5.18 | . Placement of the proposed ADC in the (a) energy plot and (b) the Walden FOM plot of the                |

|      | Murmann survey [49]                                                                                      |

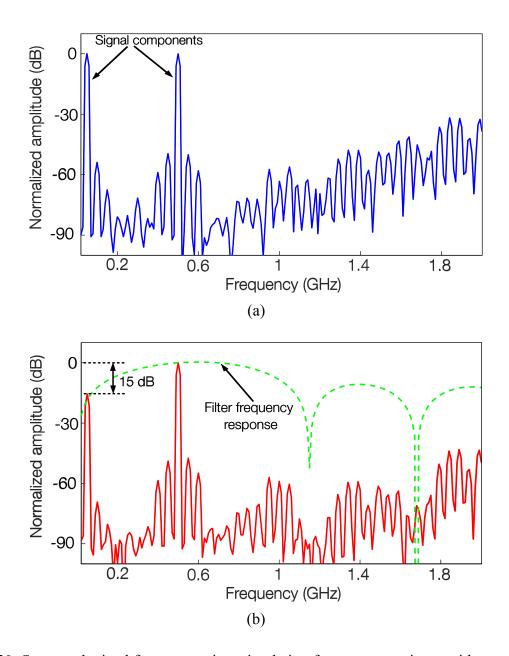

| 5.19. System output spectrum, obtained from a transient noise simulation, for a full-scale single- |

|----------------------------------------------------------------------------------------------------|

| tone input at 100 MHz when the DSP is configured to implement a 16-tap decimation filter;          |

| filter frequency response is also shown (dashed).                                                  |

| 5.20. Spectra obtained from a transient simulation for a two-tone input with two tones at 50 MHz   |

| and 500 MHz, and with the DSP configured to implement a 16-tap high-pass transfer                  |

| function. (a) ADC output spectrum; and (b) system output spectrum, showing a 15 dB                 |

| attenuation of the component at 50 MHz relative to the one at 500 MHz. Filter frequency            |

| response is also shown (dashed).                                                                   |

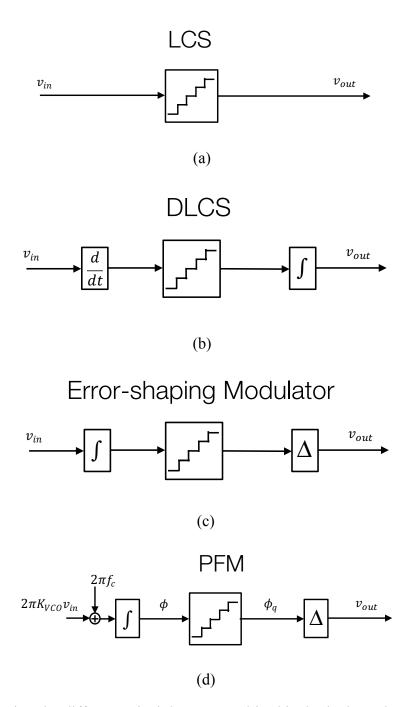

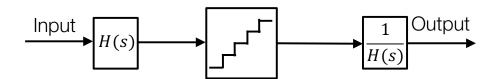

| 6.1. Connecting the different principles proposed in this thesis through models of (a) an LCS      |

| quantizer; (b) the DLCS quantizer of Chap. 2; (c) the error-shaping modulator of Chap. 3;          |

| and (d) the PFM encoder of Chaps. 4-5.                                                             |

| 6.2. A general CT encoder can be developed by preceding an LCS quantizer with a general transfer   |

| function $H(s)$ and by following it with the inverse of the transfer function                      |

## **List of Tables**

| 1.1 | signal domains and corresponding processors for continuous/discrete combinations of time        |  |  |  |

|-----|-------------------------------------------------------------------------------------------------|--|--|--|

|     | and amplitude1                                                                                  |  |  |  |

| 1.2 | Performance summary of prior CT ADC work                                                        |  |  |  |

| 1.3 | Comparison of prior CT DSP work with state-of-the-art DT DSPs                                   |  |  |  |

| 2.1 | Performance comparison of LCS (6b), DLCS (6b), and AR DLCS (signal-dependent average            |  |  |  |

|     | resolution) for different input signals. All inputs are full scale                              |  |  |  |

| 3.1 | Sizing of transistors and values of other components in the transconductor circuit in Fig. 3.9. |  |  |  |

|     | 51                                                                                              |  |  |  |

| 3.2 | Comparison of the proposed ADC with sampled ADCs with bandwidths ≤100 MHz and                   |  |  |  |

|     | modest SNDR values. 64                                                                          |  |  |  |

| 3.3 | Comparison of the proposed ADC with other CT ADCs. 65                                           |  |  |  |

| 3.4 | Table summarizing the specifications of the FIR filter and those of its individual blocks 70    |  |  |  |

| 3.5 | Sizing/values of different components in the delay cell shown in Fig. 3.25                      |  |  |  |

| 3.6 | Summary of the delay cell performance and comparison with other similar delay cells in prior    |  |  |  |

|     | art                                                                                             |  |  |  |

| 3.7 | Comparison of proposed CT ADC/DSP/DAC system with state-of-the-art CT/DT DSPs       | P/DAC system with state-of-the-art CT/DT DSPs and |  |  |

|-----|-------------------------------------------------------------------------------------|---------------------------------------------------|--|--|

|     | analog FIR filters.                                                                 | . 90                                              |  |  |

| 4.1 | Comparison of the VCO-based PWM encoder system with an LCS CT ADC/DSP system        | for                                               |  |  |

|     | identical CT DSP specifications.                                                    | 103                                               |  |  |

| 4.2 | 2 Comparison of the VCO-based PFM encoder system with an 8-bit LCS CT ADC/DSP sys   | tem                                               |  |  |

|     | and the VCO-based PWM encoder system for identical CT DSP specifications            | 125                                               |  |  |

| 5.1 | Sizes of transistors in the delay cell used in the delay line, shown in Fig. 5.6(a) | 146                                               |  |  |

| 5.2 | Performance summary of the asynchronous digital delay cell in the delay line        | 149                                               |  |  |

| 5.3 | Sizes of transistors in the delay cell used in the ADC, shown in Fig. 5.7.          | 151                                               |  |  |

| 5.4 | Performance summary of the asynchronous digital delay cell in the ADC.              | 160                                               |  |  |

| 5.5 | Values for width and length parameters for the current DACs shown in Fig. 5.11      | 164                                               |  |  |

| 5.6 | Performance summary of a unit NDAC/PDAC.                                            | 165                                               |  |  |

| 5.7 | Comparison of the PFM CT ADC with prior-published CT ADCs.                          | 175                                               |  |  |

| 5.8 | 3 Comparison of the proposed CT ADC/DSP/DAC system with relevant state-of-the-art   | СТ                                                |  |  |

|     | DSP, DT DSP, and analog processors.                                                 | 178                                               |  |  |

## **Acknowledgements**

I would like to thank my advisor, Prof. Yannis Tsividis, for taking me under his wing and giving me an exciting research topic to work on. He allowed me absolute freedom to pursue and lead my own research ideas, intervening only to steer me in the right direction. His penchant for pursuing bold research ideas and broad interests is inspiring and contagious. It is thus no surprise that working under him has been a truly transformative experience.

Thanks are due to my defense committee members—Prof. Timothy Dickson, Dr. Dominique Morche, Prof. Matthias Preindl, and Prof. Mingoo Seok—for their patience in reading the thesis and providing valuable feedback.

A major part of my thesis was done as part of a collaboration with Dominique Morche and Alin Ratiu at CEA-LETI. I am thankful to Dominique for his unique perspective which helped us evaluate many ideas early on. Alin's passion for research was infectious, and it drove us to achieve something significant together. Colleagues at LETI, including Iulia Tunaru, Robert Polster, and Matthieu Verdy, made my time in Grenoble very memorable. Observing the French way of life first hand in Grenoble was an eye-opening experience, one that I will always cherish.

Working with Pablo Martinez-Nuevo early on in my PhD gave me the confidence to pursue unconventional ideas; I thank him for being a great colleague. I also thank Xiaoyang Zhang and Prof. Yong Lian for their wisdom, guidance, and support during our collaboration. I thank Prof. Thao Nguyen for his enlightening lectures and stimulating discussions, some of which changed the way I think for the better. I also thank Prof. Peter Kinget for providing thoughtful advice over the years. Thanks are also due to Bob Schell for many helpful discussions.

I was lucky to have Suhas, Arun, and Sean to assist me in my projects; I thank them for their diligent help. I am grateful to Anuya Patil, Piyush Patil, Ranjit Desai, Vihang Patil, and Arjun Gupta for their help in editing this thesis. I thank the electrical engineering department administration, especially Elsa Sanchez and Laura Castillo, for their assistance throughout.

I would like to thank all my colleagues at CISL. In particular, I thank Kshitij for teaching me the ways of the PhD early on; Baradwaj, Jayanth, Jianxun, and Karthik for their advice and support on myriad issues; and Tugce, Ning, Sarthak, Shravan, and Vivek for their camaraderie. I found a great colleague, collaborator—and friend—in Yu Chen; my many interactions with him helped me grow as a researcher. I thank Mayank Misra for his camaraderie and friendship during our PhD journey. His many jokes made the tough times seem a lot easier.

I thank Prof. Anurup Mitra at BITS, Pilani for making me fall in love with analog circuits, and Dr. S.C. Bose at CEERI, Pilani for helping me reaffirm and pursue it further. I am also thankful to Mr. Santosh Kumar at CEERI for his mentorship during my time at CEERI. I am indebted to colleagues at STMicroelectronics for expanding my technical knowhow.

I owe a debt of gratitude to my entire family for their unwavering support. I thank my parents, Pradeep and Sanyogita, for teaching me the value of honest hard work. I am also grateful to my brothers, Piyush and Mimoh, for their invaluable friendship.

Finally, the value of being married to a (experimental) psychologist became clear to me during the tumult of grad-school life. I would thus like to thank Anuya for being by my side throughout this incredible journey, sometimes as a colleague (even drawing some of the figures in this thesis) and sometimes as reviewer-number-two. And though I will miss my time at Columbia, I look forward to likewise being by her side as she pursues her own research journey.

## **Chapter 1**

## Introduction

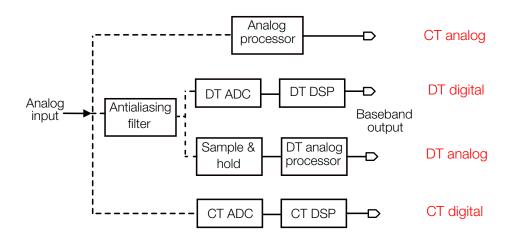

## 1.1 Signal Processors and Processing Domains

Advances in CMOS technology have resulted in a very diverse application space today. Developing a one-size-fits-all signal processor without compromising performance or energy efficiency is thus not practical. The correct approach involves an educated processor choice tailored to a specific application. As regards to processor choice, if we split signal domains along the time and amplitude axes, we end up with four possibilities shown in Table 1.1 [1] with distinct signal processor types. When both time and amplitude axes are continuous, the resulting signal is continuous-time (CT) analog; the processor is a classical analog one. When both axes are discrete, the discrete-time (DT) digital domain results; a classical DT digital signal processor (DSP<sup>1</sup>) processes signals in this domain. Signals in which the time axis is discrete while the amplitude

| Time       | Amplitude  | Signal domain | Processor           |

|------------|------------|---------------|---------------------|

| Continuous | Continuous | CT analog     | Classical analog    |

| Discrete   | Discrete   | DT digital    | Classical DT DSP    |

| Discrete   | Continuous | DT analog     | Analog sampled-data |

| Continuous | Discrete   | CT digital    | CT DSP              |

**Table 1.1**: Signal domains and corresponding processors for continuous/discrete combinations of time and amplitude.

<sup>&</sup>lt;sup>1</sup> In this thesis, DSP will stand as an abbreviation for both "digital signal processing" and "digital signal processor" depending on the context.

axis is continuous are DT analog and can be processed by sampled-data analog processors (e.g. switched-capacitor filters). Finally, by symmetry, the signal domain with a continuous time axis and a discrete amplitude axis is called "CT digital", and the corresponding processor is called "CT DSP" [1].

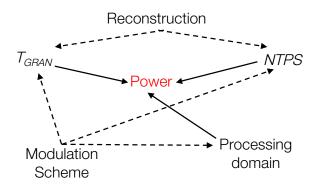

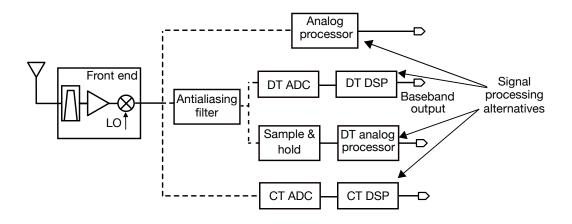

Fig. 1.1 depicts the different signal processing alternatives, drawn based on these signal domains. Each processing category has unique features and limitations; the former can be exploited while the latter will act as hindrances in the context of specific applications. For instance, analog signal processing, while power efficient, does not offer the desired programmability, making it inappropriate for applications that demand a high degree of the latter. DT DSP allows a high degree of programmability. However, it requires a DT analog-to-digital converter (ADC)<sup>2</sup> with sampling at regular clock intervals. Sampling results in aliasing and, in the case of Nyquist-rate sampling, an antialiasing filter with stringent specifications needs to precede the DT ADC so

Fig. 1.1. Signal processing alternatives based on signal domains.

\_

<sup>&</sup>lt;sup>2</sup> In this thesis, an ADC will also be referred to as an "encoder" or, in some cases, a "modulator".

Fig. 1.2. A typical CT DSP signal processing chain.

as to band-limit the input signal. Such an antialiasing filter can be quite power-hungry. Oversampling can simplify the filter specifications, but the high sampling rate results in a major power overhead for the DT ADC and the DT DSP. The DT analog representation, too, suffers from aliasing, and requires an antialiasing filter. Thus, power-efficient handling of DT digital and DT analog signals is a challenge. In contrast, the CT digital domain and CT DSP present an interesting signal processing paradigm that allows A/D conversion with no sampling in time, and thus, with no aliasing. It is discussed in detail next.

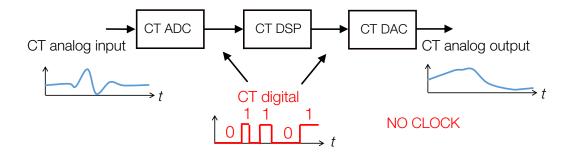

### 1.2 Continuous-Time Data Conversion and DSP

The CT DSP signal processing chain is shown in Fig. 1.2. An input analog signal is converted into CT digital form by a clockless CT ADC (to be described later) [2], [3]; the CT digital output is then processed *directly* by a clockless CT DSP with no sampling in time, producing another (processed) CT digital signal at its output. The DSP output can be converted back to analog form using a CT digital-to-analog converter (DAC). CT DSP presents a principle where digital signals that are binary functions of *continuous* time are processed, while their timing details, as they evolve in continuous time, are preserved in the DSP. Being digital, such a DSP has the amplitude noise immunity and programmability of a conventional DT DSP.

**Fig. 1.3.** Level-crossing sampling: When an input crosses a level, the digital output transitions to a code that corresponds to that level.

Much of the prior work in CT DSP systems is based on CT A/D conversion using level-crossing sampling (LCS) [3]–[13]. Therefore, even though CT DSP is not restricted to LCS, we will use the latter as vehicle to describe the constraints and low-power design considerations of a general CT DSP system. In the process, we will highlight the achievements and limitations of prior work on CT DSP. Once the latter is understood, methods can be developed to further improve these systems.

#### 1.2.1 CT ADC

#### **System description**

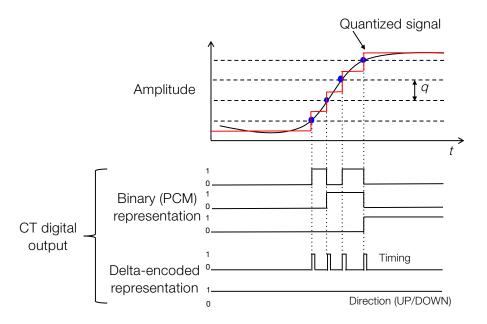

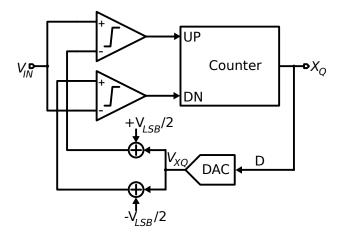

A CT ADC converts an analog input into a CT digital form. LCS is one possible method of encoding analog signals in CT digital form. For an *N*-bit LCS ADC, there are  $2^N$  amplitude levels (Fig. 1.3), separated by  $q = V_{FS}/2^N$  in amplitude, where  $V_{FS}$  is the full-scale amplitude range

of the ADC and q is the amplitude quantization step. Each level has an N-bit binary code associated with it. Every time the input crosses a level, the output of the ADC<sup>3</sup> transitions to a code that corresponds to that particular level. The ADC output "token" or "sample" is thus a bundle of a timing signal—which indicates the instant of crossing—and the N-bit digital code that represents the value of the level, giving its pulse-code-modulated (PCM) representation [14]. This output is CT digital as its transitions are not synchronized to any clock, and can, in principle, occur at any point in time (provided a level is crossed). It is important to note that this output cannot be termed "asynchronous" as, unlike such signals, the timing of the level crossing is an integral part of this CT digital signal encoding and needs to be preserved in any subsequent processing [1].

The PCM code at the CT ADC output can be converted back to the analog amplitude level it represents using a CT DAC. Shown in Fig. 1.3 as the "Quantized signal", this represents the zero-order-hold (ZOH) reconstruction of the original analog input to the  $ADC^4$ . In a uniform-resolution LCS system, any two consecutive crossed levels are always spaced in amplitude by one quantization step, q. The digital code thus always changes by  $\pm$ 1 between any two crossings. Therefore, the N-bit PCM code can be compressed to 2-bit form using delta encoding (Fig. 1.3), with one bit indicating the timing of the crossing and the other one representing the sign of crossing (UP/DOWN).

-

<sup>&</sup>lt;sup>3</sup> The most straightforward LCS encoder is a clockless flash ADC [69]. For an N-bit ADC, there are  $2^N$  clockless comparators that detect level crossings, and their  $2^N$  outputs together give a thermometric-encoded version of the digital output. The latter, when fed into a thermometric decoder, generates the corresponding N-bit PCM code.

<sup>&</sup>lt;sup>4</sup> The reconstructed analog amplitude levels are not exactly equal to the levels used during quantization; they are instead placed at the midpoints between quantization levels. This is done to minimize reconstruction error [3].

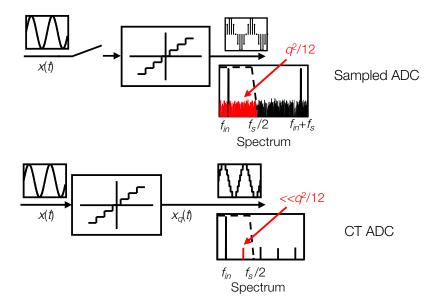

**Fig. 1.4.** Spectral comparison between DT and CT ADCs [1]. For sinusoidal inputs, CT ADCs produce only harmonic distortion in the output spectrum, whereas DT ADCs additionally alias the distortion components, thereby creating "quantization noise floor".

#### **Output spectrum and SER**

The cascade of an LCS CT ADC and a CT DAC represents an amplitude quantizer—an LCS quantizer—without any sampling in time. As there is no sampling in time, no aliasing occurs. No anti-aliasing filter is thus required in an LCS CT ADC/DSP/DAC system [1]. In a Nyquist-rate-clocked DT ADC, the analog input in sampled in time, followed by amplitude quantization of the sampled value. Sampling create aliases of the input in the spectrum, which extend over an infinite bandwidth; the nonlinearity of the amplitude quantizer then creates intermodulation products of these aliases that stretch right into baseband, creating what is often called "quantization noise". Assuming a sufficient numbers of level are crossed (i.e. quantization is not too coarse), the total power of this quantization noise in a bandwidth equal to half the Nyquist sampling rate,  $f_s$ , is  $q^2/12$ , where q is the amplitude quantization step size (see Fig. 1.4). For a full-scale single-tone input, this results in the well-known signal-to-error ratio (SER) of 6*N*+1.76 dB [15], for an *N*-bit

ADC. In contrast, an LCS quantizer only quantizes the analog input, with no sampling in time. The quantizer nonlinearity results in quantization distortion at the output<sup>5</sup>, which, for single-tone inputs, manifests itself as harmonics in the output spectrum<sup>6</sup>. The total integrated power of all these harmonics in an infinite bandwidth is  $q^2/12$ , for an amplitude quantization step size of q. Therefore, the total power of the quantization error harmonics that fall in the signal band can be much lower than  $q^2/12$ , and, consequently, the SER can be higher than 6N+1.76 dB, for an N-bit LCS quantizer. Therefore, for a given quantization step, CT LCS ADC can result in a much higher SER than a Nyquist ADC, provided the power of the noise generated by circuit components is much lower than the quantization error power.

#### **System Parameters**

There are two important parameters of any CT ADC (LCS or otherwise) that have significant implications towards the subsequent CT DSP design and system-level power budget specifications. We will discuss them now.

1. **Granularity** ( $T_{GRAN}$ ): Timing is a crucial aspect of the CT digital signal representation at the CT ADC output, and it has to be preserved precisely along the processing chain. The tightest constraints to achieve this arise when the time between two consecutive CT ADC output tokens is at its minimum. This minimum is termed the granularity,  $T_{GRAN}$ , and, to a significant extent, defines the CT DSP design as we will describe soon.

<sup>5</sup> We thus say that LCS quantization results only in "quantization error" and not "quantization noise" floor.

7

\_

<sup>&</sup>lt;sup>6</sup> A two-tone input will create intermodulation products in the output spectrum.

**Fig. 1.5.** An example plot showing the exponential worsening of NTPS and  $T_{GRAN}$  with LCS quantizer resolution.

2. **Number of tokens per second** (*NTPS*): As we will discuss next, the CT DSP is event-driven with power dissipation that varies with input activity [1]. Therefore, every token produced by the CT ADC has a certain DSP energy cost, and the total DSP power varies directly with the number of tokens produced per second (*NTPS*) by the ADC.

For an *N*-bit LCS ADC handling a full-scale sinusoidal input,  $T_{GRAN} = (2^N \pi f_{in,max})^{-1}$  and  $NTPS = 2^{N+1} f_{in}$  [3], where  $f_{in}$  is the input frequency and  $f_{in,max}$  is the maximum input frequency. As can be seen, NTPS and  $T_{GRAN}$  worsen exponentially as the ADC resolution increases, and respectively worsen linearly and hyperbolically with a rising  $f_{in,max}$  [3]. As an example,  $T_{GRAN}$  and NTPS are plotted against N in Fig. 1.5. The implications of this on the CT DSP will be discussed soon.

#### 1.2.2 CT DSP

The output of the CT ADC is processed by a clockless CT DSP that preserves the timing details of the digital output as it evolves in CT. While a number of CT DSP implementations are possible, we restrict ourselves to linear DSP. CT linear finite-impulse-response (FIR) DSP, implemented using a transversal structure shown in Fig. 1.6, has already been demonstrated for kHz-GHz range applications [3], [10], [16] and has been shown to handle signals in many CT/DT digital formats [16]. So far, only transversal structures have been demonstrated, while recursive ones, used to implement infinite impulse response (IIR) filters, remain a work in progress. This thesis will consider only FIR DSP, and all proposed improvements in the encoders and the processors will be focused towards optimizing a system that contains an FIR DSP.

An FIR (Fig. 1.6) DSP processes an input signal by delaying it along a tapped delay-line, multiplying the tap outputs with appropriate coefficients, and then summing the multiplier outputs to generate a single final output. An  $N^{\text{th}}$ -order FIR filter has N delays, each with value  $T_{TAP}$ , and N+1 taps/coefficients. The frequency response of such a filter repeats every  $f_s = 1/T_{TAP}$ , and its nature can be modified by changing the filter coefficients. This transversal structure can handle

**Fig. 1.6.** The CT DSP that follows the CT ADC uses a transversal structure to implement an FIR filter.

CT/DT analog/digital signals with appropriate modifications. For instance, if the input to the FIR is CT analog, the delays, multipliers and adder are analog circuits; if the input is DT digital, these blocks are clocked digital circuits. In our case, the input to the CT DSP is the output of the CT ADC, which is CT digital in nature. Therefore, the tap delays are implemented using (clockless) asynchronous digital delays, and the multipliers and adder are asynchronous digital circuits [3]. All signals inside the block diagram shown in Fig. 1.6 are binary functions of continuous time. The highly digital nature of the structure allows a good degree of programmability in terms of response type (e.g. lowpass/bandpass), performance (e.g. number of taps), and specifications (e.g. passband width).

As the CT DSP delays the ADC output tokens along its delay-line, it needs to precisely preserve their timing details. The time-spacing between these tokens can be as small as the granularity,  $T_{GRAN}$ . The tap delay in the CT DSP,  $T_{TAP}$ , is usually much larger than  $T_{GRAN}$ .

**Fig. 1.7.** To preserve timing details, each tap delay,  $T_{TAP}$ , is implemented as a cascade of unit delay cells, each with a delay of  $T_{GRAN}$ .

<sup>&</sup>lt;sup>7</sup> In some CT DSPs, the adder is implemented in the analog domain, by converting the multiplier output from digital to analog domain using a CT DAC [10]. We will study the impact of signal domains on efficiency of operations in Sec. 1.2.3.

Therefore, in order to preserve all the tokens and their time-spacing, each tap delay is implemented using a cascade of  $N_D = [T_{TAP}/T_{GRAN}]$  number of clockless digital delay cells, each implementing a delay of  $T_{GRAN}$ , as shown in Fig. 1.7. For example, for an 8-bit LCS case with a full-scale 4 kHz  $f_{in,max}$ ,  $T_{GRAN} = 300$  ns. A tap delay of 25  $\mu$ s will then require each tap delay to be implemented as a cascade of  $25\mu$ s/300 ns  $\approx 83$  cells. Every ADC output token goes through all the 83 delay cells to undergo a delay defined by a single tap.

To connect the CT DSP described thus far with the complete system, we refer to Fig. 1.8, which gives a system-level view of the CT ADC/DSP/DAC system described in Ref. [17]. A CT ADC decomposes the analog input into several binary CT digital signals,  $b_{1-N}(t)$ . Each of the latter is processed in parallel by a slice of a CT digital FIR filter, composed of CT digital delays and digital multipliers as described above. The outputs of all slices are weighted and summed in a CT digital adder, whose output is converted to analog form using a CT DAC. Note, however, that this

Fig. 1.8. System-level view of the CT ADC/DSP/DAC system from Ref. [17].

system shows only the principle. There are now more efficient implementations, some of which are described in this thesis.

Let us now consider the power dissipation and chip area of the CT DSP. The digital blocks that implement each of the three operations in the FIR filter—delay, multiplication, and addition—are event-driven. There cannot be a delay/multiply/add operation unless there is an input token; if there is no input token, no operation takes place, and no energy is spent (besides that due to leakage in circuits, which we assume negligible for now). Every operation takes a certain amount of energy per token. Therefore, as the number of tokens per second, *NTPS*, increases, the FIR filter power dissipation, which is the product of energy per token and the *NTPS*, increases. This is why a CT FIR DSP is said to be event-driven with activity-dependent power dissipation [1], [3], [10]. The power dissipation of the DSP (ignoring leakage) is given by [3]:

$$P_{DSP} = P_{Delay-Line} + P_{Arithmetic}$$

$$= \left[ \left| \frac{T_{TAP}}{T_{GPAN}} \right| \times (N_{taps} - 1) \times E_{Del} + E_{Arithmetic} \right] \times NTPS$$

(1.1)

where  $E_{Del}$  and  $E_{Arithmetic}$  are respectively the energy taken by a single delay cell to delay a token and the energy dissipated by the arithmetic blocks—the mutiplier-adder combination—per token;  $N_{taps}$  is the number of filter taps (equal to number of tap delays plus 1). The chip area of the CT DSP is dominated by that of the delay line (as compared to the arithmetic blocks in it, especially when dealing with low-frequency signals) [3] and is given by:

$$A_{Delay-line} = \left| \frac{T_{TAP}}{T_{GRAN}} \right| \times (N_{taps} - 1) \times A_{Del}$$

(1.2)

where  $A_{Del}$  is the chip area occupied by a single delay cell unit.

From (1.1) and (1.2), it is clear that, in order to keep the DSP power dissipation and chip area low for a given set of specifications ( $T_{TAP}$ ,  $N_{taps}$ ), the NTPS needs to be low and  $T_{GRAN}$  needs to be high. Interestingly, both of these parameters are set by the CT ADC alone, as was discussed in Sec. 1.2.1. For the case of LCS, an exponential worsening of  $T_{GRAN}$  and NTPS with ADC resolution results in an exponential rise in the DSP power dissipation and chip area. Using typical values of  $E_{Del}$  and  $E_{Arithmetic}$ , obtained from the integrated implementation in Ref. [16],  $P_{DSP}$  and  $A_{Delay-line}$  were calculated using (1.1) and (1.2) for an 8-tap CT FIR filter, and plotted against ADC resolution, N, in Fig. 1.9. The exponential rise in  $P_{DSP}$  and  $A_{Delay-line}$  is clear.

We end this section by noting that the existence of the CT digital signal domain predates its categorization in Ref. [1]. For instance, signals that are asynchronous pulse-width modulated [18], pulse-frequency modulated [19], asynchronous delta [20] or sigma-delta modulated [21] are all CT digital. Most, if not all, of these benefit from alias-free generation and have unique spectral properties. However, the CT digital domain is not fully exploited to enable greater programmability and scalability in systems that involve such signals. Considering this, the

**Fig. 1.9.** Dynamic power dissipation and delay line chip area of an 8-tap FIR CT DSP with  $T_{TAP} = 25 \, \mu s$  and for  $f_{in} = 2 \, kHz$ , estimated using (1.1) and (1.2), using typical numbers obtained from Ref. [16]:  $E_{Del} = 50 \, \text{fJ}$ ,  $E_{Arithmetic} = 150 \, \text{pJ}$ ,  $A_{Del} = 20 \, \mu \text{m}^2$ .

fundamental contribution of Ref. [2] was the demonstration that such CT digital signals can be processed directly by a DSP in continuous time using digital blocks like clockless delays, multipliers and adders, allowing flexible filtering capabilities with good programmability. This thesis attempts to take the state of research in this field one step closer to what it promises to be.

### 1.2.3 Considerations for Low Power and Area in a CT ADC/DSP System

Implementing a CT ADC/DSP system with low power dissipation and chip area requires optimization of both the ADC and DSP for it. The design considerations to achieve low power are summarized in the diagram shown in Fig. 1.10. The techniques presented in this thesis exploit one or more of these considerations to achieve improved energy efficiency in a complete CT ADC/DSP system. We will discuss each of them in detail now.

1. *NTPS and T\_{GRAN}*: The total power dissipation (ignoring leakage) and chip area of a CT ADC/DSP system are given by:

$$P_{SYS} = P_{ADC} + P_{DSP} = P_{ADC} + \left[ \left| \frac{T_{TAP}}{T_{GRAN}} \right| \times (N_{taps} - 1) \times E_{Del} + E_{Arithmetic} \right] \times NTPS$$

(1.3)

$A_{SYS} = A_{ADC} + A_{Delay-line} + A_{Arithmetic}$

$$= A_{ADC} + \left| \frac{T_{TAP}}{T_{GRAN}} \right| \times (N_{taps} - 1) \times A_{Del} + A_{Arithmetic}$$

(1.4)

Where  $P_{ADC}$  and  $A_{ADC}$  are respectively the power dissipation and chip area of the ADC,  $A_{Arithmetic}$  is the area occupied by the arithmetic blocks (multipliers and adder), and the expressions for  $P_{DSP}$  and  $A_{Delay-line}$  are obtained from (1.1) and (1.2).

Clearly, the NTPS and  $T_{GRAN}$  directly impact the system power and area. Both the NTPS and  $T_{GRAN}$  are defined based on the encoding scheme in the CT ADC. As was discussed in the

Fig. 1.10. Diagram depicting design considerations for achieving low power in a CT DSP system.

previous section and clearly seen in Fig. 1.9, in the case of LCS, they worsen exponentially with resolution and impose a severe penalty on the CT DSP power dissipation and area. This has so far limited the integrated CT DSP implementations to low orders [3], [10], [16]. It is thus clear that any CT DSP system that wishes to achieve high energy efficiency needs to adopt an encoder that can significantly relax the tight exponential trade-off between the *NTPS*,  $T_{GRAN}$ , and the ADC resolution. In this thesis, we consider a number of approaches to achieve this.

2. *Modulation scheme*: A CT ADC encodes analog information by modulating one or more aspects of a CT digital signal at its output. For instance, LCS modulates the binary code of the CT digital output in proportion to the analog input, resulting in the classical pulse-code modulation [14], but in continuous time. On the other hand, delta modulation encodes the analog input by modulating the pulse density of the CT digital output in proportion to the input slope [20].

The choice of modulation scheme influences the CT ADC/DSP system in many important ways. First, the modulation scheme defines the power dissipation of the CT ADC—the modulator/encoder. Next, it directly affects the NTPS and  $T_{GRAN}$ , and, as discussed above, the system power dissipation. Finally, the nature of the encoded output—single/multi-bit—influences

the power dissipation of the CT FIR filter. The latter involves delay, multiply, and add operations. Delaying a 1-bit digital signal in continuous time is more energy efficient [3] than delaying a multibit one, as the latter requires memory to store and access digital information [16]; this is in addition to needing asynchronous delay units to delay the timing information. Furthermore, CT/DT digital multiplication becomes extremely simple and energy-efficient when one of the operands (say, the A/D encoder output) is 1-bit, as the multiplier can be implemented using pass-gates [10]. In contrast, multiplying two multi-bit digital operands—CT or DT—is significantly more power hungry [16].

The choice of modulation scheme can thus significantly affect the energy efficiency of the CT ADC/DSP system. In this thesis, modulation schemes other than the hitherto-common LCS are considered and shown to give drastic improvements over existing CT DSP systems in terms of energy efficiency.

3. *Reconstruction*: The output of the CT ADC (or CT DSP) can be converted back to analog form using a CT DAC. In Sec. 1.2.1, ZOH—or piecewise constant—reconstruction was discussed. Using higher-order reconstruction, the quantization error can be significantly reduced. Conversely, for a given accuracy requirement, a CT system with higher-order reconstruction can use a CT ADC with a lower resolution than that in one that uses ZOH reconstruction. For example, it was shown in Ref. [22] that an LCS ADC with only 4-bit resolution can achieve single-tone SER of above 100 dB using higher-order reconstruction schemes. Given the exponential dependence of *NTPS* and  $T_{GRAN}$  on resolution and their implications on system power, the gains obtained from going for higher-order over ZOH reconstruction can be significant. The catch in this, however, is that higher-order reconstruction schemes transfer the onus from the ADC to the DAC. Unless the power dissipation constraints on the DAC side are significantly relaxed, higher-order reconstruction may

not be feasible. Besides, higher-order reconstruction schemes are generally slow and non-real-time in nature [22].

In this thesis, we assume that the application context forces a tight power budget on every block—the ADC, DSP, and the DAC. This is true in case of applications like wireless sensor nodes, where every node is power constrained, thereby not allowing the DAC, which is expected to be at the receiver sensor node, a very high power budget. In any such application, any encoder that allows a higher-order reconstruction scheme needs to be fast, able to operate in real time, and such that it will not overwhelm the power budget at the DAC end of the chain. This thesis proposes such a scheme.

4. Adaptive-resolution quantization: The NTPS- $T_{GRAN}$ -resolution trade-off is valid in the case of uniform-resolution LCS quantization, in which the encoder uses a fixed quantization resolution independent of the input. Adaptive-resolution quantization attempts to exploit certain signal characteristics and accordingly intervene in the quantization process with an adaptive quantization step, with the aim to relax the NTPS- $T_{GRAN}$ -resolution trade-off while not compromising accuracy. For instance, Ref. [23] proposed an adaptive-resolution (AR) LCS quantization scheme that varies the quantization step in proportion to the input slope—the higher the slope, the higher the quantization step and vice versa. It was shown that the resulting degradation in in-band accuracy is negligible; an order of magnitude relaxation in  $T_{GRAN}$  and drastic reduction in  $NTPS^8$  was demonstrated [9] for a given quantization accuracy requirement. As this example shows, AR

\_

<sup>&</sup>lt;sup>8</sup> The exact amount of reduction is input signal dependent.

quantization schemes can be used to improve a given modulation scheme. This aspect is explored in this thesis to improve an existing modulation scheme that also achieves superior reconstruction. 5. Hybrid processing domains: To lower the system power dissipation, one needs to optimize the FIR filter to lower its power dissipation while retaining flexibility for given specifications. This can be achieved by choosing an encoding format and signal domain tailored to lower the energy required for a particular operation—delay, multiply, or add—in the FIR filter. Delay operation can be conducted with high energy efficiency in the CT/DT digital or DT analog domain, unlike the case with the CT analog domain [10]. Multiplication in the CT/DT digital/analog domain can be quite power hungry. However, as discussed above, if the ADC encodes the analog input in a digital signal with few bits (e.g. 2), multiplication becomes extremely simple and energy-efficient, as it can be achieved with pass gates. Finally, addition is far more energy efficient when done in the CT/DT analog domain as compared to the CT/DT digital domain. For instance, the multi-bit CT digital multiply-add operations in the FIR filter in Ref. [16] consume 150 pJ/token, whereas the single-bit CT digital multiplication followed by analog addition in the FIR filter in Ref. [10] dissipates 30 fJ/token/tap or 180 fJ/token. While it is not entirely fair to compare the two due to their different resolutions (8-bit in Ref. [16] versus 3-bit in Ref. [10]), a four-orders-of-magnitude improvement based on appropriate choice of processing domains is significant and noteworthy.

We thus conclude that the energy efficiency of an operation depends on the signal domain and the encoding format (few bits versus too many bits) involved, and so does the energy efficiency of the resulting FIR filter. It is clear that an energy-efficient FIR filter would be one that has a preceding CT/DT ADC that encodes the analog input in a CT/DT digital form with few bits; asynchronous/DT digital delays in the delay-line; simple pass-gates as multipliers; and addition of the digital outputs of the multiplier performed in the analog domain by first converting them using

DACs. This approach of choosing hybrid processing domains was adopted in the CT DSP system in Ref. [10] and demonstrated to process GHz-range signals with an energy efficiency that was almost two order of magnitude better than previous CT DSPs and within a factor of 2 of state-of-the-art DT DSPs. The system, however, had a limited resolution of 3 bits in the flash LCS encoder, and a flash architecture would cause an exponential power and area penalty with any increase of resolution. In this thesis, we propose modulation/encoding schemes that can exploit this concept of hybrid processing domains in the FIR to achieve good energy efficiency, while extending resolution beyond 3 bits.

We conclude this section by noting one topic that we have not considered so far: that of circuit-level improvements in the CT ADC, asynchronous digital delay and the multiplier-adder circuits. These can respectively help keep parameters  $P_{ADC}$ ,  $E_{Del}$ , and  $E_{Arithmetic}$  in (1.3)-(1.4) low, thereby lowering power dissipation at the system level. For instance, adaptive biasing of zero-crossing detectors in the CT ADC in Ref. [9] along with adaptive-resolution quantization brought about an order of magnitude improvement in the energy efficiency over prior CT ADC work. The asynchronous delay architecture proposed in Ref. [24] brought about a 2× improvement in the energy efficiency over that in Ref. [25]. Parallelization in the CT DSP can also help relax the granularity constraint, at the expense of area and a higher sensitivity to mismatch [10]. These techniques are universal and can be applied to any of the schemes proposed in this thesis; in fact, in some cases, they have been. However, they cannot be considered to be the central contributions of this thesis. The latter, instead, would be the underlying principles—including the modulation/reconstruction scheme—that allow a drastic system-level relaxation of constraints, thereby facilitating a low-power and low-area implementation.

|                                                    | Schell,<br>JSSC'08 [3] | Kurchuk,<br>JSSC'12 [10]     | Weltin-Wu,<br>JSSC'13 [9] |

|----------------------------------------------------|------------------------|------------------------------|---------------------------|

| Technology                                         | 90 nm CMOS             | 65 nm CMOS                   | 130 nm CMOS               |

| Supply (V)                                         | 1                      | 1.2                          | 1                         |

| Input bandwidth $(f_{BW})$                         | 10 kHz                 | 2.4 GHz<br>(0.8 GHz-3.2 GHz) | 20 kHz                    |

| Core area (mm <sup>2</sup> )                       | 0.06                   | 0.0036                       | 0.36                      |

| SNDR (dB)                                          | 58                     | 20.3                         | 47-54                     |

| Total power, P (μW)                                | 50                     | 2700                         | 2-8                       |

| Walden figure of merit <sup>a</sup> (fJ/conv-step) | 3769                   | 66                           | 200-850                   |

| $P/(2f_{BW})$ (pJ)                                 | 2500                   | 0.56                         | 200                       |

| Antialiasing filter required?                      | No                     | No                           | No                        |

<sup>&</sup>lt;sup>a</sup>Walden figure of merit is defined as:  $FOM = \frac{P}{2f_{BW}2^{ENOB}}$ ; ENOB = (SNDR-1.76)/6.

**Table 1.2.** Performance summary of prior CT ADC work.

## 1.3 Thesis Goals and Organization

Tables 1.2 and 1.3 respectively summarize the prior CT ADC and CT DSP work, all of which is based on LCS encoding. Table 1.3 also includes relevant DT DSP and analog processors for comparison. Prior CT ADC/DSP systems achieve a degree of programmability that is comparable to DT DSPs. However, despite significant improvements over time, either their energy efficiency [3] or resolution [10] remains relatively poor.

The CT ADC, particularly, is worse by over an order of magnitude compared to state-of-the-art DT ADCs. The CT ADC is crucial towards achieving high system-level energy efficiency as its contribution to the system power dissipation is two-fold. First, it adds to the total system power consumption. Further, it also defines the power dissipation of the CT DSP by setting the NTPS and  $T_{GRAN}$ . Once the encoder is fixed, there are very few techniques other than brute-force

|                                              | Schell,<br>JSSC'08 [3] | Kurchuk,<br>JSSC'12 [10]     | Agrawal,<br>ISSCC'10 [67] | Toifl,<br>ESSCIRC'14<br>[68] |

|----------------------------------------------|------------------------|------------------------------|---------------------------|------------------------------|

| Technology                                   | 90 nm CMOS             | 65 nm CMOS                   | 32 nm CMOS                | 32 nm CMOS                   |

| Supply (V)                                   | 1                      | 1.2                          | 1                         | 0.6                          |

| Туре                                         | CT DSP                 | CT mixed-signal DSP          | DT DSP                    | DT DSP                       |

| Input bandwidth, $f_{BW}$                    | 10 kHz                 | 2.4 GHz<br>(0.8 GHz-3.2 GHz) | 1.05 GHz                  | 8 GHz                        |

| Average sample rate                          | 0-8 MS/s               | 0-45 GS/s                    | 2.1 GS/s                  | 16 GS/s                      |

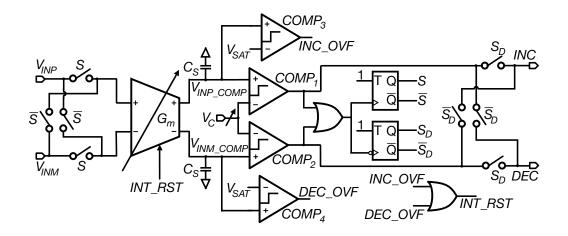

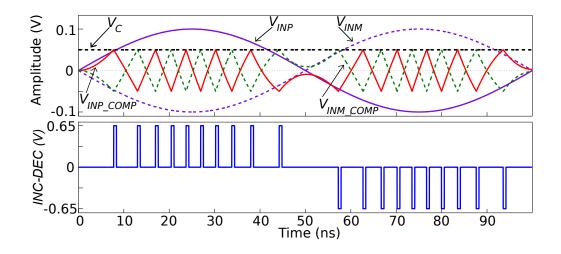

| Core area (mm <sup>2</sup> )                 | 0.55                   | 0.073                        | 0.004                     | 0.033                        |