### Photonic Interconnects Beyond High Bandwidth

Ke Wen

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

#### COLUMBIA UNIVERSITY

2017

© 2017 Ke Wen All Rights Reserved

#### ABSTRACT

#### Photonic Interconnects Beyond High Bandwidth

#### Ke Wen

The extraordinary growth of parallelism in high-performance computing requires efficient data communication for scaling compute performance. High-performance computing systems have been using photonic links for communication of large bandwidth-distance product during the last decade. Photonic interconnection networks, however, should not be a wire-for-wire replacement based on conventional electrical counterparts. Features of photonics beyond high bandwidth, such as transparent bandwidth steering, can implement important functionalities needed by applications. In another aspect, application characteristics can be exploited to design better photonic interconnects. Therefore, this thesis explores codesign opportunities at the intersection between photonic interconnect architectures and high-performance computing applications. The key accomplishments of this thesis, ranging from system level to node level, are as follows.

Chapter 2 presents a system-level architecture that leverages photonic switching to enable a reconfigurable interconnect. The architecture, called Flexfly, reconfigures the inter-group level of the widely-used Dragonfly topology using information about the application's communication pattern. It can steal additional direct bandwidth for communication-intensive group pairs. Simulations with applications such as GTC, Nekbone and LULESH show up to 1.8x speedup over Dragonfly paired with UGAL routing, along with halved hop count and latency for cross-group messages. To demonstrate the effectiveness of our approach, we built a 32-node Flexfly prototype using a silicon photonic switch connecting four groups and demonstrated 820 ns interconnect reconfiguration time. This is the first demonstration of silicon photonic switching and bandwidth steering in a high-performance computing cluster.

Chapter 3 extends photonic switching to the node level and presents a recon-

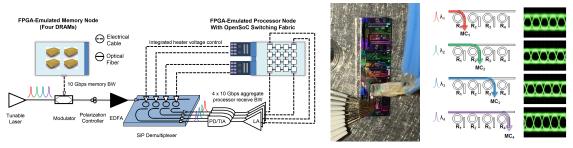

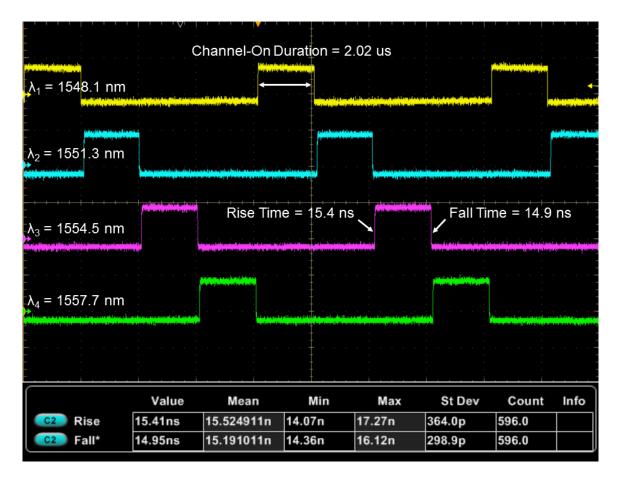

figurable silicon photonic memory interconnect for many-core architectures. The interconnect targets at important memory access issues, such as network-on-chip hot-spots and non-uniform memory access. Integrated with the processor through 2.5D/3D stacking, a fast-tunable silicon photonic memory tunnel can transparently direct traffic from any off-chip memory to any on-chip interface – thus alleviating the hot-spot and non-uniform access effects. We demonstrated the operation of our proposed architecture using a tunable laser, a 4-port silicon photonic switch (four wavelength-routed memory channels) and a 4x4 mesh network-on-chip synthesized by FPGA. The emulated system achieves a 15-ns channel switching time. Simulations based on a 12-core 4-memory model show that for such switching speeds the interconnect system can realize a 2x speedup for the STREAM benchmark in the hot-spot scenario and a reduction of execution time for data-intensive applications such as 3D stencil and K-means clustering by 23% and 17%, respectively.

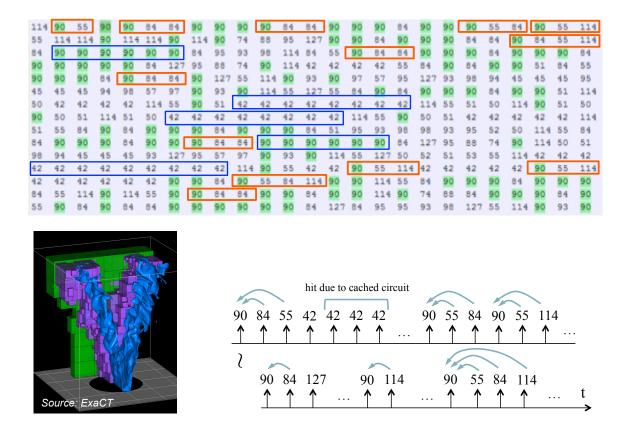

Chapters 4 explores application-level characteristics that can be exploited to hide photonic path setup delays. In view of the frequent reuse of optical circuits by many applications, we proposed a circuit-cached scheme that amortizes the setup overhead by maximizing circuit reuses. In order to improve circuit "hit" rates, we developed a reuse-distance based replacement policy called "Farthest Next Use". We further investigated the tradeoffs between the realized hit rate and energy consumption. Finally, we experimentally demonstrated the feasibility of the proposed concept using silicon photonic devices in an FPGA-controlled network testbed.

Chapter 5 proceeds to develop an application-guided circuit-prefetch scheme. By learning temporal locality and communication patterns from upper-layer applications, the scheme not only caches a set of circuits for reuses, but also proactively prefetches circuits based on predictions. We applied this technique to communication patterns from a spectrum of science and engineering applications. The results show that setup delays via circuit misses are significantly reduced, showing how the proposed technique can improve circuit switching in photonic interconnects.

# Contents

| Li      | List of Figures                                                             |                                                                                                                                                                                                     |                                                                        |  |

|---------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|

| Li      | st of                                                                       | Tables                                                                                                                                                                                              | x                                                                      |  |

| A       | ckno                                                                        | wledgements                                                                                                                                                                                         | xi                                                                     |  |

| 1       | Intr                                                                        | oduction                                                                                                                                                                                            | 1                                                                      |  |

|         | 1.1                                                                         | Communication Requirement within HPC                                                                                                                                                                | 1                                                                      |  |

|         | 1.2                                                                         | The Memory Wall in Post Moore's Law and Many-core Era                                                                                                                                               | 3                                                                      |  |

|         | 1.3                                                                         | Photonic Interconnects                                                                                                                                                                              | 5                                                                      |  |

|         | 1.4                                                                         | Beyond Just High Bandwidth                                                                                                                                                                          | 6                                                                      |  |

|         |                                                                             |                                                                                                                                                                                                     |                                                                        |  |

| Pa      | art I:                                                                      | Leveraging Photonic Switching                                                                                                                                                                       | 9                                                                      |  |

| Ра<br>2 |                                                                             | Leveraging Photonic Switching<br>otonics Enabled Flexible Topology – A Dragonfly Example                                                                                                            | 9<br>10                                                                |  |

|         |                                                                             |                                                                                                                                                                                                     | _                                                                      |  |

|         | Pho                                                                         | otonics Enabled Flexible Topology – A Dragonfly Example                                                                                                                                             | 10                                                                     |  |

|         | <b>Pho</b><br>2.1                                                           | otonics Enabled Flexible Topology – A Dragonfly Example<br>Motivation                                                                                                                               | <b>10</b><br>10                                                        |  |

|         | Pho<br>2.1<br>2.2                                                           | otonics Enabled Flexible Topology – A Dragonfly Example         Motivation                                                                                                                          | <b>10</b><br>10<br>11                                                  |  |

|         | <ul><li>Pho</li><li>2.1</li><li>2.2</li><li>2.3</li></ul>                   | <b>Detonics Enabled Flexible Topology</b> – A Dragonfly Example         Motivation         Motivation         The Dragonfly Topology         Traffic Characterization on Dragonfly                  | <ul> <li>10</li> <li>10</li> <li>11</li> <li>12</li> </ul>             |  |

|         | <ul> <li>Pho</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ul> | otonics Enabled Flexible Topology – A Dragonfly Example         Motivation         The Dragonfly Topology         Traffic Characterization on Dragonfly         Flexfly: A Reconfigurable Dragonfly | <ul> <li>10</li> <li>10</li> <li>11</li> <li>12</li> <li>14</li> </ul> |  |

|    | <ol> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ol> | Profiling Circuit Reuse Distance                              | 64<br>66<br>68<br>70<br>73<br>77 |

|----|------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|

|    | <ul><li>4.5</li><li>4.6</li><li>4.7</li></ul>                                            | Predicting Circuit Reuse Distance                             | 64<br>66<br>68<br>70             |

|    | 4.5<br>4.6                                                                               | Predicting Circuit Reuse Distance                             | 64<br>66<br>68                   |

|    | 4.5                                                                                      | Predicting Circuit Reuse Distance                             | 64<br>66<br>68                   |

|    |                                                                                          | Predicting Circuit Reuse Distance                             | 64<br>66                         |

|    | 4.4                                                                                      | Profiling Circuit Reuse Distance                              |                                  |

|    |                                                                                          |                                                               |                                  |

|    | 4.3                                                                                      | A Reuse Distance Based Approach                               | 63                               |

|    | 4.2                                                                                      | Source of Delays in Silicon Photonic Links                    | 62                               |

|    | 4.1                                                                                      | Motivation                                                    | 60                               |

| 4  | Reu                                                                                      | sing Optical Circuits in HPC Applications                     | 59                               |

| Pε | art II                                                                                   | : Avoiding Path Setup Overhead                                | 58                               |

|    | 3.7                                                                                      | Summary                                                       | 57                               |

|    | 3.6                                                                                      | Hardware Demonstration                                        | 52                               |

|    | 3.5                                                                                      | Performance Evaluation                                        | 45                               |

|    | 3.4                                                                                      | Alleviating Hotspots                                          | 44                               |

|    | 3.3                                                                                      | Optimizing Core-Memory Affinity                               | 42                               |

|    | 3.2                                                                                      | Integrated Photonic Memory Interconnect for Reconfigurability | 41                               |

|    | 3.1                                                                                      | Motivation                                                    | 38                               |

| 3  | Rec                                                                                      | onfigurable Memory Interconnect for Many-core Processors      | 37                               |

|    | 2.12                                                                                     |                                                               | 50                               |

|    |                                                                                          | Summary                                                       | 36                               |

|    |                                                                                          | Related Work                                                  | 34                               |

|    |                                                                                          | Power Penalty Analysis                                        | 32                               |

|    | 2.9                                                                                      | Large-Scale Implementation and Cost                           | 30                               |

|    |                                                                                          | Experimental Demonstration                                    | 25                               |

|    | 5.1 Motivation $\ldots$ |                                                        |    |  |

|----|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----|--|

|    | 5.2                                                                                                      | Circuit Prefetch Using Application-specific Predictors | 80 |  |

|    | 5.3                                                                                                      | Performance Evaluation                                 | 83 |  |

|    | 5.4                                                                                                      | Summary and Discussion                                 | 89 |  |

| 6  | Con                                                                                                      | clusion and Remarks                                    | 91 |  |

| 7  | Fut                                                                                                      | ure Work Recommendations                               | 93 |  |

|    | 7.1                                                                                                      | On Reconfigurable Networks                             | 93 |  |

|    | 7.2                                                                                                      | On Setup Delay Avoidance                               | 94 |  |

| Bi | bliog                                                                                                    | graphy                                                 | 96 |  |

| A  | Appendix: Relevant Author Publications 11                                                                |                                                        |    |  |

# List of Figures

| 1.1 | Diverse communication patterns of the "Seven Dwarf" applications identi-          |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | fied by Phillip Colella [8] and a group of experts from Berkeley [9]. Figure      |    |

|     | compiled from $[9], [10], \ldots, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots$ | 2  |

| 1.2 | (left) Cache size normalized by GFLOPS. (right) Normalized cache area.            | 4  |

| 1.3 | (left) Absolute off-chip memory bandwidth. (right) off-chip byte per              |    |

|     | FLOP ratio.                                                                       | 4  |

| 1.4 | Microring-based silicon photonic link                                             | 5  |

| 1.5 | (a) Rewiring links or steering bandwidth using a circuit switch. (b) Pho-         |    |

|     | tonics enabled flexible topologies                                                | 7  |

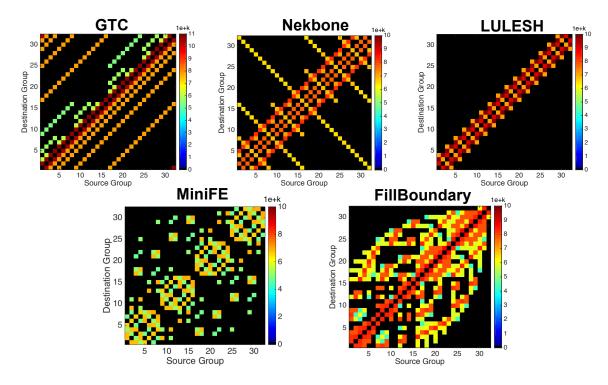

| 2.1 | (a) A six-group Dragonfly, all-to-all both inter- and intra- group. (b)           |    |

|     | Connectivity matrix.                                                              | 11 |

| 2.2 | Group-to-group traffic matrices of applications run on a 32-group Drag-           |    |

|     | onfly                                                                             | 13 |

| 2.3 | Construction flow of the Flexfly architecture                                     | 15 |

| 2.4 | Representative ETM's from applications using the three association strate-        |    |

|     | gies; here switch radix $r = 8$ , hence ETM size is $8 \times 8$                  | 18 |

| 2.5 | Decomposition of an example ETM into three switching modes $(r=8). \ .$           | 20 |

| 2.6 | Global link allocation with switch radix $r = 8$ (upper) and $r = 32$ (lower).    |    |

|     | Note that the color scales are different across sub-figures                       | 22 |

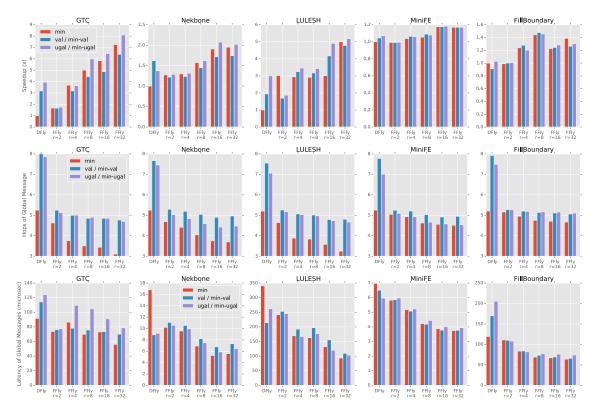

| 2.7  | (Top) Speedup of Flexfly $(r = 2, 4, 8, 16, 32)$ with various routing mecha-                                                                                                                          |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | nisms over Dragonfly with minimal routing (normalized to 1.0x). (Middle                                                                                                                               |          |

|      | and bottom) Hops and latencies of cross-group messages. Val and UGAL                                                                                                                                  |          |

|      | are used on Dragonfly. Min-Val and Min-UGAL are used on Flexfly                                                                                                                                       | 25       |

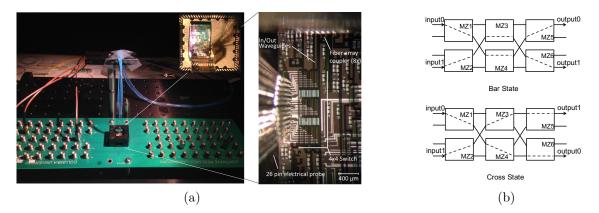

| 2.8  | (a) Socketed switch chip mounted on a PCB; (b) Bar and cross configu-                                                                                                                                 |          |

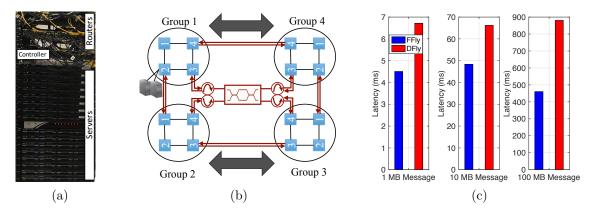

|      | rations for ports 1 and 4 in the six-MZI Benes switch                                                                                                                                                 | 26       |

| 2.9  | (a) 32-node Flexfly prototype and (b) corresponding topology diagram                                                                                                                                  |          |

|      | $(2 \times 2 \times 4)$ ; (c) Comparing round trip time over 8 pairs of servers (each pair                                                                                                            |          |

|      | in different groups), in Dragonfly or Flexfly configurations                                                                                                                                          | 27       |

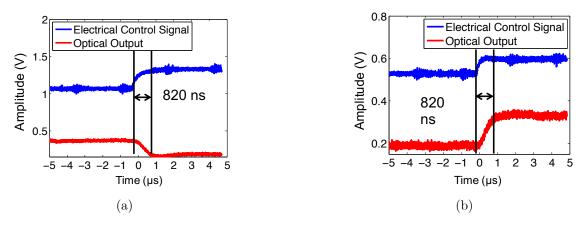

| 2.10 | Silicon photonic switch setup time for (a) $bar$ and (b) $cross$ states                                                                                                                               | 28       |

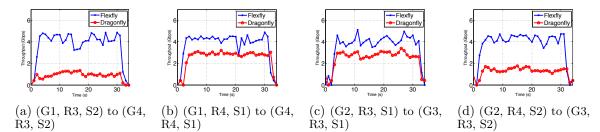

| 2.11 | (a-d) Measured throughput of servers in a data transfer between G1 to G4 $$                                                                                                                           |          |

|      | and G2 to G3. G: group, R: router, S: server. Throughput is higher in the                                                                                                                             |          |

|      | Flexfly-adapted configuration $(bar \text{ state})$ as two global links are awarded                                                                                                                   |          |

|      |                                                                                                                                                                                                       |          |

|      | to each of the above group pairs                                                                                                                                                                      | 29       |

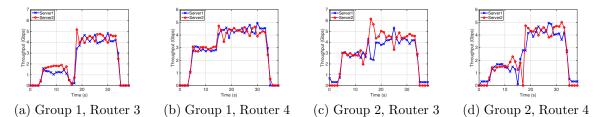

| 2.12 | to each of the above group pairs                                                                                                                                                                      | 29       |

| 2.12 |                                                                                                                                                                                                       | 29       |

| 2.12 | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.                                                                                                                             | 29<br>29 |

|      | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra                                                    |          |

|      | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra<br>global link is provided between the two groups. |          |

|      | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra<br>global link is provided between the two groups  |          |

|      | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra<br>global link is provided between the two groups  |          |

|      | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra<br>global link is provided between the two groups  |          |

|      | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra<br>global link is provided between the two groups  |          |

| 2.13 | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra<br>global link is provided between the two groups  | 29       |

| 2.13 | Demonstration of on-the-fly reconfiguration across the Flexfly prototype.<br>Reconfiguration is performed at second 15 approximately and one extra<br>global link is provided between the two groups  | 29       |

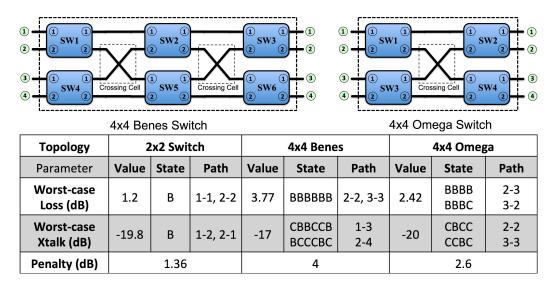

| 2.15 | (top) 4×4 Beneš and Omega topologies based on optimized 2×2 switches.      |    |

|------|----------------------------------------------------------------------------|----|

|      | (bottom) Worst-case of insertion loss and crosstalk for all possible map-  |    |

|      | pings from the input ports to the output ports.                            | 33 |

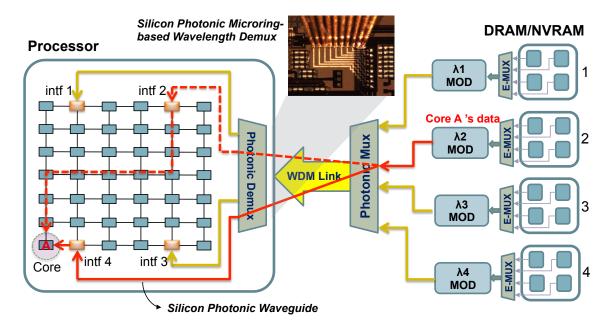

| 3.1  | A many-core multi-memory architecture using a SiP demux as reconfig-       |    |

|      | urable memory fabric. Dashed red path: 10 hops on NoC; solid red path:     |    |

|      | 1 hop only                                                                 | 39 |

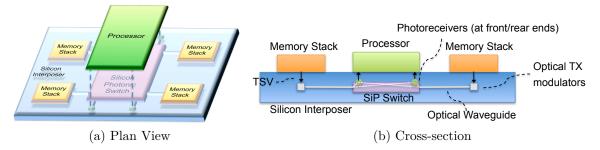

| 3.2  | A 2.5D stacking solution using a Silicon interposer with an embedded       |    |

|      | active Silicon photonic interconnect.                                      | 41 |

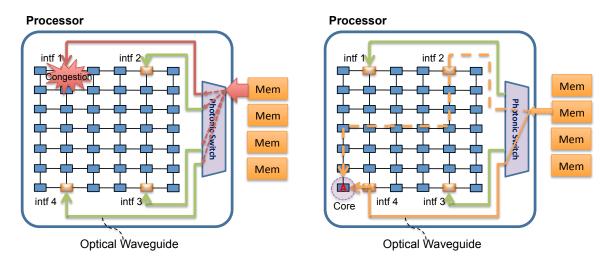

| 3.3  | Architectural benefit of SiP switch: alleviating hotspots (left) and opti- |    |

|      | mizing core-memory affinity (right)                                        | 43 |

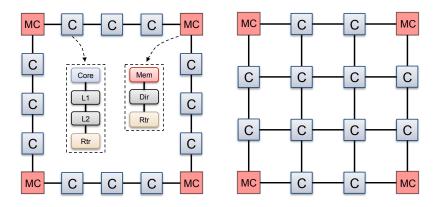

| 3.4  | Simulated 12-core 4-MC architecture in ring and mesh configuration         | 45 |

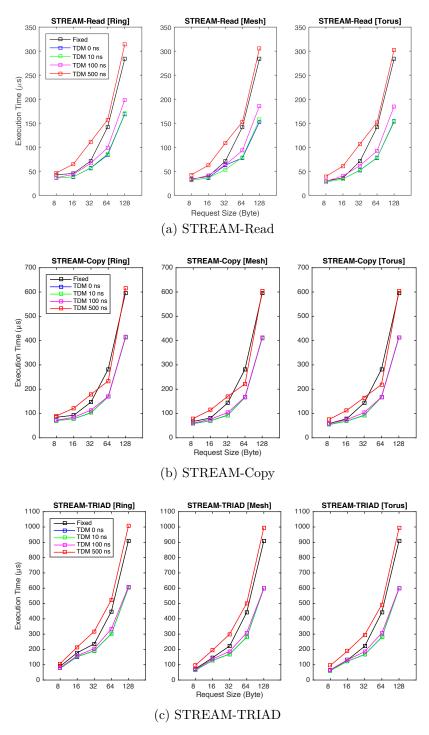

| 3.5  | Execution time of STREAM with different kernels (read, copy and            |    |

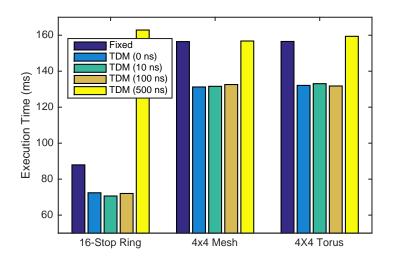

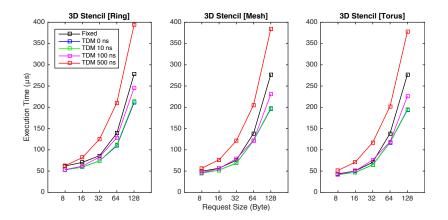

|      | TRIAD), under fixed or TDM-switched memory connection modes                | 46 |

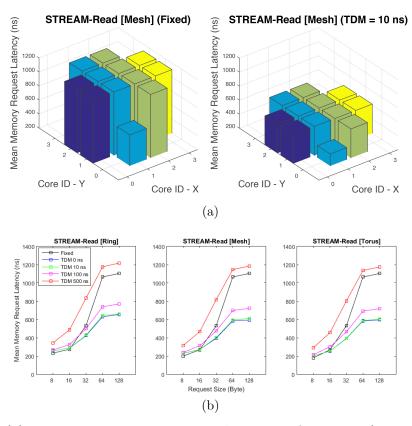

| 3.6  | (a) Respective memory request latencies of 12 cores (in mesh topology)     |    |

|      | under fixed vs. TDM modes, request size $= 64B$ ; (b) Mean memory          |    |

|      | request latency across all 12 cores                                        | 48 |

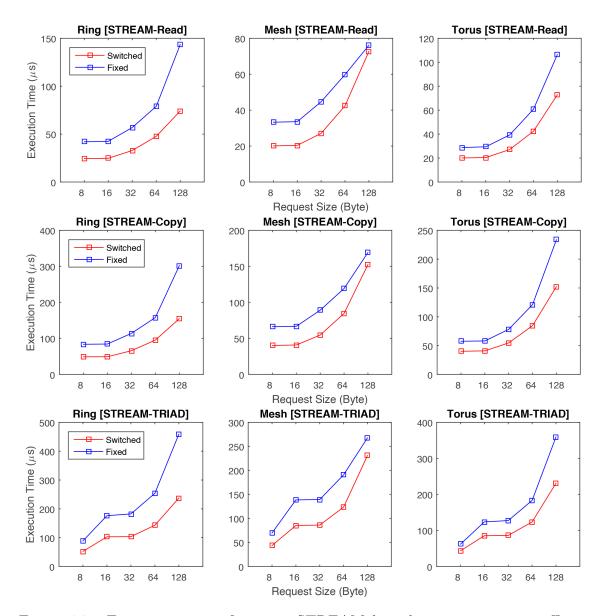

| 3.7  | Execution time of various STREAM kernels using native or affinity-         |    |

|      | optimized memory interfaces.                                               | 49 |

| 3.8  | Run time of streamcluster with fixed and reconfigurable (TDM) mem-         |    |

|      | ory connections                                                            | 51 |

| 3.9  | Execution time of 3D-stencil, under fixed or TDM-switched memory con-      |    |

|      | nection modes.                                                             | 52 |

| 3.10 | (a) Many-core multi-memory testbed based on a fast tunable laser, a SiP    |    |

|      | wavelength demux and an OpenSoC NoC. (b) Chip image with probes            |    |

|      | landed and fiber array attached. (c) Measured eye diagrams                 | 53 |

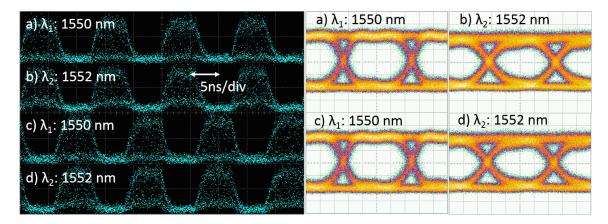

| 3.11 | Experimental demonstration of time-sequenced switching diagrams with       |    |

|      | a channel switching time of 15 ns.                                         | 54 |

| 3.12 | OpenSoC switch fabric outputs showing four cores simulatenously receiv-                           |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | ing memory data from four memory interfaces $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 55 |

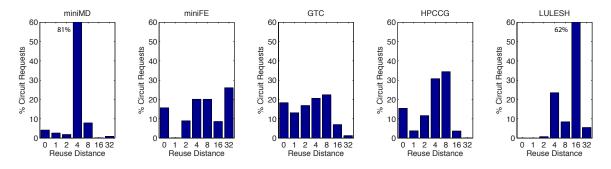

| 4.1  | Distribution of reuse distances for HPC benchmarks (64 nodes). Each bin                           |    |

|      | corresponds to a range between its own label (included) and the next label                        |    |

|      | (excluded), same below                                                                            | 65 |

| 4.2  | Distribution of reuse distances for HPC benchmarks (256 nodes); 512                               |    |

|      | nodes for LULESH.                                                                                 | 65 |

| 4.3  | Distribution of time-based reuse distances for HPC benchmarks (64                                 |    |

|      | nodes). For miniMD, GTC and HPCCG, a high percentage of circuit                                   |    |

|      | reuses are within 16 $\mu$ s                                                                      | 66 |

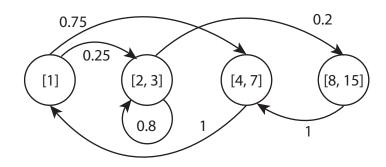

| 4.4  | Example for Transition Matrix Based Preditor. Upper: reuse distance                               |    |

|      | sequence of a circuit. Lower: modeling of the sequence transition using                           |    |

|      | a Markov chain. Each state of the Markov chain corresponds to a bin in                            |    |

|      | the distribution histogram                                                                        | 68 |

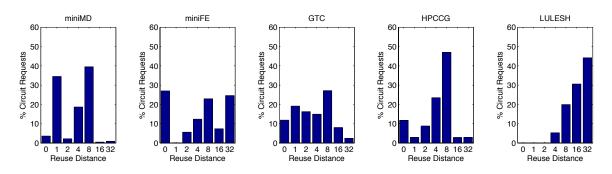

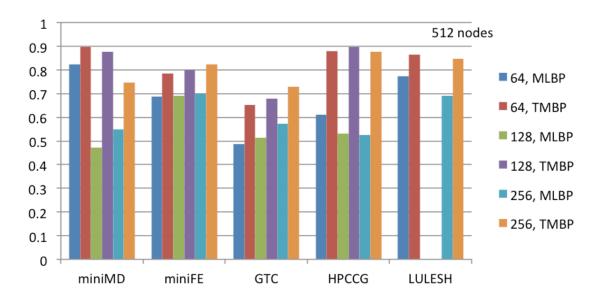

| 4.5  | Reuse distance prediction accuracy of Transition Matrix Based Preditor                            |    |

|      | (TMBP) versus Maximum Likelihood Based Predictor (MLBP), across                                   |    |

|      | different benchmarks and different numbers of nodes. TMBP shows as                                |    |

|      | much as $40\%$ and $36\%$ higher accuracy than MLBP in cases of miniMD                            |    |

|      | and HPCCG, respectively.                                                                          | 68 |

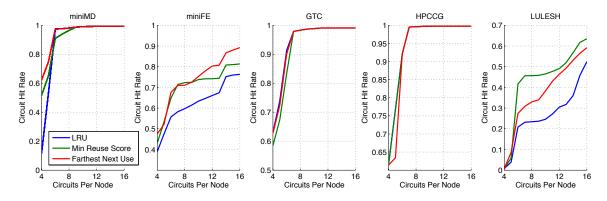

| 4.6  | Circuit hit rates (64 nodes) for replacement policies: LRU, Farthest Next                         |    |

|      | Use and Minimum Reuse Score, across different benchmarks                                          | 71 |

| 4.7  | Circuit hit rate (256 nodes) for replacement policies: LRU, Farthest Next                         |    |

|      | Use and Minimum Reuse Score. 512 nodes for LULESH                                                 | 71 |

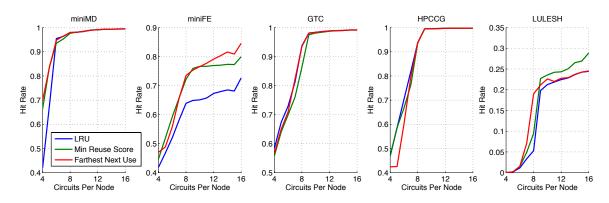

| 4.8  | Circuit hit rate (geometric mean of all benchmarks except LULESH) when                            |    |

|      | maximum vacant time is set to infinity, 1 ms and 1 $\mu$ s                                        | 72 |

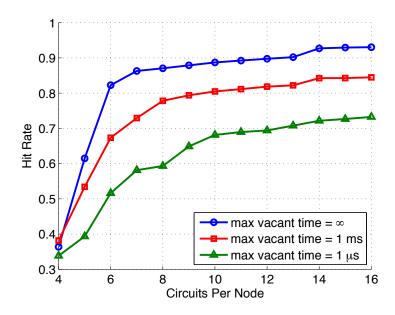

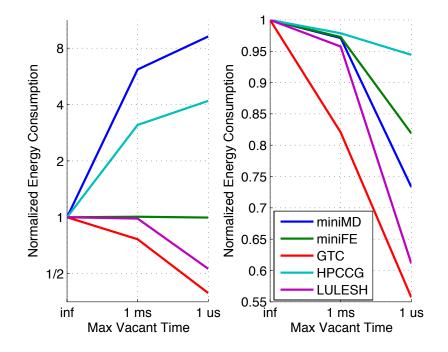

| 4.9 | Energy consumption of circuits versus maximum vacant time. Left: max |    |

|-----|----------------------------------------------------------------------|----|

|     | circuits per node = 6, Right: max circuits per node = 16. All energy |    |

|     | values are normalized to the infinite-vacant-time case               | 73 |

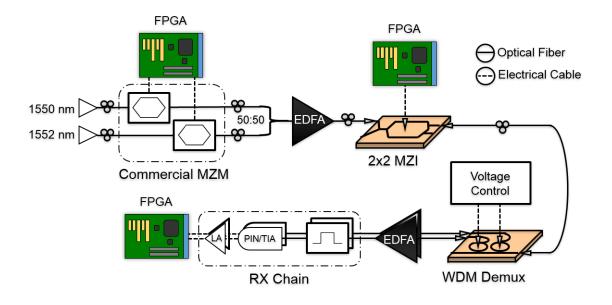

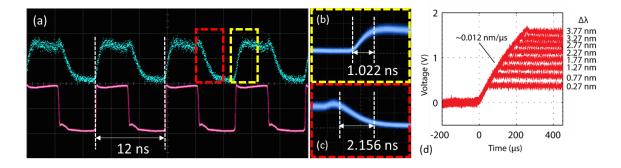

- 4.10 Experimental setup for dynamic WDM circuit reconfiguration (Only one switch to demultiplexer path is shown).75

- 4.11 Left: optically-switched WDM data: (i) 1550 nm and (ii) 1552 nm through one path of the 2x2 MZI switch; (iii) 1550 nm and (iv) 1552 nm through the other path of the switch. Right: optical eye patterns of modulated data. 76

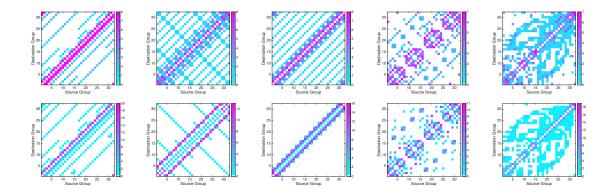

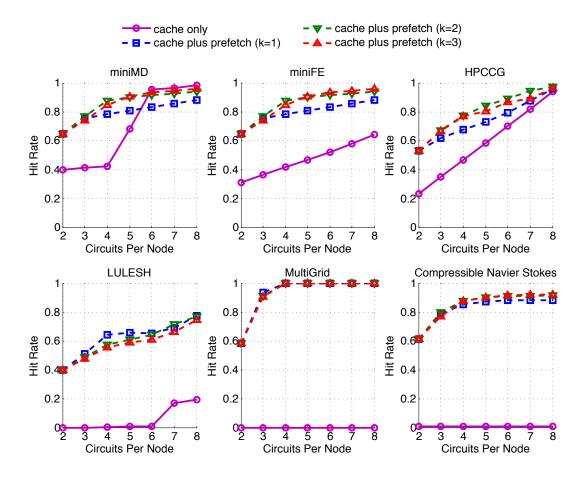

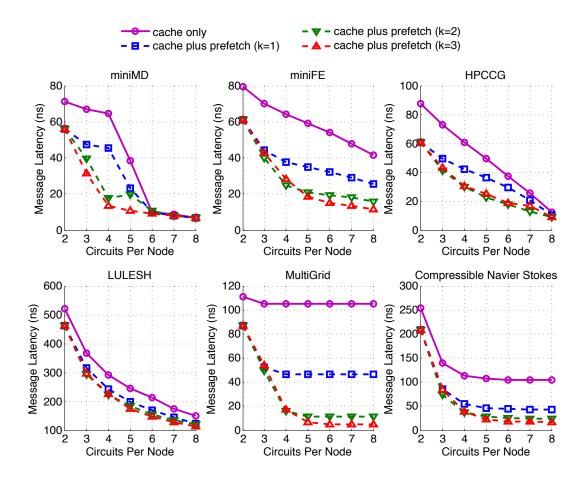

- 5.2 Circuit hit rates achieved by the caching-plus-prefetch scheme (dashed)

with different tail lengths k, versus the caching-only scheme (solid), in a

256-rank simulation. Both schemes employ the least recently used replacement policy.

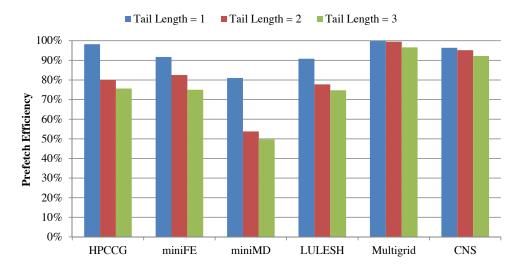

85

- 5.3 Prefetch efficiency against different tail lengths k. The prefetch efficiency is a percentage of prefetches that result in a hit, out of the total prefetches. 87

5.4 Message latency of caching-plus-prefetch scheme (dashed) with different tail lengths k, versus the caching-only scheme (solid), in a 256-rank simulation. Both schemes use the least recently used replacement policy. Circuit setup latency is 100 ns, circuit bandwidth is 100 Gb/s. . . . . . . 88

# List of Tables

| 2.1 | Quality of association with $G = 32, r = 8$                                   |    |

|-----|-------------------------------------------------------------------------------|----|

| 2.2 | Application size and parameters                                               | 23 |

| 2.3 | Content of Flexfly racks                                                      | 31 |

| 3.1 | Routing latency (clocks) from port $(0, 0)$ to port $(X, Y)$ in unit of clock |    |

|     | cycles                                                                        | 56 |

| 3.2 | Breakdown table of latency, and scaling the emulator by a factor of $10 \ $ . | 56 |

| 5.1 | Description of benchmarks used in the simulation and their communica-         |    |

|     | tion features (numbers mearsured at 256 ranks)                                | 83 |

## Acknowledgements

I would like to thank my advisor, Professor Keren Bergman, for advising my PhD study. Without her support and guidance, I would not be able to work in such an interesting field.

I also want to acknowledge US Department of Energy, Sandia Nation Labs and Lawrence Berkeley Lab for sponsoring my research. Special thanks to Jeremiah Wilke and John Shalf who led me into the core of high performance computing and provided valuable comments.

To my colleagues in Lightwave Research Lab, I owe them a lot for the generous help in all aspects. I would like to thank Sébastien Rumley, David Calhoun, Payman Samadi, Christine Chen, Hang Guan, Meisam Bahadori, Yiwen Shen and many others for their collaboration and contribution in my research projects.

I would also like to thank all the members in the dissertation committee, Professor Keren Bergman, Professor Luca Carloni, Professor Michal Lipson, Professor Vishal Misra, and John Shalf.

## Chapter 1

### Introduction

### 1.1 Communication Requirement within HPC

The performance of extreme-scale high-performance computing (HPC) systems relies heavily on the interconnection network as concurrency increase results in massive data exchange between network endpoints [1]–[4]. Designing networks that properly balance compute capability is challenging: over-provisioning the network incurs unnecessary cost [5], while under-provisioning negates the benefits of extra concurrency.

A relatively simple way to denote the computer capability is the number of floating point operations per second (FLOP/s), measured by the LINPACK benchmark. Since the stall of clock frequency around 2004 [6] due to the end of Dennard Scaling [7], increasing the number of cores has been the new driving force for performance improvement. By decomposing a problem to a larger number of "workers", reduction of total execution time is expected. The reduction, however, is often disproportional to the core increase, as parallelism implies communication. With the extraordinary growth in parallelism at all system scales, the performance of today's systems is increasingly determined by how data is communicated among the numerous compute resources rather than by the total raw computation resources available. Assuming

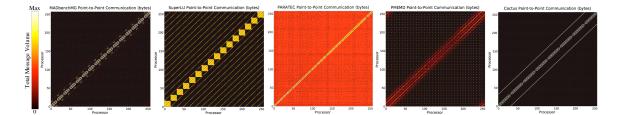

Figure 1.1: Diverse communication patterns of the "Seven Dwarf" applications identified by Phillip Colella [8] and a group of experts from Berkeley [9]. Figure compiled from [9], [10].

a 0.01 byte/FLOP node verbosity, i.e. each node injects 0.01 byte of data into the network per FLOP, a future exascale supercomputer  $(10^{18} \text{ FLOP/s})$  will require 10 PB/s data movement capability. This number is about three orders of magnitude higher than today's global Internet bandwidth usage (about 28 TB/s, 2015).

The need for high bandwidth is not the only aspect. In HPC, the application communication pattern can be highly diverse. In 2004, Phillip Colella [8] identified "seven dwarfs" – seven numerical methods important for scientific computing – which have distinctive communication patterns [9], [10] (see Fig. 1.1). In production runs, the patterns can further diverge due to different domain decomposition strategies, mapping strategies, communication algorithms, etc. Such diversity poses a big challenge to interconnect design, since having a single topology that works well for all applications is almost impossible. Over the last decade, the interconnect topology has seen a transition from multidimensional torus (as in IBM BlueGene/P and Blue-Gene/Q) to Dragonfly (as in Cray XC series). While each generation works best for a certain class of applications – for example, the BlueGene 5D torus for neighbor intensive applications and the Cray Dragonfly for all-to-all applications like FFT – they often fail to do so for another class. It is thus desirable to have a *reconfigurable network* that can create different topologies for different applications – just as how *reconfigurable computing* (like FPGA) adapt for heterogeneous compute needs.

# 1.2 The Memory Wall in Post Moore's Law and Many-core Era

The critical role of memory in computing roots in the long-live von Neumann model, where the memory acts as the source and sink of the processing unit. When the flow injection or egression gets congested, the processing unit will have to stall. Memories in exascale have an even higher bandwidth demand than the system interconnect for its higher byte-per-FLOP ratio (0.1 byte/FLOP in general). That is, an exascale machine will need 100 PB/s memory access bandwidth in total.

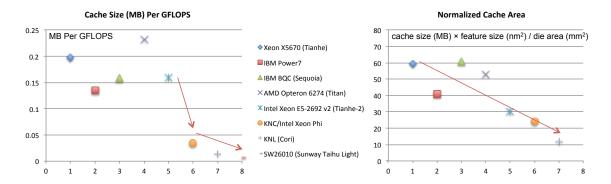

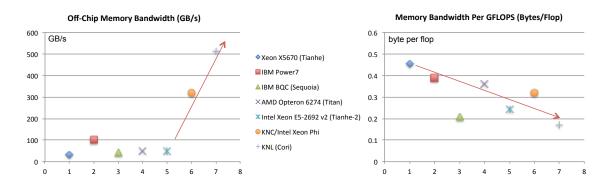

Due to the lag-behind of DRAM performance scaling as compared to transistor performance scaling, there has been a "memory wall" in the last two decades. A major remedy for this has been putting more caches on the processor chip, which is enabled by Moore's Law scaling. However, Moore's Law is ending as we enter the last years of shrinking transistors. Chip designers will thus have to use the available transistors more effectively. One may interpret a few already signs of this trend. As shown in Fig. 1.2, area devoted to cache on a supercomputer processor chip is decreasing, both in terms of (a) MB per FLOP/s and (b) normalized chip area – cache size (MB)  $\times$  features size  $(nm^2)$  / die size  $(mm^2)$ . Especially, a sharp fall is clear as the industry gets into the many-core era (around 2013). Interestingly, this cache cliff matches the time when Moore's Law was said to be dead in the economic sense – starting from 2013, the number of transistors bought per dollar has stayed flat. The fact that chipmakers are willingly trading the cache area for more FLOPs, along with the rise of data-centric throughput computing, calls for much higher offchip memory bandwidth. Fig. 1.3 shows this trend: the sharp increase of the off-chip memory bandwidth matches the cache cliff of Fig. 1.2. This increase, however, is still not enough to balance the FLOPS increase as the bytes per flop ratio continues to drift away from the ideal point.

Figure 1.2: (left) Cache size normalized by GFLOPS. (right) Normalized cache area.

Figure 1.3: (left) Absolute off-chip memory bandwidth. (right) off-chip byte per FLOP ratio.

The memory bandwidth increase is also rapidly stressing the pin count limit of the processor package. For example, KNL requires 3647 pins in the socket, plus 1024 pins in the interposer for each of the eight on-package memory stacks. The pin density of standard chip package, however, cannot scale indefinitely. The ever-increasing bandwidth demand thus requires a more efficient chip I/O technology for processors beyond the Moore's Law.

There is more to this grim description. As many-core architectures start to get widely adopted, effects such as hotspots and non-uniform-memory-access (NUMA) emerge as a result of using network-on-chip to access memory [11]. These effects, in addition to the bandwidth bottleneck, place a detrimental scaling barrier to dataintensive computing. Moreover, they require careful designs that can accurately de-

Figure 1.4: Microring-based silicon photonic link.

liver the bandwidth to where needed, rather than purely increasing the memory bandwidth in a brute-force way.

### **1.3** Photonic Interconnects

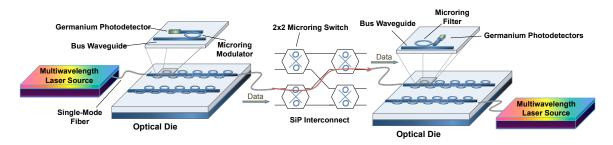

Optical interconnects have emerged as a promising technology for large-scale systems as they can support transmission of very high data rates in an energy-efficient manner. By using wavelength division multiplexing (WDM), a single optical fiber or waveguide can transmit tens of independent channels achieving terabit/s aggregate bandwidth. In addition, due to the low loss of the optical medium, the high bandwidth data movement can scale over warehouse distances and provide end-to-end connectivity in a distance-agnostic manner. Photonic interconnects thus have the potential to satisfy the bandwidth demand for exascale.

Silicon photonic technology, in particular, presents a potential platform for realizing photonic components in a cost-effective manner. The technology uses silicon rather than conventional materials as the core transmission medium. It thus allows the formation of optical communication devices (including modulators, switches, filters, detectors, etc.) in the same materials and process platform as used in the complementary metal oxide semiconductor (CMOS) industry [12]. This capability brings many advantages, including small device footprints, low power consumption and the potential for low-cost large-scale integration. Fig. 1.4 shows a silicon photonics link. It consists of modulators, switches, wavelength demultiplexer and photo detectors. Modulators are usually based on a ring structure. By tuning the ring's resonance on or off with respect to the laser wavelength, on-off keying can be implemented. For fast modulation, mechanisms that change the carrier density within the optical mode are often employed, including carrier injection, depletion and accumulation [13]. The carrier density changes the refractive index of the waveguide and hence the resonance wavelength of the ring. By cascading multiple rings on the same waveguide working on different resonance, WDM transmission is possible. In this case, each ring modulates a different wavelength.

At the reception side, a wavelength demultiplexer is required to separate the wavelengths, i.e. dropping them at different ports. The demux can be also based on the ring structure. Different from modulation, the tuning of the demux (as well as any other switching devices) might not need to operate as fast. Thermal tuning methods are thus widely employed. Heating or cooling the ring will change its dimension, hence the distance experienced by light and hence the resonance.

### 1.4 Beyond Just High Bandwidth

Due to the lack of practical buffers in the optical domain, current high-performance interconnection networks employ optical interconnects to transmit data while electronic routers are used for switching and routing. While these designs resolve the bandwidth  $\times$  distance problem, they require multiple optical-electronic-optical (O/E/O) conversions at the interfaces. As the power consumption of the electronic switching and the O/E/O interfaces scale poorly with the increased serial data rate, such switch designs might not be able to scale in a power efficient manner to address the growing communication needs of HPC.

As an alternative solution, electronically controlled optical switching (Fig. 1.4),

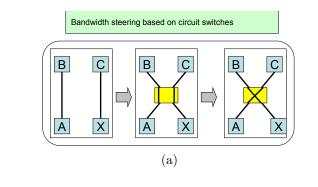

Figure 1.5: (a) Rewiring links or steering bandwidth using a circuit switch. (b) Photonics enabled flexible topologies.

in which the data signals remain primarily in the optical domain, have been proposed and demonstrated [14]–[18]. In these photonic switches, the energy consumption is essentially decoupled from the data rate [19] and can therefore scale in an energy efficient manner. Moreover, the switches can provide bandwidth steering (i.e. dynamic rewiring) functionality for their electrical clients. See Fig. 1.5a for a simple example based on a 2-by-2 switch. We can hence utilize this bandwidth steering/rewiring feature to reconfigure network topologies for the diverse communication requirements, covering, for example, both all-to-all and neighbor-intensive patterns (Fig. 1.5b). Part I of this thesis ("Leveraging Photonic Switching") will explore this direction in the context of system interconnect (Chapter 2) and memory interconnect (Chapter 3), respectively.

Another feature of photonic interconnects beyond just bandwidth is its end-to-end connectivity. In a network with node-to-node optical connections, energy dissipation due to electrical packet switching can be eliminated, and network architecture flattened. However, due to the circuit switched nature, such network may suffer from path setup time. Part II of this thesis ("Avoiding Path Setup Overhead") develops remedy approaches for this aspect by observing and leveraging application-level characteristics. Chapters 4 and 5 present passive and active latency-hiding techniques, respectively.

# Part I:

# Leveraging Photonic Switching

## Chapter 2

# Photonics Enabled Flexible Topology – A Dragonfly Example

### 2.1 Motivation

The Dragonfly network [20], [21] has emerged as a low-diameter, high-radix solution for HPC interconnects. A Dragonfly has two levels: in the lower level, intra-group routers are connected in local networks called groups, usually in an all-to-all or 2Dflattened butterfly (2D-FB) topology [22]; in the upper level, groups are connected through an all-to-all or high-degree topology.

With its high-connectivity at both levels, Dragonfly can greatly reduce the network diameter over topologies such as multidimensional torus or fat tree. A Dragonfly can connect any two routers within a distance of 5 if the intra-group network is a 2D-FB or a distance of 3 if an all-to-all network. A price for the high-connectivity, however, is diluted per-link bandwidth. In particular, the bandwidth of inter-group (global) links, carrying all the traffic between two large sets of routers, becomes the most scarce resource and can become bottleneck for the entire network [23]. Many scientific applications on a Dragonfly platform, unfortunately, tend to concentrate

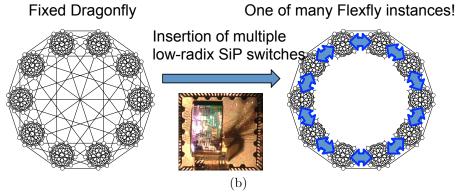

Figure 2.1: (a) A six-group Dragonfly, all-to-all both inter- and intra- group. (b) Connectivity matrix.

traffic on only a few of these links. +1/-1 neighbor-group based communication pattern, for example, is prevalent for many applications (detailed later). Moreover, inter-group traffic matrix is often sparse, leading to bandwidth allocated for idle pairs.

Ideally, total available bandwidth should be allocated where most needed. Being a fixed topology, however, Dragonfly can only try to achieve this through global or adaptive routing. Numerous routing strategies [20], [24]–[29] have been proposed, but they result in longer-distance paths and cross-group interference [30]–[32].

### 2.2 The Dragonfly Topology

Dragonfly is a direct topology that partitions S routers into G groups. Figure 2.1a illustrates a six-group Dragonfly. Each router is connected to C compute nodes (not shown in the figure), enabling a direct network of N = C \* S total compute nodes.

Links in Dragonfly are segregated into two *tiers*. Bottom-tier links connect routers of the same group, they are thus *local*, *intra-group* links. Top-tier links go over group boundaries and are thus *global*, *inter-group* links. There are no strict rules for the *intra-group* topology. For groups composed of a small number of routers (e.g. n < 20), an all-to-all topology is practical. For larger groups, a 2D-Flattened Butterfly (2D-FB) [33] is generally retained, meaning that routers form a 2D lattice and are fully-connected in each row and column. As for the upper tier, the groups are usually fully connected. That is, the global links are disposed such that any pair of groups are connected by k links. Each group thus has k(G-1) outgoing and incoming links. To allow a balanced distribution of the links over the n routers within a group, k(G-1) should be a multiple of n. In the simplest ("canonical" Dragonfly), k = 1 and n = G - 1, and each router within a group is a gateway to one particular remote group. The total number of routers is then S = G(G-1), while the number of global links is the same. If an all-to-all intra-group topology is used, there are G(G-1)(G-2) intra-group links; for a 2D-FB intra-group topology, the number is  $2G(G-1)(\sqrt{G-1}-1)$ . The number of *intra-group* links exceeds the number of *inter-group* links by a factor of O(G) for all-to-all or  $O(\sqrt{G})$  for 2D-FB.

A key feature of Dragonfly topologies is their strictly bounded *diameter*. In the worst case, a message towards another group must i) route to the corresponding gateway within the source group, ii) traverse the global link, and iii) route to the destination router within the destination group. The diameter D of Dragonfly thus equals  $1+2D_{intra}$ , where  $D_{intra}$  is the diameter of the intra-group topology. Hence, if the intra-group network is all-to-all, then D = 3; if the intra-group network is 2D-FB, then D = 5.

### 2.3 Traffic Characterization on Dragonfly

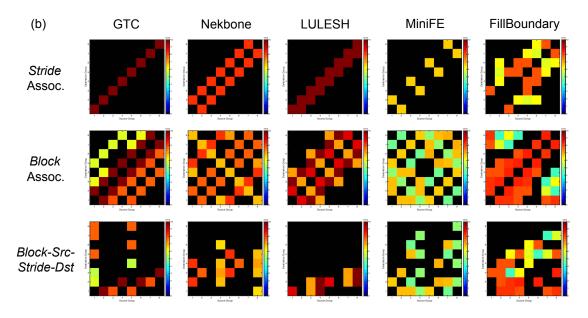

Although Dragonfly has many advantages as mentioned above, its bandwidth allocation at the inter-group level can consistently mismatch the executed traffic pattern. In Fig. 2.2(b-f), group-to-group (G2G) traffic matrices are collected from a set of representative HPC applications. The figures show that G2G traffic matrices are far from

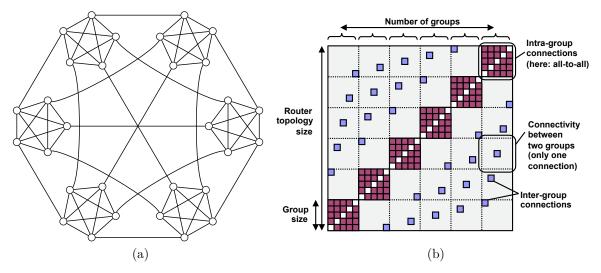

Figure 2.2: *Group-to-group* traffic matrices of applications run on a 32-group Dragonfly.

being uniform and many pairs of groups do not communicate at all (black regions). Also apparent: a large portion of traffic concentrates on just a few source-destination pairs, e.g. +1/-1 neigbors.

Among these evaluated applications, GTC (Gyrokinetic Toroidal Code) [34], [35] is a particle-in-cell simulation for plasma microturbulence and features neighborintensive point-to-point communications. The most distinguishing feature of GTC is (cyclic-shifted) diagonal lines with the heaviest traffic on the +1/-1 neighbor groups, which is also referred to as the "worst-case" adversarial traffic pattern for Dragonfly. Nekbone represents the main computational kernel of Nek5000 [36], an application for large eddy simulations and direct numerical turbulence simulations based on spectral element methods. The Nekbone kernel studied in this paper solves a Poisson equation using conjugate gradient iteration with no preconditioner. In addition to intensive traffic along the diagonal, Nekbone also has a complement (anti-diagonal) pattern due to collectives. LULESH [37] is a proxy-app representing typical hydrocodes. In this paper, LULESH partitions the problem into a collection of volumetric elements defined by a 3D mesh and features 3D neighbor based communications. LULESH has a thick ribbon-shape pattern along the diagonal. MiniFE is a Finite Element mini-app from the Mantevo suite [38]. It assembles and solves a sparse linear system from a conduction equation using a conjugate-gradient algorithm. Its traffic pattern is characterized by an absence of diagonal lines. Lastly, FillBoundary is a simple code designed to profile communication patterns associated with ghost cell exchanges. We simulated the halo update of a BoxLib-based [39] production partial differential equation (PDE) solver. FillBoundary has an irregular traffic matrix and induces traffic between about half of the group pairs (with the heaviest traffic concentrated on a few pairs).

For many applications like the above ones, the traffic pattern is known a-priori. This information can be used for configuring the interconnect at, for example, job launch time. For other applications that are more dynamic, an iterative aspect usually exists in traffic patterns, and the runtime middleware should easily be able to characterize network traffic based on the first few iterations and then perform the reconfiguration.

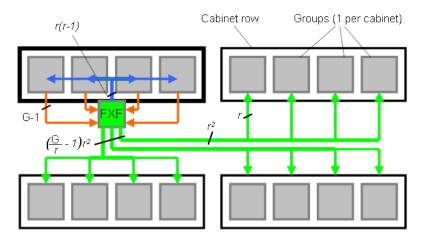

### 2.4 Flexfly: A Reconfigurable Dragonfly

We propose Flexfly, a silicon photonics (SiPh) based architecture that enables flexible allocation of Dragonfly global links. In Flexfly, the global links initially composing the all-to-all topology can be "stolen" from their original destination groups, and reassigned to traffic-intensive ones. By trading the global links in this way, Flexfly creates additional *direct* bandwidth for intensively-communicating group pairs, matching the topology to the application traffic. Flexfly achieves such reconfigurability through

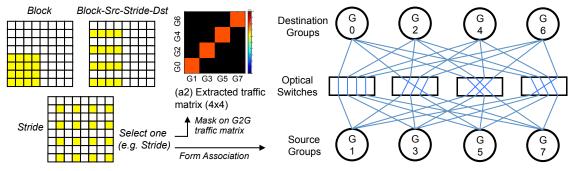

(a1) Group association masks (G=8, r=4) (a3) Connections in an Association (switch states showing a DFly configuration)

Figure 2.3: Construction flow of the Flexfly architecture.

transparent SiPh circuit switching. Unlike previous optical switching solutions which rely on large port counts (equal to the number of nodes, racks, routers [40] or groups [41]), Flexfly is designed in a way to support the use of low-radix optical switches, independently of the global system scale. Such low radices enable massive low-cost fabrication through current SiPh technologies and realizable SiPh switch designs. As compared to adaptive routing, Flexfly creates multiple minimal paths and mitigates the need for indirect routing.

In this section, we describe how Dragonfly groups, in topologies of any size, can be interconnected with arbitrary-radix SiPh switches and how the link re-allocation is performed.

A construction flow for the Flexfly architecture is shown in Fig. 2.4. A group association mask is used to extract a sub traffic matrix from the group-to-group traffic matrix. Examples of mask for G = 8, r = 4 (r being the optical switch radix), and the extracted traffic matrix (ETM) corresponding to the *Stride* mask, are shown in Fig. 2.4. Also corresponding to the mask is a set of source and destination groups, which we call an Association. These groups are originally fully-connected in Dragonfly. In Flexfly, r optical switches each of radix r are inserted in the middle of the  $r^2$  optical connections owned by each Association, as shown in Fig. 2.4(3). An Association is thus composed of r source groups and r destination groups. The source and destination groups do not have to be the same. The ETM size is also  $r \times r$ .

In Fig. 2.4(3), the state of the switches ensures an all-to-all connectivity among the Association. This corresponds to the "original" Dragonfly connectivity. In presence of non-uniform traffic, this all-to-all connectivity can be reconfigured to reallocate global bandwidth to traffic intensive source-destination group pairs. Considering, for example, the ETM in Fig. 2.42, switches can be configured such that all four links originated at G1, G3, G5 and G7 are destined to G0, G2, G4 and G6, respectively. In that case, the bandwidth concentration within the Association is maximal (r = 4-fold). It should be noted that associating the groups will not lead to network isolations, since a group can appear in multiple Associations.

#### Group Association Strategies

Multiple strategies exist when creating Associations contained in a Dragonfly, corresponding to different group association masks. Each strategy results in different sets of ETMs, which may exhibit variable potential for link concentration. In this set of possibilities, we are interested in the strategies that a) distribute traffic evenly across associations, b) provide flexibility that can be exploited by major HPC traffic patterns, and c) allow easy cabling across the supercomputer cabinets. With respect to b), remark that in Fig. 2.4(2), all the "dark" (unused) links can be re-allocated to the four active group pairs. We therefore look for strategies favoring such situations. Here we propose three major strategies for comparison: Stride association, Block association, and Block-Source-Stride-Destination (BSSD) association. Their respective masks are shown in Fig. 2.4(1). We will evaluate the "quality of association" of these strategies based on the applications shown in Section 2.

The *Stride* strategy selects groups with a stride of k = G/r in both source and destination dimensions. This strategies generally allows the distribution of heavy traffic spots into different associations. The stride k, however, should avoid coupling

|            | std of number of         | -                        | max number of      |

|------------|--------------------------|--------------------------|--------------------|

|            | nonzeros $(\sigma_{nz})$ | centage $(\sigma_{pct})$ | nonzeros in a line |

|            |                          |                          | $(n_{NZL})$        |

| Block      | 13.12                    | 6.72                     | 2.86               |

| Stride     | 10.23                    | 6.09                     | 2.56               |

| Block-Src- | 7.14                     | 0.93                     | 4.38               |

| Stride-Dst |                          |                          |                    |

Table 2.1: Quality of association with G = 32, r = 8

with the distance between two intensive destinations. By contrast, the *Block* strategy selects r continuous groups in both source and destination dimensions. *Block* relies on an assumption that neighboring sources tend to "favor" the same configuration when connecting to destinations – for example, in GTC each source group prefers connections to their +1 neighbors. Such "harmony" allows for skewing the original source-destination (s-d) connections within a switch by the same amount, thus simplifying the determination of the switch state. The *Block* strategy, however, fails to efficiently distribute the traffic across *Associations* in presence of traffic concentrated along the diagonal (for neighbors-intensive communication patterns as in LULESH). Hence, it results in higher chance of creating fully occupied ETMs on one side, and purely dark ETM's on the other side. The third strategy, *BSSD*, is a mixture of the previous two for comparison purpose. Fig. 2.4 show how the different strategies generate distinct ETMs.

#### Evaluation of Association Strategies

We evaluate which association strategy provides flexibility in the most relevant way for HPC applications. We use three metrics from the ETM pool as a measure of "quality of association": 1) standard deviation of the number of nonzeros across ETM's  $(\sigma_{nz})$ , 2) standard deviation of the traffic percentage across ETM's  $(\sigma_{pct})$  and 3) average of maximum number of nonzeros in a line (row or column) of an ETM

Figure 2.4: Representative ETM's from applications using the three association strategies; here switch radix r = 8, hence ETM size is  $8 \times 8$ .

$(n_{NZL})$ . The first two metrics are intended to indicate how evenly the G2G traffic is distributed across different ETMs/associations. The third metric  $n_{NZL}$ , by contrast, indicates the maximum communication degree of a source or destination group within an association, i.e. how many links are necessary for a source or destination to cover its non-zero traffic. The higher this value, the lower the flexibility, as "necessary" links cannot be stolen (described later in Sec. 2.5).

Since it is impossible to find a single association strategy that works best for every application, we use a statistical approach to evaluate the above strategies based on the application set described in Sec. 2.3. The statistics are hence a pool of ETM's extracted from the G2G traffic matrices of those applications, using respectively the three association strategies.

The evaluation result is shown in Table 2.1. *BSSD* achieves the smallest  $\sigma_{nz}$  and  $\sigma_{pct}$ , i.e. it distributes traffic most evenly among the ETM's. However, for  $n_{NZL}$ , the performance of *BSSD* is the worst; indeed, the  $n_{NZL}$  of *BSSD* is much higher than that resulting from the *Stride* strategy or *Block* strategy. This means that *BSSD*

requires more "necessary" switching modes to cover the nonzeros in ETM, reducing the amount of free links (flexibility) useable for intensive traffic. The *Stride* strategy, in comparison, achieves the lowest  $n_{NZL}$  and hence the highest flexibility. Therefore, we use it in later application-based simulations.

### 2.5 Link Stealing Algorithm

After forming the associations, Flexfly applies a link stealing algorithm to each of the associations for allocating global bandwidth based on the ETM (note that in practice, associations are formed once for all at design time, whereas to link stealing algorithm is applied for each new application). The task of the link stealing algorithm is to find a set of switch states for the r optical switches owned by an association. Since each association is independent, the link stealing algorithm can be applied in parallel. Furthermore, limited radixes r ensures that each problem remains small in scale.

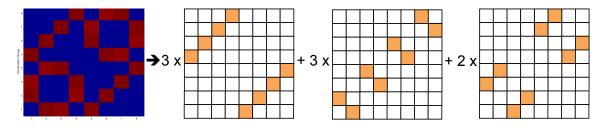

A decomposition example for r = 8 is shown in Fig. 2.5. Rather than using the 8 switches for forming an all-to-all topology, Flexfly picks permutation matrices (each corresponding to a switch state) to cover the heavy traffic, resulting in a 2 to 3 times bandwidth increase for each nonzero s-d pair.

Here we formulate the link stealing problem with a min-max rule: given a nonnegative  $r \times r$  ETM  $T = (t_{ij})$ , find a set of r permutation matrices  $\{P_1, P_2, ..., P_r\}$ , such that

$$\max_{i,j} \frac{T_{ij}}{(\sum_{k=1}^r P_k)_{ij}} \to \min$$

It is already known that a *decomposition problem* with a min-max optimization rule is NP-hard [42]. Here we give a heuristic algorithm yielding an efficient decomposition.

In the algorithm, a nonzero entry T will be given a weight close to infinity if that entry has not been allocated a link. In this way, the algorithm makes sure that

Figure 2.5: Decomposition of an example ETM into three switching modes (r = 8).

#### Algorithm 1 Min-Max Decomposition

#### **Require:** $T_{r \times r}$

- 1:  $inf \leftarrow a$  large number

- 2:  $D_{r \times r} \leftarrow 0$

- 3: Define a bipartite graph G = (V, E), where  $(i, j) \in E$  has weight:

$$w_{ij} = \begin{cases} T_{ij}/(D_{ij}+1), & \text{if } D_{ij} \ge 1\\ T_{ij} \cdot \textit{inf}, & \text{otherwise} \end{cases}$$

- 4: Find a maximum weight matching  $P_k$  in G

- 5:  $D \leftarrow D + P_k$

- 6: If k = r, STOP; else go to 3.

an uncovered nonzero entry will have higher priority in getting picked than those already covered, even if the latter has much more traffic to send. Due to the nature of permutation matrices, whereby the line sum of each row and column is always 1, the final allocation matrix D will have a line sum of r for each row and column. This means that the number of transmitters needed by a source group for that association, i.e. row sum of D, does not exceed r; and similarly, the number of receivers needed per destination group, i.e. column sum of D, does not exceed r either. Each permutation matrix in  $\{P_1, ..., P_r\}$ , which corresponds to an input-output mapping, can be carried out by one optical switch in that association.

### 2.6 Routing in Flexfly

In this section, we discuss the routing schemes for Flexfly. Since in Flexfly there can be multiple *direct* links to the same destination group, the routing scheme must be able to efficiently utilize these links.

#### Minimal Valiant Routing

In Flexfly, to load-balance the traffic across multiple minimal paths, the Valiant algorithm approach can be used to randomizes the path selection. This algorithm, which we call Min-Val, takes three steps for a source router  $R_s$  in group  $G_s$ :

- 1. If  $G_s \neq G_d$ ,  $R_s$  randomly selects a router  $R_a$  in  $G_s$  that has a global channel to  $G_d$  ( $R_a$  can be  $R_s$  itself) and route within  $G_s$  from  $R_s$  to  $R_a$ ;

- 2. traverse the global channel from  $R_a$  to reach router  $R_b$  in  $G_d$ ;

- 3. If  $R_b \neq R_d$ , route within  $G_d$  from  $R_b$  to  $R_d$ .

Different from the Valiant routing in Dragonfly, MIN-VAL in Flexfly does not involve intermediate groups, i.e., the path selection is always among minimal paths. This ensures exactly one global hop for all cross-group packets, enabling more than 50% throughput in global level.

#### Minimal UGAL Routing

The Min-Val algorithm works well in load-balancing traffic evenly across multiple minimal paths. However, it does not consider different congestion states of different paths. Minimal UGAL (Min-UGAL) overcomes this drawback by using queue lengths to estimate network delay and choose the path with minimal delay. Similar to Min-Val, Min-UGAL does not involves intermediate group either. For the UGAL-L version [43], which uses *local* queue information at the current router, the algorithm is described as follows: if  $q_m H_m \leq q_{nm} H_{nm}$ , route minimally; else route non-minimally. Here, the minimal and non-minimal paths both take one global hop, and differ only in the number of hops within source/destination groups.

Figure 2.6: Global link allocation with switch radix r = 8 (upper) and r = 32 (lower). Note that the color scales are different across sub-figures.

# 2.7 Simulation

In this section, we use the HPC applications from Sec. 2.3 to evaluate Flexfly performance relative to minimal and UGAL routing for Dragonfly. The application configurations are shown in Table. 2.2. In the simulation, we assume the Dragonfly network has an all-to-all topology in the upper level and a 2D-flattened Butterfly in the lower level. We assume 3 GB/s for both intra- and inter- group links and an injection bandwidth of 8 GB/s. Switch hop latencies are 40 ns. The applications are simulated either in form of mini-apps (GTC, MiniFE and LULESH) or by replaying timestamped MPI traces using the DUMPI tracing tool (Nekbone and FillBoundary). Both forms are simulated through the SST simulator (SST/macro) [44]. Trace replay uses a coarse-grained packet simulator that models routing and control-flow at the level of packets [45]. Traces were collected in a MPI-only fashion on CPU-only machines. Here we examine "optimistic" scenarios for on-node parallelism, assuming a compute time speedup factor of 1/1152 leveraging abundant on-node parallelism (multi-threading with accelerators) in future applications. The traces were obtained from a NERSC web portal on characterization of DoE mini-apps [46].

Fig. 2.6 shows the global link allocation generated by the link stealing algorithm

for different applications. With a modest radix r = 8, the allocation matrices already become very similar to the G2G traffic matrices in Sec. 2.3. As r increases, more "unused" links can be stolen for intensive traffic pairs. When r = G = 32 (full reconfigurability) every unused link can be stolen for traffic and the allocation matrix pattern matches the G2G traffic matrix.

| Application  | Size | XYG    | Concentra-<br>tion | Parameter       |

|--------------|------|--------|--------------------|-----------------|

| GTC          | 1024 | 4 8 32 | 1                  | $npartdom{=}32$ |

| Nekbone      | 1024 | 4 8 32 | 1                  | DUMPI trace     |

| LULESH       | 4096 | 4 8 32 | 4                  | nx = 256        |

| MiniFE       | 1024 | 4 8 32 | 1                  | nx = 256        |

| FillBoundary | 1000 | 4 8 32 | 1                  | DUMPI trace     |

Table 2.2: Application size and parameters

## Application Speedup

Fig. 2.7 (top chart) shows the speedup of Flexfly (Ffly) with different switch radices as compared to Dragonfly (Dfly). Here we use minimal, Valiant and UGAL routing for Dragonfly, and minimal, Min-Val and Min-UGAL routing for Flexfly. For comparison purpose, the speed of Dfly-Min is normalized to 1.0x. When minimal routing is used, Flexfly achieves at most 7.1x speedup over Dfly-Min and 1.8x speedup over Dfly-UGAL in the case of GTC (the most neigbor intensive application). When Min-UGAL routing is used, these two speedup numbers are 8x and 2x. In the case of LULESH, Flexfly with r = 32 and any routing algorithm achieves 5x speedup over Dfly-Min and 1.7x over Dfly-UGAL. For MiniFE and FillBoundary, Flexfly also shows better performance than both Dfly-Min and Dfly-UGAL, but with a modest speedup (< 1.5x). This limited speedup is due to the less sparse traffic matrix of these two application, which results in reduced stealing possibility. Another reason for MiniFE is that its communication is not very intensive, rendering the performance more compute-bounded. Within Flexfly, the performance also improves in general as the switch radix r increases (due to more flexibility).

From the above results, one can see that the sparser the traffic matrix is, the more free links Flexfly can steal, and hence the better the performance. In light of this, a more aggressive approach would be to sparsify the traffic matrix *before* applying the link stealing algorithm. This is done by eliminating the light traffic dots that are not "worth" allocating one full link of bandwidth. A possible approach is to use two links that would be allocated for two heavy traffic dots to provide a two-hop path for the light traffic dot (similar to indirect routing). In this way, the link that would have been allocated to the light traffic dot can be freed for servicing heavy traffic. Although indirect paths are used, it is used for the light traffic, creating little impact on the network load. By contrast, in UGAL or other indirect routing approaches for Dragonfly, the indirect paths are often used by heavy traffic, which can quickly consume the capacity of the network.

#### Hop Counts and Latency

A closer look of the architecture performance can be found in the middle and bottom charts of Fig. 2.7. On the hop count experienced by global messages, Valiant and UGAL routing result in much more hops than minimal routing in Dragonfly due to the traversal of intermediate groups (about 40-50% increase). By contrast, Flexfly with any switch radix and any of Min, Min-Val and Min-UGAL routing, requires even less hops than Dfly-Min. There are two reasons for that: (1) the three Flexfly routing algorithms all rely on direct global links rather than intermediate groups, and (2) the increased distribution of wanted global links in the group plane reduces the distance to/from cross-group gateways. Specifically, Ffly-Min halves the hop count compared to Dfly-UGAL in cases of GTC and LULESH. With respect to the latency of global messages, the same trend is observed, as a combined result of reduced hop counts

Figure 2.7: (Top) Speedup of Flexfly (r = 2, 4, 8, 16, 32) with various routing mechanisms over Dragonfly with minimal routing (normalized to 1.0x). (Middle and bottom) Hops and latencies of cross-group messages. Val and UGAL are used on Dragonfly. Min-Val and Min-UGAL are used on Flexfly.

and increased cross-group bandwidth. In cases of GTC, LULESH and FillBoundary, Ffly-Min (r = 32) achieves 2x, 2.5x and 3.2x reduction in global message latency over Dfly-UGAL. The difference in message latencies across application is mainly due to different message sizes.

# 2.8 Experimental Demonstration

We built a 32-node Flexfly prototype using a 2-by-2 SiPh switch to evaluate the implementation complexity and performance improvements compared to Dragonfly.

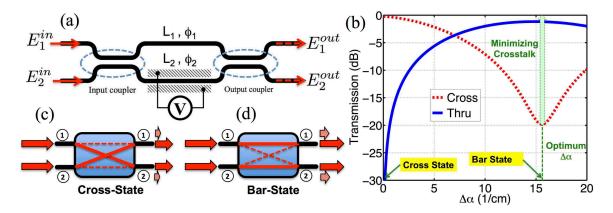

Figure 2.8: (a) Socketed switch chip mounted on a PCB; (b) Bar and cross configurations for ports 1 and 4 in the six-MZI Benes switch.

# Silicon Photonic Switch

The SiPh switch (Figure 2.8a) embedded in the HPC testbed was manufactured through the OpSIS [47] foundry. The chip was mounted in a plastic leaded chip carrier socket that was soldered on a printed circuit board (PCB). The SMA input/output from the board is connected to the bias control units (Fig. 2.8a). The switch is a rearrangeably non-blocking  $4 \times 4$  Beneš topology [48], comprised of three stages and six  $2 \times 2$  Mach-Zehnder interferometer (MZI) elements. Further characterization of the device is reported in [49]. For this particular demonstration, the switch is biased to either a *bar* or a *cross* state, turning it as a  $2 \times 2$  as illustrated in Fig. 2.8b. Dynamic extinction ratios are maximally 15 dB and minimally 7 dB in the *bar* state, while in the *cross* state it ranges from 19 to 24 dB. A Data Acquisition (DAQ) unit was employed to generate the voltages applied to the device. A C program controls the DAQ and is directly callable by a *controller server*.

# **Flexfly Prototype**

The 32-node prototype comprises 16 routers divided in four groups. This structure, shown in Fig. 2.9b, corresponds to a G = 5 Dragonfly whose fifth group has been

Figure 2.9: (a) 32-node Flexfly prototype and (b) corresponding topology diagram  $(2 \times 2 \times 4)$ ; (c) Comparing round trip time over 8 pairs of servers (each pair in different groups), in Dragonfly or Flexfly configurations.

removed (due to Ethernet switch limited port count). Two servers are connected to each router (C = 2), as shown in Fig. 2.9b and Fig. 2.15. Each server is equipped with a dual-core Intel Xeon processor, 10 GB RAM, and a 10Gbps Network Interface Card (NIC). Routers are 10G OpenFlow [50] Ethernet switches. The intra group links are 10G Direct-Attached Cables. For inter-group links, 10G SFP+ transceivers are connected to a 3-meter long Single-Mode Fiber (SMF). One of the servers (the *controller server*) sends reconfiguration commands to the DAQ for switching between the *bar* and *cross* states and to the routers for updating the flow table rules.

#### Experimental Results

We began by measuring the switching time of the silicon photonic switch, controlled by the DAQ. Figures 2.10a and 2.10b show the switching time of the *bar* and *cross* states. We were able to achieve 820 ns switching time using a DAQ supporting mega-sample per second analog output. Note that faster switching times could be reached using an RF driver rated for GHz range instead (the intrinsic switching time of the MZI-based switch with P-N junctions being in nanoseconds-range [49]). This measurement shows that switch reconfigurations can be applied rapidly.

Figure 2.10: Silicon photonic switch setup time for (a) bar and (b) cross states.

By injecting traffic using the Hpcbench MPI benchmark [51], we measured the message round-trip delay between 8 pairs of servers located in two groups. For the traffic pattern, we had each server in G1 communicating with a corresponding server in G4. In the *cross* state, which corresponds to the original Dragonfly topology, there is one global link between the two groups. Setting the switch in the *bar* state grants an additional link to this G1–G4 group pair. We measured the message round-trip delay between each pair of servers using messages of 1MB, 10MB and 100MB. The experiment was averaged over 10 runs. Fig. 2.9c shows the average latency over the 8 pairs of servers. In the Flexfly-adapted configuration, the round trip delay reduces by 33%, 35% and 47% compared to Dragonfly, for 1, 10, and 100MB messages respectively.

We then generated four point-to-point traffic flows between routers 3 and 4 of Group 1 and Group 4, and four other flows between routers 3 and 4 of Groups 2 and 3 (as indicated by the gray arrows in Fig. 2.9b). The routing scheme utilizes minimal routing, i.e., the direct global link between the groups are used for inter-group transmission. The traffic is generated by iperf [52], a network measurement tool. We measured the throughput between servers. In Dragonfly configuration (*cross* state of the SiPh switch), there is an optical global link between each two groups. In this

Figure 2.11: (a-d) Measured throughput of servers in a data transfer between G1 to G4 and G2 to G3. G: group, R: router, S: server. Throughput is higher in the Flexfly-adapted configuration (*bar* state) as two global links are awarded to each of the above group pairs.

Figure 2.12: Demonstration of on-the-fly reconfiguration across the Flexfly prototype. Reconfiguration is performed at second 15 approximately and one extra global link is provided between the two groups.

case, all G1–G4 traffic is routed over the global link attached to routers 4. Similarly, all G2–G3 traffic goes over the global link attached to routers 3. That is, these two global links are each shared by four flows. In contrast, the global links between G1–G3 and G2–G4 are unused. By configuring the switch from *cross* to *bar* (Flexfly), these unused global links are allocated to the G1–G4 and G2–G3 pairs, resulting in superior throughput improvement (about 2x as shown in Fig. 2.11). Note that in the Dragonfly configuration, flows that have to take extra intra-group hops (Figs. 2.11a and 2.11d) retains a lower share of the global bandwidth. These extra hops, which increases the round-trip time, can potentially affect the flow control, resulting in lowered bandwidth. In contrast, in the Flexfly configuration, all flows can be routed over minimal hops, leading to a fairer bandwidth access in that particular case.