# Finding, Measuring, and Reducing Inefficiencies in Contemporary Computer Systems

## Melanie Kambadur

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

## **ABSTRACT**

# Finding, Measuring, and Reducing Inefficiencies in Contemporary Computer Systems

## Melanie Kambadur

Computer systems have become increasingly diverse and specialized in recent years. This complexity supports a wide range of new computing uses and users, but is not without cost: it has become difficult to maintain the efficiency of contemporary general purpose computing systems. Computing inefficiencies, which include nonoptimal runtimes, excessive energy use, and limits to scalability, are a serious problem that can result in an inability to apply computing to solve the world's most important problems. Beyond the complexity and vast diversity of modern computing platforms and applications, a number of factors make improving general purpose efficiency challenging, including the requirement that multiple levels of the computer system stack be examined, that legacy hardware devices and software may stand in the way of achieving efficiency, and the need to balance efficiency with reusability, programmability, security, and other goals.

This dissertation presents five case studies, each demonstrating different ways in which the measurement of emerging systems can provide actionable advice to help keep general purpose computing efficient. The first of the five case studies is Parallel Block Vectors, a new profiling method for understanding parallel programs with a fine-grained, code-centric perspective aids in both future hardware design and in optimizing software to map better to existing hardware. Second is a project that defines a new way of measuring application interference on a datacenter's worth of chip-multiprocessors, leading to improved scheduling where applications can more effectively utilize available hardware resources. Next is a project that uses the GT-Pin tool to define a method for accelerating the simulation of GPGPUs, ultimately allowing for the development of future hardware with fewer inefficiencies. The fourth project is an experimental energy survey that compares and combines the

latest energy efficiency solutions at different levels of the stack to properly evaluate the state of the art and to find paths forward for future energy efficiency research. The final project presented is NRG-Loops, a language extension that allows programs to measure and intelligently adapt their own power and energy use.

# Table of Contents

| Li | st of | Figures                                                      | iv |

|----|-------|--------------------------------------------------------------|----|

| Li | st of | Tables                                                       | xi |

| 1  | Intr  | roduction                                                    | 1  |

|    | 1.1   | Computing Diversity                                          | 1  |

|    | 1.2   | Hardware-Software Mismatches Cause Efficiency Problems       | 3  |

|    | 1.3   | Why Efficiency is (Still) Important                          | 4  |

|    | 1.4   | Considerations Besides Efficiency                            | 5  |

|    | 1.5   | Measurement's Role in Improving Efficiency                   | 7  |

|    | 1.6   | Summary of Contributions                                     | 8  |

|    | 1.7   | Dissertation Outline                                         | 9  |

| 2  | Bac   | kground: Measuring the Intersection of Hardware and Software | 11 |

|    | 2.1   | Computer Systems                                             | 11 |

|    | 2.2   | An Overview of Computing Analyses                            | 16 |

|    | 2.3   | Dynamic Performance Analyses                                 | 18 |

| 3  | Par   | allel Block Vectors                                          | 23 |

|    | 3.1   | Introduction                                                 | 24 |

|    | 3.2   | Parallel Block Vector Profiles                               | 26 |

|    | 3.3   | Harmony: Efficient Collection of PBVs                        | 30 |

|    | 3.4   | Architectural Design Applications of PBVs                    | 35 |

|    | 3.5   | Pinpointing Software Performance Issues with PBVs            | 43 |

|   | 3.6  | Related Work                                                 | 51  |

|---|------|--------------------------------------------------------------|-----|

|   | 3.7  | Limitations and Future Work                                  | 52  |

|   | 3.8  | Discussion                                                   | 54  |

| 4 | Dat  | acenter-Wide Application Interference                        | 56  |

|   | 4.1  | Introduction                                                 | 57  |

|   | 4.2  | Complexities of Interference in a Datacenter                 | 58  |

|   | 4.3  | A Methodology for Measuring Interference in Live Datacenters | 64  |

|   | 4.4  | Applying the Measurement Methodology                         | 69  |

|   | 4.5  | Performance Opportunities                                    | 75  |

|   | 4.6  | Related Work                                                 | 78  |

|   | 4.7  | Limitations and Future Work                                  | 80  |

|   | 4.8  | Discussion                                                   | 81  |

| 5 | Fast | t Computational GPGPU Design                                 | 83  |

|   | 5.1  | Introduction                                                 | 84  |

|   | 5.2  | Background                                                   | 86  |

|   | 5.3  | Tracing GPU Programs with GT-Pin                             | 89  |

|   | 5.4  | A Study of Large OpenCL Applications                         | 92  |

|   | 5.5  | Selecting GPU Simulation Subsets                             | 96  |

|   | 5.6  | Related Work                                                 | 106 |

|   | 5.7  | Limitations and Future Work                                  | 108 |

|   | 5.8  | Discussion                                                   | 109 |

| 6 | Ene  | ergy Efficiency Across the Stack                             | 110 |

|   | 6.1  | Introduction                                                 | 111 |

|   | 6.2  | Background on Energy Management                              | 114 |

|   | 6.3  | Experimental Design and Methodology                          | 116 |

|   | 6.4  | System-Level Results                                         | 121 |

|   | 6.5  | Application-Level Energy Management                          | 132 |

|   | 6.6  | Related Work                                                 | 130 |

|           | 6.7                  | Limitations and Future Work | 140 |

|-----------|----------------------|-----------------------------|-----|

|           | 6.8                  | Discussion                  | 140 |

| 7         | NR                   | G-Loops                     | 142 |

|           | 7.1                  | Introduction                | 142 |

|           | 7.2                  | NRG-Loops                   | 147 |

|           | 7.3                  | NRG-RAPL                    | 150 |

|           | 7.4                  | Case Studies                | 154 |

|           | 7.5                  | Related Work                | 163 |

|           | 7.6                  | Limitations and Future Work | 164 |

|           | 7.7                  | Discussion                  | 165 |

| 8         | Cor                  | nclusions                   | 166 |

|           | 8.1                  | Summary of Findings         | 166 |

|           | 8.2                  | Looking Forward             | 168 |

|           |                      |                             |     |

| Bi        | iblio                | graphy                      | 171 |

| ${f A}_1$ | ppendix Acronyms 204 |                             |     |

# List of Figures

| 3.1 | Parallel block vector for matrix multiplication. For each basic block in an            |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | application, top, the profile, bottom, indicates the block execution frequency at each |    |

|     | possible thread count (i.e., degree of parallelism)                                    | 28 |

| 3.2 | Harmony instrumentation points. Profiler action is taken upon various runtime          |    |

|     | events. Careful engineering offloads expensive work to the least frequent events, in   |    |

|     | particular program start and finish which do not overlap with the execution of         |    |

|     | the program itself. This results in minimal profiling work at the most frequent        |    |

|     | events (i.e., basic block executions), reducing the profiling overhead and minimizing  |    |

|     | perturbation                                                                           | 29 |

| 3.3 | Direct instrumentation example. Each basic block is augmented to record its            |    |

|     | execution at the current degree of parallelism. The additional three instruction use   |    |

|     | only one register and do not induce any register spills                                | 32 |

| 3.4 | Thread library wrapper example. Here the instrumentation decrements and                |    |

|     | increments the effective thread count upon upon entry to and exit from of a blocking   |    |

|     | call respectively                                                                      | 32 |

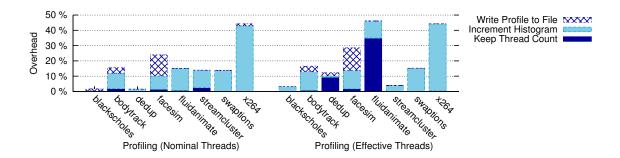

| 3.5 | Low overhead of instrumentation. Program slowdown due to profile collection            |    |

|     | ranges from $2\%$ to $44\%$ with an average overhead of $18\%$                         | 34 |

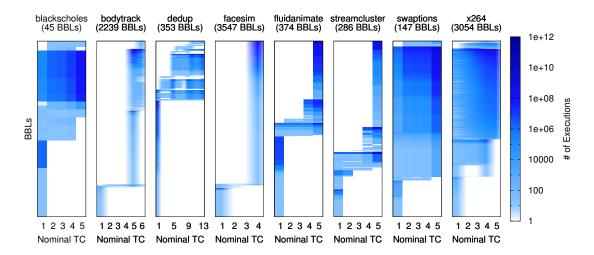

| 3.6 | Parallel block vectors for Parsec. These heatmaps are a visualization of the           |    |

|     | profiles produced by Harmony. For the given application, they show the number of       |    |

|     | times (shading) each static block (row) was executed at each degree of parallelism     |    |

|     | (column)                                                                               | 36 |

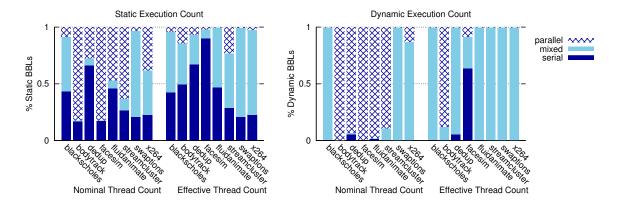

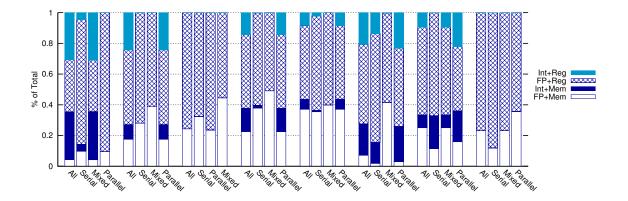

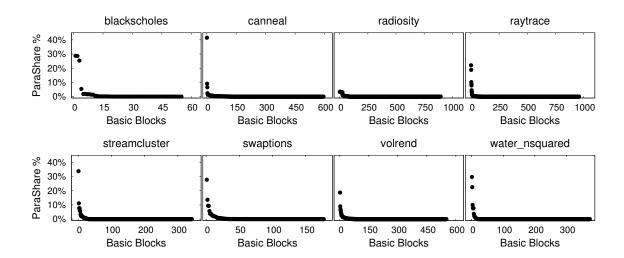

| 3.7  | Classifying basic blocks by parallelism. These graphs show the percentage of              |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | blocks which execute only serially (serial), blocks which execute both serially and       |    |

|      | in parallel (mixed), and blocks which only execute in parallel (parallel) for each        |    |

|      | application, for both nominal and effective thread counting, and for both static and      |    |

|      | dynamic block executions                                                                  | 36 |

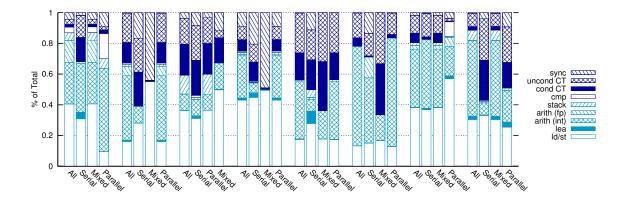

| 3.8  | Opcode mix by class. Instruction mixes for the entire program compared with the           |    |

|      | mixes for each basic block class (serial, parallel, and mixed). In all applications, the  |    |

|      | instruction mixes for both purely serial and purely parallel blocks differ significantly  |    |

|      | from whole program mixes                                                                  | 37 |

| 3.9  | Memory interaction by class. The proportion of memory operations for serial               |    |

|      | and parallel basic blocks differ from the proportion in the program as a whole. $$ . $$ . | 39 |

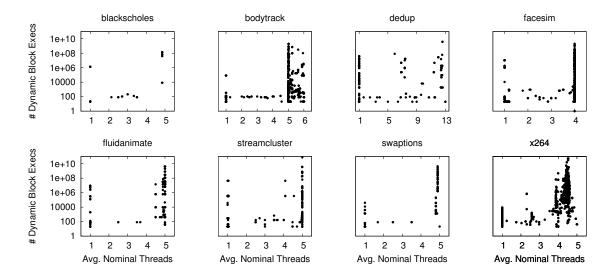

| 3.10 | Hottest blocks are not always the most parallel blocks. Each static basic                 |    |

|      | block's weighted average nominal thread count was calculated and then plotted             |    |

|      | against its total number of dynamic executions. The graphs show that the hottest          |    |

|      | blocks are primarily split between those that execute only serial and those that          |    |

|      | execute near the max degree of parallelism                                                | 41 |

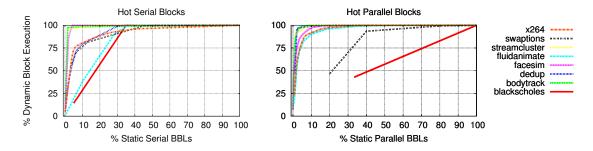

| 3.11 | Few basic blocks represent large portions of serial and parallel runtime.                 |    |

|      | For basic blocks that were determined by parallel block vectors to always execute         |    |

|      | serially (left) or in parallel (right), percentages of runtime execution are attributed   |    |

|      | to static basic blocks. For most applications, a small number of blocks represents a      |    |

|      | large fraction of the total runtime                                                       | 42 |

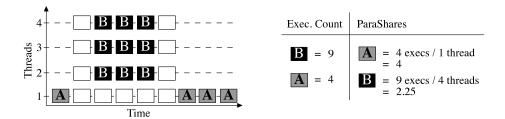

| 3.12 | ParaShares rank basic blocks to identify those with the greatest impact                   |    |

|      | on parallel execution, weighting each block by the runtime parallelism exhibited          |    |

|      | by the application each time the block was executed                                       | 43 |

| 3.13 | ParaShare rankings identify important blocks to target for multithreaded                  |    |

|      | performance optimizations. These graphs show the ParaShare percentages (or-               |    |

|      | dered from greatest to least share) of all the basic blocks in eight benchmark appli-     |    |

|      | cations                                                                                   | 45 |

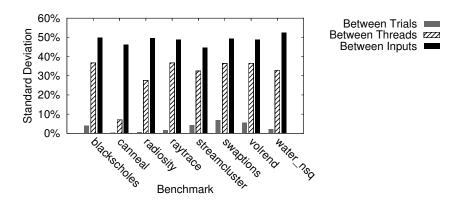

| 3.14 | Robustness of the metrics. Runtimes and basic block execution counts can                   |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | change across program trials, but the differences are small relative to differences in     |    |

|      | ParaShares collected across varying thread counts or input sizes                           | 48 |

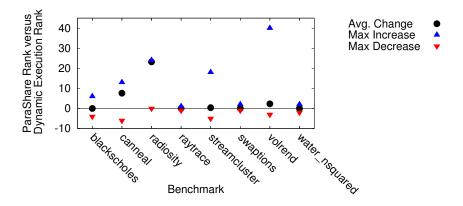

| 3.15 | ParaShares versus unweighted rankings in top 20 blocks. ParaShares do                      |    |

|      | not always highlight new 'hot' blocks, but can often significantly impact the relative     |    |

|      | importance of a block versus dynamic instruction count rankings $not \ weighted \ by$      |    |

|      | parallelism                                                                                | 49 |

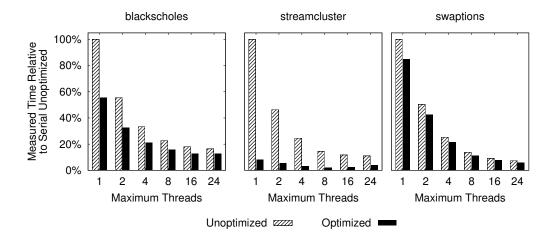

| 3.16 | ParaShares pinpoint inefficiencies that lead to significant opportunities                  |    |

|      | for optimization. With the extremely targeted profiling provided by ParaShares,            |    |

|      | we were able to improve benchmark performance by up to $92\%$ through source code          |    |

|      | changes less than 10 lines long                                                            | 50 |

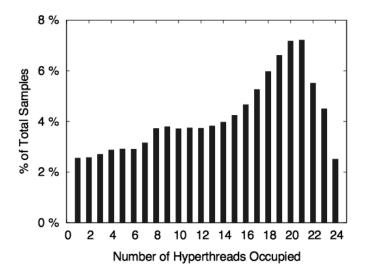

| 4.1  | Datacenter machines are filled with applications. Profiling 1000 12-core, 24               |    |

|      | hyperthread Google servers running production workloads, we found the average              |    |

|      | machine had more than 14 of the 24 hyperthreads in use. These results reveal the           |    |

|      | extent of multi-way interference, which is largely un-handled by existing interference     |    |

|      | management techniques                                                                      | 60 |

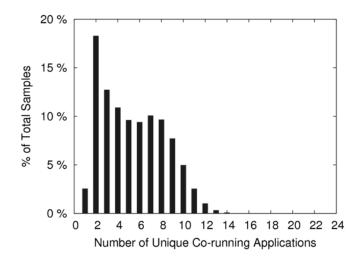

| 4.2  | Datacenter servers have diverse application mixes. Google server profiling                 |    |

|      | reveals that most machines run five or more unique applications at once, and some-         |    |

|      | times as many as 20. Many past works consider only two applications running                |    |

|      | together at a time, a scenario present only 20% of the time in to this data                | 61 |

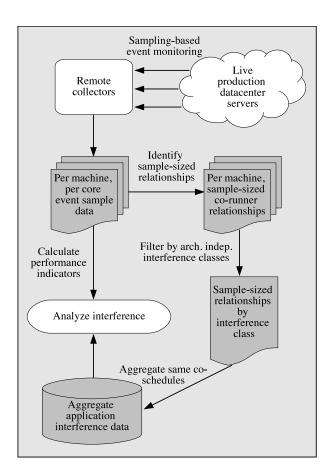

| 4.3  | A methodology for measuring application interference on live production                    |    |

|      | servers is described in Section 4.3.                                                       | 65 |

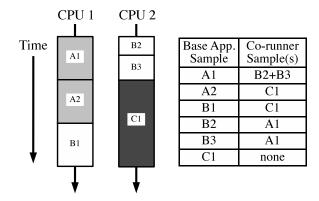

| 4.4  | Sample sized co-runners. Timelines of two CPUs on the same machine are                     |    |

|      | shown to the left. Each segment represents a performance sample (e.g., $2$ million         |    |

|      | instructions) from an application. For example, $A1$ is the first sample of application    |    |

|      | A. The table to the right shows the co-runner samples for each base application            |    |

|      | sample. Application $A1$ has two co-runners because two consecutive samples of             |    |

|      | application $B$ run for its duration. In this contrived example, sample $C1$ is especially |    |

|      | long to illustrate the uncommon case of a sample having no co-runners.                     | 67 |

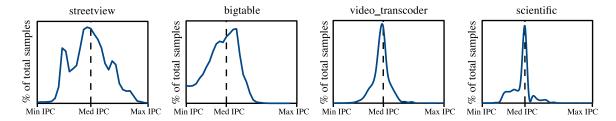

| 4.5 | Median IPC is a good performance indicator for the Google data col-                    |        |

|-----|----------------------------------------------------------------------------------------|--------|

|     | lected. Each graph shows the performance variations of the specified application       |        |

|     | when scheduled with eight of their most common co-runners. The overall median          |        |

|     | IPCs for each base application correspond well to their performance curves             | 71     |

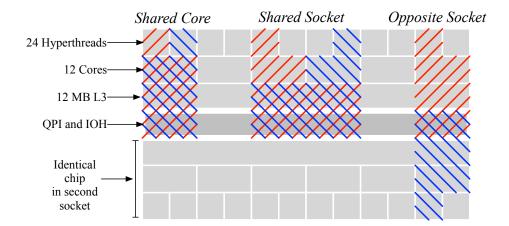

| 4.6 | Westmere Interference Classes. The profiled Intel Westmeres are dual-socket            |        |

|     | machines, supporting $12$ hyperthreads per socket. Interference relationships are par- |        |

|     | titioned into three classes as depicted here: shared core, shared socket, and opposite |        |

|     | socket                                                                                 | 72     |

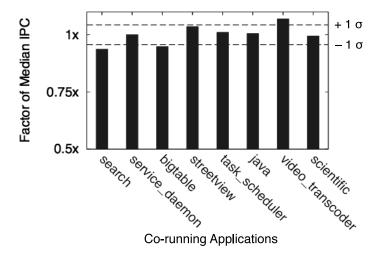

| 4.7 | Streetview's performance variations across co–runners. Bars represent streets          | ⁄iew's |

|     | normalized median performance when co–located with eight common co-runner ap-          |        |

|     | plications. Dashed horizontal lines show overall variance of all measured streetview   |        |

|     | samples                                                                                | 74     |

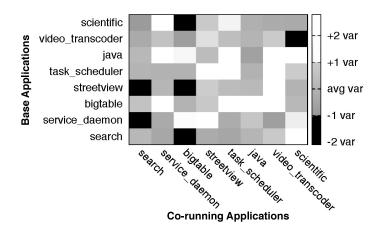

| 4.8 | Beyond noisy interferers in the Google data. Shared core co-runner applica-            |        |

|     | tions along the x-axis affect the performance of base applications along the y-axis.   |        |

|     | White boxes show co-runners that positively interfere beyond the average variance      |        |

|     | with base applications, while black boxes show co-runners that negatively interfere    |        |

|     | beyond the average variance                                                            | 77     |

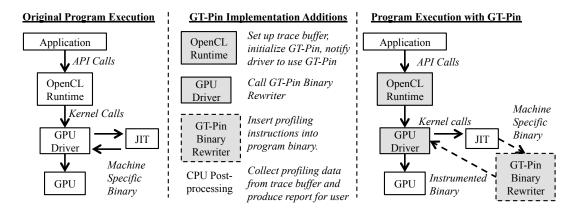

| 5.1 | The GT-Pin Implementation makes multiple changes to the OpenCL runtime                 |        |

|     | and the GPU driver, and adds a new GT-Pin binary re-writer and a CPU post-             |        |

|     | processor. From a user perspective, however, the tool is easy to use and non-          |        |

|     | intrusive, with low overheads, no perturbation, and no source code modifications       |        |

|     | or recompilation required                                                              | 86     |

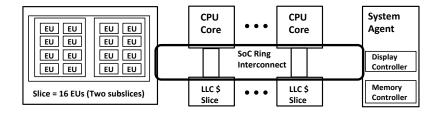

| 5.2 | The Processor Architecture of our test system, which has an Intel Core i7-3770         |        |

|     | CPU and HD 4000 GPU                                                                    | 92     |

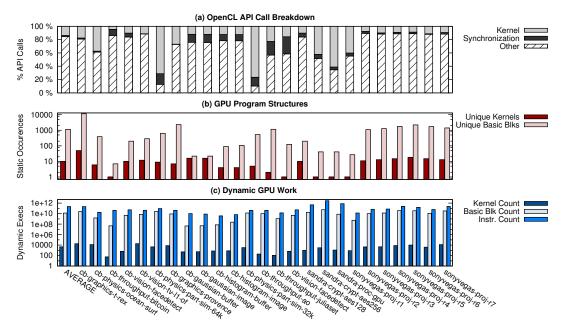

| 5.3 | Benchmark Characterization. OpenCL call breakdowns (% synchronization,                 |        |

|     | kernel, and other API calls) were measured on the CPU $host$ using CoFluent; pro-      |        |

|     | gram structure counts (unique kernels and static basic blocks) and dynamic work        |        |

|     | counts (executions of kernels, basic blocks, and instructions) were measured on the    |        |

|     | GPU device using GT-Pin                                                                | 93     |

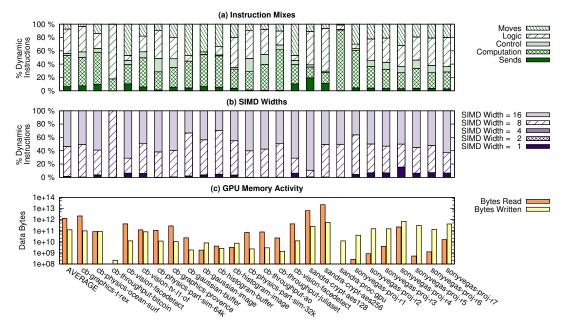

| 5.4 | <b>GPU Work.</b> GT-Pin can also measure GPU instruction mixes, the SIMD widths              |     |

|-----|----------------------------------------------------------------------------------------------|-----|

|     | of instructions (i.e., how data-parallel an application is), and the cumulative number       |     |

|     | of bytes read and written to memory across hardware threads                                  | 95  |

| 5.5 | Feature and Division Space Exploration. Applications vary in terms of which                  |     |

|     | of 10 different feature vector choices and 3 interval division sizes are best able to select |     |

|     | subsets that match full program performance. Also, the most accurate selection               |     |

|     | configurations are not always the best at reducing the number of instructions to             |     |

|     | simulate                                                                                     | 100 |

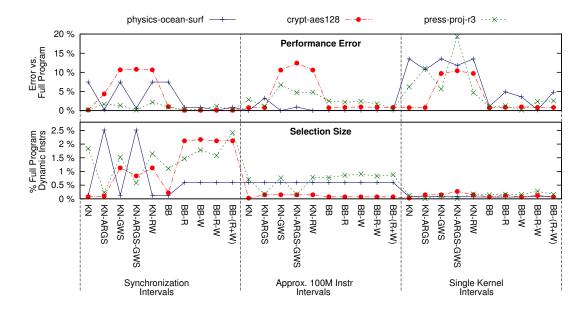

| 5.6 | Optimizing Selection to Minimize Error results in individual applications                    |     |

|     | choosing different interval/feature vector configurations. Across applications, errors       |     |

|     | average 0.3% and simulation speedups average 35X, ranging from 6X to 6509X                   | 102 |

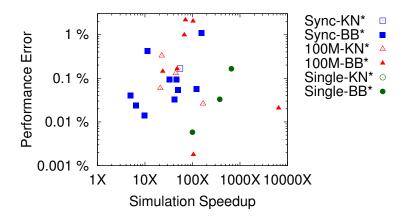

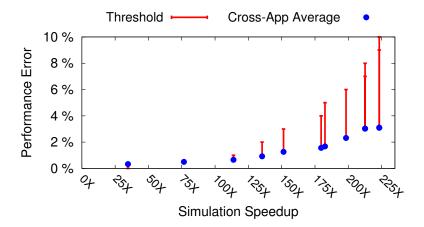

| 5.7 | Optimizing for Both Error and Selection Size means choosing the per appli-                   |     |

|     | cation configuration that has the smallest selection size with an error below a given        |     |

|     | $\it threshold.$ For example, with an error threshold of 3%, simulation speedups average     |     |

|     | 223X                                                                                         | 103 |

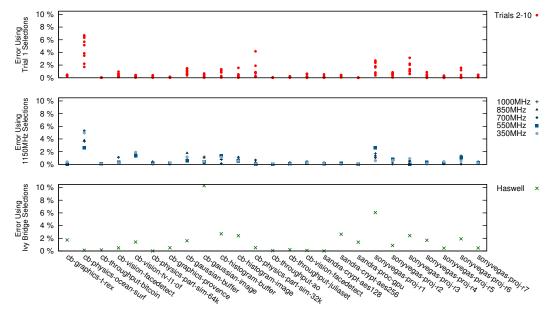

| 5.8 | Timed Validation. One trial's selection are still accurate across trials, frequencies,       |     |

|     | and architecture generations                                                                 | 104 |

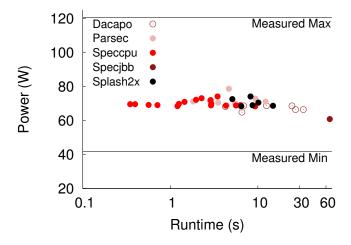

| 6.1 | Baseline Performance and Power. The 41 benchmark applications exhibited                      |     |

|     | more variation in runtime than in power when run at our $baseline$ configuration of          |     |

|     | a single thread utilizing a processor set to maximum frequency, and with compil-             |     |

|     | er/JVM optimizations and processor idle states all enabled                                   | 119 |

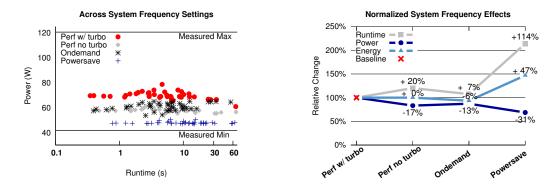

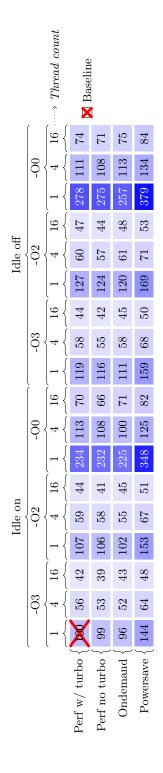

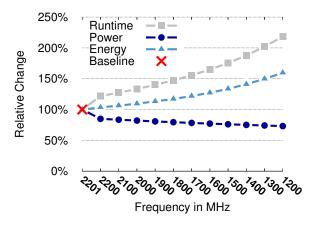

| 6.2 | System frequency tuning algorithms, such as $ondemand$ save at most $6\%$ of                 |     |

|     | energy across applications versus the system baseline of maximum frequency with              |     |

|     | Turbo Boost enabled ( $perf\ w/\ turbo$ ). Other frequency tuning options include dis-       |     |

|     | abling Turbo Boost for decreased runtime but no net energy savings $(perf\ no\ turbo)$       |     |

|     | or a powersave option that saves an average of $31\%$ of the power, but with great           |     |

|     | costs to runtime (powersave)                                                                 | 120 |

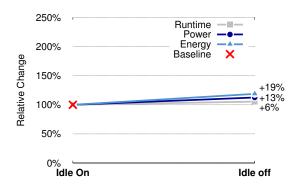

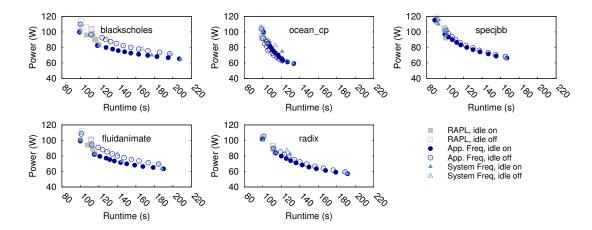

| 6.3 | <b>Processor idle states</b> enable 19% energy savings relative to the mode that prevents    |     |

|     | cores from entering these power-saving sleep modes                                           | 194 |

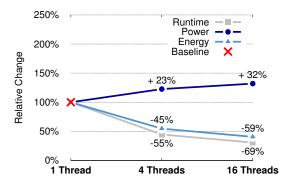

| 6.4  | Parallelization increases energy savings for all applications tested. For our 12         |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | core, 24 hyperthread server, running 16 application threads consumed just $45\%$ of      |     |

|      | the energy of the serial execution                                                       | 124 |

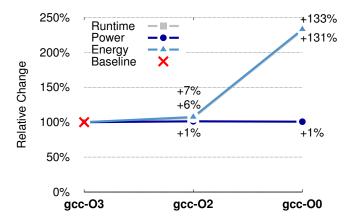

| 6.5  | Standard compiler optimization sets save energy, but largely through runtime             |     |

|      | reductions not power reductions. Applications without optimization take $133\%$ more     |     |

|      | energy and 131% more time than fully optimized applications                              | 127 |

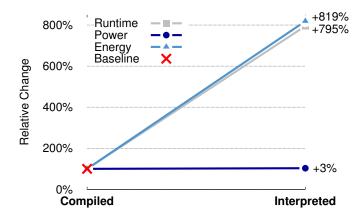

| 6.6  | Java compilation saves substantial energy versus interpreted code, which consumes        |     |

|      | 8X the energy, but again these savings are due to runtime, not power                     | 127 |

| 6.7  | Energy effects of combining multiple configurations. This table shows cross-             |     |

|      | level energy interactions of the five energy configurations discussed so far, as a per-  |     |

|      | centage of the baseline, (i.e., baseline = $100\%$ ). Note that the matrix includes data |     |

|      | from only the parallel, native benchmark suites: Parsec, Splash2x                        | 129 |

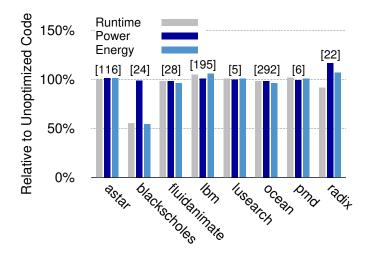

| 6.8  | Source code tuning methods from prior embedded systems research were not very            |     |

|      | effective energy savers for for our complex and already well-optimized benchmarks        |     |

|      | running on servers                                                                       | 133 |

| 6.9  | Application-specific frequency tuning, or running an application at a single             |     |

|      | discrete frequency, allows power-performance tradeoffs to be flexibly manipulated.       | 135 |

| 6.10 | RAPL power caps, which limit the amount of power a part of the chip is allowed to        |     |

|      | consume over a given time window, yield a more limited power-performance tradeoff        |     |

|      | range                                                                                    | 135 |

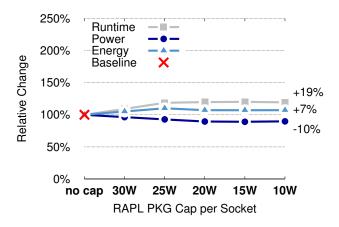

| 6.11 | Application-specific strategies versus system level strategies for frequency             |     |

|      | tuning. RAPL caps, application-specific frequency tuning, and system frequency           |     |

|      | governors could not be combined with each other, so we compared their power              |     |

|      | performance effects instead. All three could be combined with idle states, however,      |     |

|      | which when enabled saved energy across all of the different frequency configurations.    | 137 |

| 7.1  | The NRG-Loops Syntax                                                                     | 146 |

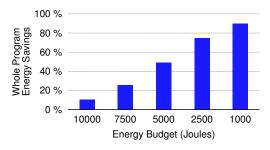

| 7.2  | An NRG Perforate Loop augments bodytrack to (left) drop different specified              |     |

|      | percentages of frames to save energy, or (right) maximize quality without exceeding      |     |

|      | various allocated energy budgets.                                                        | 155 |

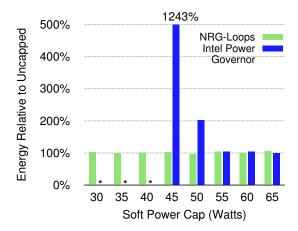

| 7.3 | NRG Adapt Loops can meet a preset power budget by adjusting application-                  |       |

|-----|-------------------------------------------------------------------------------------------|-------|

|     | internal thread count, analogously to the Intel Power Governor tuning DVFS. For           |       |

|     | the string matching application shown, NRG-Loops can set a broader range of caps          |       |

|     | (Power Governor caps could not be used below 45 Watts), and required up to $12\mathrm{X}$ |       |

|     | less energy to enforce them                                                               | 158   |

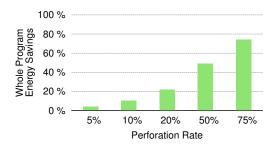

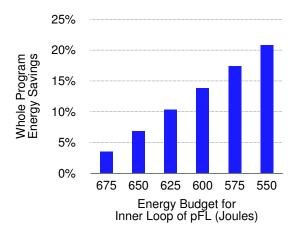

| 7.4 | NRG Truncate Loops estimate a mathematical clustering algorithm within streamcle          | uster |

|     | to save various amounts of whole program energy depending on the degree of ap-            |       |

|     | proximation                                                                               | 160   |

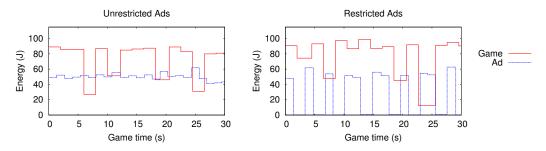

| 7.5 | A minesweeper game uses NRG-Adapt Loops to prioritize game power                          |       |

|     | over third-party advertisements. Run unchecked, the ads sometimes consumes                |       |

|     | more power than the game, but NRG-Loops can force the ads to occasionally pause,          |       |

|     | decreasing net game+ad energy                                                             | 160   |

# List of Tables

| 3.1 | A case for fine-grained identification of performance inefficiencies. To          |     |

|-----|-----------------------------------------------------------------------------------|-----|

|     | examine the functions that take up $90\%$ of the parallel execution, a programmer |     |

|     | must examine an average of 338.5 lines per program. To examine the basic blocks   |     |

|     | that consumed the same amount, they would need to look at an average of only $50$ |     |

|     | lines per program                                                                 | 47  |

| 4.1 | Profiling and Collection Statistics                                               | 70  |

| 5.1 | Benchmarks used in this study                                                     | 93  |

| 5.2 | The Program Interval Space explores three different ways of dividing GPU pro-     |     |

|     | gram traces into intervals                                                        | 98  |

| 5.3 | The Program Feature Space explores ten feature vectors, with the above keys       |     |

|     | and values that count the dynamic execution count of the respective key           | 98  |

| 6.1 | Experimental benchmarks, chosen to represent a range of languages, program-       |     |

|     | ming styles, and application domains                                              | 116 |

| 6.2 | A summary of the energy efficiency techniques explored in this experi-            |     |

|     | mental survey.                                                                    | 117 |

# Acknowledgments

I owe thanks to many people who have supported and enriched my experiences as a Ph.D. student. First, I want to thank my advisor Martha Kim for helping me to generate and refine research ideas, for meticulously reading paper drafts, for all of the long hours she spent with me leading up to deadlines, and for helping to improve my writing, presentation, and research skills. Martha was a great research partner!

Many professors at Columbia have given me invaluable instruction, advice, and feedback on my work. In particular, I would like to thank Al Aho, Simha Sethumadhavan, and Luca Carloni, who gave me the most feedback on my work and are all (not so coincidentally) serving on my thesis committee. I also want to thank Adrian Sampson for serving on my thesis committee, and a number of wonderful internship mentors from whom I received excellent guidance during my Ph.D., including Tipp, Rick, Nenad, C.K., Harish, Sunpyo, Matthai, Karin, and Gagan. Several of these people are also co-authors on the work presented in this dissertation. I had only one student co-author, Kui, who deserves my acknowledgement and thanks for his help with the PBV work. I was very fortunate to receive financial support from a number of companies, government agencies, professional groups, and individuals, and I am grateful to all of them as well. I also received wonderful administrative assistance from our department staff, in particular from Jessica, Daisy, Elias, and Cindy.

Next, I want to thank the students in the CSL and arch-reading groups who attended my talks and gave me project feedback. I especially want to thank Lisa, John, Robert, Kanad, Joel, Andrea, and Emilio, some of my fellow "fish bowl" inhabitants who crossed the line from colleagues to friends. I am also thankful to all of the WICS board ladies for helping me create lots of great memories as we planned our events, especially Arthi, Erica, and Heba with whom I spent the most time over the years, and our faculty advisor Julia. I have been lucky to make additional supportive friends at Columbia, including Jon, Eva,

Bingyi, Anna, Sasha, Cinar, and my "study group" — Sebastian, Paul, and Barbara — who helped me through the early years of my Ph.D.

My thanks as well to my three brothers and my parents for their support and encouragement, and in particular to my father for inspiring me to study computer science (and pursue a Ph.D.) in the first place. Of course, my biggest thanks must go to my amazing husband, Anju, who has been the most important person in my life since I met him nearly a decade ago.

## Chapter 1

# Introduction

A proliferation of computing uses, users, and producers in recent years has resulted in a diverse range of computing technologies at all levels of the computer system stack. While exciting for the computing industry, this ubiquity-induced complexity of computer systems has made it difficult to effectively match the requests of arbitrary software applications to general purpose hardware and operating systems. This dissertation will demonstrate the presence of resultant hardware-software mismatches and show that they cause runtime or energy efficiency losses. It will then show that new measurement technologies can be effective in maintaining reasonable efficiency in current systems and in achieving better efficiency in future systems.

The remainder of this introduction explains the diversity and complexity within the modern system stack, explains how efficiency issues arise in general purpose computing, and discusses the importance of efficiency as well as other system design considerations. Following this discussion is a brief overview of how measurement and analysis technologies can identify efficiency issues and improve them, a summary of the contributions of this dissertation, and an outline for the remainder of the document.

#### 1.1 Computing Diversity

Computing has entered a new era of ubiquity. Over 3 billion people now purchase and use over 2 billion personal computers, tablets, and smart phones per year [67, 163]. There

are 5 billion "things" (i.e., devices such as cars or thermostats) currently connected to the *Internet of Things (IoT)* [68], and there are over 6.5 million technology workers in the United States alone [74]. The number of computer science researchers is also growing — in 2014 the United States produced around 1800 computer science Ph.D.s per year as opposed to 1000 per year in the 1990s and 200 per year in the late 1970s and early 1980s [237, 269].

In keeping pace with the expanding number of uses, users, and producers, computing technology has become increasingly specialized and diverse. As recently as the late 1980s, there were primarily two classes of computers, supercomputers and PCs, with a handful of simple embedded devices, such as pocket calculators. Today, there are many categories of computers. There are massive datacenters hosting cloud computing services and supplying storage space to record as much as possible of a "big-data" obsessed world. For personal computing, there are smartphones and a variety of of desktop servers, laptops, tablets, and "2-in-1's". In addition to phones, almost every form of electronics has become "smart" with the help of embedded computers, from watches, fitness monitors, and sports equipment to televisions, thermostats, and refrigerators, to cars, trains, and airplanes, to factory equipment and computerized "drones". Beyond this, today's computers live not just in electronics, but also on and in plants and animals, from GPS microchips, to pacemakers and cochlear implants, to nanotechnology.

To serve the myriad users and uses, and because so many different people are contributing to the development of modern computing technologies, diversity has percolated to nearly all of the components and layers of the computer system stack. On the architectural side, processing logic could be a basic general purpose CPU, a specialized processor such as a domain specific processor or micro-controller, and it could be programmable logic (i.e., FPGAs), or a fixed-function chip (i.e., ASICs). Beyond these processing categories, there are many different configuration options such as whether processing cores are inorder or out-of-order, whether multiprocessing is used (either in the form of simultaneous-multiprocessing [SMT] or chip-multiprocessing [CMP]), and whether a single chip contains multiple heterogeneous processors. Memory technologies are equally diverse and also frequently heterogeneous, utilizing SRAM, DRAM, FLASH and likely soon a variety of other types of Non-Volatile (NV)RAM. Memory and processors may be 2.5- or 3-D stacked tech-

nologies, or utilize near-data processing (NDP), where processing units are moved adjacent to or into data storage [13]. Languages are diverse as well, and may be objected oriented, compiled or interpreted, domain specific, dynamic or static. As with hardware, it is common to see heterogeneous software, with one application utilizing multiple languages. The number of higher-level languages has grown from about 200 in 1972 to 8500 in the present day, a count that exceeds that of known human languages [79]. Handling the translation between all of these languages and platforms has required that compilers become complex too; and operating systems face a similar challenge in providing a secure and simple interface to users on the diverse range of devices. For example, the Android operating system must be made to work on roughly 4000 distinct hardware platforms [248].

Dealing with computing diversity presents at least one notable problem: it has become difficult to effectively map arbitrary software requests to general purpose hardware resources. When hardware–software mappings are nonoptimal, the result is *inefficiency*, or the overuse of runtime, power, or both (i.e., energy).

# 1.2 Hardware-Software Mismatches Cause Efficiency Problems

The hardware-software matching problem is an issue where either 1) more resources are delivered by hardware than are needed by software, 2) more resources are requested by software than can be delivered by hardware, or 3) where both 1) and 2) occur simultaneously.

Though not always the case, the goals of programming languages and computer architecture are frequently at odds. At the kernel of each problem we want to compute, there is some hard-to-define amount of necessary computational resources. Translating from human intent to something a machine can understand — i.e., writing a computer program — sometimes results in resource requests beyond the essential. Similarly, making hardware delivery too potent sometimes means more resources are delivered than strictly needed. It is possible for software and hardware to over— or under—provision simultaneously: for example, a program might use a higher—precision data type (e.g., a 64-bit float) when a lower—precision data type would suffice (e.g., an 8-bit float), and hardware might supply

multiple processors when only a single processor is needed by the program. This (potentially dual) mismatch in requested resources and delivered resources can result in wasted execution cycles, wasted power, or both. Evidence of efficiency losses might include cache misses, pipeline stalls, processors that are idle but still drawing power, TLB misses, excess page swapping, task starvation, or tail latencies.

In a perfect world, computer programmers and their programs would make whatever requests they desire and hardware would deliver as many resources as it could within size, thermal, and cost constraints. Then, the compiler, the operating system, and middleware would make adjustments between the two to eliminate mismatches. Unfortunately, this is a job that is only partially solved by today's compilers and operating systems, and it is a job that is becoming increasingly difficult to automate as hardware and software complexity increase. In order to avoid unnecessary compromises to programmability and hardware design, and to reduce resource waste, we need to improve our understanding of the efficiency between hardware and software, and make coordinated efforts between applications, compilers, operating systems, and hardware to reconcile mismatched resource requests and delivery to the greatest extent possible.

#### 1.3 Why Efficiency is (Still) Important

Over time, advances in computer architecture have dramatically increased computational efficiency. The 1946 Eniac computer drew 150,000 Watts of power to deliver 500 floating point operations per second (FLOPS), while modern smartphones consume around a single Watt to deliver a peak performance of billions of FLOPS [6, 197]. In fact, a single modern smartphone has more computational capabilities than the computers used to get Apollo 11 to the moon [205]. Today's fastest supercomputer, the Tianhe-2, has a processing rate of 33.86 petaFLOPS — that's nearly 34 million-billions of operations per second [53].

With such commendable advances, the need for even more runtime and power efficiency might not be immediately apparent, but there are a number of important reasons to care about continued efficiency advances. Some of these are:

• To reduce computing's ecological footprint. The IT-sector is already responsible

for around 2% of global carbon emissions, and with the expected growth in computing use and users, this number could soon be a lot higher if energy efficiency improvements are not made [44]. On a more local level, the energy costs of technology could become a barrier for individual users if not kept in check — today, an iPhone already has a higher monthly electric bill than a standard home refrigerator [253].

- To solve new problems or put computers in new places. Greater efficiency is required to reach the "exascale" era of computing (where computers can compute a billion-billion operations per second), which promises technological advances such as fully replicating the brain and providing global climate solutions such as controlled fusion. On the other side of computing scale, with greater efficiency, better miniaturization could be achieved and an entirely different set of important problems could be solved. For example, scientists are working on computers so small they can be swallowed in a pill and will transmit medical readings to doctors [177].

- To make existing computing solutions more cost effective or accessible. Efficiency is not just important for pushing the limits of the kinds of problems that computers can solve. It is also import for increasing the availability or decreasing the cost of existing computation. For example, partly due to increased computational efficiency, biotechnicians were able to reduce genome sequencing costs from \$10 million in 2007 to under \$1000 in 2011 [78, 180]. As another example, image recognition (i.e., computer vision) is performed today on powerful servers in the "cloud", but with better efficiency, image recognition could be performed on mobile devices to improve privacy and latency for users, and to decrease costs for service providers.

#### 1.4 Considerations Besides Efficiency

The systems today that are closest to optimially efficient are called application-specific integrated circuits, or ASICs. ASICs are hrdware customized to specific, well-tuned applications to minimize inefficiencies, nearly eliminating undesirable events such as pipeline stalls and cache misses, and saving orders of magnitude of energy. Anton is one example of an ASIC that targets molecular biology applications, improving runtime performance by

nearly two orders of magnitude and considerably reducing power versus general-purpose computing solutions [209]. For many applications, however, complete specialization is not a panacea, and is instead impractical, undesirable, or both. Efficiency in computer system design must be balanced with a multitude of competing goals, such as:

- **Security** at both the software and hardware level, which can sometimes compete with efficiency by adding extra circuity or code to ensure a system is protected.

- **Programmability** or the ability to write programs quickly and without regard to efficiency, perhaps in languages that tend to request more resources than necessary. For example, object oriented programming which helps developers reason about program structure and arguably write more readable code has been shown to unnecessarily waste energy [20].

- Reusability of software functions and objects, and of instruction set architectures and functional units in hardware. Reusability saves human resources, such as developer time, but can be at odds with computational efficiency. For example, programs may link an entire statistics library when they only need one of its functions.

- Accuracy and Verifiability; extra precision or additional functionality such as test cases are often employed to ensure error-less programs, and there is value in being able to prove that a program is correct in all circumstances (e.g., in all of the non-deterministic runs of a multithreaded program). Both of these goals typically require an efficiency tradeoff.

- Reasonable Area, Device Size, Durability and other similar hardware goals also

may require trading away computational efficiency.

- Cost. Many of the above are also associated with reduced expenses for computing producers or consumers. For example, buying one very computationally-powerful server is not typically as cost-effective as buying many wimpy servers at a lower price per unit. Similarly, while writing code in C++ and CUDA might provide the fastest execution time for an application, a company may find it cheaper to hire Python developers and pay for more machine time.

Another important and related issue is the presence of legacy code and devices. Often, it is prohibitively expensive for companies to replace obsolete devices, because efficiency is a second class goal to cost. Later in this dissertation, there are a couple of examples of the legacy effect. For example, in the study of application interference on Google servers (Chapter 4), we note that the search giant uses a wide variety of microarchitectural platforms. Also, we discuss a new trend in Chapter 5, where once specialized processors — Graphics Processing Units (GPUs) — have now been put to general purpose use because of their low price point and ubiquity.

#### 1.5 Measurement's Role in Improving Efficiency

The efficiency of contemporary and emerging computer systems can be improved with the guidance of performance analysis techniques and measurement methodologies. Given the delicate balancing act of honoring competing system design goals, rather than striving to completely eliminate inefficiencies, the aim should be to understand them in the context of other tradeoffs, and to reduce them only as appropriate. Additionally, we need to determine when it is necessary to optimize or specialize applications or hardware, versus when it is possible to reconcile the mismatches with system tools. New measurement methods and tools can help locate potential efficiency issues, and can evaluate the potential tradeoffs of solutions to reduce them. Measurement and program analysis are important for a number of reasons:

- To compare alternate solutions. Measurement helps us compare different solutions' efficiency, and can determine which microarchitecture, which algorithm, which language, or which optimization technique is best. For example, in Chapter 6, we experimentally compare different energy efficiency techniques that span the computer system stack.

- To account for real—time data. Efficiency is often dependent on real—time events, such as user inputs or battery-levels. Our measurement—based methodologies in Chapters 4 and 7 are able to account for both.

- To identify hotspots. It is common for efficiency issues to be localized to small parts of the software or hardware. Measurement—based techniques are well-suited for pinpointing such hotspots, especially when their poor efficiency is contributed by more than one layer of the system stack. We demonstrate this in Chapter 3.

- To test future designs. When possible, proactive efficiency solutions are better than retroactive efficiency solutions. Measurement technologies can help direct the way towards more efficient hardware-software co-designs, as is shown in Chapter 5.

To summarize, measurement techniques are effective for addressing efficiency issues in modern general purpose computer systems because they help us account for dynamic events, help us understand unpredictable interactions between system layers, and because they help us to be proactive in avoiding efficiency issues even before they occur.

#### 1.6 Summary of Contributions

As discussed above, the novel contributions of this dissertation support our thesis that measurement techniques that work at the intersection of hardware and software can improve the efficiency of contemporary and emerging general purpose computer systems. The contributions are divided into five case studies — one per chapter — that find inefficiencies within a variety of recent or emerging hardware and software paradigms. Most of this work has been previously written about in nine peer-reviewed publications and a technical report, each of which were primarily authored by the author of this dissertation [113–122].

The first contribution is *Parallel Block Vectors*, or PBVs, a new way of profiling program parallelism at very fine granularity. PBVs help identify opportunities to match future hardware to current software, or to optimize future software versions for current hardware. The second contribution is a new method of identifying minimal but representative regions within programs written for GPGPUs (general purpose graphics processing units). Finding these salient regions allows for the acceleration of cycle-accurate performance simulators, which in turn leads to GPUs with resource deliveries that are more adequately matched to software needs. The third contribution of this dissertation is a new method of profiling the interference between multiple applications in a datacenter that are forced to *co-locate* on

a single multicore for the sake of improving system efficiency. Unfortunately, co-location's attempt to ameliorate system throughput can sometimes negatively affect individual applications' latency. Our new profiling method looks for opportunities to co-locate applications that preserve both full system throughput and individual application latency.

The next contribution of this dissertation is a measurement-based language extension called NRG-Loops. NRG-Loops allow applications to react to power and energy measurements taken at runtime with on-the-fly adjustments to functionality, performance, and accuracy. Since the adjustments are conditionally enabled, NRG-Loops have the potential to allow a single piece of source code to match its resource requests to multiple types of underlying architectures, without significant effort on the part of the programmer. The final contribution is an experimental survey that quantifies the relative effectiveness of previously uncompared energy efficiency techniques across the system stack. The survey also combines different techniques to find whether their compound effects are negative or positive, and whether they are additive or synergistic.

#### 1.7 Dissertation Outline

The remainder of this dissertation is organized as follows:

- Chapter 2 provides background information on the terminology and components associated with computer systems, as well as on the measurement and analysis methods that existed prior to this dissertation.

- Chapter 3 presents the new Parallel Block Vector profiling tool for examining program parallelism from a fine-grained, code-centric perspective.

- Chapter 4 presents the new measurement method for quantifying (and mitigating) application interference on Datacenter CMPs.

- Chapter 5 presents a new method for identifying minimal but representative regions of programs in GPGPUs, with the aim of accelerating microarchitecture performance simulators.

- Chapter 6 presents an experimental survey that compares and combines energy efficiency solutions at different levels of the compute stack.

- Chapter 7 presents the new NRG-Loop syntax extension that allows programs to intelligently react to their own power and energy use.

- Chapter 8 summarizes the contributions of this work and suggests ideas for the community's future work.

- Appendix 8.2 defines acronyms that appear throughout this dissertation.

# Chapter 2

# Background: Measuring the Intersection of Hardware and Software

Analysis tools and measurement techniques for understanding the behaviors that arise at the intersection of computer software and computer hardware are an essential part of improving computer systems' efficiency. This chapter begins with a discussion of the terminology and components associated with computer systems in Section 2.1 to give readers context for the holistic, whole–system approach that we need to take to improve system efficiency. Next, Section 2.2 gives a high-level overview of the main types of computing analyses available today. There are many analysis methods one might use to study computer systems, but only some are relevant to this dissertation's goal of identifying and reducing system-wide inefficiencies; Section 2.3 explores the most relevant types of analyses in more depth.

#### 2.1 Computer Systems

When this dissertation refers to *computer systems*, it means all of the hardware and software technology that come together to form a computing device and its operations. Prior work is inconsistent in how it breaks down the layers in a computer system; we choose to divide the system into three coarse layers: *Hardware*, *System*, and *Application*. The

term platform is sometimes used in this and other works to encompass both the Hardware—and System—Layers, while the term software includes the System—and Application—Layers. The term stack or system stack is frequently used to describe an ordered set of the system layers, typically with the Hardware—Layer at the bottom of the stack, the System—Layer at the middle of the stack, and the Application—Layer at the top of the stack. Below is a description of the components or configuration options within each layer. As discussed in the introduction, computer systems are now vastly diverse, so the following list is not comprehensive, but it does cover all major characteristics of the computer systems explored later in this dissertation. By convention, layer components are denoted in **boldface**, while concepts and configuration options are italicized.

#### 2.1.1 Hardware-Layer

The Hardware–Layer houses all of the tangible, physical elements of the computer system. These include **power supplies** and **peripherals**, that allow external communication to the computer such as monitors and other types of displays, keyboards, microphones, and cameras. The layer also includes everything inside of a computer case, such as fans, I/O and other buses, batteries, and the motherboard. The motherboard holds circuitry that makes up the computer's microarchitecture, or particular implementation of an instruction set architecture (ISA)'s processor, including datapaths, execution units (EUs) such as arithmetic logic units (ALUs), floating point units (FPUs), and branch prediction units, as well as on-die memory caches which today are typically implemented using static random access memory (SRAM) technology. The next largest layer of the memory hierarchy — the main memory — is today most frequently dynamic random-access memory (DRAM), and is also on the motherboard. New types of memory technologies are of continual interest to the architecture research community, and recently a popular area of exploration for caches or main memory technology is non-volatile RAM (NVRAM). NVRAM is persistent, meaning that it retains its memory state even if its power supply is cut. A few types of NVRAM currently being explored include Phase-Change RAM (PCRAM), Magnetoresistive RAM (MRAM) and Resistive RAM (RRAM) [193]. A particular type of NVRAM called *flash* is already widely utilized for the largest the largest layer of the memory hierarchy — **storage**. Alternatively, storage may be on hard disk drives (HDDs).

Processor technology long ago moved beyond the basic Von Neumann model of a single central processing unit (CPU), and has since been undergoing continuous changes. In particular, computers today now frequently use parallel and/or heterogeneous processing. Parallel processing simultaneously executes multiple instructions, and may be implemented as simultaneous multithreading (SMT), chip-multiprocessing (CMP), or often, both. In the SMT model, one superscalar processor contains multiple independent hardware threads that each issue their own instructions within a single cycle. CMP multiprocessing integrates at least two (though possibly hundreds of) independent processors on a single *chip*. It is also common to see server computers with more than one socket — so that one motherboard actually contains multiple CMPs, each of which may be simultaneously multithreaded. Heterogeneous processing, or computer systems that use more than one kind of processor or core, typically each with unique ISAs, is also gaining popularity. Heterogeneous processing systems often include a CPU as well as some application specific processors such as qraphics processing units (GPUs). Cores may be implemented with custom logic (i.e., application specific integrated circuits [ASICs]), or with reprogrammable logic (i.e., field-programmable quate arrays [FPGAs]). An alternative or supplement to heterogeneous processing is asymmetric multiprocessing (AMP), where cores use the same ISA, but are of different sizes. AMP is currently popular because it allows users to exploit different choices of power—and runtime-efficiency tradeoffs for possible energy savings.

#### 2.1.2 System-Layer

The System-Layer contains a piece of software called the **operating system (OS)** that connects users and applications to the Hardware-Layer, manages hardware settings, and attempts to ensure computer-wide security. In some computer layer taxonomies, the System-Layer is merely an analogue for the computer's operating system, but our classification also includes *System* Virtual Machines (VMs), web browsers, the BIOS and other types of firmware.

• System VMs are essentially platforms within an OS; a system VM abstracts the hardware of a single machine into multiple virtual *partitions*, each of which may execute its

own operating system environment. To the overlying operating systems, the virtual machines appear identical to real hardware.

- Browsers are software that facilitates communication with the internet. They allow users to both post and receive information. Although browsers could be considered a part of the Application–Layer, we include them here because with the advent of technologies such as complex web applications and Google's Chromebook, the line between operating systems and browsers is blurring [254].

- A system's BIOS or Basic Input/Output System is a type of *firmware* software that controls and monitors hardware, and is permanently stored in read—only memory. The BIOS handles the *booting* (i.e., power startup) process of computer hardware.

In addition to maintaining basic hardware functionality, the System–Layer is now taking on the relatively new role of tuning dynamically adjustable hardware configurations. An example of this that is discussed in detail later in this dissertation is dynamic voltage and frequency scaling (DVFS) — a process where the operating system adjusts voltage supplies or hardware frequencies to manage power usage.

#### 2.1.3 Application-Layer

The Application–Layer contains **program source code** and the tools and mechanisms that connect that code to the platform layers. These include **programming languages** of which there are many types: assembly languages, high-level languages (which may be further divided into categories such as imperative/functional, object-oriented/procedural, static/dynamic), scripting languages, domain specific languages, and visual languages (i.e., those that are not text–based). These categories are not necessarily mutually exclusive, for example the AWK language could be considered both a scripting language and a domain specific language because it is primarily used for text data processing. This layer also includes the **interpreters**, **compilers**, and **process or application Virtual Machines** (VMs) that implement programming languages. Each of the three differs with respect to how this is done; for interpreters, source code is parsed and directly executed on the target platform, or occasionally first translated into an **intermediate representation**. Compilers

translate the source code to a platform-specific **target program**, usually incorporating both machine-independent and machine-dependent optimizations for a more efficient target program. Application VMs translate source to a platform-independent target language, then wrap the resultant program and their own functionality into a single process to execute. VMs often feature just-in-time (JIT) compilation, where most compilation is conducted at run time, in contrast to ahead-of-time (AOT) compilation. Also in this layer are the **assemblers** and **linkers**, that respectively (1) follow up after the compiler to convert assembly programs into object files and (2) merges the object files into a single executable file. After linking, executables are loaded by the operating system, which involves creating memory space for the program and starting its execution (the **loaders** that complete this operation could be considered a part of the System-Layer, but we place them here for continuity).

Finally, there are application program interfaces (APIs) and libraries. APIs specify how different computing components may interact via functions, object collections, or protocols. APIs work as generalized connectors, for example making it easy for applications to communicate with GPUs (e.g., OpenCL) or other hardware components (such as hardware disk drives or video cards), or with databases and web browsers. APIs are frequently implemented as libraries, which consist of a collection of functions written in a programming language, that have well-defined behavior and invocation procedures. Libraries may connect languages to system functionalities (an example being the pthreads library that allows C and C++ programs to spawn new threads), provide hardware–specific high–efficiency implementations (as do the CUDNN library for accelerating deep neural networks on GPUs or optimized BLAS libraries for scientific computing kernels), or simply abstract broadly used functions to aid software engineers (for example, the C++ Standard Template Library [STL] that contains generic implementations for objects such as hash maps and heaps).

#### 2.1.4 Distributed Computing

Distributed computing is a relatively old technology with origins in the 1970s [4], that has much more recently become ubiquitous. Distributed computing connects multiple computers with a network, coordinating their communication and data sharing via some form of

message passing. It could be considered a part of the System–Layer, but we list distributed computing separately here because it differs from traditional single computer systems in three key ways. First, distributed computing systems contain multiple instances of individual computer systems, each autonomously operating and each with its own local memory. Second, distributed systems are asynchronous — the constituent computers do not share a global clock. Third, distributed systems can tolerate failures of entire computers and can still continue computation; a mechanism called independent failure.

There are a couple of circumstances responsible for the current popularity of distributed computing. The first is the need that some companies and agencies have for reliability greater than that of a single computer, and in particular that of a single hard drive. Another reason is that it is frequently cheaper to purchase multiple less powerful (in terms of operations per second, or RAM size) machines, than it is to purchase one machine with the same operational capabilities. Additionally, even the most powerful computer can sometimes not service one organization's data storage or I/O request bandwidth needs. Finally, outsourced server management (i.e., to distributed computer service providers such as Amazon Web Services<sup>1</sup>) is becoming a very popular business decision.

#### 2.2 An Overview of Computing Analyses

Before getting into the specifics of the measurement and analysis techniques that this dissertation will use, we need to understand the larger context of all the tools and methods available to analyze computer systems.

To organize the available tools and methodologies, we consider the general type of analysis conducted. The three main types of analysis are:

- 1. Static Program Analysis

- 2. Hardware Synthesis, Emulation, and Simulation

- 3. Dynamic Analysis and Measurement

<sup>&</sup>lt;sup>1</sup>https://aws.amazon.com/

Static program analysis is a set of methods that examines source code or assembly code without executing it. Analysis may be done by humans (for example, Big-O notation for estimating runtime), or by tools (for example, compilers checking for type correctness or optimization opportunities). Static analysis considers code alone, in isolation of the platform and hardware, so it is difficult to extrapolate the analysis data into information that represents whole system behavior. Due to its lack of suitability for examining complex interactions between system layers, static analysis is not a primary focus of this dissertation.

Synthesis, emulation, and simulation are techniques used to design and optimize hardware. Hardware synthesis takes an algorithmic description of a problem and implements the behavior it describes in hardware. For the sake of optimization, the synthesis process performs different types of analyses. Emulation is when one piece of hardware is imitated with another piece of hardware, typically to analyze how a not–yet–existing piece of hardware might perform. Simulation has a similar goal to emulation, but models in detail the internal states of the non-existing hardware. While emulation and simulation should in theory report the same final performance numbers when analyzing a given piece of hardware, only simulation will be able to report detailed and continuous information about the internal processes of the hardware in question. We do not use hardware synthesis, emulation, or simulation techniques in this dissertation, in part because they are not fully accurate when it comes to understand hardware–software interactions [37] or, if accurate, they are prohibitively complex and extremely slow Except in Chapter 5 — which uses dynamic analyses to improve the speed of a certain type of simulation — synthesis, emulation, and simulation are not further discussed in this dissertation.

Dynamic analyses and measurements involve recording information about software as it runs on an existing platform. Since dynamic analysis tracks actual execution, it is the method best suited to capture complex hardware-software interactions, and thus the general method used throughout this dissertation. We devote the next section of this chapter to discussing when, where, how, and for what to use dynamic performance analysis techniques.

#### 2.3 Dynamic Performance Analyses

There are many kinds of dynamic performance analyses for studying computer systems. Rather than try to comprehensively catalogue the many open—source, commercial, and academic measurement and analysis tools, this section's aim is to distinguish different types of analysis techniques based on how, when, where, and what is measured. Later, we explicitly name relevant tools in the "Related Work" sections of individual chapters.

#### 2.3.1 Instrumentation

One distinction that can be made to differentiate dynamic analysis techniques is in *how* measurements are initiated, beginning with whether *instrumentation* is used or not. Instrumentation is the process of dictating system monitoring through code instructions inserted directly into the program being measured. The instruction code may be inserted at many different points, such as:

- within program source code or library code;

- within program binary code;

- within assembly or machine code;

- within a compiler; or

- within an operating system.

The code could also be inserted by different agents, such as:

- directly by the programmer (e.g., printf calls), with or without the support of programming language—level instrumentation directives;

- by a compiler; or

- by a system driver.

The code can also be injected at different times, for example:

• during or after a program is written;

- during or after compilation, either pre- or post-linking; or

- during execution, for example via JIT re-compilation.

One possibly confusing nomenclature detail to note is that when instrumentation is inserted pre-compilation or at compilation or link time, it is said to be *static instrumentation*, whereas if instrumentation is inserted post-compilation at execution time, it is said to be *dynamic instrumentation*. However, the static—or dynamic—prefixes refer only to the time of instrumentation, and both types of instrumentation are still *dynamic* analyses, because in both cases the collection of data will occur at runtime.

Deciding when, how, and where to instrument a program is a delicate tradeoff that must take into account the required efforts of the analysis tool developer, the efforts of the end-user, and the collection goals. For example, instrumentation inserted via dynamic instrumentation directly into binaries is attractive from a user-standpoint, because it requires neither program rewrites nor recompilation. However, dynamic instrumentation tools can require significantly more effort on the part of the analysis tool developer — in part because dynamic instrumentation tools must be specific to the intermediate representation (frequently an ISA) of the programs they instrument, thus requiring not only a detailed understanding of this representation by the tool developers, but also multiple versions of the tools for different representations.

#### 2.3.2 Independent Measurement

When instrumentation is not used, that is, when monitoring instructions are external to the program being monitored, we say that the program is *independently monitored*. Monitors could be a standalone application that reads hardware counters (such as cache miss rates or instructions retired) or operating system statistics (such as number of child processes spawned or percentage of processor utilization). Independent measurement could also be built into some part of the system, including the hardware, the operating system, or the compiler. Finally, independent measurement may be completely external to the computer system being measured, for example on another machine in a distributed network, or with an external meter, such as the "Kill A Watt" electricity monitor that connects to a computer's

power supply to account various statistics such as voltage, current, and power draw.

#### 2.3.3 Collection and Recording Policies

Orthogonal to whether they are instigated by instrumentation or by independent monitoring, dynamic analyses may utilize one of two types of recording policies, continuous monitoring or periodic sampling. Continuous monitoring, as the name suggests, continues to collect data for the duration of an application's execution. Periodic sampling instead collects data only for short lengths at a time, then pauses for an interval, then collects data again, and repeats. The sampling periods may be punctuated by random— or timer—based intervals, or may be based on machine statistics such as processor cycles or instructions retired. Another analysis policy decision that is orthogonal to the method of measurement is whether data is recorded as trace or as a profile. The difference between traces and profiles is that traces save detailed consecutive and often time—stamped lists of events (such as an ordered function execution log), whereas profiles summarize the data with aggregate event counts (such as a list of function call frequency counts). While traces can potentially provide users with more information, they may also take more resources to record, store, and post-process.

#### 2.3.4 What to Collect

The options for what information dynamic analyses can be used to track are almost endless. One major distinction that can be made about what kinds of information dynamic analyses collect is whether that information relates to *performance* or *correctness*. Performance information includes quantitative metrics such as runtime, energy, power, device size or hardware area, or system financial cost. Correctness information includes data on the reliability of systems, on program bugs such as data races, on security issues, or on testing–related issues such as test case code–coverage. In a few cases, the two categories may overlap; for example data that shows a program spending significant time in mutex locks may be considered both performance–related (because of the excess runtime incurred) or correctness–related (because of the potential underlying concurrency bug). In line with the goal of identifying and reducing inefficiencies, the dynamic analyses in this dissertation

focus almost entirely on collecting performance information. Some examples of performance information that may be collected include:

- processor metrics, such as processing frequencies, cycle counts, instruction execution counts, or instruction mixes (i.e., what proportions of different types of instructions are issued);

- memory metrics, such as cache misses, page faults, or I/O bus cycles;

- synchronization and concurrency metrics, such as number of locks, time spent waiting at barriers, or the number of active threads or processes;

- programmatic metrics, such as function calls or basic block counts;

- scheduling metrics, such as response time, throughput, or latency;

- speed metrics, such as instructions retired per cycle (IPC), floating point operations per second (FLOPS), processor idle time, or processor utilization rates;

- power and energy metrics, such as peak power, minimum power, TDP, or performance per watt.

## 2.3.5 Dynamic Analysis Pitfalls

There are a couple of downsides or potential problems with dynamic analyses.

Overheads and Perturbation One major potential pitfall of dynamic analyses is perturbation, or the possibility that the overheads of the measurement process will affect the actual data being measured. This is especially a concern of instrumentation, given that extra instructions are added to the programs to be measured. To ensure result integrity, perturbation must be carefully monitored, reigned in, and if necessary, corrected. Non-perturbative overheads — those that do not affect the measurements — can also be problematic if they present as significant compilation time or runtime increases. For example, Chapter 5 must deal with the excessive (but non-perturbative) overheads involved in simulating GPUs.

Other Pitfalls There are other precautions one must take to avoid measurement inaccuracies. Due to the nature of dynamic analyses measuring real events on real systems, they can be *unsound*, that is not representative of all possible variations. Nondeterminism in parallel programs, different user inputs, or program–external events such as operating system interrupts, battery power levels, or processor frequency variations can result in different measurement results across program executions. Typically, reasonable accuracy of measurement can be assured with repeated trials (until a statistically significant result is achieved), a varied supply of inputs, and control over as many external events as possible (such as disabling dynamic processor frequency tuning).

# Chapter 3

# Parallel Block Vectors

The advent of multi-core processing and its subsequent rise is largely a consequence of a decline in transistor scaling. Facing limits to performance per area due to heat thresholds, architects needed a way to deliver speed without excess power consumption. One solution that they came up with is the multicore processor, which substitutes the previous single large, powerful, and power–hungry processing core for multiple smaller, less powerful but also less power–hungry cores. The multiple cores use thread level parallelism or TLP — executing instructions simultaneously on multiple cores. There are a few reasons why multiple cores can increase net performance with lower net power consumption; one is that the smaller cores can be run at a lower frequency than the single large core and still deliver faster net processing speeds due to TLP. Sometimes, opting out of the expensive wide superscalar out–of–order (OOO) cores used in uniprocessing (because the instruction-level parallelism (ILP) they provide is no longer needed with TLP) further helps multiprocessing come out ahead on the performance–per–power spectrum.

Given the efficiency opportunities that multiprocessing can provide for general purpose computing, the technology seems like a clear win. There is a major downside of multiprocessing, however: writing and debugging the programs that can run on multiprocessors, i.e., multithreaded programs, is a challenge and an ongoing area of research. There are many hurdles, including legacy single—threaded code that must be rewritten, and added difficulty in debugging programs that now exhibit nondeterminism (different behaviors across different executions). Also, it is difficult for programmers to reason about parallel algorithms,