## Challenges and Solutions for High Performance Analog Circuits with Robust Operation in Low Power Digital CMOS

#### Chun-Wei Hsu

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

2015

©2015

Chun-Wei Hsu

All Rights Reserved

#### **Abstract**

## Challenges and Solutions for High Performance Analog Circuits with Robust Operation in Low Power Digital CMOS

#### Chun-Wei Hsu

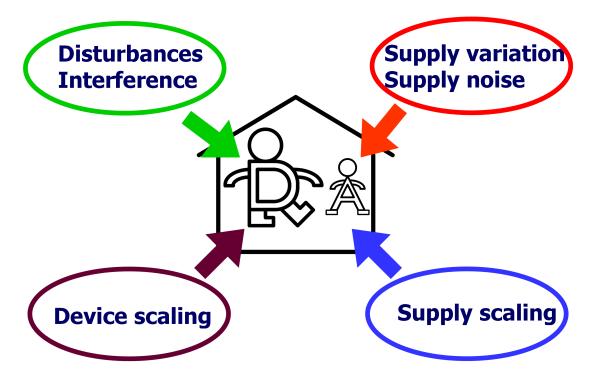

In modern System-on-Chip products, analog circuits need to co-exist with digital circuits integrated on the same chip. This brings on a lot of challenges since analog circuits need to maintain their performance while being subjected to disturbances from the digital circuits. Device size scaling is driven by digital applications to reduce size and improve performance but also results in the need to reduce the supply voltage. Moreover, in some applications, digital circuits require a changing supply voltage to adapt performance to workloads. So it is further desirable to develop design solutions for analog circuits that can operate with a flexible supply voltage, which can be reduced well below 1V. In this thesis challenges and solutions for key high performance analog circuit functions are explored and demonstrated that operate robustly in a digital environment, function with flexible supply voltages or have a digital-like operation.

A combined phase detector consisting of a phase-frequency detector and sub-sampling phase detector is proposed for phase-locked loops (PLLs). The phase-frequency function offers robust operation and the sub-sampling detector leads to low in-band phase noise. A 2.2GHz PLL with

a combined phase detector was prototyped in a 65nm CMOS process, with an on-chip loop filter area of only 0.04mm<sup>2</sup>. The experimental results show that the PLL with the combined phase detector is more robust to disturbances than a sub-sampling PLL, while still achieving a measured in-band phase noise of -122dBc/Hz which is comparable to the excellent noise performance of a sub-sampling PLL.

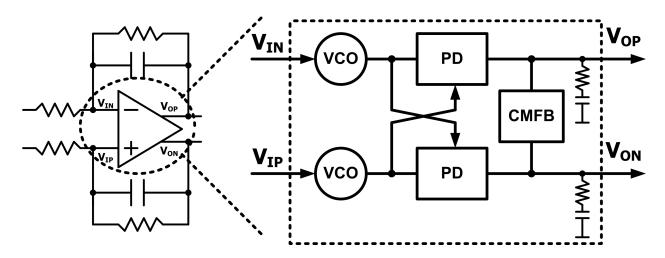

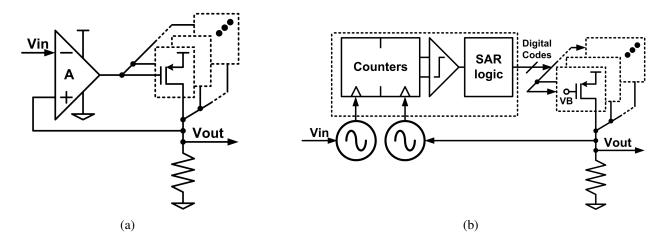

A pulse-controlled common-mode feedback (CMFB) circuit is proposed for a 0.6V-1.2V supply-scalable fully-differential amplifier that was implemented in a low power/leakage 65nm CMOS technology. An integrator built with the amplifier occupies an active area of 0.01mm<sup>2</sup>. When the supply is changed from 0.6V to 1.2V, the measured frequency response changes are small, demonstrating the flexible supply operation of the differential amplifier with the pulse-controlled CMFB.

Next, models are developed to study the performance scaling of a continuous-time sigma-delta modulator (SDM) with a varying supply voltage. It is demonstrated that the loop filter and the quantizer exhibit different supply dependence. The loop noise performance becomes better at a higher supply thanks to larger signal swings and better signal-to-noise ratio, while the figure of merit determined by the quantization noise gets better at a lower supply voltage, thanks to the quantizer power dissipation reduction. The theoretical models were verified with simulations of a 0.6V-1.2V 2MHz continuous-time SDM design in a 65nm CMOS low power/leakage process.

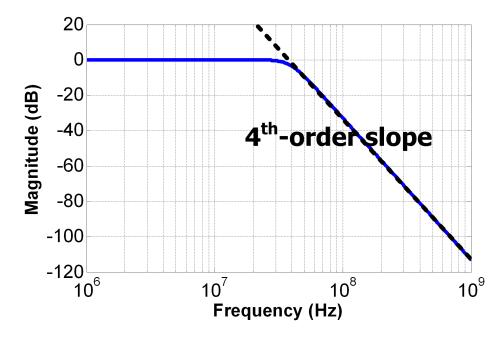

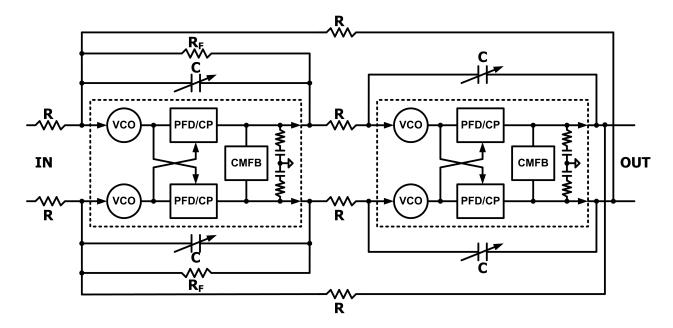

Finally, two design techniques are introduced that leverage the continued improvement of digital circuit blocks for the realization of analog functions. A voltage-controlled-ring-oscillator-based amplifier with zero compensation is proposed that internally uses a phase-domain representation

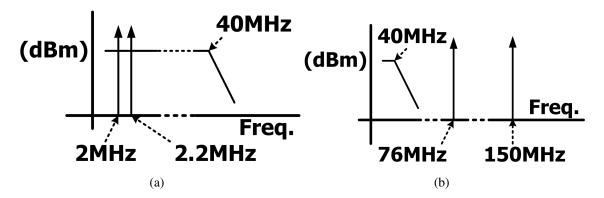

of the analog signal. This provides a huge DC gain without significant penalties on the unity-gain bandwidth or area. With this amplifier a 4th-order 40-MHz active-UGB-RC filter was implemented that offers a wide bandwidth, superior linearity and small area. The filter prototype in a 55nm CMOS process has an active area of 0.07mm<sup>2</sup> and a power consumption of 7.8mW at 1.2V. The in-band IIP3 and out-of-band IIP3 are measured as 27.3dBm and 22.5dBm, respectively. A digital in-situ biasing technique is proposed to overcome the design challenges of conventional analog biasing circuits in an advanced CMOS process.

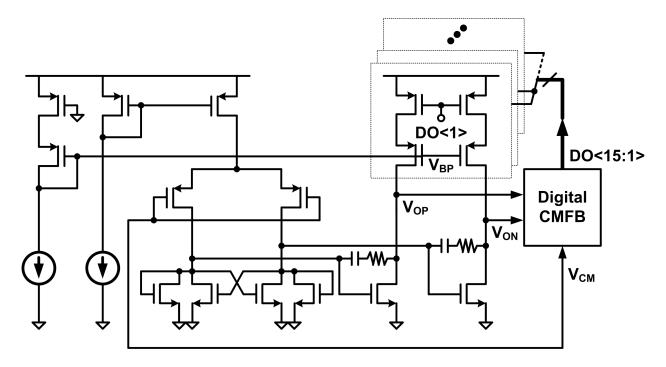

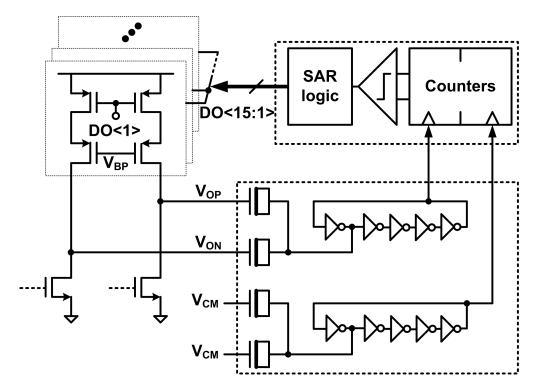

A digital CMFB was simulated in a 65nm CMOS technology to demonstrate the advantages of this digital biasing scheme. Using time-based successive approximation conversion, the digital CMFB provides the desired analog output with a more robust operation and a smaller area, but without needing any stability compensation schemes like in conventional analog CMFBs.

In summary, analog design techniques are continuously evolving to adapt to the integration with digital circuits on the same chip and are increasingly using digital-like blocks to realize analog functions in highly-integrated SOC chips. The signal representation in analog circuits is moving from traditional electrical signals such as voltage or current, to time and phase-domain representations. These changes make analog circuits more robust to voltage disturbances and supply variations. In addition to improved robustness, analog circuits based on timing signals benefit from the faster and smaller transistors offered by the continued feature scaling in CMOS technologies.

## **Contents**

| Li | st of Figures iv |                                                                                 |     |

|----|------------------|---------------------------------------------------------------------------------|-----|

| Li | st of T          | Tables                                                                          | xii |

| 1  | Intro            | oduction                                                                        | 1   |

|    | 1.1              | Motivation                                                                      | 1   |

|    | 1.2              | Outline                                                                         | 4   |

| 2  | A Sı             | ub-Sampling-Assisted Phase-Frequency Detector for Low-Noise PLLs with Ro-       |     |

|    | bust             | Operation under Supply Interference                                             | 5   |

|    | 2.1              | Introduction                                                                    | 6   |

|    | 2.2              | Developing a Combined Phase Detector Designed for Robustness                    | 8   |

|    | 2.3              | Simulation-based verification of the Locking Issues in Sub-Sampling-based Phase |     |

|    |                  | Detectors and Robustness of the Combined Phase Detector                         | 13  |

|    | 2.4              | Noise Analysis for the Combined Phase Detector                                  | 18  |

|    | 2.5              | Circuit Design of a Low In-band Phase Noise PLL with Robust Operation           | 21  |

|   |       | 2.5.1    | Combined Phase Detector                                               | 22 |

|---|-------|----------|-----------------------------------------------------------------------|----|

|   |       | 2.5.2    | Voltage Controlled Oscillator, Programmable Divider and Loop Filter   | 25 |

|   | 2.6   | Experi   | mental Results                                                        | 27 |

|   |       | 2.6.1    | Robustness of the Phase Detector to Supply Voltage Disturbances       | 33 |

|   |       | 2.6.2    | Low In-band Phase Noise                                               | 35 |

|   | 2.7   | Conclu   | isions                                                                | 40 |

| 3 | A Su  | ipply-Se | calable Differential Amplifier With Pulse-Controlled Common-Mode Feed | l- |

|   | back  | ζ.       |                                                                       | 43 |

|   | 3.1   | Introdu  | action                                                                | 44 |

|   | 3.2   | Pulse-o  | controlled Common-mode Feedback                                       | 47 |

|   | 3.3   | Impler   | nentation of a Supply-scalable Amplifier with the PC CMFB             | 48 |

|   | 3.4   | Experi   | mental Results                                                        | 53 |

|   | 3.5   | Conclu   | isions                                                                | 59 |

| 4 | Effe  | cts of S | upply Scaling on the Performance of Continuous-Time Delta-Sigma Mod-  | •  |

|   | ulate | ors      |                                                                       | 60 |

|   | 4.1   | Introdu  | action                                                                | 61 |

|   | 4.2   | Perform  | mance-Setting Elements in a Continuous-time Delta-sigma Modulator     | 63 |

|   | 4.3   | Model    | s for the Supply Scaling of CT DSM Performance                        | 65 |

|   |       | 4.3.1    | Dependence of the Quantization Noise on the Supply Voltage            | 65 |

|   |       | 4.3.2    | Dependence of the Loop Filter Noise on the Supply Voltage             | 66 |

| Bi | bliogı | caphy                                                                           | bliography 118 |  |  |

|----|--------|---------------------------------------------------------------------------------|----------------|--|--|

| 7  | Sum    | amary                                                                           | 115            |  |  |

|    | 6.5    | Conclusions                                                                     | 112            |  |  |

|    |        | 6.4.2 Successive-approximation Operation                                        | 111            |  |  |

|    |        | 6.4.1 Voltage-frequency Conversion                                              | 108            |  |  |

|    | 6.4    | Implementation of the Digital CMFB                                              | 107            |  |  |

|    | 6.3    | A Digital Common-mode Feedback Circuit Adopting the Digital Biasing Technique   | 106            |  |  |

|    | 6.2    | The Digital Biasing Technique                                                   | 104            |  |  |

|    | 6.1    | Introduction                                                                    | 102            |  |  |

| 6  | Digi   | tal In-situ Biasing Technique                                                   | 101            |  |  |

|    | 5.5    | Conclusions                                                                     | 99             |  |  |

|    | 5.4    | Experimental Results                                                            | 94             |  |  |

|    | 5.3    | Active-UGB-RC Filter Implementation                                             | 91             |  |  |

|    | 5.2    | A VCO-based Amplifier with Zero Compensation                                    | 80             |  |  |

|    | 5.1    | Introduction                                                                    | 79             |  |  |

|    | Con    | pensation                                                                       | 78             |  |  |

| 5  | A 40   | OMHz 4th-order Active-UGB-RC Filter using VCO-Based Amplifiers with Zero        |                |  |  |

|    | 4.6    | Conclusions                                                                     | 76             |  |  |

|    | 4.5    | Simulation Results of the Supply-Scalable Continuous-time Delta-sigma Modulator | 73             |  |  |

|    | 4.4    | Design Example of a Supply-Scalable Continuous-time Delta-sigma Modulator       | 68             |  |  |

# **List of Figures**

| 1.1 | Design challenges to analog circuits integrated with digital circuits                    | 2  |

|-----|------------------------------------------------------------------------------------------|----|

| 1.2 | The supply voltage, cut-off frequency and minimum gate length of transistors from        |    |

|     | 2013 to 2026 by ITRS                                                                     | 3  |

| 1.3 | Examples of the time operation: frequency modulation and pulse-width modulation          | 4  |

| 2.1 | Block diagram of a sub-sampling phase detector and associated waveforms and              |    |

|     | characteristics                                                                          | 8  |

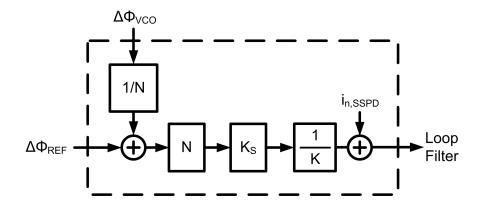

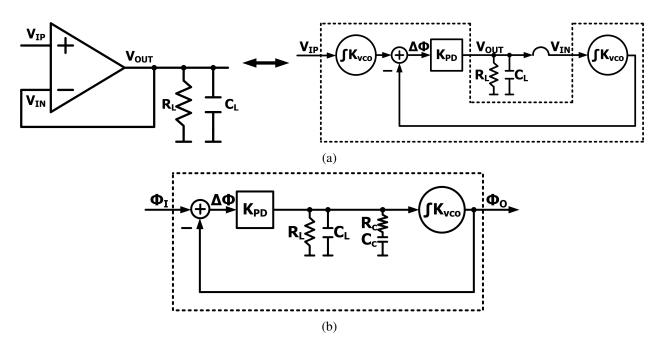

| 2.2 | Phase domain model of the sub-sampling phase detector                                    | 9  |

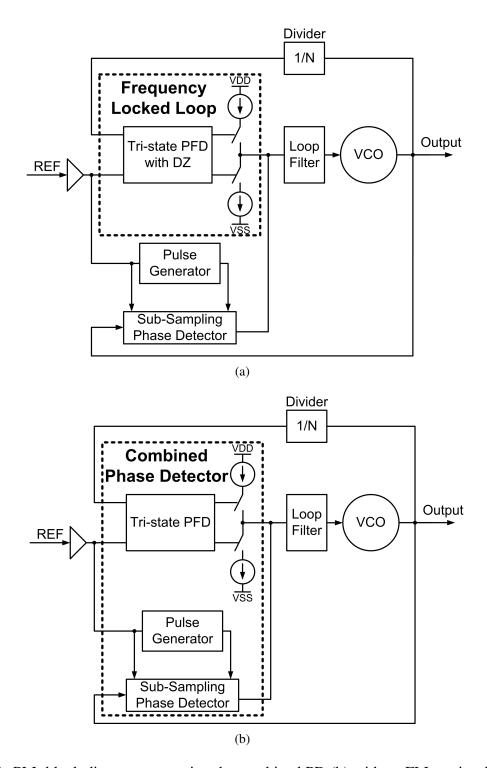

| 2.3 | PLL block diagram comparing the combined PD (b) with an FLL-assisted SSPD                |    |

|     | (a). The tri-state PFD in the combined PD does not have a dead zone (DZ)                 | 11 |

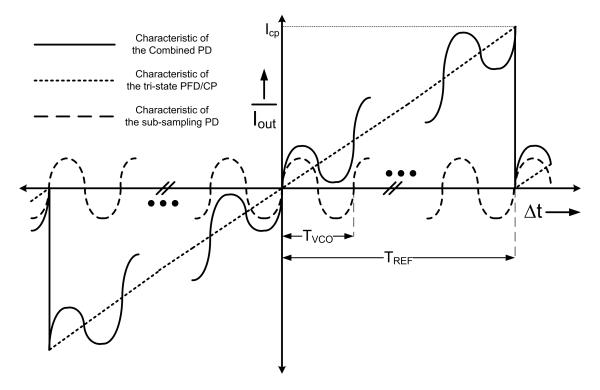

| 2.4 | Characteristics of the combined phase detector, the PFD, and the sub-sampling PD         | 12 |

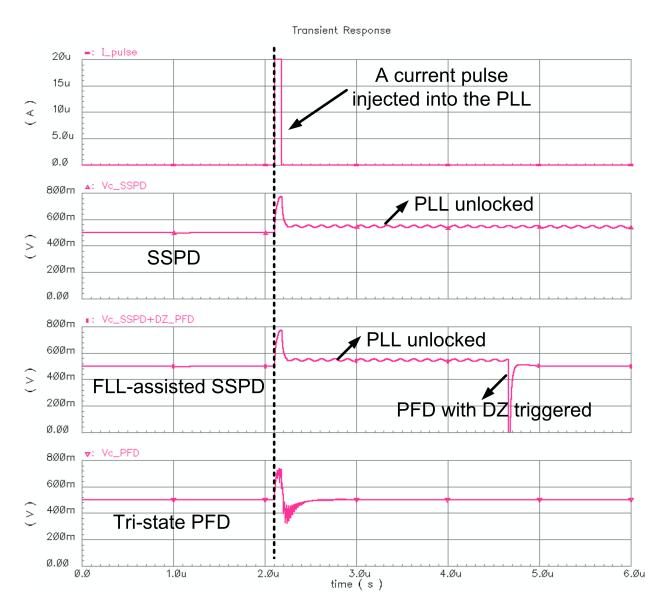

| 2.5 | Interference robustness simulation results for PLLs with different types of phase        |    |

|     | detectors; an SSPD-only PLL loses lock; a PLL with an FLL-assisted SSPD reac-            |    |

|     | quires lock, albeit after a long time (2.5 $\mu$ s in this example) during which the PLL |    |

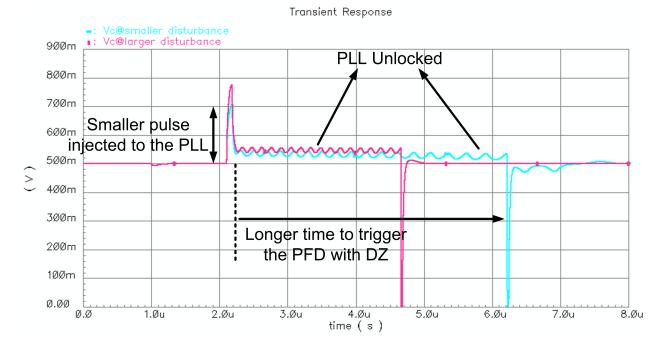

|     | is unlocked; a PLL with a PFD operates robustly for the same disturbance                 | 14 |

| 2.6  | Simulated results of a PLL using an FLL-assisted PFD subjected to disturbances   |    |

|------|----------------------------------------------------------------------------------|----|

|      | of different strengths                                                           | 16 |

| 2.7  | Simulation results of the PLL with a conventional PFD and the proposed combined  |    |

|      | PD under the disturbance                                                         | 17 |

| 2.8  | Phase domain model for the PLL with the combined phase detector                  | 18 |

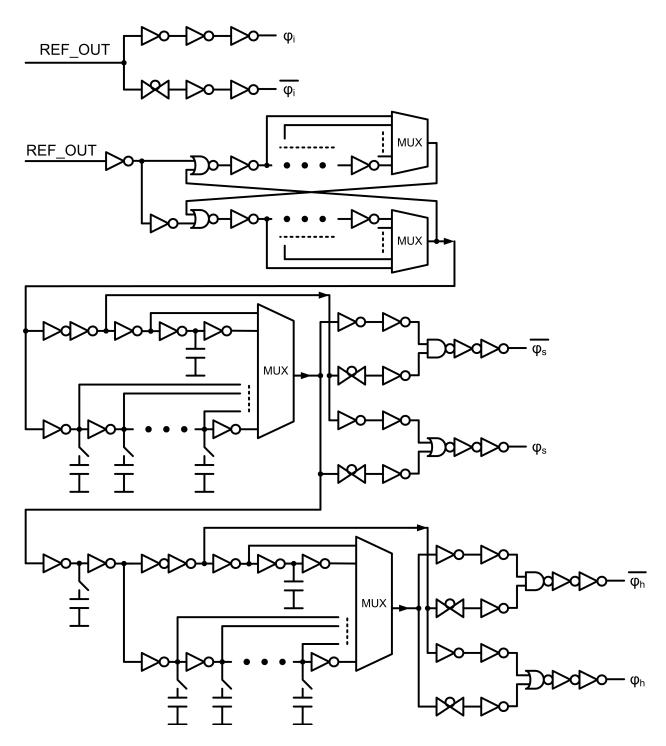

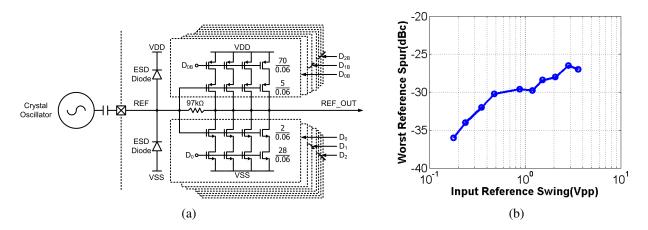

| 2.9  | Circuit implementation of the sub-sampling phase detector. The units for W and L |    |

|      | are $\mu$ m                                                                      | 23 |

| 2.10 | Detailed implementation of the pulse generator used in the sub-sampling PD       | 24 |

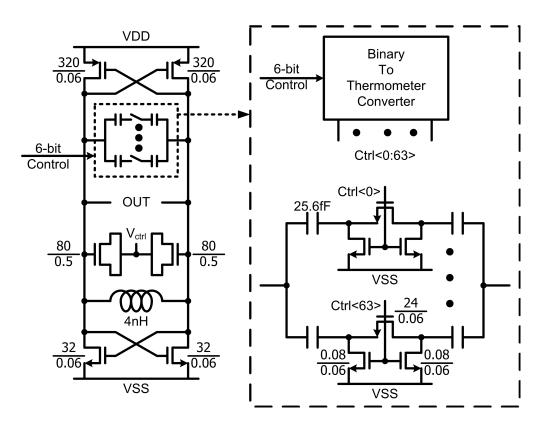

| 2.11 | Circuit implementation of the LC-VCO used in the PLL. The units for W and L      |    |

|      | are μm                                                                           | 26 |

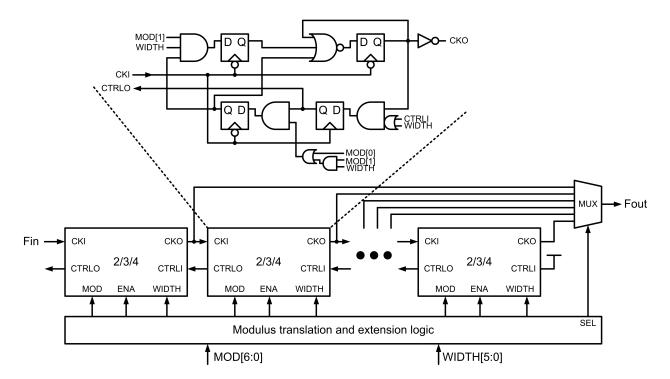

| 2.12 | Block diagram of the frequency divider                                           | 27 |

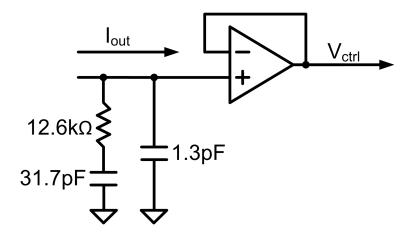

| 2.13 | Loop filter implementation                                                       | 28 |

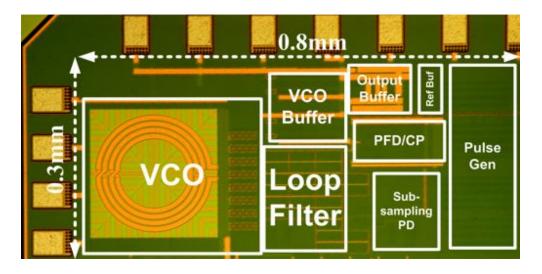

| 2.14 | Die photo of the PLL                                                             | 28 |

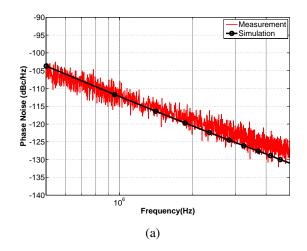

| 2.15 | (a) Measured and simulated phase noise spectrum of the VCO (b) Measured tuning   |    |

|      | curve of the LC-VCO for three cap-bank settings                                  | 29 |

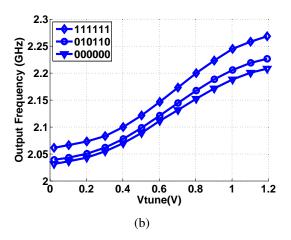

| 2.16 | Measured phase noise spectrum of the PLL when operating with a reference fre-    |    |

|      | quency of 50MHz and a divisor of 41 and output frequency of 2.05GHz (blue trace  |    |

|      | lower bandwidth and lower peaking) and divisor of 44 and output frequency of     |    |

|      | 2.2GHz (red trace higher bandwidth and with higher peaking)                      | 29 |

| 2.17 | Measured reference spurs of the PLL when operating at 2.2GHz                     | 30 |

| 2.18 | Root causes to reference spurs in a sub-sampling PLL                             | 31 |

| 2.19 | (a) Measured VCO output spectrum while the SSPD's output is disabled (b) Mea-          |    |

|------|----------------------------------------------------------------------------------------|----|

|      | sured reference spurs by decreasing the driving setting of the buffer between the      |    |

|      | VCO and SSPD as $f_{\rm REF}$ =40MHz                                                   | 32 |

| 2.20 | (a) Circuit diagram of the reference buffer with the digitally controlled strength (b) |    |

|      | Measured reference spurs for different reference swings                                | 33 |

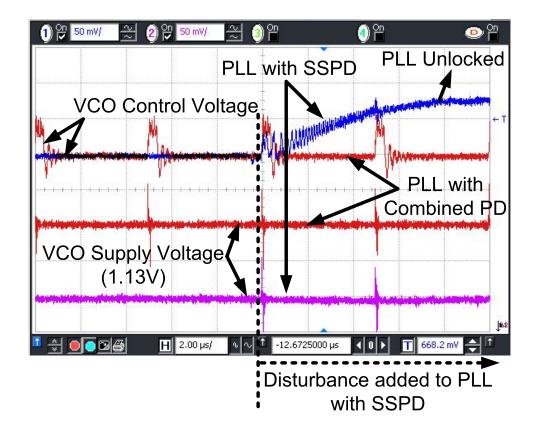

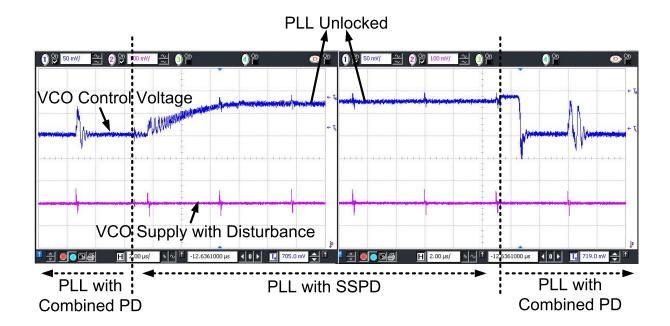

| 2.21 | Effect of VCO supply voltage disturbances on the PLL's operation; using the com-       |    |

|      | bined PD the PLL can sustain substantial disturbances; using the sub-sampling PD       |    |

|      | only, the PLL loses lock as soon as the disturbances are applied                       | 34 |

| 2.22 | While operating with disturbances on the VCO supply, the PD of the PLL is              |    |

|      | switched between the combined and sub-sampling-only operation mode; in sub-            |    |

|      | sampling-only mode, the PLL loses lock, but it recovers as soon as switching back      |    |

|      | to combined operation mode                                                             | 35 |

| 2.23 | Measured phase noise spectrum of the PLL when operating at 2.2GHz with the             |    |

|      | combined phase detector and the tri-state phase detector only                          | 36 |

| 2.24 | Measured phase noise spectrum of the used crystal reference source showing -           |    |

|      | 157.4dBc/Hz at 200kHz and -163.6dBc/Hz at 1MHz                                         | 37 |

| 2.25 | A comparison between the measured and simulated phase noise spectrum of the            |    |

|      | PLL using the combined phase detector, and the simulated phase noise spectrum          |    |

|      | of the PLL with a modified loop filter to improve the loop's phase margin              | 38 |

| 2.26 | Measured phase noise spectrum of the PLL with the combined PD and the tri-state        |    |

|      | PED only as the output frequency of 2.15GHz                                            | 39 |

| 2.27 | Measured in-band phase noise vs reference swing; the presented PLL operates at    |    |

|------|-----------------------------------------------------------------------------------|----|

|      | 1.1 V, whereas Gao-09 [6] operates at 1.8V; for Hsu-08 [16], Wang-08 [17] and     |    |

|      | Gu-06 [18] the peak-to-peak reference swing has been assumed to be equal to the   |    |

|      | respective chip supply voltage                                                    | 40 |

| 3.1  | Analog circuits with flexible supply operation in mobile systems                  | 45 |

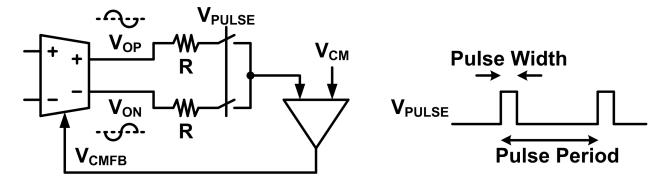

| 3.2  | Proposed pulse-controlled common-mode feedback circuit                            | 47 |

| 3.3  | (a) Conventional passive R-C common-mode feedback circuit (b) Proposed pulse-     |    |

|      | controlled common-mode feedback circuit                                           | 48 |

| 3.4  | Fully differential amplifier with the proposed pulse-controlled common-mode feed- |    |

|      | back circuit in a feedback application                                            | 49 |

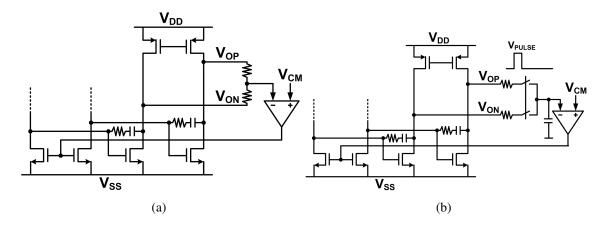

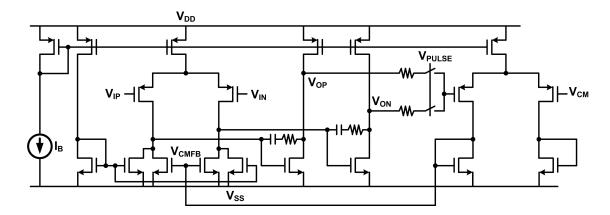

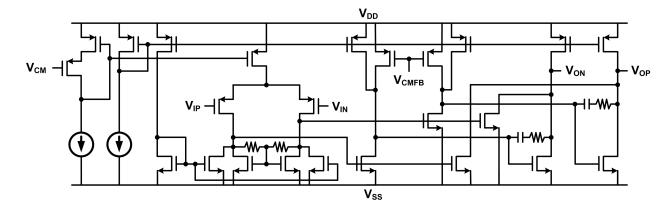

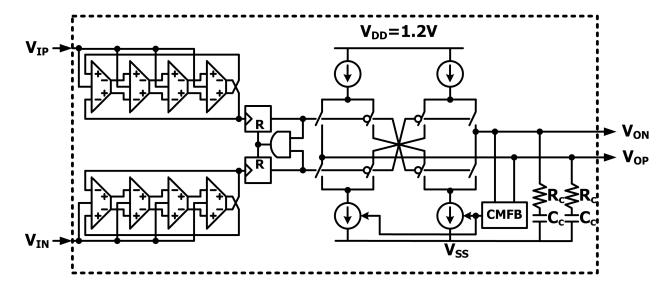

| 3.5  | Circuit implementation of the supply scalable differential amplifier with the PC  |    |

|      | CMFB                                                                              | 50 |

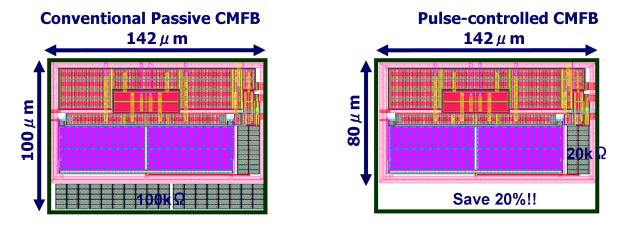

| 3.6  | Layout comparison of the amplifier with RC CMFB and PC CMFB                       | 51 |

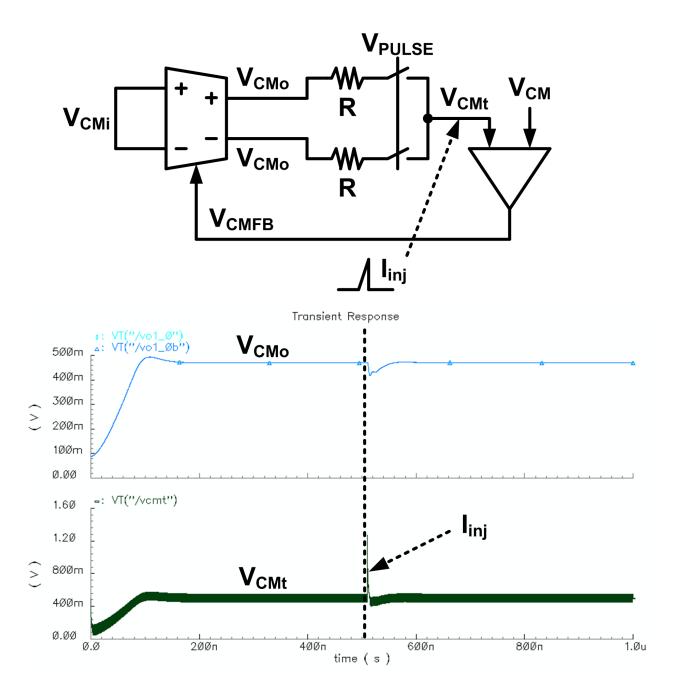

| 3.7  | Simulation with injecting a large current impulse                                 | 52 |

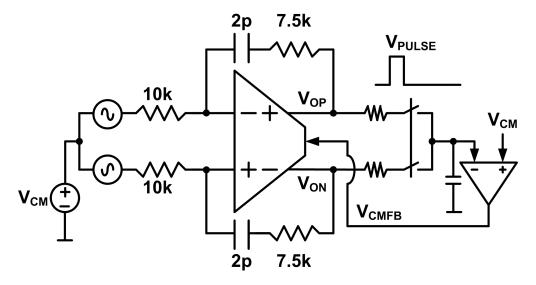

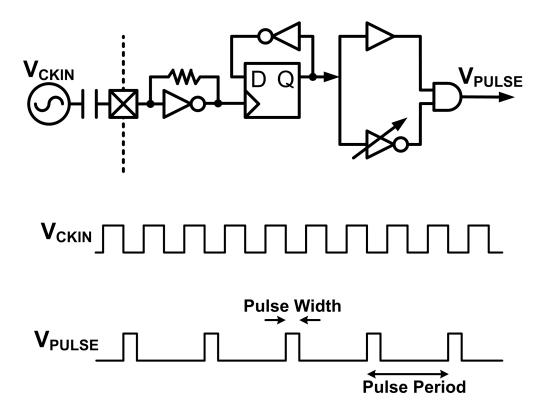

| 3.8  | Schematic of the pulse timing generator for the PC CMFB                           | 53 |

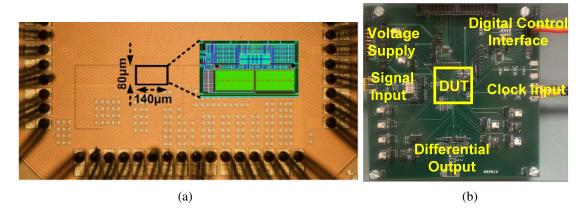

| 3.9  | (a) Die photo and layout inset of the differential amplifier with the PC CMFB (b) |    |

|      | Measurement setup of the amplifier with the PC CMFB                               | 54 |

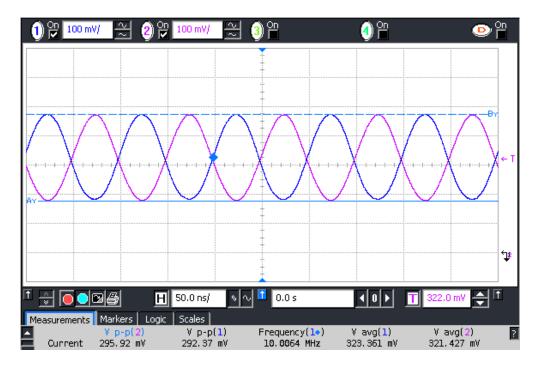

| 3.10 | Measured time-domain waveform of the differential output of the amplifier with    |    |

|      | the PC CMFB at $V_{DD}$ =0.6V                                                     | 54 |

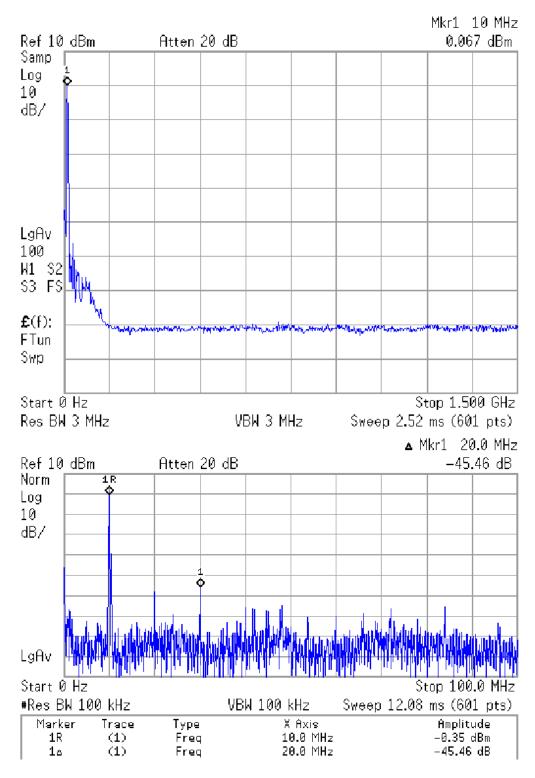

| 3.11 | Measured wideband output spectrum (top) of the amplifier with a 10MHz, 0dBm       |    |

|      | input and its inband output spectrum from 0 to 100MHz (bottom)                    | 56 |

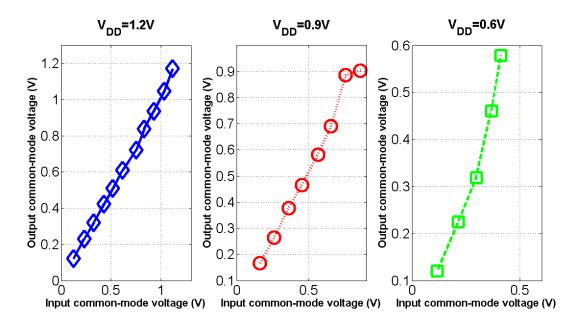

| 3.12 | Measured output common-mode voltage of the amplifier with the PC CMFB while                       |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | varying the common-mode reference and operating at different supplies from 0.6V                   |    |

|      | to 1.2V                                                                                           | 57 |

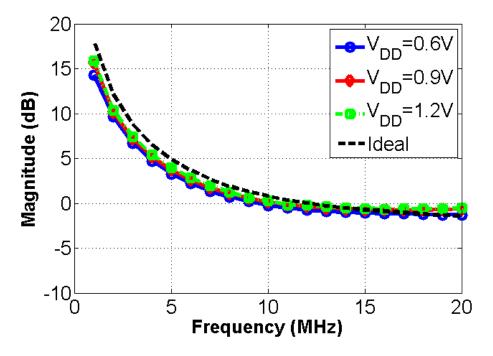

| 3.13 | Comparison between the ideal transfer function and the measured frequency re-                     |    |

|      | sponse of the feedback amplifier for different supplies                                           | 57 |

| 4.1  | Noise contributions to a continuous-time delta-sigma modulator                                    | 62 |

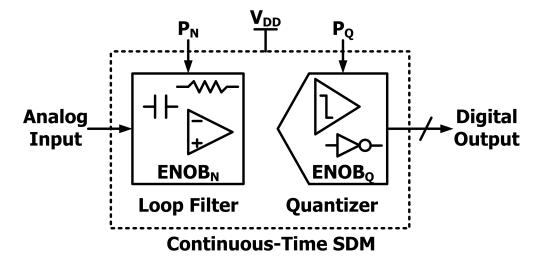

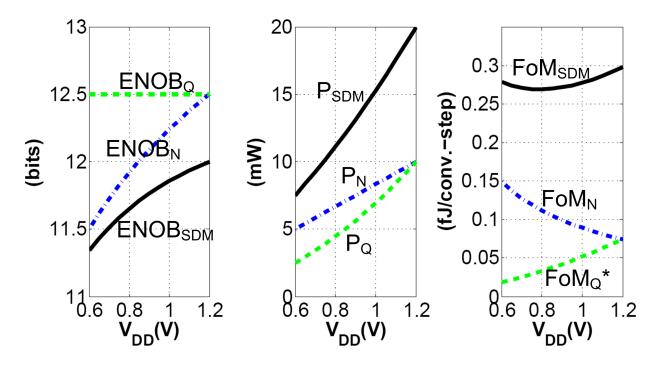

| 4.2  | Supply-scaling performance models of the loop filter, quantizers and overall DSM                  |    |

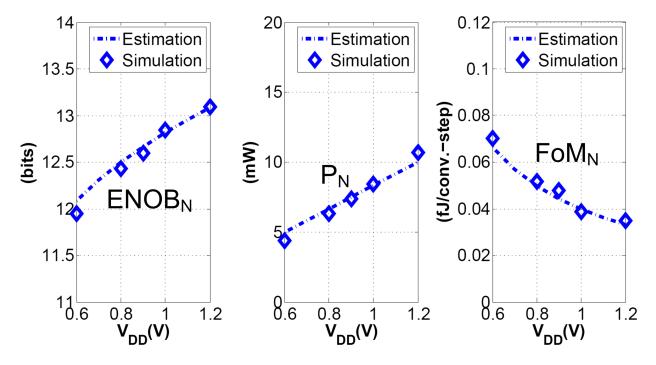

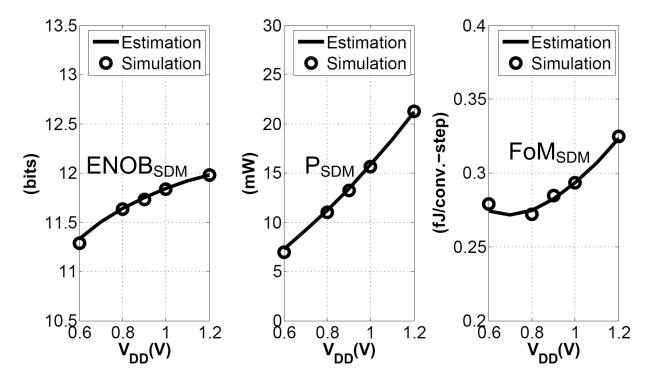

|      | $(FoM_Q*=FoM_Q/2^{ENOB_Q}) \qquad \ldots \qquad \ldots \qquad \ldots \qquad \ldots \qquad \ldots$ | 68 |

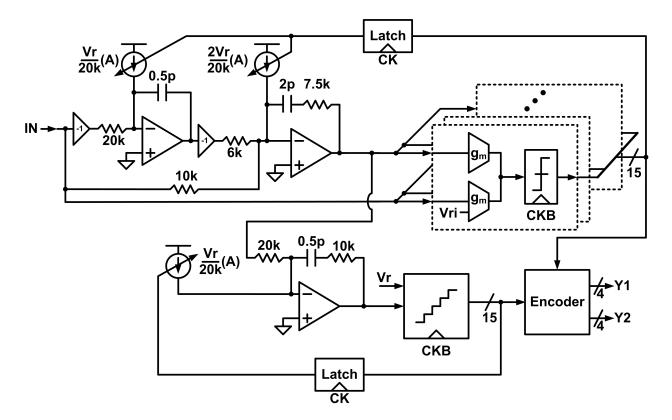

| 4.3  | Architecture of the supply-scalable continuous-time delta-sigma modulator                         | 69 |

| 4.4  | Schematic of the first amplifier of the loop filter                                               | 70 |

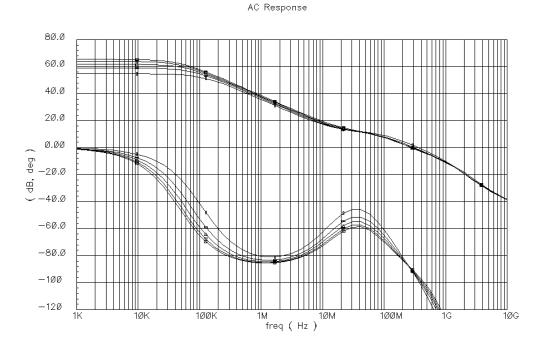

| 4.5  | Simulated Bode plot of the first amplifier for supplies of 0.6V, 0.75V, 0.9V, 1.05V               |    |

|      | and 1.2V                                                                                          | 71 |

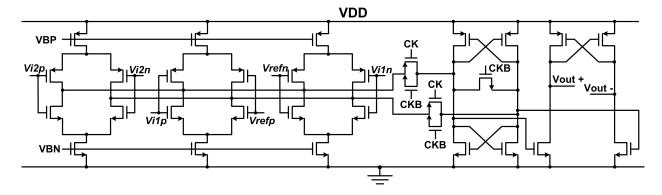

| 4.6  | Circuit of the two-input comparator used for the first quantizer                                  | 72 |

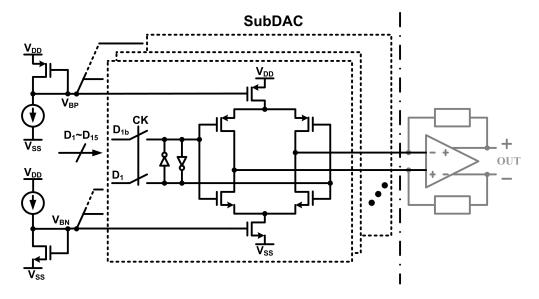

| 4.7  | Sub-DAC realization using fifteen current-steering cells                                          | 73 |

| 4.8  | Layout of the cascaded 2-1 CT DSM                                                                 | 74 |

| 4.9  | Comparison between the simulation and analytical models of the DSM with a                         |    |

|      | transistor-level loop filter and behavioral sample-and-hold circuits while sweep-                 |    |

|      | ing the supply voltage                                                                            | 75 |

| 4.10 | Simulated and estimated performance of complete transistor-level CT DSM as a                      |    |

|      | function of the supply voltage                                                                    | 76 |

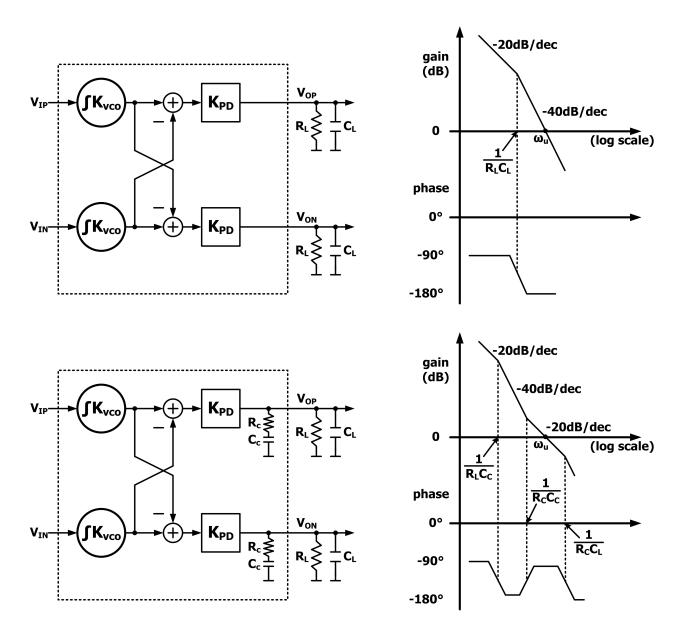

| 5.1  | Comparisons of a continuous-time filter using the Gm-C type and ring-oscillator-        |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | based structure by taking the examples of (a) an integrator and (b) a biquad            | 79 |

| 5.2  | Earlier proposed VCO-based amplifier [42] whose use is limited to RF modulator          |    |

|      | applications                                                                            | 81 |

| 5.3  | (a) A unity-gain buffer using the prior VCO-based amplifier (b) The phase domain        |    |

|      | model of a type-II 3rd order PLL with the divisor equal to one                          | 82 |

| 5.4  | The comparison of prior VCO-based amplifier and the proposed VCO-based am-              |    |

|      | plifier with zero compensation                                                          | 83 |

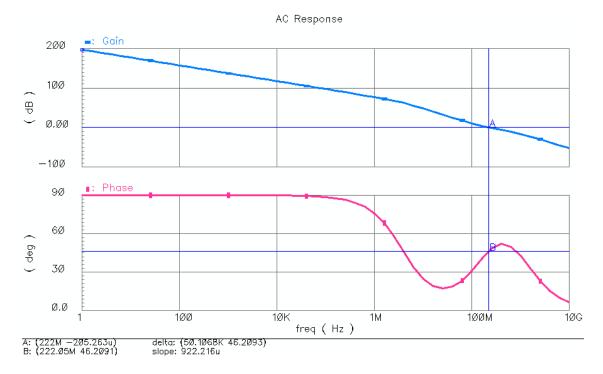

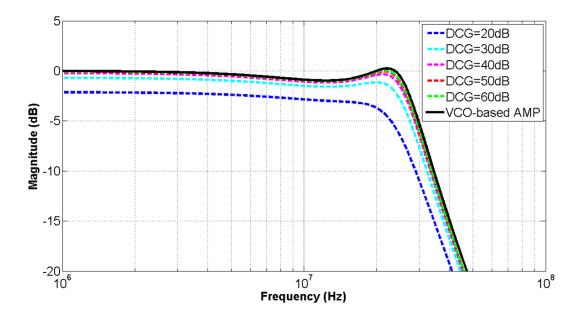

| 5.5  | Simulated Bode plot of the VCO-based amplifier with zero compensation                   | 85 |

| 5.6  | Block diagram of a first-order filter using the proposed VCO-based amplifier with       |    |

|      | zero compensation                                                                       | 85 |

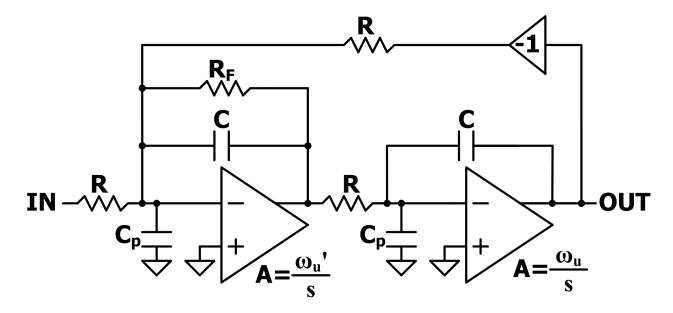

| 5.7  | Schematic of the proposed VCO-based amplifier with zero compensation                    | 87 |

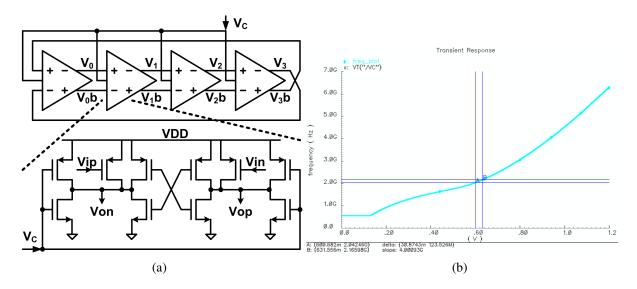

| 5.8  | (a) Circuits of the ring oscillator (b) The simulated characteristic of the ring oscil- |    |

|      | lator showing $K_{VCO}$ =4GHz at the output frequency 2GHz                              | 88 |

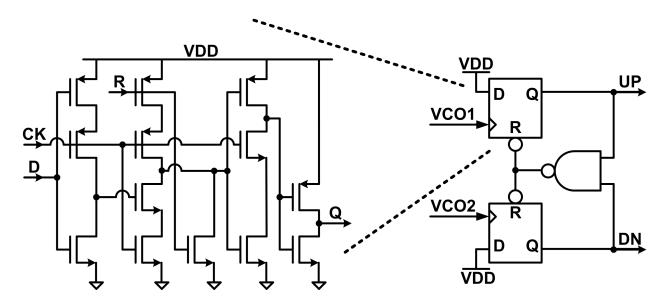

| 5.9  | Schematics of the phase-frequency detector with high speed D-flip-flops                 | 88 |

| 5.10 | Implementations of the charge pump and common-mode feedback circuit                     | 89 |

| 5.11 | Comparisons of a 3rd-order Chebyshev active-RC filter using the amplifiers with         |    |

|      | different DC gains and the VCO-based amplifiers                                         | 90 |

| 5.12 | Block diagram of a 4th-order active-UGB-RC filter realized with one biquad while        |    |

|      | limiting the UGB of the amplifiers to obtain additional integrators [41]                | 92 |

| 3.13 | The frequency response of a 4th-order Butterworth low-pass fifter implemented by    |    |

|------|-------------------------------------------------------------------------------------|----|

|      | a 4th-order active-UGB-RC filter using a biquad                                     | 92 |

| 5.14 | Architecture of the 4th-order active-UGB-RC filter using the VCO-based ampli-       |    |

|      | fiers with zero compensation                                                        | 93 |

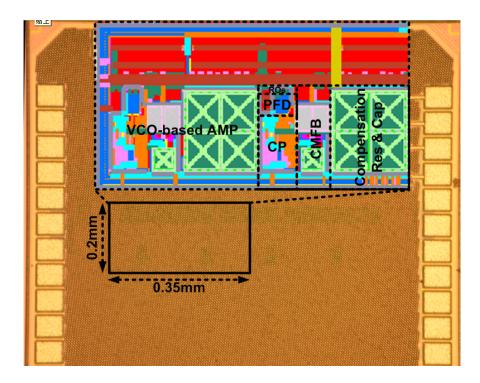

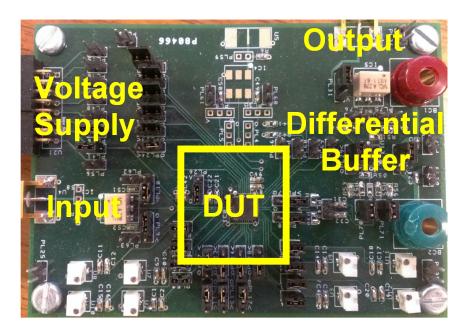

| 5.15 | Die photo of the 4th-order filter with an insert of the layout                      | 94 |

| 5.16 | Measurement setup of the 4th-order active-UGB-RC filter                             | 95 |

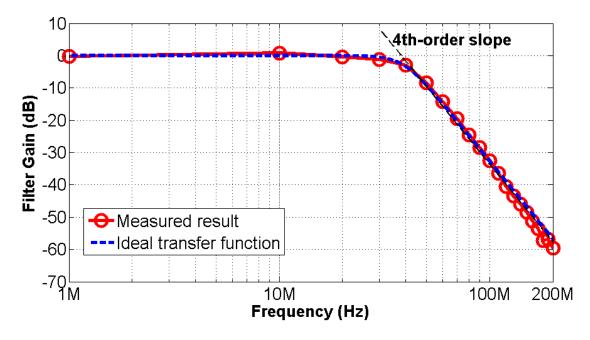

| 5.17 | Measured frequency response of the 4th-order 40MHz filter compared with the         |    |

|      | ideal transfer function of a 4th-order Butterworth filter                           | 95 |

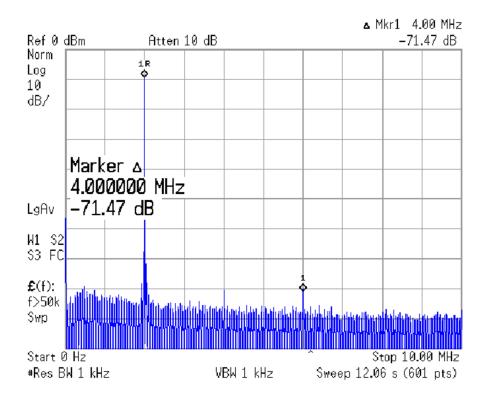

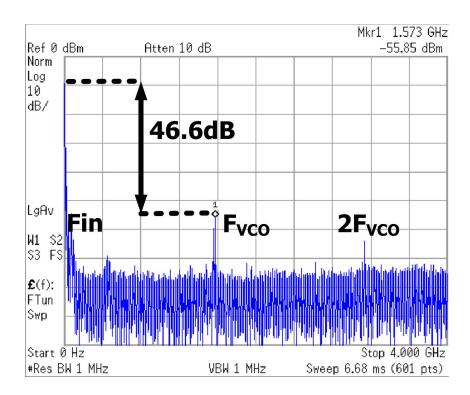

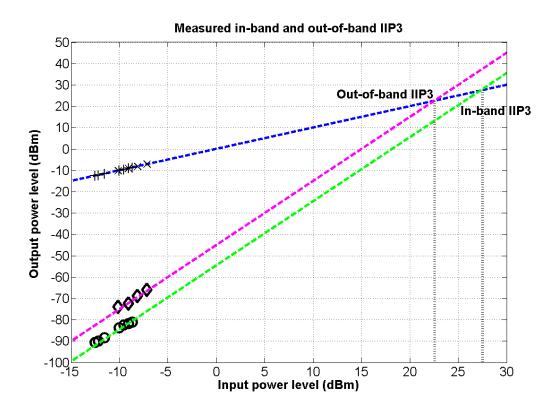

| 5.18 | Measured narrow-band output spectrum the filter with a 2MHz and -3dBm input         | 96 |

| 5.19 | Measured wide-band output spectrum of the filter showing the high-frequency         |    |

|      | spurs caused by the VCO-based amplifier                                             | 97 |

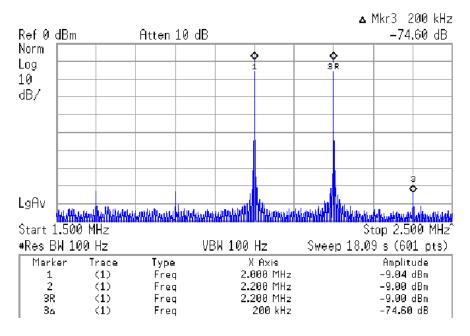

| 5.20 | Measured output spectrum of the filter for a two-tone input with the power level    |    |

|      | -9dBm at the frequency of 2MHz and 2.2MHz                                           | 97 |

| 5.21 | (a) Two-tone input for the measurement of in-band IIP3 (b) Two-tone input for the   |    |

|      | measurement of out-of-band IIP3                                                     | 98 |

| 5.22 | Measured in-band IIP3 with two tones at 2MHz and 2.2MHz and out-of-band IIP3        |    |

|      | with two tones at 76MHz and 150MHz                                                  | 98 |

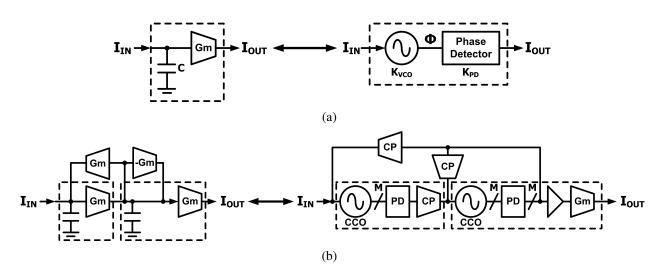

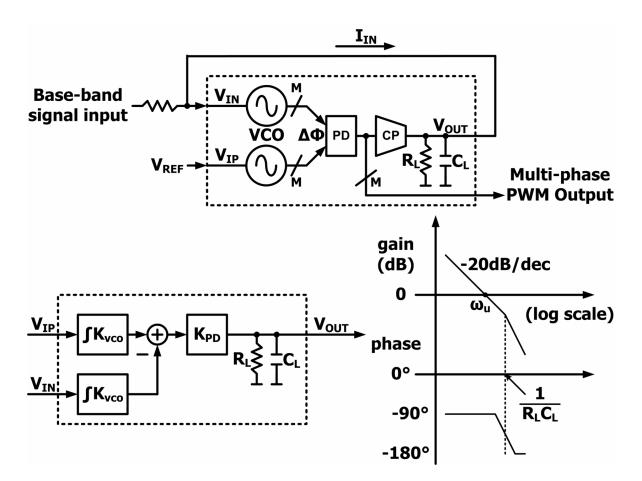

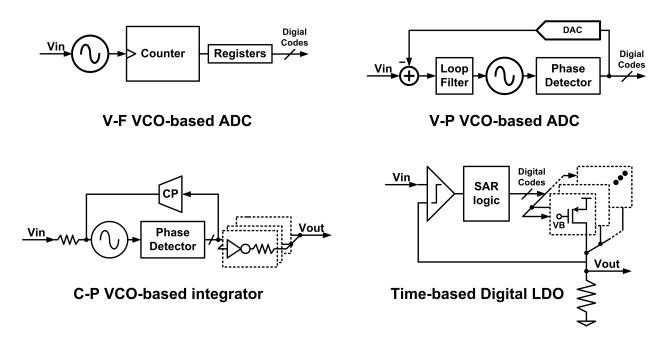

| 6.1  | Block diagrams of different time-based, frequency-based or phase-based circuits . 1 | 02 |

| 6.2  | A voltage regulator uses (a) an analog biasing technique and (b) a digital biasing  |    |

|      | technique                                                                           | 05 |

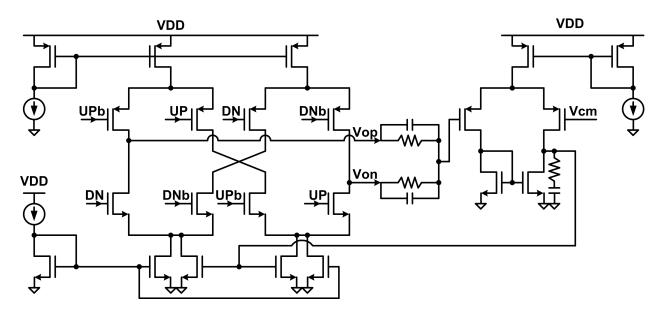

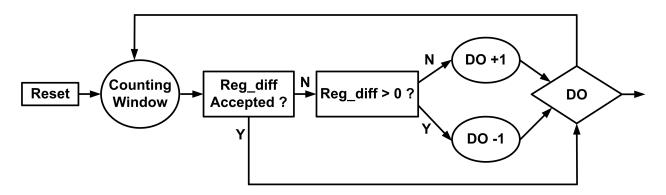

| 63   | A fully-differential amplifier with a digital common-mode feedback circuit 1        | 06 |

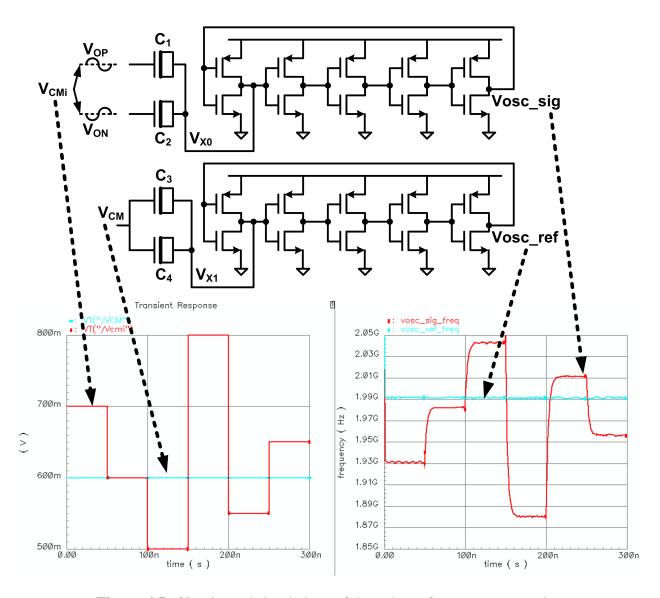

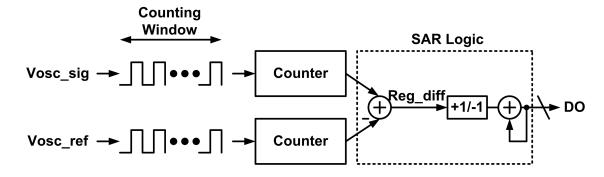

| 6.4 | Digital common-mode feedback circuit                                          | 108 |

|-----|-------------------------------------------------------------------------------|-----|

| 6.5 | Circuits and simulations of the voltage-frequency conversion                  | 109 |

| 6.6 | The successive-approximation operation and the state diagram of the SAR logic | 111 |

| 6.7 | The simulated result of the digital CMFB                                      | 113 |

## **List of Tables**

| 2.1 | Performance comparison table  | 42 |

|-----|-------------------------------|----|

| 3.1 | Simulation results            | 51 |

| 3.2 | Performance summary           | 58 |

| 4.1 | Performance comparison table  | 77 |

| 5.1 | Filter Performance Comparison | 99 |

#### Acknowledgments

I hope to acknowledge the support and assistance of many people who have contributed to the completion of this dissertation. First of all, I would like to express my sincere appreciation to my advisor Professor Peter R. Kinget for his guidance and advice, and teaching me much knowledge for my research. His discipline and attention to details is an inspiration during my PhD. I also thank my committee members: Prof. Harish Krishnaswamy, Prof. Mingoo Seok, Dr. Yves Baeyens and Dr. Kadaba(Kumar) Lakshmikumar for their invaluable time, comments and feedback.

I would give my thanks to SRC Grant 2008-HC-1836 for my financial funding; MediaTeK Inc., Texas Instruments and VIA Telecom Inc. for their fabrication donation and Alcatel-Lucent Technologies for measurement supports. I also wish to express my appreciation to Brian Ginsburg (TI) and UT Dallas for help with the tape-out, Manar El-Chammas (TI), Doug Garrity (Freescale), Brandt Braswell (Freescale) and Ram Kumar (Intel) for technical discussions.

I am grateful to all my colleagues, past and present of the Columbia Integrated System Laboratory (CISL) where most of my research works was done. Their suggestions and assistance have helped me move forward much smoother in the initial phase of my research. In no particular order, they are Shih-An Yu, Kshitij Yadav, Karthik J. Tripurari, Baradwaj Vigraham, Jayanth Kuppambatti, Chengrui Le, Jianxun Zhu, Rabia Tugce Yazicigil and Yang Xu.

Most of all, I would like to sincerely thank for the love, support, and encouragement from my families, my parents and my wife Man-Chun Chang. Without their love and understanding, I wouldn't be able to pursue my PhD and this work would never have come into existence.

## Chapter 1

#### Introduction

#### 1.1 Motivation

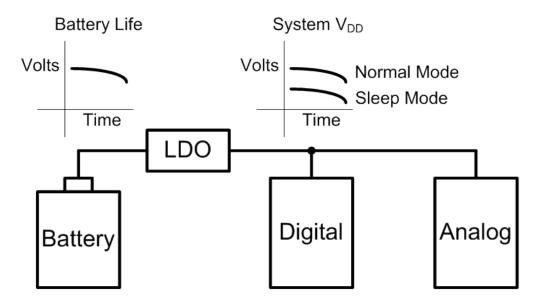

The continued advancement of CMOS technologies has fueled tremendous progress in low-cost and highly-integrated System-on-Chip products over the past decades. However, the integration of analog and digital circuits on a single chip leads to a lot of design challenges for the analog circuits which are shown in Fig. 1.1. Robust operation in the presence of disturbances or supply noise that couple through the substrate or supply from digital functions has become an essential requirement for analog circuits. Nevertheless, it is difficult for high performance analog circuits to maintain robustness because they have more sensitivity to signal quality, and less immunity to disturbances or interference. In addition, the analog circuits are required with flexible supply operation because digital core circuits need a higher supply to increase the operating frequency and process more applications, but a lower voltage at sleep mode to save idle power. The supply-scalable analog

Figure 1.1: Design challenges to analog circuits integrated with digital circuits

circuits also help extend battery life because they are able to fully use the power of batteries. However, these analog circuits with large supply tolerances meet the problems of limiting signal headroom, especially in low power/leakage CMOS technologies.

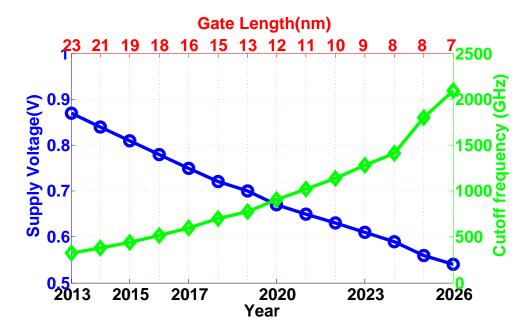

Additionally, digital circuits benefit from smaller and faster devices through the advancement of the CMOS technology, but the device scaling brings with it design difficulties to analog parts such as a low analog power gain by small output impedance and short-channel effects including drain-induced barrier lowering (DIBL), punch-through, and velocity saturation. Fig. 1.2 summarizes the transistor performance of the projected technology nodes from 2013 to 2026 by the International Technology Roadmap for Semiconductors, 2013 [Online]. With a steady reduction of the feature size and effective gate oxide thickness, the cut-off frequency of the CMOS transistors is increasing, while their available supply voltage is scaled down accordingly for power density.

**Figure 1.2:** The supply voltage, cut-off frequency and minimum gate length of transistors from 2013 to 2026 by ITRS

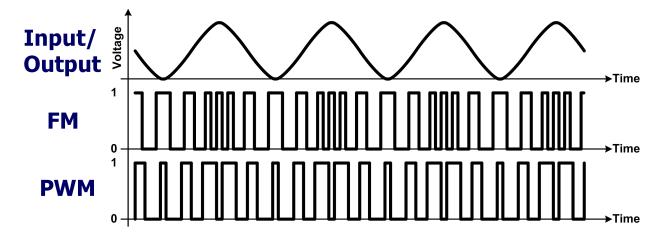

This scaling trend is pushing the analog interface to adopt digital approaches by replacing traditional voltage or current operation to time/frequency/phase operation and taking advantage of supply or device scaling, but keep the voltage or current inputs and outputs. The time or phase operation only has two discrete levels of voltage or current so that it is not sensitive to disturbances or supply changes and has more scaling benefits. Fig. 1.3 shows the two examples of the time operation: frequency modulation and pulse-width modulation.

In this dissertation, several analog examples are demonstrated to explore challenges and solutions for high performance analog circuits with robust operation, flexible supply operation, or digital-like operation. The research vehicles include a 2.2GHz phase-locked loop, an integrator with a zero of 10MHz, a 2MHz continuous-time sigma-delta modulator, a 4th-order 40MHz continuous-time filter, and a differential amplifier.

Figure 1.3: Examples of the time operation: frequency modulation and pulse-width modulation

#### 1.2 Outline

Most of the research contributions to this dissertation show the challenges and solutions of high performance analog circuits integrated with digital circuits and are included in the publications [3] [7] [33] [49]. The dissertation is organized as follows. Chapter 1 presents a motivation for the dissertation. In chapter 2, a combined phase detector was provided for PLLs with robust operation under disturbances while offering low in-band phase noise and low jitter. Chapter 3 describes a pulse-controlled CMFB for a fully-differential amplifier from 0.6V to 1.2V in a low power/leakage CMOS technology. In chapter 4, the supply-scaling models of a continuous-time sigma-delta modulator were verified by circuit simulations with the supplies between 0.6V and 1.2V. Chapter 5 shows a VCO-based amplifier with zero compensation for getting a large DC gain without any penalties associated with the large DC gain. Chapter 6 introduces a digital biasing solution using ultra-compact digital circuits for analog interfaces. In chapter 7, a summary of these works is given with one possible direction for extending the topics of study included in this dissertation.

## Chapter 2

## A Sub-Sampling-Assisted Phase-Frequency

### **Detector for Low-Noise PLLs with Robust**

## **Operation under Supply Interference**

It has recently been demonstrated that sub-sampling phase detectors (SSPDs) enable phase-locked loop (PLL) realizations with very low in-band noise [1] [2] [3]. However, the PLL can become susceptible to disturbances or interference via substrate or power supply coupling as experienced in SOC, which could put the PLL out of lock. A tri-state phase-frequency detector with a dead-zone is traditionally added to act as an auxiliary frequency-locked loop (FLL) to enable the PLL to regain lock, albeit after a long delay. A different solution is proposed to combine a tri-state PFD with an SSPD wherein the PLL is prevented from losing its lock while simultaneously achieving the superior in-band phase noise performance. A 2.2GHz integer-N PLL has been prototyped in

a 65nm CMOS process to demonstrate the advantages of the proposed combined phase detector. It has been experimentally verified that the PLL is more robust to disturbances than a PLL with a sub-sampling phase detector; it further achieves a measured in-band phase noise of -122dBc/Hz when operating with the proposed combined PD from a 1.1V supply.

#### 2.1 Introduction

Phase-locked loops (PLLs) are crucial building blocks for clock synthesis or carrier frequency generation in practically all system-on-chip (SOC) integrated circuits. Key performance metrics are low jitter or phase noise, and low power dissipation. However, in the context of SOC applications, robust operation in the presence of disturbances or interference that couple through the substrate or supply from large digital functions into the (embedded) PLL has become an essential requirement.

Jitter of a PLL is an important concern in clock synthesis applications. For a given power budget, [4] has shown that the minimum jitter for a PLL is achievable when the contribution from the out-of-band portion of the PLL's phase noise spectrum equals the contribution from the inband portion. Further, an equal distribution of power between the VCO and the PLL blocks has been proven to be the optimum strategy. The power budget for the VCO is thus fixed to half of the available power budget, and after optimizing the VCO design for the best phase noise performance, the PLL's jitter can be improved only by lowering the in-band noise (and accordingly increasing the PLL's loop bandwidth).

The choice of the phase detector (PD) design is critical as the noise of the PD is a significant contribution to the in-band phase noise of a PLL. Tri-state phase/frequency detectors (PFDs) are

popular for their inherent ability to discriminate both phase and frequency, thus widening the acquisition range of the PLL [5]. Recently, a PLL using sub-sampling phase detectors (SSPDs) has been demonstrated with ultra-low in-band phase noise [6]. However, PLLs using SSPDs have very small capture ranges, can false lock and are sensitive to disturbances (often on the VCO's supply or coupling through the substrate) which can push the PLL out of its locked state. An auxiliary FLL in the form of a tri-state PFD with dead-zone fixes the capture range and false lock problems. It also helps regain the lock after the PLL loses lock due to a disturbance or interference, but as shown below it requires a long acquisition time which may not be acceptable in many clock synthesis applications.

In this chapter, I would like to present a sub-sampling-assisted phase-frequency detector named by a combined phase detector which maintains the low in-band phase noise feature of [6], but makes it as robust to disturbances as PFD-based PLLs. This prevents the PLL from losing lock and thus eliminates the time wasted in lock re-acquisition when the PLL's output is unreliable. Further, the robustness is achieved without compromising the in-band phase noise performance of the PLL.

The rest of the chapter is organized as follows: section 2.2 discusses the operation of the proposed combined PD [7] and describes the measures to ensure robustness. Section 2.3 presents simulations demonstrating the lack of interference robustness in PLLs with sub-sampling-based phase detectors while PLLs with the proposed combined PD offers a similar robustness as PLLs with a PFD. Section 2.4 presents a detailed noise analysis of the combined PD, showing its superior noise performance over PFDs. Section 2.5 describes the circuit implementation of the blocks of a

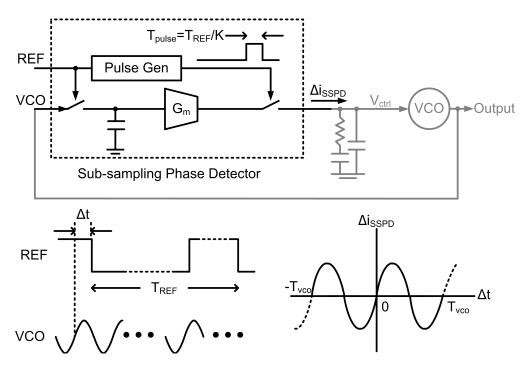

**Figure 2.1:** Block diagram of a sub-sampling phase detector and associated waveforms and characteristics

2.2GHz PLL prototype with the combined PD. Section 2.6 presents the experimental results with a focus on the robustness of PLL operation to disturbances on power supply while achieving a low in-band phase noise.

# 2.2 Developing a Combined Phase Detector Designed for Robustness

The block diagram of a standard SSPD [6] is shown in Fig. 2.1 and its basic operation can be summarized as follows. The VCO output voltage,  $v_{\text{VCO}}(t) = A_{\text{VCO}} \sin(\omega_{\text{VCO}} t + \Delta \phi_{\text{VCO}})$ , with an amplitude  $A_{\text{VCO}}$  and an angular frequency  $\omega_{\text{VCO}} = 2\pi/T_{\text{VCO}}$ . The phase  $\Delta \phi_{\text{VCO}}$  is sampled

at falling edges of the input reference signal REF. The reference is assumed to be frequency-locked to the VCO, so that its angular frequency  $\omega_{\text{REF}} = 2\pi/T_{\text{REF}} = \omega_{\text{VCO}}/N$ , but with a time shift  $\Delta t = \Delta \phi_{\text{REF}}/\omega_{\text{REF}}$  between falling edges of REF and corresponding VCO zero crossings. The voltage sample,  $\hat{v} = A_{\text{VCO}} \sin(\Delta \phi_{\text{VCO}}) = A_{\text{VCO}} \sin(\omega_{\text{VCO}} \Delta t) = A_{\text{VCO}} \sin(N\Delta \phi_{\text{REF}})$  is converted into a current with a transconductor with transconductance  $G_{\text{m}}$ . That current is gated and only steered to the loop filter for a duration  $T_{\text{pulse}} = T_{\text{REF}}/K$  and then integrated by the loop filter. K is the ratio of the reference period to pulse width and is the gain reduction factor of the SSPD. The loop filter has a time constant much larger than  $1/\omega_{\text{REF}}$  so that only the average of the current matters for modeling the phase detector operation in a steady state.

Because of the equality of  $\Delta\phi_{VCO}$  and  $N\Delta\phi_{REF}$ , there is an additional gain factor N at REF input of the SSPD compared to its VCO input. Thus, the equivalent phase domain model of the SSPD can be shown as Fig. 2.2.

Figure 2.2: Phase domain model of the sub-sampling phase detector

A PLL with the SSPD can achieve very low in-band phase noise [6]. However, the SSPD only performs phase detection with small locking range and no frequency detection. As a result, the PLL operating only with the SSPD may be locked to any harmonic of  $f_{REF}$ . To overcome the

frequency locking problem of the SSPD, [6] uses a tri-state PFD with a dead zone (DZ) of  $(-\pi, \pi)$  as an auxiliary FLL (referred to as FLL-assisted SSPD for simplicity). The auxiliary FLL is activated only when the magnitude of the timing error exceeds  $T_{\rm REF}/2$ . The PLL subjected to disturbances requires a long lock re-acquisition time, as will be discussed in section 2.3.

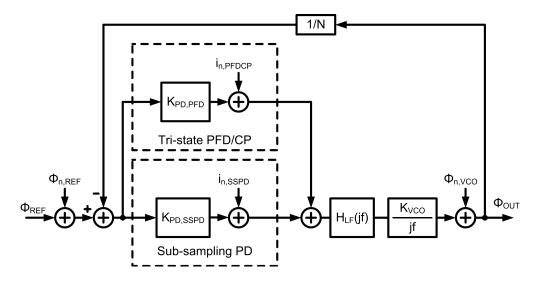

The core idea of the proposed phase detector is to combine the SSPD and the tri-state PFD in such way that the frequency-locked loop feature is always active. The comparison between an FLL-assisted SSPD and the proposed combined phase detector comprised of a tri-state PFD with a charge pump (CP) and an SSPD is shown in Fig. 2.3. The transfer characteristic of the combined phase detector is shown in Fig. 2.4. It is formed by summing the characteristics of the tri-state PFD/CP and the SSPD. The y-axis shows the averaged output current of the combined phase detector  $\overline{I_{\text{out}}}$  for a given time difference  $\Delta t$  between the falling edges of the REF signal and the corresponding zero-crossings of the VCO.

To retain the same frequency locking ability of a tri-state PFD, the zero output of the combined phase detector may only occur at  $\Delta t = 0$  and the combined phase detector needs to produce positive currents for all positive  $\Delta t$  and negative currents for all negative  $\Delta t$ . To achieve this, the maximum output current of the SSPD must be smaller than the output current of the PFD/CP for  $\Delta t = (\pm 3/4) T_{\text{VCO}}$ , which is  $\pm 3I_{\text{CP}}/(4N)$  where  $I_{\text{CP}}$  is the charge pump current of the tri-state PFD/CP. When keeping the sub-sampling phase detector's output current smaller than  $3I_{\text{CP}}/(4N)$ , the combined phase detector will continue to operate as a frequency detector in the presence of frequency errors and, as a result, the PLL will have a single stable locking point. It is noted that the

**Figure 2.3:** PLL block diagram comparing the combined PD (b) with an FLL-assisted SSPD (a). The tri-state PFD in the combined PD does not have a dead zone (DZ).

**Figure 2.4:** Characteristics of the combined phase detector, the PFD, and the sub-sampling PD gain of the combined PD in the transfer characteristic is dominated by the gain of the sub-sampling PD.

Except for frequency locking at the divisor of an integer, the PLL with the combined phase detector is also able to work with a fractional division ratio which is not allowed for a sub-sampling PLL. While operating in the fractional-N mode, the PLL with the combined PD is similar to a charge-pump PLL rather than a sub-sampling PLL because the maximum current of the sub-sampling PD is much smaller than  $I_{CP}$  and the sub-sampling PD can be viewed as a small non-zero current source at the output of the combined PD. Thus, as the PLL with a fractional divisor is locking, there is a non-zero steady-state phase difference input to the combined PD because of the output current offset caused by the sub-sampling PD.

Even though the combined PD can be used for a fractional-N PLL, there are some challenges brought by this PD. The combined PD essentially is a non-linear PD, so the modulated quantization error of the PLL will be folding back to lower frequencies and then degrades phase noise. In addition, the non-zero balanced phase difference of the PLL is inappropriate for some applications requiring small static phase errors.

# 2.3 Simulation-based verification of the Locking Issues in Sub-Sampling-based Phase Detectors and Robustness of the Combined Phase Detector

This section presents simulation-based evidence to demonstrate the locking issues in PLLs with sub-sampling-based phase detectors in contrast to the robustness of PLLs with tri-state PFDs. It will be shown that a PLL with the combined PD, which retains the frequency detecting capabilities of the tri-state PFD, is as robust as a PFD-based PLL.

Transient simulations were conducted on type II third-order PLLs using (a) an SSPD, (b) an FLL-assisted SSPD, (c) a conventional tri-state PFD, and (d) the combined PD. Verilog-A based behavioral models were used to describe the circuit blocks. The PLLs were driven by a reference frequency of 50MHz with the parameters set as follows: N=44;  $K_{VCO}=150MHz/V$ ; a loop filter consisting of a parallel capacitor 1.3pF and a resistor 12.6k $\Omega$  in series with a capacitor 31.7pF. A disturbance in the form of a current pulse is injected into the loop filter to measure the dynamics of the loop in various cases.

**Figure 2.5:** Interference robustness simulation results for PLLs with different types of phase detectors; an SSPD-only PLL loses lock; a PLL with an FLL-assisted SSPD reacquires lock, albeit after a long time  $(2.5\mu \text{s})$  in this example) during which the PLL is unlocked; a PLL with a PFD operates robustly for the same disturbance.

Fig. 2.5 shows the simulated transient of VCO control voltage in PLLs using (a) an SSPD, (b) an FLL-assisted SSPD, and (c) a tri-state PFD. The PD gains of the PLLs with the above PDs are set to the same value of  $K_{PD} = 0.25/(2\pi) (\text{mA/radian})$  so that they have the same loop response. After the disturbance occurs, the PLL using just the SSPD goes out of lock due to its narrow locking range given the lack of frequency detection capabilities. The PLL using the conventional tri-state PFD, however, is very robust to disturbances and remains locked, as shown by the simulation. In the PLL using an FLL-assisted SSPD, the FLL (dead-zone PFD) [6] is enabled only when the magnitude of the phase error is greater than  $\pi$  and is quiet while the phase error falls within the DZ. The lock-re-acquisition time of the PLL with the FLL-assisted SSPD is simulated to be  $2.5\mu s$ . For the same magnitude of the disturbance, a PLL with the conventional PFD is observed to recover to steady state as quickly as within  $0.4\mu s$ .

When the PLL with an FLL-assisted SSPD is pushed out of lock by a disturbance, the phase error needs to exceed  $\pi$  for the FLL to engage the relocking process. The associated lock-reacquisition time  $\Delta T$  can be estimated as follows. Due to the disturbance, there is an error voltage  $\Delta V(t)$  on the VCO control voltage; this voltage change leads to a phase change  $\Delta \phi_{\rm VCO}$  equal to the integral of  $2\pi K_{\rm VCO}\Delta V(t)$ . The phase error at the phase detector,  $\Delta \phi_{\rm REF}$ , is  $\Delta \phi_{\rm VCO}/N$  and reaches a magnitude of  $\pi$  after a time  $\Delta T$  calculated from:

$$\left| \int_0^{\Delta T} \frac{K_{\text{VCO}} \Delta V(t)}{N} dt \right| > 0.5, \tag{2.1}$$

**Figure 2.6:** Simulated results of a PLL using an FLL-assisted PFD subjected to disturbances of different strengths

If  $\Delta V(t)$  is approximated to be constant, the lock-re-acquisition time can be computed as

$$\Delta T = 0.5 \frac{N}{K_{\text{VCO}} \Delta V}.$$

(2.2)

Eq. (2.2) shows that the lock re-acquisition time depends on the strength of the disturbance; the PLL will have a longer lock re-acquisition time for a weaker disturbance<sup>1</sup>, because it takes more time for the magnitude of the phase error to accumulate to  $\pi$ . This phenomenon was verified using simulations. The PLL with the FLL-assisted SSPD was observed to have a simulated lock-reacquisition time of  $2.5\mu s$  for a stronger disturbance while it is  $4\mu s$  for a weaker disturbance as shown in Fig. 2.6.

<sup>&</sup>lt;sup>1</sup>Note that the disturbance has to remain sufficiently large to unlock the PLL.

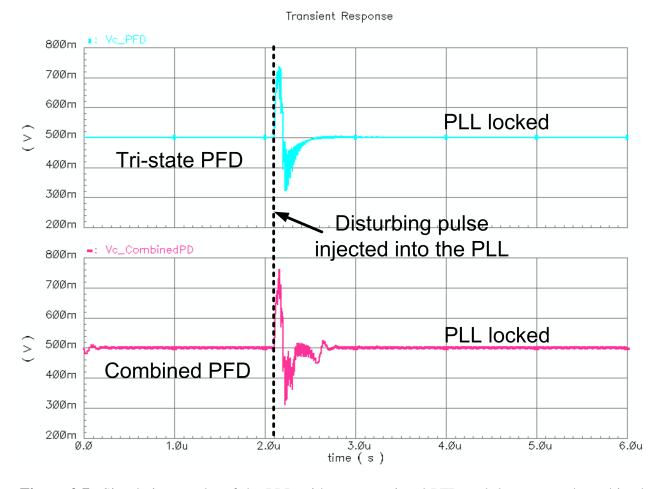

**Figure 2.7:** Simulation results of the PLL with a conventional PFD and the proposed combined PD under the disturbance

A comparison is made for PLLs with a tri-state PFD and the proposed combined PD by adding an SSPD to the PFD. Transient response of their control voltages to a disturbance is shown in Fig. 2.7. The simulation results show that the PLLs with the PFD and the combined PD have a similar robustness when subjected to disturbances. Due to the retention of the frequency detecting feature of a conventional tri-state PFD, a PLL using the combined PD is prevented from losing lock and thus the long lock-re-acquisition time (as in the case of an FLL-assisted SSPD) can be avoided.

Figure 2.8: Phase domain model for the PLL with the combined phase detector

#### 2.4 Noise Analysis for the Combined Phase Detector

Now it is demonstrated that a combined phase detector has a superior noise performance than a tri-state PFD. The phase domain model of the PLL with a combined PD in locked condition is shown in Fig. 2.8.  $H_{LF}(jf)$  is the transfer function of the loop filter,  $K_{VCO}$  is the frequency tuning gain of the VCO, and  $K_{PD,PFD}$  is the gain of the tri-state PFD/CP. The gain of the sub-sampling PD,  $K_{PD,SSPD}$ , is given by:

$$K_{\text{PD,SSPD}} = \frac{\overline{\Delta i_{SSPD}}}{\Delta \phi_{\text{REF}}} = N \cdot \frac{\overline{\Delta i_{SSPD}}}{\Delta \phi_{\text{VCO}}}$$

$$= N \left( \frac{S}{\omega_{\text{VCO}}} G_{\text{m}} \right) \frac{T_{\text{pulse}}}{T_{\text{REF}}} = N \cdot K_{S} \cdot \frac{1}{K}$$

(2.3)

where  $\overline{\Delta i_{SSPD}}$  is the averaged output current of the sub-sampling phase detector and S is the slope of the VCO signal around the SSPD's operating point.  $S = A_{\text{VCO}}\omega_{\text{VCO}}$  and  $K_S = A_{\text{VCO}}G_{\text{m}}$  when locked around the zero-crossing of the VCO.

The gain of the combined phase detector is now  $K_{\text{PD,comb}} = K_{\text{PD,PFD}} + K_{\text{PD,SSPD}}$ . Under the condition to maintain the frequency detecting ability derived in section 2.2, the maximum gain of the combined phase detector around the zero-timing-error point can be expressed by:

$$K_{\text{PD,comb,MAX}} = \frac{\overline{I_{\text{out}}}}{\Delta \phi_{\text{REF}}} = \frac{I_{\text{CP}}}{2\pi} + \left(\frac{3I_{\text{CP}}}{4N}\right) \frac{T_{\text{REF}}}{T_{\text{VCO}}}$$

$\approx 5.7 \cdot \frac{I_{\text{CP}}}{2\pi} = 5.7 \cdot K_{\text{PD,PFD}}.$  (2.4)

Using the phase-domain model, the power spectral density of the output phase noise of the PLL,  $S_{\phi,n,out}$ , can be derived as:

$$S_{\phi,n,out} = \left| \frac{1}{1 + L(jf)} \right|^2 S_{\phi,n,VCO} + \left| \frac{L(jf) \cdot N}{1 + L(jf)} \right|^2 S_{\phi,n,REF}$$

$$+ \left| \frac{L(jf) \cdot N}{1 + L(jf)} \right|^2 \frac{1}{K_{PD,comb}^2} \left( S_{i,n,PFDCP} + S_{i,n,SSPD} \right)$$

(2.5)

where  $S_{\phi,n,\text{block}}$  is the noise power spectral density from a specific 'block' and L(jf) is the loop transfer function of the PLL, equal to  $K_{\text{PD,comb}} \cdot H_{\text{LF}}(jf) \cdot (K_{\text{VCO}}/(jf))/N$ .

If the PFD/CP noise is decided by the thermal noise current of the CP, the output power spectral density of the PFD/CP can be expressed by:

$$S_{i,n,PFDCP} = 4kT\gamma \left(\frac{gm_{CP}}{I_{CP}}\right)I_{CP}\left(\frac{T_{idle}}{T_{REF}}\right)$$

where  $gm_{CP}$  is the transconductance of the CP current sources and  $(T_{idle}/T_{REF})$  is the duty cycle of switching the CP on in a steady state to avoid the dead zone.

The main contributors to the noise of the SSPD are the sampling switch and the transconductor. Timing errors due to the noise in the pulse generator changes pulse width which marginally changes the gain of the SSPD which is inconsequential. The power spectral density of the total output current noise of the SSPD can be derived to be:

$$S_{i,n,\text{SSPD}} = \frac{\overline{v_{\text{n,samp}}^2}}{f_{\text{REF}}/2} \cdot \frac{G_{\text{m}}^2}{K^2} + \frac{S_{i,n,\text{Gm}}}{K}$$

(2.6)

where  $\overline{v_{n,samp}^2}$  is the variance of the noise voltage at the output of the sampler consisting of the sampling switch and the capacitor  $C_{samp}$ ;  $S_{i,n,Gm}$  is the power spectral density of the current noise of the transconductor. Noted that  $S_{i,n,Gm}$  is divided by K rather than  $K^2$  because the current noise of the transconductor is sampled by a pulse signal with a duty cycle (1/K) so that the noise has an extra aliasing factor of K to the output. Assuming white noise,  $\overline{v_{n,samp}^2}$  is  $(kT/C_{samp})$  and  $S_{i,n,Gm} = 8kT\gamma G_m$ .

In the combined PD, the circuit noise sources from the SSPD undergo an additional attenuation by K in (2.6) due to the gating with a narrow pulse width when compared to the tri-state PFD/CP's noise sources. Due to this attenuation, the contribution from the SSPD to the noise at the output of the combined PD is negligible and thus the total output noise is close to  $S_{i,n,PFDCP}$ . For example, with  $f_{REF}$ =50MHz,  $C_{samp}$  =20fF,  $G_{m}$ =0.5mA/V and K=44 $\pi$ ,  $S_{i,n,SSPD}$  is -247.3 dBc/Hz while  $S_{i,n,PFDCP}$ =-238.6 dBc/Hz given  $I_{CP}$ =0.25mA,  $(gm_{CP}/I_{CP})$ =10 and  $(T_{idle}/T_{REF})$  = 5%.

Because of the addition of the SSPD, the total gain of the combined PD,  $K_{PD,comb}$ , is larger than the gain of the PFD/CP,  $K_{PD,PFD}$ . Therefore, compared with the PFD/CP, the combined PD has smaller input-referred noise because of the larger gain, but similar output noise. From (2.4),

it can be derived that the combined PD's gain can be up to 5.7 times (15dB) higher than the gain of the tri-state PFD/CP. This increased gain of the combined PD without any additional significant noise increase results in up to 15dB smaller noise contributions from the phase detector to the PLL's noise (referred to its input).

For a PLL design with a given loop transfer function L(jf), the noise contributions in (2.5) from the VCO and the reference remain unaltered with the choice of a phase detector. Assuming the same VCO and reference frequency and loop filter design, the total phase detector's gain is also largely unaltered. Comparing a combined PD with a conventional PFD/CP given the same total phase detector's gain, the output noise of the combined PD dominated by its PFD/CP's noise is smaller than the noise of the conventional PFD/CP because the combined PD has smaller PFD/CP's gain and CP current while most gain of the combined PD is provided by the SSPD. As a result, the use of the combined PD gives smaller noise contribution to the PLL than the conventional tri-state PFD/CP used alone.

# 2.5 Circuit Design of a Low In-band Phase Noise PLL with Robust Operation

Based on the analysis presented above, a PLL using the proposed combined phase detector can maintain the disturbance robust operation of a PFD-based PLL while offering superior jitter performance similar to SSPD-based PLLs. These unique advantages of the proposed combined phase detector have been demonstrated with an integer-N PLL prototype targeted at clock synthesis or

two-step PLL (cascaded PLL) applications [8,9]. It operates with a reference frequency of 50MHz and provides an output at 2.2GHz with a loop bandwidth of 5MHz.

The phase domain model for the PLL with combined phase detector (see Fig. 2.8) is the same as for a classical integer-N PLL but with a lower noise phase detector. The PLL parameters such as  $K_{\text{PD,comb}}$ ,  $K_{\text{VCO}}$ , as well as the loop filter parameters can be determined for a given reference frequency, output frequency and settling behavior using a classical design procedure as outlined e.g. in [4]. Once these parameters are determined, the phase detector circuit level design proceeds as explained below.

#### 2.5.1 Combined Phase Detector

To retain the frequency detecting ability of a tri-state PFD, the maximum output current of the SSPD in the combined PD needs to be smaller than  $3I_{CP}/(4N)$  as discussed in section 2.2. Leaving some margins for error in the gain of the SSPD, the maximum output current of the SSPD is chosen to be:

$$\overline{\Delta i_{\text{SSPD,max}}} = \frac{K_S}{K} = \frac{2I_{\text{CP}}}{\pi N} < \frac{3I_{\text{CP}}}{4N}$$

(2.7)

Now, the total gain of the combined PD can be expressed as:

$$K_{\text{PD,comb}} = \frac{I_{\text{CP}}}{2\pi} + \frac{NK_S}{K} = \frac{5I_{\text{CP}}}{2\pi}$$

(2.8)

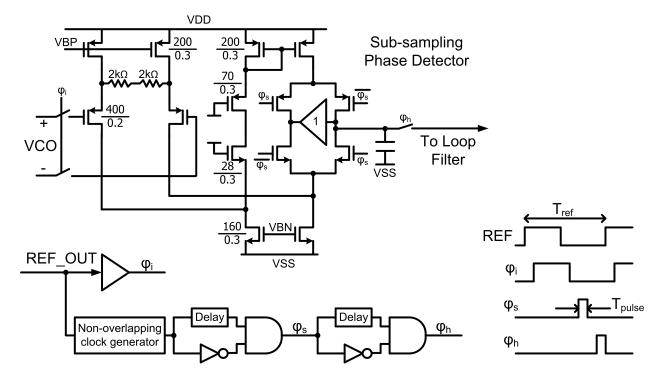

**Figure 2.9:** Circuit implementation of the sub-sampling phase detector. The units for W and L are  $\mu$ m.

Given  $K_S = A_{VCO}G_m$ , the value of the transconductor can be calculated as:

$$G_{\rm m} = \frac{4}{5} \times \frac{K_{\rm PD,comb}}{A_{\rm VCO}} \times \frac{K}{N}$$

(2.9)

Assuming  $K_{\text{PD,comb}} = \frac{1.25}{2\pi} (\text{mA})$ ,  $A_{\text{VCO}} = 1\text{V}$  differential and the gain reduction factor of K is chosen to be  $\pi N$ , the value of the transconductor,  $G_{\text{m}}$ , is equal to 0.5 (mA/V) and  $I_{\text{CP}} = 0.25 (\text{mA})$ . Given the chosen parameters, the overall in-band phase noise contributed by the band-limited

Figure 2.10: Detailed implementation of the pulse generator used in the sub-sampling PD

SSPD noise and PFD/CP noise is given by:

$$\mathcal{L}_{\text{inband}} = \frac{N^2}{2} \left( \frac{S_{i,n,\text{SSPD}} + S_{i,n,\text{PFDCP}}}{K_{\text{PD,comb}}^2} \right) = \frac{N^2}{2} \left( \frac{16S_{i,n,\text{SSPD}}}{25K_{\text{PD,SSPD}}^2} + \frac{S_{i,n,\text{PFDCP}}}{25K_{\text{PD,PFD}}^2} \right)$$

$$= \frac{16}{25} \left( \frac{kT}{C_{\text{samp}}} \cdot \frac{1}{A_{\text{VCO}}^2} \cdot \frac{1}{f_{\text{REF}}} + \frac{4kT\gamma}{G_{\text{m}}} \cdot \frac{K}{A_{\text{VCO}}^2} \right) + \frac{8\pi^2 kT\gamma N^2}{25I_{\text{CP}}} \left( \frac{gm_{\text{CP}}}{I_{\text{CP}}} \right) \left( \frac{T_{\text{idle}}}{T_{\text{REF}}} \right) (2.10)$$

With  $f_{\text{REF}}$ =50MHz, N=44,  $C_{\text{samp}}$  =20fF,  $(gm_{\text{CP}}/I_{\text{CP}})$ =10 and  $(T_{\text{idle}}/T_{\text{REF}})$  = 5%, the overall inband noise floor is as low as -134.2 dBc/Hz.

The detailed transistor implementation of the sub-sampling phase detector is shown in Fig. 2.9. A sample-and-hold filter is used to reduce the reference ripple caused by the sub-sampling phase detector because it generates a SINC function with a notch at reference frequency [10]. Fig. 2.10 shows the detailed circuits of the pulse generator programming the pulse width and delay by changing the delay cells between two inputs of the AND gates. In addition, a unity-gain buffer is inserted in the transconductor to maintain the same voltages at the current sources' drain nodes and at the capacitor of loop filter. The buffer reduces the output current ripple due to charge sharing between these nodes during switching.

### 2.5.2 Voltage Controlled Oscillator, Programmable Divider and Loop Filter

The circuit implementation of the VCO is shown in Fig. 2.11. An inverter-based LC-VCO is chosen to avoid the flicker noise contribution from the bias current source [11]. The VCO uses a 6-bit control for setting the capacitance of the capacitor bank to tune the frequency coarsely and standard MOS varactors for fine-tuning the frequency. The VCO was designed to have a

frequency tuning gain ( $K_{VCO}$ ) of 150MHz/V (fine-tuning) and a tuning range from 1.9GHz to 2.3GHz (including coarse tuning). The simulated phase noise is -112dBc/Hz at 1MHz offset and the used Q of the inductor is 6.6 at 2.2GHz.

The block diagram of the programmable divider is shown in Fig. 2.12. The divider has a ripple structure similar to a truly modular divider which is composed of a chain of divide-by-2 or 3 modules [12] [13]. Unlike [12], the cell in this implementation provides an additional modulus of 4 in addition to 2 and 3 to extend the programmable range. This block was fully synthesized with standard logic cells.

As shown in Fig. 2.13, the on-chip loop filter consists of a series resistor with the value of

**Figure 2.11:** Circuit implementation of the LC-VCO used in the PLL. The units for W and L are  $\mu$ m.

Figure 2.12: Block diagram of the frequency divider

12.6k $\Omega$ , a series capacitor of 31.7pF and a parallel capacitor of 1.3pF. These small capacitor sizes in the loop filter can be implemented on-chip with MOM capacitors to avoid leakage. A unity-gain buffer is placed between the loop filter and the VCO to isolate the loop filter from pulling by the large VCO swing since only a small capacitance is used in loop filter for wide loop bandwidth. This buffer acts as a first-order filter that increases the order of the loop filter; its noise only impacts the loop filter noise contribution which is not a significant noise contribution in the PLL.

## 2.6 Experimental Results

The proposed PLL was implemented in a 65nm digital low leakage CMOS process. Fig. 2.14 shows the die photo of the chip. It occupies an area of 0.24mm<sup>2</sup> (without bond-pads) while its

Figure 2.13: Loop filter implementation

loop filter area is  $0.04\text{mm}^2$ . The circuits draw 8mA (excluding the  $50\Omega$  output buffers) of which 3mA is drawn by the LC-VCO. The prototyped PLL can operate with three different modes for the phase detector: tri-state PFD only, sub-sampling PD only, and combined PD.

Figure 2.14: Die photo of the PLL

The measured phase noise and tuning curves of the VCO are shown in Fig. 2.15. The measured phase noise is -112dBc/Hz at 1MHz offset which matches the simulation. The measured frequency tuning range of the VCO is from 2.04GHz to 2.22GHz for the cap-bank setting of 6'b010110 and

**Figure 2.15:** (a) Measured and simulated phase noise spectrum of the VCO (b) Measured tuning curve of the LC-VCO for three cap-bank settings

**Figure 2.16:** Measured phase noise spectrum of the PLL when operating with a reference frequency of 50MHz and a divisor of 41 and output frequency of 2.05GHz (blue trace lower bandwidth and lower peaking) and divisor of 44 and output frequency of 2.2GHz (red trace higher bandwidth and with higher peaking)

**Figure 2.17:** Measured reference spurs of the PLL when operating at 2.2GHz

using coarse tuning the VCO output frequency range is from 2.03GHz to 2.27GHz. The PLL was driven with a 50MHz crystal reference source [14]. The output frequency can be set from 2.05GHz to 2.2GHz in steps of 50MHz by changing the frequency division ratio with the above cap-bank setting. The in-band phase noise level is very consistent across the output frequency range. Fig. 2.16 shows the output phase noise spectrum of the PLL, measured with an Agilent E4446 Spectrum Analyzer, at two different output frequencies, 2.05GHz and 2.20GHz respectively.

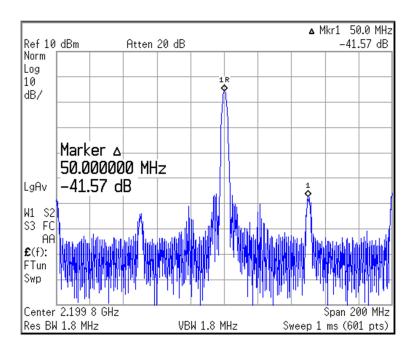

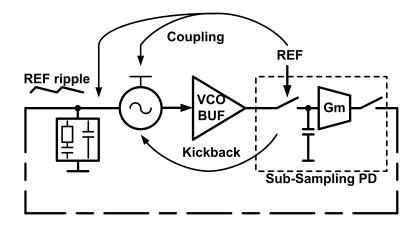

The reference spurs in the PLL output have been measured in Fig. 2.17. The relatively large reference spur comes from the kickback in a sub-sampling PD [15] and coupling from reference signal to VCO supply through the ESD circuitry. <sup>2</sup>

Larger reference spurs were observed in the sub-sampling PLL because the spurs are not sup-

<sup>&</sup>lt;sup>2</sup>The dependence of the reference spur on the interaction between the VCO and SSPD discussed in [15] was also observed in the measurement by changing the size of the inverter-based buffer between the VCO and SSPD. The spur reduction technique adopted for an SSPD can be applied into the combined PD.

Figure 2.18: Root causes to reference spurs in a sub-sampling PLL

pressed by its wide loop bandwidth. The reference spurs of a sub-sampling PLL are usually generated by the ways shown in Fig. 2.18. The first one is the coupling from input reference to the supply or the control voltage of the VCO. But, it can be decreased by careful layout and good isolation between critical blocks. Secondly, the reference spurs are due to the leakage of loop filter which requires the sub-sampling PD to provide compensating current for its pulse-controlled duration and then leads with a large ripple on the control voltage of the VCO. The reference ripple can be reduced by implementing the loop filter with a sample-and-hold filter or MOM capacitors for few reference disturbances from the sub-sampling PD to loop filter.

The reference spurs are also caused by the kickback from the sub-sampling PD through a VCO buffer and then to the VCO. It is a serious problem to a sub-sampling PLL because the VCO output is constantly sampled by the reference signal in the SSPD. Thus, the reference spurs would be generated by directly modulating the VCO output with the reference disturbance. In addition, non-ideal effects of the sampling switch such as charge injection or clock feed-through and the VCO load change caused by the sampling operation can also influence the VCO output and make

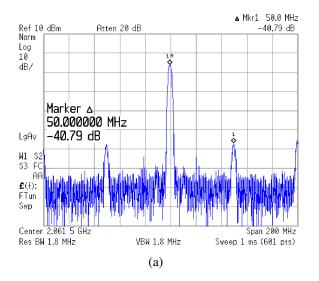

**Figure 2.19:** (a) Measured VCO output spectrum while the SSPD's output is disabled (b) Measured reference spurs by decreasing the driving setting of the buffer between the VCO and SSPD as  $f_{\text{REF}}$ =40MHz

reference spurs become large. The reference spurs is reduced by increasing the isolation between the SSPD and VCO. The impact of the kickback was observed by disabling the SSPD output, but keeping the VCO output being disturbed by the SSPD. In this case, the measured spurs at the VCO output were shown in Fig. 2.19(a). Besides, while the PLL is locking, smaller reference spurs were measured in Fig. 2.19(b) by changing the size of the inverter-based VCO buffer to increase isolation as well as lowering input reference frequency to reduce kickback.

The reference spurs were also observed for different reference swings. The reference swing is adjusted by the digitally controlled strength of the reference buffer as Fig 2.20(a). While changing the reference swing, the worst reference spurs were measured in Fig. 2.20(b) showing that larger reference swing leads to poorer reference spurs because it makes the kickback become more serious. It is noted that there may be large variations on the measured reference spurs given the certain reference swing because the spurs are more related with the edges of reference and VCO

**Figure 2.20:** (a) Circuit diagram of the reference buffer with the digitally controlled strength (b) Measured reference spurs for different reference swings

signals as discussed in [15]. In fact, to alleviate the problem of high reference spurs caused by the sub-sampling PD, the techniques proposed in [15] can also be applied into future versions of the combined PD.

## 2.6.1 Robustness of the Phase Detector to Supply Voltage Disturbances

It has been experimentally verified that a PLL with the proposed combined PD has a better rejection to disturbances on the power supply compared to a PLL with a sub-sampling PD alone.

A PLL integrated with digital circuits may experience periodic disturbances through the substrate, the power supply or other means. In the experimental set-up, these disturbances were collectively modeled as periodic impulses to the supply voltage of the VCO. Periodic impulses were chosen to mimic the effect of digital circuits and the supply voltage of the VCO was chosen because the sub-sampling PD is most sensitive to phase change of VCO's output.

The disturbances are generated by applying a pulse signal to VCO supply through a large ac-

**Figure 2.21:** Effect of VCO supply voltage disturbances on the PLL's operation; using the combined PD the PLL can sustain substantial disturbances; using the sub-sampling PD only, the PLL loses lock as soon as the disturbances are applied.

coupling capacitor. Fig. 2.21 shows the effect of these supply voltage disturbances on a PLL using the combined PD versus the sub-sampling PD alone. For supply disturbances with the peak-to-peak swing of around 100mV, the control voltage of the VCO in a PLL with the combined PD shows periodical ripples, but returns to the original value. However, the control voltage of VCO in a PLL with the sub-sampling PD alone jumps to another value which makes the PLL lose lock after turning on the disturbances.

Fig. 2.22 shows another result confirming the superior immunity of the PLL with a combined PD to disturbances. While supply disturbances are present, the PLL is switched between two

**Figure 2.22:** While operating with disturbances on the VCO supply, the PD of the PLL is switched between the combined and sub-sampling-only operation mode; in sub-sampling-only mode, the PLL loses lock, but it recovers as soon as switching back to combined operation mode.

modes of phase detection: one with the combined PD and the other with sub-sampling PD only. When the phase detection mechanism is changed from the combined PD to the sub-sampling PD, the control voltage of VCO jumps to another value and the PLL looses lock due to the disturbances on the VCO's supply. As soon as the PFD is reactivated and the PLL operates with the combined PD again, the control voltage of the VCO goes back to the original value and the PLL locks correctly.

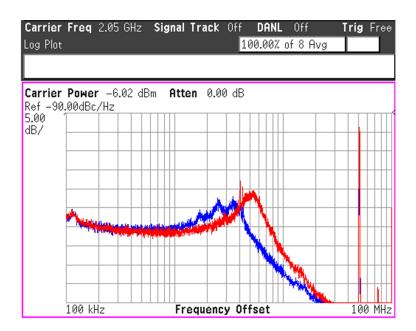

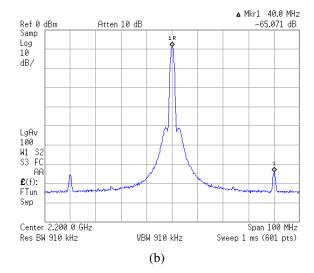

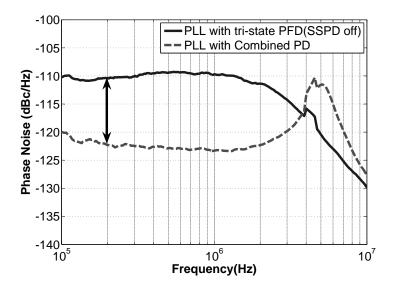

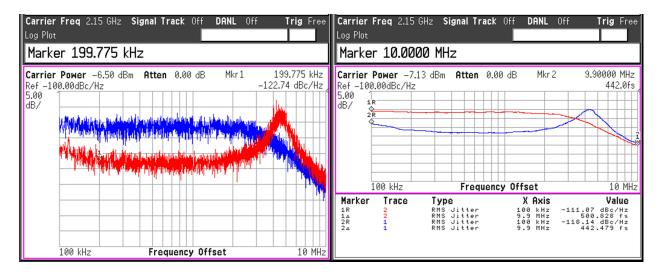

#### 2.6.2 Low In-band Phase Noise

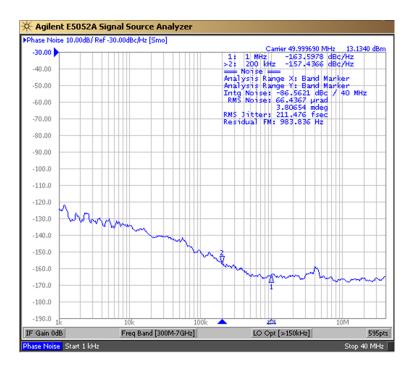

The output phase noise spectra of the PLL with the combined phase detector and with the tristate PFD alone (i.e. the sub-sampling phase detector is turned off) are measured with an Agilent

**Figure 2.23:** Measured phase noise spectrum of the PLL when operating at 2.2GHz with the combined phase detector and the tri-state phase detector only

E5052A Signal Analyzer and compared in Fig. 2.23. By turning on the sub-sampling phase detector, the in-band phase noise is reduced from -110dBc/Hz to -122dBc/Hz at a 200-kHz frequency offset. The measured RMS jitter shows an improvement from 564fs to 448fs (integrated from 100kHz to 10MHz) and from 649fs to 484fs (integrated from 10kHz to 40MHz). The in-band phase noise reduction is 12dB, even though the phase detector's gain increase suggests a possible improvement up to 14dB[see (2.4) and (2.8)]. However, in this measurement when operating with the combined phase detector, the in-band noise becomes dominated by the reference phase noise, and at that point the increased phase detector gain has no more effect [see (2.5)].

The reference noise from the used 50MHz CPRO XTAL was measured by -157dBc/Hz at 200 kHz in Fig. 2.24; this results in an in-band phase noise of -124dBc/Hz at 200 kHz with a divisor of 44. The measured noise level is -122dBc/Hz; the 2dB increase can be attributed to the noise contributed by the on-chip reference buffer. In addition, a set of measurements was done by using

**Figure 2.24:** Measured phase noise spectrum of the used crystal reference source showing - 157.4dBc/Hz at 200kHz and -163.6dBc/Hz at 1MHz.

increasing pulse widths (i.e. reducing K) and thus increased the combined phase detector's gain; the in-band phase noise initially reduced as expected; but it stopped reducing at a -122dBc/Hz level most likely due to the contribution of the reference noise given its measured level as calculated above since the PD's noise contribution for large pulse widths is not dominated to the in-band phase noise.

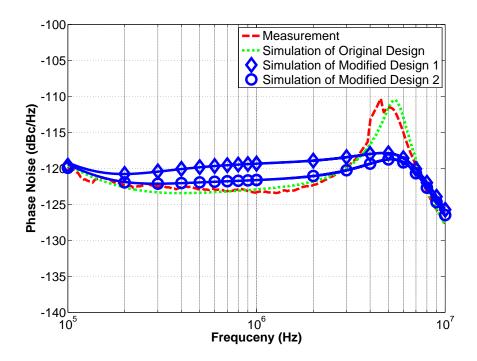

The noise peaking observed in Fig. 2.23 at the edge of the loop bandwidth when operating with the combined phase detector is caused by the reduced phase margin due to an increased loop bandwidth while the sub-sampling phase detector is active<sup>3</sup>. The peaking observed in measurement is seen in simulation also. Fig. 2.25 shows a comparison of the measured phase noise spectrum

<sup>&</sup>lt;sup>3</sup>The PLL was required to operate both with a combined PD and tri-state PFD in order to demonstrate the phase noise improvement. When the PLL is switched to using the combined PD, its phase margin degrades, resulting in noise peaking. However, in a real design, the PLL will only be operating with a combined PD. The loop bandwidth and phase margin requirements will be known a-priori and the issue of noise peaking can be avoided.

**Figure 2.25:** A comparison between the measured and simulated phase noise spectrum of the PLL using the combined phase detector, and the simulated phase noise spectrum of the PLL with a modified loop filter to improve the loop's phase margin.

with simulated phase noise spectrum of the PLL. The peaking can be removed in a redesign by changing the loop filter so that there is a better phase margin for the PLL. A simulation was done with a first modified loop filter changing the loop's pole and zero so that the PLL with the combined PD has a 46-degree phase margin and no peaking. The modified loop filter has a series RC branch with a series resistor of  $9.2k\Omega$  and a series capacitor of 69.1pF, and a parallel capacitor of 0.17pF. A second design example uses a modified loop filter with a series resistor of  $9.2k\Omega$  and a series capacitor of 69.1pF and a parallel capacitor of 0.5pF for a 42-degree phase margin but lower inband noise. Fig. 2.25 shows the simulated phase-noise spectrum of the PLLs with the modified loop filters which maintain excellent in-band phase noise performance. The RMS jitter integrated

from 10kHz to 10MHz is 448fs in the measurement, 447fs in the simulation of the original design, 339fs for the modified design 1 and 294fs for the modified design 2.

**Figure 2.26:** Measured phase noise spectrum of the PLL with the combined PD and the tri-state PFD only as the output frequency of 2.15GHz

With the divisor of 43, the output spectrum of the PLL with the combined PD and the tri-sate PFD was measured in Fig. 2.26. By changing from the tri-state PFD to the combined PD, the measured in-band phase noise is reduced from -112dBc/Hz to -123dBc/Hz at a 200-kHz frequency offset and the measured RMS jitter shows an improvement from 501fs to 442fs (integrated from 100kHz to 10MHz). Compared with operating at 2.2GHz, the in-band phase noise of the PLL at 2.15GHz is a little better because the lower division ratio reduces the noise contribution from the phase detector and reference.

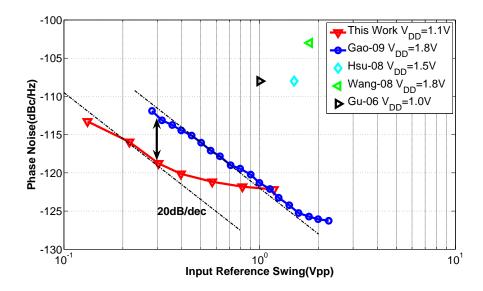

The in-band phase noise level is a function of the amplitude of the applied reference signal [6, 7]. The measured in-band phase noise is plotted as a function of the peak-to-peak reference amplitude in Fig. 2.27 while keeping the supply voltage of the chip constant at 1.1V; the reference buffer in the design has a simulated small signal gain of 8.6x when operating from 1.1V; a 20dB/dec

**Figure 2.27:** Measured in-band phase noise vs reference swing; the presented PLL operates at 1.1 V, whereas Gao-09 [6] operates at 1.8V; for Hsu-08 [16], Wang-08 [17] and Gu-06 [18] the peak-to-peak reference swing has been assumed to be equal to the respective chip supply voltage.

improvement is observed until the phase-noise stops improving for large reference swings which result in slewing of the output reference buffer.

In comparison with the PLL in [6], operating with a 1.8V supply, the PLL has a 6dB better inband phase noise at the reference amplitudes lower than 300mV. Due to a smaller available supply voltage in 65nm, the PLL cannot use the same large reference signal as in the 180nm technology. Even with a larger available reference signal, the PLL achieves an inband phase noise comparable to [6, 15]. A detailed comparison of this work with other implementations is summarized in Table 2.1.

## 2.7 Conclusions

This chapter proposes a combined PD for PLLs with robust operation under disturbances while offering low in-band phase noise and low jitter. The combined PD uses a low noise sub-sampling PD in parallel with a conventional tri-state PFD in such way that it retains the frequency locking feature of a tri-state PFD while obtaining the superior in-band phase noise performance of a sub-sampling PD.

Simulation-based comparison of an SSPD, an FLL-assisted SSPD, a conventional tri-state PFD and the combined PD shows that a PLL using an SSPD is sensitive to any disturbance, a PLL using an FLL-assisted SSPD will regain lock but after a long delay of being unlocked, while a PLL using the combined PD is immune to disturbances and quickly reaches steady state after disturbances, similarly to PLLs with traditional PFDs.

Measurement-based comparison of the robustness of the combined PD and the SSPD has been made and the combined PD was experimentally shown to be more robust. The measured in-band phase noise of the PLL is improved from -110dBc/Hz to -122dBc/Hz at 200kHz between the conventional PFD and the combined PD.

Table 2.1:

Performance comparison table

|                             |            | [9]        | [15]         | [16]         | [18]         | [19]         | [50]       | [21]         | [22]         |

|-----------------------------|------------|------------|--------------|--------------|--------------|--------------|------------|--------------|--------------|

| Output Frequency 2          | 2.2GHz     | 2.21GHz    | 2.21GHz      | 3.67GHz      | 3.125GHz     | 2.08GHz      | 3.1GHz     | 4GHz         | 2.3GHz       |

| Reference Frequency 5       | 50MHz      | 55.25MHz   | 55.25MHz     | 50MHz        | 62.5MHz      | 130MHz       | 108MHz     | 40MHz        | 48MHz        |

| Supply Voltage              | 1.1V       | 1.8V       | 1.8V         | 1.5V         | 1V           | 1.2V         | 1.2V       | 1.2V         | 1.8V         |

| Inband Phase Noise -12      | -122dBc/Hz | -126dBc/Hz | -121dBc/Hz   | -108dBc/Hz   | -108dBc/Hz   | -119dBc/Hz   | -110dBc/Hz | -105dBc/Hz   | -112dBc/Hz   |

| @Maximum A <sub>REF</sub> @ | @ 200kHz   | @ 200kHz   | @ 200kHz     | @ 400kHz     | @ 100kHz     | @ 1.4MHz     | @100kHz    | @ 200kHz     | @ 50kHz      |

| Reference Spur -4           | -41.6dBc   | -46dBc     | -80dBc       | -65dBc       | ı            | -47.8dBc     | ı          | -71dBc       | -55dBc       |