# Accelerating Similarly Structured Data

Lisa Wu

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

## COLUMBIA UNIVERSITY

2014

### $\bigcirc 2014$

Lisa Wu All Rights Reserved

## ABSTRACT

## Accelerating Similarly Structured Data

### Lisa Wu

The failure of Dennard scaling [Bohr, 2007] and the rapid growth of data produced and consumed daily [NetApp, 2012] have made mitigating the dark silicon phenomena [Esmaeilzadeh *et al.*, 2011] and providing fast computation for processing large volumes and expansive variety of data while consuming minimal energy the utmost important challenges for modern computer architecture. This thesis introduces the concept that grouping data structures that are previously defined in software and processing them with an accelerator can significantly improve the application performance and energy efficiency.

To measure the potential performance benefits of this hypothesis, this research starts out by examining the cache impacts on accelerating commonly used data structures and its applicability to popular benchmarks. We found that accelerating similarly structured data can provide substantial benefits, however, most popular benchmark suites do not contain shared acceleration targets and therefore cannot obtain significant performance or energy improvements via a handful of accelerators. To further examine this hypothesis in an environment where the common data structures are widely used, we choose to target database application domain, using tables and columns as the similarly structured data, accelerating the processing of such data, and evaluate the performance and energy efficiency. Given that data partitioning is widely used for database applications to improve cache locality, we architect and design a streaming data partitioning accelerator to assess the feasibility of big data acceleration. The results show that we are able to achieve an order of magnitude improvement in partitioning performance and energy. To improve upon the present ad-hoc communications between accelerators and general-purpose processors Vo et al., 2013, we also architect and evaluate a streaming framework that can be used for the data partitioner and other streaming accelerators alike. The streaming framework can provide at least 5GB/s per stream per thread using software control, and is able to elegantly handle interrupts and context switches using a simple save/restore. As a final evaluation of this hypothesis, we architect a class of domain-specific database processors, or Database Processing Units (DPUs), to further improve the performance and energy efficiency of database applications. As a case study, we design and implement one DPU, called Q100, to execute industry standard analytic database queries. Despite Q100's sensitivity to communication bandwidth on-chip and off-chip, we find that the low-power configuration of Q100 is able to provide three orders of magnitude in energy efficiency over a state of the art software Database Management System (DBMS), while the high-performance configuration is able to outperform the same DBMS by 70X.

Based on these experiments, we conclude that grouping similarly structured data and processing it with accelerators vastly improve application performance and energy efficiency for a given application domain. This is primarily due to the fact that creating specialized encapsulated instruction and data accesses and datapaths allows us to mitigate unnecessary data movement, take advantage of data and pipeline parallelism, and consequently provide substantial energy savings while obtaining significant performance gains.

# **Table of Contents**

| Lis      | st of | Figures                                     | iv  |

|----------|-------|---------------------------------------------|-----|

| Lis      | st of | Tables                                      | vii |

| 1        | Intr  | oduction                                    | 1   |

|          | 1.1   | Architectural Challenges                    | 2   |

|          | 1.2   | Accelerating Memory Operations              | 3   |

|          | 1.3   | Big Data Acceleration                       | 4   |

|          | 1.4   | Contributions                               | 5   |

|          | 1.5   | Thesis Outline                              | 6   |

| <b>2</b> | Cac   | he Impacts of Datatype Acceleration         | 7   |

|          | 2.1   | Architecture of ADPs                        | 7   |

|          | 2.2   | Evaluation of ADPs                          | 8   |

|          |       | 2.2.1 Instruction Delivery                  | 9   |

|          |       | 2.2.2 Data Delivery                         | 12  |

|          | 2.3   | Summary of Findings on ADPs                 | 15  |

| 3        | Acc   | eleration Targets                           | 17  |

|          | 3.1   | Profiling of Benchmark Suites               | 17  |

|          | 3.2   | Results and Analysis                        | 18  |

|          | 3.3   | Summary of Findings on Acceleration Targets | 19  |

| 4        | Har | rdware Accelerated Range Partitioning                  | <b>21</b> |

|----------|-----|--------------------------------------------------------|-----------|

|          | 4.1 | Data Partitioning is Important                         | 22        |

|          | 4.2 | Partitioning Background                                | 23        |

|          | 4.3 | Software Partitioning Evaluation                       | 26        |

|          | 4.4 | HARP Accelerator                                       | 29        |

|          |     | 4.4.1 Instruction Set Architecture                     | 29        |

|          |     | 4.4.2 Microarchitecture                                | 30        |

|          | 4.5 | Evaluation Methodology                                 | 31        |

|          | 4.6 | Evaluation Results                                     | 32        |

|          | 4.7 | Design Space Exploration                               | 36        |

|          | 4.8 | Summary of Findings on HARP                            | 39        |

| <b>5</b> | ΑH  | Iardware-Software Streaming Framework                  | 40        |

|          | 5.1 | HARP System Integration                                | 41        |

|          | 5.2 | Streaming Framework                                    | 42        |

|          |     | 5.2.1 Instruction Set Architecture                     | 43        |

|          |     | 5.2.2 Microarchitecture                                | 44        |

|          | 5.3 | Evaluation Methodology                                 | 45        |

|          | 5.4 | Evaluation Results                                     | 46        |

|          | 5.5 | Summary of Findings on Streaming Framework             | 47        |

| 6        | Q10 | 00: A First DPU                                        | 48        |

|          | 6.1 | Q100 Instruction Set Architecture                      | 49        |

|          | 6.2 | Q100 Microarchitecture $\ldots$                        | 52        |

|          | 6.3 | Q100 Tile Mix Design Space Exploration                 | 56        |

|          | 6.4 | Q100 Communication Needs                               | 59        |

|          |     | 6.4.1 On-chip bandwidth constraints                    | 60        |

|          |     | 6.4.2 Off-chip bandwidth constraints                   | 63        |

|          |     | 6.4.3 Performance impact of communication resources    | 63        |

|          |     | 6.4.4 Area and power impact of communication resources | 65        |

|          |     | 6.4.5 Intermediate storage discussion                  | 66        |

|    | 6.5    | Q100   | Evaluation             | 66 |

|----|--------|--------|------------------------|----|

|    |        | 6.5.1  | Methodology            | 66 |

|    |        | 6.5.2  | Performance            | 67 |

|    |        | 6.5.3  | Energy                 | 71 |

|    |        | 6.5.4  | Scalability            | 71 |

|    | 6.6    | Summ   | ary of Findings on DPU | 73 |

| 7  | Rela   | ated W | Vork                   | 74 |

| 8  | Con    | clusio | ns                     | 78 |

| Bi | ibliog | raphy  |                        | 80 |

# List of Figures

| 2.1  | ADI Impacts on Instruction Fetch                                        | 10 |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Instruction Fetch Energy Breakdown                                      | 10 |

| 2.3  | Instruction Access Time Breakdown                                       | 11 |

| 2.4  | L1 Data Store Configurations                                            | 12 |

| 2.5  | ADI Impacts on Data Delivery                                            | 13 |

| 2.6  | Data Delivery Energy Breakdown                                          | 13 |

| 2.7  | Data Access Time Breakdown                                              | 14 |

| 2.8  | Example PARSER code snippet using hash table ADIs                       | 16 |

| 3.1  | Potential Speedup with Various Granular Acceleration Targets            | 19 |

| 4.1  | Partitioning Example                                                    | 23 |

| 4.2  | Partitioned-Join Example                                                | 24 |

| 4.3  | Join Execution Time with respect to TPC-H Query Execution Time $\ldots$ | 25 |

| 4.4  | A Partitioning Microbenchmark Pseudocode                                | 26 |

| 4.5  | Partition Function Kernel Code                                          | 26 |

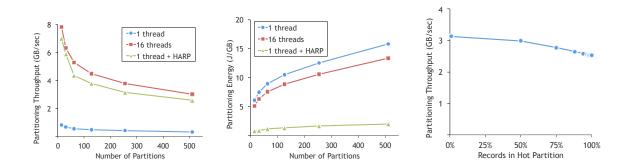

| 4.6  | Multi-threaded Software Partitioning Performance                        | 29 |

| 4.7  | HARP Microarchitecture Block Diagram                                    | 31 |

| 4.8  | HARP vs. Software Partitioning Performance                              | 33 |

| 4.9  | HARP vs. Software Partitioning Energy                                   | 33 |

| 4.10 | HARP Skew Analysis                                                      | 33 |

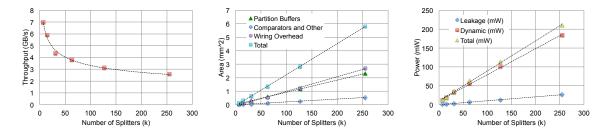

| 4.11 | HARP Performance Sensitivity to Partitioning Factor                     | 36 |

| 4.12 | HARP Area Sensitivity to Partitioning Factor                            | 36 |

| 4.13 | HARP Power Sensitivity to Partitioning Factor                                      | 36 |

|------|------------------------------------------------------------------------------------|----|

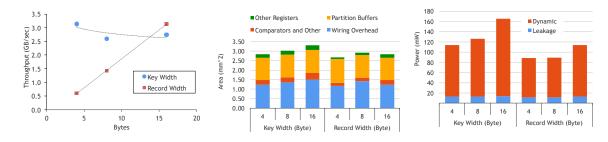

| 4.14 | HARP Performance Sensitivity to Key and Record Widths                              | 37 |

| 4.15 | HARP Area Sensitivity to Key and Record Widths                                     | 37 |

| 4.16 | HARP Power Sensitivity to Key and Record Widths                                    | 37 |

| 4.17 | Coping with Fixed Partition Size                                                   | 38 |

| 4.18 | Coping with Fixed Record Width                                                     | 38 |

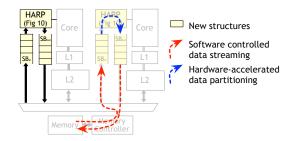

| 5.1  | An Integrated HARP System Block Diagram                                            | 42 |

| 5.2  | HARP Integration with Existing Software Synchronization                            | 42 |

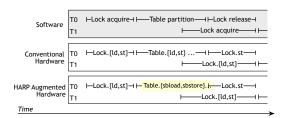

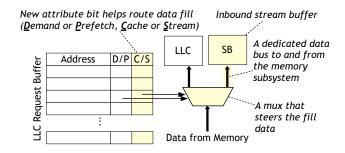

| 5.3  | Streaming Framework Datapath                                                       | 44 |

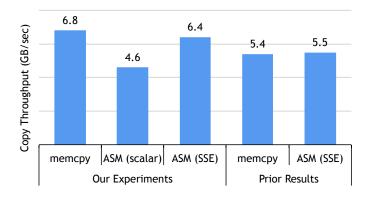

| 5.4  | Streaming Framework Performance                                                    | 46 |

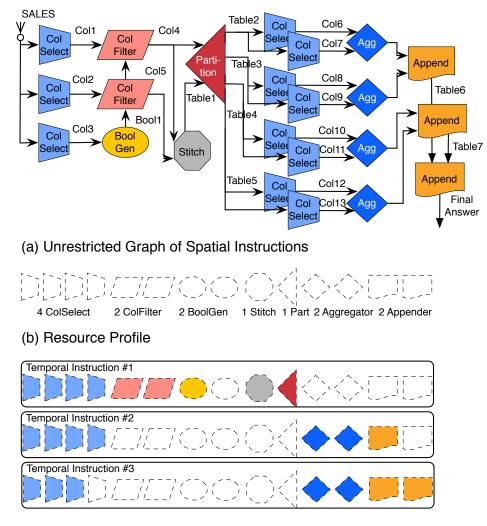

| 6.1  | An Example Query Spatial Instruction Representation                                | 50 |

| 6.2  | An Example Query Directed Graph and Temporal Instruction Representation            | 51 |

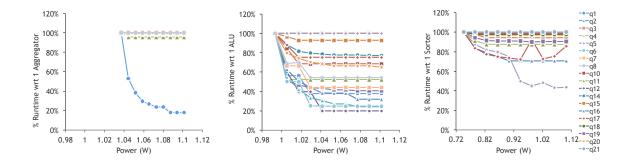

| 6.3  | Aggregator Sensitivity Study                                                       | 57 |

| 6.4  | ALU Sensitivity Study                                                              | 57 |

| 6.5  | Sorter Sensitivity Study                                                           | 57 |

| 6.6  | Three Q100 Designs Performance and Power                                           | 59 |

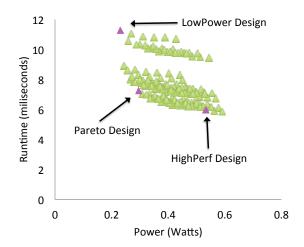

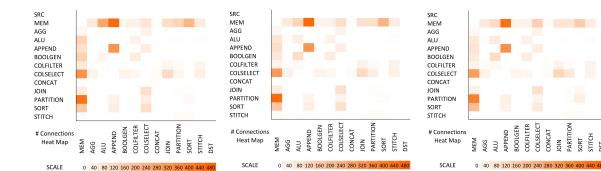

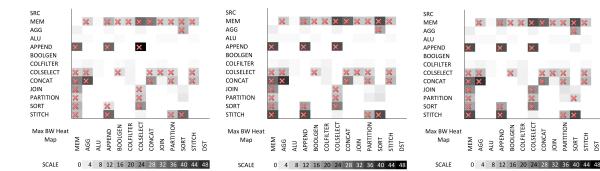

| 6.7  | LowPower Design Connection Count Heat Map                                          | 60 |

| 6.8  | Pareto Design Connection Count Heat Map                                            | 60 |

| 6.9  | HighPerf Design Connection Count Heat Map                                          | 60 |

| 6.10 | LowPower Design Connection Bandwidth Heat Map $\ldots \ldots \ldots \ldots \ldots$ | 61 |

| 6.11 | Pareto Design Connection Bandwidth Heat Map                                        | 61 |

| 6.12 | HighPerf Design Connection Bandwidth Heat Map                                      | 61 |

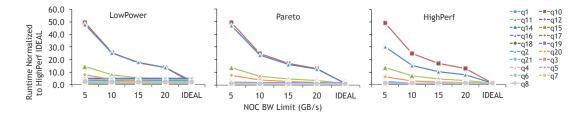

| 6.13 | NoC Bandwidth Sensitivity Study                                                    | 61 |

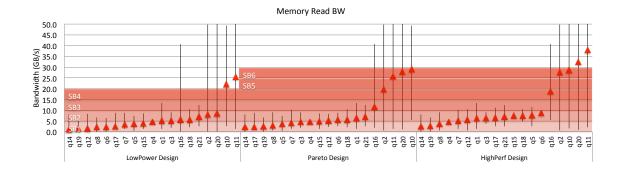

| 6.14 | TPC-H Query Read Memory Bandwidth Demands                                          | 62 |

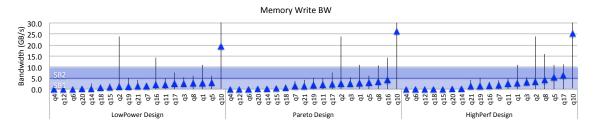

| 6.15 | TPC-H Query Write Memory Bandwidth Demands                                         | 62 |

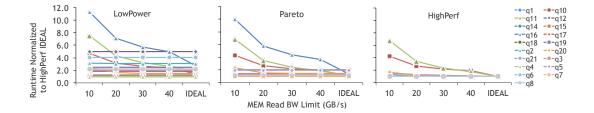

| 6.16 | Memory Read Bandwidth Sensitivity Study                                            | 64 |

| 6.17 | Memory Write Bandwidth Sensitivity Study                                           | 64 |

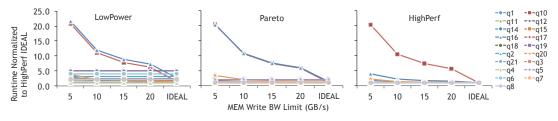

| 6.18 | Q100 Performance Slowdown with Memory and NoC Bandwidth Limits $\ .$ .             | 65 |

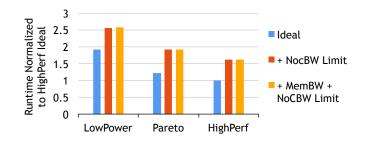

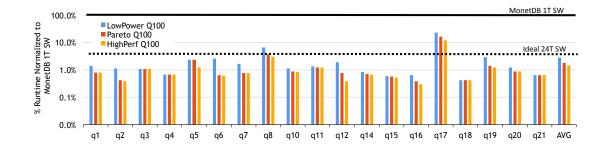

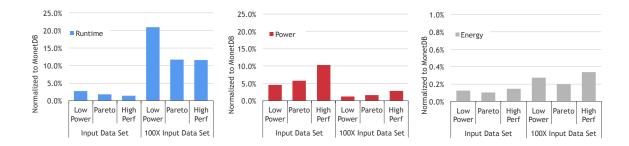

| 6.19 | Q100 Performance vs. Software                                                      | 68 |

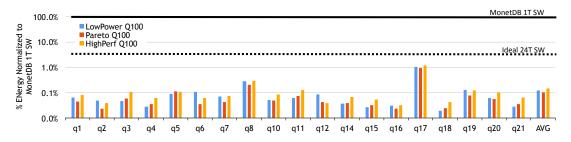

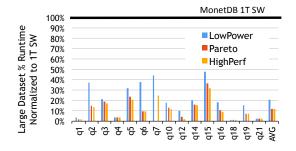

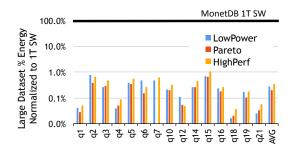

| 6.20 | Q100 Energy vs. Software                             | 68 |

|------|------------------------------------------------------|----|

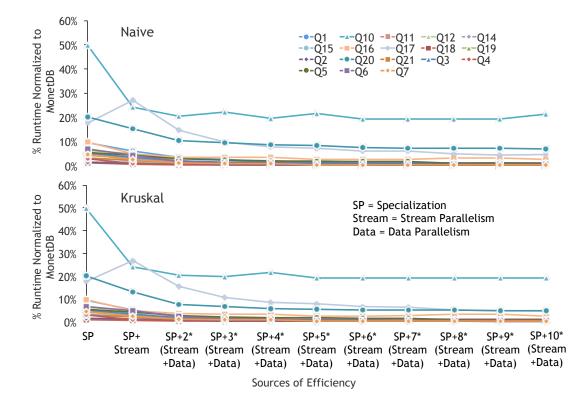

| 6.21 | Q100 Performance Efficiency as Parallelism Increases | 69 |

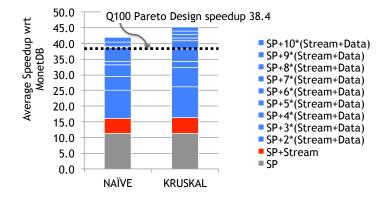

| 6.22 | Q100 Performance Speedup Breakdown by Source         | 70 |

| 6.23 | Q100 Performance with Large Data Sets                | 71 |

| 6.24 | Q100 Energy with Large Data Sets                     | 71 |

| 6.25 | Q100 Small and Large Data Set Scaling Comparison     | 72 |

# List of Tables

| 2.1 | Example ADIs for Hash Tables                                              | 8  |

|-----|---------------------------------------------------------------------------|----|

| 3.1 | Acceleration Targets for Each Benchmark Suite                             | 18 |

| 4.1 | System Configuration for Software Partitioning Experiments                | 28 |

| 4.2 | HARP ISA                                                                  | 29 |

| 4.3 | HARP Area and Power Overheads                                             | 34 |

| 4.4 | HARP DSE Parameters                                                       | 35 |

| E 1 | Streaming Framework ISA                                                   | 43 |

| 5.1 |                                                                           | 45 |

| 5.2 | HARP and Stream Buffers Area and Power Overheads                          | 46 |

|     |                                                                           |    |

| 6.1 | Q100 Tiles Area and Power Overheads                                       | 53 |

| 6.2 | Q100 DSE Configurations                                                   | 58 |

| 6.3 | Three Q100 Designs Area and Power Overheads with NoC and SB $\ . \ . \ .$ | 65 |

| 6.4 | System Configuration for Software Measurements                            | 67 |

# Acknowledgments

I am extremely thankful for the support, guidance, and friendship of my advisor Martha Kim throughout my years at Columbia. Martha taught me how to persevere through problems that seem impossible to solve; she taught me how to be meticulous in my work; she taught me how to face challenges when I feel defeated. She was a constant in helping me mature technically, academically, professionally, and also personally. I would not be able to complete this journey without her understanding of me having to spend (a small but not nonexistent) part of my time battling with a part-time job. Martha's motivation, enthusiasm, and her outstanding ability to distill research questions and present insights have been invaluable. She pushed me to greater success with her patience and perfectionism in our work.

I am also grateful for Ken Ross's excellent instruction on databases, his sharing his extensive knowledge in the field, and his guidance on the project that became the culmination of my thesis. Many thanks for Simha Sethumadhavan's time and feedback on my work and his generosity to let me use his compute resources.

I have been very fortunate to have Doug Carmean and Joel Emer as my long time mentors and advocates, both at work and at school. I am extremely grateful for their support, guidance, encouragement, hard questions, and insightful feedback on my research and at Intel. I would also like to thank George Chrysos for his understanding and support while I worked part-time to complete my degree.

Many thanks to John Demme and Melanie Kambadur for their support and friendship; I have learned a great deal from them and thoroughly enjoyed their company in and outside of the fish bowl.

Last but not least, I am tremendously thankful for the support of my family. My parents' many fasting and praying sessions, their encouragement, and their love have got me through

days and nights of success and defeat. My brother Leo's "tough" love when I really needed a kick in the butt have allowed me to carry on.

To Adonai Elohai.

## Chapter 1

# Introduction

Harvard Business Review recently published an article on Big Data that lead with a piece of artwork by Tamar Cohen titled "You can't manage what you don't measure" [McAfee and Brynjolfsson, 2012]. It goes on to describe big data analytics as not just important for business, but essential. The article emphasized the analyses must process large *volumes* of a wide *variety*, and at real-time or nearly real-time *velocity*. With the big data technology and services market forecast to grow from \$3.2B in 2010 to \$16.9B in 2015 [IDC Research, 2012], and 2.6 exabytes of data created each day [McAfee and Brynjolfsson, 2012], it is imperative for the research community to develop machines that can keep up with this data deluge.

However, the architecture community is facing challenges that require radical microarchitectural innovations to deliver performance gains while adhering to the required power constraints. These challenges are: (1) failure of Dennard scaling and dark silicon projections leave us with no clear path to exploit more transistors on die without violating the power envelope, (2) utilizing multiple simple cores (i.e. multicore architecture) can provide some parallel performance gain with energy efficiency but the gain is limited by Amdahl's law and the scaling is not sustainable, (3) creating application-specific integrated circuits, or ASICs, may not be cost effective if the specialization target is not broadly reused/applicable to provide substantial performance benefits, and (4) the accelerator interfaces to general purpose processors are ad-hoc and difficult to program.

### **1.1** Architectural Challenges

More than thirty years ago, Dennard et. al. from the IBM T. J. Waston Research Center published a paper detailing MOSFET scaling rules stating that with each technology generation, the devices got smaller, faster, and consumed less power [Bohr, 2007]. This is commensurate with Moore's law stating that the transistors on integrated circuits doubled approximately every two years, along with processing speed and memory capacity. These technology trends were followed by the semiconductor industry through the 1990's improving transistor density by 2X every 3 years, and increasing transistor count by 2X every 18 months. More recently, however, voltage scaling, a key component in the MOSFET scaling, has reached a limit where the voltage and frequency scaling are no longer possible, as the sub-threshold leakage is not just a tiny contributor to total chip logic power consumption any more. The transistor counts are still doubling on die, but they can not all operate at full speed without substantial cooling systems, and the fraction of a chip that can run at full speed is getting exponentially worse with each process generation [Venkatesh et al., 2010]; this is known as the utilization wall. Together with dark silicon projections Esmaeilzadeh and others, 2011, it is shown that only 7.9X average speedup is possible over the next five technology generations with only 79% of the chip fully operational at 22nm, and less than 50% of the chip fully operational at 8nm. This phenomenon leaves the community to explore solutions alongside of either trading area for power to utilize multicore architecture to provide more parallel performance for less power, or using specialization to allow the same number of transistors to provide more application performance for less power.

In theory, parallel processing on multicore chips can match historic performance gains while meeting modern power budgets, but as recent studies show, this requires near-perfect application parallelization [Hill and Marty, 2008]. In practice, such parallelization is often unachievable: most algorithms have inherently serial portions and require synchronization in their parallel portions. Furthermore, parallel software requires drastic changes to how software is written, tested, and debugged. Multicore scaling is also not sustainable as increased number of cores put more pressure on memory bandwidth and necessitate the support and management of increased number of outstanding memory requests [Cascaval and others, 2010]. Creating ASICs is another solution for computational power and performance efficiency because it removes unnecessary hardware for general computation while delivering exceptional performance via specialized control paths and execution units. However, given the cost associated with designing, verifying, and deploying an accelerator, it is uneconomical and impractical to produce a custom chip for every application. Hence, a particular operation only becomes a feasible and realistic acceleration target when it is used across a range of applications.

Furthermore, hardware accelerators, such as graphics coprocessors, cryptographic accelerators [Wu *et al.*, 2001], or network processors [Franke *et al.*, 2010; Carli *et al.*, 2009], provide custom-caliber efficiency in a general-purpose setting for their target domain, but often have awkward, ad hoc interfaces that make them difficult to use and impede software portability [Vo *et al.*, 2013]. Therefore, it is important to carefully choose the acceleration targets and their interface to general-purpose processors to provide high-performance, energy-efficient computation in a form palatable to software.

### 1.2 Accelerating Memory Operations

Before a suitable acceleration target can be chosen, we want to understand where most of the energy is spent when doing an operation in the computer system. [Dally *et al.*, 2008] found that in one RISC processor, each arithmetic operation consumes only 10 pJ but reading the two operands from the data cache for that particular operation required 107 pJ each, and writing the result back required another 121 pJ. This shows us that data supply energy dominates the execution of this arithmetic instruction by an order of magnitude compared to the actual computation. If we can reduce the data movement of an operation, we can in turn reduce the energy consumed. In this thesis, we architect accelerators that accelerate memory operations by specializing memory subsystems to provide energy efficiency for computations that require lots of data movement. We also opt for acceleration targets that are widely applicable, or coarse-grained enough to provide performance improvement for important workloads.

The spectrum of accelerators available today ranges from coarse-grain off-load engines such as GPUs to fine-grain instruction set extensions such as SSE. By encapsulating data and algorithms richer than the usual fine-grained arithmetic, memory, and control-transfer instructions, accelerating datatypes that are already defined in software provides ample implementation optimization opportunities in the form of an already familiar programming interface. Architects have made heroic efforts to quickly execute streams of fine-grained instructions, but their hands have been tied by the narrow scope of program information that conventional ISAs afford to hardware. Good software programming practice has long encouraged the use of carefully written, well-optimized libraries over manual implementations of everything; datatype acceleration simply supply such libraries in a new form.

### **1.3 Big Data Acceleration**

Datatypes manipulated in relational database applications are mostly tables, rows, and columns. These similarly structured data have long been the software optimization exploration focus of the Database Management System (DBMS) software community. Examples include using column stores [Idreos *et al.*, 2012; Lamb *et al.*, 2012; SAP Sybase IQ, 2013; Kx Systems, 2013; Abadi *et al.*, 2009; Stonebraker *et al.*, 2005]. pipelining operations either in rows or columns [Abadi *et al.*, 2007; Boncz *et al.*, 2005], and vectorizing operations across entries within a column [Zukowski and Boncz, 2012], to take advantage of commodity server hardware.

We propose applying those same techniques, but in hardware, to construct a domainspecific processor for databases. Just as conventional DBMSs operate on data in logical entities of tables and columns, our processor manipulates these same data primitives. Like DBMSs use software pipelining between relational operators to reduce intermediate results we too can exploit pipelining between relational operators implemented in hardware to increase throughput and reduce query completion time. In light of the SIMD instruction set advances in general purpose CPUs in the last decade, DBMSs also vectorize their implementations of many operators to exploit data parallelism. Our hardware does not use vectorized instructions, but exploits data parallelism by processing multiple streams of data, corresponding to tables and columns, at once.

This thesis claims that grouping similarly structured data and processing them together provides performance and energy efficiency. As a case study, we use tables and columns as the similarly structured data, and architect specialized hardware control and datapaths to accelerate the processing of read-only analytic database workloads. This class of database domain-specific processors, called DPUs, are analogous to GPUs. Whereas GPUs target graphics applications, DPUs target relational database workloads.

### **1.4** Contributions

The contributions of this thesis are as follows:

- A preliminary study on the analysis of cache impacts on datatype acceleration using sparse vectors and hash tables to assess the potential performance and energy savings of datatype acceleration.

- A preliminary study of acceleration targets using popular benchmark suites to assess the applicability of datatype acceleration.

- The architecture and design of a data partitioning accelerator, to assess the feasibility of big data acceleration.

- The architecture of a high-bandwidth, hardware-software streaming framework that transfers data to and from a streaming accelerator and integrates seamlessly with existing hardware and software.

- An energy-efficient DPU instruction set architecture for processing data-analytic workloads, with instructions that both closely match standard relational primitives and are good fits for hardware acceleration.

- A proof-of-concept DPU design, called Q100, that reveals the many opportunities, pitfalls, tradeoffs, and overheads one can expect to encounter when designing small accelerators to process big data.

### 1.5 Thesis Outline

In the next two chapters, we present the preliminary studies exploring the benefits and challenges of datatype acceleration and choosing appropriate acceleration targets. Chapters 4 and 5 describe the architecture and design of an accelerator for an important database operation, data partitioning, and its communications to and from the general processor. Chapters 6 and 7 detail a DPU instruction set architecture, microarchitecture, implementation, and evaluation of the proof of concept DPU, Q100. Chapters 8 and 9 examine related work and conclude.

## Chapter 2

# Cache Impacts of Datatype Acceleration

In this preliminary experiment, we consider predefined software data structures, or datatypes, as acceleration targets and examine the cache impacts of doing so. We supplement generalpurpose processors with *abstract datatype processors* (ADPs) to deliver custom hardware performance. ADPs implement *abstract datatype instructions* (ADIs) that expose to hardware high-level types such as hash tables, XML DOMs, relational database tables, and others common to software.

### 2.1 Architecture of ADPs

ADIs are instructions that express hardware-accelerated operations on data structures. Table 2.1 shows example ADIs for a hash table accelerator. The scope and behavior of a typical ADI resembles that of a method in an object-oriented setting: ADIs create, query, modify, and destroy complex datatypes, operations that might otherwise be coded in 10s or 100s of conventional instructions. Multiple studies in a range of domains conclude that the quality of interaction across an application's data structures is a significant determinant of performance [Jung *et al.*, 2011; Liu and Rus, 2009; Williams *et al.*, 2007]. Because ADIs encapsulate data structures as well as the algorithms that act on them, they can be implemented using specialized datapaths coupled to special-purpose storage structures that can

| ADI                                     | Description                                            |

|-----------------------------------------|--------------------------------------------------------|

| new <i>id</i>                           | Create a table; return its ID in register $id$         |

| put <i>id</i> , <i>key</i> , <i>val</i> | Associate $val$ with $key$ in table $id$               |

| get val, id, key                        | Return value $val$ associated with $key$ in table $id$ |

| remove id                               | Delete hash table with the given ID                    |

Table 2.1: Example Abstract Datatype Instructions for Hash Tables

be considerably more efficient than the general-purpose alternative. While there has been a great deal of research on specialized datapaths and computation, few researchers have considered specializing the memory system. For this study, we focus our exploration on a hash table accelerator with specialized storage (HASHTAB) and a sparse vector accelerator with specialized storage (SPARSEVEC).

As with other instruction set extensions, we assume a compiler will generate binaries that include ADIs where appropriate. When an ADI-enhanced processor encounters an ADI, the instruction and its operand values are sent to the appropriate ADP for execution. For example, operations on hash tables would be dispatched to the hash table ADP; operations on priority queues would be dispatched to the priority queue ADP. While ADIs can be executed in either a parallel or serial environment, we only consider single-threaded execution here.

### 2.2 Evaluation of ADPs

In this experiment, we quantify the impact of ADIs on instruction and data delivery to the processing core via the memory hierarchy. We examine two contemporary, performancecritical, serial applications that are not obviously amenable to parallelization: support vector machines and natural language parsing.

• Machine learning classification is used in domains ranging from spam filtering to cancer diagnosis. We use LIBSVM [Chang and Lin, 2001], a popular support vector machine library that forms the core of many classification, recognition, and recommendation

engines. In particular, we used LIBSVM to train a SVM for multi-label scene classification [Boutell *et al.*, 2004]. The training data set consists of 1211 photographs of outdoor scenes belonging to six potentially overlapping classes, *beach*, *sunset*, *field*, *fall foliage*, *mountain* or *urban*. We target the sparse vector type with an ADP with specialized instructions for insertion, deletion, and dot product operations on sparse vectors.

• Parsing is a notoriously serial bottleneck in natural language processing applications. For this study, we selected an open source statistical parser developed by Michael Collins [Collins, 1999]. We trained the parser using annotated English text from the Penn Treebank Project [University of Pennsylvania, 1995] and parsed a selection of sentences from the Wall Street Journal. For this application we target hash tables, assuming ADI support for operations such as table lookup and insertion. An example code snippet of the PARSER benchmark and its corresponding ADI version is shown in Figure 2.8.

We instrument these two applications using Pin [Intel Corporation, 2011], and feed the dynamic instruction and data reference streams to a memory system simulator. We then combine the output access counts with CACTI's [HP Labs, 2011] characterization of the access time and energy of each structure to compute the total time and energy spent fetching instructions and data. We evaluate a design space of fifty-four cache configurations for ADI-enhanced and ADI-free instruction streams. We consider direct-mapped and 2-way L1 caches of capacity 2 KB to 512 KB (each with 32 B lines), and unified L2 caches (each with 64 B lines) of sizes 1 MB (4-way), 2 MB (8-way), and 4 MB (8-way). We keep main memory capacity fixed at 1 GB.

#### 2.2.1 Instruction Delivery

First, we compare the instruction fetch behavior of an ADI-equipped processor to its ADIfree counterpart. We characterize the hierarchy by total energy consumed, dynamic and leakage, over all levels of the hierarchy; and total time spent accessing the memory system.

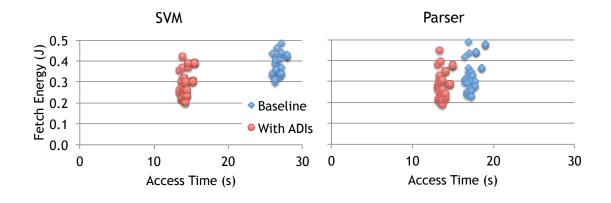

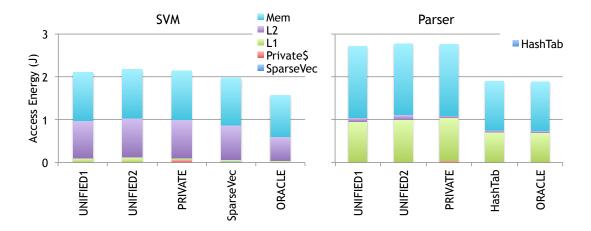

Figure 2.1: The scatter plots show instruction fetch performance and energy tradeoffs across a design space of 54 cache configurations. ADIs reduce time and energy an average of 21% and 19% respectively relative to ADI-free baselines for Parser and an average of 48% and 44% for SVM.

Figure 2.2: The bar charts display the breakdown of instruction fetch energy for each Pareto optimal cache configuration. For all but one cache configuration (16K+1M for Parser), L2 dynamic energy dominates as workload instruction footprint fits into the L2 capacity.

Figures 2.1–2.3 show the results of our instruction fetch experiments for SVM and Parser benchmarks. The scatter plots in Figure 2.1 graph the total instruction fetch energy against the total instruction fetch time. Here, the diamonds show the instruction cache behavior for ADI-free programs; the circles show the change in efficiency with the addition of ADIs. Of the two programs, SVM shows the greatest improvement, confirming the importance of the sparse vector dot product in the execution of this benchmark. The Parser benchmark

Figure 2.3: The bar charts display the breakdown of instruction access time for each Pareto optimal cache configuration. Even though the number of memory accesses are small, the latency per access is more than 10X L1 or L2 cache access time that the total access time is dominated by memory accesses.

shows more modest improvements, reflecting the smaller fractional importance of the hash table datatype in this application. From this design space we identify the set of Pareto-optimal cache designs: three from SVM and four for Parser. Selecting the optimal cache configurations for each benchmark is optimistic, as in reality many applications will share a single configuration; we do so here in order to measure ADIs against the best possible performance a cache can offer.

The charts in Figure 2.2 and Figure 2.3 show the detailed breakdown of energy and instruction fetch time of each optimal cache configuration. The energy consumption is divided into static and dynamic components for each level of the hierarchy. When a program's instruction footprint does not fit into the L1 instruction cache (L1I), we see L2 dynamic energy dominate. However, the dynamic L1I energy becomes dominant as the L1I size increases and the working set begins to fit. Figure 2.3 shows the overall time the memory system spends delivering instructions. Because main memory is far slower than the L1 cache, even the minuscule number of instruction fetches that go to main memory after missing both caches tend to dominate.

To summarize our findings on instruction fetch, each application gains in performance over all Pareto optimal cache designs, with the improvements in performance and energy savings coming in proportion to the reduction in total instructions fetched. To the extend instruction fetch consumes time and energy, these results suggest that changing the instruction encoding can reap important benefits, regardless of application domain.

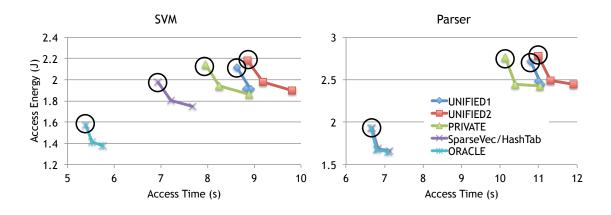

#### 2.2.2 Data Delivery

Below, we examine the costs and benefits of segregating and serving streams of data according to its type. We compare several different L1 data cache organizations while keeping the other levels of the hierarchy fixed. We hold the total L1 resources (i.e., total number of bits) constant but deploy them in several ways, illustrated in Figure 2.4: as a single, unified L1 cache (UNIFIED1 and UNIFIED2); two identical, private caches (PRIVATE); and one normal cache plus one type-specific storage unit (SPARSEVEC and HASHTAB, described below). To provide an upper bound on the data access savings one can hope to see, we also model an infinite, instantaneous, zero-energy storage unit to serve type-related memory requests (ORACLE).

UNIFIED1 UNIFIED2 PRIVATE SparseVec HashTab ORACLE

Figure 2.4: L1 data storage configurations used for data delivery experiments. All configurations fix the L1 storage size constant at 8 KB (except for ORACLE).

We consider a naïve implementation of a sparse vector store, which consists of a RAM storage array and a small number of registers that hold pointers to the next element in a particular sparse vector. The processing core can issue two types of requests to the sparse vector store: *begin vector*, which notifies the vector store that the processor is about to initiate an operation of the vector at a particular base address; and *next element* events, through which the processor requests the next element (i.e., index, value pair) in a sparse vector. Our experimental results indicate there is significant benefit both in data delivery speed and energy consumption from issuing operation-specific events such as the next-element requests instead of generic load and store operations. There are a number of ways to improve the microarchitecture of our simple sparse vector store. One option is

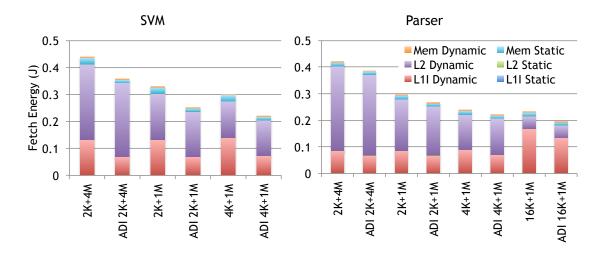

Figure 2.5: The scatter plots show data delivery performance and energy tradeoffs across a design space. HASHTAB reduced access time by up to 38% and energy by up to 33%. SPARSEVEC reduced access time by up to 20% and energy by up to 9%.

Figure 2.6: The bar charts display the breakdown of data access energy by memory structure for each circled configuration from Figure 2.5.

prefetching. The SPARSEVEC knows the processor is doing a dot product operation and thus always knows what the processor will request next. Even a simple prefetch algorithm can be expected to reduce data delivery time.

We evaluate the Parser benchmark in a similar manner to SVM. Instead of a SPARSE-VEC, we employ a type-specific storage for hash tables, HASHTAB. Similar to the SPARSE-VEC, the HASHTAB at its core is simply a RAM array whose total capacity is partitioned into two regions: the first caches portions of the table backbone; the second caches table elements themselves. As with SPARSEVEC there is ample room for microarchitects to opti-

Figure 2.7: The bar charts display the breakdown of access time by memory structure for each circled configuration from Figure 2.5.

mize the implementation of this storage structure, employing aggressive datapaths or more sophisticated storage structures such as CAMs. Other research, particularly from the networking domain, has outlined microarchitectural techniques to support efficient associative lookups in hardware [Zane and Narlikar, 2003; Carli *et al.*, 2009].

The scatter plots in Figure 2.5 plot the Pareto optimal energy-performance curves for the four generic cache organizations (UNIFIED1, UNIFIED2, PRIVATE, ORACLE) plus the type-specific stores (SPARSEVEC and HASHTAB). In this case we see that the specialized store is a vast improvement over the general purpose stores, nearly matching ideal storage properties. Specialized storage structures, SPARSEVEC and HASHTAB, showed 13–19.7% and 35.1–38% performance gains for SVM and Parser respectively while reducing energy by 5.9–8.6% and 28.9–33.1% respectively. The PRIVATE configuration is less complex to design but gained at most 7.9% and 5.9% while costing 1.4% and 1.7% more energy for SVM and Parser respectively.

Both the energy and runtime breakdowns in Figures 2.6 and 2.7 indicate that the specialized hash table store operates as a near-perfect cache. It reduces L2 pressure, which in turn reduces trips to memory, where most of the time and energy costs lie. In both cases, datatype-specific management policies were able to outperform equivalent-capacity general purpose caches, regardless of cache configuration. This is because the generic cache has no knowledge of the semantics of a hash table or a sparse vector. In contrast, the specialized cache only caches the desired entries or structures, effectively increasing the capacity of the storage.

### 2.3 Summary of Findings on ADPs

Datatype acceleration marries high-level datatypes with processor architecture—an unusually large range of abstraction—to solve a pressing problem: how to improve the energy efficiency of large-scale computation. Our experiments found such specialization can improve instruction and data delivery energy by 27% and 38% respectively. The impact on the overall system will depend on the relative importance of instruction and data delivery, which varies between embedded systems [Dally *et al.*, 2008] and high-performance cores [Natarajan *et al.*, 2003]. This study show that data structures, or datatypes, represent suitable acceleration targets with significant performance and energy potential gains. By aligning specialized hardware with common programming constructs, datatype specialization can improve both energy and performance efficiency while providing programmability.

#### $\triangleright$ Sample code from PARSER benchmark

void add\_counts(unsigned char \*event,int olen,int \*backoffs,char type,hash\_table \*hash)

```

{

int i; key_type key; unsigned char buffer[1000]; int len;

int ns[100]; len = 3+olen+backoffs[1]; key.key = buffer;

for(i=0;i|len;i++)

buffer[i] = event[i];

buffer[0] = type;

buffer[1] = BONTYPE;

for(i=1;i=backoffs[0];i++)

{

buffer[2] = i;

key.klen = 3+olen+backoffs[i];

ns[i] = hash_add_element('A',&key,hash,1);

}

• • •

}

\triangleright Sample code converted to Abstract Datatype Instructions for hash tables

void add_counts(unsigned char *event,int olen,int *backoffs,char type,hash_table *hash)

```

```

{

```

}

```

int i; key_type key; unsigned char buffer[1000]; int len;

int ns[100]; len = 3+olen+backoffs[1]; key.key = buffer;

for(i=0;ijlen;i++)

buffer[i] = event[i];

buffer[0] = type;

buffer[1] = BONTYPE;

for(i=1;ij=backoffs[0];i++)

{

buffer[2] = i;

key.klen = 3+olen+backoffs[i];

ns[i] = hash_adi_put(hash,&key,'A');

}

```

**Figure 2.8:** The hash table used for parsing a selection of sentences in the COLLINS PARSER benchmark is constructed using this subroutine. The entire function call *hash\_add\_element* from the original code is substituted with one ADI instruction *hash\_adi\_put*.

## Chapter 3

# Acceleration Targets

From the previous experiments, we found that datatype acceleration can be effective but the workloads may or may not utilize the datatypes. We perform another preliminary study and examine a wide range of industry standard benchmarks, assessing the potential of several acceleration targets within them. Depending on the language used for a particular application, there exists various granular data containers or data structures that can potentially be suitable acceleration targets. We start out looking at the smallest predefined data containers, such as standard library method calls for specific datatypes.

In order to isolate and group similar data containers, we profile popular benchmark suites and answer the following three questions:

- Do the benchmarks exhibit any common functionality at or above the function/method call level?

- What impact does the language or programming environment have on the potential acceleration of a suite of applications?

- How many unique accelerators would be required to see benefits across a particular benchmark suite? Does this change across suites and source programming languages?

### 3.1 Profiling of Benchmark Suites

To explore these questions, we profile four benchmark suites: SPEC2006 (C) [Standard Performance Evaluation Corporation, 2006], SPECJVM (Java) [Standard Performance Evalua-

| Benchmark       | Granularity |        |             |

|-----------------|-------------|--------|-------------|

| Suite           | fine        | medium | coarse      |

| SPEC2006        | function    | —      | application |

| SPECJVM         | method      | class  | package     |

| DACAPO          | method      | class  | package     |

| UNLADEN-SWALLOW | function    | _      | object      |

Table 3.1: Acceleration Targets for Each Benchmark Suite

tion Corporation, 2008], Dacapo (Java) [The DaCapo Research Project, 2006], and Unladen-Swallow (Python) [Google Inc., 2009]. Each source language provides a slightly different set of potential acceleration targets. For example, SPEC2006 is written in C and offers two target granularities: individual functions or entire applications. In contrast, a Java benchmark offers three granularities: methods, classes (i.e., all of the methods for a particular class), and entire applications. We classify each of these potential targets as *fine*, *medium*, or *coarse* granularity according to Table 3.1.

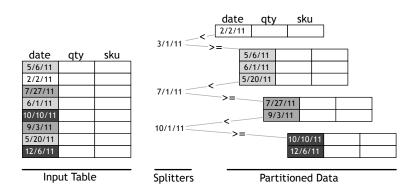

For each class of acceleration targets, we sort the targets by decreasing execution time across the entire benchmark suite. Assuming that building an accelerator for a particular target (1) provides infinite speedup of the target, and (2) incurs no data or control transfer overhead upon invocation or return, we compute an upper bound on the speedup of the overall suite for the most costly target(s). We repeat this analysis for each target granularity in each benchmark suite, as outlined in Table 3.1.

### **3.2** Results and Analysis

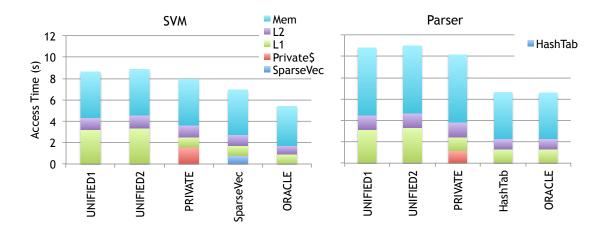

Our results show that popular benchmark suites exhibit minimal functional level commonality. For example, it would take 500 unique, idealized accelerators to gain a 48X speedup across the SPEC2006 benchmark suite. The C code is simply not modular for acceleration, and few function accelerators can be re-used across a range of applications. For benchmarks written in Java, however, we see more commonality as language level constructs such as classes encapsulate operations for easy re-use. The question remains whether building 20

Figure 3.1: Max speedup of benchmark suite for {fine, medium, and coarse}-granular acceleration targets.

accelerators for SpecJVM or 50 accelerators for Dacapo is worth the investment for the 10X speedups to be had. In the particular Python benchmark suite we used, we found that the applications made minimal use of the built-ins (e.g., dict or file) resulting in very minimal opportunity for acceleration beyond the methods themselves. Our intuition is that this may be an artifact of a computationally-oriented performance benchmark suite, and is likely not reflective of the overall space of Python workloads.

### 3.3 Summary of Findings on Acceleration Targets

Our analyses of SPEC2006 confirm what C-cores [Venkatesh and others, 2010], ECOcores [Sampson and others, 2011], and DYSER [Govindaraju and others, 2011] also found: that when accelerating unstructured C code, the best targets are large swaths of highlyapplication-specific code. Our Java analyses indicate some hope for common acceleration targets in classes, though the advantage of targeting classes over individual methods appears modest. Across the board, our data show that filling dark silicon with specialized accelerators will require systems containing tens or even hundreds of accelerators. In particular, popular benchmark suites, containing a collection of kernels attempting to represent a wide range of application characteristics, do not contain suitable acceleration targets. This conclusion points us to choose acceleration targets carefully in order to realize the potential performance and energy efficiency gains while offset the cost of designing unique circuitries.

## Chapter 4

# Hardware Accelerated Range Partitioning

The preliminary studies up to this point show that datatype acceleration is still a good idea, but needs to be implemented in an environment where the targeted data containers/structures are widely used. We choose to focus on the database application domain, specifically, analytic relational databases. We target relational databases for the following four reasons: (1) relational databases process structured datatypes, namely columns and tables, so we would expect to see benefits similar to the conclusion of our first preliminary study in Chapter 2; (2) relational databases are well established and accepted by the database community, so building hardware for such standard is broadly-applicable; (3) relational database applications are compute-bound, and there is potential for performance improvement; and (4) relational database applications are ubiquitous and increasingly important as evidenced by the fact that Oracle, Microsoft, and IBM build and support commercial relational databases.

Relational database applications being compute-bound are evidenced by the following observations. Servers running Bing, Hotmail, and Cosmos (Microsoft's search, email, and parallel data analysis engines, respectively) show 67%–97% processor utilization but only 2%–6% memory bandwidth utilization under stress testing [Kozyrakis *et al.*, 2010]. Google's BigTable and Content Analyzer (large data storage and semantic analysis, respectively)

show fewer than 10 K/msec last level cache misses, which represents just a couple of percent of the total available memory bandwidth [Tang *et al.*, 2011]. These observations clearly show that despite the relative scarcity of memory pins, these large data workloads do not saturate the available bandwidth and are largely compute-bound.

In this chapter, we explore targeted deployment of hardware accelerators to improve the throughput and energy efficiency of large-scale data processing in relational databases. In particular, data partitioning is a critical operation for manipulating large data sets. It is often the limiting factor in database performance and represents a significant fraction of the overall runtime of large data queries.

We start by providing some background on data partitioning, then we describe a hardware accelerator for a specific type of partitioning algorithm called range partitioning. We present the evaluation of the hardware accelerated range partitioner, or HARP, and show that HARP provides an order of magnitude improvement in partitioning performance and energy compared to a state-of-the-art software implementation.

### 4.1 Data Partitioning is Important

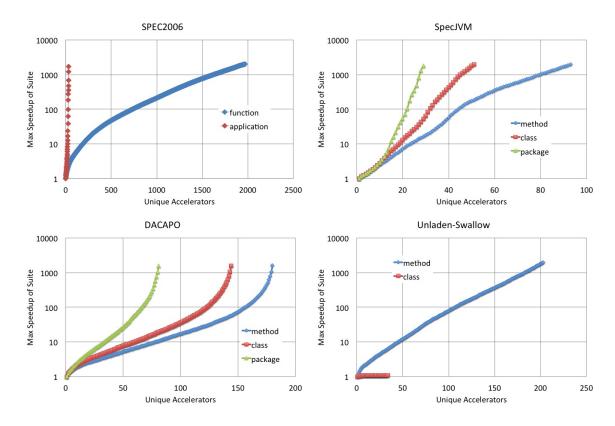

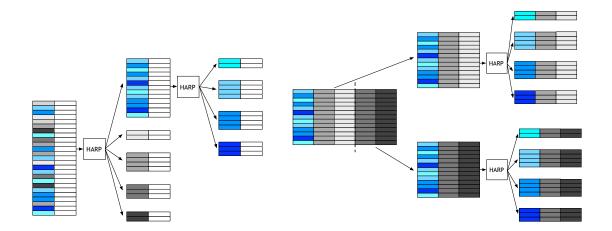

Databases are designed to manage large quantities of data, allowing users to query and update the information they contain. The database community has been developing algorithms to support fast or even real-time queries over relational databases, and, as data sizes grow, they increasingly opt to *partition* the data for faster subsequent processing. As illustrated in the small example in Figure 4.1, partitioning assigns each record in a large table to a smaller table based on the value of a particular field in the record, such as the transaction date in Figure 4.1. Partitioning enables the resulting partitions to be processed independently and more efficiently (i.e., in parallel and with better cache locality). Partitioning is used in virtually all modern database systems including Oracle Database 11g [Oracle, 2013], IBM DB2 [IBM, 2013a], and Microsoft SQL Server 2012 [Microsoft, 2012] to improve performance, manageability, and availability in the face of big data, and the partitioning step itself has become a key determinant of query processing performance.

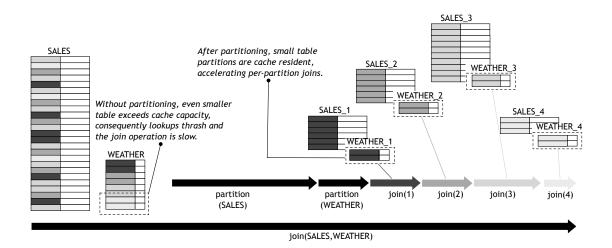

Figure 4.1: An example table of sales records *range partitioned* by date, into smaller tables. Processing big data one partition at a time makes working sets cache-resident, dramatically improving the overall analysis speed.

#### 4.2 Partitioning Background

Partitioning a table splits it into multiple smaller tables called *partitions*. Each row in the input table is assigned to exactly one partition based on the value of the *key* field. Figure 4.1 shows an example table of sales transactions partitioned using the transaction date as the key. This work focuses on a particular partitioning method called *range partitioning* which splits the space of keys into contiguous ranges, as illustrated in Figure 4.1 where sales transactions are partitioned by quarter. The boundary values of these ranges are called *splitters*.

Partitioning a table allows fine-grained synchronization (e.g., incoming sales lock and update only the most recent partition) and data distribution (e.g., New York sales records can be stored on the East Coast for faster access). When tables become so large that they or their associated processing metadata cannot fit in cache, partitioning is used to improve the performance of many critical database operations, such as joins, aggregations, and sorts [Ye *et al.*, 2011; Blanas *et al.*, 2011; Kim *et al.*, 2009]. Partitioning is also used in databases for index building, load balancing, and complex query processing [Chatziantoniou and Ross, 2007]. More generally, a partitioner can improve locality for any application that needs to process large datasets in a divide and conquer fashion, such as histogramming, image alignment and recognition, MapReduce-style computations, and cryptoanalysis.

Figure 4.2: Joining two large tables easily exceeds cache capacity. Thus, state of the art join implementations partition tables first and then compute partition-wise joins, each of which exhibits substantially improved cache locality [Kim *et al.*, 2009; Blanas *et al.*, 2011]. Joins are extremely expensive on large datasets, and partitioning represents up to half of the observed join time [Kim *et al.*, 2009].

To demonstrate the benefits of partitioning, let us examine joins. A *join* takes a common key from two different tables and creates a new table containing the combined information from both tables. For example, to analyze how weather affects sales, one would join the sales records in SALES with the weather records in WEATHER where SALES.date == WEATHER.date. If the WEATHER table is too large to fit in the cache, this whole process will have very poor cache locality, as depicted on the left of Figure 4.2. On the other hand, if both tables are partitioned by date, each partition can be joined in a pairwise fashion as illustrated on the right. When each partition of the WEATHER table fits in the cache, the per-partition joins can proceed much more rapidly. When the data is large, the time spent partitioning is more than offset by the time saved with the resulting cache-friendly partition-wise joins.

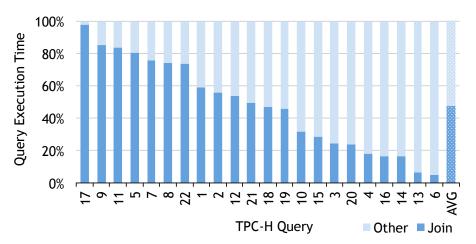

Join performance is critical because most queries begin with one or more joins to cross reference tables, and as the most data-intensive and costly operations, their influence on overall performance is large. We measured the fraction of TPC-H [Transaction Processing Performance Council, 2003] query execution time attributable to joins using MonetDB [Centrum Wiskunde and Informatica, 2012], an open-source database designed to provide high

Figure 4.3: Several key database operations such as join, sort, and aggregation use partitioning to improve their performance. Here we see joins consuming 47% of the TPC-H execution time on MonetDB. With state of the art join algorithms spending roughly half of the join time partitioning [Kim *et al.*, 2009], we estimate that partitioning for joins alone accounts for roughly one quarter of query execution time.

performance on queries over large datasets.<sup>1</sup> Figure 4.3 plots the percent TPC-H runtime spent joining tables. The values shown are the median across the ten runs of each query. Ranging from 97% to 5%, on average TPC-H spends 47% of its execution time in a join operation. State of the art implementations of joins spend up to half their time in partitioning [Kim *et al.*, 2009], thus placing partitioning at approximately 25% of TPC-H query execution time.

In addition to performance, a good partitioner will have several other properties. Ordered partitions, whereby there is an order amongst output partitions, is useful when a query requires a global sort of the data. Record order preservation, whereby all records in a partition appear in the same order they were found in the input table, is important for some algorithms (e.g. radix sorting). Finally, skew tolerance, maintains partitioning throughput even when input data is unevenly distributed across partitions. HARP provides all three of these properties as well as high performance and low energy.

<sup>&</sup>lt;sup>1</sup>Data collected using MonetDB 11.11.5 (release configuration, compiled with maximal optimization) on a dual-processor server (Intel Xeon X5660, 6C/12T, 2.8 GHz, with 12 MB LLC) with 64 GB DRAM. MonetDB used up to 24 threads per query, each of which was executed ten times in random order to minimize the impact of cached results.

```

NumRecs \leftarrow 10^8

\triangleright Alloc. and init. input

in \leftarrow malloc(NumRecs \cdot RecSize)

for r = 0..(NumRecs - 1) do

in[r] \leftarrow RandomRec()

end for

for p = 0..(NumParts - 1) do

\triangleright Alloc. output

out[p] \leftarrow malloc(NumRecs \cdot RecSize)

end for

for i = 0..NumRecs do

▷ Partitioning inner loop

r \leftarrow in[i]

p \leftarrow PartitionFunction(r)

*(out[p]) \leftarrow r

out[p] \gets out[p] + RecSize

end for

```

**Figure 4.4:** After initializing an input table and pre-allocating space for the output tables, the partitioning microbenchmark iterates over the input records, computes the output partition using *PartitionFunction()*, and writes it to that partition.

```

inline unsigned int

PartitionFunction

(register parttype key) {

register unsigned int low = 0;

register unsigned int hi = N+1;

register unsigned int mid = hi >> 1

for( int i = 0; i < D; i++ ) {</pre>

__asm__ volatile("CMP %4, %2\n"

"CMOVG %3, %0\n"

"CMOVL %3, %1\n"

: "=a"(low), "=b"(hi)

: "r"(key), "r"(mid), "r"(R[mid])

"a"(low), "b"(hi)

);

mid = (hi + low) >> 1;

7

return (mid << 1) - (key == R[mid])

}

```

Figure 4.5: The implementation of PartitionFunction() for range partitioning. For each record, the range partitioner traverses an array of N splitters. This optimized code performs a binary search up to D = log2(N) levels deep.

#### 4.3 Software Partitioning Evaluation

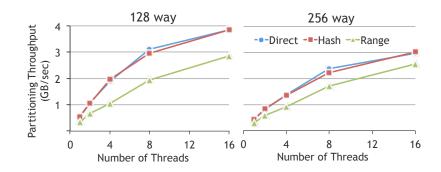

We now characterize the performance and limitations of software partitioning on general purpose CPUs. Since partitioning scales with additional cores [Cieslewicz and Ross, 2008; Kim *et al.*, 2009; Blanas *et al.*, 2011], we analyze both single- and multi-threaded performance.

For these characterizations, we use a microbenchmark whose pseudocode is shown in Figure 4.4. First, it initializes an input table with a hundred million random records. While actual partitioning implementations would allocate output space on demand *during* partitioning, we conservatively pre-allocate space for the output tables beforehand to streamline the inner loop. The partitioning inner loop runs over an input table reading one record at a time, computing its partition using a partition function, and then writing the record to

the destination partition. We compare three partitioning methods which are differentiated by the implementations of the partition function:

- Hash: A multiplicative hash of each record's key determines its destination partition.

- **Direct**: Like hash partitioning, but eliminates hashing cost by treating the key itself as the hash value.

- Range: Equality range partitioning using the state of the art implementation [Ross and Cieslewicz, 2009], which performs a binary search of the splitters. We show the exact code in Figure 4.5 as this is the software against which we will evaluate HARP.

The software partitioners were compiled with gcc 4.4.3 with -O3 optimization and executed on the hardware platform described in Table 4.1. Each reported result is the median of 10 runs, partitioning 10<sup>8</sup> records per run. We experimented with 8 byte records as in [Kim *et al.*, 2009] and 16 byte records as in prior work [Cieslewicz and Ross, 2008; Blanas *et al.*, 2011], but show the latter results here as they provide higher throughput and are most directly comparable to HARP. These software measurements are optimistic. The input keys are evenly distributed across partitions, while this is not typically the case in real-world data. Moreover, the microbenchmark pre-allocates exactly the right amount of memory and performs no bounds checking during partitioning, whereas, in the real world, it is impossible to know exactly how many records will land in each partition, making it impossible to pre-allocate perfectly.<sup>2</sup>

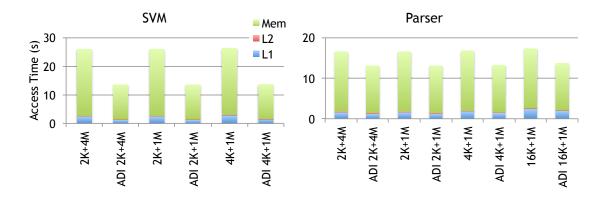

Figure 4.6 shows the throughput of the *hash*, *direct*, and *range* partitioners for 128-way and 256-way partitioning (i.e., 128 and 256 output partitions). Examining single-threaded performance, we see that the hash function computation incurs negligible cost relative to the direct method. Our per-record hash partitioning times match prior studies [Kim *et al.*, 2009], as does the drop in throughput between 128- and 256-way single-threaded

$<sup>^{2}</sup>$ To pre-allocate partitions, Kim et al. [Kim *et al.*, 2009] make an additional pass through the input to calculate partition sizes so that partitions are free of fragmentation, arguing that since the partitioning process is compute-bound, the extra pass through the data has only a small performance impact. An alternate approach is simply to allocate large chunks of memory on demand as the partitioning operation runs.

|                     | System Configuration               |

|---------------------|------------------------------------|

| Chip 2X Intel E5620 |                                    |

|                     | 4C/8T, 2.4 $GHz,12~MB$ LLC         |

| Memory              | 24 $GB$ per chip, 3 Channels, DDR3 |

| Max Memory BW       | $25.6 \ GB/sec$ per chip           |

| Max TDP             | 80 Watts per chip                  |

| Lithography         | 32 nm                              |

| Die area            | 239 $mm^2$ per chip                |

Table 4.1: Hardware platform used in software partitioning and streaming experiments (Sections 4.3 and 5.2 respectively). Source: Intel [Intel Corporation, 2010].

partitioning which is consistent with earlier observations that 128-way partitioning is the largest partitioning factor that does not incur excessive L1 TLB thrashing.

Range partitioning's throughput is lower than direct or hash partitioning because it must traverse the splitter array to determine the destination partition for each record, despite the heavily optimized implementation shown in Figure 4.5. It is possible to improve the traversal even further by using SIMD instructions as described by Schlegel et al. [Schlegel *et al.*, 2009] and we found that a SIMD-enhanced binary search improves the throughput of range partitioning up to 40%. However, the overall throughputs, 0.29 *GB/sec* without SIMD, and 0.4 *GB/sec* with, represent a tiny fraction of the 25.6 *GB/sec* maximum throughput potential of the machine. There are inherent bottlenecks in software range partitioning. In particular, to determine the correct partition for a particular record, the best-known software algorithm, used here, traverses a binary tree comparing the key to a splitter value at each node in the tree. The comparisons for a key are sequentially dependent, and the path through the tree is unpredictable. The combination of these properties results, unavoidably, in pipeline bubbles.

Because partitioning scales with multiple threads, we also consider the performance of multithreaded software implementations. As the data in Figure 4.6 indicate, 16 threads improve range partitioning throughput by 8.5X peaking at 2.9 and 2.6 *GB/sec* for 128-and 256-way partitioning respectively. Even after deploying all compute resources in the server, partitioning remains compute-bound, severely underutilizing the available memory

**Figure 4.6:** Range partitioning is the most costly for both 128- and 256-way partitioning. As parallel threads are added, throughput improves.

| HARP Instructions                                                                 |  |  |  |  |  |

|-----------------------------------------------------------------------------------|--|--|--|--|--|

| <pre>set_splitter <splitter number=""> <value></value></splitter></pre>           |  |  |  |  |  |

| Set the value of a particular splitter (splitter number ranges from 0 to $126$ ). |  |  |  |  |  |

| partition_start                                                                   |  |  |  |  |  |

| Signal HARP to start partitioning reading bursts of input records.                |  |  |  |  |  |

| partition_stop                                                                    |  |  |  |  |  |

| Signal HARP to stop partitioning and drain all in-flight data.                    |  |  |  |  |  |

Table 4.2: Instructions to control the Hardware Accelerated Range Partitioner (HARP).

bandwidth. In contrast, we will demonstrate that a single HARP-accelerated thread is able to achieve the throughput of close to 16 software threads, but at a fraction of the power.

#### 4.4 HARP Accelerator

#### 4.4.1 Instruction Set Architecture

The HARP accelerator is managed via the three instructions shown in Table 4.2. set\_splitter is invoked once per splitter to delineate a boundary between partitions; partition\_start signals HARP to start pulling data from the input stream; partition\_stop signals HARP to stop pulling data from the input stream and drain all in-flight data to the output stream. To program a 15-way partitioner, for example, 7 set\_splitter instructions are used to set values for each of the 7 splitter values, followed by a partition\_start to start HARP's partitioning.

#### 4.4.2 Microarchitecture

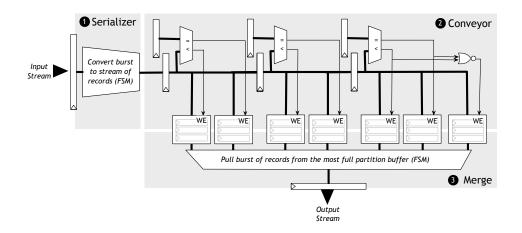

HARP pulls and pushes records in 64 byte bursts (tuned to match system vector width and DRAM burst size). The HARP microarchitecture consists of three modules, as depicted in Figure 4.7 and is tailored to range partition data highly efficiently.

- 1. The *serializer* pulls bursts of records from input stream, and uses a simple finite state machine to pull each individual record from the burst and feed them, one after another, into the subsequent pipeline. As soon as one burst has been fed into the pipe, the serializer is ready to pull the subsequent burst.

- 2. The *conveyor* is where the record keys are compared against splitters. The conveyor accepts a stream of records from the serializer into a deep pipeline with one stage per splitter. At each stage, the key is compared to the corresponding splitter and routed either to the appropriate partition, or to the next pipeline stage. Partition buffers, one per partition, buffer records until a burst of them is ready.

- 3. The *merge* module monitors the partition buffers as records accumulate. It is looking for full bursts of records that it can send to a single partition. When such a burst is ready, *merge* drains the partitioning buffer, one record per cycle, and sends the burst to output stream.

HARP uses deep pipelining to hide the latency of multiple splitter comparisons. We experimented with a tree topology for the *conveyor*, analogous to the binary search tree in the software implementation, but found that the linear conveyor architecture was preferable. When the pipeline operates bubble-free, as it does in both cases, it processes one record per cycle, regardless of topology. The only difference in total cycle count between the linear and tree conveyors was the overhead of filling and draining the pipeline at the start and finish respectively. With large record counts, the difference in time required to fill and drain a k-stage pipeline versus a log(k)-stage pipe in the tree version, is negligible. While cycle counts were more or less the same between the two, the linear design had a slightly shorter clock period, due to the more complex layout and routing requirements in the tree, resulting in slightly better overall throughput.

**Figure 4.7:** HARP draws records in bursts, serializing them into a single stream which is fed into a pipeline of comparators. At each stage of the pipeline, the record key is compared with a splitter value, and the record is either filed in a partition buffer (downwards) or advanced (to the right) according to the outcome of the comparison. As records destined for the same partition collect in the buffers, the merge stage identifies and drains the fullest buffer, emitting a burst of records all destined for the same partition.

The integer comparators in HARP can support all SQL data types as partitioning keys. This is because the representations typically lend themselves to integer comparisons. For example, MySQL represents dates and times as integers: dates as 3 bytes, timestamps 4 bytes, and datetimes as 8 bytes [MySQL, 2012]. Partitioning ASCII strings alphabetically on the first N characters can also be accomplished with an N-byte integer comparator.

#### 4.5 Evaluation Methodology

To evaluate the throughput, power, and area efficiency of our design, we implemented HARP in Bluespec System Verilog [Bluespec, Inc., 2012].

**Baseline HARP Parameters** Each of the design points extends a single baseline HARP configuration with 127 splitters for 255-way partitioning. The baseline supports 16 byte records, with 4 byte keys. Assuming 64 byte DRAM bursts, this works out to 4 records per burst.

**HARP Simulation** Using Bluesim, Bluespec's cycle-accurate simulator, we simulate HARP partitioning 1 million random records. We then convert cycle counts and cycle time into absolute bandwidth (in GB/sec).

HARP Synthesis and Physical Design We synthesized HARP using the Synopsys [Synopsys, Inc., 2013] Design Compiler followed by the Synopsys IC Compiler for physical design. We used Synopsys 32 nm Generic Libraries; we chose HVT cells to minimize leakage power and normal operating conditions of 0.85 V supply voltage at 25°C. The post-place-and-route critical path of each design is reported as logic delay plus clock network delay, adhering to the industry standard of reporting critical paths with a margin<sup>3</sup>. We gave the synthesis tools a target clock cycle of 5 or 2 ns depending on design size and requested medium effort for area optimization.

Xeon Area and Power Estimates The per-processor core area and power figures in the analyses that follow are based on Intel's published information and reflect our estimates for the system we used in our software partitioning measurements as described in Table 4.1.

#### 4.6 Evaluation Results

We evaluate the proposed HARP accelerator in the following categories:

- 1. Throughput comparison with the optimistic software range partitioning from Section 4.3.

- 2. Area and power comparison with the processor core on which the software experiments were performed.

- 3. Non-performance partitioner desiderata.

For all evaluations in this section, we use the baseline configuration of HARP outlined in Section 4.5 unless otherwise noted.

$^{3}$ Critical path of the 511-partition design, post-place-and-route, is obtained by scaling the synthesis output, using the Design Compiler to IC Compiler ratio across designs up to 255 partitions.

Figure 4.8: A single HARP unit outperforms single threaded software from 7.8X with 63 or 255 partitions to 8.8X with 31 partitions, approaching the throughput of 16 threads.

Figure 4.9: HARP-augmented cores partition data using 6.3-8.7X increases, throughput drops by at less energy than parallel or serial most 19% due to increased occursoftware.

Figure 4.10: As input imbalance rence of back-to-back bursts to the same partition.

**HARP Throughput** Figure 4.8 plots the throughput of three range partitioner implementations: single-threaded software, multi-threaded software, and single-threaded software plus HARP. We see that HARP's throughput exceeds a single software thread by 6.5X-8.8X, with the difference primarily attributable to the elimination of instruction fetch and control overhead of the splitter comparison and the deep pipeline. In particular, the structure of the partitioning operation does not introduce hazards or bubbles into the pipeline, allowing it to operate in near-perfect fashion: always full, accepting and emitting one record per clock cycle. We confirm this empirically as our measurements indicate average cycles per record ranging from 1.008 (for 15-way partitioning) to 1.041 (for 511-way partitioning). As Figure 4.8 indicates, it requires 16 threads for the software implementation to match the throughput of the hardware implementation. At  $3.13 \ GB/sec$  per core with HARP, augmenting all or even half of the 8 cores with HARP would provide sufficient compute bandwidth to fully utilize all DRAM pins.

In terms of absolute numbers, the baseline HARP configuration achieved a 5.06 nscritical path, yielding a design that runs at 198 MHz, delivering partitioning throughput of  $3.13 \; GB/sec$ . This is 7.8 times faster than the optimistic single-threaded software rangepartitioner described in Section 4.3.

|        | HARP Unit  |        |            |                  |  |  |  |  |  |

|--------|------------|--------|------------|------------------|--|--|--|--|--|

| Num.   | A          | Area   | Р          | ower             |  |  |  |  |  |

| Parts. | $mm^2$     | % Xeon | W          | % Xeon           |  |  |  |  |  |

| 15     | 0.16       | 0.4%   | 0.01       | 0.3%             |  |  |  |  |  |

| 31     | 0.31       | 0.7%   | 0.02       | 0.4%             |  |  |  |  |  |

| 63     | 0.63       | 1.5%   | 0.04       | 0.7%             |  |  |  |  |  |

| 127    | 1.34       | 3.1%   | 0.06       | 1.3%             |  |  |  |  |  |

| 255    | 2.83       | 6.6%   | 0.11       | $\mathbf{2.3\%}$ |  |  |  |  |  |

| 511    | $5.82^{4}$ | 13.6%  | $0.21^{4}$ | 4.2%             |  |  |  |  |  |

Table 4.3: Area and power overheads of HARP units for various partitioning factors.

Area and Power Efficiency The addition of the accelerator hardware do increase the area and power of the core. Table 4.3 quantifies the area and power overheads of the accelerator and stream buffers relative to a single Xeon core. Comparatively, the additional structures are very small, with the baseline design point adding just 2.83  $mm^2$  and 0.11 W.

**Energy Efficiency** From an energy perspective, this slight increase in power is overwhelmed by the improvement in throughput. Figure 4.9 compares the partitioning energy per GB of data of software (both serial and parallel) against HARP-based alternatives. The data show a 6.2–8.7X improvement in single threaded partitioning energy with HARP. If all eight cores were augmented with HARP, we estimate running eight HARP-enhanced cores (with one thread per core) would be 5.70–6.43X more energy efficient than running sixteen concurrent hyper-threads on those eight cores.

**Order Preservation** HARP is record order preserving by design. All records in a partition appear in the same order they were found in the input record stream. This is a useful property for other parts of the database system and is a natural consequence of the structure of HARP, where there is only one route from input port to each partition, and it is impossible for records to pass one another in-flight.

<sup>&</sup>lt;sup>4</sup>Scaled conservatively from the baseline design using area and power trends seen in Figures 4.12 and 4.13.

| HARP Design Space Configurations |    |    |    |     |     |     |    |  |

|----------------------------------|----|----|----|-----|-----|-----|----|--|

| # Splitters                      | 7  | 15 | 31 | 63  | 127 | 255 |    |  |

| # Partitions                     | 15 | 31 | 63 | 127 | 255 | 511 |    |  |

| Key Width (Bytes)                |    |    |    |     | 4   | 8   | 16 |  |

| Record Width (Bytes)             |    |    | 4  | 8   | 16  |     |    |  |

Table 4.4: Parameters for HARP design space exploration with baseline configuration highlighted.