# Image Understanding Algorithms on Fine-Grained Tree-Structured SIMD Machines

Hussein A. H. Ibrahim

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY 1984

O 1984

Hussein A. H. Ibrahim

ALL RIGHTS RESERVED

#### ABSTRACT

# Image Understanding Algorithms on Fine-Grained Tree-Structured SIMD Machines

#### Hussein A. H. Ibrahim

An important goal for researchers in computer vision is the construction vision systems that interpret image data in real time. Such systems typically require a large amount of computation for processing raw image data at the lowest level, and for sophisticated decision making at the highest level. Recent advances in VLSI circuitry have led to several proposals for parallel architectures for computer vision systems. In this thesis, we demonstrate that fine-grained tree-structured SIMD machines, which have favorable characteristics for efficient VLSI implementation, can be used for the rapid execution of a wide range of image understanding tasks. We also identify the limitations of these architectures and propose methods to ameliorate these difficulties. The NON-VON supercomputer, currently being constructed at Columbia University, is an example of such an architecture.

The major contribution of this thesis is the development and analysis of several parallel image understanding algorithms for the class of architectures under consideration. The algorithms developed in this research have been selected to span different levels of computer vision tasks. They include image correlation, histogramming, connected component labeling, the computation of geometric properties, set operations, the Hough transform method for detecting object boundaries, and the correspondence problem in moving light display applications. The algorithms incorporate novel approaches to reduce the effects of communication bottleneck usually associated with tree architectures.

# Table of Contents

| 1. | Introduction                                                      | 1         |

|----|-------------------------------------------------------------------|-----------|

|    | 1.1. Levels of Computer Vision Tasks                              | 4         |

|    | 1.2. Motivations For This Research                                | 6         |

|    | 1.3 Contributions of This Research and Organization of Subsequent | 7         |

|    | Chapters                                                          |           |

| 2. | Parallel Image Processing Architectures: An Overview              | 11        |

|    | 2.1 Mesh-Connected Architectures                                  | 12        |

|    | 2.2. Pipelined Architectures                                      | 14        |

|    | 2.3 Multiprocessor Architectures                                  | 16        |

|    | 2.4. Hierarchical Architectures                                   | 17        |

| 3. | The NON-VON Supercomputer Architecture                            | 22        |

|    | 3.1 The Small Processing Element Design                           | 25        |

|    | 3 2. Communication in NON-VON                                     | 27        |

|    | 3.3. N-PASCAL An Overview                                         | 30        |

| 4. | Image Representation                                              | 34        |

|    | 4.1 Image Data Structures: An Overview                            | 35        |

|    | 4 1 1. Multi-Resolution Pyramids on NON-VON                       | 36        |

|    | 4 1 2 Binary Image Trees on NON-VON                               | 39        |

|    | 4.2 Initialization and Image Loading                              | 42        |

|    | 421. Loading the Image                                            | 47        |

|    | 4 2 2 Building the Binary Image Tree                              | 51        |

|    | 423 Building the Multi-Resolution Pyramid                         | 54        |

| 5. | Low-Level Image Processing Algorithms                             | <b>59</b> |

|    | 5 1 Image Histogramming                                           | 60        |

|    | 5 2. Thresholding                                                 | 67        |

|    | 5 3. Image Correlation                                            | 71        |

|    | 5.3.1 Image Shift Algorithms                                      | 73        |

|    | 5.3.2. Image Correlation Algorithms                               | 83        |

| 6. Geometric Algorithms                         |             | 94                |

|-------------------------------------------------|-------------|-------------------|

| 6.1. Connected Component Labeling               |             | 95                |

| 6 1 1 The Connected Component Labeling Alg      | gorithm     | 95                |

| 6 1 2. Connected Component Labeling Simulation  | ion         | 107               |

| 6.2. Computing Connected Component Properties   |             | 108               |

| 6.2.1. Area                                     |             | 112               |

| 6.2.2. Perimeter                                |             | 113               |

| 6.2.3. Moments                                  |             | 115               |

| 6 2.4. Centroid                                 |             | 118               |

| 6.2.5. Compactness                              |             | 119               |

| 6 2 6. Eccentricity                             |             | 119               |

| 6.2.7. Euler Number                             |             | 120               |

| 6 2.8 Connected Component Properties Simul      | ation       | 128               |

| 6.3. Set Operations                             |             | 129               |

| 6.3.1. Complement                               | •           | 130               |

| 6 3 2 Intersection                              |             | 131               |

| 633 Union                                       |             | 133               |

| 7. The Hough Transform                          |             | 135               |

| 71. The Hough Transform Algorithm - A Direct.   | Approach    | 138               |

| 72. The Hough Transform Algorithm - A MSIMD     | Approach    | 143               |

| 7.3. Simulation Results                         |             | 151               |

| 8. Moving Light Displays                        |             | 154               |

| 8 1 The Tracking Algorithm                      |             | 155               |

| 9. Conclusion and Directions for Furthe         | er Research | 166               |

| References                                      |             | 170               |

|                                                 | 4: Q-4      |                   |

| Appendix A. The NON-VON 3 Instruct              |             | 182               |

| Appendix B. NON-VON 3 Code                      | for Selec   |                   |

| Algorithms  D. NON VON Too Josephson            |             | <b>187</b><br>187 |

| B 1 NON-VON Tree Initialization                 |             |                   |

| B 2. Image I/O                                  |             | 191<br>197        |

| B 3. Binary Image Tree Building                 | _           |                   |

| B 4. Gray-Scale Image Histogram and Thresholdin | 'g          | 200               |

| B 5 Binary Image Shifting                       |             | 204               |

| B 6 Gray-Scale Image Shifting                   |             | 207               |

| B7 Conneceted Component Labeling                |             | 209               |

| Appendix C. Some Functional Simulato            | r Results   | 218               |

| C 1. Hough Transform                            |             | 218               |

| C.2. Moving Light Displays                      |             | 220               |

# List of Figures

| Figure 2-1: | A Two-Dimensional Cellular Array                          | 12  |

|-------------|-----------------------------------------------------------|-----|

| Figure 2-2: | Organization of Pipelined Architectures                   | 14  |

| Figure 2-3: | An MIMD Architecture                                      | 16  |

| Figure 2-4: | A Hierarchically Organized Architecture                   | 19  |

| Figure 2-5: | Organization of the Pyramid Machine                       | 20  |

| Figure 3-1: | Top Level Organization of NON-VON                         | 23  |

| Figure 3-2: | NON-VON 3: Block Diagram of the Small Processing          | 27  |

|             | Element                                                   |     |

| Figure 3-3: | Inorder Embedding of the Linear Array                     | 29  |

| Figure 4-1: | An Image and its Multi-Resolution Pyramid                 | 37  |

| · ·         | Representation                                            |     |

| Figure 4-2: | A Picture and its Quadtree                                | 40  |

| Figure 4-3: | Binary Image Tree Rectangle Arrangement                   | 41  |

| Figure 4-4: | Coordinate System for Binary Image Trees                  | 43  |

| Figure 4-5: | A Binary Image and its Binary Image Tree                  | 55  |

|             | Representation                                            |     |

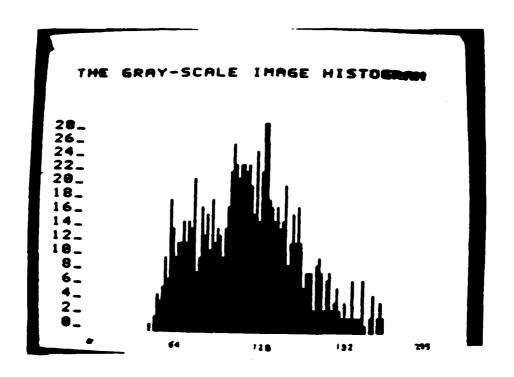

| Figure 5-1: | The Gray-Scale Image Histogram                            | 66  |

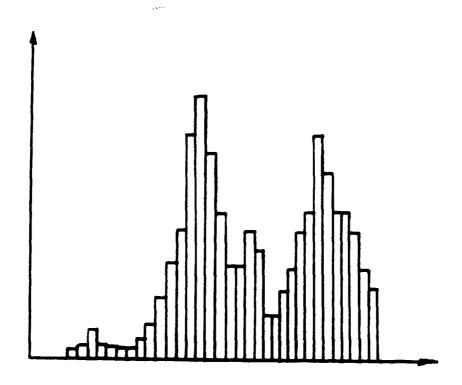

| Figure 5-2: | A Bimodal Histogram                                       | 68  |

| Figure 5-3: | The Binary Image After Thresholding                       | 70  |

| Figure 5-4: | Binary Image Shifting                                     | 77  |

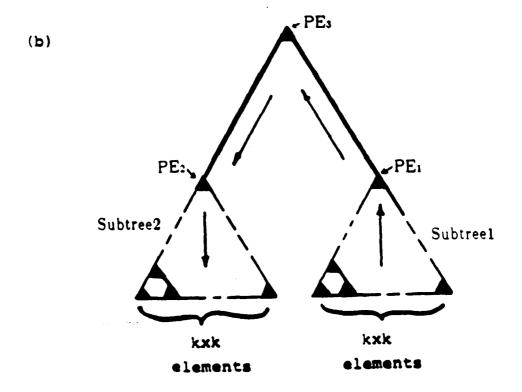

| Figure 5-5: | A $2k \times k$ Subimage and its NON-VON Tree             | 79  |

| · ·         | Representation                                            |     |

| Figure 5-6: | Image Correlation Template in a 4 x 4 Subimage            | 88  |

| Figure 6-1: | Connected Component Labeling of a Binary Image            | 96  |

| Figure 6-2: | Cases of a Rectangle Adjacent to Two Rectangles           | 105 |

| Figure 6-8: | Some Simulation Results                                   | 109 |

| Figure 6-4: | Possible Configurations of Three or Four Nodes That       | 121 |

| •           | Intersect a Point                                         |     |

| Figure 6-5: | Testing for S Points                                      | 123 |

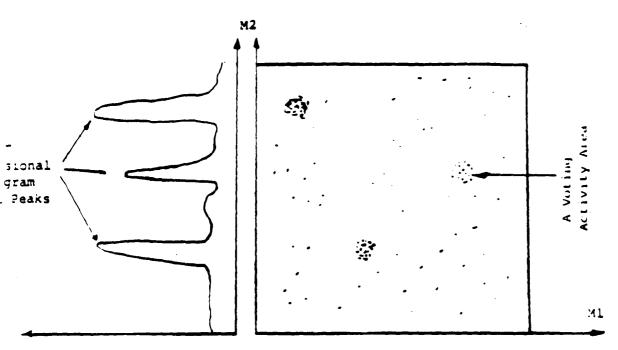

| Figure 7-1: | The Two-Dimensional Histogram of Parameter Values         | 148 |

| Figure 7-2: | The Input Boundary Points                                 | 152 |

| Figure 7-3: | Some Hough Transform Simulation Results                   | 153 |

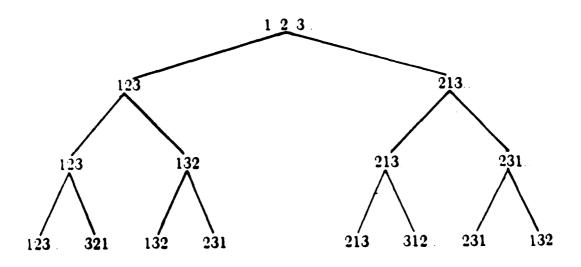

| Figure 8-1: | Permutations of the Initial Solution First Three Elements | 158 |

# List of Tables

| Table 4-1: | Image I/O           | Execution | n Time fo | or Some Pai | rallel Machines | 52 |

|------------|---------------------|-----------|-----------|-------------|-----------------|----|

| Table 5-1: | Execution Some Para |           |           | Low-Level   | Operations on   | 93 |

### Acknowledgments

I wish to express my sincerest thanks to my research advisors, David Shaw and John Kender, for their constant guidance, support and encouragement throughout my graduate studies at Columbia University; their influence on this work and on me has been tremendous. I consider myself fortunate indeed to have had the privilege and pleasure to have worked with two such distinguished and dedicated individuals. Salvatore Stolfo has also contributed to the contents of the research reported in this thesis with his support and thoughtful counseling on several occasions.

Special thanks are due to Cyrus Levinthal of Columbia University and Robert Hummel of New York University for generously agreeing to serve as outside committee members, and for their careful reading of this dissertation

Among the other individuals who have made contributions of various sorts to the completion of this dissertation are Theodore Bashkow, Mary Forry, Bruce Hillyer, Richard Korf, Jim Kurose, Gerald Maguire, and Stephen Unger

But beyond all else, I owe much to my wife Nihal Nounou, not only for her continuous support and encouragement, but also for her help in proofreading this thesis and for her constructive criticism of its contents.

This research was supported in part by the Defense Advanced Research Projects Agency, under contract N00039-84-C-0165, and by the New York State Center for Advanced Technology in Computers and Information Systems at Columbia University

To my parents

# Chapter 1 Introduction

The field of image understanding, also referred to as computer vision or image analysis, has developed quickly during the last decade, with growing applications in various fields. Industrial production, medicine, space exploration, robotics, and the discovery of natural resources are but a few examples of such areas. An important goal for researchers in this field is to construct computer-based vision systems that receive an image or a sequence of images from a sensory device and output an interpretation of this input in real time. Input images with reasonable resolution contain large quantities of data, and conventional von Neumann machines require an excessive amount of time to sequentially process the fetched data. Image understanding applications, however, usually involve computations that can be performed simultaneously on many or all of the image elements. Consequently, parallel computers are highly desirable for fast execution of image understanding tasks

A computer implementation of a complete vision system not only requires the performance of many computations on large structured arrays of raw image data at the lowest level, but also sophisticated decision making at the highest level. With recent advances in very large scale integrated (VLSI) circuitry, it is feasible now to embed a number of processing and memory elements within a single chip in a cost-effective

manner. This has led to a surge in research aimed at developing new computer organizations that meet the large computational and decision requirements of image analysis tasks by exploiting the new technology. Various kinds of special parallel machines for computer vision have been proposed and some have been implemented; examples are described in [Duff 76], [Krus 76], [Dyer 81], [Kush 83], [Pott 83], and [Reev 84].

The organization of some of the proposed machines is based on a very large number of very small processing elements (PE's). Throughout this thesis, we will refer to such machines as fine-grained or highly parallel machines. In such machines, different schemes are used to interconnect the PE's. For example, the PE's can be connected together in the form of a two-dimensional mesh, or they can be placed at the nodes of a binary tree. If all the PE's simultaneously execute the same instruction on their own data, the machine is said to be executing in single instruction stream, multiple data stream (SIMD) mode [Flyn 72]. On the other hand, if the PE's execute different instruction streams concurrently on different data streams, then the machine is said to be executing in multiple instruction stream, multiple data stream (MIMD) mode.

In this thesis, we investigate how fine-grained tree-structured SIMD computer architectures, which have favorable characteristics for efficient VLSI implementation, can be used for the rapid execution of a wide range of vision tasks. We also discuss certain limitations of these

architectures as vision machines and propose methods to ameliorate these difficulties. The NON-VON supercomputer, currently being constructed at Columbia University<sup>1</sup>, is a representative example of this class of architectures

Several parallel image understanding algorithms, spanning different levels of vision algorithms, have been developed and implemented on a functional simulator of the NON-VON machine. Some of these algorithms have also been tested on a machine instruction-level simulator of NON-VON. The design, implementation and time analysis of these algorithms are discussed in this thesis, as are issues related to image representation and image I/O. NON-VON's performance for the developed algorithms is also compared with that of other highly parallel vision machines.

In the rest of this chapter, we first discuss the nature of image understanding tasks and the manner in which they affect the design of the proposed architectures. In Section 1.2, we outline the central issues related to the construction of such highly parallel machines, and describe the motivations for this research. In Section 1.3, we state the major contributions of this work and outline the organization of subsequent chapters

<sup>&</sup>lt;sup>1</sup>The first prototype is expected to be completed by March 1985.

### 1.1. Levels of Computer Vision Tasks

Computer vision tasks may be divided into three characteristic classes low-level vision, intermediate-level vision, and high-level vision. Low-level image processing deals with the raw image data received from the sensory devices and usually produces an output of the same size as the input Low-level vision processing is sometimes referred to in the literature as signal level processing, since input image data may be viewed as a signal to be processed. Examples of low-level vision tasks include image restoration, noise removal, gathering certain statistics about the image, image enhancement, and simple feature extraction such as edge detection [Ball 82]. Since such tasks usually involve the execution of the same sequence of instructions repeatedly on all of the image data, they are well suited for fast execution on machines of SIMD architecture. Most special hardware systems proposed for image understanding tasks are of this type.

Intermediate-level vision tasks are usually concerned with aggregating image features obtained from low-level vision tasks and transforming the image into some symbolic representation, such as labeled graphs of relations between image features. Examples of such tasks include the Hough transform method for detecting object boundaries described by parametric curves, and interpreting the shape of three-dimensional objects from two-dimensional images. Intermediate-level vision tasks may be

viewed as the interface between low-level processing and processing of the symbolic image representations on the high-level. There are some open research questions regarding tasks on this level. Examples of such problems include the choice of the best sets of features to be extracted by low-level procedures for the task at hand, and the manner in which they are represented for use in high-level vision tasks.

High-level vision tasks accept a symbolic representation of an image and classify image features and segments into known classes. They also match these symbolic representations to known symbolic structures for the final interpretation of the image. Techniques used in these tasks are similar to those used in the fields of artificial intelligence and pattern recognition. High-level vision tasks usually involve multiple operations that can be executed independently. For example, the same image segment can be analyzed using different techniques. Architectures suited for these kinds of tasks are usually of the MIMD class.

In Chapter 2, we overview some of the architectures that have been proposed to implement these tasks, and discuss the advantages and disadvantages of these different architectures.

#### 1.2. Motivations For This Research

There are several motivations for this research. First, tree-structured machines have favorable characteristics for efficient VLSI implementation, such as area-efficient layout, simple interconnection scheme, and a bounded number of I/O ports per chip. Thus, tree machines are easy to construct and expand. The reader is referred to [Ibra 83] for a detailed discussion of this aspect of tree machines.

Second, NON-VON's hardware, with its support for the fast global broadcast of instructions and data to all PE's, is well-suited for the rapid execution of a wide range of vision tasks, especially low-level SIMD vision tasks. A detailed discussion of this aspect of NON-VON's architecture is presented in Chapter 2.

Third. NON-VON has some special hardware features that have been designed to support large scale data processing, and which have proven useful in vision tasks to ameliorate some of the problems related to the communication bottleneck generally associated with tree architectures. We will describe these features in Chapter 3

The fourth motivation is based on the fine granularity of the NON-VON PE's, which is well suited to image analysis tasks involving large amounts of data. 7

Furthermore, the hierarchical nature of the NON-VON tree allows the efficient implementation of existing hierarchical and multi-resolution algorithms for image analysis. Algorithms based on the aggregation of values computed at a number of image points can be executed very quickly by virtue of the hierarchical nature of the machine.

NON-VON's architecture also supports the concurrent manipulation of massive amounts of symbolic data, which is useful in high-level vision tasks. Relational image databases can be handled very efficiently on the NON-VON machine. The implementation of such systems is discussed in [Shaw 82]. Rapid execution of expert systems on tree machines is also discussed in [Stol 82]. The efficient use of image databases and of expert vision systems for high-level vision, are interesting research questions that are however beyond the scope of this thesis.

# 1.3. Contributions of This Research and Organization of Subsequent Chapters

The major contribution of this thesis is the development and analysis of parallel algorithms for several image understanding tasks on highly parallel tree-structured SIMD machines. The image analysis applications considered in this thesis have been selected to span different levels of computer vision applications. These algorithms incorporate novel approaches to exploit the machine's tree organization and to reduce the effects of communication bottleneck usually associated with tree

-

#### architectures.

Issues that affect the design and time analysis of these algorithms are also addressed in this dissertation. Image representation in tree machines is one such issue. We describe how hierarchical data structures can be modified to represent images in the NON-VON tree. Fast image I/O is an important factor for efficient implementation of vision algorithms. In this thesis, we propose different methods to perform I/O efficiently in tree machines.

More specifically, we have developed and analyzed parallel algorithms for fast image correlation, and for quasi-parallel connected component labeling. A fast, distributed, space-efficient algorithm has been developed to implement the Hough transform method for detecting object boundaries. We have also developed a parallel algorithm that quickly enumerates possible solutions for the correspondence problem in moving light display applications. Other fast algorithms have been developed, including image histogramming, set operations, and the computation of the geometric properties of objects.

NON-VON's performance for different image algorithms is analyzed and compared with that of other highly parallel image understanding architectures. Two simulators have been used to simulate the image algorithms. A functional simulator has been implemented on a VAX

11/750 augmented with a Grinnell image processor, and using the programming language C We have used this simulator to test all of the algorithms described in this thesis. A Lisp-based machine instruction-level simulator that has been developed for the NON-VON machine is used to execute some of the image algorithms. Based on simulation results, NON-VON's performance is compared with that of other highly parallel architectures for image analysis systems, and many algorithms are shown to execute faster on NON-VON than on other highly parallel machines. We have also identified the limitations of tree machines in the rapid execution of certain image analysis tasks, and have proposed special modifications to the NON-VON architecture for the rapid execution of these tasks.

In what follows, we outline the organization of the remaining chapters. In the following chapter, a number of special parallel architectures for image understanding are reviewed, with an emphasis on their basic architectural features and the vision applications for which they are best suited. The NON-VON architecture is described in Chapter 3, and is compared with other proposed hierarchical architectures for vision. A parallel programming language, based on PASCAL, is also described in Chapter 3. This language, referred to as N-PASCAL, is used to describe the developed algorithms throughout the thesis.

In Chapter 4, we introduce certain hierarchical data structures for

image processing, and demonstrate how they can be used to represent images in the NON-VON tree. We also discuss in Chapter 4 the initialization procedures for the NON-VON tree, along with various issues related to image I/O.

Four groups of algorithms are presented in this thesis:

- 1 Signal level processing algorithms.

- 2 Geometric algorithms.

- 3. Aggregation algorithms.

- 4 High-level algorithms.

Examples of these groups are presented in Chapters 5 through 8, respectively. The first two groups represent low-level vision tasks, while the third and fourth groups represent intermediate- and high-level vision tasks, respectively. Time analysis results are presented for each algorithm, and NON-VON's performance is compared with that of other architectures. Simulation results, obtained by implementing the image understanding algorithms on the functional simulator and on the NON-VON instruction-level simulator, are also presented and analyzed. Chapter 9 includes the conclusion of this thesis and outline possible directions for further research.

## Chapter 2

## Parallel Image Processing Architectures: An Overview

In this chapter, we describe several of the parallel architectures that have been proposed for computer vision, with an emphasis on the match between their underlying architectural features and various image analysis tasks. Advantages and disadvantages of the surveyed machines as vision machines are also discussed. These architectures may be classified into four categories based on the scheme used to interconnect the processing elements.

- 1 Mesh-connected architectures

- 2 Pipelined architectures.

- 3 Multiprocessor Architectures

- 4 Hierarchical architectures.

We will focus on the last of these architectural families, and will show in more detail the motivation behind it

#### 2.1. Mesh-Connected Architectures

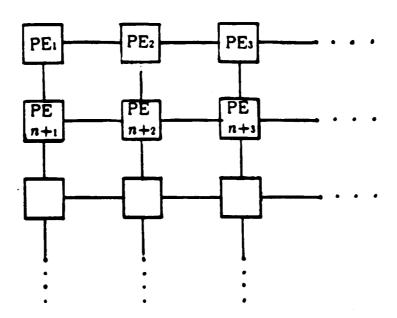

Cellular logic arrays, proposed by Unger [Unge 58], [Unge 59] for use as parallel image processors, form the basis for many later architectural proposals in this category. In cellular logic arrays, also referred to as two-dimensional arrays or parallel array processors, an image is divided into a regular two-dimensional array of cells, with a PE assigned to each cell. Physically adjacent PE's can communicate with each other, and each PE has some local storage and some hardware to manipulate its contents. The PE's execute in SIMD mode with instructions broadcast by the host computer. Figure 2-1 shows the organization of a two-dimensional cellular array.

Figure 2-1: A Two-Dimensional Cellular Array (Adapted from [Rose 83])

Loading and unloading of images are usually performed alongside the

perimeter of the array. All the data paths within a single PE are typically one bit wide, for this reason, such machines are also referred to as biffary array processors [Reev 84]. With recent advances in VLSI, machines containing as many as 16K one-bit PE's (organized in a 128 × 128 array) have been constructed.

The fundamental advantage of this family of architectures is that it maps the physical adjacency of image elements directly into hardware, thus making access to neighborhood information very rapid. Many low-level image operations, such as image filtering and local image feature detection, can be executed very rapidly in parallel on this architecture. Operations involving the gathering of statistics about the whole image are not as fast as local operations. They execute in a time proportional to the array diameter (that is, to the square root of the number of PE's).

VLSI implementation of such machines involves designing chips with a number of PE's interconnected together in the form of a rectangular grid. The PE's on the perimeter of the grid communicate with other chips through I/O ports. With VLSI device dimensions scaling down, an increasing number of PE's can be embedded on one chip. However, the number of pins required for inter-chip communication increases in proportion to the square root of the number of PE's per chip. Thus, the number of PE's to be embedded on one chip is limited by the number of pins allowed by the technology. One way of dealing with this problem

involves time-multiplexing the use of I/O ports between several PE's on the perimeter of the chip [Weem 84]. This, however, reduces the speed of inter-chip communication.

Examples of operational machines in this architectural family include CLIP4 [Duff 76] which is a 96 × 96 PE LSI machine, the MPP [Pott 83] with an array of 128 × 128 PE's, and the ICL DAP [Mark 80], containing an array of 64 × 64 PE's. A further discussion of cellular logic arrays can be found in [Rose 83] and [Reev 84].

## 2.2. Pipelined Architectures

Other parallel machines proposed for image understanding make use of pipelining as a way of introducing parallelism into the system.

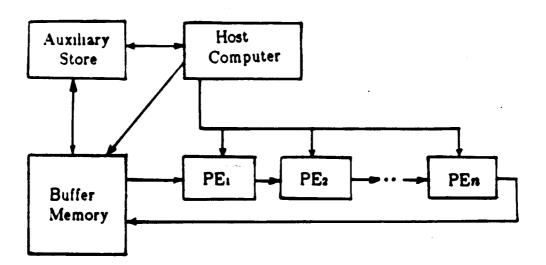

Figure 2-2: Organization of Pipelined Architectures (Adapted from [Reev 84])

Figure 2.2 depicts the basic organization of this family of architectures.

Image data is passed to the first stage of the pipeline from the scanning device, or from a buffer meniory. The function of each stage is specified by the host computer through the instruction bus

Machines of this type are most efficient in real-time low-level image processing applications where the image data source is connected to the machine directly, and generates data at the speed of a simple pipeline step. Such architectures can be fully utilized when the image processing tasks have a number of steps equal to the number of the pipeline stages. The architecture has its limitations, though, and when dealing with more than one image at a time, or when performing operations such as geometric corrections, due to the limited interconnection scheme of the pipeline.

An example of this family of architectures is the Cytocomputer [Ster 83], which is used in biomedical image processing. The Cytocomputer has 80 binary stages in one pipeline and 25 grey level stages in a second pipeline, each stage operates on a three by three window in the image. Binary stages are capable of implementing all possible logical operations on the nine elements by means of a look-up table memory in each stage. This makes such operations extremely fast in these stages. The gray level stages can perform 8-bit arithmetic operations on their window operands

### 2.3. Multiprocessor Architectures

Members of this category of architectures make use of a high-bandwidth interconnection network for communication between an independent set of PE's

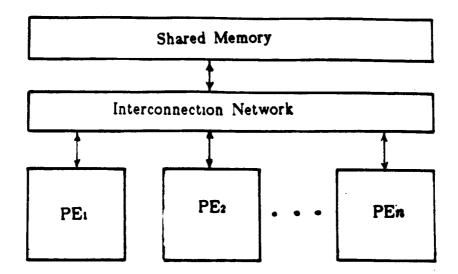

Figure 2-3: An MIMD Architecture (Adapted from [Reev 84])

The processors in such architectures can typically execute different programs (MIMD mode), or the same program (SIMD mode) at any point in time. Communication among the PE's is affected by sending messages through the interconnection network or through a shared memory, as shown in Figure 2.3

Parallel machines of this type are mostly efficient in executing high-level image understanding tasks, in which the image is no longer represented as a large array of data, but rather in the form of a symbolic description

of objects. For example, different processors may be assigned different algorithms for the analysis of the same image object. Because of the complexity of the interconnection network required to connect the PE's, machines of this type can not embody more than few thousand processors. The distribution of tasks between independent processors and the synchronization of different PE's present added complications.

Examples of this class of architectures include PASM [Sieg 81] and ZMOB [Kush 82]. The proposed architecture of PASM comprises 1024 PE's interconnected together by means of a permutation network. The machine also contains a number of control units that enable the machine to execute as an independent set of SIMD machines. ZMOB, on the other hand, consists of 256 identical PE's, connected to each other and to a VAX 11/780 host computer by a high-speed bus. The PE's communicate with each other and with the host machine by means of messages transferred through the bus. The reader is referred to [Kush 82] and [Sieg 81] for a description of the implementation of some image tasks on these two machines.

### 2.4. Hierarchical Architectures

A fourth architectural approach is suggested by the vision systems of humans and higher animals. The human visual system processes pictorial information through a series of layers, each containing a large set of parallel receptors and processors. Input information to the visual system

cones, in the retina. The retina behaves in many ways like a mesh of PE's. This raw information is then transformed into gradients, and contours are enhanced by two other parallel sets of processor layers in the retina [Uhr 80]. The transformed information is then carried by the optic nerve to the higher portions of the visual system. Information reaching the higher portions is compressed in size by a factor of about 100, and it is then processed and transformed by several layers of parallel processors.

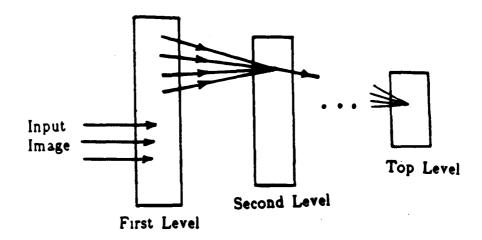

These generated proposals observations have for hierarchical architectures for image understanding systems. Such architectures are often referred to in the literature as hierarchical, cone, or pyramid In hierarchical architectures, processing takes place in a series machines of levels, as shown in Figure 2.4. At the lowest level is the raw pictorial information input to the system by a sensory device A set of transformations is first performed on this input; their output is then either stored on the same level or passed to the next level in the hierarchy. This process continues for several layers in the hierarchy. Data may also flow top-down in the hierarchy of layers, or laterally within any layer

Hierarchical architectures are well suited to the fast execution of multiresolution feature (color, texture, edge, etc.) algorithms. In addition,

Figure 2-4: A Hierarchically Organized Architecture (Adapted from [Uhr 84])

many algorithms that use hierarchical data structures, such as quadtrees, [Klin 76], can be implemented efficiently on hierarchical machines. Global feature information, such as bit counting, can be rapidly accumulated at the top of the hierarchical structure.

A number of special hierarchical parallel machines have been proposed for image processing tasks ([Hans 78], [Uhr 78], [Dyer 81], [Tani 83a]). The pyramid machine proposed by Dyer [Dyer 81] is a representative example of this class of architectures. The organization of a pyramid machine is shown in Figure 2.5. PE's in each layer are organized as two dimensional arrays, with each PE capable of communicating with its immediately adjacent PE's. Each PE also communicates with four PE's in the layer below it, and with one PE in the layer above it. Pyramid

Figure 2-5: Organization of the Pyramid Machine (From [Tani 83a])

machines are difficult to build because of the complexity of their wiring, and only a few projects for building a 16 × 16 base pyramid machines are under way ([Tani 83a] and [Scha 84])

The NON-VON supercomputer [Shaw 82] is another example of a hierarchical machine. Its architecture includes a large number of small PE's that form the nodes of a complete binary tree. NON-VON has been designed to support the massively parallel manipulation of data records stored in its PE's. This aspect of the NON-VON machine makes it attractive for vision applications that involve a large amount of data. Furthermore, hierarchical data structures proposed for image analysis, including multi-resolution pyramids and quadtrees, can be effectively used

to represent images on NON-VON. Also, the binary image tree data structure proposed by Knowlton [Know 80] as a variant of quadtrees, can be mapped directly onto the NON-VON machine to represent binary images in a manner to be described in Chapter 4.

The present version of the NON-VON architecture differs from other proposed pyramid machines in that it does not implement in hardware the mesh connections at each level. Thus, local operations execute faster on mesh-connected and pyramid machines. Careful design of the algorithms can speed up these operations considerably, as will be described later. The architecture of NON-VON is described in the following chapter, and the differences between its architecture and other proposed pyramid machines are presented

## Chapter 3

# The NON-VON Supercomputer Architecture

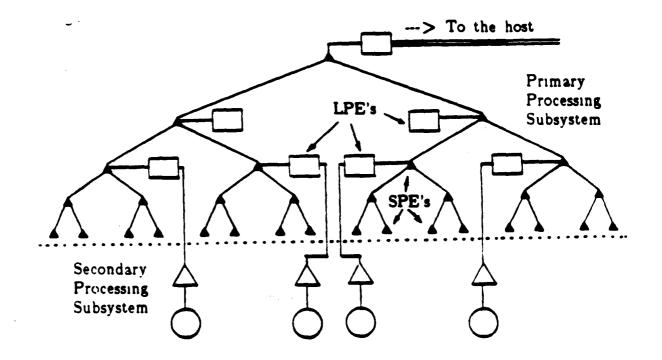

The name NON-VON is used to describe a family of massively parallel tree-structured machines intended to support large scale data manipulation [Shaw 84]. The architectures of all the NON-VON family members include a tree-structured primary processing subsystem (PPS) based on custom VLSI circuits, along with a secondary processing subsystem (SPS) based on a bank of intelligent disk drives. Figure 3-1 shows the top-level organization of the NON-VON architecture.

The PPS is configured as a binary tree of small processing elements (SPE's) Each SPE comprises a small RAM (up to 256 bytes), a modest amount of processing logic, and an I/O switch that supports various modes of communication within the tree, as will be described in Section 3.2

The SPS is based on a number of rotating storage devices. Associated with each disk head in the SPS is a separate sense amplifier and a small amount of logic capable of dynamically examining the data passing

Figure 3-1: Top Level Organization of NON-VON (From [Hill 83])

beneath it [Shaw 82]. This organization supports parallel transfer of data between the PPS and SPS, which is necessary to keep I/O from becoming a bottleneck.

NON-VON 1 and NON-VON 3, the first two members of the NON-VON family, include a single special control processor (CP) at the root of the tree. The CP is responsible for coordinating different activities within the PPS. It is capable of broadcasting instructions to be executed

simultaneously by all active PE's Thus, NON-VON 1 and NON-VON 3 function for the most part as SIMD machines, with all SPE's simultaneously executing the same instruction. (The single exception involves transfers between the SPS and the PPS, which will not be discussed in this dissertation.) We will call the algorithms that use this mode of execution SIMD algorithms.

The first member of the NON-VON family, NON-VON 1, contains chips with only one PE, and is being constructed primarily to evaluate certain electrical, timing, and layout area characteristics. The chip has already been tested and has been proven functional. A modified version of the chip with eight PE's has been designed for use in NON-VON 3. The modified chip, partial prototype of which has recently been fabricated has less area per PE, and the instruction set has been made more powerful by generalizing register-to-register data transfers and adding more arithmetic processing power.

The design of the NON-VON 3 PE is briefly described in the following section. All algorithms developed in this thesis are based on the NON-VON 3 architecture and instruction set. Appendix A contains a listing of all such instructions. It is expected that the time required to execute a NON-VON 3 instruction in all PE's in a tree of 15 levels (32K PE's) is approximately 250 nsec. We will use this number throughout this thesis to compute the execution time for the developed algorithms.

The emerging design for NON-VON 4 [Shaw84a] would include a number of large processing elements (I.PE's) connected to all nodes above a certain tree level. Each LPE would include an off-the-shelf 32-bit microprocessor, a reasonable amount of memory (between 256K bytes and one megabyte), and some special hardware to interface with the rest of the machine A high-bandwidth multi-stage interconnection network would be used to interconnect the set of LPE's. The LPE's would be capable of executing their own programs, or of functioning as CP's for the subtrees they root. Thus, NON-VON 4 would have the capability of executing in MIMD and "multiple-SIMD" (MSIMD) modes. The LPE network should significantly improve the bandwidth of communication involving the top of the tree.

In the following sections, we describe the design of the SPE in the NON-VON 3 machine and the various communication modes supported by both the NON-VON 1 and NON-VON 3 machines. We also introduce the N-PASCAL programming language, which will be used to describe the vision algorithms developed on the NON-VON machine.

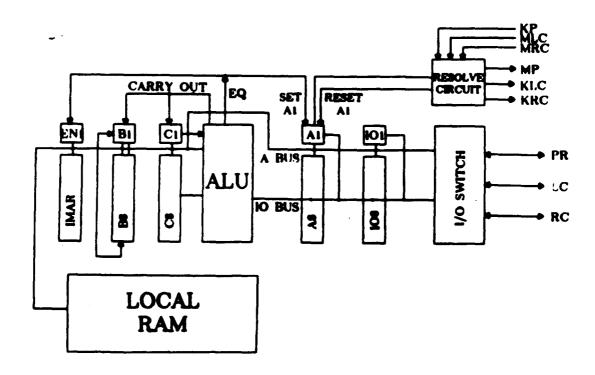

## 3.1. The Small Processing Element Design

Figure 3-2 depicts the main functional blocks of the NON-VON 3 PE. They are the eight-bit arithmetic logical unit (ALU); an array of five byte registers, called A8, B8, C8, IO8, and IMAR; an array of five one-bit registers, called A1, B1, C1, IO1, and EN1; a 64 word × 9-bit

random access memory (RAM), and two special combinational networks, called the I/O switch and the RESOLVE circuit [Shaw 84b]. A PE executes the instructions broadcast by the CP as long as its enable bit. EN1, is set. If the enable bit is reset, the PE is disabled and only an ENABLE instruction will activate it again.

Two internal buses, called the A bus and the IO bus, run through the data path Both are capable of transferring either one- or eight-bit data, depending on the instruction being executed. The A bus is used to transfer data between the registers, the RAM, and the I/O switch. The IO bus is required to support inter-PE communication, as will be seen in the following section. It connects the dual-port registers IO and A, the I/O switch, and the ALU.

The ALU comprises an eight-bit comparator that compares the contents of the A8 register with one of the other eight-bit registers, and sets A1 and B1 to indicate the result. If A8 is compared with B8, for example A1 is set iff A8 is equal to B8, and B1 is set iff A8 is less than B8. Eight-bit addition, subtraction, and logical operations are also supported by the ALU In the case of addition and subtraction, C1 is used to hold the carry output. One-bit logical operations are also supported by a special one-bit logical function unit. The RAM allows access to one 8- or 1-bit location per instruction cycle, and the IMAR register is used to store the memory address used in RAM operations.

Figure 3-2: NON-VON 3 Block Diagram of the Small Processing Element (From [Shaw 84b])

## 3.2. Communication in NON-VON

Inter-PE communication in NON-VON is supported by the I/O switch, which is a matrix of pass transistors that routes data between the two internal buses and the I/O ports. The NON-VON I/O switch supports the following three modes of communication.

1 Global bus communication, supporting both broadcast by the CP to all PE's in the PPS as required for SIMD execution, and data transfers from a single selected PE to the CP. No concurrency is achieved when data is transferred from one PE to another through

the CP using the global communication instructions. An instruction called RESOLVE can be used to disable all but a single PE chosen from a specified set of PE's. This is an example of a hardware multiple match resolution scheme, in the terminology of the literature of associative processors. The CP, upon executing a RESOLVE instruction, is able to determine whether executing the instruction has resulted in any PE being enabled. The REPORT instruction transfers data from the single chosen PE to the CP using global bus communication.

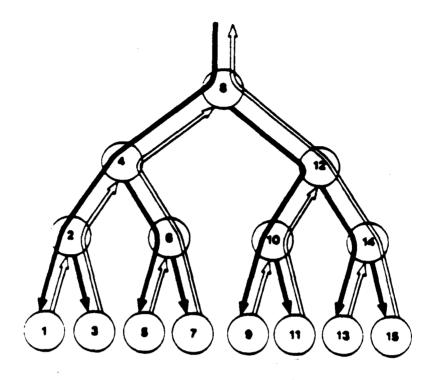

- 2. Tree communication, supporting data transfers among PE's that are physically adjacent within the PPS tree. Instructions support data transfers to the parent (P), left child (LC), and right child (RC) PE's Full concurrency is achieved in this mode, since all nodes can communicate with their physical tree neighbors in parallel.

- 3 Linear communication, in which the whole tree is reconfigured to act as a linear array of PE's. This mode of communication supports data transfers to the left neighbor (LN) or right neighbor (RN) PE's in the linear array. Linear communication is useful for applications that require a predefined total ordering of data. Figure 3-3 shows how the linear logical sequence is mapped onto the tree-structured physical topology of the PPS by inorder enumeration [Knut 73]. The paths needed to transfer data concurrently between linear neighbors in the tree concurrently are shown in Figure 3-3. Two phases are required to complete the linear communication cycle. Note that every other element in the inorder sequence is a leaf node. In the first phase, data is transferred along the arrows originating from the leaf PE's, while in the second phase, data passes along the black arrows terminating at the leaf PE's.

The original NON-VON architecture which was not intended to efficiently support computer vision applications, differs from other proposed highly parallel hierarchical image understanding architectures (for example, [Tani 83]) in that it does not employ any extra physical links to perform mesh neighbor communication. This has certain advantages from a hardware point of view, as it results in a fixed

Figure 3-3: Inorder Embedding of the Linear Array (From [Shaw 82])

number of pins per integrated circuit chip, independent of the number of PE's on that chip. This makes it possible to increase the size of the tree as chip dimensions scale down by simply embedding more PE's on the chip increasing the machine size involves only removing the old PE chips and plugging in the new ones. On the other hand, the lack of mesh connections slows many local operations in which the output value at an image point depends on its own image value and that of neighbor points

A vision-oriented variant of the NON-VON 3 machine that includes mesh connections to supplement the current tree-structured architecture is now in the early stages of design. Alternative algorithms exploiting these

hardware modifications will be discussed later in this thesis.

NON-VON's other special hardware features, including its ability to be configured logically as a linear array, its fast global instruction broadcast and its hardware multiple match resolution scheme, have proven useful in the vision algorithms we have developed to overcome some of the problems related to the communication bottleneck generally associated with tree architectures.

#### 3.3. N-PASCAL: An Overview

In this section we introduce a PASCAL-based parallel language called N-PASCAL, which will be used to describe the NON-VON vision algorithms presented in this thesis. This language is closely related to a PASCAL-based parallel language, NV-PASCAL, that has been designed to be used on SIMD architectures [Baco 82]. The principal idea behind the design of N-PASCAL has been to create features that make full use of the machine's parallel capabilities while retaining all of the high-level constructs of PASCAL.

N-PASCAL is based on standard PASCAL as described in [Jens 74]. One new data type and two extra constructs have been added to standard PASCAL. The new data type is referred to as the vector—var (for vector variable), and the two new constructs are the parallel assignment and WHERE statements. In addition, built-in functions allow

the programmer to explicitly make use of the NON-VON tree communication instructions. We now briefly describe the N-PASCAL constructs that have been used to describe image understanding algorithms presented in this thesis.

The new data type vector—var is used to express the parallelism in the language. Vector variables reside in the PPS and are associatively addressed, whereas standard PASCAL variables reside in the CP and are sequentially addressed. In the following sections, variables that are defined to be of type vector—var are referred to as vector variables, while scalar variables refer to those that are stored in the CP. In the NV-PASCAL procedures described in this thesis, we will use italics to refer to scalar variables and capital letters to refer to vector variables. Small bold letters will be used to refer to the reserved keywords of the language.

There are two types of statements in N-PASCAL sequential and parallel. The sequential statements are those of standard PASCAL, while the parallel statements are those that operate on vector variables. The assignment statement can be either sequential or parallel. The sequential assignment statement is the assignment statement encountered in standard PASCAL. The parallel assignment statement is the one that refers to a variable that is defined as a vector variable. The parallel assignment statement is executed concurrently in all active PE's in the machine For

example, upon execution of the following segment of an NV-PASCAL program

vector\_var COUNTER integer;

begin

COUNTER := 0;

the vector variable COUNTER stored in all PE's is initialized to zero

The WHERE statement is a form of parallel conditional statement that operates only on vector variables. The form of the WHERE statement is as follows:

WHERE < conditional expression > DO < statement > [ ELSEWHERE < statement > ];

It is used to first select only those PE's with vector variables that satisfy the boolean expression. The statement following the DO is then executed in only those PE's. If the optional ELSEWHERE clause is included, the statement following the ELSEWHERE keyword is executed in the subset of the PE's that failed to satisfy the original conditional expression. An example of the WHERE statement follows:

vector\_var

COUNTER, VALUE integer;

where COUNTER > 50 do VALUE = 100 elsewhere VALUE = 0,

The vector variable COUNTER is tested in all PE's and in those PE's whose COUNTER value exceeds 50, the vector variable VALUE is set to

100 In all PE's whose COUNTER value is less than or equal to 50, the variable VALUE is set equal to zero. An important point to remember is that the WHERE statement in general executes both the statement following the DO and the statement following the ELSEWHERE (the exception being the case in which all or none of the PE's satisfy the condition).

Built-in functions based on the NON-VON instruction set are employed to implement operations that use the tree communication modes of the machine, which are described in Section 3.2. Function names that start with 'N\_' correspond to NON-VON machine instructions, and their parameters correspond to the arguments of these instructions.

# Chapter 4

## Image Representation

In this chapter, we examine certain data structures for representing images on parallel tree-structured machines. This subject is of prime importance, as it greatly affects the design of image algorithms. Methods used for image input and output are also affected by the choice of data structure. The choice of a data structure for a set of problems can even influence the design of a machine architecture for efficiently solving those problems. For example, mesh-connected architectures map into hardware the two-dimensional array data structure used most commonly to represent images on sequential machines. Similarly, the hierarchical nature of the NON-VON architecture affects the choice of data structures used to represent images on it.

An overview of data structures used to represent images on sequential machines is presented in Section 4.1, with an emphasis on hierarchical data structures. We then demonstrate how two of these hierarchical data structures can be modified to represent images on binary trees. A procedure for initializing the NON-VON tree is presented in Section 4.2. Algorithms and issues related to the loading and unloading of images in

procedures used to build the data structures employed in the algorithms described in this thesis

## 4.1. Image Data Structures: An Overview

Storing raw pictorial data requires a large amount of memory About 512 x 512 bytes are needed, for example, to store a single black and white television frame Two-dimensional arrays are commonly used for storing images, where every element in the array represents a corresponding area in the image space. These small areas are referred to Pixels can take different shapes, producing different as pixels Most commonly they are squares, but they can also be tessellations rectangles, triangles, or hexagonals. The value of the array elements can represent the intensity of the image at the corresponding pixels or other values such as the spectral components of color pixels. Mesh-connected architectures use this data structure to represent images, with each PE being assigned a pixel, or a block of pixels in the case where there are fewer PE's than there are pixels in the image. Other data structures used to represent images include chain codes, graphs, and relational databases See [Tani 80b] for further discussion of these data structures.

Hierarchical data structures can be mapped naturally onto tree machines. They are often used in image understanding tasks because they allow many algorithms to be expressed in forms suitable for divide-

and-conquer techniques. They also support certain techniques for data compaction and image transmission [Know 80]. Hierarchical data structures include multi-resolution pyramids, regular decompositions, and quadtrees [Tani 80b].

In what follows, we present two of these hierarchical data structures, namely multi-resolution pyramids and a modified version of quadtrees called binary image trees, and show how they are used to represent images on NON-VON.

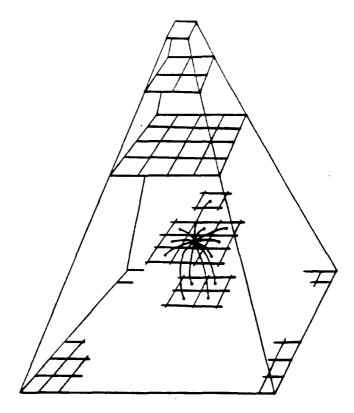

#### 4.1.1. Multi-Resolution Pyramids on NON-VON

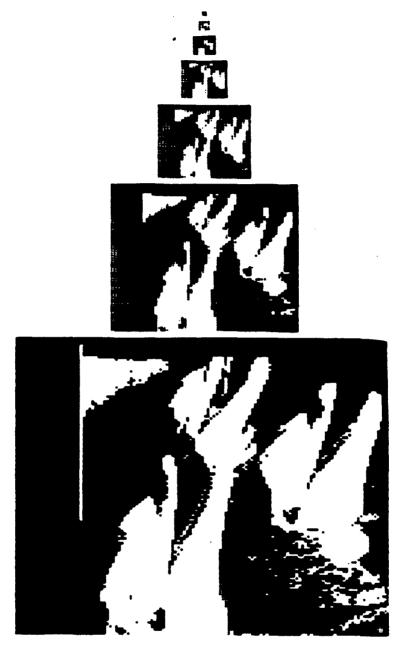

A multi-resolution pyramid can be defined as a sequence  $\{I(L), I(L-1), I(0)\}$  of images, each represented as a two dimensional array, where I(L) is the original image, and I(m-1) is a version of I(m) at half the resolution. (This is the same definition Tanimoto used in [Tani 80b].) The term "image resolution" refers to the number of pixels used to describe the image. For example, if I(m) represents a version of the image with resolution  $64 \times 64$ , then I(m-1) represents the same image at resolution  $32 \times 32$ . Figure 4-1 shows an image and its multi-resolution pyramid representation. The pyramid provides reduced resolution versions of the image. If more than one operation is to be performed on the image, then each operation should use only the resolution required for this operation. The extra amount of memory required to store the pyramid representation is 1/3 that of the amount of memory used to

Figure 4-1: An Image and its Multi-Resolution

Pyramid Representation

(From [Tani 75])

store the original image

Multi-resolution pyramids can also be defined in terms of trees rather than arrays. In this case, they are referred to as pyramid trees. A

multi-resolution pyramid is defined in terms of quartic (4-ary) trees as follows. The leaf nodes represent the pixels of the image at its highest resolution (the base of the pyramid), and the nodes of an internal level of the tree represent the pixels of a reduced resolution version of the image. Thus, going from one level in the tree to the level above it results in an image with one-fourth the resolution. Note that the four child nodes of a parent node represent a  $2 \times 2$  region in the image.

An image at a specific level can be computed from the image at the level below it in the pyramid tree in different ways. Typically, a parent node is set equal to the average value of its four children. This averaging process can be viewed as a kind of low-pass filtering of the image followed by resampling. Hence, images with lower resolution retain the gross features of the image. For binary images, the averaging process is defined to result in the binary value 1 only if three or more of the children have the binary value 1, and to result in 0 otherwise.

In the NON-VON tree, the leaf level is used to store the original image, whereas the internal levels are used to represent the image at coarser resolutions. Since NON-VON is a binary tree, the resolution reduction from one level in the tree to the level above it is only a factor of two, and hence two NON-VON levels are used to effect the same reduction as one level in the multi-resolution pyramid. We use this image representation whenever we deal with gray-scale images. In

Section 42 we show in detail how this can be done

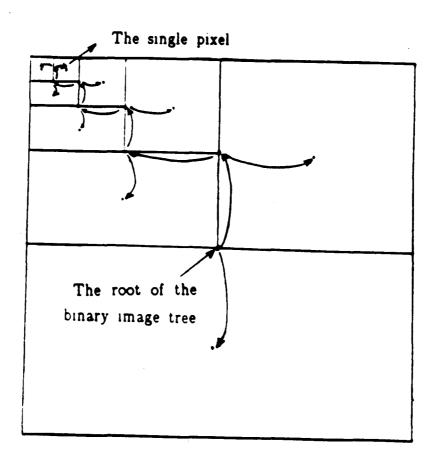

## 4.1.2. Binary Image Trees on NON-VON

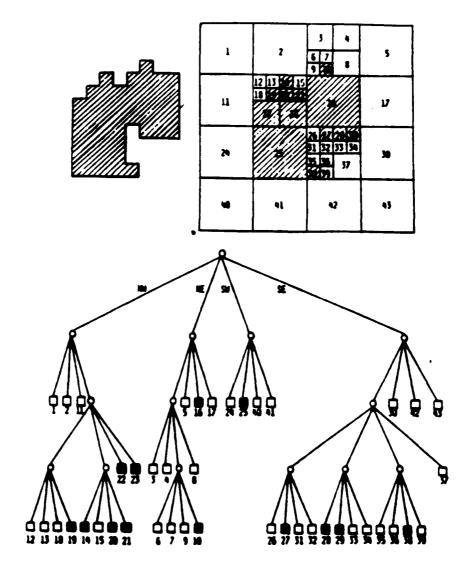

Binary image trees are a variant of quadtrees, which were proposed by Knowlton [Know 80] as an encoding scheme for compactly transmitting gray-scale and binary images. Quadtree data structures are similar in many aspects to multi-resolution pyramids. A good way to visualize the quadtree is by assuming that the image is a square whose dimensions are a power of 2. The quadtree data structure is built by subdividing the whole image into four square quadrants with dimensions that are half that of the image. This process is repeated recursively for each quadrant n times, until the single pixel level is reached, as shown in Figure 4-2. The root of the quadtree corresponds to the whole image, the leaves correspond to the single pixels, and the nodes of the tree correspond to quadrants of the square represented by their parent node. If the four children of a node share the same value, they are all deleted and the father's value represents them all.

Quadtrees are used mainly to encode binary images, and the nodes in a quadtree are interpreted differently from the nodes in a multi-resolution pyramid tree. In the case of binary images, nodes of the quadtree can take one of three values. If the node's children are all black, then the node is black. If they are all white, then the node is white. The node will take the value gray if its children do not have the same value, or if

Figure 4-2: A Picture and its Quadtree (From [Same 82])

a black node may thus be omitted, significantly reducing the amount of memory required to store the picture on a sequential machine.

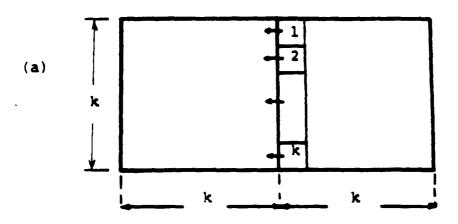

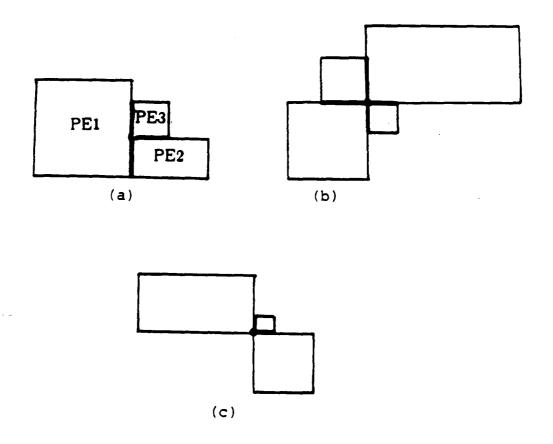

Binary image trees are a variant of quadtrees in which the whole image is subdivided into two halves. This process of subdividing into two

halves is repeated recursively until the single pixel level is reached. Figure 4-3 illustrates the binary image tree data structure. Note that the shape-of the subdivisions changes from level to level in the binary image tree. Specifically, it is either a square or a rectangle with the width equal to twice the length. We will refer to these subdivisions as rectangles throughout the rest of this thesis.

Figure 4-3: Binary Image Tree Rectangle Arrangement

The shape of the rectangles at any level can be determined by testing to

see if the level number is odd or even. Going from one level to the next

level down the tree increases the resolution by only a factor of two.

while in quadtrees the resolution is increased by a factor of four.

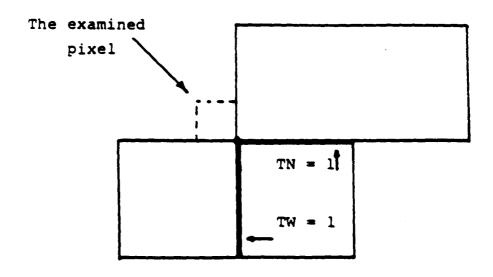

Binary image trees are mapped naturally onto binary tree machines. On NON-VON, the leaf processors are used to store image information at the single pixel level, while non-leaf PE's correspond to rectangles of size larger than the pixel size. A record associated with each PE is used to store information about the location, size, contents, and adjacency relation of the part of the image it represents. A flag associated with each PE indicates whether the rectangle represented by that PE is part of the binary image tree. An algorithm for building the binary image tree and storing the rectangle information is described later in this chapter. We will use binary image trees whenever we are dealing with binary images.

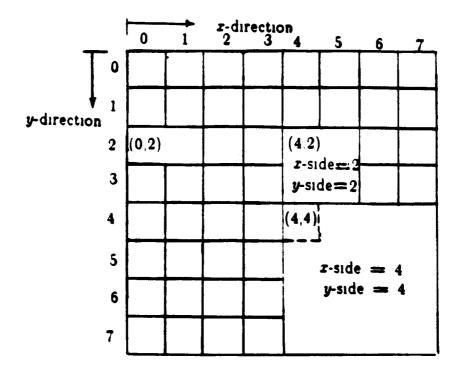

### 4.2. Initialization and Image Loading

Image processing algorithms on NON-VON use information that is stored initially in each PE. Each PE corresponds to a rectangle in the original image. On the leaf PE level, each rectangle corresponds to a single pixel in the two-dimensional array that represents the original image. The location of each rectangle is indicated by specifying the coordinates of its upper left-most corner pixel. The horizontal direction is referred to as the z-direction, while the vertical direction is referred to as the y-direction. The origin of the coordinate system (0,0) is the upper left-most pixel in the image, and the values of the coordinates increase to the right in the z-direction, and down in the y-direction, as shown in

Figure 4-3

In addition to the x-address and y-address, each PE stores the width (x-side), and the height (y-side) of the rectangle it represents. For a  $256 \times 256$  image, four bytes are needed to store the location and size information. The root level is labeled the 0-th level, while the leaf level is the n-th level. Other information is also stored in each PE, and will be described later.

Figure 4-4: Coordinate System for Binary Image Trees

The N-PASCAL algorithm for initializing the NON-VON tree follows:

/\* The following variables are defined in the main driver of all vision

manner. This has led to a surge in research aimed at developing new computer organizations that meet the large computational and decision requirements of image analysis tasks by exploiting the new technology. Various kinds of special parallel machines for computer vision have been proposed and some have been implemented; examples are described in [Duff 76], [Krus 76], [Dyer 81], [Kush 83], [Pott 83], and [Reev 84].

The organization of some of the proposed machines is based on a very large number of very small processing elements (PE's). Throughout this thesis, we will refer to such machines as fine-grained or highly parallel machines. In such machines, different schemes are used to interconnect the PE's. For example, the PE's can be connected together in the form of a two-dimensional mesh, or they can be placed at the nodes of a binary tree. If all the PE's simultaneously execute the same instruction on their own data, the machine is said to be executing in single instruction stream, multiple data stream (SIMD) mode [Flyn 72]. On the other hand, if the PE's execute different instruction streams concurrently on different data streams, then the machine is said to be executing in multiple instruction stream, multiple data stream (MIMD) mode.

In this thesis, we investigate how fine-grained tree-structured SIMD computer architectures, which have favorable characteristics for efficient VLSI implementation, can be used for the rapid execution of a wide range of vision tasks. We also discuss certain limitations of these

procedures described in this thesis. Some of these variables are used in the initialization procedure. The rest are used in other procedure definitions. \*/

```

program vision_algorithms();

vector_var

XSIDE, YSIDE, XADD, YADD: integer;

GRAY_VALUE, TREE, COMP_LABEL: integer;

FQUAD: char;

BINARY: boolean;

```

/\* The following procedure marks leaf PE's by setting the variable LEAF equal to 1 in all leaf PE's and 0 elsewhere. \*/

```

Procedure mark_leaf(var LEAF: boolean);

vector_var

TEMP: boolean;

begin

```

/\* 1 Initialize TEMP to the value 0 in all PE's. On executing a "receive from left child" instruction (RECV1 LC), all leaf PE's receive a logical 1. All other PE's receive whatever is sent by their left children. This procedure thus serves to mark all leaf PE's. The N\_RECV1 is a primitive function that corresponds to the NON-VON instruction RECV1. On executing this function each PE receives the value of its left child boolean variable TEMP into its own variable LEAF. \*/

```

TEMP = false,

N_RECVI(LC, TEMP, LEAF);

end,

```

```

Procedure tree_init(no_levels INTEGER),

var

lev_count, x, y integer;

vector_var

XADD1 YADD1 integer,

LEAF N boolean,

begin

```

/\* 1 The initialization algorithm starts by initializing the size information It starts at the leaf level by storing the value 1 in each PE width and length variables (XSIDE, YSIDE) The function mark leaf(L) sets the boolean variable L to 1 only in leaf PE's. The boolean variable N is used to mark the level up the tree next to the current level. It is set equal to 0 only in current level PE's, and to 1 elsewhere. A level counter lev count is initialized to 0. \*/

```

lev_count = 0;

x = 1, y = 1,

N = true,

mark_leaf(LEAF),

where LEAF = true do

begin

XSIDE = 1,

YSIDE = 1,

N = false,

end,

```

/\* 2 Enable PE's on the next level up the tree. N\_RECV1(LC, N, N) sets the variable N equal to 0 only in PE's whose children have the N variable set to 0. The size variables are then computed on that level If the level number is equal to no\_levels, then the size initialization is complete and the algorithm starts address initialization; otherwise the size initialization continues. \*/

```

while lev_count < no_levels do

begin

N_RECV1(LC, N, N);

if lev_count mod 2 = 1 then

z = z * 2

else y = y * 2,

where N = false do

begin

XSIDE = z,

YSIDE = y;

end.

lev_count = lev_count + 1,

end.

```

/\* 3 At this point only the root PE has its N variable set to 0 Set

the variables XADD and YADD in the parent PE equal to 0. \*/

```

where N = false do

begin

XADD := 0;

YADD := 0;

end:

```

/\* 4. For address information, left children always have the address of their parents. This step computes the right child address of each enabled parent and stores the computed values in the variables XADD1 and YADD1. Left children are then enabled. Read the address of their parent and store it as their own address. The same is repeated for right children, except that they read their address from the variables XADD1, and YADD1. \*/

```

while lev count > 0 do

begin

if lev count mod 2 = 0 then

begin

XADD1 = XADD

YADD1 = YADD + YSIDE div 2

end

else

begin

XADD1 = XADD + XSIDE div 2

YADD1 = YADD:

end.

N SEND8(LC, XADD, XADD);

N SEND8(LC, YADD, YADD),

N SEND8(RC, XADD1, XADD),

N SEND8(RC, YADD1, YADD),

lev count = lev count - 1,

end:

end.

```

The initialization algorithm takes time proportional to the number of levels in the tree (19 levels in the case of a 512 X 512 image). The

NON-VON 3 code for this procedure is presented in Appendix B. It takes

18 µsec to initialize one level at 4 Mhz (68 NON-VON 3 instructions)

Initializing a tree with 15 levels thus requires 0.27 msec

#### 4.2.1. Loading the Image

In tree machines, loading and unloading the tree through the root can be a bottleneck for algorithms with extensive I/O operations. To overcome this, a real NON-VON system would load and unload image data in parallel through I/O devices connected to all PE's at some intermediate level in the PPS tree. Loading an image point through the root only involves first broadcasting its z- and y-coordinates and enabling the PE with the same values for z and y on the leaf level. The image point value is then broadcast and stored in the enabled PE. The N-PASCAL procedure for this loading procedure follows:

```

Procedure tree_load1(z_side, y_side integer);

var

i, j integer;

begin

```

/\* 1. The function read\_file(file-name) returns the next integer value in the file "file-name". The procedure arguments are the lengths of the image sides. \*/

```

for i = 0 to x_{side-1} do

for j = 0 to y_{side-1} do

where ((XADD = i) \text{ and } (YADD = j))

do GRAY_{VALUE} = read_{file(image)};

end.

```

The NON-VON 3 code for this loading procedure is included in Appendix B Seven NON-VON 3 instructions, requiring about 20  $\mu$ sec of execution time at 4 Mhz, are used to load one image point. Loading an 128  $\times$  128 image through the root thus takes about 32 msec using this procedure.

Instead of broadcasting the data byte by byte and isolating a single destination leaf PE at a time, blocks of image data can be broadcast and stored in the PE's in an intermediate level. These PE's then load the blocks of data in parallel into the leaf PE's in their subtrees. Next we describe the N-PASCAL procedure to perform this operation along with an analysis of the time required for its execution.

```

Procedure tree_load2(x_side, y-side: integer);

var

i. j. k. n1 integer,

vector_var

LEAF. N boolean;

X1, Y1, TEMP integer;

begin

```

/\* 1 The leaf PE's are marked, and so are the PE's on the intermediate level. We assume a block size of 16 bytes \*/

```

N = false;

mark\_leaf(LEAF);

where ((XSIDE = 4) \text{ and } (YSIDE = 4)) \text{ do } N = true;

```

/\* 2 Loop to load the blocks in intermediate level PE's starting at RAM location 16 \*/

```

i = 0;

while i < x side-1 do

begin

j = 0

while j < y_side-1 do

begin

where ((XADD = i) \text{ and } (YADD = j) \text{ and } (N = \text{true}))

do for k = 1 to 16

do N BROADCAST8(read file(image), RAM(15+k)),

j = j + 4

end.

i = i + 4

end:

/* 3 Now load the blocks in parallel into the leaf PE's. The addresses

of the PE's relative to the address of the root of the subtree are stored

in X1 and Y1 */

X1 = XADD \mod 4

Y1 = YADD \mod 4

n1 = 16.

/* Loop until the first block element reaches the leaf PE's. */

for k = 1 to 4 do

begin

where N = \text{true do } N \quad \text{READRAM8}(n1, \text{ TEMP});

N RECV8(P, TEMP, TEMP);

nI = nI + 1,

end.

/* Now loop to load the elements */

for i = 0 to 3 do

for j = 0 to 3 do

begin

where ((i = X1) \text{ and } (j = Y1)) do

GRAY VALUE = TEMP:

if n1 < 32 then

where N = \text{true do } N = \text{READRAM8}(n1, \text{TEMP});

N RECVS(P. TEMP, TEMP),

n1 = n1 + 1,

```

end:

end;

In the above algorithm, Step 2 is similar to the first loading procedure. It takes about 2  $\mu$ sec to load the first byte, but the next 15 bytes in the block are loaded at the rate of 4 bytes per  $\mu$ sec. Thus, it takes about 6  $\mu$ sec to load a block of 16 bytes, and about 6.14 msec to load a 128  $\times$  128 gray-scale image. Step 3 requires about 10 NON-VON 3 instructions to load one byte of the block into a leaf PE. Thus, about 0.04 msec is needed to perform this step, which is very small compared with the time required to execute Step 3.

It should be noted that increasing the block size reduces the time required to perform the first step of the second loading procedure. For example, a block size of 32 requires 10  $\mu$ sec to be loaded into the intermediate level, and hence 5.12 msec are required to load a 128  $\times$  128 gray-scale image. Increasing the block size also increases the time required to load the blocks in the subtrees. Using the numbers cited above, the time to load an image of size A using block size S can be computed by the following expression

loading time = (A/S)(2 + S/4) + 25S µsec.

The value of S that minimizes this expression is equal to  $0.9A^{1/2}$ . Thus, a block size of about 115 bytes results in the minimum loading time for an image of size 128  $\times$  128. If the size of the available memory in each

PE is less than this number, then using as much memory as we can for this loading procedure results in the minimum loading time. The NON-VON 3 code for this procedure is presented in Appendix B.

The time required to load images could be reduced significantly through parallel loading of the subtrees rooted by the PE's at some intermediate level. If the I/O devices are connected to the intermediate level containing 64 PE's, then the above described procedures would be executed in parallel in the 64 subtrees, and the time of execution would be reduced approximately by a factor of 64. If more than one image are to be stored in the tree, then the address and size information stored in each PE will be common to these images. Other image information has to be duplicated for each loaded image.

Table 4.1 provides a summary of the execution times for different NON-VON I/O procedures and for some existing parallel image processing machines

#### 4.2.2. Building the Binary Image Tree

In this subsection, we describe the procedure for constructing the binary image tree representation of a binary image stored in the leaf PE's. The vector character variable FQUAD is used in each PE to indicate the type of rectangle held by this PE. The value 'B' refers to black rectangles, 'W' to white ones, and 'G' to gray rectangles. The value 'N' indicates

Table 4-1: Image I/O Execution Time for Some Parallel Machines

| The Parallel Machine                                           | Instruction<br>Rate | I/O time (msec)<br>(128 × 128) |

|----------------------------------------------------------------|---------------------|--------------------------------|

|                                                                |                     |                                |

| ICL DAP                                                        | 4 Whz               | 4.096                          |

| Goodyear aerospace MPP                                         | 10 Mhz              | 0.102                          |

| 101-A01 3                                                      |                     |                                |

| a. Loading through the root only                               | 4 Mhz               | 5.120                          |

| b. Loading through I/O device<br>connected to the 64 PE level. | 4 Ma                | 0.080                          |

|                                                                |                     |                                |

that the rectangle is white or black but has been merged with a similar rectangle to form a larger one. The vector integer variable TREE corresponds to the number of black pixels in the rectangle represented by the PE. It takes the value 0 when the rectangle is white, and is equal to the area of the rectangle in the case of black rectangles. We assume that the binary image is stored in the NON-VON tree in the vector variable BINARY. The N-PASCAL algorithm for building the binary image tree follows:

```

Procedure build_binimg(no_levels INTEGER),

label 2;

var

cur_lev integer;

vector_var

GV1_GV2_integer,

FQ1_FQ2_char;

LEAF, N_boolean,

begin

```

/\* 1 Enable all PE's on the leaf level. Set N equal to 0 only in the current level. \*/

```

N = true,

cur_lev = 1,

mark_leaf(LEAF),

where LEAF = true do

begin

where BINARY = true do TREE = 1

elsewhere TREE = 0,

N = false,

end

```

/\* 2 Mark PE's on the level just above cur\_lev. Let all the enabled PE's read the values of TREE and FQUAD in their children. The value of TREE in the enabled PE's will be set equal to the sum of the two TREE variables in their children. FQUAD will be set to 'G' if FQUAD in the two children are different, or if one of them is 'G'. If the two variables FQUAD in the two children are both either 'W' or 'B', then the parent FQUAD will be set to the mutual value and the FQUAD in the two children will be set to 'N'. \*/

/\* 3 If the root is reached, stop, otherwise, enable all PE's above and

```

go to step two. */

if cur_lev <> no_levels then

begin

cur_lev = cur_lev + 1;

goto 2;

end;

end;

```

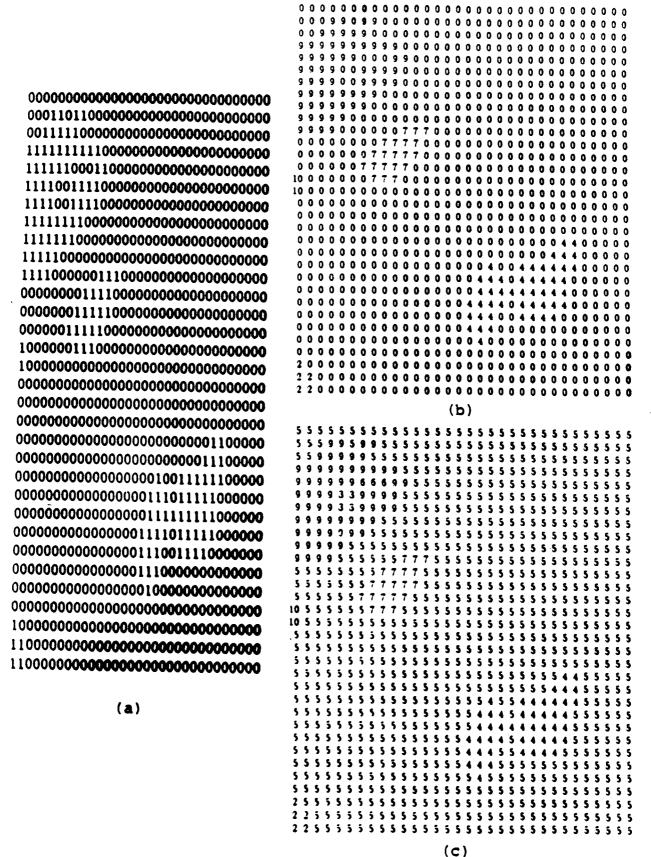

After the above algorithm is executed, the root PE has its TREE variable set equal to the number of black pixels in the whole image, and in general, each PE's TREE variable will be equal to the number of black pixels in the tree rooted by that PE. Steps 2 and 3 are repeated a number of times equal to the number of levels in the tree. Thus, the algorithm takes time proportional to the height of the binary tree. The NON-VON 3 code is included in Appendix B. It requires about 50 NON-VON 3 instructions per level (12.5  $\mu$ sec); for a tree with 15 levels (corresponding to a 128  $\times$  128 original image), the execution time for this procedure is thus about 0.175 msec. Figure 4-5 shows a binary image and the binary image tree representation of it as output by the functional simulator

#### 4.2.3. Building the Multi-Resolution Pyramid

The multi-resolution pyramid representation of a gray-scale image can be built using a procedure similar to the one used to build the binary image tree. The variable GRAY\_VALUE in each PE is set equal to the average of the values of GRAY\_VALUE in its two children. This step is repeated a number of times equal to the height of the tree. The

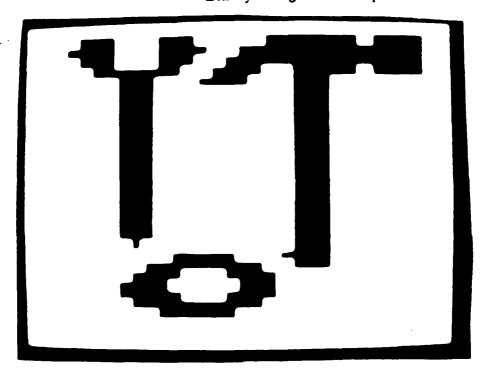

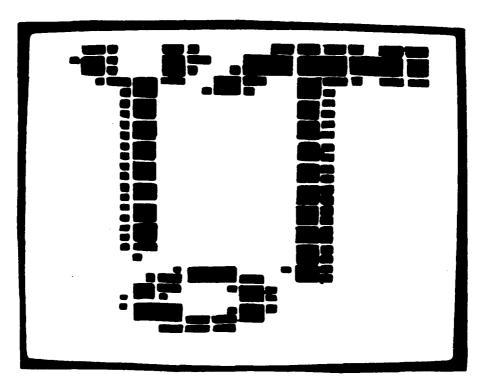

Figure 4-5: A Binary Image and its

Binary Image Tree Representation

(a) The Input Binary Image

(b) The Binary Image Tree