## Advanced Integration of Devices Enabled by Laser Crystallization of Silicon

Vincent W. Lee

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

Vincent W. Lee

All Rights Reserved

#### ABSTRACT

## Advanced Integration of Devices Enabled by Laser Crystallization of Silicon

## Vincent W. Lee

The push for higher levels of performance drives research and innovation in all areas of electronics. Thus far, shrinking circuit sizes and development of new material systems have satisfied this need. Continued scaling and material improvements have become increasingly difficult; simultaneously, more functionality is needed in smaller spaces. Advanced integration techniques provide a solution by engineering together previously incompatible systems.

The fabrication of high-performance devices typically requires high temperature processing steps. Since fabrication occurs sequentially, the high temperature prevents the direct integration of two high-performance layers, as completed devices cannot withstand the processing temperatures of subsequent steps. There are significant challenges to integrating process-incompatible systems, and techniques such as wafer bonding, heteroepitaxial growth, and various thin film technologies have shown limited success.

In this work, advanced integration is achieved through laser crystallization processes. Unique to laser methods is the ability to locally heat the surface of a material while keeping the underlying substrate at room temperature. This property allows for high performance electronic materials to be integrated with substrates of different functionalities. This thesis focuses on three key components for advanced integration:

- 1. Laser-crystallized electronic devices, 2. Relevant substrates for integration, and

- 3. The feasibility of integrating of laser-crystallized devices with low-temperature

substrates.

Two types of laser-crystallized devices are explored. Thin-film, laser-crystallized silicon transistors are fabricated at low-temperatures and exhibit high mobilities above  $400 \text{ cm}^2/Vs$ . Vertical structure diodes built from laser-crystallized silicon outperformed epitaxially-grown diodes of the same geometry.

Light emitting diode (LED) arrays are fabricated from compound semiconductor substrates and tested for display applications. These LED arrays are envisioned to sit underneath the laser-crystallized devices, enabling new applications where both high brightness and high performance transistors are needed. Substrates of low- $\kappa$  dielectric material are also of interest, as they are widely used for their low capacitance properties. Preliminary results suggest that laser crystallization of silicon can be successfully performed on a low- $\kappa$  dielectric.

In addition to enabling new device architectures, it is important for laser crystallization methods to leave the underlying layers unaffected. Simulations of the laser irradiation process predict substrate temperatures to reach only 70°C even when the surface reaches the melting temperature of silicon (1400°C). Integration feasibility is further investigated with measurements on conventional front-end field effect transistors. When comparing properties from wafers with and without laser processing, no changes in transistor characteristics are observed.

In all three components of work, proof-of-principle devices and concepts lay out the groundwork for future investigation. The developed technologies have promising applications in both the microelectronics and display industry. In particular, the integration of LEDs and laser-crystallized silicon enables a high-brightness microdisplay platform for head-mounted displays, pico projectors, and head-up displays.

## Table of Contents

| 1 | Intr | roduction                                                           | 1  |

|---|------|---------------------------------------------------------------------|----|

|   | 1.1  | Background and Motivation                                           | 1  |

|   | 1.2  | Diodes, Light Emitting Diodes, and Field Effect Transistors         | 3  |

|   |      | 1.2.1 Diodes                                                        | 3  |

|   |      | 1.2.2 Light Emitting Diodes                                         | 6  |

|   |      | 1.2.3 Metal Oxide Semiconductor Field Effect Transistors            | 8  |

|   | 1.3  | Objectives and Approach                                             | 11 |

| 2 | Seq  | uential Lateral Solidification of Silicon for Thin Film Transistors | 12 |

|   | 2.1  | Introduction                                                        | 12 |

|   | 2.2  | Sequential Lateral Solidification Methods                           | 13 |

|   | 2.3  | Laser Crystallization Simulations                                   | 17 |

|   | 2.4  | Thin Film Transistors using Sequential Lateral Solidification       | 22 |

|   |      | 2.4.1 Fabrication of TFTs                                           | 22 |

|   |      | 2.4.2 Characterization of TFTs                                      | 24 |

|   |      | 2.4.3 Van der Pauw Sheet Resistance                                 | 27 |

|   | 2.5  | Conclusions                                                         | 30 |

| 3 | Ligl | nt Emitting Diode Array                                             | 31 |

|   | 3.1  | Introduction                                                        | 31 |

|   | 3.2  | Design                                                              | 34 |

|   | 3.3  | Fabrication                                                 | 36 |

|---|------|-------------------------------------------------------------|----|

|   | 3.4  | LED Characterization                                        | 42 |

|   | 3.5  | Projection Methods                                          | 44 |

|   | 3.6  | Directly Addressed vs. Passive Matrix vs. Active Matrix     | 50 |

|   | 3.7  | Conclusions                                                 | 52 |

| 4 | Lase | er Crystallization for 3DIC                                 | 53 |

|   | 4.1  | Introduction to Three Dimensional Integrated Circuits       | 53 |

|   | 4.2  | Laser Crystallization of Via Structures                     | 54 |

|   |      | 4.2.1 Laser Crystallization of Silicon Via on Tungsten      | 56 |

|   |      | 4.2.2 Laser Crystallization of Silicon Via on Silicon Wafer | 59 |

|   | 4.3  | Fabrication of Version One Diodes                           | 61 |

|   |      | 4.3.1 Characterization of Version One Diodes                | 62 |

|   | 4.4  | Fabrication of Version Two Diodes                           | 63 |

|   |      | 4.4.1 Characterization of Version Two Diodes                | 65 |

|   | 4.5  | Front-End CMOS devices                                      | 68 |

|   | 4.6  | Conclusions                                                 | 74 |

| 5 | Lase | er Crystallization of Alternative Material Systems          | 76 |

|   | 5.1  | Introduction                                                | 76 |

|   | 5.2  | Laser Crystallization on Low- $\kappa$ Dielectrics          | 77 |

|   | 5.3  | Laser Crystallization of Copper Interconnects               | 79 |

| 6 | Con  | aclusions and Future Work                                   | 84 |

|   | 6.1  | Contributions of This Work                                  | 84 |

|   | 6.2  | Future Work                                                 | 85 |

|   |      | 6.2.1 Lumiode: High Brightness Microdisplays                | 85 |

|   |      | 6.2.2 Three-Dimensional Integrated Circuits                 | 88 |

|   |      | 6.2.3 Crystallization of Copper                             | 80 |

| A  | Inte  | egration of Foundry CMOS with Or | ganic Light | Emitting | Diodes | 90  |

|----|-------|----------------------------------|-------------|----------|--------|-----|

|    | A.1   | Introduction                     |             |          |        | 90  |

|    | A.2   | Circuit Design and Layout        |             |          |        | 91  |

|    |       | A.2.1 Directly Addressed         |             |          |        | 95  |

|    |       | A.2.2 Current Mirror             |             |          |        | 95  |

|    |       | A.2.3 NAND Digital Drive         |             |          |        | 98  |

|    | A.3   | Test Circuit Board Design        |             |          |        | 101 |

|    | A.4   | Experimental Results             |             |          |        | 103 |

|    |       | A.4.1 Wirebond Protection        |             |          |        | 103 |

|    |       | A.4.2 Organic LED Fabrication    |             |          |        | 105 |

|    | A.5   | Conclusion and Future Work       |             |          |        | 107 |

| Bi | bliog | graphy                           |             |          | -      | 107 |

## List of Figures

| 1.1 | Schematic drawing of p-n junction showing its depletion region and                        |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | drift and diffusion currents                                                              | 4  |

| 1.2 | Band diagram for a p-n junction diode in (a) equilibrium state, (b)                       |    |

|     | reverse bias, and (c) forward bias                                                        | 4  |

| 1.3 | Typical Current-Voltage characteristic of a semiconductor diode. Adapted                  |    |

|     | from reference [12]                                                                       | 5  |

| 1.4 | Band diagram of LED heterojunction. Electrons and holes are confined                      |    |

|     | within the middle region where recombination occurs and photons are                       |    |

|     | emitted                                                                                   | 7  |

| 1.5 | Cross sectional scanning electron micrograph of LED heterojunction.                       |    |

|     | The n-AlGaAs and p-AlGaAs have a larger band gap. Electrons and                           |    |

|     | holes in the intrinsic-Al $_{0.3}{\rm GaAs}$ layer where light emission occurs. $$ . $$ . | 7  |

| 1.6 | Standard n-channel MOSFET structure in (a) equilibrium, (b) accu-                         |    |

|     | mulation when a negative gate bias is applied, and (c) inversion when                     |    |

|     | a positive gate bias is applied                                                           | 8  |

| 1.7 | Typical current-voltage characteristics of an n-channel MOSFET. Adapted                   | l  |

|     | from reference [12]                                                                       | 9  |

| 2.1 | Scanning electron micrographs of defect-etched samples following laser                    |    |

|     | annealing. (a) Excimer Laser Annealing method. (b) Line-Scan SLS.                         |    |

|     | (c) Two-Shot SLS. (d) Dot SLS. [20]                                                       | 14 |

|     |                                                                                           |    |

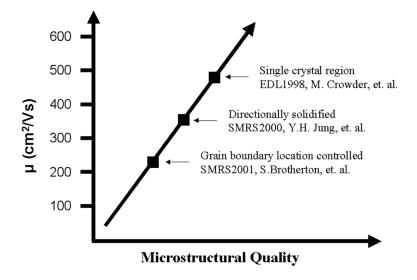

| Electron mobilities of materials prepared with different SLS methods.                |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Grain boundary location controlled, or Two-Shot SLS. Directionally                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Solidified, or Line-Scan SLS. Single Crystal Region, or Dot SLS. $[30]$ .            | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

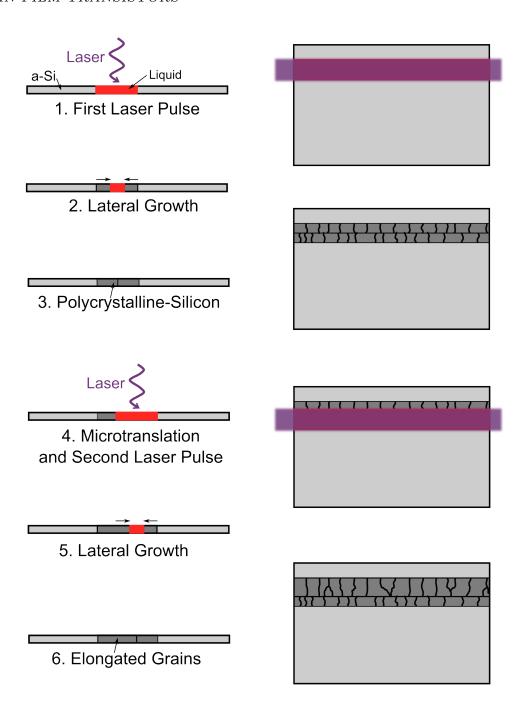

| Cross section (left column) and top view (right column) of line-scan                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| sequential lateral solidification (SLS) process flow                                 | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

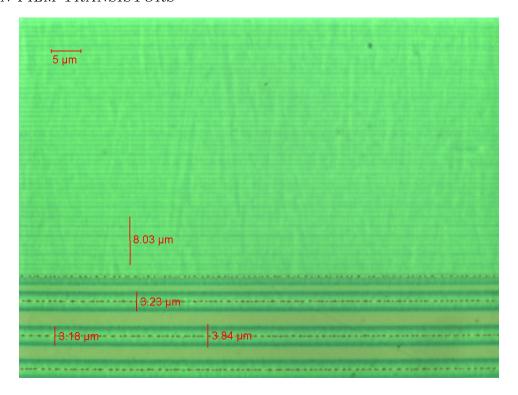

| Micrograph of line-scan SLS method. Bottom of micrograph shows a                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| single laser beam with a width of around 3.5 $\mu$ m. Top of micrograph              |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| shows typical Line-Scan SLS material                                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

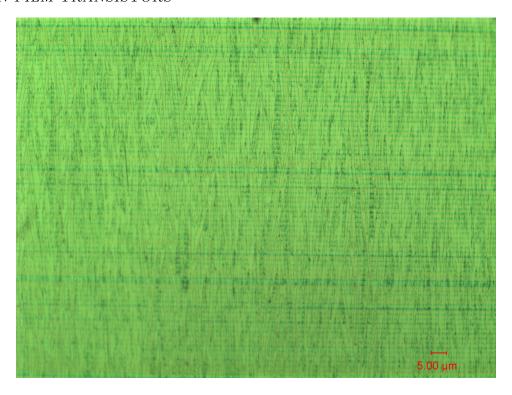

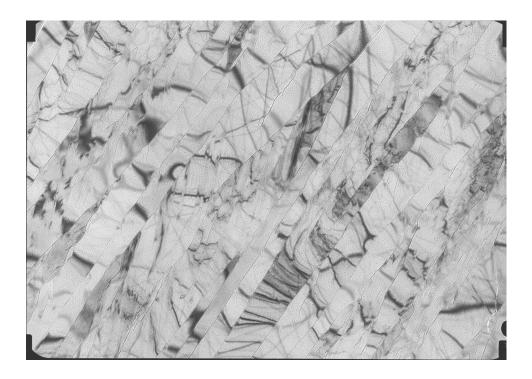

| Micrograph of line-scan SLS method after a 5 second SECCO defect                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| etch to highlight grain boundaries.                                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transmission electron micrograph of high aspect ratio grains in a typ-               |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ical line-scan SLS material. Total size of the micrograph is 9.89 $\mu \mathrm{m}$ x |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.95 $\mu$ m                                                                         | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

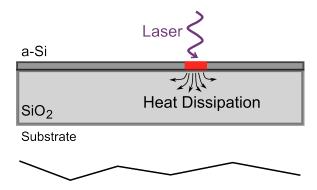

| Schematic cross section showing the importance of the buffer layer                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| between the laser-crystallized film and the substrate for heat dissipation.          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

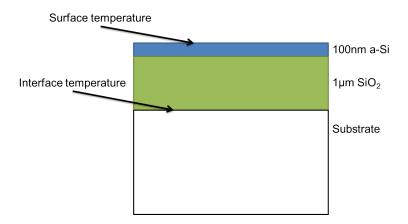

| Simulated structure of 100 nm of silicon on top of 1 $\mu$ m of silicon              |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| dioxide. Schematic points to the two points of interest: the surface                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| temperature and the interface temperature between the $\mathrm{SiO}_2$ buffer        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and the underlying substrate                                                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

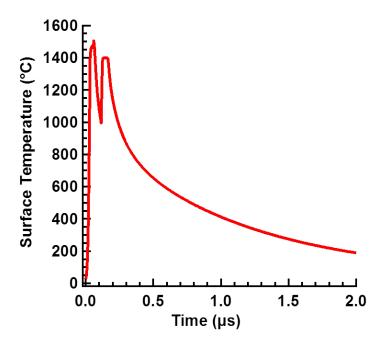

| Surface temperature of silicon film during laser processing. Tempera-                |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ture quickly reaches the silicon melt temperature and cools to below                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 200°C after 2 $\mu$ s                                                                | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interface temperature between $\mathrm{SiO}_2$ and substrate. The substrate sees     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| a maximum temperature of 70°C during the entire crystallization process.             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Temperature profile of simulated sample up to 3500 ns during laser pro-              |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| cessing. Most of the heat used to melt the amorphous-Si is dissipated                |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| in the $\mathrm{SiO}_2$ buffer layer before it reaches the substrate below           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                      | Grain boundary location controlled, or Two-Shot SLS. Directionally Solidified, or Line-Scan SLS. Single Crystal Region, or Dot SLS. [30] . Cross section (left column) and top view (right column) of line-scan sequential lateral solidification (SLS) process flow Micrograph of line-scan SLS method. Bottom of micrograph shows a single laser beam with a width of around 3.5 $\mu m$ . Top of micrograph shows typical Line-Scan SLS material |

| 2.12 | Process flow for fabrication of lateral thin film transistors. (a) Laser                       |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | crystallization of amorphous silicon. (b) Ion implantation for source                          |    |

|      | and drain electrodes. (c) Activation of ion implanted dopants. (d)                             |    |

|      | Definition of silicon active area. (e) Deposition of source and drain                          |    |

|      | electrodes. (f) Deposition of gate dielectric. (g) Deposition of gate                          |    |

|      | metal for completed transistor device                                                          | 23 |

| 2.13 | Micrograph of completed thin film silicon transistors                                          | 25 |

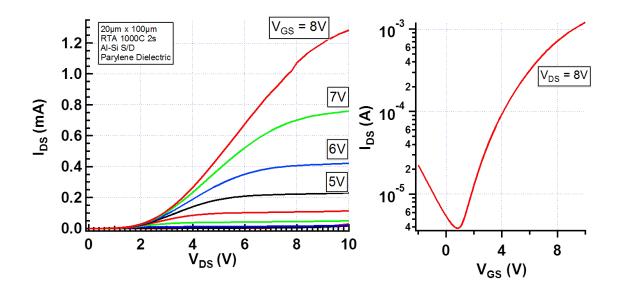

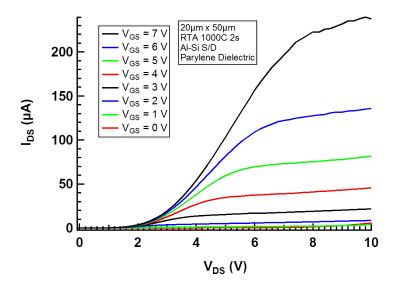

| 2.14 | Drain current vs drain voltage ( $I_{DS}$ vs. $V_{DS}$ ) and transfer character-               |    |

|      | istics ( $I_{DS}$ vs. $V_{GS}$ ) of SLS TFT device with grain boundaries parallel              |    |

|      | to conduction channel. Device length and width is 20 $\mu \mathrm{m} \ge 100~\mu \mathrm{m}$ . | 25 |

| 2.15 | Drain current vs drain voltage ( $I_{DS}$ vs. $V_{DS}$ ) of SLS TFT device with                |    |

|      | grain boundaries parallel to channel. Device length and width is 20                            |    |

|      | $\mu$ m x 50 $\mu$ m                                                                           | 26 |

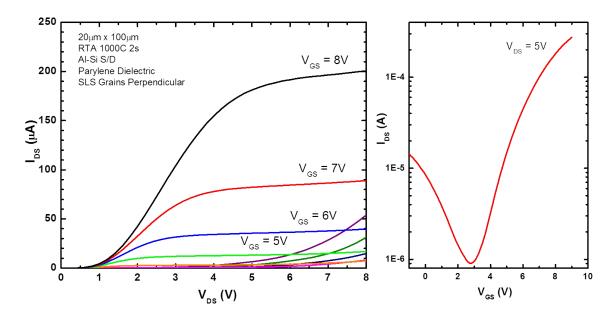

| 2.16 | Drain current vs drain voltage ( $I_{DS}$ vs. $V_{DS}$ ) and transfer characteris-             |    |

|      | tics ( $I_{DS}$ vs. $V_{GS}$ ) of SLS TFT device with grain boundaries perpen-                 |    |

|      | dicular to channel. Device length and width is 20 $\mu m$ x 100 $\mu m$                        | 27 |

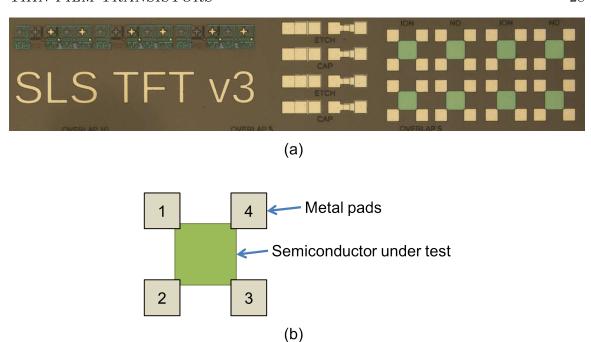

| 2.17 | (a) Micrograph of test structures incorporated on SLS TFT samples                              |    |

|      | including alignment marks, capacitance test structures, via etch test                          |    |

|      | structures, and van der Pauw test structures. (b) Schematic of van der                         |    |

|      | Pauw test structure showing the placement and numbering of the four                            |    |

|      | metal pads                                                                                     | 28 |

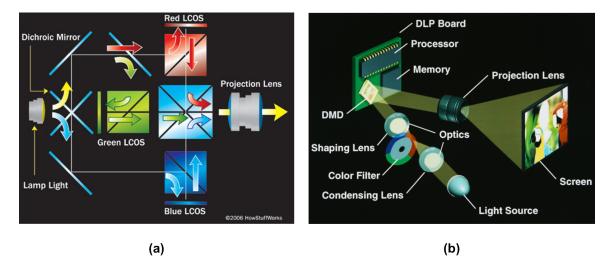

| 3.1  | Light path of typical projection systems. (a) Liquid crystal on silicon                        |    |

|      | based system. (b) Digital micromirror based system                                             | 32 |

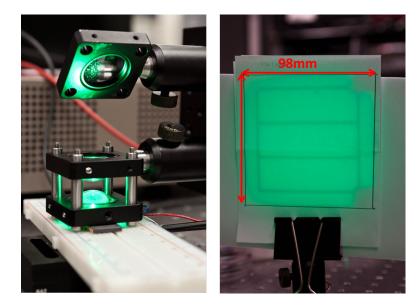

| 3.2  | Cree EZ1000 LED in a projection format. Left: Simple two optic mag-                            |    |

|      | nifying setup. Right: Projected image with 100X linear magnification,                          |    |

|      | easily viewable in ambient light                                                               | 34 |

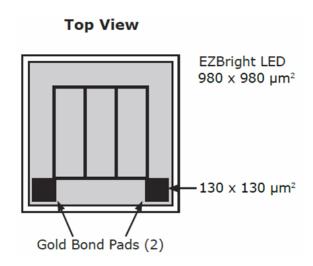

| 3.3  | Drawing of Cree EZ1000 LED. Bond pad structure and LED size                                    |    |

|      | shown. [70]                                                                                    | 35 |

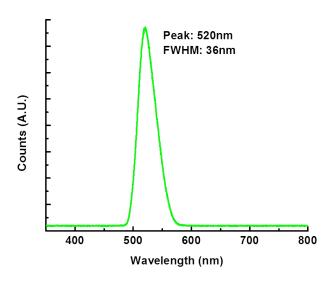

| 3.4  | Spectrum of Cree Green EZ1000 with a peak wavelength of 520nm                  | 36 |

|------|--------------------------------------------------------------------------------|----|

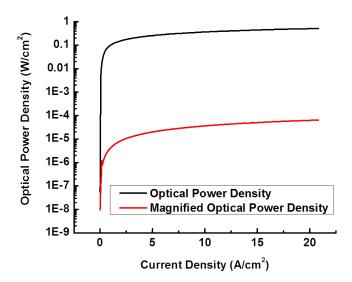

| 3.5  | Optical power density of the source LED and optical power density of           |    |

|      | 100X magnified LED image                                                       | 37 |

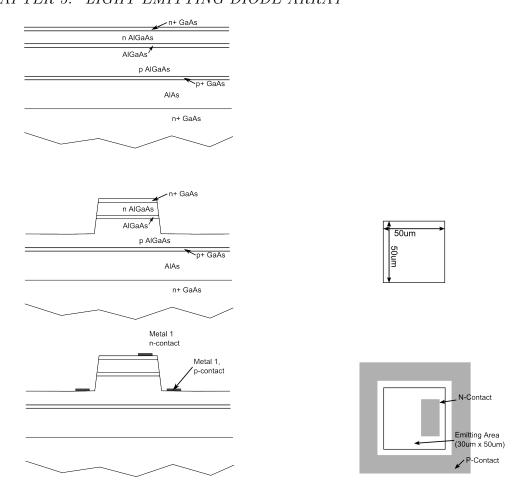

| 3.6  | First three steps of LED array fabrication process. Left side shows            |    |

|      | cross section, right side shows top view of the respective step                | 38 |

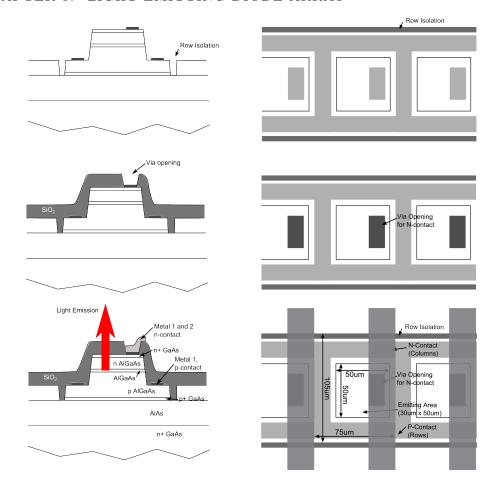

| 3.7  | Final three steps of LED array fabrication process. Left side shows            |    |

|      | cross section, right side shows top view of the respective step                | 39 |

| 3.8  | Cross sectional scanning electron micrograph of sample after the first         |    |

|      | etch process. This shows the different epitaxial layers and the correct        |    |

|      | etch depth                                                                     | 40 |

| 3.9  | (a) Schematic of LED array with row cross-talk issues. The rows are            |    |

|      | all connected together through the p+ GaAs layer. (b) Micrograph of            |    |

|      | LED array with cross-talk issue. Each column is addressed as a single          |    |

|      | element rather than 10 individual elements. Cross-talk extends to the          |    |

|      | bond pads shown by the perimeter of the bond pad lighting up                   | 41 |

| 3.10 | Cross sectional scanning electron micrograph of sample after second            |    |

|      | etch process. This shows the different epitaxial layers and the correct        |    |

|      | etch depth, right past the p+ GaAs to isolate each row                         | 42 |

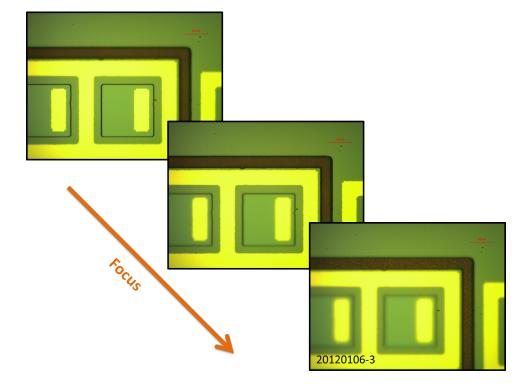

| 3.11 | Three micrographs showing shift in focus on each of the etched layers.         |    |

|      | This provides a rough quick check of etch depth                                | 43 |

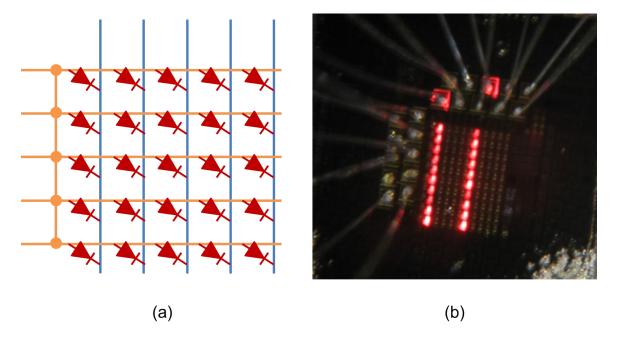

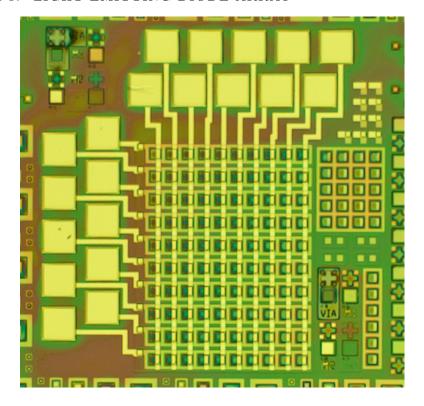

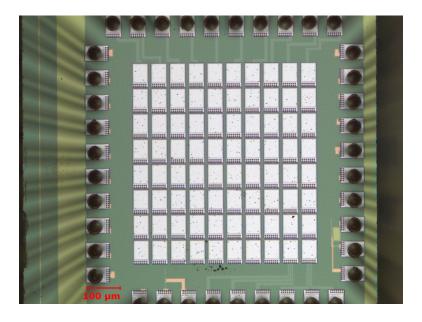

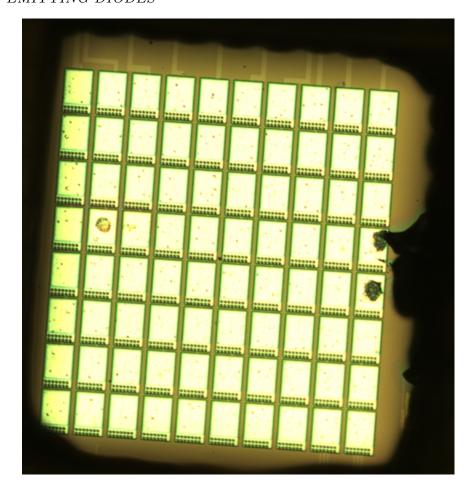

| 3.12 | Micrograph of $10 \times 10$ LED array fabricated with a five photomask        |    |

|      | process. Each LED is 50 $\mu$ m x 50 $\mu$ m                                   | 44 |

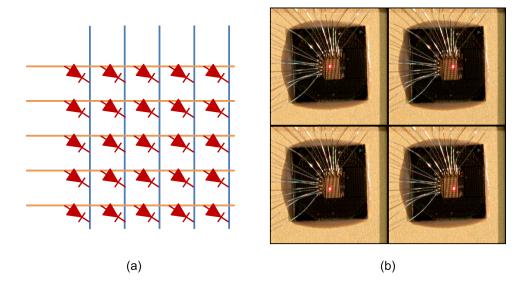

| 3.13 | A 10x10 passive-matrix. Each LED is individually controlled by ad-             |    |

|      | dressing the associated row/column. (a) Circuit schematic of the passive-      |    |

|      | matrix. (b) Photographs of LED passive-matrix array with four arbi-            |    |

|      | trary pixels addressed                                                         | 45 |

| 3.14 | Photograph of LED array in a dual-in-line package for testing                  | 45 |

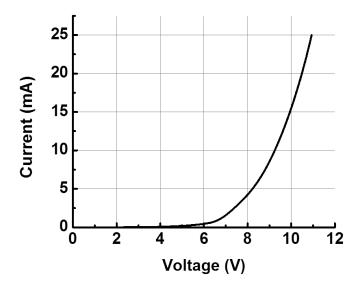

| 3.15 | Typical current-voltage characteristic of a 50 $\mu$ m x 50 $\mu$ m LED pixel. | 46 |

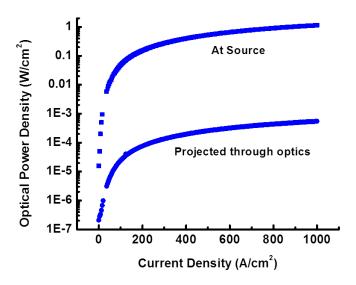

| 3.10 | Typical optical power density vs input current density characteristics                       |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | of a 50 $\mu \mathrm{m}$ x 50 $\mu \mathrm{m}$ LED pixel at the source and projected through |    |

|      | optics                                                                                       | 46 |

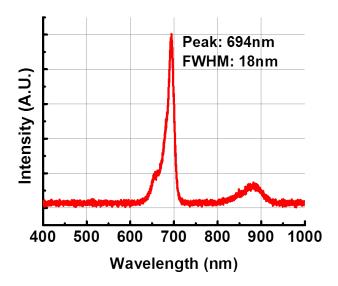

| 3.17 | Spectrum of the LED pixel. The peak wavelength is 694nm, governed                            |    |

|      | by the undoped AlGaAs recombination layer                                                    | 47 |

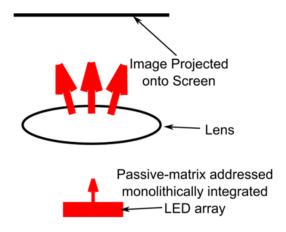

| 3.18 | Schematic drawing of LED experimental setup which consists of the                            |    |

|      | LED passive matrix focused through two optics onto an image plane.                           | 47 |

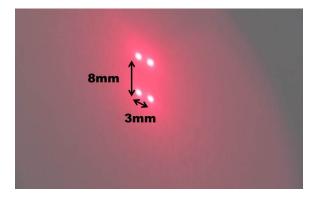

| 3.19 | Photograph of four LED pixels magnified by 20X and projected onto                            |    |

|      | a screen. On the array, these four pixels are spaced is approximately                        |    |

|      | $400~\mu\mathrm{m} \ge 150~\mu\mathrm{m}$                                                    | 48 |

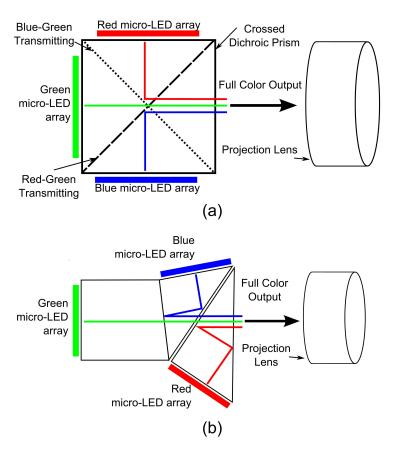

| 3.20 | Two proposed projection schemes using three separate LED arrays,                             |    |

|      | red, green, and blue. (a) Projection scheme commonly used for 3LCD                           |    |

|      | projectors. (b) Projection scheme commonly used for LCoS projectors.                         | 49 |

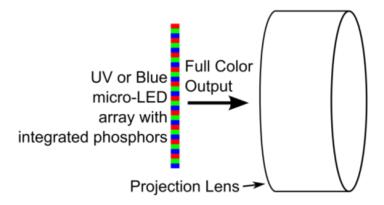

| 3.21 | Proposed projection scheme using a single LED array and a color down-                        |    |

|      | conversion layer consisting of red, green, and blue phosphors                                | 50 |

| 3.22 | Proposed projection scheme using a single LED array and a color down                         |    |

|      | conversion layer consisting of red, green, and blue phosphors                                | 51 |

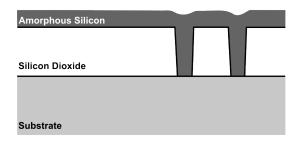

| 4.1  | Schematic cross section of initial via structure on tungsten. Via holes                      |    |

|      | are etched into silicon dioxide and filled with a<br>morphous silicon                        | 55 |

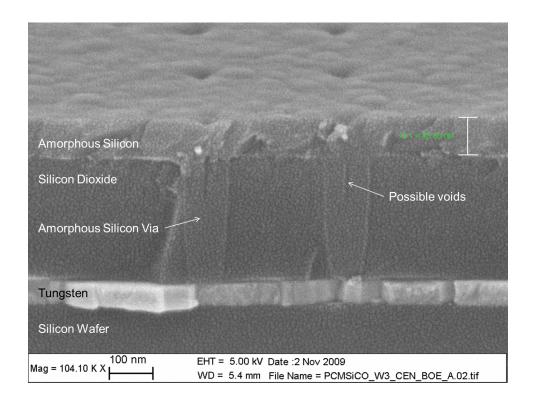

| 4.2  | Cross section scanning electron micrograph of an amorphous silicon-                          |    |

|      | filled via hole                                                                              | 55 |

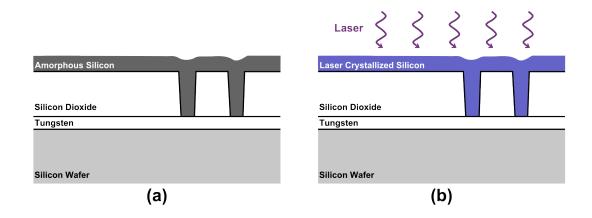

| 4.3  | Process flow for fabrication of vertical structures. (a) Amorphous sili-                     |    |

|      | con deposited in silicon dioxde vias. (b) Laser crystallization of amor-                     |    |

|      | phous silicon.                                                                               | 56 |

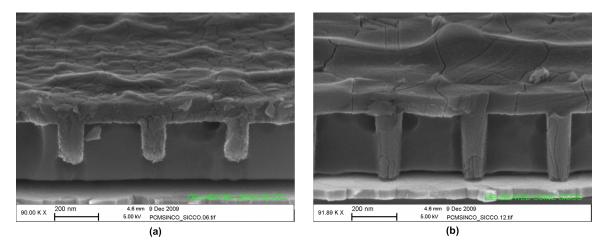

| 4.4  | Cross sectional scanning electron micrographs of laser crystallized vias                     |    |

|      | with two laser energies, (a) lower $800mJ/cm^2$ laser energy, (b) higher                     |    |

|      | $1800 \ mJ/cm^2$ laser energy                                                                | 57 |

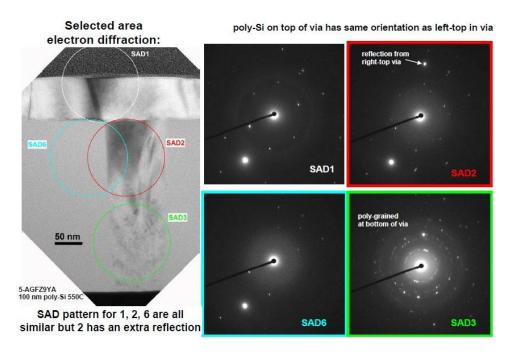

| 4.5  | Transmission electron micrograph of laser crystallized via on tungsten.           |    |

|------|-----------------------------------------------------------------------------------|----|

|      | Selected-area-diffraction shows small polycrystalline grains near the             |    |

|      | bottom which merge into larger grains near the top of the via                     | 58 |

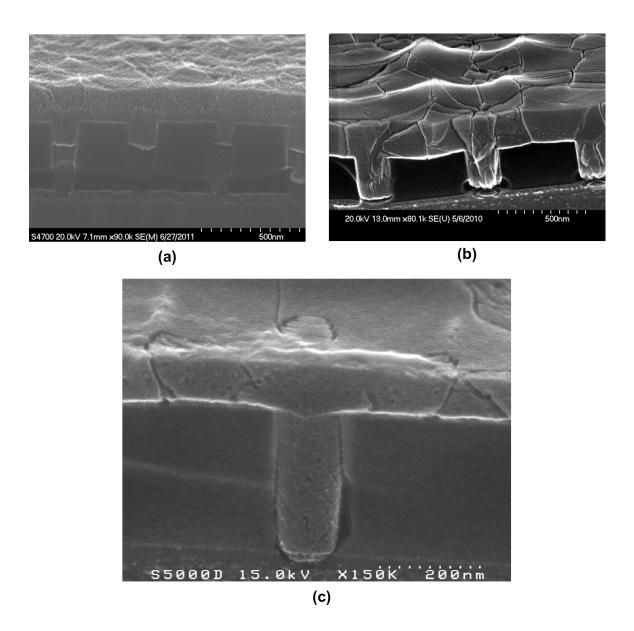

| 4.6  | Cross sectional scanning electron micrographs of laser crystallized sil-          |    |

|      | icon vias on a silicon wafer produced with varying laser energies. (a)            |    |

|      | 675 $mJ/cm^2$ (b) 1350 $mJ/cm^2$ (c) 1800 $mJ/cm^2$ . At energy (c) the           |    |

|      | laser melts the silicon all the way to the bottom of the via and seeds            |    |

|      | crystallization from the single crystal silicon wafer                             | 60 |

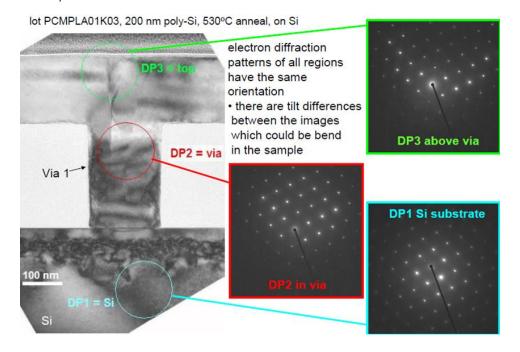

| 4.7  | Transmission electron micrograph of laser crystallized silicon via, on a          |    |

|      | silicon wafer. Selected-area-diffraction shows that all regions have the          |    |

|      | same crystal orientation, seeded from the silicon wafer                           | 61 |

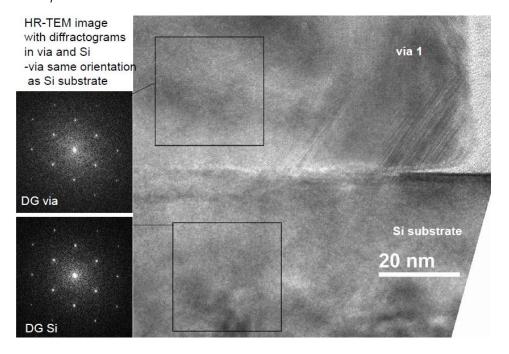

| 4.8  | A high resolution transmission electron micrograph of laser crystallized          |    |

|      | via on tungsten. TEM diffraction images on the left show that the via             |    |

|      | region is seeded directly from the silicon wafer                                  | 62 |

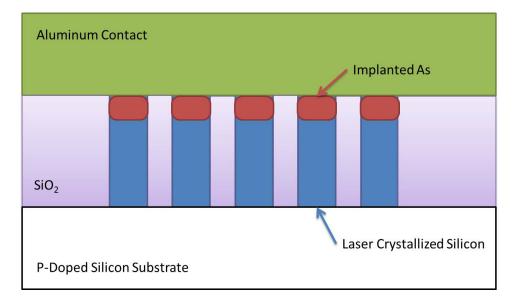

| 4.9  | Schematic cross section of version one laser crystallized diodes formed           |    |

|      | in via holes. Diodes are electrically probed through the aluminum                 |    |

|      | contact and the silicon wafer                                                     | 63 |

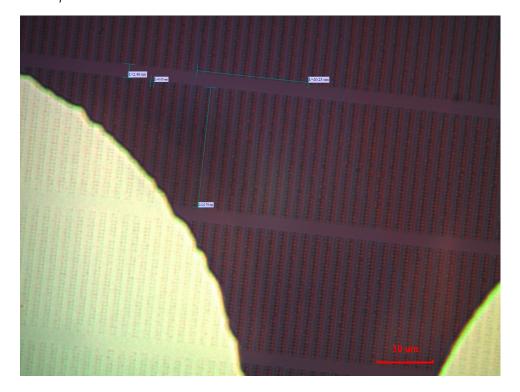

| 4.10 | Micrograph of version one diodes formed in via holes contacted by a               |    |

|      | large aluminum metal layer. The 150 $\mu\mathrm{m}$ diameter aluminum pad has     |    |

|      | contact with approximately 25,000 diodes                                          | 64 |

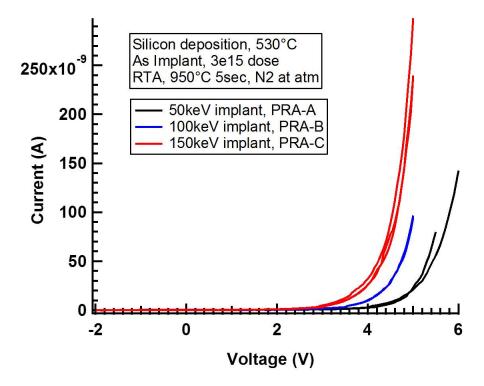

| 4.11 | Current-Voltage characteristics of version one diodes. Aluminum metal             |    |

|      | layer is approximately 150 $\mu\mathrm{m}$ in diameter, contacting 25,000 diodes. |    |

|      | Curves shift with changes in the arsenic implant energy                           | 65 |

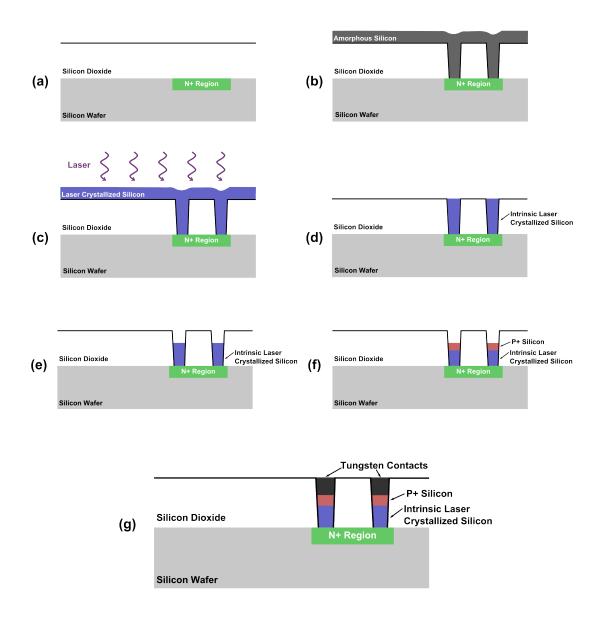

| 4.12 | Process flow for fabrication of version two vertical diodes. (a) Ion im-                                        |    |

|------|-----------------------------------------------------------------------------------------------------------------|----|

|      | plantation and silicon dioxide deposition. (b) Via opening etch for                                             |    |

|      | vertical structures and amorphous silicon deposition. (c) Laser crys-                                           |    |

|      | tallization. (d) Chemical mechanical polishing. (e) Etch back of laser                                          |    |

|      | crystallized silicon. (f) Ion implantation of p+ side. (g) Deposition of                                        |    |

|      | tungsten contacts                                                                                               | 66 |

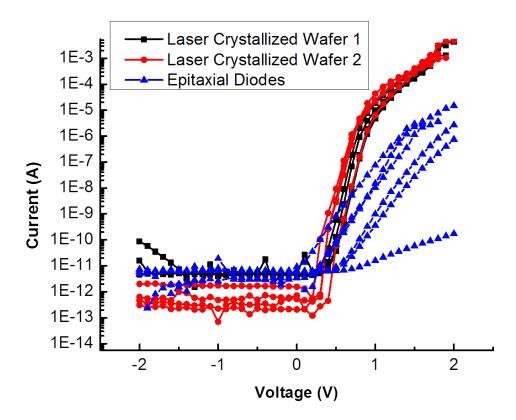

| 4.13 | Current-Voltage characteristics of version two laser crystallized diodes                                        |    |

|      | compared with epitaxially grown diodes. Laser crystallized diodes are                                           |    |

|      | more consistent and exhibit a much higher on-current                                                            | 67 |

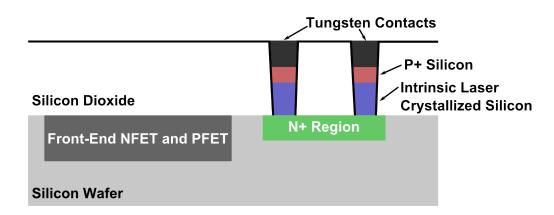

| 4.14 | Cross sectional schematic of laser crystallized diodes integrated directly                                      |    |

|      | on standard NFET and PFET front-end transistors                                                                 | 68 |

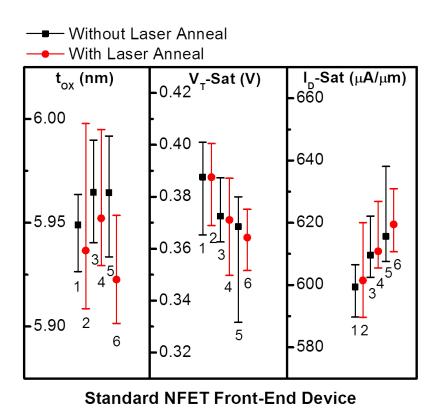

| 4.15 | Fundamental device characteristics ( $\mathbf{t}_{ox}$ , $\mathbf{V}_T - Sat$ , $\mathbf{I}_D - Sat$ ) measured |    |

|      | across six wafers with and without laser anneal. Twenty NFET devices                                            |    |

|      | were measured for each wafer. Each vertical line marks the median and                                           |    |

|      | two end-points of the twenty devices. Black lines are wafers without                                            |    |

|      | laser annealing. Red lines are wafers with laser annealing                                                      | 69 |

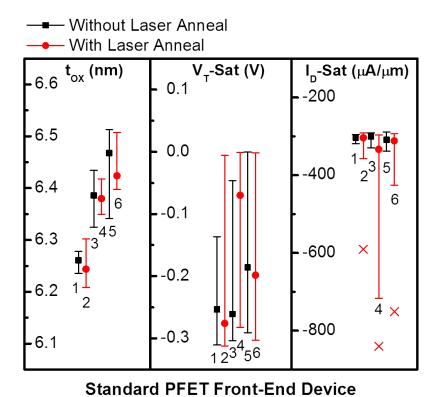

| 4.16 | Fundamental device characteristics (t <sub>ox</sub> , $V_T - Sat$ , $I_D - Sat$ ) measured                      |    |

|      | across six wafers with and without laser annealing. Twenty PFET                                                 |    |

|      | devices are measured for each wafer. Each vertical line shows marks                                             |    |

|      | median, and two end-points of the twenty devices. Black lines are                                               |    |

|      | wafers without laser annealing. Red lines are wafers with laser annealing.                                      | 71 |

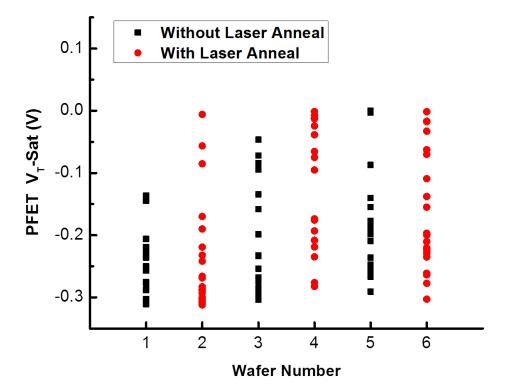

| 4.17 | $V_T - Sat$ of PFET devices measured across six wafers, with twenty                                             |    |

|      | transistors per wafer. Black lines are wafers without laser annealing.                                          |    |

|      | Red lines are wafers with laser annealing. Wafers show a similar spread                                         |    |

|      | of data points with and without laser annealing                                                                 | 72 |

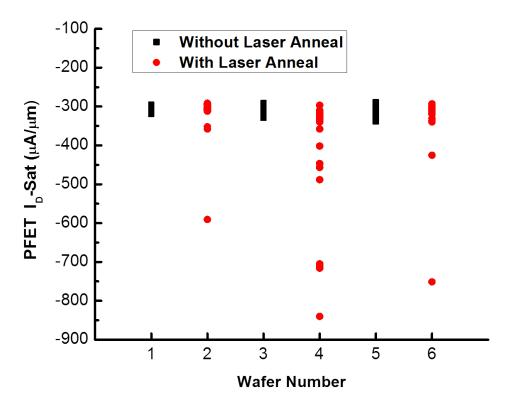

| 4.18 | $I_D - Sat$ of PFET devices measured across six waters, with twenty          |    |

|------|------------------------------------------------------------------------------|----|

|      | transistors per wafer. Black lines are wafers without laser annealing.       |    |

|      | Red lines are wafers with laser annealing. There are several outliers in     |    |

|      | the wafers with laser annealing, but the majority of devices fall within     |    |

|      | the same range                                                               | 73 |

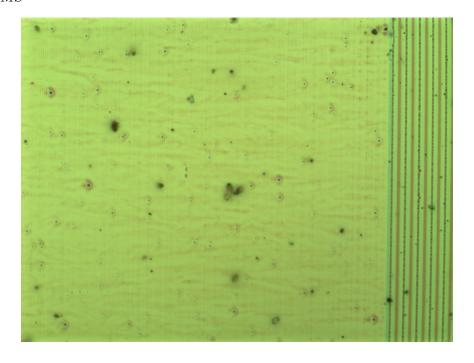

| 5.1  | Micrograph of SLS of silicon on a low- $\kappa$ dielectric wafer. The non-   |    |

|      | porous dielectric material is 300 - 500 nm thick and has a $\kappa=3.1.$     | 78 |

| 5.2  | Micrograph of SLS of silicon on a low- $\kappa$ dielectric wafer. The porous |    |

|      | dielectric material is 300 - 500 nm thick and has a $\kappa = 2.4$ - 2.6     | 79 |

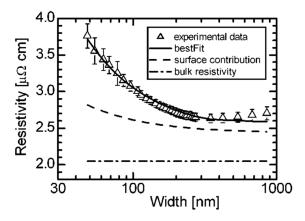

| 5.3  | Resistivity of 50 nm height copper lines versus width. As lines become       |    |

|      | narrower, the experimentally measured resistivity in the wires increases     |    |

|      | dramatically. Fig. from reference [104]                                      | 80 |

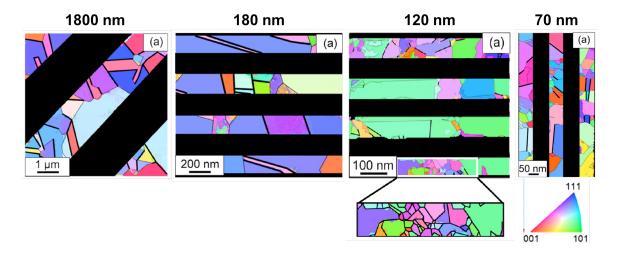

| 5.4  | Diffraction Scanning Transmission Electron Microscopy (D-STEM) im-           |    |

|      | ages adapted from reference [107]. Shows images for four copper line         |    |

|      | widths (1800 nm, 180 nm, 120 nm, and 70 nm), and the effect of line          |    |

|      | width on the copper microstructure                                           | 81 |

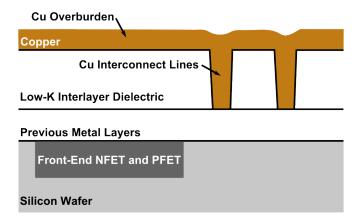

| 5.5  | A simplified schematic cross section of copper interconnect lines with       |    |

|      | overburden. This structure is laser recrystallized to change the mi-         |    |

|      | crostructure within the interconnect lines                                   | 82 |

| 5.6  | Single shot laser recrystallization of copper on a wafer. Laser energy       |    |

|      | varies from lowest (a) to highest (d). (a) Below melting threshold.          |    |

|      | (b)-(d) Above melting threshold, 850 - 1000 $mJ/cm^2$ . The formation        |    |

|      | of elongated grains from the edge of the laser exposure area is observed.    | 83 |

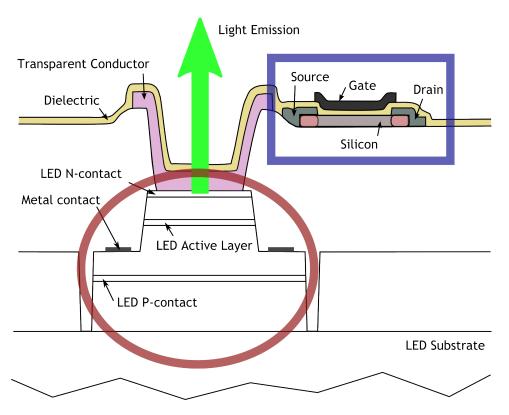

| 6.1  | Integration of SLS thin film transistor process, from chapter 2, with        |    |

|      | LED array process, from chapter 3. The monolithically integrated             |    |

|      | system incorporates advantages of both systems                               | 86 |

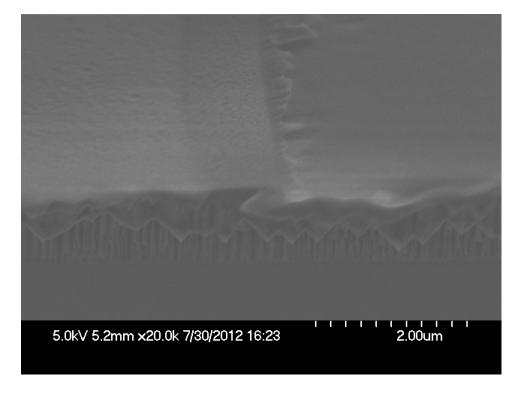

| 6.2  | Cross sectional scanning electron micrograph of green LED wafer              | 87 |

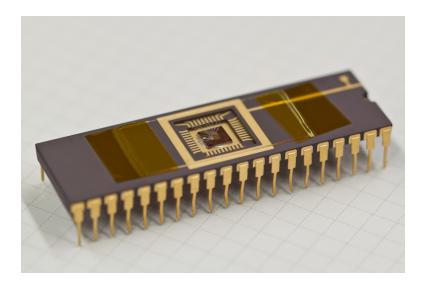

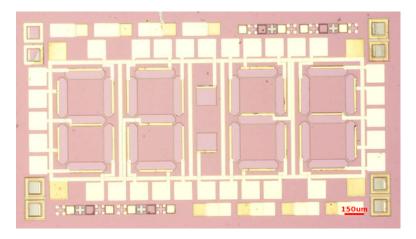

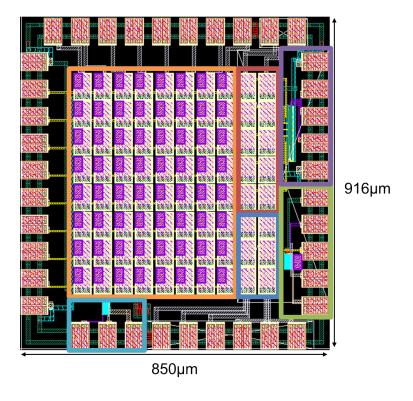

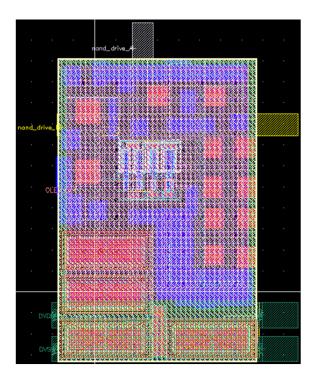

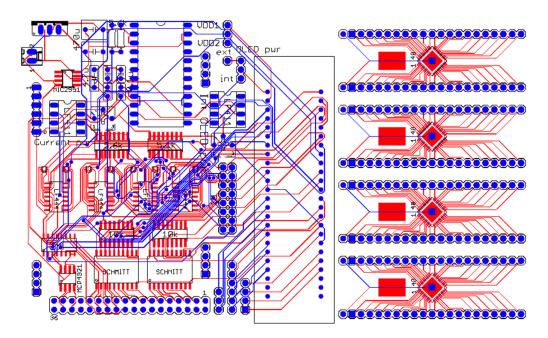

| A.1  | Micrograph CMOS chip which supports direct integration with Organic      |     |

|------|--------------------------------------------------------------------------|-----|

|      | Light Emitting Diodes                                                    | 92  |

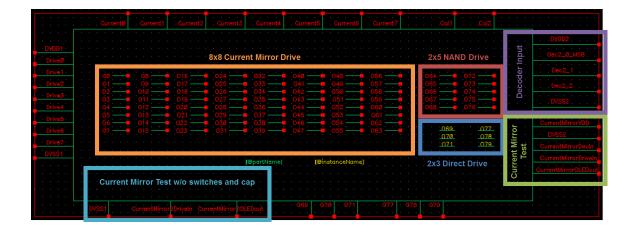

| A.2  | Full layout with outlines for each section of the chip. Fabricated chip  |     |

|      | includes test circuits, and three different driving schemes              | 93  |

| A.3  | Full symbol with all parts and input/output pins marked                  | 93  |

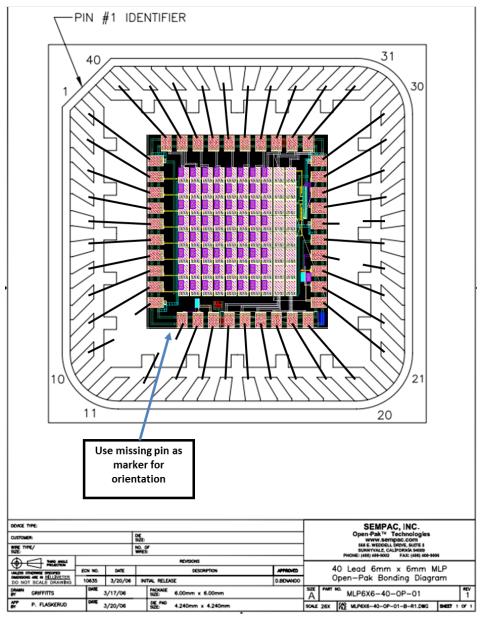

| A.4  | Bonding diagram matching CMOS chip with pins on a 40-pin QFN             |     |

|      | package. Missing pin on bottom left corner is used as an orientation     |     |

|      | marker                                                                   | 94  |

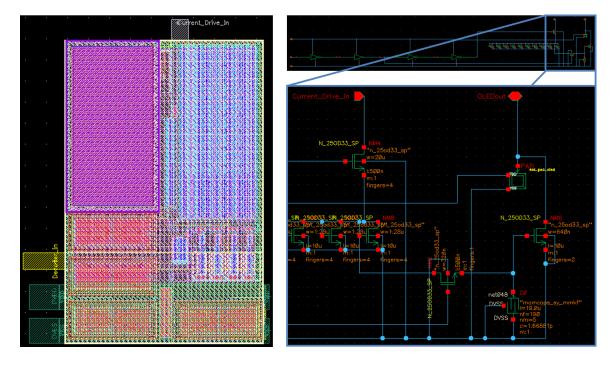

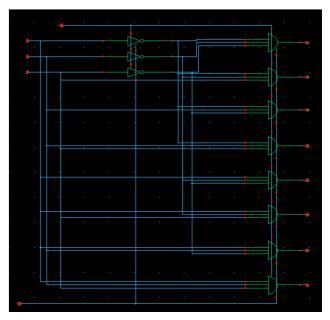

| A.5  | Layout of current mirror circuit (left). Circuit schematic of current    |     |

|      | mirror (right)                                                           | 97  |

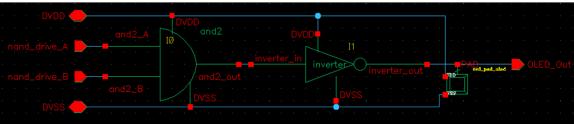

| A.6  | Layout of NAND circuit (top). Abstracted circuit schematic of NAND       |     |

|      | with OLED bond pad (bottom)                                              | 99  |

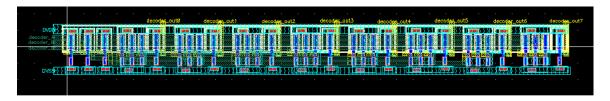

| A.7  | Layout of decoder circuit (top). Circuit schematic of decoder circuit    |     |

|      | (bottom)                                                                 | 100 |

| A.8  | Printed Circuit Board as designed. PCB interfaces with Arduino con-      |     |

|      | trol and connects through a 40-pin Zero-Insertion-Force socket to in-    |     |

|      | terface with CMOS chip. On the right are four QFN to DIP printed         |     |

|      | circuit boards                                                           | 101 |

| A.9  | Photograph of test board. CMOS chip in QFN package shown at top,         |     |

|      | soldered to a DIP interface board. Electronics are fully controlled with |     |

|      | an Arduino Mega microcontroller                                          | 102 |

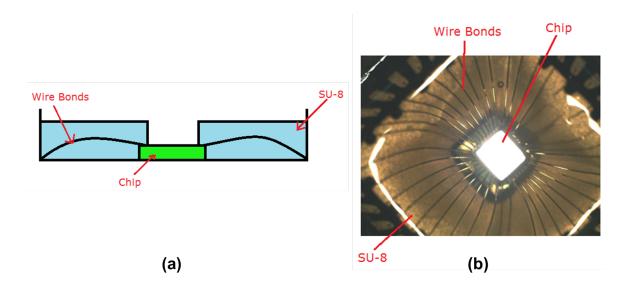

| A.10 | (a) Cross sectional schematic of CMOS chip wirebonded into QFN           |     |

|      | package. The wirebonds are covered with SU-8 and an opening is           |     |

|      | defined to expose the CMOS surface. (b) Micrograph of SU-8 on chip       |     |

|      | with defined opening                                                     | 103 |

| A.11 | Micrograph of SU-8 on chip with defined opening                          | 104 |

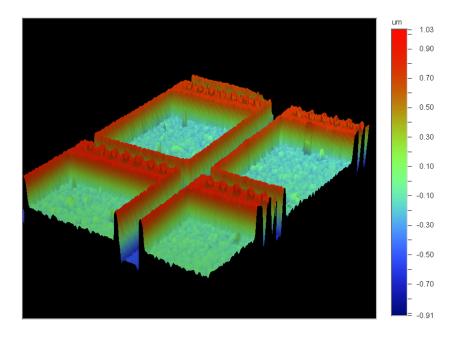

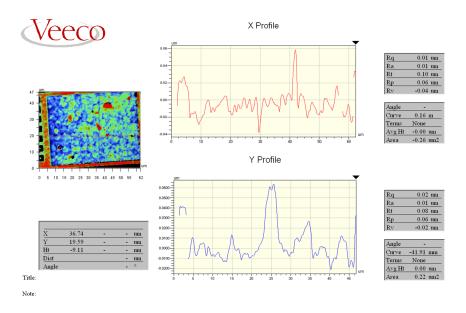

| A.12 | Optical profilometer image of multiple bond pads. Total height differ-   |     |

|      | ence is about 2 $\mu$ m                                                  | 106 |

| A.13 Optical profilometer image of bond pad surface. Total height difference |     |

|------------------------------------------------------------------------------|-----|

| is about 0.1 $\mu$ m                                                         | 106 |

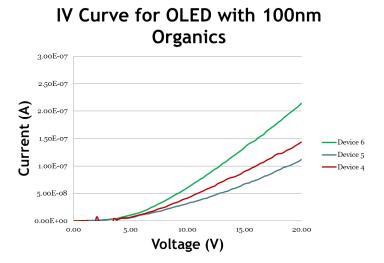

| A.14 Initial current-voltage characteristics of OLED devices                 | 107 |

## List of Tables

| 2.1 | Van der Pauw Sheet Resistance Data (Ohms/Square) | 29  |

|-----|--------------------------------------------------|-----|

| 3.1 | LED Layer Structure                              | 37  |

| A.1 | Pin Definitions of CMOS Chip                     | 96  |

| A.2 | Material Stack for Organic LED                   | 105 |

## Acknowledgments

I would first like to thank my advisor, Professor Ioannis Kymissis, for his support and guidance throughout my years here. His positive energy and always helpful feedback kept me going forward. Second, the support and friendship of all the current and past members in the Columbia Lab for Unconventional Electronics have been amazing. In particular, I'd like to thank Dr. Nadia Pervez, Dr. Brian Tull, Dr. Zhang Jia, Dr. Yu-Jen Hsu, John Sarik, Haig Norian, Jonathan Beck, Marshall Cox, Shyuan Yang, and Hassan Edrees for all the lengthy discussions and various contributions to my work.

I would like to thank all the members of Professor James Im's research group. In particular, Dr. Alexander Limanov - without his help and willingness to continuously try failed laser experiments this thesis would not be possible. In addition, I owe thanks to Adrian Chitu and Gabriel Ganot for their help with additional experiments and laser simulation work.

I would like to thank all of the collaborators who contributed material, samples, measurements, and time to various projects. Dr. Chung Lam, Dr. Edward Kiewra, Dr. Asit Ray, and Professor Robert Laibowitz for wafers and measurement support in the 3DIC project. Professor Robert Laibowitz and Dr. Noel Russell for low- $\kappa$  dielectric material. And lastly, Dr. Christian Witt for providing wafers in the recrystallization of copper.

I would also like to thank everyone who was involved in the OLED/CMOS integration project. In particular, Zeynep Basaran, who took on this challenging project over several summers, and developed the project from a CMOS chip and board to

a nearly fully integrated process. In addition, Dr. Ajay Balankutty, Keith Dronson, and Haig Norian for CMOS design and tape-out help, version 1 of the test circuit board, and shared knowledge of his SU-8 encapsulation process, respectively.

My girlfriend, Nancy Twu, for all her love, support, and understanding.

Finally, the love and support of my family. My mom and dad, and my two brothers.

To my Mom and Dad

## Chapter 1

### Introduction

#### 1.1 Background and Motivation

Much of the advancement in the electronics and semiconductor industry can be attributed to the shrinking of transistor gate lengths and resulting increase of transistor density and performance. While significant efforts continue on fulfilling Moore's Law, the doubling of transistor density every two years, shrinking is increasingly difficult, motivating research in alternative technologies such as advanced integration techniques [1][2][3][4].

Many categories of semiconductors are widely utilized for various applications, including silicon, compound semiconductors, oxide semiconductors, amorphous silicon, and organic semiconductors. Each group has distinct performance advantages, leading to their adoption in different industries. For example, crystalline silicon has been strongly optimized for high performance computing, while III-V compound semiconductors have a direct band gap, making them very efficient light emitters. Organic and oxide semiconductors have very low process temperatures and are compatible with many substrates such as plastic and glass.

Advanced integration of different materials enables new platforms by allowing for more functionality in the same space. However, integration of different material systems is difficult because of incompatible fabrication processes and substrates, as well as material issues such as lattice matching and chemical compatibility. Various integration techniques have been demonstrated for limited systems through the use of shape self-assembly [5], wafer bonding [6], and heteroepitaxy growth [7][8]. Several of these have been demonstrated in the laboratory, but with limited yields and no commercial success to date. Wafer bonding and gluing of compound semiconductor wafers to apertured and thinned silicon wafers has also recently been demonstrated 9, but suffers from a range of practical problems including poor bonding due to the limited thermal budget and mismatched coefficients of thermal expansion. Heteroepitaxial growth of compound semiconductor devices on pre-fabricated silicon circuitry is a promising approach, but it is limited by the availability of compatible growth processes. Metal alloy bump bonding is used to make small arrays of IR detectors on transparent substrates, but the general applicability of this strategy is limited |10|. Perhaps the most encouraging strategy is recent work showing the use of small indium bonds to attach a silicon wafer with an LED array [11]. However, like metal alloy bump bonding, the ultimate level of integration and device yield is limited by the size and reliability of the bonding process.

In many cases, the significant challenge to integration is making processes compatible. Many of the high performance materials such as silicon and compound semiconductors require high temperature processes (600-1000°C) during growth or device fabrication, but cannot withstand these temperatures in post-processing. For example, silicon transistors typically have several high temperature growth and dopant activation steps (up to 1000°C), but after these initial steps, temperatures cannot exceed 400°C or the device characteristics may shift. This is problematic when a post-processing step such as growing a second layer of silicon or growing other materials (III-Vs) is desired, since all of these processes will exceed the 400°C threshold.

One promising technique allowing for better process compatibility is laser crystallization. A high power laser can shoot short pulses or a continuous wave at a material, exposing it to energies high enough to induce phase transitions or crystallize amorphous material at the surface, but leaving the underlying substrate at about room temperature and unaffected. In a typical laser crystallization process, the irradiated film can reach melting temperatures for the film (1400°C for silicon), but because the exposure area is localized and the pulse duration is short, only the top surface is transformed.

Laser crystallization is proposed as a means to monolithically integrate multiple high performance materials. This is significant for currently incompatible systems such as silicon on compound semiconductors and multi-layered high performance silicon. New devices fabricated monolithically with these systems can enable breakthroughs in both displays and microelectronics.

# 1.2 Diodes, Light Emitting Diodes, and Field Effect Transistors

Three devices are discussed throughout this thesis: diodes, light emitting diodes (LEDs), and field effect transistors (FETs) [12][13].

#### 1.2.1 Diodes

A diode is a two-terminal electronic device which allows electrical current to pass in only one direction. Modern day diodes are built from n-type and p-type semiconductor materials. To produce n-type materials, silicon is doped with a group V donor element. When the group V element is activated within the silicon lattice, it donates an extra electron to the silicon, and the electron freely moves around and conducts electricity. Phosphorus and arsenic are typical donor atoms for silicon. For p-type material, silicon is doped with a group III acceptor element, typically boron. Within a silicon lattice, the group III element is missing an electron and can accept an electron from silicon. This creates a void in the silicon where an electron is missing, also

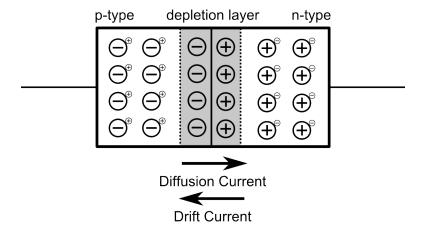

Figure 1.1: Schematic drawing of p-n junction showing its depletion region and drift and diffusion currents.

known as a hole. Holes are positively charged due to lack of an electron, and can also conduct electricity. As electrons hop from a filled state to a hole, it can appear as if the hole is moving in the opposite direction of the electron. Thus, both n-type and p-type materials can conduct electricity, but n-type preferentially conducts with electrons and p-type preferentially conducts with holes.

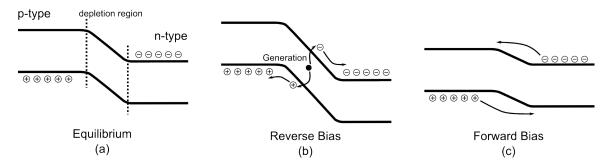

Figure 1.2: Band diagram for a p-n junction diode in (a) equilibrium state, (b) reverse bias, and (c) forward bias.

Placing p-type and n-type materials together forms a p-n junction, and the semiconductor diode. Because one side of the junction has a high concentration of delocalized of holes, and the other side has a high concentration of delocalized of electrons, the mobile electrons and holes diffuse across the junction and recombine to form a depletion region, fig. 1.1. As more of these electrons and holes recombine, an electric field forms within the depletion region and induces a drift current in the opposite direction of the diffusion current. In equilibrium, the diffusion current and the drift current are in equal and opposite directions. Schematically, the p-n junction has a band diagram similar to fig. 1.2a.

When biased with an external potential, the equilibrium between diffusion current and drift current is disturbed. In reverse bias, a negative voltage is applied to the p-side of the diode causing the depletion width widens and no current is allowed to pass except for a very small component caused by thermal generation, 1.2b. In forward bias, the depletion width shrinks and the electrons and holes on the n-side and p-side now have enough energy to pass through the depletion region and conduct current, fig. 1.2c. A typical current-voltage characteristic of a diode is shown in fig. 1.3, governed by the following equations [12]:

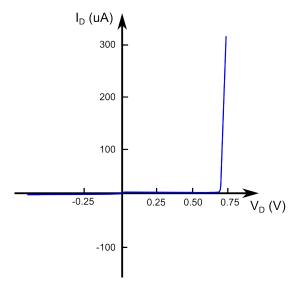

Figure 1.3: Typical Current-Voltage characteristic of a semiconductor diode. Adapted from reference [12]

$$I_D = I_0(e^{V_D/V_{th}} - 1)$$

where  $I_0 = qn_i^2 A[(D_p/N_dW_n) + (D_n/N_aW_p)]$  for short-base diodes, where minority carriers crossing the p-n junction do not recombine before reaching the contacts, and  $I_0 = qA[(D_pp_{n0}/L_p) + (D_nn_{p0}/L_n)]$  for long-base diodes, where minority carriers crossing the p-n junction do recombine before reaching the contacts.

The non-linear characteristics of diodes can be used in simple switching applications, rectifying applications such as the conversion of alternating current signals to direct current, or clamping circuits such as electrostatic discharge circuits.

#### 1.2.2 Light Emitting Diodes

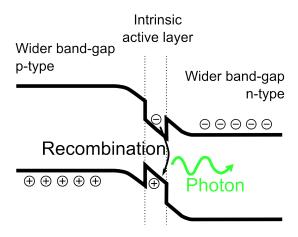

Light emitting diodes (LEDs) are a subset of diodes, which as the name implies, emit light. Instead of silicon, LEDs are typically fabricated from III-V compound semiconductor materials, such as aluminum gallium arsenide, or indium gallium nitride. When compared to silicon, which has an indirect band gap, aluminum gallium arsenide (AlGaAs) and indium gallium nitride(InGaN) have the direct band gaps required for efficient light output. Modern LEDs are heterojunctions, consisting of multiple AlGaAs or InGaN films. By adjusting the ratio of aluminum to gallium or indium to gallium in these materials the band gap can be adjusted. The Al/Ga or In/Ga ratios in the multilayer heterojunction structure of the LED is engineered to confine and induce recombination in a specific layer and thus control the wavelength of light output. Fig. 1.4 shows the band diagram for an LED heterojunction. This is similar to the diode band diagram in the previous section, except electrons and holes are now confined in a layer between the p-type and n-type layers, the intrinsic active layer. This active layer is engineered for a particular band gap to produce a particular peak light emission wavelength.

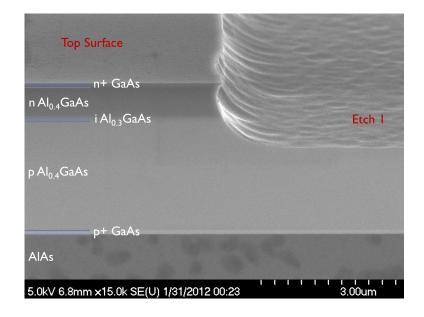

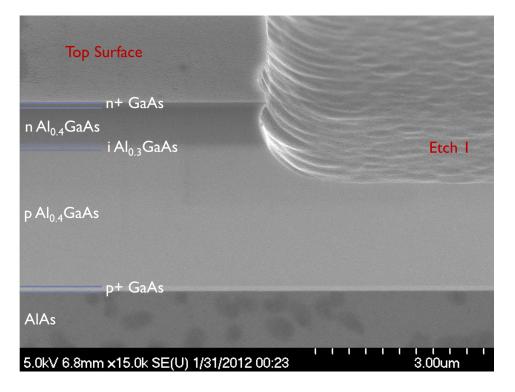

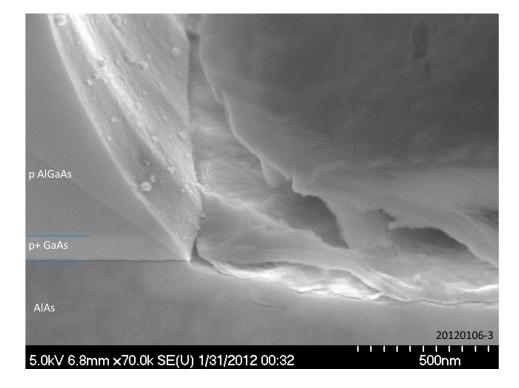

A representative cross sectional image of a LED is shown in fig. 1.5. Each layer in the heterojunction is annotated in the image. The n-AlGaAs and p-AlGaAs confine electrons and holes to the intrinsic-AlGaAs where recombination occurs and photons

Figure 1.4: Band diagram of LED heterojunction. Electrons and holes are confined within the middle region where recombination occurs and photons are emitted.

Figure 1.5: Cross sectional scanning electron micrograph of LED heterojunction. The n-AlGaAs and p-AlGaAs have a larger band gap. Electrons and holes in the intrinsic-Al $_{0.3}$ GaAs layer where light emission occurs.

are emitted.

LEDs are commercially available with wavelengths from ultraviolet to infrared and used in an ever-increasing range of applications. Some of these applications include display backlights, camera flash lighting, solid-state lighting, and water purification.

#### 1.2.3 Metal Oxide Semiconductor Field Effect Transistors

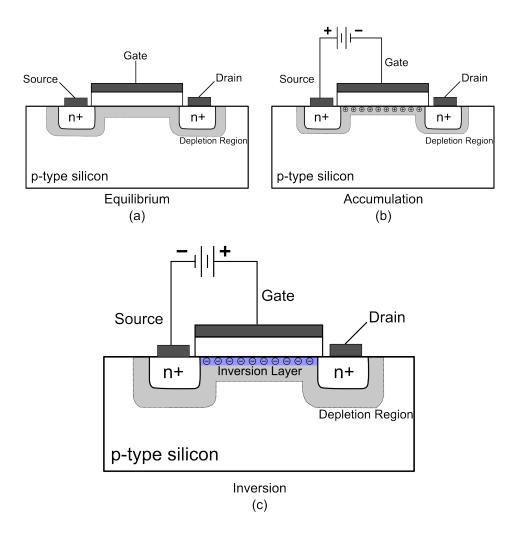

Figure 1.6: Standard n-channel MOSFET structure in (a) equilibrium, (b) accumulation when a negative gate bias is applied, and (c) inversion when a positive gate bias is applied.

Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) are the most ubiquitous electronic device, appearing in almost all electronics. In a standard n-channel MOSFET, fig. 1.6, the source and drain regions are heavily n-doped in a p-type semiconductor. Above the p-type channel region is a gate dielectric and gate metal. When the MOSFET is off, electrical conduction between the source and drain is blocked by the back-to-back p-n junctions. When a negative bais is applied to the gate, accumulation of holes occurs in the channel as these holes are attracted to the semiconductor/dielectric interface. Again, because of the back-to-back p-n junction, current cannot conduct between the source and drain even with this accumulated hole layer.

As a positive bias is applied, the depletion region underneath the channel expands, shown in fig. 1.6c. After a certain threshold voltage, an inversion layer of mobile electrons is formed in the channel. An electrical conduction path between the source and drain appears in this inversion scenario, and can be controlled with the bias at the gate.

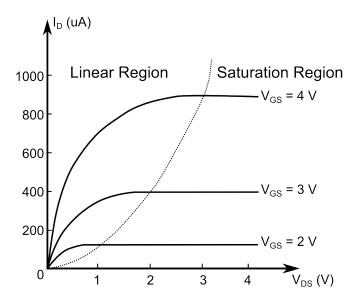

Figure 1.7: Typical current-voltage characteristics of an n-channel MOSFET. Adapted from reference [12]

At small biases between the source and drain, the current increases linearly with the applied voltage. In the linear region, the channel behaves similar to a resistor. As the bias increases between the source and drain, the channel on the drain side becomes smaller as the gate has less of an effect. Eventually, this reaches the saturation region of device operation where increases in source and drain bias do not change the current. Fig. 1.7 shows a typical n-channel MOSFET current-voltage characteristic with the regions of operation marked [12]. The source-drain current can be calculated with the equations below for the different regions.

```

Cutoff: I_{DS} = 0

when (V_{GS} \leq V_{Tn})

Linear: I_{DS} = (W/L)\mu_n C_{ox}[V_{GS} - V_{Tn} - (V_{DS}/2)]V_{DS}

when (V_{GS} \geq V_{Tn}, V_{DS} \leq V_{GS} - V_{Tn})

Saturation: I_{DS} = (1/2)(W/L)\mu_n C_{ox}(V_{GS} - V_{Tn})^2

when (V_{GS} \geq V_{Tn}, V_{DS} \geq V_{GS} - V_{Tn})

```

Similarly, p-channel devices can be fabricated by changing the substrate to n-type doping, and the source and drain contacts to heavily doped p-type material. The device operation voltages are then opposite. Instead of applying a positive voltage at the gate for inversion, a negative voltage past the threshold voltage is applied and the inverted, mobile charges are now holes. The regions of operation, linear and saturation, are similar for p-channel and n-channel, and the p-channel FET equations are given below.

```

Cutoff: I_{SD} = 0

when (V_{SG} \leq |V_{Tp}|)

Linear: I_{SD} = (W/L)\mu_p C_{ox}[V_{SG} - |V_{Tp}| - (V_{SD}/2)]V_{SD}

when (V_{SG} \geq |V_{Tp}|, V_{SD} \leq V_{SG} - |V_{Tp}|)

Saturation: I_{SD} = (1/2)(W/L)\mu_p C_{ox}(V_{SG} - |V_{Tp}|)^2

when (V_{SG} \geq |V_{Tp}|, V_{SD} \geq V_{SG} - |V_{Tp}|)

```

When both n-channel and p-channel devices are fabricated on the same substrate and used together in circuit designs, this is called Complementary Metal Oxide Semi-conductor (CMOS) technology. MOSFETs and more specifically CMOS technologies appear in essentially all electronic devices and are the basic building block for digital circuits as switches and for analog circuits as amplifiers.

#### 1.3 Objectives and Approach

This thesis focuses on monolithically-integrating normally process-incompatible materials to make systems with extended functionality. Reconciling the low process temperatures of certain materials with the necessity for high quality crystalline materials makes laser crystallization an attractive route towards this advanced integration. Chapter 2 discusses a specific laser crystallization method (sequential lateral solidification), the fabrication of high mobility thin film silicon transistors using this method, and characterization of these devices. Chapter 3 covers the fabrication of LED arrays, their potential uses in display and non-display applications, and their eventual integration with laser crystallized silicon transistors to form active-matrix circuits. Three dimensional integrated circuits, specifically the building and characterization of vertical diode devices, and the effects of laser crystallization on underlying devices are examined in chapter 4. Finally, chapter 5 discusses the application of laser annealing to other material systems, in particular sequential lateral solidification on low- $\kappa$  dielectrics and its relevance to back-end three dimensional integrated circuits, and laser crystallization of copper for reduced wire resistivity.

## Chapter 2

# Sequential Lateral Solidification of Silicon for Thin Film Transistors

#### 2.1 Introduction

Single crystal silicon is the predominant semiconductor material used in microelectronics due to its high performance and extensive optimization history. However, the methods of obtaining single crystals are limited; both the float-zone and Czochralski processes grow ingots from molten silicon. This poses a challenge to integration with other substrates if a single crystal silicon layer is desired on top of another material. What is needed is a method of growing the highest quality silicon possible without effect to the underlying substrate.

The use of laser energy as a means to crystallize amorphous silicon has long been established given the success in obtaining highly crystalline silicon through a low temperature process [14][15][16][17]. The laser energy can be adjusted to create partial melting conditions or fully melted amorphous films [18][19]. In partial melting, the laser melts only the top surface, leaving the lower material solid. The solid amorphous film then nucleates the crystallization, resulting in very small grains. In the complete melting regime, the laser fully melts the amorphous silicon film. Nucleation and

grain growth occur at random at the molten silicon/substrate interface, and again only produces small grains. In a narrow energy window between partial melting and complete melting is the regime called super lateral growth [18]. Here, the laser energy density is just below what is necessary for complete melting, and the scattered, non-molten, solid seeds at the bottom of the molten silicon film act as preferential nucleation sites, leading to larger grains upon cooling. Excimer Laser Annealing (ELA) takes advantage of this regime and offers fairly large crystal sizes and electron mobilities of approximately  $100 \ cm^2/Vs$ , but relies on this non-equilibrium process and narrow energy density window.

Sequential Lateral Solidification (SLS) is a laser crystallization method which operates in the complete melting regime where process tolerances are much larger, and at the same time can produce large grains of polycrystalline silicon with electron mobilities up to  $500 \ cm^2/Vs$ .

#### 2.2 Sequential Lateral Solidification Methods

Sequential Lateral Solidification (SLS) is a pulsed-laser crystallization method which combines laser irradiation through a patterned mask with precise submicrometer translations of a sample stage [21][22][23]. The shape of the laser irradiation is controlled by a reticle in the beam path and affects the microstructural quality of the laser-crystallized material. Three popular types of SLS are two-shot SLS, line-scan SLS, and dot-SLS. Of the three, two-shot SLS makes polycrystalline silicon material with the lowest mobility, but covers a large area with two laser shots versus the thousands of laser shots required for other laser annealing methods [24][25]. Line-scan SLS produces material with high mobility in a directional manner, and transistors with channels in the correct orientation have much higher mobilities [26][27][28]. Dot-SLS makes an area of nearly single crystal material with electron mobilities above what is achievable by line-scan SLS [29]. However, with dot-SLS, only the single crystal

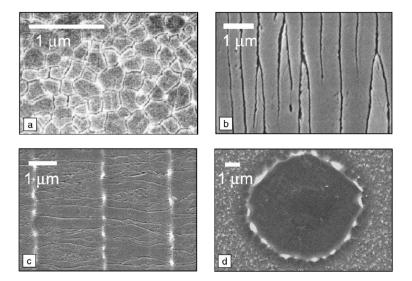

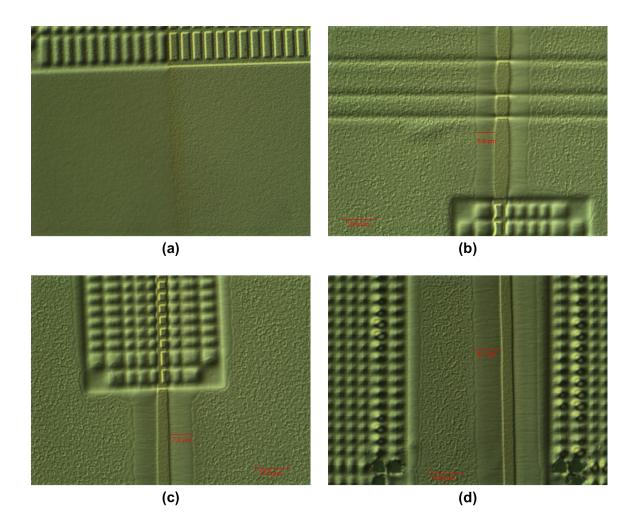

Figure 2.1: Scanning electron micrographs of defect-etched samples following laser annealing. (a) Excimer Laser Annealing method. (b) Line-Scan SLS. (c) Two-Shot SLS. (d) Dot SLS. [20]

regions in the total area are useful. The resulting materials obtained from these methods are compared in fig. 2.1 where the scanning electron microscope images show the relative microstructures [25]. For electronic devices, electron mobility is an important characteristic of a material and can be partially determined from the microstructure quality, fig. 2.2 [30]. For comparison, the mobility of amorphous silicon devices is approximately 1  $cm^2/Vs$ , and devices fabricated with excimer laser annealing have mobilities of approximately  $100 \ cm^2/Vs$ .

Line-scan SLS offers the best option in advanced integration work since it produces a uniform, high mobility material over a large area. Fig. 2.3 shows the process flow for line-scan SLS. The process begins with a thin-film of amorphous silicon which is then irradiated with a long and thin laser beam. This 30-300 ns beam is typically 2-3  $\mu$ m wide and can be as long as 1 meter. The exposed amorphous silicon is fully melted into a liquid state and allowed to cool. As the cooling proceeds, the interfaces to the liquid region cool faster and thus crystallize first. The grains nucleate from

Figure 2.2: Electron mobilities of materials prepared with different SLS methods. Grain boundary location controlled, or Two-Shot SLS. Directionally Solidified, or Line-Scan SLS. Single Crystal Region, or Dot SLS. [30]

the edges and grow to meet in the middle, fig. 2.3, step 3. There is now a small area of polycrystalline silicon. The sample stage is then translated less than half the laser width, and the sample is exposed to a second laser pulse. This time, the laser melts half of the polycrystalline silicon formed in the first step, and half of the original amorphous silicon film. As the newly formed liquid area cools, grains are again seeded from the solid edges. Because this region overlaps with the previous laser pulse, one edge of the liquid area seeds directly from the polycrystalline silicon, fig. 2.3, step 5. The crystals grow preferentially in the direction of the stage translation, forming elongated grains, fig. 2.3, step 6. This process repeats until the whole area has been transformed from amorphous silicon to polycrystalline silicon. Fig. 2.4 and 2.5 show line-scan SLS material before and after a grain boundary defect etch to highlight the grain boundaries. Fig. 2.6, a transmission electron micrograph, shows the directional elongation of the grains.

Another important aspect of laser crystallization is the refractory layer, placed be-

Figure 2.3: Cross section (left column) and top view (right column) of line-scan sequential lateral solidification (SLS) process flow.

Figure 2.4: Micrograph of line-scan SLS method. Bottom of micrograph shows a single laser beam with a width of around 3.5  $\mu$ m. Top of micrograph shows typical Line-Scan SLS material.

tween the substrate and laser crystallization layer. This refractory layer can withstand the heat of the molten top film and buffers the heat from the underlying substrate, fig 2.7. Typically 500 nm to 1  $\mu$ m of silicon dioxide is used to protect the substrate and keep it cool throughout the laser process.

## 2.3 Laser Crystallization Simulations

Sequential lateral solidification becomes particularly interesting when applied to a stack of multiple materials such as silicon on top of a III-V substrate. In order to use SLS on silicon with lower temperature substrates, the bottom layers must stay cool enough to maintain their properties and avoid damage of the substrate. SLS on

Figure 2.5: Micrograph of line-scan SLS method after a 5 second SECCO defect etch to highlight grain boundaries.

silicon is currently commercialized for glass substrates which can support up to 600°C [31][32][33], and laser processes have also been demonstrated on a variety of substrates including polymers which have a temperature limit of only 150-200°C [34][35][36].

Simulations of the laser process were performed using a finite-difference model method [37]. The simulated structure, shown in fig. 2.8, contains 1  $\mu$ m of silicon dioxide and 100 nm of amorphous silicon. The two planes of interest are the surface temperature at the very top of the amorphous silicon, and the interface temperature between the SiO<sub>2</sub> buffer and the underlying substrate. As discussed in later chapters, the underlying substrate, containing devices such as III-V LEDs or and completed front-end CMOS transistors, cannot withstand high temperature processing.

The simulation begins with a 308nm laser pulse with 30 ns pulse duration starting at time = 0 seconds. The results of this simulation are shown in fig. 2.9, 2.10 and

Figure 2.6: Transmission electron micrograph of high aspect ratio grains in a typical line-scan SLS material. Total size of the micrograph is 9.89  $\mu$ m x 6.95  $\mu$ m.

Figure 2.7: Schematic cross section showing the importance of the buffer layer between the laser-crystallized film and the substrate for heat dissipation.

Figure 2.8: Simulated structure of 100 nm of silicon on top of 1  $\mu$ m of silicon dioxide. Schematic points to the two points of interest: the surface temperature and the interface temperature between the SiO<sub>2</sub> buffer and the underlying substrate.

Figure 2.9: Surface temperature of silicon film during laser processing. Temperature quickly reaches the silicon melt temperature and cools to below 200°C after 2  $\mu$ s.

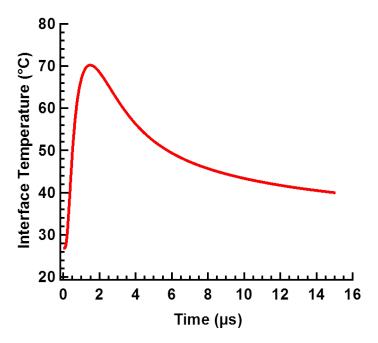

Figure 2.10: Interface temperature between SiO<sub>2</sub> and substrate. The substrate sees a maximum temperature of 70°C during the entire crystallization process.

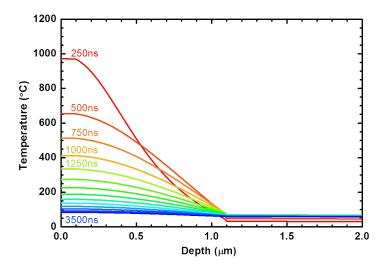

2.11. As expected at the surface, fig. 2.9, the silicon film reaches its melting point very quickly when exposed to the laser. At a wavelength of 308nm, 99.995% of the laser energy is absorbed by the 100 nm of silicon [38][39]. This prevents the laser from heating the substrate and prevents ultraviolet exposure of the substrate. This also implies that the substrate is only heated by diffusive heat energy through the buffer layer from the molten silicon. The film then cools; the second observed increase in temperature, just before 2  $\mu$ s can be attributed to the release in latent heat as the film solidifies from liquid to solid. After solidification, the surface cools very quickly and reaches 200°C after 2  $\mu$ s.

The simulated interface temperature, shown in fig. 2.10, reaches a maximum of 70°C at around 1.5  $\mu$ s. This is the maximum temperature that the substrate encounters during the laser crystallization process. Again, the materials cool exponentially and reach about 40°C by 15  $\mu$ s. Experimentally, the laser is pulsed at 100 Hz, or 10

Figure 2.11: Temperature profile of simulated sample up to 3500 ns during laser processing. Most of the heat used to melt the amorphous-Si is dissipated in the  $SiO_2$  buffer layer before it reaches the substrate below.

ms. This gives the substrate ample time to return to room temperature before the subsequent laser pulse. In industrial systems, laser pulses are around 5000 Hz, or 200  $\mu$ s, again enough time for the substrate to cool back to room temperature between laser pulses.

# 2.4 Thin Film Transistors using Sequential Lateral Solidification

### 2.4.1 Fabrication of TFTs

The thin film transistor fabrication process begins with an electron beam deposition of 1  $\mu$ m of SiO<sub>2</sub> and 100 nm of Si. The deposition chamber has a base pressure of  $10^{-7}$  torr to ensure low gas incorporation and the substrate is held at 400°C during

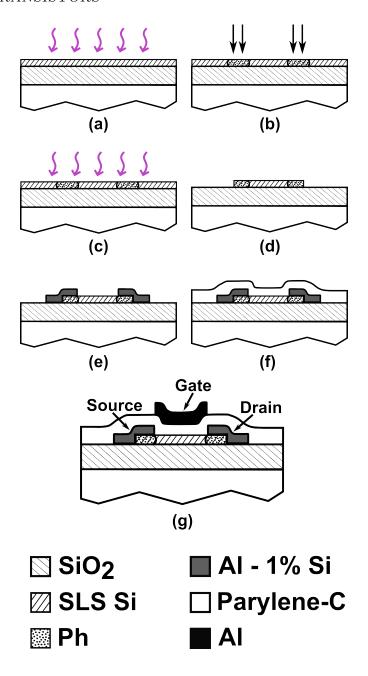

Figure 2.12: Process flow for fabrication of lateral thin film transistors. (a) Laser crystallization of amorphous silicon. (b) Ion implantation for source and drain electrodes. (c) Activation of ion implanted dopants. (d) Definition of silicon active area. (e) Deposition of source and drain electrodes. (f) Deposition of gate dielectric. (g) Deposition of gate metal for completed transistor device.

deposition for improved film quality. Next, line-scan sequential lateral solidification (SLS) laser processing is performed with a 308 nm XeCl excimer laser, fig. 2.12a. In the experimental setup, the laser beam is 6 cm x 1.5  $\mu$ m, with energies above  $300mJ/cm^2$  for complete melting. Each translation of the stage is half the width of the beam, or 0.75  $\mu$ m. This allows the melted silicon to seed crystal growth from the grains grown in the previous pulse. More information on the line-scan SLS process can be found above and in Sposili, et.al. [21]

Select areas are ion implanted with  $1 \times 10^{15}$  cm<sup>-2</sup> of phosphorus at 10 keV to form contact areas for the source and drain, fig. 2.12b. These dopants are then activated with a  $1000^{\circ}$ C, 2 second, rapid thermal annealing process to ensure all implanted dopants are activated, fig. 2.12c. The silicon active areas are then patterned and etched with a SF<sub>6</sub> plasma, fig. 2.12d. Aluminum source and drain contacts are thermally evaporated and patterned using a lift-off process, fig. 2.12e. Contacts are then annealed at 350°C in argon for 1 hour. A 200 nm film of parylene-C is used as a gate dielectric, fig. 2.12f, and finally an aluminum gate metal is evaporated and patterned, fig. 2.12g. A micrograph of the completed devices is shown in fig. 2.13.

#### 2.4.2 Characterization of TFTs