Optically-Connected Memory: Architectures and Experimental Characterizations

Daniel Brunina

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

2012

### Abstract

Optically-Connected Memory: Architectures and Experimental Characterizations

#### Daniel Brunina

Growing demands on future data centers and high-performance computing systems are driving the development of processor-memory interconnects with greater performance and flexibility than can be provided by existing electronic interconnects. A redesign of the systems' memory devices and architectures will be essential to enabling high-bandwidth, low-latency, resilient, energy-efficient memory systems that can meet the challenges of exascale systems and beyond.

By leveraging an optics-based approach, this thesis presents the design and implementation of an optically-connected memory system that exploits both the bandwidth density and distance-independent energy dissipation of photonic transceivers, in combination with the flexibility and scalability offered by optical networks. By replacing the electronic memory bus with an optical interconnection network, novel memory architectures can be created that are otherwise infeasible. With remote optically-connected memory nodes accessible to processors as if they are local, programming models can be designed to utilize and efficiently share greater amounts of data. Processors that would otherwise be idle, being starved for data while waiting for scarce memory resources, can instead operate at high utilizations, leading to drastic improvements in the overall system performance.

This work presents a prototype optically-connected memory module and a custom processor-based optical-network-aware memory controller that communicate transparently and all-optically across an optical The memory modules and controller are interconnection network. optimized to facilitate memory accesses across the optical network using a packet-switched, circuit-switched, or hybrid packet-and-circuit-switched approach. The novel memory controller is experimentally demonstrated to be compatible with existing processor-memory access protocols, with the memory controller acting as the optics-computing interface to render the optical network transparent. Additionally, the flexibility of the optical network enables additional performance benefits including increased memory bandwidth through optical multicasting. This optically-connected architecture can further enable more resilient memory system realizations by expanding on current error dectection and correction memory protocols. The integration of optics with memory technology constitutes a critical step for both optics and computing. The scalability challenges facing main memory systems today, especially concerning bandwidth and power consumption, complement well with the strengths of optical communications-based systems. Additionally, ongoing efforts focused on developing low-cost optical components and subsystems that are suitable for computing environments may benefit from the high-volume memory market. This work therefore takes the first step in merging the areas of optics and memory, developing the necessary architectures and protocols to interface the two technologies, and demonstrating potential benefits while identifying areas for future work. Future computing systems will undoubtedly benefit from this work through the deployment of high-performance, flexible, energy-efficient optically-connected memory architectures.

## Contents

| Li             | st of                                                                                                                                                                                                                                                                                           | Figure  | es                               | V  |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------|----|--|--|--|

| List of Tables |                                                                                                                                                                                                                                                                                                 |         |                                  |    |  |  |  |

| 1              | Introduction  1.1 Trends in Large-Scale Computing  1.1.1 High-Performance Computers  1.1.2 Data Centers  1.2 The Memory Wall  1.3 Main Memory  1.4 The Optics-Computing Interface  1.4.1 Silicon Photonics  1.4.2 Optical Interconnection Networks  1.4.3 Optically-Connected Memory  1.5 Scope |         | 1                                |    |  |  |  |

|                | 1.1                                                                                                                                                                                                                                                                                             | Trends  | in Large-Scale Computing         | 2  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                 | 1.1.1   | High-Performance Computers       | 3  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                 | 1.1.2   | Data Centers                     | 7  |  |  |  |

|                | 1.2                                                                                                                                                                                                                                                                                             | The M   | emory Wall                       | 10 |  |  |  |

|                | 1.3                                                                                                                                                                                                                                                                                             | Main I  | Memory                           | 13 |  |  |  |

|                | 1.4                                                                                                                                                                                                                                                                                             | The O   | ptics-Computing Interface        | 18 |  |  |  |

|                |                                                                                                                                                                                                                                                                                                 | 1.4.1   | Silicon Photonics                | 19 |  |  |  |

|                |                                                                                                                                                                                                                                                                                                 | 1.4.2   | Optical Interconnection Networks | 20 |  |  |  |

|                |                                                                                                                                                                                                                                                                                                 | 1.4.3   | Optically-Connected Memory       | 21 |  |  |  |

|                | 1.5                                                                                                                                                                                                                                                                                             | Scope   |                                  | 24 |  |  |  |

| 2              | Opt                                                                                                                                                                                                                                                                                             | ical In | terconnection Networks for OCM   | 27 |  |  |  |

|                | 2.1                                                                                                                                                                                                                                                                                             | Optica  | l Network Architecture           | 27 |  |  |  |

|                |                                                                                                                                                                                                                                                                                                 | 2.1.1   | Switching Protocols              | 30 |  |  |  |

### CONTENTS

|   | 2.2 | Implie  | eations for Memory Architectures    | 31 |

|---|-----|---------|-------------------------------------|----|

|   | 2.3 | Scalab  | pility                              | 34 |

|   |     | 2.3.1   | OOK Characterization                | 35 |

|   |     | 2.3.2   | DPSK Characterization               | 37 |

|   | 2.4 | Discus  | ssion                               | 40 |

| 3 | Opt | ically- | Connected Memory Modules            | 42 |

|   | 3.1 | Lesson  | ns from Preliminary Work            | 44 |

|   |     | 3.1.1   | Memory Interface Latency            | 44 |

|   |     | 3.1.2   | Bandwidth Matching                  | 45 |

|   |     | 3.1.3   | Burst-Mode Transceivers             | 46 |

|   | 3.2 | OCMI    | M Implementation Details            | 47 |

|   |     | 3.2.1   | FPGA Hardware Structures            | 50 |

|   | 3.3 | Summ    | ary                                 | 53 |

| 4 | Opt | ical-N  | etwork-Aware Memory Controller      | 55 |

|   | 4.1 | Novel   | Memory Access Protocol              | 57 |

|   |     | 4.1.1   | Circuit-Switched Memory Controller  | 60 |

|   | 4.2 | Hybrid  | d Packet- and Circuit-Switched OCM  | 63 |

|   |     | 4.2.1   | Experimental Setup                  | 65 |

|   |     | 4.2.2   | Experimental Results                | 71 |

|   | 4.3 | Memo    | ry Multicasting                     | 73 |

|   |     | 4.3.1   | Multicasting Memory Access Protocol | 74 |

|   |     | 4.3.2   | Experimental Setup and Results      | 76 |

|   | 4 4 | Discus  | ssion                               | 79 |

| 5 | Res | ilient ( | OCM architectures                  | 81  |

|---|-----|----------|------------------------------------|-----|

|   | 5.1 | Backgr   | round                              | 82  |

|   | 5.2 | Overvi   | ew of Error Correction             | 85  |

|   | 5.3 | Experi   | mental Characterization            | 90  |

|   |     | 5.3.1    | Experimental Setup                 | 90  |

|   |     | 5.3.2    | Advanced Error Correction for OCM  | 93  |

|   |     | 5.3.3    | System Performance                 | 95  |

|   |     | 5.3.4    | Results                            | 97  |

|   | 5.4 | Discus   | sion                               | 102 |

| 6 | OC  | M with   | Integrated Silicon Photonics       | 104 |

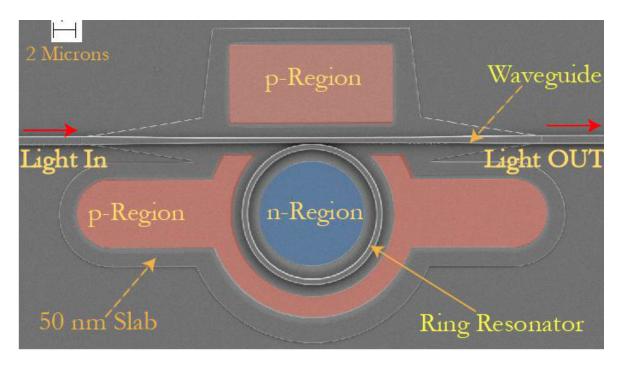

|   | 6.1 | Micror   | ing Nanophotonic Devices           | 105 |

|   | 6.2 | Techno   | ological Challenges of Integration | 107 |

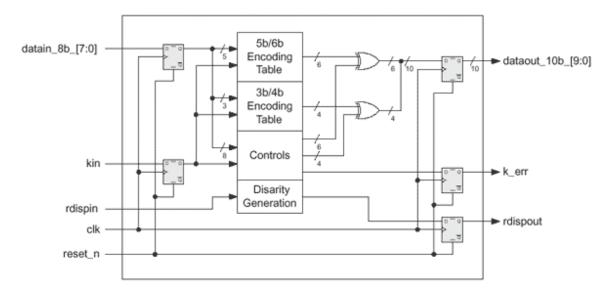

|   |     | 6.2.1    | Line Codes                         | 109 |

|   | 6.3 | Experi   | mental Demonstration               | 112 |

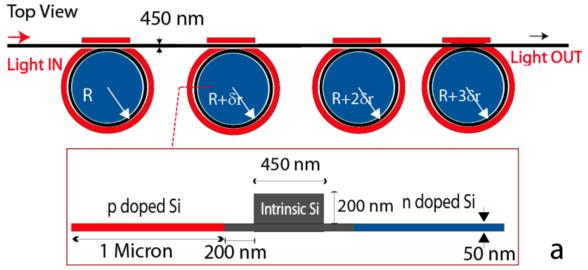

|   |     | 6.3.1    | Silicon Microring Modulators       | 113 |

|   |     | 6.3.2    | Results                            | 117 |

|   | 6.4 | Discus   | sion                               | 118 |

| 7 | Sun | nmary    | and Conclusions                    | 120 |

|   | 7.1 | Overvi   | ew                                 | 120 |

|   | 7.2 | Future   | Work                               | 123 |

|   |     | 7.2.1    | Photonic Integration               | 123 |

|   |     | 7.2.2    | Cluster Architectures              | 124 |

|   |     | 7.2.3    | Burst-Mode Receivers               | 125 |

### CONTENTS

|            | 7.2.4 | Con  | nmerci | ial I | Depl | loyn | nen | t. |   |     |     |      |  |  |  |  |  |  | 126 |

|------------|-------|------|--------|-------|------|------|-----|----|---|-----|-----|------|--|--|--|--|--|--|-----|

| 7.3        | Summ  | nary |        |       |      |      |     |    |   |     |     | <br> |  |  |  |  |  |  | 127 |

| Glossary   |       |      |        |       |      |      |     |    |   | -   | 129 |      |  |  |  |  |  |  |     |

| References |       |      |        |       |      |      |     |    | - | 131 |     |      |  |  |  |  |  |  |     |

# List of Figures

| 1.1 | Performance Trends in Top500 Supercomputers                     | 4  |

|-----|-----------------------------------------------------------------|----|

| 1.2 | Photograph of Power 775 Drawer                                  | 6  |

| 1.3 | Blue Gene Q Compute Chip                                        | 8  |

| 1.4 | The Memory Gap: Graph of Processing Power vs Memory Bandwidth . | 11 |

| 1.5 | Graph of SDRAM Technology Trends                                | 12 |

| 1.6 | Illustration of Memory Scalability Challenges                   | 14 |

| 1.7 | Block Diagram of SDRAM Bank                                     | 16 |

| 1.8 | Illustration Depicting the Integration of Optics and Computing  | 20 |

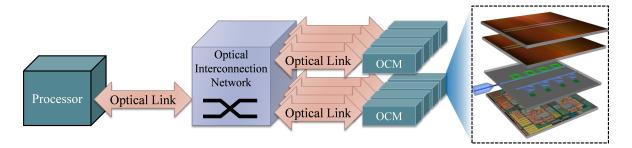

| 1.9 | Optically-Connected Memory Block Schematic                      | 22 |

|     |                                                                 |    |

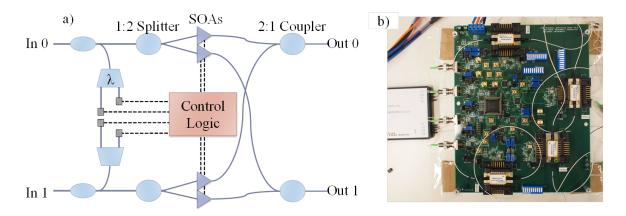

| 2.1 | 2×2 Photonic Switching Node                                     | 28 |

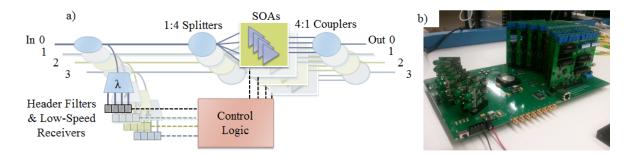

| 2.2 | $4\times4$ Photonic Switching Node                              | 29 |

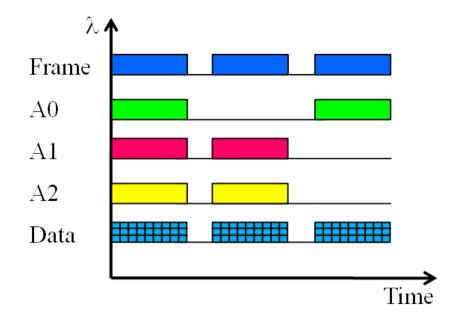

| 2.3 | Wavelength-Striped Message Format                               | 29 |

| 2.4 | 2-Stage 4×4 Network Test Bed                                    | 36 |

| 2.5 | Scalability Characterization: 40-Gb/s OOK Optical Eye Diagrams  | 36 |

| 2.6 | Sensitivity curves for 40-Gb/s OOK and DPSK Scalability         |    |

|     | Characterization                                                | 38 |

### LIST OF FIGURES

| 2.7  | Scalability Characterization: Experimental Setup for DPSK Traffic $$ | 39 |

|------|----------------------------------------------------------------------|----|

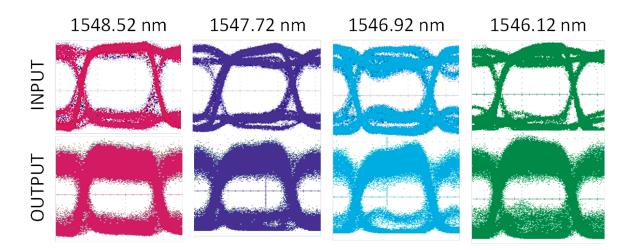

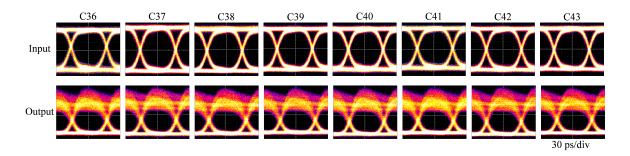

| 2.8  | Scalability Characterization: 40-Gb/s DPSK Optical Eye Diagrams $$   | 40 |

| 3.1  | Photograph of OCMM                                                   | 43 |

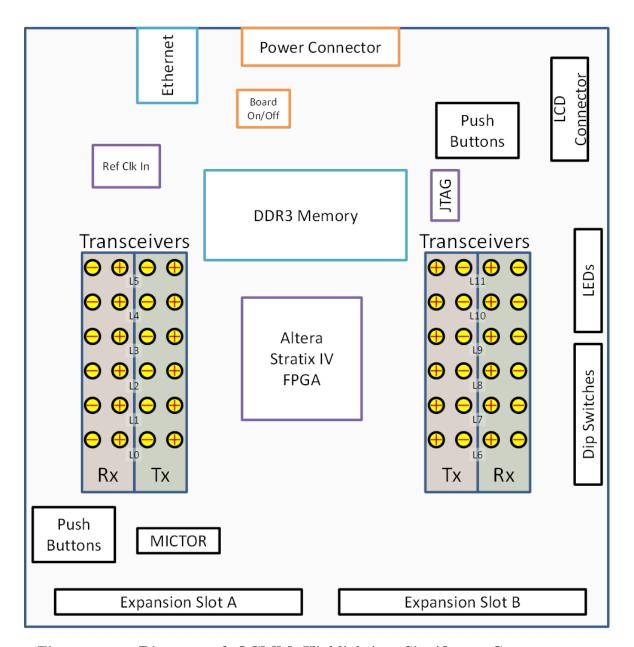

| 3.2  | Diagram of OCMM Highlighting Significant Components                  | 49 |

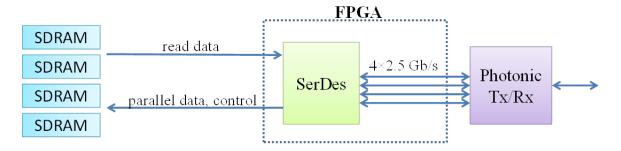

| 3.3  | Architectural Diagram of OCMM Functionality                          | 50 |

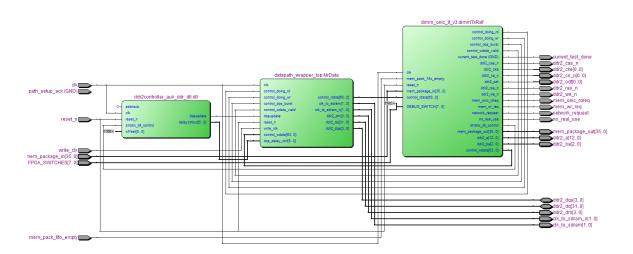

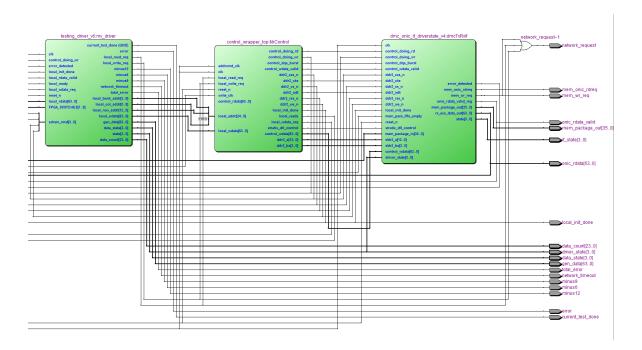

| 3.4  | Graphical Representation of OCMM Verilog Top-Level FPGA Modules      | 51 |

| 3.5  | Graphical Representation of OCMM Data Path Components                | 52 |

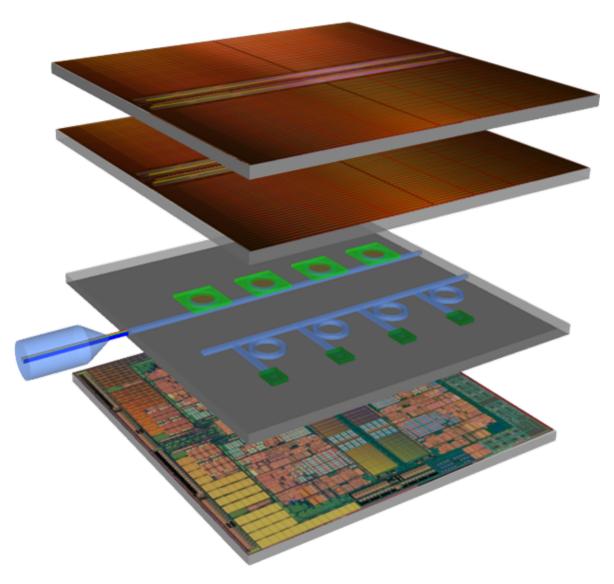

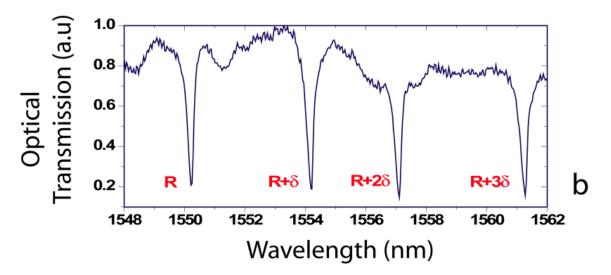

| 3.6  | Illustration of Future OCMM based on HMC                             | 54 |

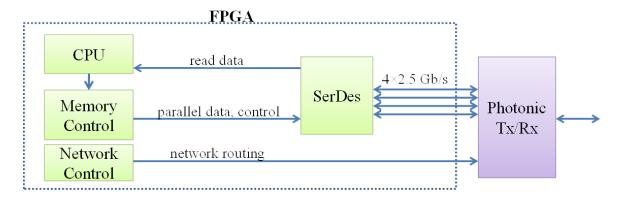

| 4.1  | Architectural Diagram of a Processor Node                            | 56 |

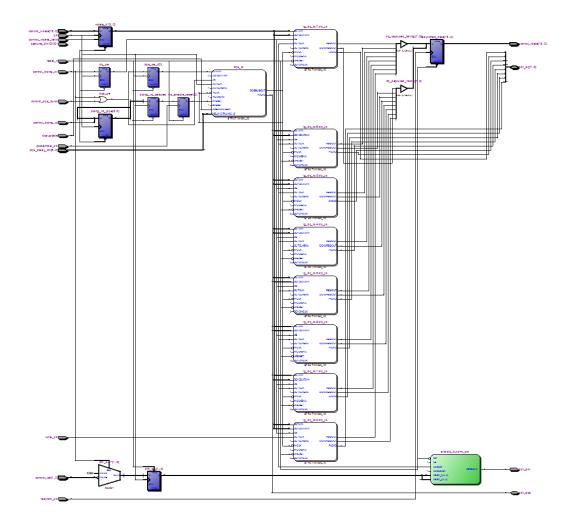

| 4.2  | Graphical Representation of CPU Verilog Top-Level FPGA Modules       | 59 |

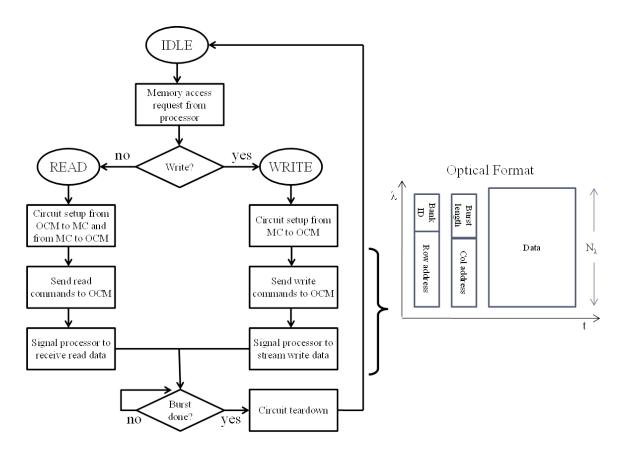

| 4.3  | Circuit-Switched Memory Controller Flowchart                         | 61 |

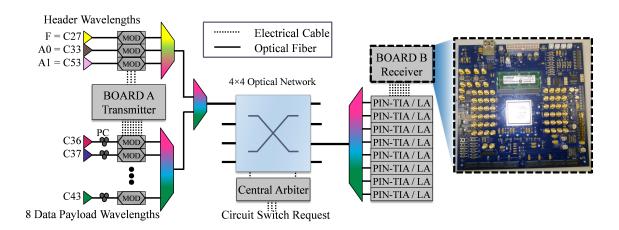

| 4.4  | Hybrid Packet- and Circuit-Switched OCM: Experimental Setup          | 67 |

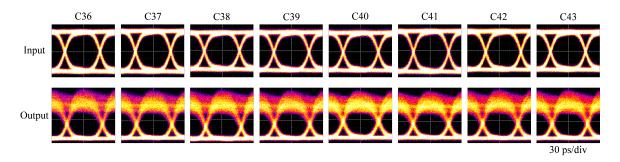

| 4.5  | Hybrid Packet- and Circuit-Switched OCM: Optical Eye Diagrams        | 71 |

| 4.6  | Example Packet- and Circuit-Switched Memory Communication            | 72 |

| 4.7  | Illustration of Memory Multicasting                                  | 74 |

| 4.8  | Block Diagram and Photograph of Memory Multicasting                  | 75 |

| 4.9  | Memory Multicasting: Experimental Setup                              | 77 |

| 4.10 | Memory Multicasting: Optical Eye Diagrams                            | 78 |

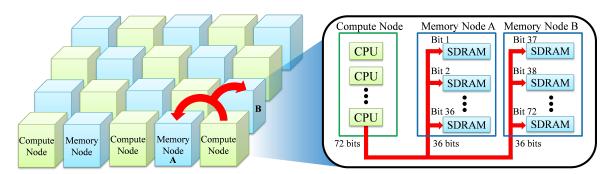

| 5.1  | Illustration of OCM and Compute Nodes Utilizing Proposed Advanced    |    |

|      | OCM ECC                                                              | 84 |

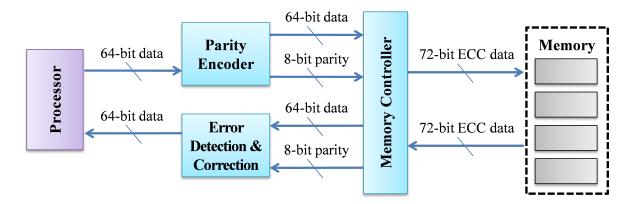

| 5.2  | Architectural Diagram of Proposed Advanced OCM ECC                   | 86 |

| 5.3  | Resilient OCM: Experimental Setup                                    | 92 |

### LIST OF FIGURES

| 5.4 | Graph of Pre-ECC BER vs Post-ECC BER                                          | 99  |

|-----|-------------------------------------------------------------------------------|-----|

| 5.5 | Resilient OCM: Optical Eye Diagrams                                           | 100 |

| 6.1 | SEM Image of Microring Modulator                                              | 106 |

| 6.2 | 8b/10b Hardware Schematic                                                     | 110 |

| 6.3 | SEM Image of WDM Microring Modulator Array                                    | 114 |

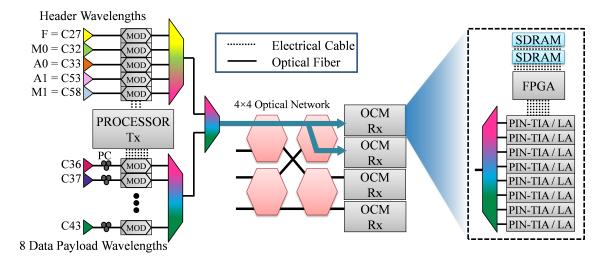

| 6.4 | Schematic and Spectra of Microring Modulator Array                            | 115 |

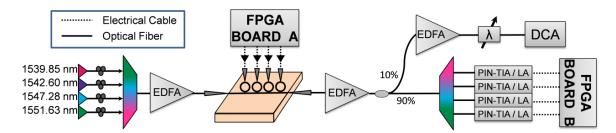

| 6.5 | OCM With Integrated Silicon Photonics: Experimental Setup $\ \ldots \ \ldots$ | 116 |

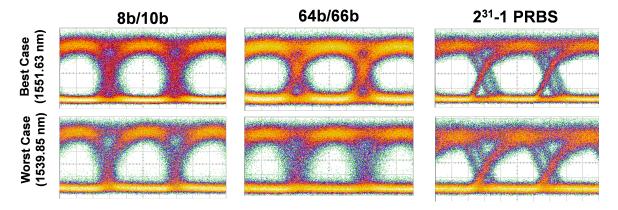

| 6.6 | OCM With Integrated Silicon Photonics: Microring-Modulated Optical            |     |

|     | Eye Diagrams                                                                  | 119 |

## List of Tables

| 6.1 | Comparison  | of   | microring-modulated   | 8b/10b | memory | data, | 64b/66b |     |

|-----|-------------|------|-----------------------|--------|--------|-------|---------|-----|

|     | memory data | a. a | and $2^{31} - 1$ PRBS |        |        |       |         | 118 |

## Acknowledgements

I am grateful for the support of my advisor, Professor Keren Bergman, for her leadership and vision that have guided me through my doctoral studies. I have learned a great deal from her, and none of this work would have been possible without her.

Thank you to the members of my dissertation committee: Professor Richard Osgood, Professor Luca Carloni, Professor Ken Shepard, and Dr. Jeffrey Kash. Professor Richard Osgood, having taught several of my optics classes, was an integral part of my Columbia education. Professor Luca Carloni has always been an eager source of feedback, and our discussions contributed greatly to my research. Thank you to Professor Ken Shepard for his humor and contributions to this work.

I am especially grateful to Dr. Jeffrey Kash for having had the opportunity to intern with his amazing research group. While at IBM Research, I had the opportunity to work with Clint Schow, Petar Pepeljugoski, Alexander Rylyakov, Dan Kuchta, Marc Taubenblatt, Laurent Schares, Fuad Doany, and Ben Lee. All of these kind, brilliant individuals made the internship an invaluable learning experience and I am grateful to them all. During that period, Ben Lee, whom I only knew briefly during his final year in the Lightwave Research Laboratory, took the time to impart to me his wisdom and experience and I thank him immensely.

Thank you to all the members of the Lightwave Research Laboratory, past and present. I had the pleasure of being mentored by Howard Wang and Ajay Garg, and the majority of my lab skills were learned from them. Throughout my time at Columbia,

they were always willing to engage in research discussions and provide valuable feedback on any ideas. Thank you to Caroline Lai, who worked with me on multiple experiments and provided mentorship both in the lab and in the subsequent research papers. I would like to thank Noam Ophir, Kishore Padmaraju, Michael Wang, Johnnie Chan, and Gilbert Hendry for their friendship and research discussions throughout the years. I have enjoyed mentoring, and hopefully have been useful to, the younger students: Atiyah Ahsan, Cathy Chen, Robert Hendry, Qi Li, Lee Zhu, Christine Chen, and Gouri Dongaonkar. Also, thank to you to Cedric Ware, Balagangadhar Bathula, Lin Xu, Wenjia Zhang, and Dawei Liu for your contributions. To all of you: I look forward to continuing our relationships in the future, both as colleagues and as friends. I wish everyone the best of luck.

I am especially thankful to my friends and family. I am most of all thankful to my mother - without your endless support and hard work I would of course not be here (literally and figuratively). Thank you to my brothers, grandmother, and great-grandmother. Thank you, Brian, for almost 20 years of friendship. It is not possible to complete a dissertation, while remaining sane, without family and a good friend.

This thesis is dedicated to my mother and grandmother.

## Chapter 1

## Introduction

Next-generation large-scale high-performance computing (HPC) systems and data centers will require microprocessors to support unprecedented off-chip bandwidths to memory, with low access latencies and interconnect power dissipation. However, today's off-chip electronic interconnects face performance challenges with low bandwidth densities, as well as distance- and data-rate-dependent energy dissipation. As a result, large-scale systems have experienced an exponentially growing performance gap between the computational performance of microprocessors and the performance of off-chip main memory systems [1]. This communications bottleneck will undoubtedly limit the overall system performance and scalability of future large-scale systems. Due to the trade-offs among the requirements in communication bandwidth, latency, and energy efficiency, the systems' high-performance microprocessors will be starved for memory data [2, 3]. Furthermore, growing data sets and server virtualization are placing demands on the system, limiting the types of applications that may be supported.

Although it is feasible for electronic interconnection networks to reach per-channel data rates up to 25 Gb/s [4], the power dissipation at such high bandwidths becomes overwhelming and contributes greatly to increased overall system cost and complexity. Currently, microprocessors are estimated to dissipate half of their energy in the interconnect alone [5]. Scaling interconnect performance using traditional approaches would continue to exacerbate this imbalance. For example, a typical main memory system consists of multiple chips of synchronous dynamic random access memory (SDRAM) packaged together onto a circuit board called a dual in-line memory module (DIMM), which is capable of providing over 120 Gb/s of peak bandwidth [6]. Multiple DIMMs must be accessed in parallel, requiring an extremely complex electronic bus, to provide the many terabits-per-second of memory bandwidths required by dataintensive applications. However, the scaling challenges facing electronic interconnects limit the number of DIMMs that can be accessed, and, consequently, the total memory bandwidth. Increasing the per-channel SDRAM data rate has been attempted [7]; however, the resulting system remains limited in use due to its significantly higher energy consumptions.

### 1.1 Trends in Large-Scale Computing

HPCs and data centers magnify the limitations of memory scalability. Their extreme scale requires high sustained memory bandwidth and capacity, while simultaneously maintaining low access latency with energy-efficient interconnects. These factors, however, require trade-offs in an electronically-interconnected memory system and reduce the total system-wide performance. Next-generation large-scale computing

systems must therefore leverage novel physical-layer technologies in order to close the processor-memory performance gap and enable future microprocessors to achieve their full potential.

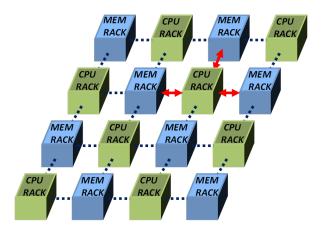

#### 1.1.1 High-Performance Computers

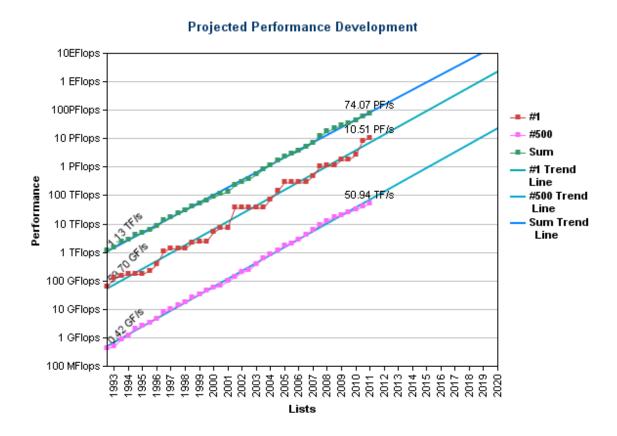

HPCs, or supercomputers, are designed to optimize processing capacity and are typically used for calculation-intensive such as: climate modeling [8], oil and gas exploration [9], quantum physics [10], and nuclear research [11]. Today's supercomputers employ tens of thousands of processors and petabytes of memory to achieve the targeted performance, as rated in floating-point operations per second (FLOPS), on the order of petaFLOPS. Given the trend in HPC performance (Figure 1.1), an exaFLOP machine should be created within this decade. Such extremescale computers rely heavily on efficient interconnects to provide the high-performance processing cores with a stready stream of data. The interconnects for these systems are typically electrically-interconnected three-dimensional (3D) torus topologies [12]. However, with the ever-increasing demands being placed on the interconnect, future HPCs require a redesign at the physical layer, potentially capitalizing on the benefits presented by optical interconnects [13].

A recent example of this trend is IBM's Power 775 [15], which was created in response to the Defense Advanced Research Projects Agency (DARPA) initiative for High Productivity Computing Systems. The goal of this initiative was to enable the creation of HPCs that are economically viable. With this goal in mind, a significant amount of inter-node communication was moved from the traditional electrical domain

Figure 1.1: Performance Trends in Top500 Supercomputers - The performance of the top supercomputers has increased by roughly  $10 \times$  every 4 years [14].

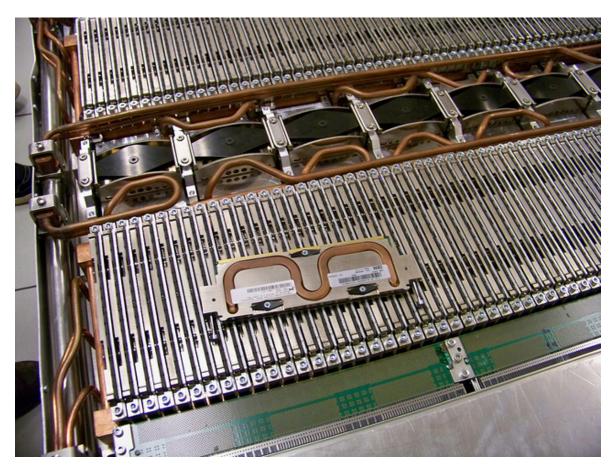

to the more efficient optical domain. Each Power 775 drawer contains up to eight nodes of four POWER7 [16] processors, resulting in up to 256 POWER7 cores and 128 DIMMs (yielding 2 TB of total memory capacity). The DIMMS (Figure 1.2) are very densely packed, requiring water cooling, due to the immense required memory bandwidth and the high power and writing complexity of electrically connecting those DIMMs to the cores. Twelve of these drawers can be combined into one rack, which requires over 1,500 DIMMs, for a total performance of 96 TFLOPS. The most notable advancement on the Power 775 drawer is the hub controller, which contains a combination of optical and electrical transceivers to achieve an aggregate 1.1 TB/s communication bandwidth.

The primary reason for a shift to optical interconnects within HPCs is the need to both overcome electrical bandwidth limitations and achieve a high FLOPS/Watt ratio. As supercomputers continue to grow, incorporating more processors and larger interconnection networks, the operating costs due to power have become a significant design consideration. This constraint results in the following trend: maximizing computational performance is no longer the only focus when designing HPCs. With this in mind, four of the top 10 supercomputers are based on the optically-interconnected Blue Gene/Q [17] architecture; at 2097.19 MFLOPS/Watt [18], this design is the most energy-efficient HPC architecture. In contrast, the electrically-connected Tianhe-1A supercomputer [19] in China consumes over 4 megawatts. If this system was located in the US, it would cost an average of 10 cents per kilowatt hour [20], and would therefore result in an electricity bill of over \$3.5 million per year; this is typical of the Top 10 systems listed on the Top500 [14].

The current top supercomputer, IBM Sequoia [14], is a Blue Gene/Q-based16.32

Figure 1.2: Photograph of Power 775 Drawer - IBM's Power 775 drawer contains up to 256 cores and 128 DIMMs. The components are densely packed to maximize performance, which necessitates water cooling. Hub modules enable high-performance optical links between drawers [15].

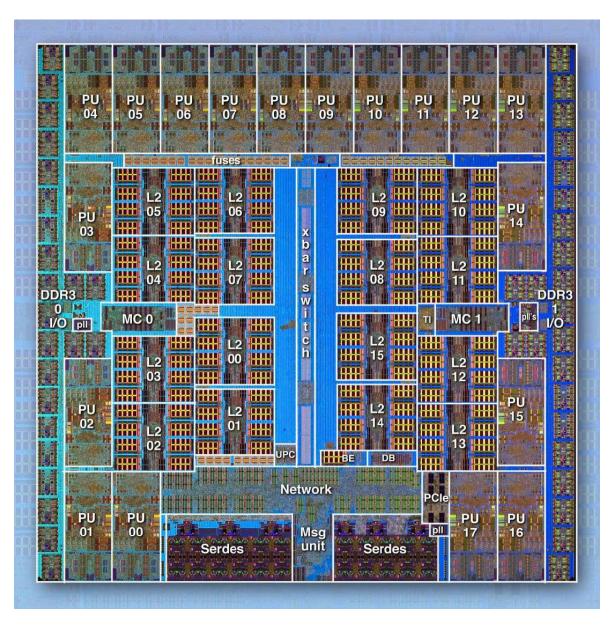

petaFLOPS machine that uses over 1.5 million cores. With a total power consumption of 7.9 MW, Sequoia is not only 1.5 times faster than the second-ranked supercomputer, the K computer [21], but also 150% more energy efficient. The K computer, which utilizes over 80,000 SPARC64 VIIIfx processors [22], results in the highest total power consumption of any Top500 system (9.89 MW). IBM Sequoia achieves its superior performance and energy efficiency through the use of custom compute chips and optical links between compute nodes. Each compute chip (Figure 1.3) contains 18 cores: 16 user cores, 1 service, and 1 spare [17]. The chips contain two memory controllers, which enable a peak memory bandwidth of 42.7 GB/s, and logic to communicate over a 5D torus that utilizes point-to-point optical links.

These trends demonstrate that current HPCs are already pushing the limits of traditional, electrical interconnection networks, not only in terms of performance but also energy. Future exascale HPCs will require unprecedented levels of processor-memory and inter-node communication, and thus require substantially higher bandwidth-density than is available in today's HPCs. The distance-dependent energy dissipation and low bandwidth-density of electrical interconnects will thus make such next-generation HPCs too expensive to operate or simply impractical to build, and a shift to optical interconnects is therefore required.

#### 1.1.2 Data Centers

Data centers are large-scale computing systems with high-port-count networks interconnecting many servers, typically realized by commodity hardware, which are designed to support diverse computation and communication loads while minimizing

**Figure 1.3: Blue Gene Q Compute Chip** - IBM's Blue Gene Q compute chip contains 18 cores and dual DDR3 memory controllers for 42.7 GB/s peak memory bandwidth. Compute nodes are connected by a 5D torus with optical links [17].

hardware and maintenance costs. Contemporary data centers consist of tens of thousands of servers, or nodes, and new mega data centers are emerging with over 100,000 nodes [23]. The tremendous rise of cloud computing has caused a dramatic increase in the need for a greater number of larger data centers in order to handle the diverse, unpredictable communication between the computational nodes/servers. Simultaneously, these data centers must remain inexpensive to build and operate in order to maximize the profitability of the underlying applications. The design constraints on data centers therefore focus on the conflicting goals of minimizing cost while meeting the high-performance requirements of future cloud services.

The performance scaling of data centers is primarily hindered by the unpredictable, communication-intensive workloads that can consist of both bursty and long-lived traffic [24, 25]. Typically, data centers are required to support data-intensive applications, such as internet searches, which require vast amounts of data to be readily available at all times. These targeted applications are most efficiently realized with the search data stored in main memory. This is due to: the relative slow speed of hard disks, which have high data capacity but unacceptably high access latencies; and the relative small storage size of on-chip memories, which could deliver the data in a fast way but cannot possibly contain all the search data [26]. Main memory therefore possesses the ideal capacity-speed ratio, at an acceptable price, for data center applications. The result is that data center networks must deliver varying amounts of memory data between servers in in a low-cost, high-performance, unpredictable manner.

Existing attempts to optimize networks for such heterogeneous traffic [27, 28] have only increased bandwidth at the expense of added complexity and power dissipation,

and therefore cost, due to the use of electronic-based switches. The resulting tradeoff makes fat trees [29] a desirable topology for data centers; however, the resulting configuration is one with significant oversubscription of the data center interconnection network, reducing overall performance to maintain an adequate performance/cost ratio.

Recent developments in data center architectures have focused on improving the performance/cost ratio by addressing the underlying physical-layer technology within the network. High-radix microelectromechanical systems- (MEMS) based optical circuit switches have been proposed as an attractive addition to data center interconnection networks [30, 31] due to the superior energy efficiency and bandwidth density of optics as compared to electrical switches. However, the main drawback of a MEMS-based approach is the relatively high switching latency associated with the technology, leading to an inflexible network. Furthermore, such implementations are inadequate for handling diverse and unpredictable data center traffic, and therefore additional physical-layer advancements are necessary for next-generation data centers.

## 1.2 The Memory Wall

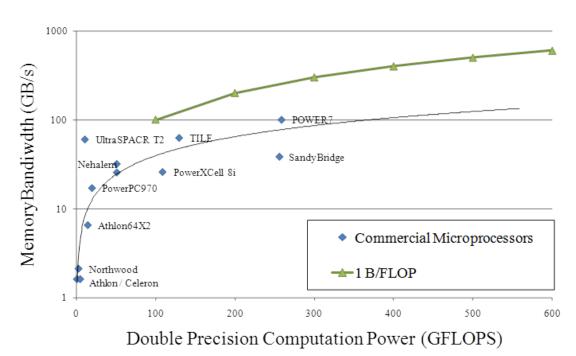

The growing disparity between processor performance and memory bandwidth has been termed the "Memory Wall" [32]. Between the years 1980 and 2000, the typical processor improved in performance (measured in MFLOPS) by approximately 50% per year, while memory bandwidth only improved by 35% per year [33]. Figure 1.4 illustrates the continuation of this trend with modern processors. The trend line for modern processors is compared to a reference 1 B/FLOP metric, which would indicate an equal amount of memory bandwidth and processor performance, and highlights the

continued growth of the processor-memory gap.

Figure 1.4: The Memory Gap: Graph of Processing Power vs Memory Bandwidth - A comparison of processor performance (GLOPS) to memory bandwidth for recent high-performance processors. The 1 B/FLOP reference line illustrates the increasing gap between performance and memory bandwidth.

The primary cause of the Memory Wall is a significant drop in bandwidth when moving from on-chip to off-chip communication, combined with the relatively high latency of SDRAM access compared to processor clock speeds. For example, the Sony-IBM-Toshiba Cell processor inter-core network can achieve bandwidths of 100 GB/s [34], while a high-performance off-chip memory link can only reach 10 GB/s [35]. A primary cause of this gap is that SDRAM technology operates at a fraction of the clock frequency of modern processors [6]. Therefore, increasing the

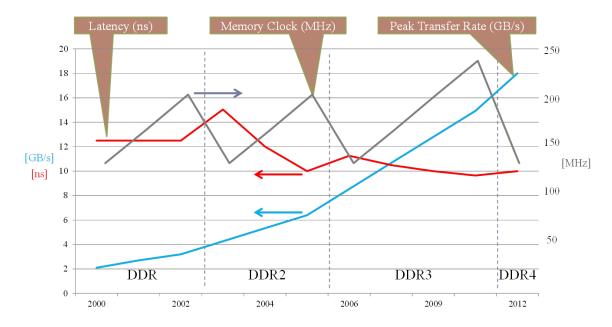

bandwidth of memory systems requires increasing the number of memory devices, which are subsequently accessed in parallel on a multi-drop bus to improve bandwidth. Each new memory device increases the physical wiring distance and capacitive load on the multi-drop memory bus. Additionally, skew limits require the electrical traces to be path-length matched [13]. The wire length and routing complexity combine to limit the minimum memory access latency and maximum bus signaling rate. The result is that while SDRAM peak bandwidth has increased roughly 10-fold over the past decade, the clock speeds and latencies of the SDRAM devices have remained almost unchanged (Figure 1.5) [36, 37].

Figure 1.5: Graph of SDRAM Technology Trends - Over the last four generations of SDRAM technology, the bandwidth has increased approximately 10-fold while latency has decreased very little. [36, 37].

Even assuming the latency of SDRAM itself can be improved to match the speed of

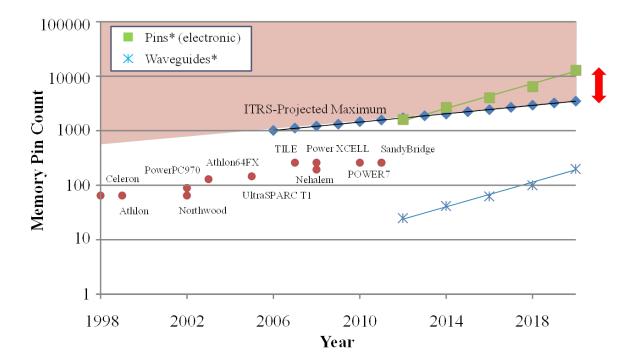

processors, the Memory Wall will persist due to limited off-chip bandwidth. Figure 1.6 illustrates how future systems will be constrained by pin-channel data rates and pin counts. The low bandwidth-density of electronics has limited memory per-channel data rates to at most 1 GHz [6] and therefore a typical DIMM utilizes a 64-bit wide electronic bus. Increasing memory bandwidth by accessing multiple DIMMs in parallel requires the processor to dedicate more pins to the memory bus, with 64 bits per parallel access (i.e. each memory channel). International Technology Roadmap for Semiconductors (ITRS) projections indicate that even next-generation high-performance processors cannot dedicate more than a few thousand pins to memory [3] even in the most aggressive estimates. Increasing the per-channel data rates is prohibitively expensive in terms of energy efficiency due to the data rate- and distance-dependent nature of electronic wiring power dissipation. The two combined factors place an upper limit on potential memory bandwidth of future processors. This trend necessitates either a shift in HPC and data center roadmaps to account for higher costs and lower performance systems, or the deployment of novel optical interconnect and switching technologies.

### 1.3 Main Memory

Contemporary memory systems are arranged in a hierarchy that is designed to balance data capacity and access efficiency. At the top of the hierarchy, i.e. closest to the processor, the on-die caches provide access to data at near-processor speeds but must remain limited in size to a few megabytes to minimize latency. At the bottom of the hierarchy, hard disks can support terabytes of data storage per device, as required by data centers' targeted applications, but their low bandwidth and millisecond access

Figure 1.6: Illustration of Memory Scalability Challenges - The number of pins on commercial processors dedicated purely to memory has increased with time to meet growing memory bandwidth demands. Future systems using electronic pins will soon require a greater number of pins than is physically possible to implement [3]. A shift to optical interconnects can accommodate the bandwidth requirements with a small number of waveguides. This graph is for a hypothetical system assuming: 1 TFLOPS in 2012 and performance doubling every 2 years, 1 B/FLOP required memory bandwidth, and per-channel data rate scaling from 5 Gb/s (2012) to 12.5 Gb/s (2020).

times can easily limit overall system performance. The optimal balance between speed and capacity currently lies in main memory (typically SDRAM), which is in the middle of the memory hierarchy.

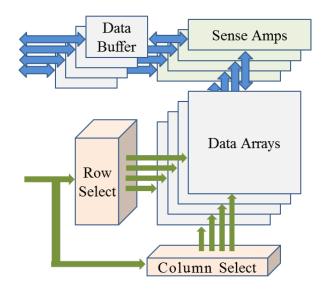

Current commercial memory modules are packaged as DIMMs, which contain multiple SDRAM chips and can provide access to gigabytes of capacity with over 100 Gb/s memory bandwidth and tens of nanoseconds access time [37]. Each SDRAM chip is comprised of several independent memory banks (Figure 1.7), which are accessed independently to allow the processor's memory controller (MC) to pipeline memory accesses to different banks. The main components of a bank are the data buffers, sense amplifiers, and data arrays. The sense amplifiers are the interface between the data arrays and the data buffers, and the data buffers function similarly to a serializer/deserializer (SerDes) for the MC-SDRAM data path. At each SDRAM clock cycle, typically 100-300 MHz, the data arrays store multiple kilobits of parallel data in the data buffers. The data buffers then transfer 64-bit data words (or 72-bit words if error correction is enabled) to the memory controller at clock frequencies up to 1 GHz with two transfers per clock cycle. This double-pumping of the 64-bit, 1-GHz memory bus allows high-end SDRAM systems to achieve peak transfer rates of over 100 Gb/s.

Accessing SDRAM is a multi-step process that requires tens of nanoseconds [6]. All main memory accesses are handled by a memory controller. The memory devices themselves, typically DIMMs, remain essentially idle in the absence of instructions from the memory controller. The microprocessor issues read-to- or write-from-memory requests to the memory controller, which translates the requests into a series of SDRAM-specific commands that are re-ordered to maximize memory bandwidth.

Figure 1.7: Block Diagram of SDRAM Bank - Anatomy of one bank of SDRAM. Four data arrays share common row and column selects for concurrent access.

Typically, the first command sent is an activate (ACT) instruction along with bank and column address bits. This step causes the sense amps to transfer all bits from the activated row into data buffers (thousands of bits over multiple modules). Next, the memory controller sends a read (RD) or write (WR) command along with the column address. For a write, the memory controller will transmit data on the data bus and overwrite any data stored at the corresponding address. A read command will use the column address to select the desired bits from the data buffers, causing the read data to be transmitted back to the memory controller.

Bandwidth is optimized by re-ordering SDRAM accesses such that all reads and writes are addressed to the same row within the SDRAM data arrays. Due to the processor-SDRAM performance gap, each access to a new row requires multiple SDRAM clock cycles and hence incurs tens of nanoseconds of latency. Therefore,

in addition to re-ordering memory accesses, the memory controller also requires the microprocessor to access SDRAM in blocks of eight data words, known as bursts, to guarantee a minimum number of accesses to a row. The burst size has doubled with each new generation of SDRAM technology, which has allowed the memory bandwidth to increase without real gains in the actual speed of SDRAM devices, and thus comes at the cost of memory access granularity.

The need to replace the complex, parallel memory bus is evident in industry; the Fully Buffered Dual In-line Memory Module (FB-DIMM) was presented as an electronic solution to memory speed and density [7]. The goal of FB-DIMM is to alleviate the limitations of electronic interconnect scaling by incorporating SerDes to operate the data bus at 12 times the memory clock rate, resulting in electronic serial links clocked at several GHz. The traditional parallel multi-drop bus is replaced by 24 point-to-point links, configured as a daisy chain, with the MC only directly communicating to one FB-DIMM. If a memory transaction is not addressed to the first FB-DIMM in the daisy chain, the transaction is passed along to the next FB-DIMM with a latency penalty of approximately 4 ns [26]. Although using FB-DIMM increases scalability by improving bandwidth density and thereby reducing pin count, the electronic interconnect will still limit memory systems in large-scale computer systems. Chaining together too many FB-DIMMs in a single channel results in unacceptable memory access times. Adding too many memory channels will not only overburden the memory controller but will also lead to the same pin count and wiring problems with traditional parallel electronic wiring.

Overall, advancements in main memory technology have lagged well behind those

of processors. The resulting Memory Wall threatens to stifle future processor advancements to due the lack of high-bandwidth, energy-efficient access to memory data. Thus far, attempts to increase the number of memory channels or scale up perchannel data rates have required unacceptable trade-offs between bandwidth, latency, and power. It is abundantly clear that a shift from electrical wires will be necessary as the next step for achieving improved processor-memory links.

## 1.4 The Optics-Computing Interface

The use of photonic technology can enable high-bandwidth links, with novel functionalities to reduce off-chip data access latency and power dissipation [38]. The integration of on-chip silicon photonic transceivers [39] will further enable processor-memory communication with the off-chip bandwidth and energy-efficiency performance equal to that of on-chip communications [39, 40]; this would be impossible using conventional electronic interconnects. In addition to achieving high per-channel data rates, optical interconnects can significantly improve communication bandwidths through wavelength-division multiplexing (WDM), and can therefore support many terabits-per-second of optical bandwidth using a single waveguide or optical fiber [41].

Active optical cables serve as an intermediate step in the shift toward optics in computing; however, such implementations still rely on traditional, inefficient electrical transceivers and therefore provide only modest performance or energy improvements. Meanwhile, the development of optical switching [42, 43, 44, 45] can drastically improve the overall performance and energy efficiency of HPCs and data centers. The challenge lies in combining the disparate technologies of computing and optical

networks to maximize the benefits achieved within a future optically-enabled computer system. The electronic technology within microprocessors has been optimized for short-distance, bursty communication that relies heavily on point-to-point links where data is frequently buffered and retransmitted. In contrast, a lack of optical buffer technology has resulted in the development of optical networks that utilize unique communication protocols that do not directly map to existing electronic systems. It is therefore necessarily to develop an optics-computing interface that can enable future processors to fully leverage the benefits of optical interconnects without significantly modifying the underlying processor functionalities.

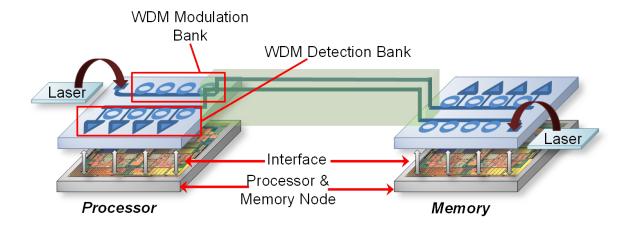

#### 1.4.1 Silicon Photonics

Close integration of photonic and processor/memory hardware is essential to realizing the full potential benefits of off-chip optical interconnects. Recent advances in silicon photonics have yielded high-performance, compact, energy-efficient, CMOS-compatible nanophotonic devices [46, 47]. Integrating these silicon photonic components with processors and memory (Figure 1.8) will eliminate the need for power-hungry off-chip electronic wires, alleviate pin-count constraints, and maximize memory bandwidth with WDM. The resulting alignment of off-chip memory bandwidth with on-chip bandwidth enables processors to access remote memory as if it were local, which is unachievable with electronic interconnects due to pinout limitations.

Silicon photonics remains a relatively immature technology, and as of yet, no process exists to fully integrate photonic transceivers directly with processors or memory devices. However, recent advances have shown optical transceiver modules that can be

Figure 1.8: Illustration Depicting the Integration of Optics and Computing - Silicon photonic modulators and detectors can be integrated with processors and memory to enable energy-efficient, high-bandwidth communication.

closely packaged with electronic transceivers [48] and processor/memory devices can communicate via non-integrated silicon photonic components [49]. These critical steps demonstrate the potential for optically-enabled processors and memory devices, and motivate the continued research of this area.

### 1.4.2 Optical Interconnection Networks

Optical interconnection networks (OINs) comprise an attractive solution to the communication bottleneck within future large-scale computing systems [13, 44, 45, 50].

Optical MEMS-based switches, such as those considered for deployment in data centers today, suffer from high switching latency and are thus unsuitable for most networks. Meanwhile, semiconductor optical amplifiers (SOAs) have been demonstrated to provide high-bandwidth, low-latency switching [43, 51] for optical switches. Additionally, silicon photonic devices can create high-bandwidth, low-

latency, energy-efficient switches [52] that can then be used to create large-scale optical networks [53]. However, as mentioned in the previous section, silicon photonics in relatively immature and is not yet suitable for the creation of large-scale optical networks. SOA-based OINs thereby serve as the basis for this dissertation. The developed protocols remain compatible with both SOA-based or silicon photonic switches.

### 1.4.3 Optically-Connected Memory

Memory interconnect architectures are especially well-suited for the deployment of optical interconnects, and especially optical networks, owing to the performance and energy requirements of main memory systems, as well as the necessary flexibility within a network to support potentially diverse and unpredictable traffic patterns. Leveraging the bandwidth-density and distance-immunity of optics will alleviate pincount constraints in microprocessors and enable optically-connected memory (OCM) to be more physically-distant from the processor, thus yielding the potential for a greater number of memory devices to be connected and accessed in parallel (Figure 1.9). The latency of these links are dictated purely by the fiber's time-of-flight latency [54], allowing efficient, transparent optical networks to provide low memory access latency. In this way, an OCM system can be constructed with greater performance and capacity, while achieving lower memory access latencies and reduced power consumptions as compared to traditional electrically-connected memory systems.

A large body of research investigates leveraging optical interconnects to address the limited scalability of main memory. The work in [55] explores the impact of

Figure 1.9: Optically-Connected Memory Block Schematic - Block schematic depicting how a next-generation processor can be connected to many optically-connected memory modules across an optical interconnection network. Inset illustrates a memory module that uses 3D-stacking to integrate SDRAM with photonic transceivers and associated driver circuitry.

accessing large banks of remote memory across optical links. The authors focus on symmetric multiprocessing (SMP) systems, and demonstrate that, within large SMP systems, the improved bandwidth from optical links outweighs the increased time-of-flight latency incurred from moving optically-attached memory physically away from processing elements.

The authors in [56] present a photonic network-on-chip (NoC) that accesses off-chip main memory, in the form of SDRAM, through a circuit-switched optical interconnect. Circuit-switched, optical access to memory was demonstrated to improve performance and reduce power consumption when compared to electrical interconnects for applications with long, predictable memory access patterns. The authors later explored the use of time-division multiplexed arbitration [57] as a means to improve routing efficiency for more diverse message sizes.

OCDIMM [58] is an optically-connected memory module based on FB-DIMM, in which silicon photonics realized near the processors and memory modules allow the

electronic memory bus to be replaced with waveguides as a shared, wavelength-routed bus. The unique advantage here is the improved memory access latency when compared to traditional FB-DIMM. The main drawback to this work is the lack of an optical interconnection network. This work effectively creates an optical daisy chain, which suffers from non-uniform latencies that could become unacceptably high as the number of memory devices increases. Each optical message must also pass through several devices in the chain to reach its destination, incurring additional insertion loss, which can also limit scalability.

In [59], the authors propose a substantial redesign of memory devices through monolithic integration of silicon photonics. This implementation assumes that silicon photonic modulators and receivers can not only be successfully monolithically integrated into memory devices, but that they can be operated at per-channel data rates of at least 10 Gb/s. The memory fabrication process is optimized for DRAM cell density, as opposed to processor fabrication that is optimized for speed, and it is therefore unlikely that any devices, electrical or photonic, can operate as proposed in [59].

The most plausible near-term method for integrating memory and photonics is the use of photonic transceiver modules packaged at the processors and memory. This is similar to FB-DIMM and OCDIMM; however, significant performance and scalability gains can be achieved from using an OIN to link many memory devices to the processor as nodes on a network. Each optically-connected memory module (OCMM) could then be accessed with uniform, low-latencies as dictated by the optical network architecture. From the perspective of the processor, each path through the optical network would

be analogous to a traditional memory channel. For example, a packet-switched optical network can provide low memory access latency for short messages, while a circuit-switched optical network delivers greater performance for longer messages (e.g. in a streaming application) [56]. To optimally route heterogeneous memory traffic, a hybrid packet-and-circuit-switched optical network [60] could be deployed between processors and memory.

In the long term, 3D integration can enable optical transceivers to be incorporated directly with processors and memory devices without the need for monolithic integration. For example, multi-layer deposited materials [61] can realize high-performance optical modulators and receivers adjacent to standard CMOS-fabricated cores. 3D-stacked memory devices, called hybrid memory cubes (HMCs), are currently under development [62] to address the lack of high-speed logic within DRAM fabrication technology. The HMC is an ideal insertion point for photonics into memory because of their 3D-integrated nature and the presence of a high-speed logic layer that can not only interface the memory cells to high-speed logic, but also the high-speed logic to photonic modules and receivers.

### 1.5 Scope

The primary contribution of this dissertation is the development and implementation of the first ever OCM system. In this system, the electrical bus between a processor and its memory is replaced by an optical interconnection network; to achieve this, processors and memory devices interface with local photonic transceivers. Additionally, this work encompasses the creation of a novel optical-network-aware memory controller

that serves as the optics-computing interface. A series of experiments is presented to characterize the OCM system across the four key metrics that must be addressed by next-generation HPCs and data centers:

- Bandwidth: The low bandwidth-density of electrical interconnects [2] and pintcount constraints [3] limit memory bandwidth. OCM must enable a roadmap to exascale memory architectures;

- Latency: The lower bound of memory access latency is the access time of each SDRAM cell [37]. Optical networks must be designed to minimize, or eliminate, any additional latency as compared to a traditional electrical memory link;

- Energy: Microprocessors dissipate up to half of their energy in the interconnect alone [5], and the electronic bus linking main memory to its processor has become a significant source of power dissipation. Significant power savings can be achieved by eliminating both the electronic memory bus and the associated input/output (I/O) buffers at each end of the link;

- Resilience: Increasing the number of memory devices in a system, as with any commodity hardware, increases the probability of a failure within the memory system as a whole [63, 64]. OINs enable novel memory protocols that can improve reliability beyond what is possible using today's electronic interconnects.

This dissertation is organized as per the following. Chapter 2 details the optical switching fabric architectures and their uses within OCM systems. Additionally, experimental results are presented to demonstrate the scalability of the switching fabric

and thus the OCM system. Chapter 3 presents the prototype of the world's first optically-connected memory module (OCMM), which was created based on analysis from Chapter 2 and serves as the remote OCM node within the subsequent detailed experiments. The optical-network-aware memory controller is described in Chapter 4, with experimental characterizations of its impact on memory bandwidth, latency, and energy. Resilient OCM architectures are discussed and experimentally characterized in Chapter 5. This demonstrates that the flexibility provided by optical interconnects provides not only improved bandwidth, latency, and energy performance but additional novel techniques to build resilient large-scale computers. In Chapter 6, the OCM system is demonstrated using silicon microring modulators in place of discrete LiNbO<sub>3</sub> modulators. This critical step characterizes for the first time not only the importance of integrated silicon photonics within processor-memory systems but also the impact of unpredictable memory data and traffic patterns on silicon photonic devices. Finally, Chapter 7 summarizes the contributions of this dissertation and describes ongoing and future work toward developing OCM for HPCs and data centers.

## Chapter 2

# Optical Interconnection Networks for OCM

This chapter details the optical network architecture utilized throughout this dissertation. Optical networks are the fundamental enabling technology for future, optically-connected HPCs and data centers. Here, the network functionalities and protocols are analyzed with regard to their impact on future computing and memory systems. Additionally, an experimental characterization is presented to demonstrate that such optical networks can scale to the sizes and bandwidths required for next-generation large-scale computers.

### 2.1 Optical Network Architecture

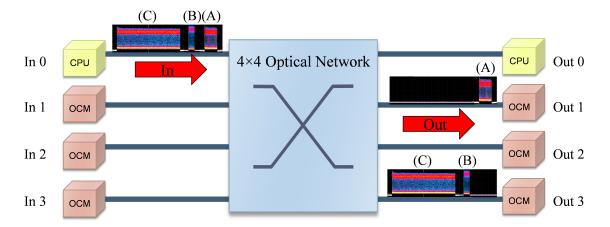

The optical networks utilized throughout this dissertation make use of one or more SOA-based optical switching nodes [65] to implement  $2\times2$  (Figure 2.1) or  $4\times4$  (Figure 2.2) switching fabric testbeds. The switching nodes are modular and may

be linked together to create larger, multi-stage networks. For example, four  $2\times2$  nodes have been configured to implement a  $4\times4$  as a 2-stage Banyan network topology. In this way, an optical network can be implemented with hundreds of thousands of nodes [66].

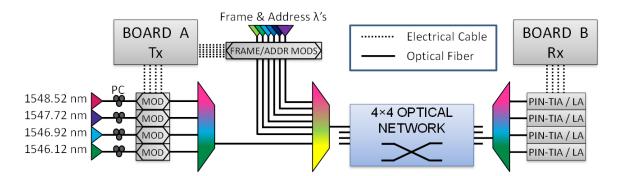

Figure 2.3 shows the wavelength-striped message format that enables messages to be transparently routed through each switching node. The use of wavelength-striping simplifies routing and minimizes switching latency: routing information is encoded on dedicated header wavelengths that are combined with the memory payload data using WDM. Each header wavelength remains constant, either logical 1 or 0, for the duration of each message. The minimum number of address headers required for an N×N network is  $\log_2(N)$ . Additional network functionalities, such as optical multicasting [67], can be added to the network by increasing the number of header wavelengths.

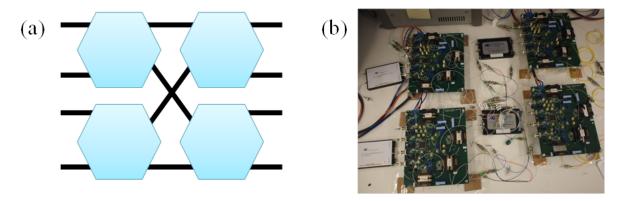

Figure 2.1:  $2 \times 2$  Photonic Switching Node - (a)Schematic and (b)photograph of the  $2 \times 2$  SOA-based photonic switching node.

All switching nodes utilize the same broadcast-and-select architecture: wavelength-striped messages enter at an input port where passive optical components (filters, couplers, fiber) direct the appropriate header wavelengths to low-speed (155-Mb/s)

Figure 2.2:  $4\times4$  Photonic Switching Node - (a)Schematic and (b)photograph of the  $4\times4$  SOA-based photonic switching node.

**Figure 2.3: Wavelength-Striped Message Format** - Low-speed header wavelengths (frame and address data) are combined with high-speed payload wavelengths using WDM.

photodetectors (PD). The electrical header data is then passed to simple, high-speed control logic that in turn gates SOA on or off. The SOAs act as broadband optical gates at each output port, and the gain provided restores power equivalent to any optical losses incurred through the switching node. The payload data, meanwhile, passes through a fiber delay line (FDL) to match the time required to filter, receive, and process the header information (approximately 10 ns). The FDL feeds the payload data into the SOAs, which are enabled just-in-time to allow transparent, low-latency routing. Each 2×2 switching node implements the control logic using a complex programmable logic device (CPLD), while the 4×4 switching nodes instead use a FPGA that allows for more diverse and advanced network functionalities.

### 2.1.1 Switching Protocols

The photonic switching nodes have been demonstrated to operate as packet switches [51], circuit switches [68], or hybrid packet and circuit switches [60]. Optical packet switching (OPS) is achieved by modulating the header wavelengths such that they are constant for the duration of each packet plus a small amount of guard time at the start and end of each packet. In this way, optical packets ranging from tens of nanoseconds up to milliseconds have been demonstrated with payload data ranging from a single 10-Gb/s wavelength channel up to eight 40-Gb/s WDM channels per packet [65]. The simple, distributed control logic within the switching fabric makes optical packet switching ideal for smaller messages or random traffic patterns. However, large numbers of larger messages may need to be broken down into multiple packets that may then overload the network or incur undesirable latency

Optical circuit switching (OCS) is ideal for larger, less random messages. Optical circuit paths, or light paths, can be created through the network through the use of a low-speed electrical control plane, such as over ethernet [4] links between the end-point nodes and the optical switching nodes. By opting for a single, up-front latency penalty to each transaction, a circuit switch eliminates the many, smaller latency penalties associated with packet-switched networks. Simulations of integrated, silicon photonic optical circuit-switched networks [53, 56] have shown the potential for significant power and performance benefits as compared to electrical packet- or circuit-switched networks. This is especially true for streaming applications, which exhibit predictable communication patterns involving large amounts of data.

OCM systems may exhibit unpredictable communication patterns involving small or large messages. It is therefore desirable to allow each end-node to analyze its own outgoing traffic and dynamically use either packet- or circuit-switching. The control logic for both previously described packet- and circuit-switching implementations can operate simultaneously within the photonic switching nodes, which requires only minimal additional control logic to arbitrate between conflicting packet and circuit traffic. Using this protocol, a memory controller can analyze the pattern of memory access requests from a processor to transmit each request (or aggregated group of requests) as packets or circuits [69].

### 2.2 Implications for Memory Architectures

The latency characteristics of an optical interconnect approach to main memory is a crucial issue to address. Current SDRAM access times are much slower than high-

performance processors, thus any additional latency is undesirable. The transparency of the photonic switching nodes reduces the overall latency to the time-of-flight between a processor and OCMMs. Each additional meter of single-mode fiber (SMF) adds approximately 5 ns [54] of latency to the memory communication path. Though this may be negligible within a single rack, it could become problematic for links spanning a large-scale computing system. One goal of this OCM design is to minimize accesses to memory nodes that are more than a few meters away (similar to the case of today's electronic networks). The main advantage of the OCM system is its sole limitation in distance with regard to time-of-flight latency, whereas electronic systems are limited in distance with regard to latency, power, and bandwidth. Parallel programming models such as PGAS [70] expect a global memory address space but already exploit locality to maximize references to a local memory. In this dissertation, local memory is the memory with the shortest optical path.

The OIN described here enables the bandwidth and latency performance of the OCM system to meet the demands of heavily loaded data centers that exceed hundreds of thousands of nodes [65, 66]. Meanwhile, high-speed transceivers operating at high per-channel data rates can leverage the available optical bandwidth, as demonstrated by the 10-Gb/s and 25-Gb/s channels in the recent 40- and 100-gigabit Ethernet standards [4]. Using multiple high-speed transceivers with WDM creates the bandwidth density necessary for OCM nodes with memory bandwidth in the 100's of gigabits per second. Many OCM nodes could be further combined using an optical interconnection network for petabit system bandwidths.

The reconfigurability of the proposed OCM system supports the diverse applications

that data centers and HPCs may run. For example, a streaming application [71] typically has a predictable traffic pattern with long, sustained memory accesses. The system can be configured to allocate OCM nodes to the appropriate processing nodes before run time, or between memory access stages, which will eliminate the latency associated with circuit-switched lightpath setup. Additionally, a web search application with unpredictable communication can leverage a hybrid packet- and circuit-switched OCM system to optimize communication on a message-by-message basis.

The network nodes can be configured to support wavelength-striped payload multicasting to enable access to multiple OCM nodes simultaneously [72]. A processor node can store data at multiple OCM nodes simultaneously with a single memory access, thereby distributing data locally to other processing nodes for distributed computing. Alternatively, the multicast-capable OCM ssytem can be configured for resilience to tolerate the failure of an entire OCMM while still maintaining error-free performance [69]. The use of multicasting can also be used to transmit along several redundant paths to the same destination node.

Reducing the power consumption of the memory system can have significant impact on overall data center and HPC designs, and huge power savings can be achieved by incorporating integrated photonic components [47] in future OCM nodes by gaining benefits from the tighter integration of optical components with electronic driver and receiver circuitry [56, 58, 59]. Silicon photonics will eliminate the need for any off-chip wiring, such as between an SDRAM chip and a transceiver, improving the overall bandwidth, latency, and energy efficiency. By modulating and receiving the optical memory transactions within the memory and processor chips, each memory link can

operate at 1 pJ/bit energy efficiency [39, 40]. Continued development of silicon photonic technology is likely to improve this further. Meanwhile, with the growing use of high data rate serial links in HPCs and data centers today, the SerDes power consumption will continue to decrease [73] to reduce the cost of the electrical drivers for the optical transceivers.

### 2.3 Scalability

Adopting high data rates and advanced modulation formats in optical interconnection networks will enable future computing systems to achieve greater performance and scalability. Traditionally, the simplicity of non-return-to-zero on-off keying (NRZ-OOK) has made it a popular modulation format for optical communication links. However, phase-shift keying (PSK), specifically differential-binary-phase-shift-keying (DBPSK or DPSK), has long been known as a potential method for improving resilience to nonlinearities, with a 3-dB improved receiver sensitivity (with balanced detection) as compared to OOK. Such benefits of advanced modulation formats are becoming more significant as data rates now exceed 10 Gb/s and even 40 Gb/s, and the optical network elements are beginning to exceed the abilities of the driver and receiver electronic circuitry. Current microprocessors already dissipate up to half of their energy in the interconnect alone [5], and scaling up per-channel data rates without optimizing overall communication efficiency would result in an undesirable increase in energy dissipation. Therefore, next-generation computer systems may require optical interconnection networks that utilize not only high per-channel data rates, but also advanced modulation formats with improved resilience and spectral efficiency [74].

This section presents an experiment that demonstrates the scalability of the photonic switching nodes utilized throughout this dissertation through ability to transparently route data modulated at 10 Gb/s to 40 Gb/s, modulated as OOK or DPSK, with negligible impact on power penalties.

### 2.3.1 OOK Characterization

The first step in demonstrating the OIN scalability is to determine the performance impact, in terms of power penalty, of increasing per-channel data rates from 10 Gb/s to 40 Gb/s while maintaining OOK modulation. To accomplish this, four 2×2 photonic switching nodes are configured as a 2-stage 4×4 optical network test-bed (Figure 2.4). Payload data consists of 8 separate wavelengths combined intro a single WDM optical packet. Each 64-ns optical packet is created using eight distributed feedback (DFB) lasers, which are passively combined and modulated with OOK data by a LiNbO<sub>3</sub> modulator. The 10-Gb/s OOK data is generated by a pulse pattern generator (PPG), using a 2<sup>15</sup>-1 pseudo-random bit sequence (PRBS), and a 10-Gb/s LiNbO<sub>3</sub> modulator. Separately, the 40-Gb/s OOK data is generated by using an identical PPG, using 2<sup>15</sup>-1 PRBS, and an electrical multiplexer to create 40-Gb/s PRBS. Each optical packet is combined with three, independently-generated network control signals, creating wavelength-striped optical packets that pass transparently through the optical test-bed.

Error-free transmission of all optical packets is experimentally measured at the output of the network using a bit-error-rate tester (BERT), with bit-error rates (BERs) less than 10<sup>12</sup>, for all eight payload wavelengths using 10-Gb/s and 40-Gb/s

Figure 2.4: 2-Stage  $4\times4$  Network Test Bed - (a)Block diagram of  $4\times4$  optical network (b)photograph of implemented optical interconnection network.

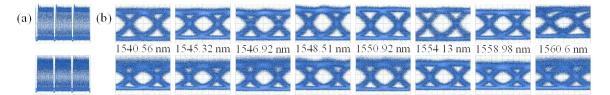

OOK modulation. Figure 2.5a shows the optical packets at the input and output of the network. Figure 2.5b shows the optical eye diagrams for the 40-Gb/s payload wavelengths.

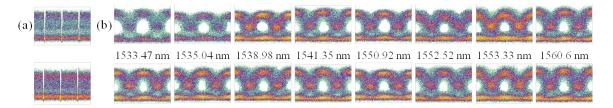

Figure 2.5: Scalability Characterization: 40-Gb/s OOK Optical Eye Diagrams - Optical eyes at the input (top) and output (bottom) of the optical network showing (a) packets; (b) each 40-Gb/s OOK payload wavelength (5 ps/div.

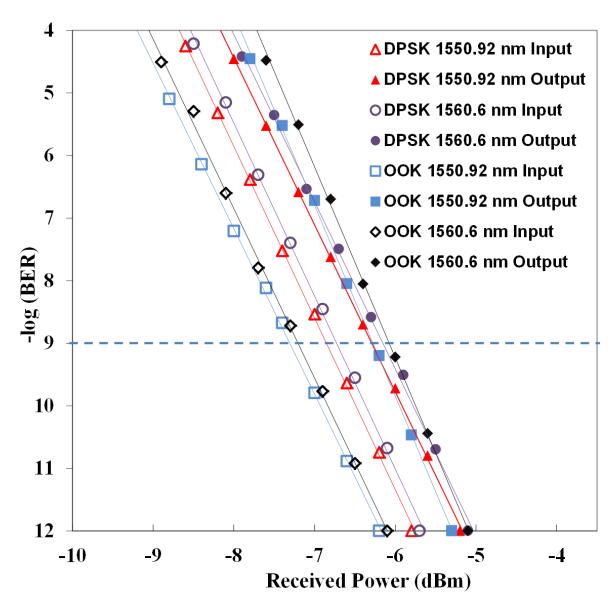

The sensitivity curves shown in Figure 2.6 demonstrate a power penalty of 1 dB for the best-case payload wavelength of 1550.92 nm (0.5 dB per SOA hop) and 1.1 dB for the worst-case payload wavelength of 1560.6 nm (0.55 dB per SOA hop). The small variation in power penalties is likely due to the slight gain curve of the erbium-doped fiber amplifier (EDFA) used in BER testing. In comparison, 10-Gb/s data typically has a power penalty of 0.45 dB per SOA hop [75]. These values are similar, however the

slight increase in power penalty for 40-Gb/s data could become a design consideration for future networks as network sizes and per-channel data rates continue to increase.

### 2.3.2 DPSK Characterization

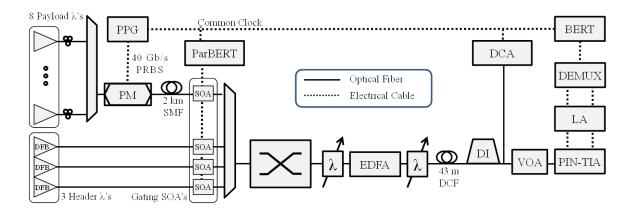

The next step in the scalability study is to demonstrate network transparency with regard to modulation formats by comparing amplitude modulation (OOK) to phase modulation (DPSK). With that aim, optical packets with 8×40-Gb/s DPSK data are then generated and transmitted through the test-bed. This second experimental setup (Figure 2.7) consists of the above transparent, 2-stage 4×4 optical test-bed, again correctly routing 64-ns wavelength-striped optical packets. A 40-Gb/s PPG drives a single 40-Gb/s phase modulator to encode 2<sup>15</sup> – 1 PRBS DPSK data onto eight payload wavelength channels, each with an average power of -14 dBm at the network input and with wavelengths ranging from 1533.47 nm to 1560.6 nm. Immediately after modulation, and before entering the network, the WDM data passes through a 2-km span of single mode fiber for decorrelation. The three separate header wavelengths (frame, address0, address1) are modulated at the packet rate using three external SOAs, which are controlled by an Agilent ParBERT.

In the experiment, the combined eight payload wavelengths are gated using a single SOA, controlled by the ParBERT, to create 64-ns optical packets. The resulting configuration is such that each optical packet consists of 8×40-Gb/s DPSK wavelength channels and 3 low-speed header wavelength channels. As before, all eleven wavelengths traverse the optical interconnection network concurrently as a single wavelength-striped packet. The amplification provided by the SOA-based switching nodes within the

Figure 2.6: Sensitivity curves for 40-Gb/s OOK and DPSK Scalability Characterization - BER curves for best case (1550.92 nm) and worst case (1560.6 nm) 40-Gb/s OOK and DPSK payload wavelengths. Input measurements are shown with open points, while output measurements are depicted with filled points. The power penalty spread from best- to worst-case is 0.1 dB for OOK and >0.1 dB for DPSK at  $10^{-9}$  BER.

Figure 2.7: Scalability Characterization: Experimental Setup for DPSK Traffic - Experimental setup for 40-Gb/s, 8-channel DPSK network characterization.

optical test-bed maintains this average power during propagation through the network and to the network output.

At the output, the eight payload wavelengths are sent to a tunable filter to select a single 40-Gb/s DPSK signal, which is amplified using an EDFA and filtered again. The single wavelength is then sent to the constructive port of a delay-line interferometer (DLI), a variable optical attenuator (VOA), and a 40-Gb/s photodiode with transimpedance (TIA) and limiting amplifiers (LA). This received electrical data is time-demultiplexed and verified using a BERT, which is gated for packetized data by the ParBERT. The 40-Gb/s optical signals are simultaneously inspected using a digital communications analyzer (DCA).

Error-free operation is confirmed for all eight 40-Gb/s DPSK payload wavelengths with BERs less than  $10^{-12}$  at the output of the optical network test-bed. The optical packets at the input and output are shown in Figure 2.8a, and Figure 2.8b shows the input and output 40-Gb/s optical eye diagrams for all 8 payload wavelengths at the

output of the constructive port of the DI. A best-case power penalty of 0.52 dB was measured at a BER of  $10^{-9}$  (Figure 2.6) for the 2-stage network at 1550.92 nm. The worst-case power penalty of 0.56 dB was measured at 1560.6 nm. This demonstrates an average power penalty of 0.26 dB per SOA switch hop when transmitting 40-Gb/s DPSK data at 1550.92 nm, and a power penalty spread >0.1 dB for all eight wavelengths ranging from 1533.47 nm to 1560.6 nm.

Figure 2.8: Scalability Characterization: 40-Gb/s DPSK Optical Eye Diagrams - Optical eyes at the input (top) and output (bottom) of the optical network showing (a) packets; (b) each 40-Gb/s DPSK payload wavelength (5 ps/div).

### 2.4 Discussion

Optical interconnection networks are critical components of future optically-connected memory systems that allow high-performance, energy-efficient integrated optical links to leverage low-latency, transparent routing through the large-scale networks required for next-generation HPCs and data centers. This, in turn, enables the deployment of OCM systems with the necessary memory capacity and bandwidth to close the memory-processor performance gap.

The optical network test bed described above is experimentally demonstrated as a data rate- and modulation format-transparent, multi-terabit optical interconnection

network [76]. The comparable power penalty for 40-Gb/s DPSK data (0.26 dB per SOA switch) versus 40-Gb/s OOK (0.5 dB per SOA switch) shows that this network can continue to operate in future HPCs in data centers regardless of the modulation type required for improved spectral efficiency and overall network scalability. In this way, low-latency optical networks can be deployed between processors and main memory to enable high-bandwidth memory access with ultra low-latencies. For this reason, the remainder of this dissertation makes use of the above optical network test bed for all experiments.

### Chapter 3

# Optically-Connected Memory Modules

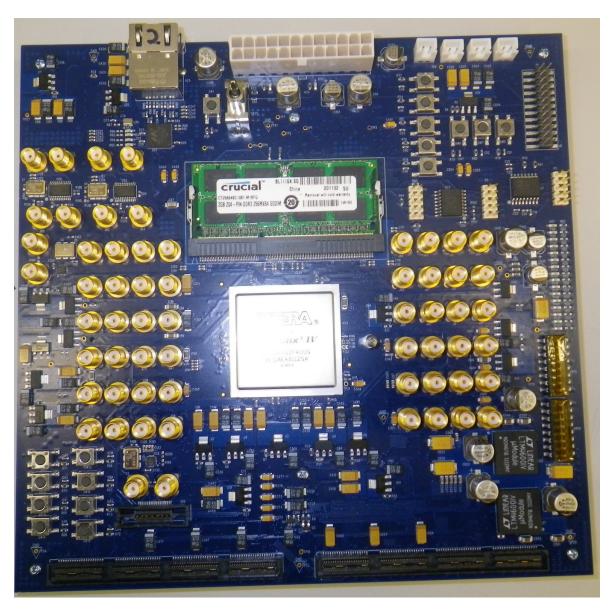

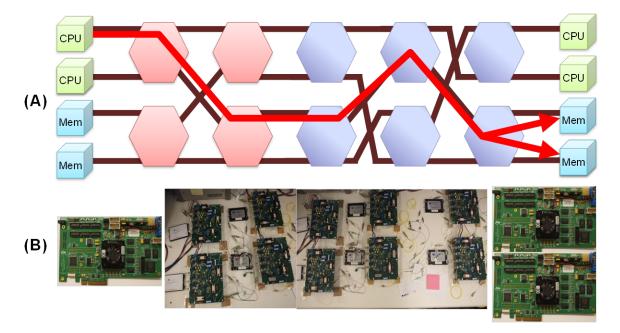

In this chapter, the first prototype high-performance OCMM (Figure 3.1) is presented, which enables the implementation and characterization of diverse OCM architectures. The main advantage of using this OCMM is the close integration of DDR3 SDRAM with high-speed serial transceivers by means of a high-performance FPGA. The FPGA provides inexpensive, flexible, and fast prototyping functionalities that are not possible using application-specific integrated circuits (ASICs) or off-the-shelf processors. This, in turn, creates a low-latency interface between the electrical domain within the physical memory devices and the optical domain within the network.

The OCMMs may be located physically distant from the associated processors, leveraging the distance-immunity (at computer-scales) of single-mode optical fibers [54]. Relocating the memory devices to be physically distant from the processor frees up board space near the processor itself without significant impact on system performance [55]. This will give system designers more flexibility in designing board

Figure 3.1: Photograph of OCMM - Photograph of the first OCMM prototype.

layouts: remaining board components, such as on-board routers or caches, can be placed closer to the processor or increased in number. Additionally, more processors can be added in the space formerly occupied by DIMMs and the associated wiring, or, rather than increasing density, the packaging can be made less costly and more easily cooled.

### 3.1 Lessons from Preliminary Work

The OCMM design draws upon preliminary work on OCM [68, 72, 77, 78] and seeks to optimize all necessary functionalities required for high-performance operation of optical-network-accessed memory. Throughout these earlier experiments, the overall memory performance was severely limited by the use of an off-the-shelf FPGA board that operated at relatively slow speeds. Additionally, the on-board SDRAM was a fixed component on the board and therefore it was not possible to explore different memory types, sizes, or speeds.

### 3.1.1 Memory Interface Latency