# Architectures and Design Automation for Photonic Networks On Chip

Gilbert R. Hendry

Submitted in partial fulfillment of the requirements for the degree of *Doctor of Philosophy* in the Graduate School of Arts and Sciences

Columbia University

2011

© 2011 Gilbert Hendry All rights reserved.

#### Abstract

#### Architectures and Design Automation for Photonic Networks-on-Chip Gilbert R. Hendry

Chip-scale photonics has emerged as an exciting field which can potentially solve many of the problems plaguing the high-performance computing industry, from large-scale to embedded. In theory, photonics is a superior communication medium because of its higher bandwidth density using wave-division multiplexing and bandwidth-power translucency to distance traveled. In practice, physical-layer design and engineering issues such as optical loss, crosstalk, and packaging have slowed its entry into widespread adoption at the chip and board scale. In this work, we present these issues and potential design improvements. The major contributions, however, are the tools and methods we have developed for the design of photonic interconnection networks, including a system-level simulator and CAD and modeling environment for layout, both of which are publicly available to the research community.

### Contents

| Li | List of Figures v |          |                                          |    |  |  |

|----|-------------------|----------|------------------------------------------|----|--|--|

| Li | ist of Tables x   |          |                                          |    |  |  |

| 1  | Intr              | oductio  | 1                                        | 1  |  |  |

|    | 1.1               | The M    | emory Wall                               | 2  |  |  |

|    | 1.2               | Exasca   | le Computing                             | 4  |  |  |

|    | 1.3               | The R    | ble of Photonics                         | 5  |  |  |

| 2  | Silic             | on Pho   | onics                                    | 7  |  |  |

|    | 2.1               | WDM      | Photonic Link                            | 7  |  |  |

|    | 2.2               | Simple   | Structures                               | 9  |  |  |

|    |                   | 2.2.1    | Waveguides                               | 9  |  |  |

|    |                   | 2.2.2    | Waveguide Taper                          | 11 |  |  |

|    |                   | 2.2.3    | Photo-Detector                           | 11 |  |  |

|    |                   | 2.2.4    | Mach-Zehnder Interferometer              | 12 |  |  |

|    | 2.3               | Ring-t   | ased Structures                          | 12 |  |  |

|    |                   | 2.3.1    | Ring Modulator                           | 13 |  |  |

|    |                   | 2.3.2    | Ring Filter                              | 15 |  |  |

|    |                   | 2.3.3    | Ring Switch                              | 15 |  |  |

|    |                   | 2.3.4    | Ring Detector                            | 16 |  |  |

| 3  | Pho               | tonic In | terconnection Network Architectures      | 18 |  |  |

|    | 3.1               | Netwo    | rk Architecture Overview                 | 18 |  |  |

|    | 3.2               | Circuit  | -Switched Architectures                  | 20 |  |  |

|    |                   | 3.2.1    | Path-Setup Protocol                      | 21 |  |  |

|    |                   | 3.2.2    | Photonic Circuit-Switched Network Design | 24 |  |  |

|    |                   |          | 3.2.2.1 Switch Design                    | 24 |  |  |

|    |                   |          | 3.2.2.2 Optical Power Budget             | 26 |  |  |

|     |                                                               | 3.2.2.3     | Data Integrity and Crosstalk                                                                 | 1 |  |  |  |

|-----|---------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------|---|--|--|--|

|     |                                                               | 3.2.2.4     | Modulator and Detector Banks                                                                 | 1 |  |  |  |

|     |                                                               | 3.2.2.5     | Mesh Topology                                                                                | 7 |  |  |  |

|     | 3.2.3                                                         | Design C    | Considerations and Improvements $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 46$ | 5 |  |  |  |

|     |                                                               | 3.2.3.1     | Gateway Concentration                                                                        | 5 |  |  |  |

|     |                                                               | 3.2.3.2     | Selective Transmission                                                                       | 3 |  |  |  |

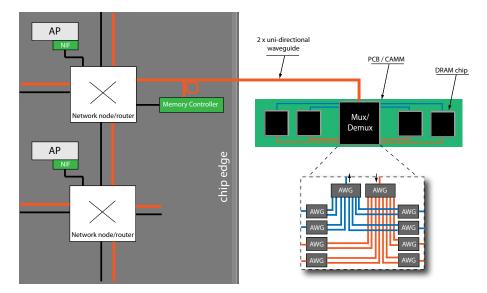

|     | 3.2.4                                                         | Off-chip    | Memory Access                                                                                | 2 |  |  |  |

|     | 3.2.5                                                         | Time Div    | vision Multiplexed Arbitration                                                               | 5 |  |  |  |

|     |                                                               | 3.2.5.1     | Fully-Connected                                                                              | 5 |  |  |  |

|     |                                                               | 3.2.5.2     | Enhanced TDM                                                                                 | 1 |  |  |  |

|     | 3.2.6                                                         | Impact o    | f Deposited Multi-layer Devices                                                              | ) |  |  |  |

|     |                                                               | 3.2.6.1     | Multi-layer Mesh                                                                             | ) |  |  |  |

|     |                                                               | 3.2.6.2     | Matrix-Crossbar                                                                              | ) |  |  |  |

| 3.3 | Wavele                                                        | ength-Arbi  | ited Architectues                                                                            | 2 |  |  |  |

|     | 3.3.1                                                         | Wavelen     | gth Bus Structures                                                                           | 3 |  |  |  |

|     |                                                               | 3.3.1.1     | Source-Routed Bus                                                                            | 3 |  |  |  |

|     |                                                               | 3.3.1.2     | Destination-Routed Bus                                                                       | 1 |  |  |  |

|     |                                                               | 3.3.1.3     | Multi-Write Single-Read                                                                      | 5 |  |  |  |

|     |                                                               | 3.3.1.4     | Single-Write Multi-Read                                                                      | 5 |  |  |  |

|     |                                                               | 3.3.1.5     | Wavelength Crossbar                                                                          | 7 |  |  |  |

|     |                                                               | 3.3.1.6     | Token-Ring                                                                                   | 7 |  |  |  |

|     | 3.3.2                                                         | Analysis    | of Wavelength-Arbited Architectures                                                          | 3 |  |  |  |

|     |                                                               | 3.3.2.1     | Corona                                                                                       | 3 |  |  |  |

|     |                                                               | 3.3.2.2     | Firefly                                                                                      | ) |  |  |  |

|     | 3.3.3                                                         | Impact o    | f Deposited Multi-Layer Devices                                                              | 2 |  |  |  |

|     |                                                               | 3.3.3.1     | Multi-layer Corona                                                                           | 2 |  |  |  |

|     |                                                               | 3.3.3.2     | Multi-layer Firefly                                                                          | 2 |  |  |  |

| 3.4 | Summ                                                          | ary         |                                                                                              | 3 |  |  |  |

| Con | Computer-Aided-Design of Photonic Interconnection Networks 85 |             |                                                                                              |   |  |  |  |

| 4.1 | Simula                                                        | ation and A | Analytical Optimization                                                                      | 5 |  |  |  |

|     | 4.1.1                                                         | PhoenixS    | Sim                                                                                          | 5 |  |  |  |

|     |                                                               | 4.1.1.1     | The Big Picture                                                                              | 5 |  |  |  |

|     |                                                               | 4.1.1.2     | Processing Plane                                                                             | 7 |  |  |  |

|     |                                                               | 4.1.1.3     | Network Plane                                                                                | ) |  |  |  |

|     |                                                               | 4.1.1.4     | RouterCrossbar                                                                               | 1 |  |  |  |

4

|   | 5.2  | Opport         | tunities and       | d Challenges for Photonics                                       |

|---|------|----------------|--------------------|------------------------------------------------------------------|

|   | 5.1  | Summa          | ary and Co         | onclusions                                                       |

| 5 | Fina | l Thoug        | ghts               | 131                                                              |

|   |      |                | 4.3.5.3            | Results                                                          |

|   |      |                | 4.3.5.2            | Power Estimation                                                 |

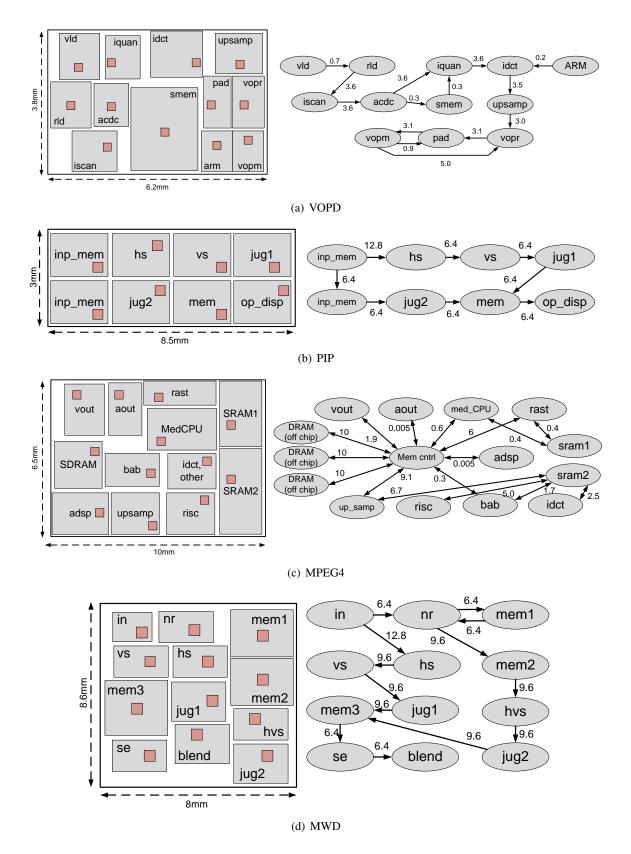

|   |      |                | 4.3.5.1            | Video Processing Benchmarks                                      |

|   |      | 4.3.5          |                    | dy: Video Processing                                             |

|   |      |                | 4.3.4.3            | Post Processing: Gateway Reordering                              |

|   |      |                | 4.3.4.2            | Optimization: WDM Link Combination                               |

|   |      |                | 4.3.4.1            | Basic Link Synthesis                                             |

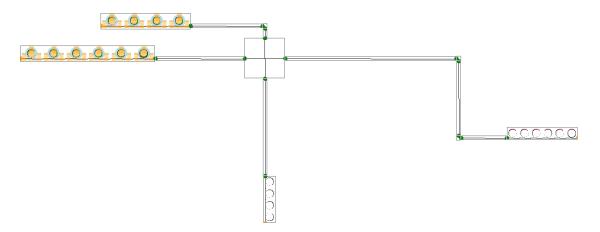

|   |      | 4.3.4          |                    | Synthesis Methods                                                |

|   |      | 4.3.3          |                    | dy: Link Instantiation                                           |

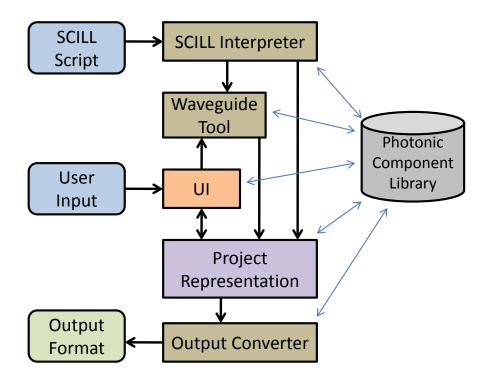

|   |      | 4.3.2          | SCILL: A           | A Layout Scripting Language                                      |

|   |      |                | 4.3.1.7            | Layout Output                                                    |

|   |      |                | 4.3.1.6            | Waveguide Tool                                                   |

|   |      |                | 4.3.1.5            | Device Placement                                                 |

|   |      |                | 4.3.1.4            | Photonic Component Library                                       |

|   |      |                | 4.3.1.3            | Layers                                                           |

|   |      |                | 4.3.1.2            | Device Modeling                                                  |

|   |      |                | 4.3.1.1            | Device Parameterization                                          |

|   |      | 4.3.1          | VANDA              | L: A Photonic CAD Tool                                           |

|   | 4.3  | Layout         | t and Synth        | nesis                                                            |

|   |      |                | 4.2.2.2            | Firefly Insertion Loss                                           |

|   |      |                | 4.2.2.1            | Corona Insertion Loss                                            |

|   |      | 4.2.2          |                    | Loss Optimization of Wavelength-Routed Network Architectures 109 |

|   |      |                | 4.2.1.2            | Matrix Crossbar Optimization Example                             |

|   |      | T, <b>2</b> ,1 | 4.2.1.1            | P-Mesh Optimization Example                                      |

|   |      | 4.2.1          |                    | Loss Optimization of Broadband Network Architectures             |

|   | 4.2  | Addres         | 4.2.0.1            | Statistics and Results                                           |

|   | 4.2  |                |                    | _KL                                                              |

|   |      | 4.1.2          |                    | IO Plane       96         _RL       97                           |

|   |      |                | 4.1.1.7<br>4.1.1.8 | Hybrid Router   95                                               |

|   |      |                | 4.1.1.6            | Photonic Devices                                                 |

|   |      |                | 4.1.1.5            | RouterArbiter                                                    |

|   |      |                | 4115               |                                                                  |

#### References

| A | Run         | ning Siı | mulations with PhoenixSim                             | 139 |

|---|-------------|----------|-------------------------------------------------------|-----|

|   | A.1         | Insertio | on Loss Analysis                                      | 139 |

|   |             | A.1.1    | Example from Section 3.2.2.5                          | 140 |

|   | A.2         | Perform  | mance Characterizations                               | 141 |

|   |             | A.2.1    | Example from Section 3.2.2.5 - Photonic Mesh          | 141 |

|   |             |          | A.2.1.1 Latency, Bandwidth, and Power                 | 141 |

|   |             |          | A.2.1.2 Crosstalk                                     | 142 |

|   |             | A.2.2    | Example from Section 3.2.3.1 - Concentration          | 142 |

|   |             | A.2.3    | Example from Section 3.2.3.2 - Selective Transmission | 142 |

|   |             | A.2.4    | Example from Section 3.2.4 - Memory                   | 142 |

|   |             | A.2.5    | TDM                                                   | 143 |

| B | Desi        | gn Auto  | omation with VANDAL                                   | 144 |

|   | <b>B</b> .1 | Using    | VANDAL                                                | 144 |

|   |             |          | B.1.0.1 Case Study from Section 4.3.3                 | 144 |

|   |             |          | B.1.0.2 Synthesis Methods from Section 4.3.4          | 147 |

|   |             |          |                                                       |     |

135

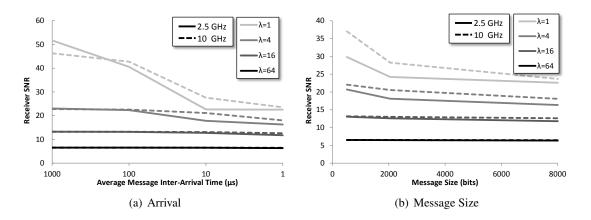

## **List of Figures**

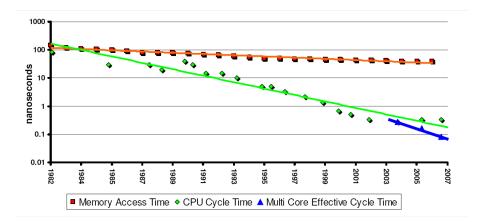

| 1.1  | Divergence of CPU power from memory access time, from Exascale report (1) 2                                                 |  |

|------|-----------------------------------------------------------------------------------------------------------------------------|--|

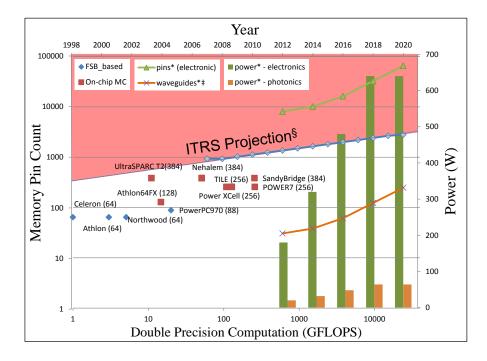

| 1.2  | Pin counts and power for today's microprocessors and projected into the near future 3                                       |  |

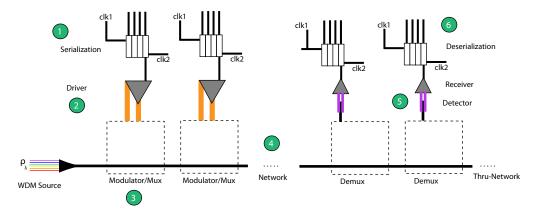

| 2.1  | Basic form of a WDM link                                                                                                    |  |

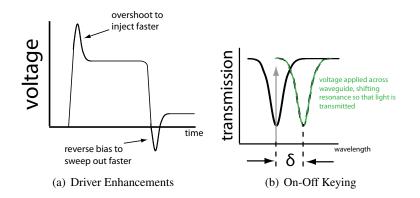

| 2.2  | Modulation operation                                                                                                        |  |

| 2.3  | Simple view of waveguides                                                                                                   |  |

| 2.4  | Waveguide taper for mode expansion                                                                                          |  |

| 2.5  | Germanium MSM photo-detector                                                                                                |  |

| 2.6  | Mach-Zehnder interferometer                                                                                                 |  |

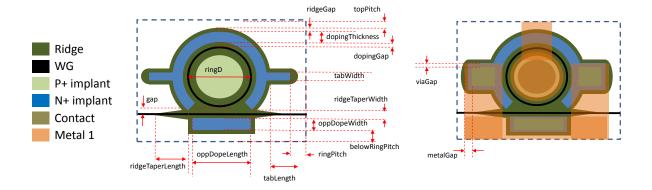

| 2.7  | Geometry of a ring modulator                                                                                                |  |

| 2.8  | Single-wavelength filter                                                                                                    |  |

| 2.9  | Optical ring resonators can be used as switching devices within an on-chip photonic                                         |  |

|      | network                                                                                                                     |  |

| 2.10 | Poly ring photo-detector                                                                                                    |  |

| 3.1  | The process of store-and-forward packet networks                                                                            |  |

| 3.2  | Anatomy of an electronic store-and-forward packet router                                                                    |  |

| 3.3  | Anatomy of a circuit router                                                                                                 |  |

| 3.4  | Path setup protocol                                                                                                         |  |

| 3.5  | Designing a $4 \times 4$ switch. (a) just the crossing waveguides. (b) adding broadband rings                               |  |

|      | to implement paths                                                                                                          |  |

| 3.6  | Various $4 \times 4$ non-blocking switch designs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 27$ |  |

| 3.7  | Higher radix switch designs                                                                                                 |  |

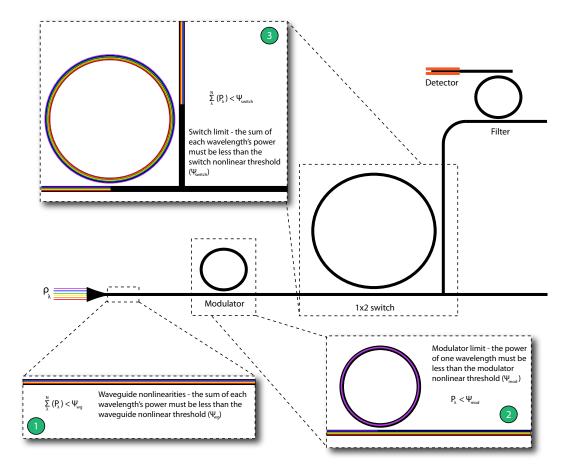

| 3.8  | Points in a photonic link where nonlinear effects can be generated. (1) in a waveguide                                      |  |

|      | (2) in a modulator (3) in a switch                                                                                          |  |

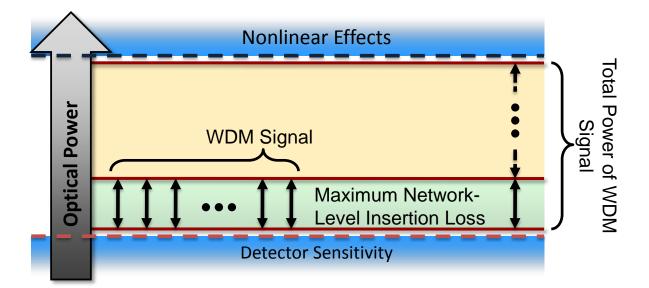

| 3.9  | Insertion loss vs. bandwidth tradeoff                                                                                       |  |

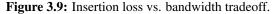

| 3.10 | Sources of noise and crosstalk within a chip-scale photonic system                                                          |  |

| 3.11 | Modulator bank and response issues.                                                         | 35 |

|------|---------------------------------------------------------------------------------------------|----|

| 3.12 | Detector bank, showing (R1) first filter response with (A) filter leakage and (B) crosstalk |    |

|      | and (R2) the response of the next filter                                                    | 36 |

| 3.13 | 4x4 Mesh topology, showing 5-port photonic switch and NIF block diagram                     | 39 |

| 3.14 | Control flowchart for a circuit-switched NIF.                                               | 40 |

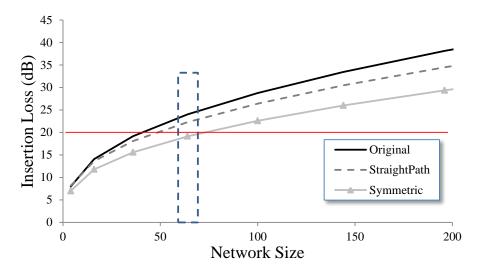

| 3.15 | Worst case network insertion loss measured in simulation using PhoenixSim for a pho-        |    |

|      | tonic mesh, using the three different kinds of $4 \times 4$ switches from Figure 3.6        | 40 |

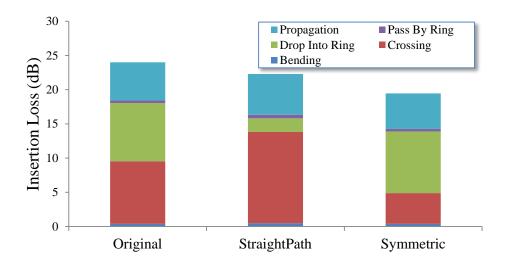

| 3.16 | Insertion loss breakdown of $8 \times 8$ P-mesh for different switch designs                | 41 |

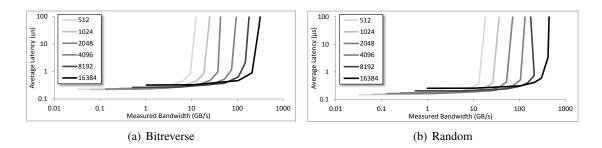

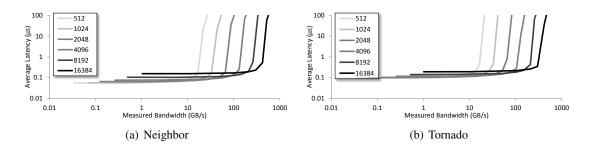

| 3.17 | Average latency versus measured bandwidth for P-Mesh running (a) Bitreverse and (b)         |    |

|      | Random synthetic traffic patterns for different message sizes, in bits                      | 42 |

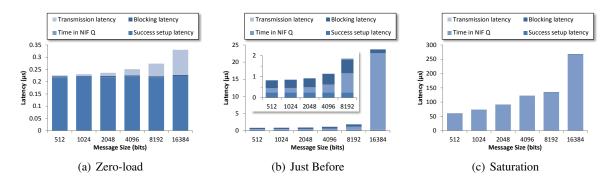

| 3.18 | Latency breakdown for Bitreverse pattern at (a) zero load, (b) just before saturation, and  |    |

|      | (c) saturation                                                                              | 42 |

| 3.19 | Average latency versus measured bandwidth for P-Mesh running (a) Neighbor and (b)           |    |

|      | Tornado synthetic traffic patterns for different message sizes, in bits                     | 43 |

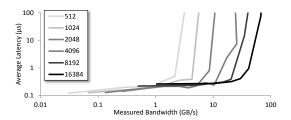

| 3.20 | Average latency versus measured bandwidth for P-Mesh running Hotspot                        | 44 |

| 3.21 | Power dissipation in P-Mesh running Random traffic showing (a) total power for various      |    |

|      | loads and (b) power breakdown at saturation.                                                | 44 |

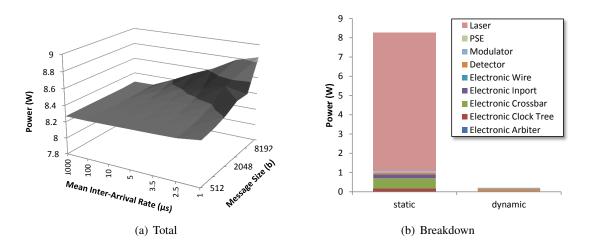

| 3.22 | Measured SNR (a) against message arrival rate for 8192b messages and (b) against mes-       |    |

|      | sage size for $1\mu s$ arrival                                                              | 45 |

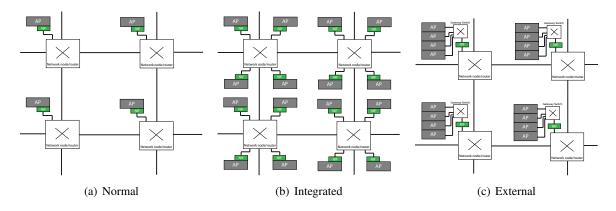

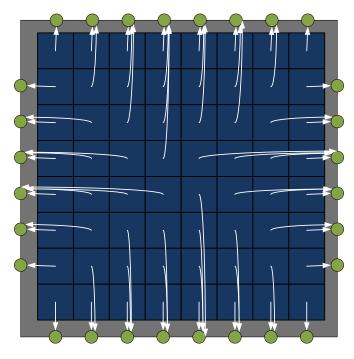

| 3.23 | Network access point (AP) concentration on a mesh, (a) normal, unconcentrated (b)           |    |

|      | integrated 4-way concentration, and (c) external 4-way concentration.                       | 47 |

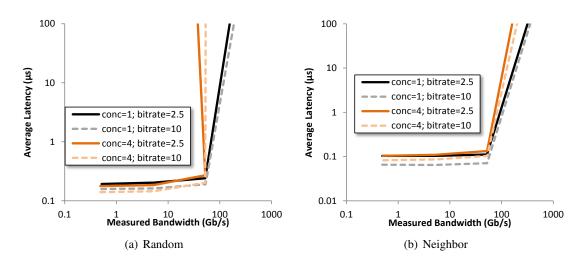

| 3.24 | Performance for (a) Random and (b) Neighbor for normal and 4-way external concen-           |    |

|      | tration, with 2.5 and 10 Gb/s modulation.                                                   | 48 |

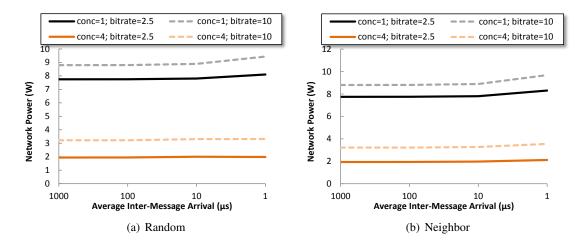

| 3.25 | Power for (a) Random and (b) Neighbor for normal and 4-way external concentration,          |    |

|      | with 2.5 and 10 Gb/s modulation.                                                            | 49 |

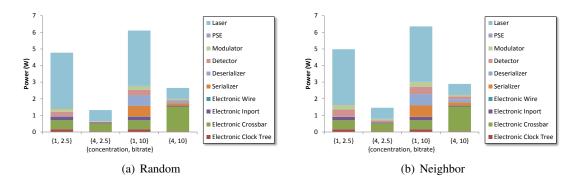

| 3.26 | Power breakdown for (a) Random and (b) Neighbor for normal and 4-way external con-          |    |

|      | centration, with 2.5 and 10 Gb/s modulation                                                 | 49 |

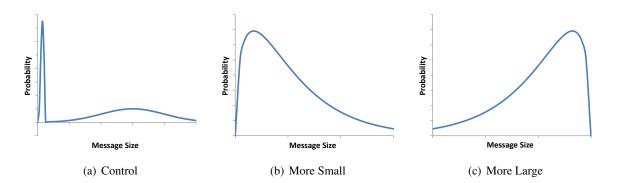

| 3.27 | Potential probability distribution of message sizes for an application                      | 51 |

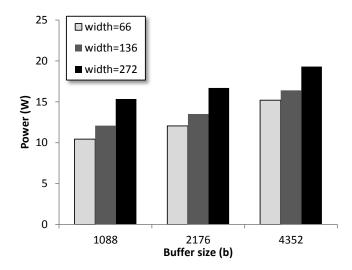

| 3.28 | Power for different buffer sizes and channel widths                                         | 52 |

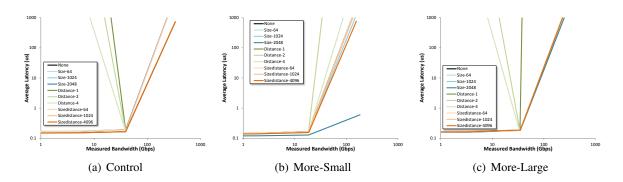

| 3.29 | Confusing graphs depicting latency and bandwidth characteristics for control-type mes-      |    |

|      | sage sizes with random destinations.                                                        | 52 |

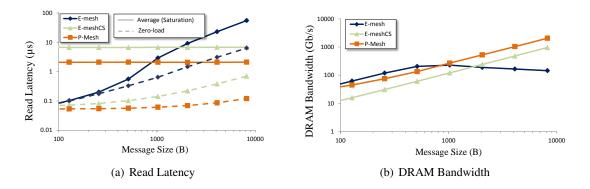

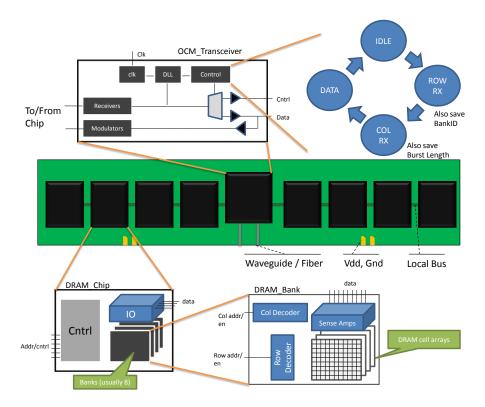

| 3.30 | Anatomy of a circuit-switched memory link                                                   | 53 |

| 3.31 | Control flowchart of circuit-switched memory controller, interacting with electronic con-   |    |

|      | trol network                                                                                | 54 |

| 3.32 | Characteristics of DRAM subsystem for packet-switched E-Mesh, circuit-switched E-         |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | Mesh, and photonic circuit-switched P-Mesh.                                               | 54 |

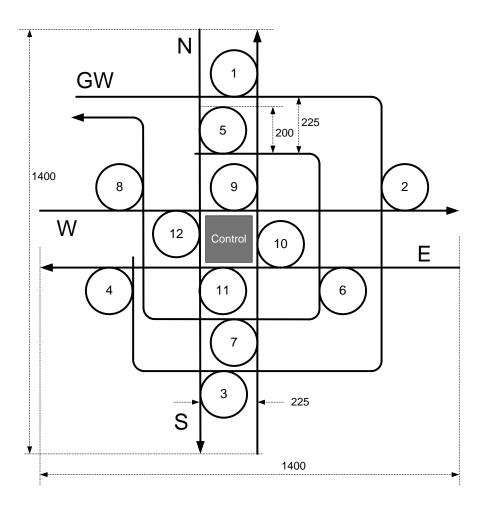

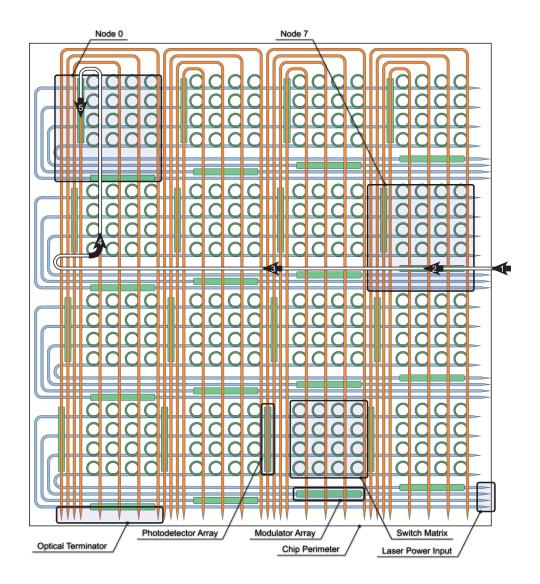

| 3.33 | Layout of TDM photonic switch, showing waveguides and ring resonators                     | 58 |

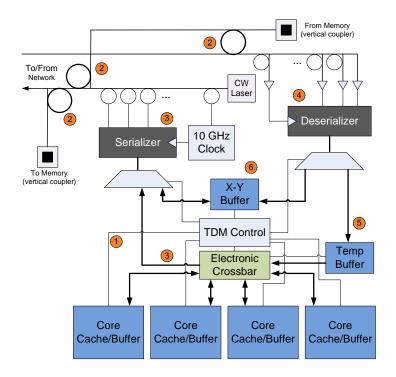

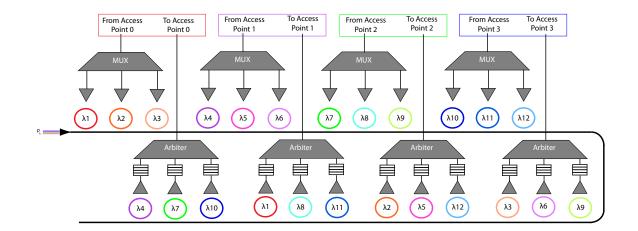

| 3.34 | TDM network gateway microarchitecture.                                                    | 60 |

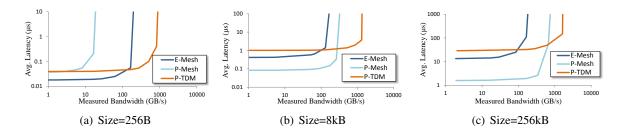

| 3.35 | Latency and bandwidth characteristics for a full-coverage 4×4 TDM network concen-         |    |

|      | trated to 64 access points for (a) 256B messages (b) $8kB$ messages (c) 256kB messages    | 61 |

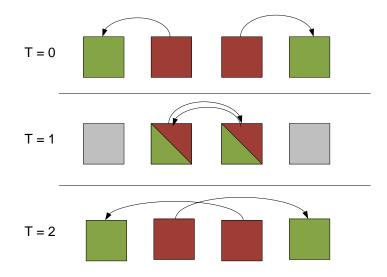

| 3.36 | Row communication TDM slots example for four nodes.                                       | 62 |

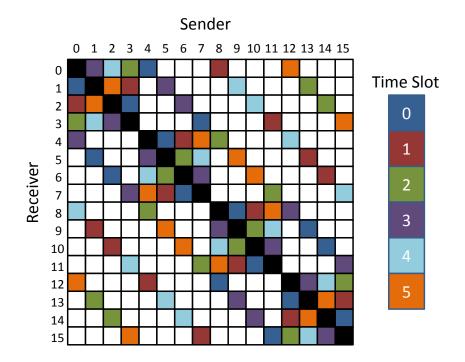

| 3.37 | E-TDM control matrix for a $4 \times 4$ network                                           | 63 |

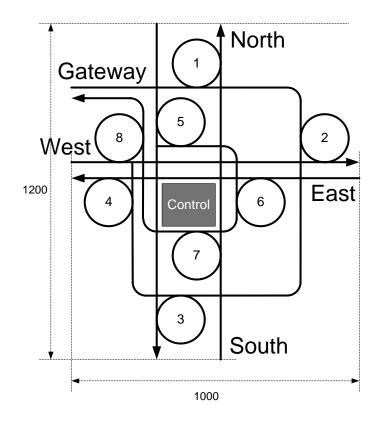

| 3.38 | Layout of ETDM photonic switch, showing waveguides and ring resonators. Units in          |    |

|      | microns                                                                                   | 64 |

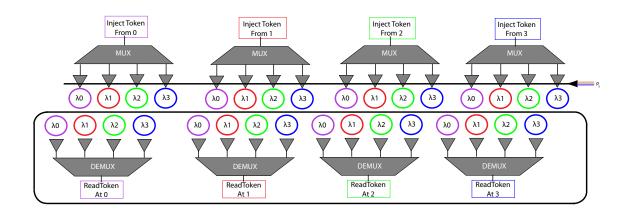

| 3.39 | ETDM network gateway microarchitecture.                                                   | 66 |

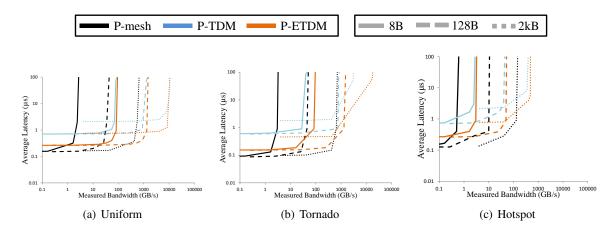

| 3.40 | Latency / bandwidth characteristics of ETDM under synthetic traffic for (a) Random (b)    |    |

|      | Tornado (c) Hotspot.                                                                      | 67 |

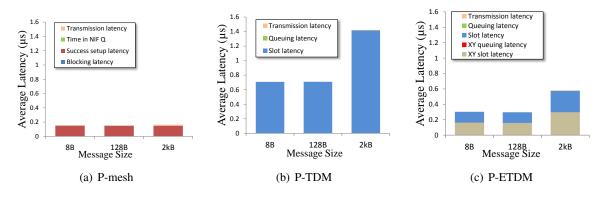

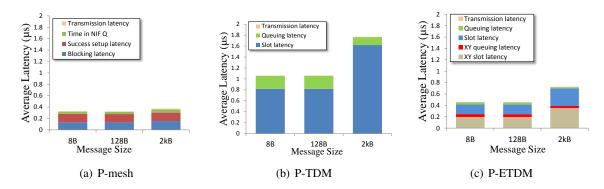

| 3.41 | Zero-load latency breakdown under Uniform traffic                                         | 68 |

| 3.42 | Half-load latency breakdown under Uniform traffic.                                        | 68 |

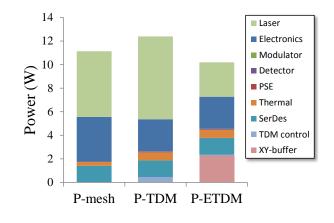

| 3.43 | Power breakdown                                                                           | 69 |

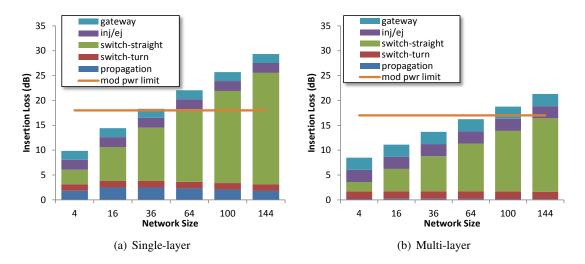

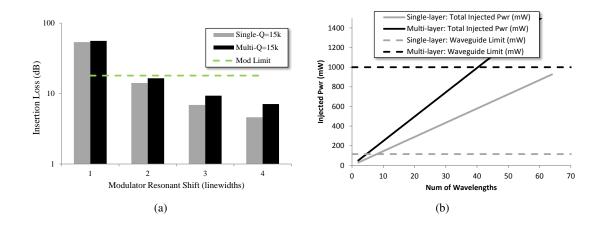

| 3.44 | Insertion loss of single- and multi-layer photonic mesh                                   | 70 |

| 3.45 | A 4×4 example of the matrix-crossbar network topology (not drawn to scale)                | 71 |

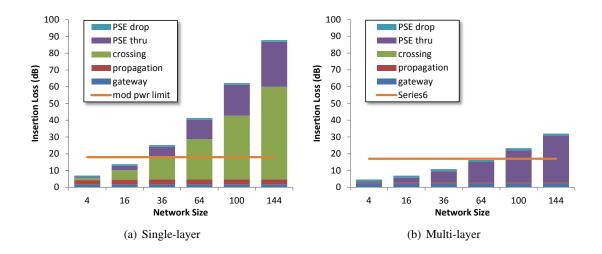

| 3.46 | Circuit-switched matrix crossbar insertion loss analysis versus network size              | 72 |

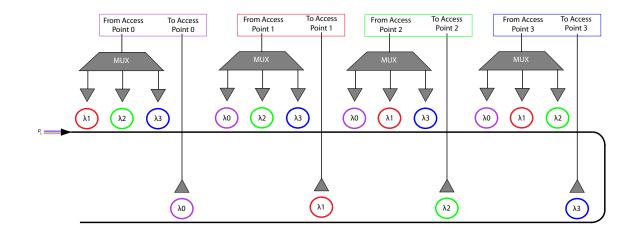

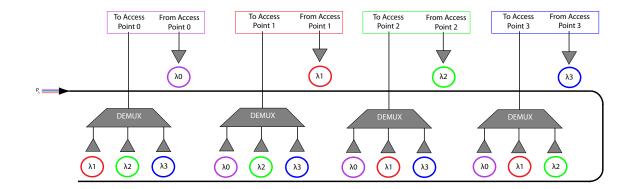

| 3.47 | Source-routed bus.                                                                        | 73 |

| 3.48 | Destination-routed bus.                                                                   | 75 |

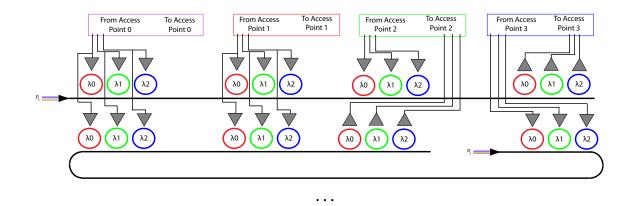

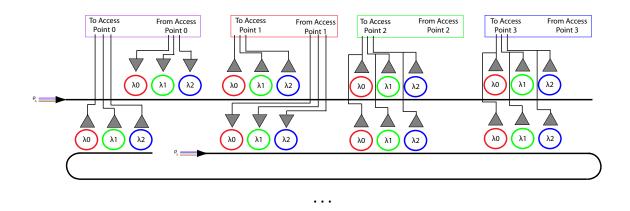

| 3.49 | Multi-Write Single-Read bus implementation with ring modulators and filters               | 76 |

| 3.50 | Single-Write Multi-Read bus implementation with ring modulators and filters               | 76 |

| 3.51 | Wavelength crossbar connecting 4 access points using ring modulators and filters          | 77 |

| 3.52 | Token ring wavelength bus for optical arbitration.                                        | 78 |

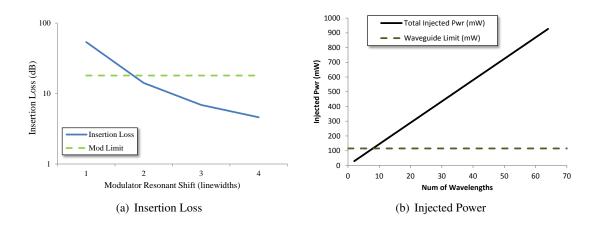

| 3.53 | Insertion loss analysis for Corona's crossbar network. (a) Worst-case insertion loss ver- |    |

|      | sus modulator resonance shift in linewidths. (b) Injected optical power required versus   |    |

|      | number of wavelength channels, limited by the nonlinear threshold.                        | 79 |

| 3.54 | Insertion loss analysis for Corona's token ring network. (a) Worst-case insertion loss    |    |

|      | versus modulator resonance shift in linewidths. (b) Injected optical power required ver-  |    |

|      | sus number of wavelength channels, limited by the nonlinear threshold.                    | 80 |

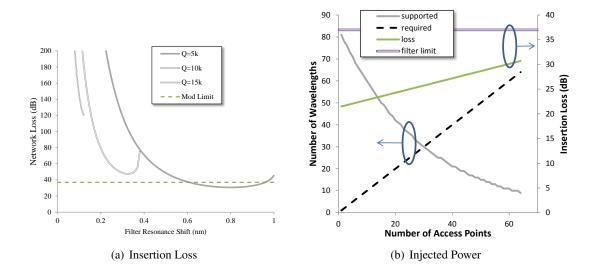

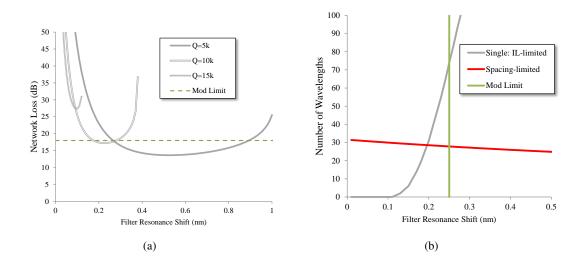

| 3.55 | Insertion loss analysis for Firefly's data network. (a) Worst-case insertion loss versus                                                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | filter resonance shift for microring resonators with different quality factors. Lines stop                                                                                       |

|      | when the quality factor cannot be maintained. (b) Number of wavelength channels pos-                                                                                             |

|      | sible in optical power budget versus resonance shift, ultimately limited by modulator                                                                                            |

|      | power and FSR                                                                                                                                                                    |

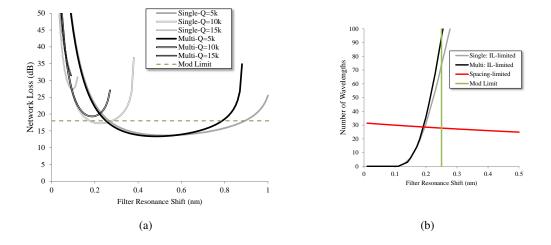

| 3.56 | Insertion loss analysis for Corona's crossbar using multi-layer devices                                                                                                          |

| 3.57 | Insertion loss analysis for one of Firefly's assembly using multi-layer devices 83                                                                                               |

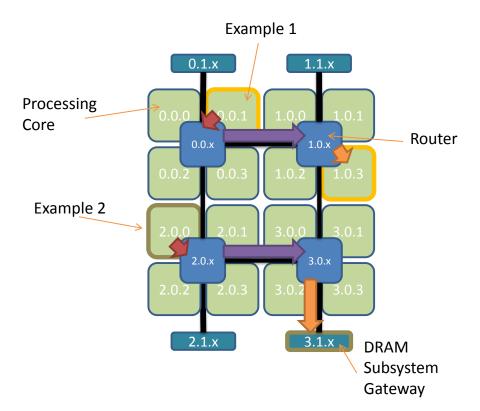

| 4.1  | Basic structure of a PhoenixSim simulation                                                                                                                                       |

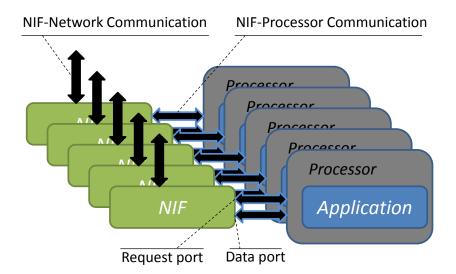

| 4.2  | Structure of the Processing Plane                                                                                                                                                |

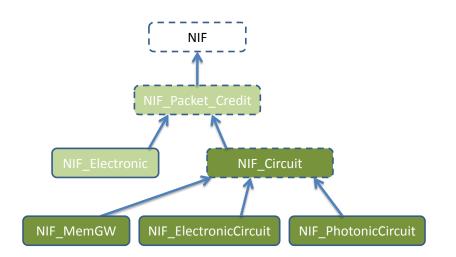

| 4.3  | Hierarchy of current NIFs. Abstract classes shown outlined with dashes                                                                                                           |

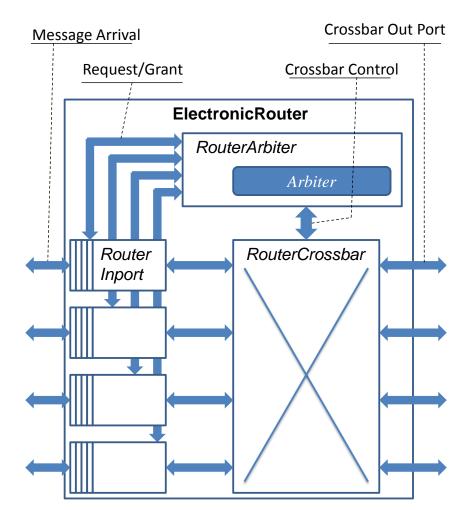

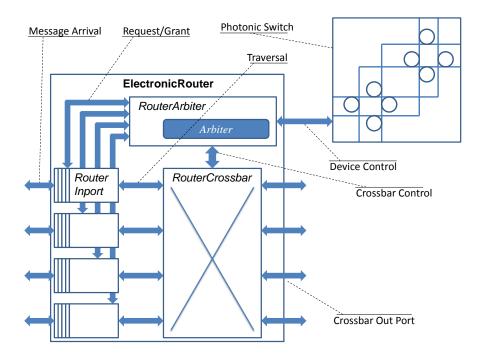

| 4.4  | Structure of Electronic Router                                                                                                                                                   |

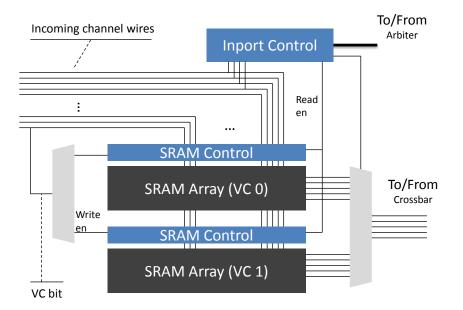

| 4.5  | RouterInport microarchitecture                                                                                                                                                   |

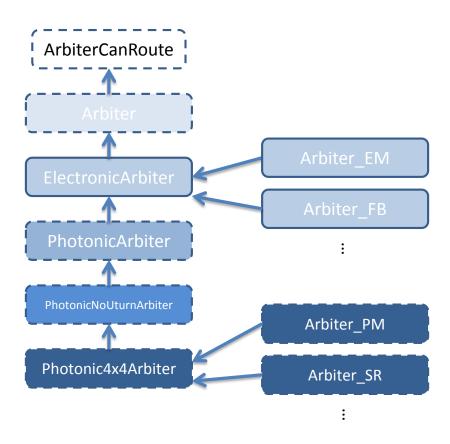

| 4.6  | Arbiter class hierarchy                                                                                                                                                          |

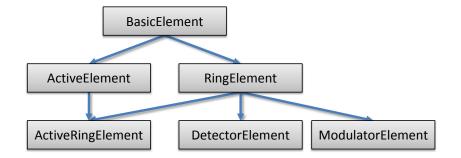

| 4.7  | Hierarchy of the photonic modeling classes                                                                                                                                       |

| 4.8  | Hybrid router consisting of a photonic switch, controlled by an electronic packet-switched                                                                                       |

|      | router                                                                                                                                                                           |

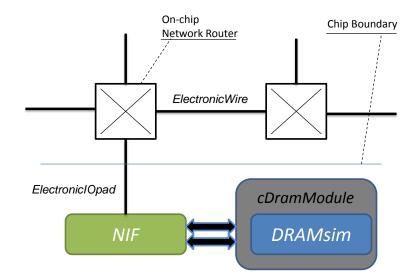

| 4.9  | DRAMsim used in a packet-switched network                                                                                                                                        |

| 4.10 | CAMM structure in DRAM-LRL                                                                                                                                                       |

| 4.11 | Default core-memory map                                                                                                                                                          |

| 4.12 | Example of how addressing and routing works                                                                                                                                      |

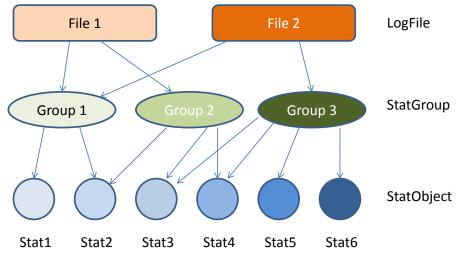

| 4.13 | How statistics work                                                                                                                                                              |

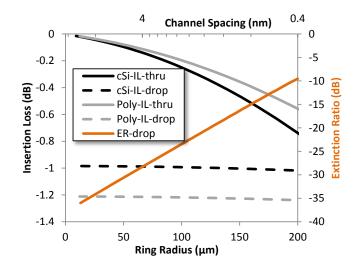

| 4.14 | PSE characteristics versus ring radius                                                                                                                                           |

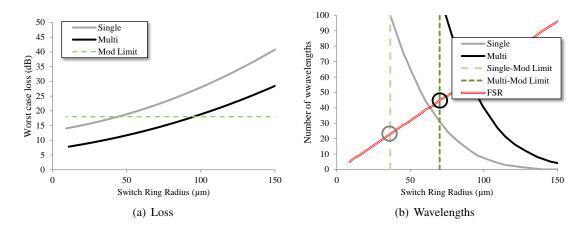

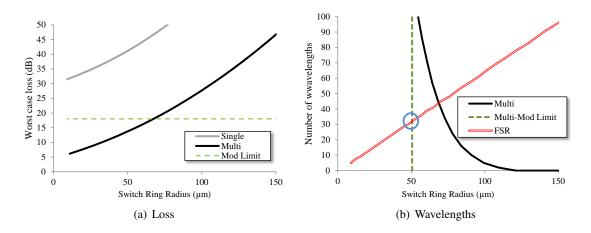

| 4.15 | Optimization of P-Mesh versus ring radius showing (a) worst-case loss and (b) number                                                                                             |

|      | of wavelengths feasible                                                                                                                                                          |

| 4.16 | Optimization of Matrix Crossbar versus ring radius showing (a) worst-case loss and (b)                                                                                           |

|      | number of wavelengths feasible                                                                                                                                                   |

| 4.17 | VANDAL composition block diagram                                                                                                                                                 |

| 4.18 | Example of component parameterization - ring modulator                                                                                                                           |

| 4.19 | VANDAL's layer editor                                                                                                                                                            |

| 4.20 | Example connection two North-facing ports                                                                                                                                        |

| 4.21 | Screenshots of response of four-modulator WDM gateway, with freespace wavelength                                                                                                 |

|      | on the x-axes and loss (dB) on the y-axes $\ldots \ldots \ldots$ |

| 4.22 | Screenshot of two photonic links                                                                                                                                                 |

| 4.23 | Example of a constraint-requirement specification of an SoC                                                                                                                      |

| 4.24 | Basic photonic link instantiation                                                                                                                                                |

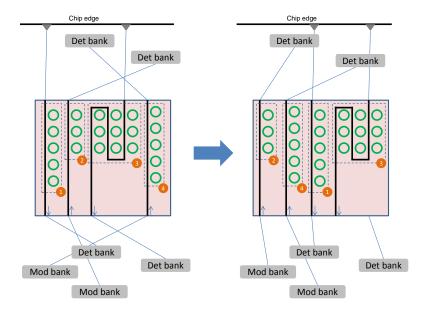

| 4.25 | Basic layout of modulator and detector banks in a gateway                              |

|------|----------------------------------------------------------------------------------------|

| 4.26 | Link combination using WDM                                                             |

| 4.27 | Gateway reordering for reducing waveguide crossings                                    |

| 4.28 | SoC floorplans and communication graphs for 4 different video processing applications. |

|      | Numbers on graphs indicate required bandwidth in GB/s. Colored regions indicate lo-    |

|      | cation of interface to photonic communication plane                                    |

### **List of Tables**

| 3.1 | Switch Design                          |

|-----|----------------------------------------|

| 3.2 | Switch Functionality                   |

| 4.1 | Insertion Loss Optimization Parameters |

| 4.2 | Ring Modulator Parameters              |

| 4.3 | SCILL Variable Types                   |

| 4.4 | SCILL Primitive Statements             |

| 4.5 | Insertion Loss Parameters              |

| 4.6 | Power Parameters                       |

| 4.7 | Results                                |

| A.1 | Optical Device Loss Parameters         |

1

### Introduction

HE past few decades have been an interesting time for computers. Incredible exponential growth in the complexity of both hardware and software of computers, as well as the amount of information available to us, has changed the way we do everything, every day. Most of this advancement comes from Gordon Moore's (possibly self-fulfilling) prophecy that the number of transistors double every 18 months. However, we could be quickly approaching the inflection point of progress.

As we start to see chips using 22nm technology and below, it is becoming apparent that transistors will not scale forever. More than a decade ago, in the late 1990's, engineers were playing new tricks to squeeze out more resolution from their 193nm photo-lithography fabs (2). Transistors will continue to get smaller from here, and many companies have at least 15nm, if not 11nm on their horizon. But where do we go from there? If trends continue, features will be a few molecules or atoms wide, incurring serious quantum effects.

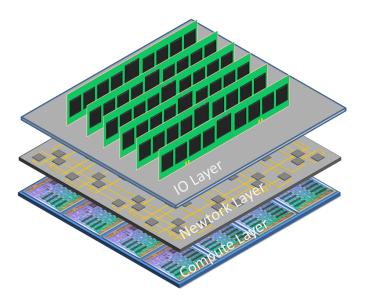

One direction is up, or 3D stacking. Besides the architectural advantages of being able to place more compute power and memory in a single package, designers benefit from 3D stacking by being able to keep logically different or fabrication-sensitive parts separate while optimizing each layer. Key challenges are now being solved for 3D stacked chips, including power and signal delivery with TSVs (3), mechanical issues such as thermally-induced stress (4), and micro-fluidic cooling using vertical pipes (5). However, 3D stacking by bonding separate layers in post-processing is a relatively costly procedure. As we will see in later chapters, deposited silicon photonics is an excellent solution for this.

Figure 1.1: Divergence of CPU power from memory access time, from Exascale report (1).

#### **1.1 The Memory Wall**

New kinds of CMOS-type devices are also being developed. Multi-gate transistors have been in development for a few years (6) which will indeed provide more transistor density, and therefore compute and storage power on chip. However, we already know we can't make a single processing unit significantly better while meeting power constraints, so parallelism has become king in the architecture world. Provided that there is enough work to be done, or enough data to crunch through for the processor, the idea is that exploiting parallelism will be the only way to increase performance.

But parallelism necessarily implies communication. Neither 3D-stacking nor transistor redesign effectively address communication challenges on-chip. Some sources say as much as 50% of the power on chip is caused by the interconnect (7). However, what is more important is off-chip communication.

The first challenge in chip I/O is scaling frequency of the links. Traditionally, this has been difficult because of the careful design of the drivers, receivers, and matched PCB paths. This struggle has led to what is usually referred to as the memory wall (or gap), which can be seen in Figure 1.1. While dramatic increases in on-chip frequencies and transistor densities have yielded huge performance gains over the last decades, this has not necessarily been the case for DRAM and other IO.

The second challenge for electronics is that package IO pin count is already becoming difficult for ball-grid arrays, and is not expected to progress all that much (8). For example, the TILE64 (9) has a couple thousand total package pins, and approximately 1000 data IO pins. According to the ITRS, this is already at the max pin-count for the cost-performance category (commodity general-purpose

Figure 1.2: Pin counts and power for today's microprocessors and projected into the near future.

microprocessors) (8).

Figure 1.2 shows some interesting data from today's microprocessors. The red and blue data points show the number of package pins dedicated to DRAM versus the computation power and year of introduction. Clearly, this number has not increased very much over the last decade for both chips using front-side buses (FSBs) and on-chip memory controllers. This is one cause of the memory wall by limiting bandwidth and connectivity.

Figure 1.2 also shows some projections for power and number of pins for a 10 TFLOP processor with 1 B/FLOP of memory bandwidth. Clearly, the number of pins rises well into the infeasible range, and power becomes unmanageable. What this figure portrays overall, is that there is simply no more

<sup>\*</sup>Hypothetical system, reaching 10 TFLOPS in 2016. Assumes doubled performance every 2 years, 1 B/FLOP required memory bandwidth, scaled bitrate from 5 (2012) to 10 Gb/s (2016). Power scales from 10 to 2 pJ/bit for electronics, 1.2 to 0.2 pJ/bit for photonics.

<sup>&</sup>lt;sup>‡</sup>Assuming 128 wavelengths WDM

<sup>&</sup>lt;sup>§</sup>This line is obtained from the bigger of the two values of the Package Pin Count Maximum projection for Cost-Performance microprocessors reported in the 2008 ITRS and dividing it by 3 (based on the assumption that 1/3 of the pins of the total package pin count is dedicated to communication with memory.)

room to put more electronic pins on a single package, so despite having more computation power on chip through transistor density, frequency, and number of parallel cores, the memory subsystem will still be limited by the same bandwidth of previous generations.

#### **1.2 Exascale Computing**

In 2008, a study was done with leading computing experts on how to achieve an Exascale computer (1). One of their main conclusions was that continuing on the path of today's programming models, execution models, computer architecture, and device technology was not sufficient due to power limitations and feasibility. A target power budget of 20 MW, more than which cannot be sustained financially (10), has been cited by the Department of Energy to realize an Exascale machine, which is 500 times faster than the 6 MW petascale machines of today. Clearly, this will require drastic changes in the way the machine is designed and implemented, and programs were spun off to try to seriously rethink the computer from all sides. Among all the issues, communication was identified as a key challenge.

The Exascale problem represents a unique challenge to the computing community, and therefore a unique opportunity for photonics. The problem poses a very real and constrained situation which will *force* engineers to consider new technologies such as photonics in a way that has not been necessary before. And, advances achieved in the area of high-performance and large-scale computing will also be applicable to other areas such as commercial or embedded systems.

From the application side, many people believe the user (programmer) *must* have some explicit control over data movement in a high-performance machine, or at the very least, make it so the programmer can't *not* be aware of data movement. This belief basically stems from the realization that implicit shared memory paradigms cannot scale efficiently. Though we may not necessarily see programs where chip-scale communication is *all* MPI-style explicit communication, programming/memory models such as partitioned global address space (PGAS) (11) will help to add data locality to programming and program execution.

#### **1.3 The Role of Photonics**

Optical communication has been around for some time in the internet backbone for long-haul transmission across the country. The idea is that optics is not as distance-dependent as electronics for both power and bandwidth because it can go much longer without have to repeat the signal. Latency benefits can also be argued, and higher bitrates are more feasible when they don't have to be repeated so often. In theory, optical transmission is very appealing for any scale of communication.

Steadily, optics has made its way down into smaller-scale and shorter-distance applications, the first being supercomputers and compute clusters. The lighter, longer, more compact form factor of optical fiber alone provides a benefit for machines with *many* connections to a compute rack. However, most of these solutions are active-cabling, which replaces electrical cables with plug-and-play fibers with transceivers at both ends. Though making use of optical technology in this way is itself interesting, many people in photonic networks research believe that we can go further and perform switching or routing optically as well. Electronic networks are typically built on a store-and-forward mechanism, where data packets are stored, routed, and arbitrated at each router in a network. By bypassing electronic switching and routing, optics as the potential to work outside the power, latency, and bandwidth restraints of the store-and-forward mechanism (see Figure 3.1 in Chapter 3). Methods using both MEMS-based circuit-switch (12) and optical packet switching (OPS) (13) have been proposed, though they have not made it into commercial systems yet.

There are many good reasons why photonics is also appealing for chip-scale communications. First, as we mentioned, photonics can provide immense IO bandwidth. For example, instead of the TILE64's (9) 1000 IO pins, photonics could use 100 waveguides (with the same pitch) using 10 wavelengths each, with higher signaling rate. As chip and IO area become more constrained, photonics is appealing because of either reduced packaging complexity or increased IO bandwidth.

Another reason why photonics is looking good is that chip-scale nanophotonics is maturing. The basic components of an on-chip link have been put together and demonstrated (14), and commercial silicon nanophotonics is becoming available today for board- and computer-scale communications (15). Though ring resonator based structures are not yet ready for production, the challenges for making them reliable are being solved right now.

The questions we are presented with now are "how do we enable large scale integration of photonic devices?" and, once that is addressed, "how do we make the best use of photonics?" This thesis presents design methodologies and tools necessary to investigate these questions. Specifically, a system-level simulator called PhoenixSim was developed for the exploration of both electronic and photonic networks on chip, which is freely available to the research community. A layout CAD tool called VANDAL was also developed targeted towards designing, modeling, and fabricating chip-scale optical links and networks. Finally, using these tools, improvements and design spaces were explored for different network architectures targeting multi-core CMPs to highly specific SoCs.

In Chapter 2, we provide a background of the photonic devices that are under investigation today, describing their functional and physical behavior and characteristics. In Chapter 3, we present network architecture designs and improvements, and considering arising issues when analyzing the collective effects of the physical layer both statically and at runtime. Finally, in Chapter 4, we present the simulation, optimization, and automation tools that are necessary to perform the design and analysis from Chapter 3. It is our ultimate aim to be able to merge the physical geometry and characteristics of photonic devices with architectural and system-level design practices, bringing the reality of chip-scale nanophotonics one step closer.

2

### **Silicon Photonics**

N this chapter, we will present an overview of some of the nanophotonic devices and structures that are common in today's research, and which will be used later in architectural designs as well as layout and synthesis. The presentation of this material is not meant to imply that any of it is novel contribution to the field nor is it an exhaustive or in-depth analysis, rather it is background material for understanding later chapters for readers who are not necessarily familiar with photonics. We will present devices as functional components and describe their geometry and modeling, in some cases for both crystalline silicon and deposited materials.

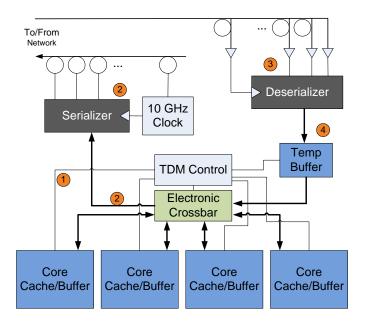

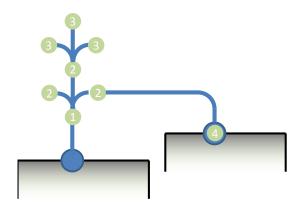

#### 2.1 WDM Photonic Link

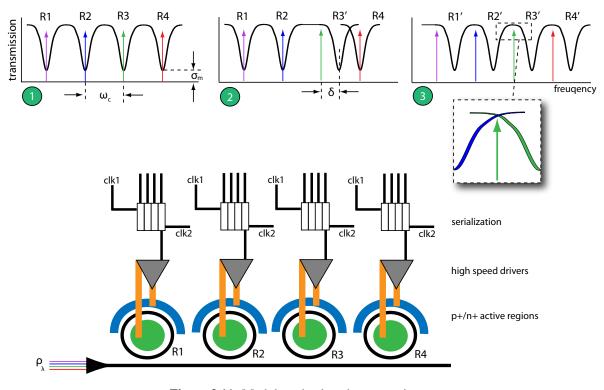

First, we will briefly describe how photonic communication works in general. Figure 2.1 shows the general structure of a Wave Division Multiplexed (WDM) link. The term WDM refers to the fact that multiple frequencies of light can *each* carry information simultaneously in the same waveguide at the same time. This is advantageous because it dramatically increases the bandwidth density (bandwidth per unit area) of a link. Of course, to properly use WDM, we require devices which can perform functions on individual frequencies in a waveguide without significantly affecting the others, which will be introduced later. Following the numbered items in Figure 2.1:

1. Data arrives to the send side of the link, which must be ramped up to the modulation clock rate, known as serialization. This stage requires buffers and circuitry which can convert between two

Figure 2.1: Basic form of a WDM link.

clock domains.

- 2. Analog circuitry drives the ones and zeros into the modulator, consisting of some amplifiers and wave-shaping circuits. One technique implemented in the driver circuitry, shown in Figure 2.2(a), overshoots the applied voltage to inject carriers quicker, and under-shoots the zero-voltage to sweep out carriers for faster modulation.

- 3. Modulators convert continuous-wave light of a specific frequency into light which carries the digital information. Many modulators arranged serially along a waveguide can operate each on their own wavelength in parallel. Usually, the continuous-wave source of light comes from lasers off-chip which are multiplexed together and launched into a waveguide. The simplest way to accomplish modulation is to use on-off keying (OOK), or blocking light for zeros, and letting light through for ones, which is shown in Figure 2.2(b).

- 4. A network transparently switches or routes the information using filters or active switches, either wavelength-dependent or broadband.

- 5. Each wavelength is filtered out, and arrives to a detector which can absorb light, producing a current. The receiver converts the current to a voltage and amplifies it up to a level which works with the digital circuitry. If some wavelengths are not filtered out and detected, they continue on to other parts of the network.

- 6. The data is ramped back down to the clock rate it started in, known as deserialization.

Figure 2.2: Modulation operation.

(a) to get a cleaner signal at high bitrates, we must apply wave-shaping circuits to the driver to sweep carriers in and out of the modulator. (b) On-Off Keying is sometimes achieved by shifting the frequency that the modulator operates on while keeping the laser source constant, which will block light for zeros, let light through for ones.

Of course, this is a simplified view of what happens. In reality many signaling issues come into play which affect communication performance such as noise, filter quality, and optical loss. But, keeping this basic structure and interoperation of components in mind, we can introduce some of the devices which have been developed to perform these functions.

#### 2.2 Simple Structures

This section describes some of the more simple integrated photonic structures and devices. Here, simple does not mean that they are easy to fabricate or model necessarily, but rather have fairly simple geometric structure, and may have fairly limited use for our purposes.

#### 2.2.1 Waveguides

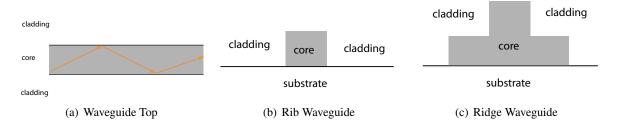

The fundamental unit of light transport on chip is the waveguide. Guiding light is fairly easy to understand: light is confined by a refractive index contrast in a narrow shaft. Figure 2.3 shows a basic diagram. In Figure 2.3(a), we see a top view of a waveguide with light reflecting off the walls. For all the light to be confined (known as *total internal reflection*), it must be incident at a small *critical* angle  $\theta_c = \arcsin(\frac{n_{cladding}}{n_{core}})$ , which is greatly exaggerated in the figure.

Light can also be confined with different structures. Figure 2.3(b) shows the rib waveguide, the

Figure 2.3: Simple view of waveguides.

simplest form. Figure 2.3(c) shows a waveguide with a *ridge*, which is useful for creating a P-I-N diode across the waveguide (as we'll discuss later). Though there are many other ways of doing this, the rib and ridge waveguides are the main structures we will consider in this work to make things simple.

The main way to characterize waveguides is by finding its *effective index*, which describes how light propagates through the waveguide, taking into account both the materials of the core and cladding as well as the geometry of the waveguide. This allows us to use a *propagation constant* ( $\beta = n_{eff} \frac{2\pi}{\lambda}$ ) when describing the propagation of a plane wave. To approximate the effective index, we use the effective index method for rectangular waveguides (16). Briefly, for a cross section of the waveguide, this involves calculating an effective 1-dimensional effective index in one direction first, then using it to find the final effective index in the other dimension. For the ridge waveguide, an average index of cladding and core can be used for the "shoulders" of the structure as an approximation.

Usually, the amount of optical power in a waveguide has a limit before nonlinear effects are produced, which can highly degrade a signal's integrity. However, sometimes nonlinear optical effects are sought after, such as using Four-Wave Mixing for frequency conversion (17), which can be used for wavelength-multicasting (18).

Recent work has shown waveguides which can support many wavelengths simultaneously (19) and can support up to 10 dBm of optical power without nonlinearities, and loss down to 0.3 dB/cm (20). Low-loss silicon nitride waveguides, which can be deposited rather than etched from crystalline silicon, have also been shown at 0.1 dB/m (21).

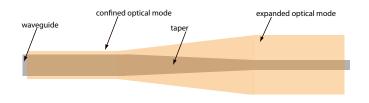

Figure 2.4: Waveguide taper for mode expansion.

#### 2.2.2 Waveguide Taper

A waveguide taper is used to alter the mode profile of confined light in a waveguide. Usually, we design a waveguide such that it is *single-mode*, or most of the optical power is inside the waveguide. Sometimes, we need to have some of the optical power outside the waveguide, such as when we are coupling off-chip to a fiber where single-mode operation is larger, or enhance evanescent coupling between waveguides. Figure 2.4 shows a waveguide taper used for this purpose. As the waveguide gets smaller, the optical mode becomes less confined, and expands out. Expanded out like this, the waveguide will be higher loss, so for longer transmissions we usually want to keep it tightly-confined. This structure has been fabricated in silicon (22), and is commonly used for lateral fiber couplings.

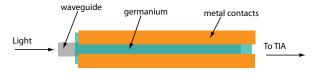

#### 2.2.3 Photo-Detector

One of the most important integrated photonic devices is the photo-detector, or photo-diode, which is used to absorb light, inducing an electrical current. Usually, we then convert electrical current into electrical voltage and amplify using a transimpedance amplifier (TIA). One way to make a photo-detector is to use a single crystal germanium film (which has good absorption in near-infrared) in a metal-semiconductor-metal (MSM) configuration (23), seen in from the top in Figure 2.5. The most important characteristic of a detector is its *responsivity*, or how much electrical current is produced for every unit of optical power introduced into it. This eventually dictates the receiver's *sensitivity*, or the minimum optical power necessary to reliably detect a logical "1". Also, it is important to keep capacitance low for low power operation (24). One characteristic of this detector is that it is broadband (will absorb any wavelength of light in the range of interest), so a wavelength filter must precede it in a WDM system. Section 2.3.4 shows a ring-based detector that can be used for both filtering and absorption.

Figure 2.5: Germanium MSM photo-detector

Figure 2.6: Mach-Zehnder interferometer

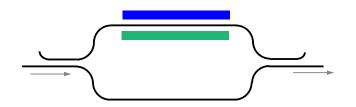

#### 2.2.4 Mach-Zehnder Interferometer

Another device is the Mach-Zehnder interferometer, shown in Figure 2.6. The idea behind this structure is that the optical power is split at the first evanescently-coupled waveguides, and a phase change is induced in one of the arms. In silicon, this can be accomplished with a p-i-n region around the waveguide. Once the light couples back together at the output, the phase change induced will cause destructive interference (optimally, a shift of  $\pi$  radians), thus canceling the amplitude of the light wave. This device is mainly useful as a modulator (25), and has been shown in the first commercially-available integrated silicon photonics (15). However, the Mach-Zehnder structure is relatively large, requiring a long interaction length (the "arms") to induce the phase change. This makes the power consumption and insertion loss high, which makes it not as useful for potential on-chip network designs.

#### 2.3 Ring-based Structures

In this section, we will discuss some of the latest research in micro-ring resonators. Ring-resonator structures have been under investigation long before nano-scale integration was possible. The ring structure creates a sort of feedback effect which ends up making the device resonant with certain frequencies. This resonant frequency also repeats, and the distance between resonances is called the free-spectral range (FSR). The smaller the ring, the longer the FSR. An FSR as large as possible is desired for modulation so as many wavelengths as possible can be used before the resonance repeats (see Section 2.3.1), and as small as possible for a broadband switch for the same reason (see Section 2.3.3). This resonant behavior

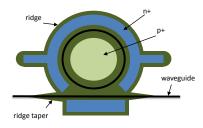

Figure 2.7: Geometry of a ring modulator.

becomes very useful for WDM systems to act on a single wavelength while ignoring any others present in the waveguide. Rings have been a hot topic of research in the past years because they are very small compared to other integrated solutions (as we will point out in the subsections below), which reduces the total area and power needed for a photonic link.

However, there are currently some unsolved challenges to ring-based devices. The first is the extreme temperature sensitivity of the devices. As much as a 1°C change in temperature will change the effective optical path length of the ring (by changing the index of the material), which starts to dramatically shift the resonant frequency. Ring structures are also highly sensitive to manufacturing variations for the same reason, and have very low yields. One way to combat these effects is to include ohmic heaters close to the ring, locally heating the area to stabilize the temperature, though an integrated solution with feedback control has not been demonstrated yet.

#### 2.3.1 Ring Modulator

Modulation, or converting digital bits stored in buffers to information in traveling light, can be done with a ring modulator. The simplest way to accomplish this is to use on-off keying (OOK). Figure 2.7 shows the structure of a ring resonator which can accomplish this for a single wavelength. By applying voltage across the p+-n+ region, we can inject carriers into the waveguide, thus changing the loss (and optical path length) of the ring, which changes the resonant wavelength. Modulation has been shown up to 18Gb/s (26) for this type of modulator. Though we consider mostly chip-scale distances in this work, the basic modulator can even be used to modulate data across very large distances (27). Finally, multiple cascaded modulators for WDM modulation is discussed later in Section3.2.2.4.

One useful way to describe the behavior of the ring modulator is with equations based on the geom-

etry and materials of the device. Yariv did this, assuming a simplified model (28):

$$|b_1|^2 = \frac{\alpha^2 + t^2 - 2\alpha |t| \cos(\theta + \phi_t)}{1 + \alpha^2 |t|^2 - 2\alpha |t| \cos(\theta + \phi_t)}$$

(2.1)

where  $\alpha$  is the inner circulation factor (the ring's loss),  $\phi_t$  is the phase change of the coupling region,  $\theta$  is the phase change around the ring  $(2\pi N_{eff}(2\pi R)/\lambda)$ , and t is the transmission coefficient. The optical power coupling coefficient between two waveguides,  $\kappa$ , can be expressed from waveguide and gap dimensions from the Appendix in (29), giving us:

$$\kappa = \frac{\omega \varepsilon_0 cos(k_{x2}\omega_2)}{2\sqrt{P_1P_2}(k_{x1}^2 + \alpha_2^2)} (n_1^2 - n_0^2)$$

$$\times \sqrt{\frac{\pi R}{\alpha_2}} exp[\alpha(\omega_2 - 2s_0)]$$

$$\times [\alpha_2 cos(k_{x1}\omega_1)sinh(\alpha_2\omega_1)$$

$$+ k_{x1}sinh(k_{x1}\omega_1)cosh(\alpha_2\omega_1)]$$

which will give us t by conserving optical power using  $t^2 + \kappa^2 = 1$ .

We can also construct different types of modulators which have some advantages over the basic ring modulator in Figure 2.7. A second-order structure (using an additional ring) can make the modulator hitless (the resonance disappears instead of shifting), which would reduce crosstalk/loss in a WDM system (30). A different kind of doping region structure can be used to create a p-i-n-i-p instead of a single p-i-n diode for faster carrier injection and depletion (31). Also, a ring coupled with a Mach-Zhender interferometer can make the ring less sensitive to temperature variations (32). Finally, a modulator using deposited polysilicon can be made, which is also very fast (33).

One important thing about on-off keying using a ring modulator is the nonlinear threshold. When the modulator is on-resonance (transmitting no light, or a logical "0"), light is circulating in the resonator building up power. Eventually, it will dissipate due to radiation and scattering losses, but if we inject too much power into it, two-photon absorption (34) and free-carrier absorption (35) will start to happen. Again, this will change the loss in the ring and start to shift the resonance, inadvertently leaking light through. A common nonlinear threshold is about 0 dBm of optical power. One way to possibly combat

Figure 2.8: Single-wavelength filter

this effect is to either use a drop port to let the optical power out (which may slow it down a little), or to use differential phase-shift keying (DPSK) (36) instead of OOK.

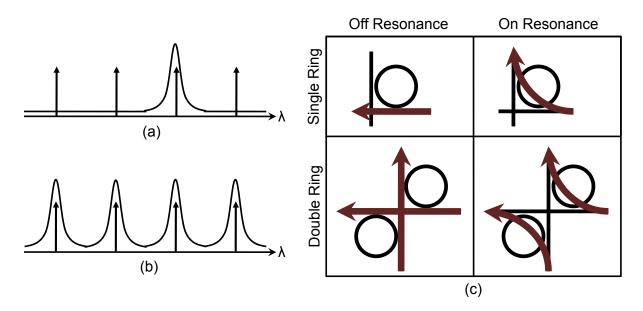

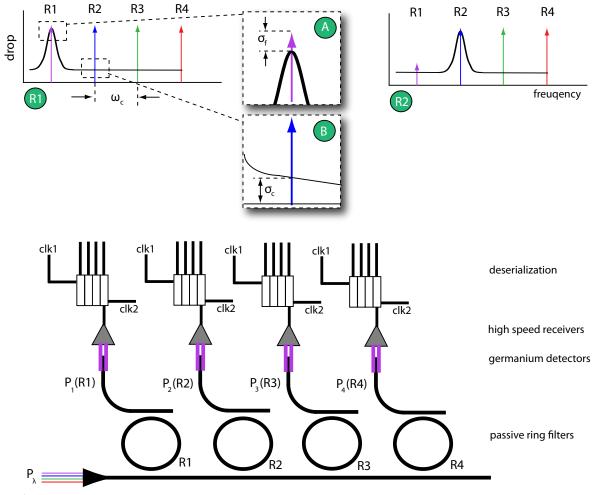

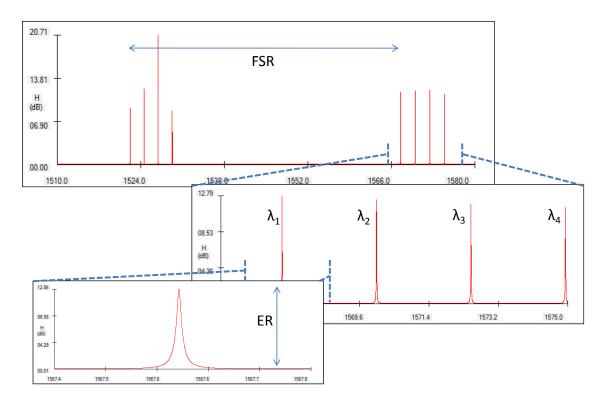

#### 2.3.2 Ring Filter

Another useful function of a ring resonator's wavelength-selective property is to filter out only one wavelength from a WDM waveguide. This is useful when we want to demultiplex wavelengths for detection, as discussed later in Section 3.2.2.4. Figure 2.8 shows this simple structure, filtering out just the blue wavelength. Filters, being one of the easier structures to fabricate because they are passive, have been demonstrated in silicon (37) and deposited silicon nitride (38).

Similarly with the modulator, we can describe the transmission equations for the drop and through port (39):

$$H_{drop} = \frac{\kappa_1^2 \kappa_2^2 \alpha}{1 - 2t_1 t_2 \alpha \cos(\theta + \phi_t) + t_1^2 t_2^2 \alpha^2}$$

(2.2)

$$H_{thru} = \frac{t_1^2 + t_2^2 \alpha^2 - 2t_1 t_2 \alpha \cos(\theta + \phi_t)}{1 - 2t_1 t_2 \alpha \cos(\theta + \phi_t) + t_1^2 t_2^2 \alpha^2}$$

(2.3)

which becomes very useful when determining channel spacing, and therefore loss and crosstalk.

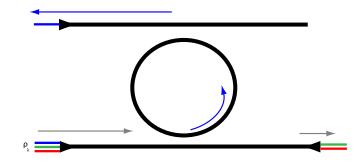

#### 2.3.3 Ring Switch

If we make the diameter of the ring larger, the FSR startes to become smaller such that the resonant modes can line up with *every* wavelength in the WDM waveguide. We then would have a broadband filter, or, if we put p+ and n+ regions around the waveguide, we can shift the resonance to make a

Figure 2.9: Optical ring resonators can be used as switching devices within an on-chip photonic network.

broadband *switch*. Figure 2.9a shows the filter configuration with smaller rings, and Figure 2.9b shows how a ring resonator's resonant profile can be designed to align with many optical wavelengths at once by making the ring larger. We can also implement double switching functionality by using two rings, as in Figure 2.9.

One important difference of the broadband switch from the filter is that because it is bigger, the drop loss will be higher, and it will take more power and take longer for it to switch its resonance. Also, it is probably a good idea to design the switch such that the default state is on-resonance, so that large drop losses are not incurred from passing through a waveguide where carriers are being injected. Broadband switches (or comb-switches) have been demonstrated in silicon with optical pumping (40) and using heaters to thermally switch the rings (41).

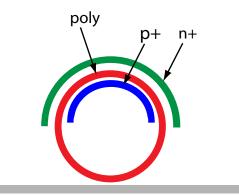

#### 2.3.4 Ring Detector

A detector can also be implemented using a ring structure, which acts as both the filtering mechanism and the absorbing medium. One way to do this is by introducing defects into the silicon which enables absorption (42). Another way is to use deposited poly-crystalline for the ring (and waveguide for a good design) (43). In both situations, a p-i-n region is placed around the ring to collect current as shown in Figure 2.10. As of today, the ring-detector structure does not exhibit responsivities as high

Figure 2.10: Poly ring photo-detector

as germanium-crystal based detectors, though the idea is that because the light circulates many times around the ring, the responsivity should be fairly good because it is subject to the absorbing region many times over.

# Photonic Interconnection Network Architectures

Ow that we have a brief understanding of the state of today's research in nanophotonic devices, we can begin to think about how we will use them in interconnection networks for chip-scale computing.

#### 3.1 Network Architecture Overview

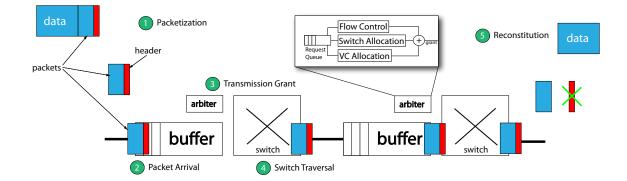

Constructing a photonic interconnection network begins by considering the usual machanisms of any network: arbitration, switching, and routing. First, let us consider how this is accomplished in typical electronic networks. In a classical electronic store-and-forward (SaF) network, data is broken up into *packets*, each of which have a *header* that describes its source, destination, identification, and other use-ful information. When traversing a network, arbitration, switching and routing can operate on individual packets on a per-router basis. This process is shown in Figure 3.1.

The first step, labeled (1), splits up the data into multiple packets, attaching the appropriate header information to each. When a packet arrives to a router, labeled (2), it is both stored in a buffer and a request is sent to an *arbiter*. The arbiter checks that there is enough available down-stream buffer space to hold the packet (flow control), checks that the input and output ports of the switch are not currently in use (switch allocation), and may optionally assign the packet to a new virtual channel (VC allocation).

Figure 3.1: The process of store-and-forward packet networks.

After the arbiter performs these checks, it grants the packet access to the switch, and simultaneously informs the switch itself to set up, labeled ③. The packet then traverses through the switch to the next router, labeled ④. At the destination, headers are discarded, and packets are placed in order, labeled ⑤.

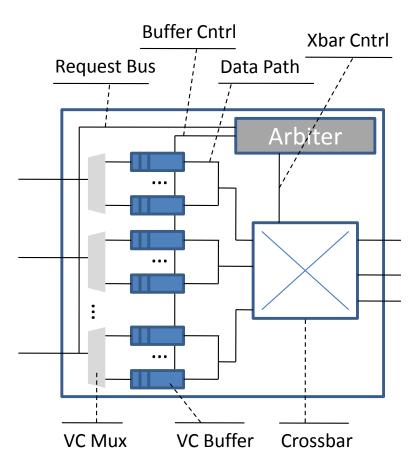

Figure 3.2 shows the structure of a typical *packet router*. Typically, a virtual channel multiplexer can route an incoming packet to the correct buffer space within its arriving clock cycle. Transmission requests and grants are sent on the buffer control bus, and packets traverse along the data path wires through the switch. This general router structure along with the SaF paradigm has led to innumerable network and NoC architecture improvements over the years, including wormhole routing, cuthrough routing, and dynamic routing. Techniques for managing buffer space in the network have been proposed for increased utilization, such as credit and token flow control.

However, the fundamental difference of photonics is that while it has benefits for strict communication of bits, it lacks the ability to store bits for an arbitrary amount of time while arbitration and routing can occur. This immediately excludes using the SaF system and general router structure implemented with pure photonics. As we will see in the next sections, there are different ways to either get around this limitation, or use photonics to implement the necessary functions without needing to store packets. These methods need to ensure *end-to-end arbitration*, or allocating a complete path from source to destination before actually transmitting the data. Alternate methods can also be employed which transmit data part-way through the network with photonics, convert to the electronic domain to temporarily store it, then complete the remaining transmission optically. This technique obviously is costly in terms of conversion hardware energy and area, but relaxes some of the arbitration constraints on performance.

Figure 3.2: Anatomy of an electronic store-and-forward packet router

In any case, the two main classes of photonic interconnection architectures are ones that use circuitswitching, and ones that use the wavelength domain for arbitration. The next sections discuss these classes of architectures in detail, and provide examples of each.

#### 3.2 Circuit-Switched Architectures

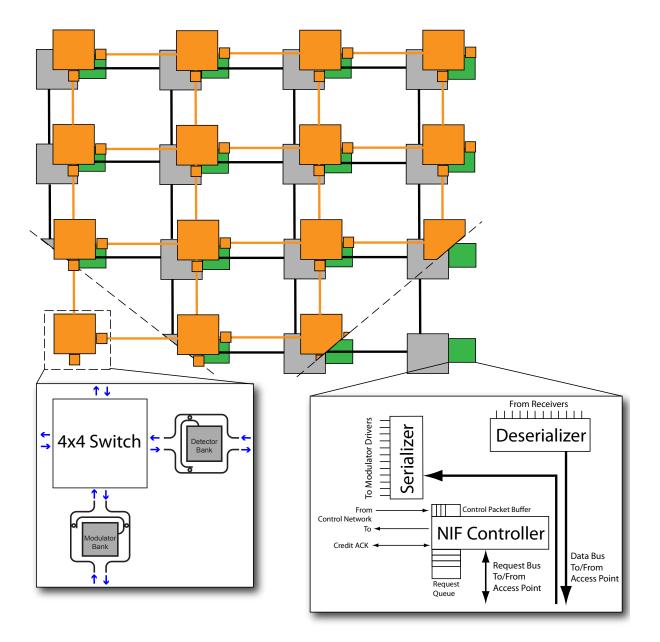

One solution to the problem of end-to-end arbitration is to use pure circuit-switching. Circuit-switching, or *spatially*-switched networks use broadband WDM signaling to produce extremely high-bandwidth connections between communicating nodes by multiplexing data onto many parallel wavelengths. Switching is enabled through the use of broadband switches that can actively be controlled to pass or switch all the wavelengths concurrently, discussed earlier in Section 2.3.3. Since this method requires some sort of logical control to activate or de-activate each ring along a path from source to destination, we use

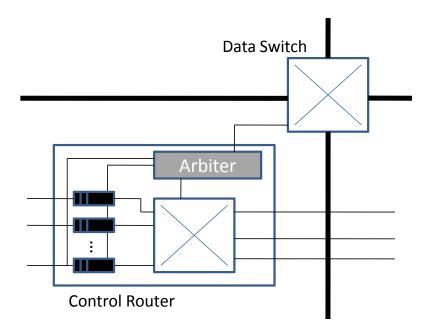

Figure 3.3: Anatomy of a circuit router

a lightweight packet-switched network to arbitrate access to a network of high speed data switches. A path-setup protocol, discussed in Section 3.2.1, is used to set up an end-to-end path through the network *ahead of time*, then transmitting the data when it is complete.

The overall structure of a *circuit router* can be found in Figure 3.3. The electronic *control router* has all the same basic parts of the packet router of Figure 3.2, and functions much the same way. One key difference is that the control router only has to handle 1- or 2-flit control messages, or basically just the header part of a normal data packet. Since the control router does not have to support large flows of data, it should be optimized for latency, and not bandwidth. We call this optimization "lightweight", because the channels are narrower, the buffers smaller, and virtual channels are not implemented, all to save power with little cost to performance. The data switch, however, is typically high-speed and high-bandwidth for increased performance. This switch could be implemented with high-speed electronics, though the focus of this book is its implementation with photonic devices.

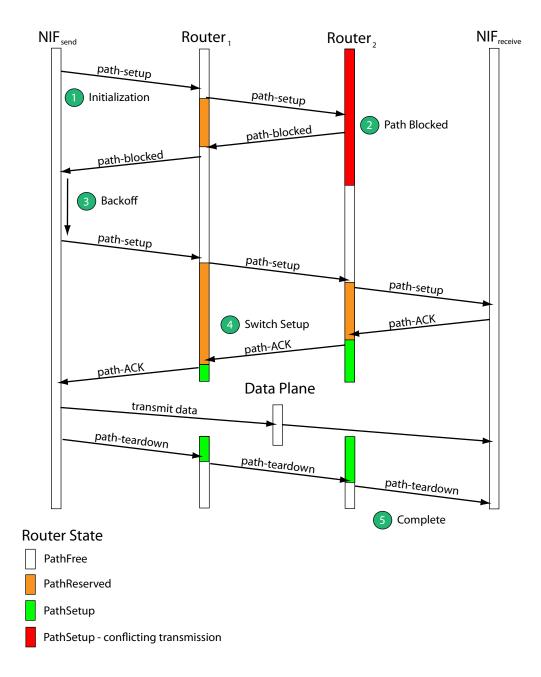

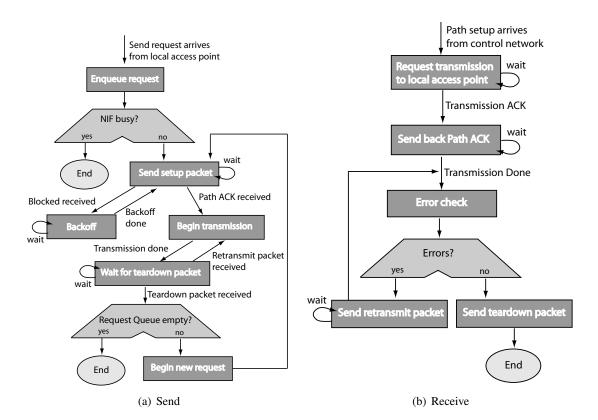

#### 3.2.1 Path-Setup Protocol

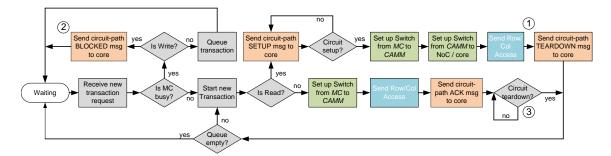

The path-setup protocol is the mechanism that the control routers use to ensure that the data switches in the network are always set correctly, and that two transmissions never conflict with each other. This is accomplished with the use of four main types of control messages: *path-setup*, *path-ACK*, *path-blocked*, and *path-teardown*. Figure 3.4 shows an example of how the path-setup protocol works.

A network transmission is first initialized, labeled (1), at a network interface (NIF) who wishes to send data to another NIF in the network. After Router<sub>1</sub> receives the path-setup message, besides the usual routing and electronic-plane arbitration, the arbiter performs the additionanal step of checking that resources in its data switch are properly allocated by keeping track of the state of every possible inputoutport port combination. After the routing (input-output port pair) is performed and Router<sub>1</sub> checks that the state is *PathFree*, and it is able to forward the path-setup message to Router<sub>2</sub>, Router<sub>1</sub> then sets its state from the inport to the outport as *PathReserved*, which indicates that the path is in the process of being set up. The path-setup message continues on to Router<sub>2</sub> where it is blocked, labeled (2).

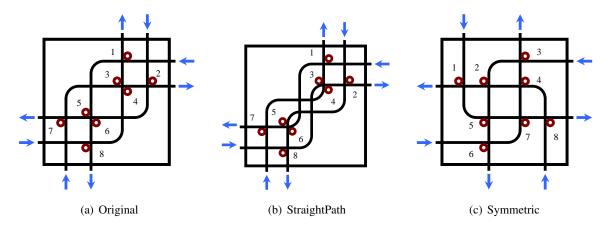

Blocking could occur if another transmission was either in the process of setting up a path (PathReserved), or already set up (PathSetup), and the input-output combination of the new transmission conflicts with the existing one. Depending on the switch design, this conflict could manifest itself in different ways. If a strictly non-blocking data switch is used, only desintation port conflicts are possible. If the data switch being used exhibits some blocking characteristics, additional blocking scenarios may occur.

Router<sub>2</sub> then turns the message around back to its source, turning it into a *path-blocked* message. This indicates to Router<sub>1</sub> that it should set its state back to PathFree, so that other transmissions may be allowed through. After the sending NIF receives the path-blocked message, it can then immediately retransmit, or implement a *backoff*. Much in the same way that Transmission Control Protocol (TCP) in internet networks uses backoff to manage network congestion when establishing a link, using backoff in the circuit path setup protocol gives the network time to free the contended resources before trying a new setup request to save power and further congestion. A good practice is to have a random chance of immediate retry, with some chance to backoff for a random or predictable amount of time. The setup then continues as normal until it is received by the destination NIF, indicating a successful setup.

The receiving NIF then sends a *path-ACK* message back through the network, which changes the states of each router to *PathSetup*. This is when the arbiter actually sends the appropriate signals to the data switch to implement the correct path, labeled 4. After the sending NIF receives the path-ACK message, it now knows that the end-to-end path is set up through the network, and can begin transmitting data on the data plane.

Figure 3.4: Path setup protocol

After the transmission is complete, the path reservation is released by sending *path-teardown* messages through the control network. Though it is shown initiated from the send side in Figure 3.4, path teardown can be initiated from either side. In fact, it may be preferable to have the destination initiate the path-teardown message in case retransmission is necessary due to bit errors.

#### **3.2.2** Photonic Circuit-Switched Network Design

Much in the same way that network topology affects latency and congestion in packet-switched electronic networks, the design and placement of photonic switches in a photonic circuit-switched network will have consequences on performance. In this section, we will show how to design a simple photonic circuit-switched network based on a mesh topology.

#### 3.2.2.1 Switch Design

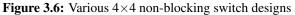

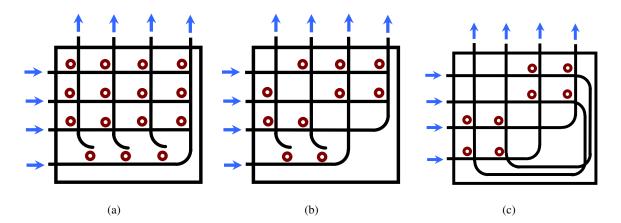

The basic building block of a spatially-switched network is the spatial switch. As we discussed earlier, and shown in Figure 2.9, we can make spatial switches which are able to switch all the wavelengths of an optical signal at once from one port to another out of ring resonators. These  $1\times 2$  and  $2\times 2$  fundamental switching units can be used to realize higher-order switches. A natural design choice is trying to implement a  $4\times 4$  switch, one port for each of the cardinal directions.

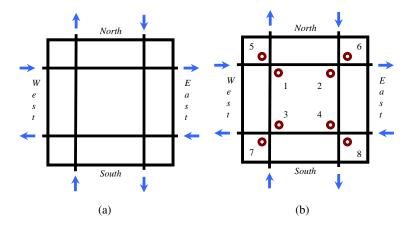

Let us consider how this can be accomplished. Start by referring to Figure 3.5(a), which is simply four intersecting waveguides implementing a bidirectional port at each cardinal direction. The column labeled 3.5(a) in Table 3.1 summarizes the functionality of this simple configuration. Obviously, this is not much of a switch because it doesn't implement all possible paths, denoted by the Inport/Outport pairs in Table 3.1. We do not consider path turnarounds (for example, *from* the East port *to* the East port), because in circuit-switching, this is unlikely to be very useful.

Now we add in broadband ring resonators at waveguide junctions to implement paths in the switch, which is shown in Figure 3.5(b) and first appeared in a paper by Shacham (44). The column labeled 3.5(b) in Table 3.1 designates which ring is used to implement which path, completing all possible paths. Note that eight rings are needed to accomplish this, because the coupling regions between the ring and waveguides must be engineered specifically to support certain optical paths for the best switch extinction.

**Figure 3.5:** Designing a  $4 \times 4$  switch. (a) just the crossing waveguides. (b) adding broadband rings to implement paths.

|        |         | Ring/Path |        |        |        |        |

|--------|---------|-----------|--------|--------|--------|--------|

| Inport | Outport | 3.5(a)    | 3.5(b) | 3.6(a) | 3.6(c) | 3.6(b) |

| W      | N       |           | 5      | _      | -      | 3      |

| W      | Е       | _         | _      | 4      | 7      | _      |

| W      | S       |           | 2      | 8      | 6      | 8      |

| N      | Е       |           | 6      | 2      | _      | 2      |

| N      | S       | _         | -      | 6      | 5      | -      |

| N      | W       |           | 4      | -      | 1      | 5      |

| E      | N       |           | 3      | 1      | 3      | 1      |

| E      | S       |           | 8      | -      | _      | 6      |

| E      | W       | _         | _      | 5      | 2      | _      |

| S      | N       | _         | _      | 3      | 4      | _      |

| S      | E       |           | 1      | —      | 8      | 4      |

| S      | W       |           | 7      | 7      | -      | 7      |

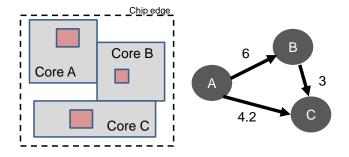

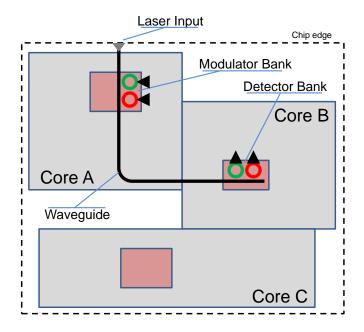

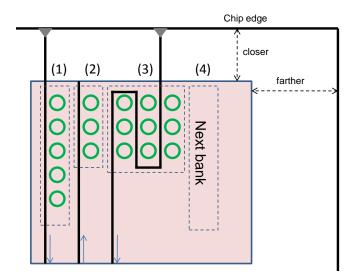

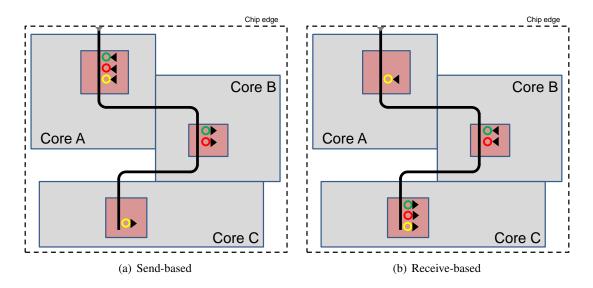

Table 3.1: Switch Design