### Data-Driven Programming Abstractions and Optimization for Multi-Core Platforms

Rebecca L. Collins

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

Rebecca L. Collins

All Rights Reserved

### **ABSTRACT**

### Data-Driven Programming Abstractions and Optimization for Multi-Core Platforms

### Rebecca L. Collins

Multi-core platforms have spread to all corners of the computing industry, and trends in design and power indicate that the shift to multi-core will become even wider-spread in the future. As the number of cores on a chip rises, the complexity of memory systems and on-chip interconnects increases drastically. The programmer inherits this complexity in the form of new responsibilities for task decomposition, synchronization, and data movement within an application, which hitherto have been concealed by complex processing pipelines or deemed unimportant since tasks were largely executed sequentially. To some extent, the need for explicit parallel programming is inevitable, due to limits in the instruction-level parallelism that can be automatically extracted from a program. However, these challenges create a great opportunity for the development of new programming abstractions which hide the low-level architectural complexity while exposing intuitive high-level mechanisms for expressing parallelism.

Many models of parallel programming fall into the category of data-centric models, where the structure of an application depends on the role of data and communication in the relationships between tasks. The utilization of the inter-core communication networks and effective scaling to large data sets are decidedly important in designing efficient implementations of parallel applications. The questions of how many low-level architectural details should be exposed to the programmer, and how much parallelism

in an application a programmer should expose to the compiler remain open-ended, with different answers depending on the architecture and the application in question. I propose that the key to unlocking the capabilities of multi-core platforms is the development of abstractions and optimizations which match the patterns of data movement in applications with the inter-core communication capabilities of the platforms.

After a comparative analysis that confirms and stresses the importance of finding a good match between the programming abstraction, the application, and the architecture, this dissertation proposes two techniques that showcase the power of leveraging data dependency patterns in parallel performance optimizations. Flexible Filters dynamically balance load in stream programs by creating flexibility in the runtime data flow through the addition of redundant stream filters. This technique combines a static mapping with dynamic flow control to achieve light-weight, distributed and scalable throughput optimization. The properties of stream communication, i.e., FIFO pipes, enable flexible filters by exposing the backpressure dependencies between tasks. Next, I present *Huckleberry*, a novel recursive programming abstraction developed in order to allow programmers to expose data locality in divide-and-conquer algorithms at a high level of abstraction. Huckleberry automatically converts sequential recursive functions with explicit data partitioning into parallel implementations that can be ported across changes in the underlying architecture including the number of cores and the amount of on-chip memory. I then present a performance model for multicore applications which provides an efficient means to evaluate the trade-offs between the computational and communication requirements of applications together with the hardware resources of a target multi-core architecture. The model encompasses all data-driven abstractions that can be reduced to a task graph representation and is extensible to performance techniques such as Flexible Filters that alter an application's original task graph. Flexible Filters and Huckleberry address the challenges of parallel programming on multi-core architectures by taking advantage of properties specific to the stream and recursive paradigms, and the performance model creates a unifying framework based on the communication between tasks in parallel applications. Combined, these contributions demonstrate that specialization with respect to communication patterns enhances the ability of parallel programming abstractions and optimizations to harvest the power of multi-core platforms.

# Table of Contents

| Intr | oducti                                        | ion                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Termi                                         | nology                                                                                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.2  | Proble                                        | em Statement                                                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.3  | Requi                                         | rements                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.4  | Hypot                                         | chesis                                                                                                                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.5  | Thesis                                        | S Outline                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bac  | kgroui                                        | nd                                                                                                                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1  | Multi-                                        | Core Platforms                                                                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.1.1                                         | Heterogeneous Architectures: IBM/Sony/Toshiba Cell BE $$                                                                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.1.2                                         | Graphics Processing Units: NVidia GeForce 8800 GTX                                                                                               | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.1.3                                         | Tiled Architectures: Tilera TILE64                                                                                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.1.4                                         | General-Purpose Architectures: Intel Core i7                                                                                                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2  | Parall                                        | el Programming Models                                                                                                                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.1                                         | Threads                                                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.2                                         | Message Passing                                                                                                                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.3                                         | Graphics Languages                                                                                                                               | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.4                                         | SPMD                                                                                                                                             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.5                                         | Stream Programming                                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.6                                         | Recursive Parallel Programming                                                                                                                   | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.7                                         | Map-Reduce                                                                                                                                       | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Bac<br>2.1 | 1.1 Termi 1.2 Proble 1.3 Requi 1.4 Hypot 1.5 Thesis  Backgroun 2.1 Multi- 2.1.1 2.1.2 2.1.3 2.1.4 2.2 Parall 2.2.1 2.2.2 2.2.3 2.2.4 2.2.5 2.2.6 | 1.2 Problem Statement  1.3 Requirements  1.4 Hypothesis  1.5 Thesis Outline  Background  2.1 Multi-Core Platforms  2.1.1 Heterogeneous Architectures: IBM/Sony/Toshiba Cell BE  2.1.2 Graphics Processing Units: NVidia GeForce 8800 GTX  2.1.3 Tiled Architectures: Tilera TILE64  2.1.4 General-Purpose Architectures: Intel Core i7  2.2 Parallel Programming Models  2.2.1 Threads  2.2.2 Message Passing  2.2.3 Graphics Languages  2.2.4 SPMD  2.2.5 Stream Programming  2.2.6 Recursive Parallel Programming |

|   | 2.3  | Progra  | amming Patterns                                         | 26 |

|---|------|---------|---------------------------------------------------------|----|

| 3 | An   | Empir   | rical Comparison of Two Multi-Core Architectures        | 29 |

|   | 3.1  | Bench   | mark Applications                                       | 31 |

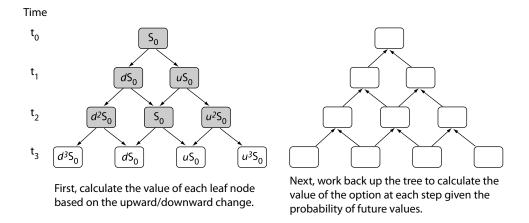

|   |      | 3.1.1   | Option Pricing                                          | 31 |

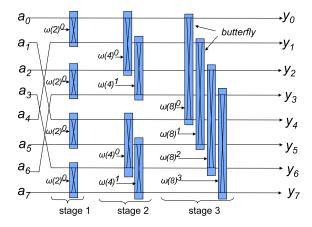

|   |      | 3.1.2   | Fast-Fourier Transform (FFT)                            | 34 |

|   |      | 3.1.3   | Bitonic Sort                                            | 35 |

|   |      | 3.1.4   | Smith-Waterman Sequence Alignment                       | 36 |

|   | 3.2  | Exper   | iments                                                  | 38 |

|   |      | 3.2.1   | Option Pricing                                          | 39 |

|   |      | 3.2.2   | Fast-Fourier Transform (FFT)                            | 42 |

|   |      | 3.2.3   | Bitonic Sort                                            | 43 |

|   |      | 3.2.4   | Smith-Waterman Sequence Alignment                       | 45 |

|   |      | 3.2.5   | Discussion                                              | 47 |

|   | 3.3  | Relate  | ed Works                                                | 49 |

|   | 3.4  | Summ    | nary                                                    | 50 |

| 4 | Flex | xihle F | Cilters: Load Balancing through Backpressure in Streams | 53 |

| - | 4.1  |         | ole Filters                                             | 57 |

|   |      | 4.1.1   | Pipeline-Aware Mapping                                  | 60 |

|   | 4.2  |         | mentation of Flex_Split and Flex_Merge                  | 61 |

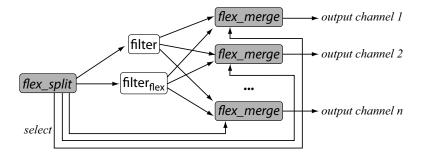

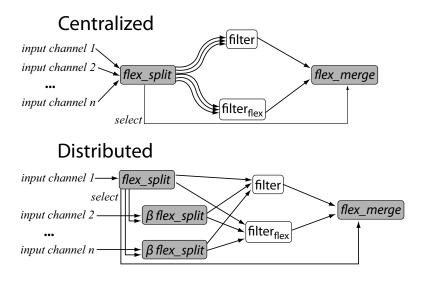

|   |      | 4.2.1   | Multi-Channel Flexible Filters                          | 64 |

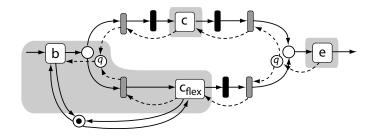

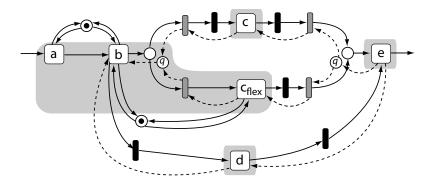

|   |      | 4.2.2   | Example                                                 | 66 |

|   |      | 4.2.3   | Practical Implementation Concerns                       | 70 |

|   | 4.3  |         | iments                                                  | 71 |

|   | 1.0  | 4.3.1   | Benchmarks                                              | 71 |

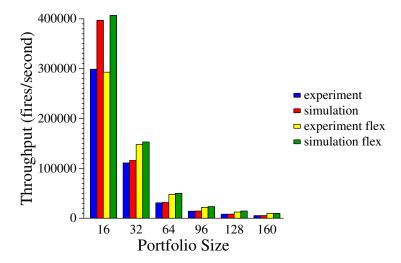

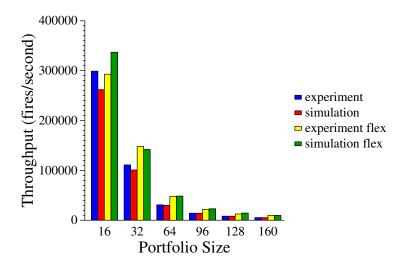

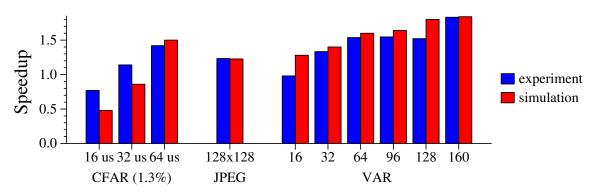

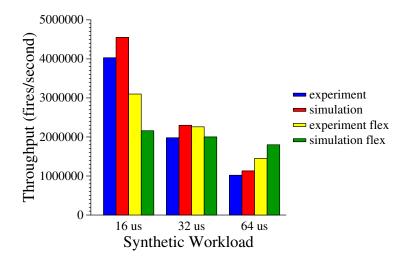

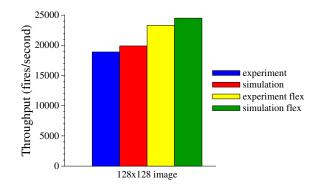

|   |      | 4.3.2   | Results                                                 | 76 |

|   |      | 4.3.3   | Balance of Communication vs. Computation                | 79 |

|   |      | 4.3.4   | Adapting to Data Dependent Flow                         | 80 |

|   |      |         |                                                         |    |

|   | 4.4 | Relate  | ed Works                                   | 81 |

|---|-----|---------|--------------------------------------------|----|

|   | 4.5 | Summ    | nary                                       | 83 |

| 5 | Huo | ckleber | cry: A Data Partition Abstraction          | 85 |

|   | 5.1 | Huckle  | eberry Programming Interface               | 89 |

|   |     | 5.1.1   | Partition Library                          | 90 |

|   |     | 5.1.2   | Example                                    | 91 |

|   |     | 5.1.3   | Optimized Local Code                       | 93 |

|   | 5.2 | Huckle  | eberry Parallel Code Generator             | 94 |

|   |     | 5.2.1   | Machine Model                              | 94 |

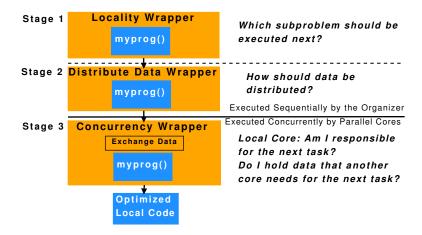

|   |     | 5.2.2   | Stages of Execution                        | 95 |

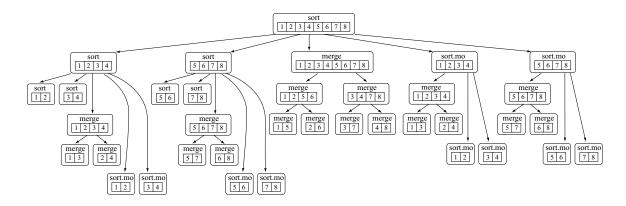

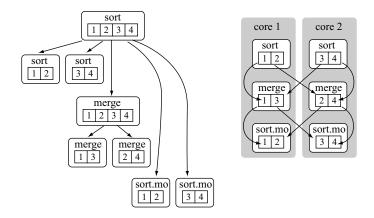

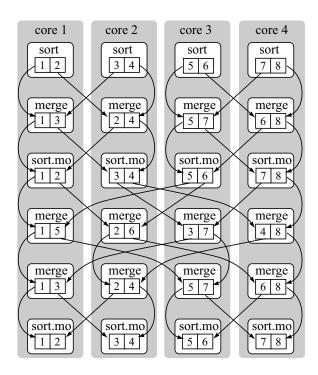

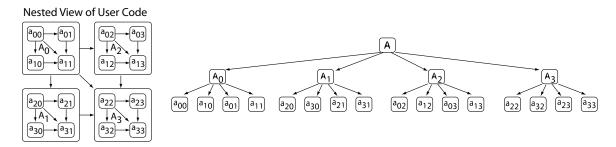

|   |     | 5.2.3   | Example: Traversing the R-Tree             | 00 |

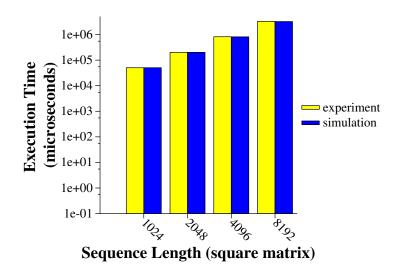

|   | 5.3 | Exper   | iments                                     | 02 |

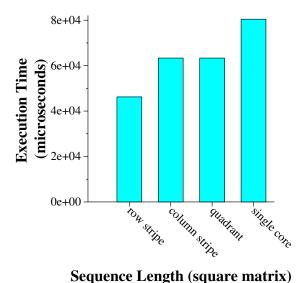

|   |     | 5.3.1   | Scalability                                | 04 |

|   |     | 5.3.2   | Problem Granularity                        | 06 |

|   |     | 5.3.3   | Throughput and the Role of Local Memory    | 08 |

|   | 5.4 | Relate  | ed Works                                   | 08 |

|   | 5.5 | Summ    | nary                                       | 10 |

| 6 | A F | Perforn | nance Model for Multi-Core Applications 12 | 11 |

|   | 6.1 | Petri I | Nets                                       | 13 |

|   | 6.2 | Comp    | ositional Multi-Core Performance Model     | 14 |

|   |     | 6.2.1   | Tasks                                      | 15 |

|   |     | 6.2.2   | Task Composition                           | 15 |

|   |     | 6.2.3   | Architecture                               | 17 |

|   |     | 6.2.4   | Mutual Exclusion                           | 18 |

|   |     | 6.2.5   | Data Buffering in Pipeline Communication   | 18 |

|   |     | 6.2.6   | Communication Latency                      | 19 |

|   |     | 6.2.7   | Flexibility                                | 21 |

| Bi | bliog | raphy 1                                          | 44  |

|----|-------|--------------------------------------------------|-----|

|    |       | 7.2.1 Parallel Index Function                    | 141 |

|    | 7.2   | Future Directions                                | 140 |

|    | 7.1   | Contributions                                    | 138 |

| 7  | Con   | clusions 1                                       | .38 |

|    | 6.7   | Summary/Future Avenues of Research               | 137 |

|    | 6.6   | Related Works                                    |     |

|    | 6.5   | Composing Different Abstractions                 | 135 |

|    |       | 6.4.3 Flexibility                                | 132 |

|    |       | 6.4.2 Communication Latency                      | 130 |

|    |       | 6.4.1 Mutual Exclusion                           | 128 |

|    | 6.4   | Experiments                                      | 128 |

|    |       | 6.3.1 Off-chip Data Swaps                        | 127 |

|    | 6.3   | Generating a Task Graph from a Recursive Program | 122 |

# List of Figures

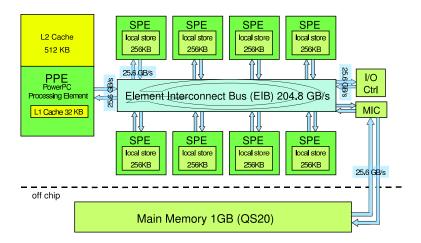

| 2.1  | Cell BE architecture                                                | 12 |

|------|---------------------------------------------------------------------|----|

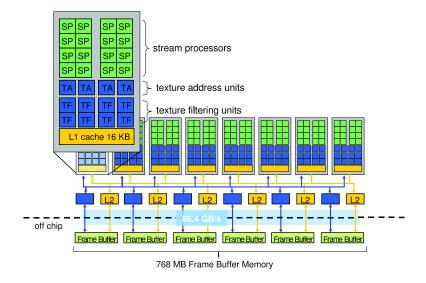

| 2.2  | GeForce 8800 architecture                                           | 14 |

| 3.1  | Dependency structure of the binomial option pricing algorithm       | 34 |

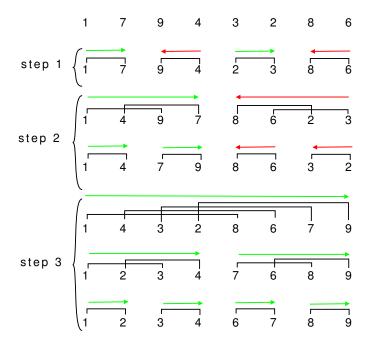

| 3.2  | FFT computation on eight input signals                              | 35 |

| 3.3  | Structure of the bitonic sort algorithm                             | 36 |

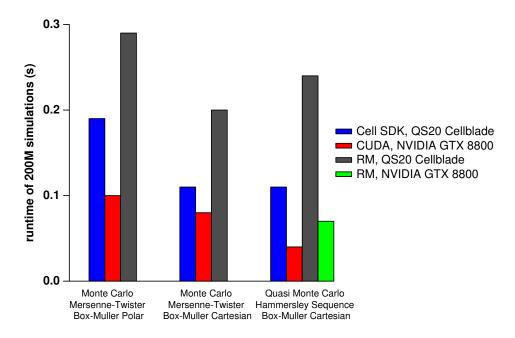

| 3.4  | Performance comparison of Monte Carlo simulations for Black-Scholes |    |

|      | option pricing                                                      | 40 |

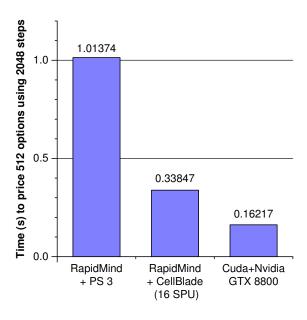

| 3.5  | Binomial option pricing                                             | 41 |

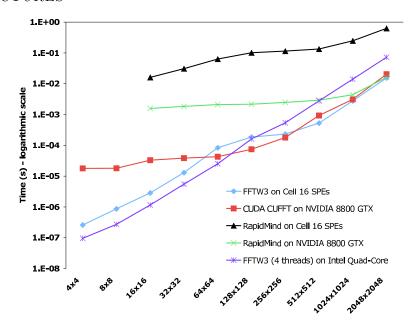

| 3.6  | Performance comparison of single-precision 2-D FFT                  | 42 |

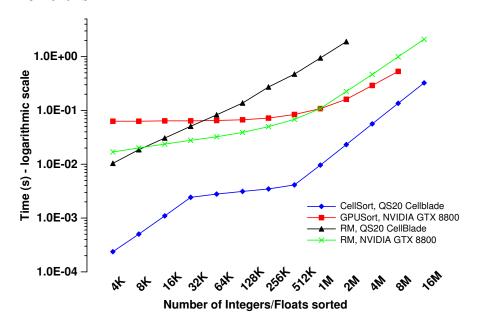

| 3.7  | Performance comparison of bitonic sort                              | 44 |

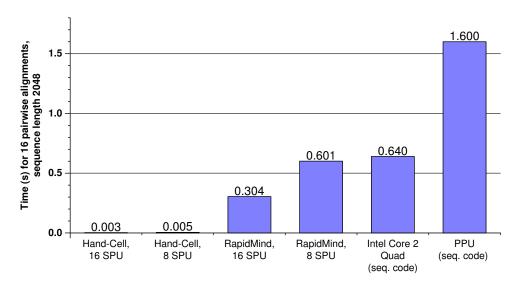

| 3.8  | Performance comparison of Smith-Waterman sequence alignment         | 46 |

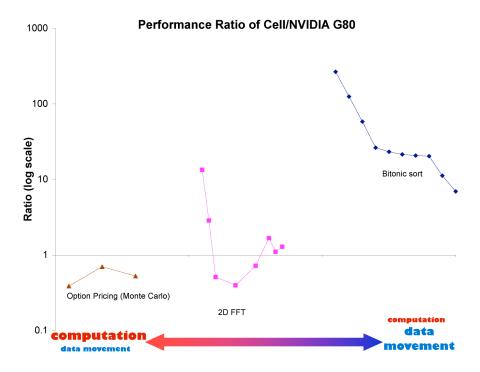

| 3.9  | Performance comparison of Cell vs. NVIDIA 8800 GTX. The x-axis      |    |

|      | shows the spectrum of computation and communication patterns. Data  |    |

|      | points toward the left side are more computation bound; data points |    |

|      | on the right are more communication bound                           | 47 |

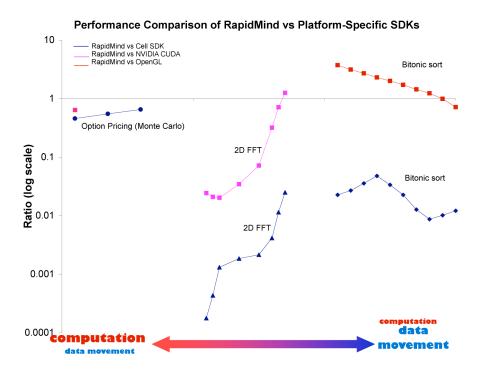

| 3.10 | Performance comparison of RapidMind vs. platform-specific SDKs      | 49 |

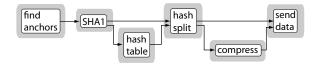

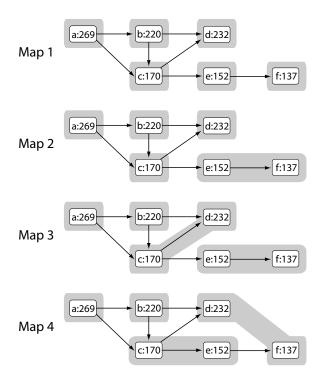

| 4.1  | Stream graph of the Dedup benchmark application                     | 54 |

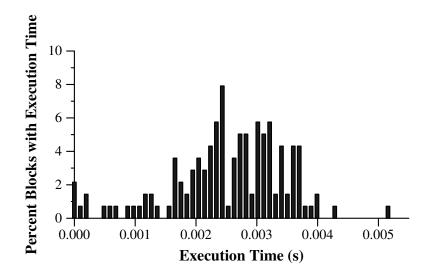

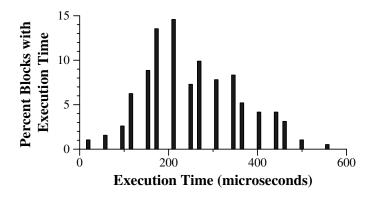

| 4.2  | Histogram of execution times for Dedup's Compress filter            | 54 |

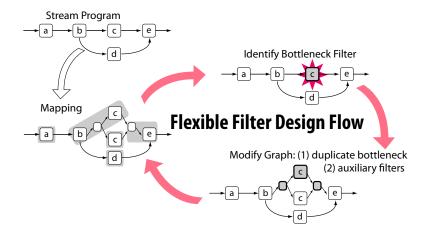

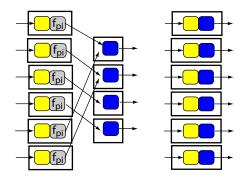

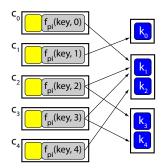

| 4.3  | Flexible filter design flow                                         | 56 |

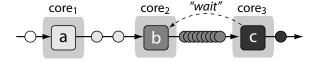

| 4.4  | Example stream program structure                                    | 57 |

| 4.5  | Pipeline mapping                                                           | 58  |

|------|----------------------------------------------------------------------------|-----|

| 4.6  | Flexible filter mapping                                                    | 58  |

| 4.7  | Example stream graph                                                       | 60  |

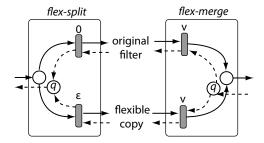

| 4.8  | Relationship of flex_split and flex_merge                                  | 61  |

| 4.9  | Block diagram of a flexible filter with $n$ output channels                | 65  |

| 4.10 | Two alternatives of a flexible filter with $n$ input channels              | 65  |

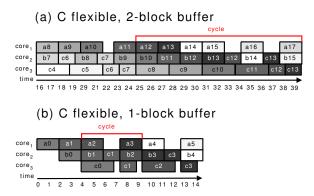

| 4.11 | Flexible filter timelines                                                  | 67  |

| 4.12 | Time-line when filter ${\cal C}$ has a granularity of two tokens per block | 69  |

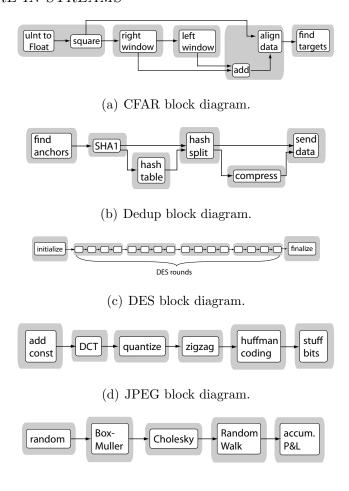

| 4.13 | Block diagrams of benchmarks used together with their mapping on           |     |

|      | the IBM Cell multi-core processor (the non-flexible case)                  | 72  |

| 4.14 | Profile of tasks for each benchmark                                        | 73  |

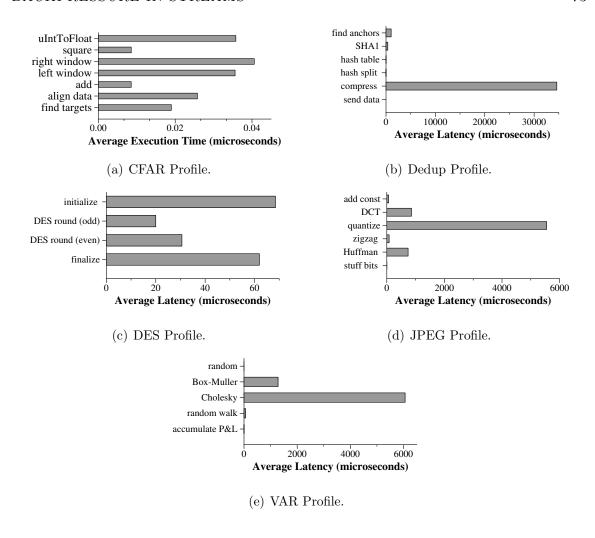

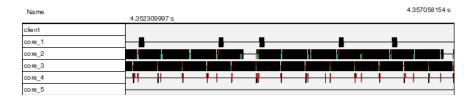

| 4.15 | Gedae trace tables of the VAR benchmark. A core's timeline is black        |     |

|      | when it is busy working on a task. Green and red marks show send           |     |

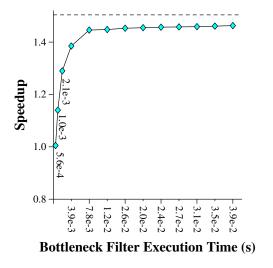

|      | and receive events                                                         | 76  |

| 4.16 | Speedup as the relative cost of a bottleneck filter increases with respect |     |

|      | to the cost of communication                                               | 79  |

| 4.17 | Histogram of workload per 114 cells, % targets/workload = 7/32 $\mu s.$ .  | 81  |

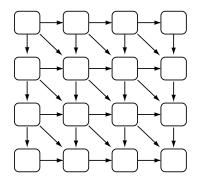

| 5.1  | Wave-front dependency pattern                                              | 86  |

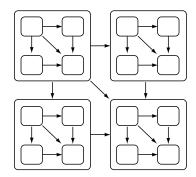

| 5.2  | Recursive quadrant dependency pattern                                      | 87  |

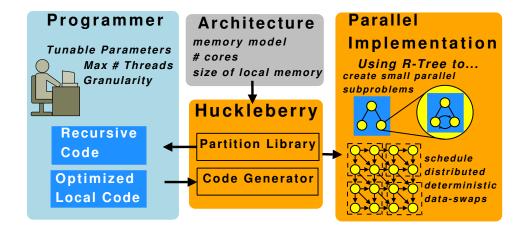

| 5.3  | Huckleberry design flow.                                                   | 88  |

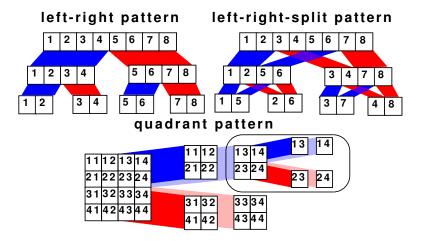

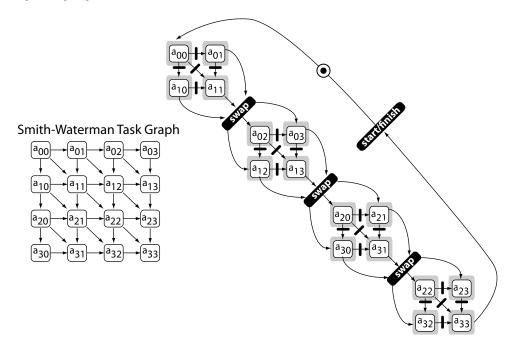

| 5.4  | Patterns of recursively applied partition methods                          | 91  |

| 5.5  | Nested dependencies between bitonic sort recursive functions from Al-      |     |

|      | gorithms 3 and 5 (programmer view)                                         | 94  |

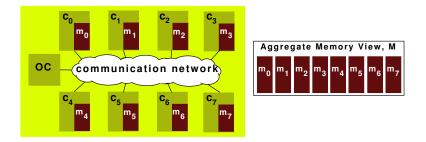

| 5.6  | Abstract machine model                                                     | 95  |

| 5.7  | Stages in a Huckleberry-generated parallel application                     | 96  |

| 5.8  | The R-Tree of bitonic sort recursive functions (code generator view),      |     |

|      | unrolled until the data partition size is two data blocks                  | 100 |

| 5.9  | Subset of bitonic sort R-Tree visited by the locality wrapper              | 101 |

| 5.10 | One subset of the bitonic sort R-Tree visited by the concurrency wrap-         |     |

|------|--------------------------------------------------------------------------------|-----|

|      | per, when there are two cores with a memory capacity of two blocks.            | 102 |

| 5.11 | One subset of the bitonic sort R-Tree as visited by the concurrency            |     |

|      | wrapper, when there are four cores, each with a memory capacity of             |     |

|      | two blocks                                                                     | 103 |

| 5.12 | Scaling cores: Speedup when $D$ and $m_i$ are fixed and the number $N$         |     |

|      | of available cores scales up                                                   | 105 |

| 5.13 | Scaling task granularity: Speedup when $I$ is constant, but $m_i$ is scaled    |     |

|      | down, forcing more cores to work on the problem                                | 106 |

| 5.14 | Scaling data size: $m_i$ remains fixed, while $I$ scales up, normalized w.r.t. |     |

|      | the highest throughput instance in that benchmark                              | 107 |

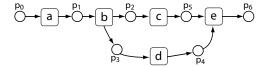

| 6.1  | Example task graph                                                             | 115 |

| 6.2  | Task graph represented as a Petri net.                                         | 116 |

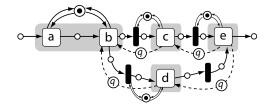

| 6.3  | Modeling mutual exclusion                                                      | 119 |

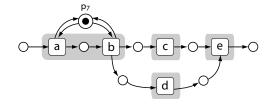

| 6.4  | Modeling backpressure                                                          | 119 |

| 6.5  | Modeling communication overhead.                                               | 120 |

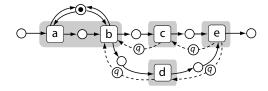

| 6.6  | Modeling flex_split and flex_merge                                             | 121 |

| 6.7  | Incorporating flexibility into the CMCP model                                  | 122 |

| 6.8  | Modeling flex_split and flex_merge with multiple channels                      | 123 |

| 6.9  | Overall Petri net performance model representation of a stream program.        | 123 |

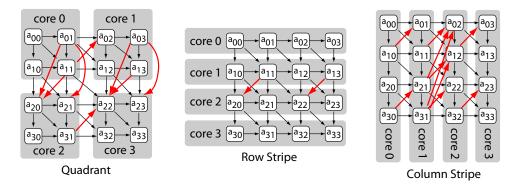

| 6.10 | Task graph tree of the Smith-Waterman benchmark                                | 124 |

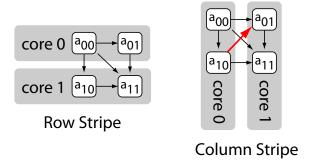

| 6.11 | Row and column stripe mappings on two cores                                    | 125 |

| 6.12 | Different mappings on four cores                                               | 126 |

| 6.13 | Multiple stages of the Smith-Waterman benchmark. The feedback loop             |     |

|      | ensures that only one data set is active at a time (pipelining the stages      |     |

|      | is not the goal in this case)                                                  | 127 |

| 6.14 | Estimated vs. actual throughput testing mutual exclusion                       | 129 |

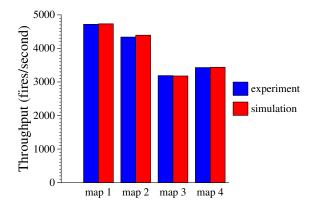

| 6.15 | Estimated vs. actual throughput testing alternative mapping options.           | 130 |

| 6.16 | Estimated vs. actual throughput for VAR, no communication latency.   | 131 |

|------|----------------------------------------------------------------------|-----|

| 6.17 | Estimated vs. actual throughput for VAR                              | 132 |

| 6.18 | Estimated vs. actual speedup across several benchmarks               | 133 |

| 6.19 | Estimated vs. actual throughput for CFAR                             | 133 |

| 6.20 | Estimated vs. actual throughput for JPEG                             | 134 |

| 6.21 | Estimated vs. actual latency of the CMCP model for Smith-Waterman    |     |

|      | on four cores                                                        | 134 |

| 6.22 | Performance comparison of three mappings of a 4x4 task array on four |     |

|      | cores                                                                | 135 |

| 7.1  | Composition with SPMD task blocks                                    | 142 |

| 7.2  | Composition with reduction task blocks                               | 143 |

| 7.3  | Composition with stream task blocks                                  | 143 |

# List of Tables

| 2.1 | Cell BE details                                                       | 12  |

|-----|-----------------------------------------------------------------------|-----|

| 2.2 | GeForce 8800 GTX details                                              | 14  |

| 2.3 | TILE64 details                                                        | 15  |

| 2.4 | Core i7 details                                                       | 16  |

|     |                                                                       |     |

| 4.1 | Baseline pipeline mapping timeline                                    | 66  |

| 4.2 | Summary of speedup results for benchmarks where one bottleneck filter |     |

|     | is made flexible                                                      | 78  |

| 6.1 | CMCP graph size compared to original task graph                       | 129 |

# Acknowledgments

First, I would like to give my sincere thanks to my advisor, Luca Carloni, for his guidance and support through this journey. His amazing energy and optimism are an example I will forever endeavor to follow. I would also like to thank my committee members, Keren Bergman, Nadya Bliss, Stephen Edwards, and Martha Kim, for their time and helpful feedback.

The hardest part about not being a student anymore is that I have to leave the community that I have belonged to for the last five and a half years and move on to a new one. Many thanks to all the the members of the CSL who I have worked with, and who have been there to listen to my practice presentations (sometimes more than once) and offer feedback. In particular, I would like to thank Cheng-Hong Li, who worked closely with me on benchmarking multi-cores, Bharadwaj Vellore, who bravely became the first user and co-developer of Huckleberry, and Nishant Shah, who worked with me developing Stream applications for the flexible filter project. I would also like to thank Eugen Schenfeld, my IBM mentor in 2007, who set me up with training at Gedae, which was essential to the development of flexible filters. I am also very thankful for the opportunity to participate in WICS, which has been a wonderful source of moral support, professional development, and great friends.

Finally, and most of all, I would like to thank my family; my parents, for supporting me from the beginning in every endeavor that I have attempted, my mother-in-law for encouraging me to pursue a PhD, my husband Seva, for helping me keep things in perspective, and my daughter Helen, for being my biggest supporter and for pointing out that Petri nets are actually many-eyed monsters.

To Seva and Helen

# Chapter 1

### Introduction

Since the invention of the integrated circuit, the semiconductor industry has succeeded in doubling the number of transistors on a single chip approximately every two years, a trend known as Moore's law [111]. As more resources have been added to the chip, the processing core has become faster through rising clock rates, deeper pipelines, and larger caches. However, it is becoming apparent that chasing Moore's law into the future will not guarantee continued performance improvements as it has in the past [1; 105. The strategies that traditionally led to faster cores now offer diminishing returns at the current scale of technology. For example, deep instruction pipelines that extract instruction-level parallelism (ILP) are one of the primary innovations that have been responsible for improved performance as the number of resources on a chip increases. However, after a certain depth, control flow interferes with the ability to overlap the execution of different instructions, hindering performance gains. Additional trends such as the complexity of design verification and power constraints also contribute obstacles to continuing to design faster cores. To sidestep these challenges, the focus for improving performance is shifting: rather than make one task run twice as quickly on a faster core, the goal instead is to run twice as many tasks in the same time on two cores |6|.

Thus, in last ten years multi-core chip architectures have gained in popularity, and today multi-core platforms permeate the computer industry from high-performance supercomputers to personal computers and even embedded devices such as smartphones [8; 36; 92; 114; 124]. Duplicating a core (or cores) versus making a single core faster defers the problem of improving program performance to the software designer by exposing parallelism in the hardware, thus enabling more kinds of parallelism including task, data, and coarse-grained pipeline parallelism.

### 1.1 Terminology

This section defines terms used throughout the dissertation.

The terms multi-core architecture, multi-core platform and multi-core system are used somewhat interchangeably. I distinguish them as follows: a multi-core architecture is a chip which hosts more than one processing core; a multi-core platform, or multi-core system, is the multi-core chip together with off-chip resources on a single board (e.g., memory, or even other chips such as the CellBlade Server boards).

A program, or application, represents an algorithm in a programming language and is part of the implementation. A parallel program is a program separated into tasks that may be executed concurrently at runtime. The complete implementation of a parallel program also includes the mapping (or mapping strategy when the mapping is dynamic) of tasks to cores on the target architecture.

A programming model, or programming abstraction, is a simplification or template that a programmer can follow in order to create a parallel program. The interface between the programmer and the model may be implemented, for example, as a library or language.

A *task* is equivalent to a function; in other words, a sequence of operations that work together to accomplish a particular goal. A task may be hierarchical, comprising several *subtasks*. There is no hard requirement about how large a task should be and

when a task should be split up into subtasks. This decision is part of the overall set of design decisions for an application, and task granularity may be tuned to suit a specific target architecture. The process of parallelization aims to split an application into independent tasks that can be executed concurrently and that equally distribute the workload. I consider only finite tasks and sets of tasks.

#### 1.2 Problem Statement

The move to multi-core chip design exposes the parallelism of hardware resources to the programmer rather than hiding it in deep instruction pipelines, leaving the responsibility to extract parallelism (beyond ILP) to the software. In order to deliver the performance promised by multi-core design, it is essential that software tools and techniques are developed that provide this capability.

Unfortunately, many challenges hamper the design of high-performance parallel code for multi-core architectures. While a linear sequence of tasks performed one after another may represent a sequential program, a parallel program includes more than one sequence of tasks that operate in parallel and at times must synchronize and share data. This change significantly increases the complexity of program design for communication, memory management, scheduling and algorithms.

Communication. Communication complexity includes ensuring correctness in inter-task synchronization (e.g., avoiding deadlocks and maintaining a correct ordering of events). The tedious job of managing lower-level synchronization primitives such as mutex locks and condition variables often proves prone to human errors. In addition to ensuring correctness with respect to communication events, the software must expose the communication structure between tasks and create a task schedule that balances communication and computation. Situations of imbalance and poor scheduling result in idle cores and lost performance.

Memory Management. Multi-core architectures often distribute memory across the chip together with the cores and expose many of the memory details to the software designer. In some cases, the hardware maintains cache-coherency among the distributed memory banks, while other cases promote flexibility in how programs use the memory by leaving coherency optional. In either case, non-uniform memory access across the chip seems likely in future architectures due to the increasing latency of sending a signal from one end of the chip to another with respect to the clock frequency. As with communication, the exposure of lower-level memory details (e.g., data alignment, direct memory access (DMA) operations, limited local memory capacity) to the programmer increases the difficulty of creating correct and efficient programs.

Scheduling. With many cores and many tasks, it is important to schedule the tasks across the cores so that the load is balanced and the dependencies between tasks do not cause some cores to be idle frequently. The mapping from program to multi-core architecture includes not only tasks to cores, but also the mapping of the communication between tasks to the on-chip communication infrastructure, and the mapping of data to the memory (in the case of a distributed memory architecture). Mappings which increase data locality between tasks minimize inter-core data movement and improve communication overhead. However, increased locality sometimes comes at the cost of decreased concurrency, and vice versa.

Algorithms. Algorithm design must reflect the new constraints, and also break an application up into tasks that can be executed concurrently. Furthermore, it is not enough to design an algorithm with a good theoretical complexity. Because of the additional design constraints, optimizations and design decisions chosen for the sequential version of an algorithm may not be ideal in a parallel setting. For example, even though Bitonic Sort's  $O(n \log^2 n)$  complexity is less than ideal for sorting, the algorithm is often used for parallel sorting because the order of its compare-and-swap

operations is not data-dependent, and tasks are evenly sized. Thus, algorithm design must exercise an awareness of the parallel resources on which software will run.

Additionally, extremely large data sets frequently drive the need for increased performance over what single core architectures can offer. Algorithms must scale, both in terms of data size and the number of cores. Often, some parallel algorithms perform better for smaller data sets while others perform better for larger data sets. For example, the Fast Fourier Transform libraries written for the Cell SDK switch between different algorithms depending on the input data size.

### 1.3 Requirements

Performance, scalability, and programmer productivity are the three necessary components of any multi-core programming tool. The search for better performance, e.g., more floating-point operations per second, motivates the design of multi-core chips. Second, each generation of microprocessors increases the number of cores on a single chip. While most of the commercially available multi-cores today host only tens of cores or fewer, industry forecasts anticipate that future designs will include hundreds of cores [6]. Parallel programs must be able to continue to offer improved performance and scale with the number of cores, or they will obsolesce in a very short time. Finally, the complexity of designing a parallel program cannot scale linearly with the number of cores, or it will quickly become unmanageable. In particular, as the number of cores approaches the hundreds and thousands, most programmers will be unable to explicitly manage hundreds of independent tasks. However, programming tools can reduce this complexity, e.g., by letting a programmer write one task that is automatically expanded to hundreds.

#### 1.4 Hypothesis

My hypothesis is that the right level of abstraction can simplify the challenges of programming multi-core systems, while still providing an acceptable level of performance and scalability. A programming abstraction supplies a simplification or template that a programmer can follow in order to create a parallel program. An abstraction can be defined by (1) what it requires of the programmer, (2) what it exposes to the programmer about the underlying multi-core platform, and (3) what it hides. High-level abstractions, which hide more and expose less, are easier for the programmer, and thus improve design time and productivity, but offer less flexibility. In contrast, low-level abstractions, which hide less and expose more, provide a greater amount of flexibility and potentially better performance, but at the cost of the programmer's time. A good abstraction hides details that the compiler handles better than humans and exposes details that humans handle better than compilers to enable a productive collaboration that creates high-performance programs rapidly.

The question: What can be reasonably asked of a programmer? depends on the context of the application being written, and also on the experience and skill set of the programmer. In my experience as a programmer, I believe that reasonable expectations include an understanding of the structure and dependencies of an algorithm, what kind of data is used, and what role the data plays in the algorithm. Essentially, the programmer must master all of the application-dependent details. Details that are platform-dependent, such as explicit memory management and data alignment, are better left to compilers as well as issues that are common to all or many parallel programs such as mutual exclusion locks. Automated tools may also mitigate algorithm-specific aspects of the implementation when those aspects can be abstracted into patterns common to more than one algorithm, for example, a pattern for breaking an application up into independent subtasks. However, note that task granularity, i.e., the size of an application's subtasks, differs from the decomposition

pattern of an algorithm because task granularity depends on platform features such as the number of cores and their communication infrastructure.

#### 1.5 Thesis Outline

This dissertation presents techniques to enhance throughput performance on applications for multi-core platforms. These approaches make it easier to write parallel programs and to optimize them once they are written. I use a variety of programming abstractions throughout the dissertation, and endeavor to uncover the needs of applications by including many benchmarks implemented on real systems with the tools that I have developed. What unifies the different programming techniques and abstractions is that they expose the role of data in applications. While this might seem like a very general statement, the utilization of the on-chip interconnect and memory systems is very important in creating efficient programs. Moreover, the chips themselves are collections of computational, communication and memory units. At some level (perhaps not the level of the programming abstraction, but as a later result of a compilation) every program is converted to a collection of computational tasks, communication events and pieces of data in order to be mapped to the chips. The different abstractions expose this in different ways to the programmer. My thesis is that the key to unlocking the capabilities of multi-core platforms is the development of abstractions and optimizations which match the patterns of data movement in the applications with the inter-core communication capabilities of the platforms.

The rest of this section summarizes the chapters of the dissertation.

Chapter 2 surveys the landscape of multi-core hardware platforms, parallel programming models and parallel application design patterns, and shows that there is great diversity in each space. An efficient implementation of a program on a multi-core platform requires a synergy between these three areas, and application design is challenging since there are so many choices.

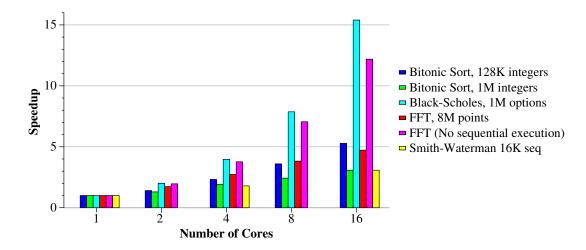

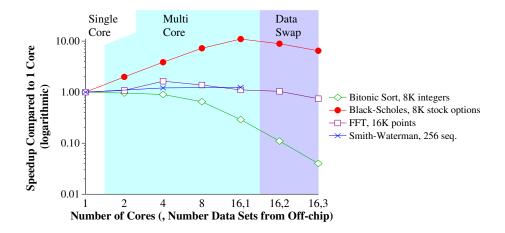

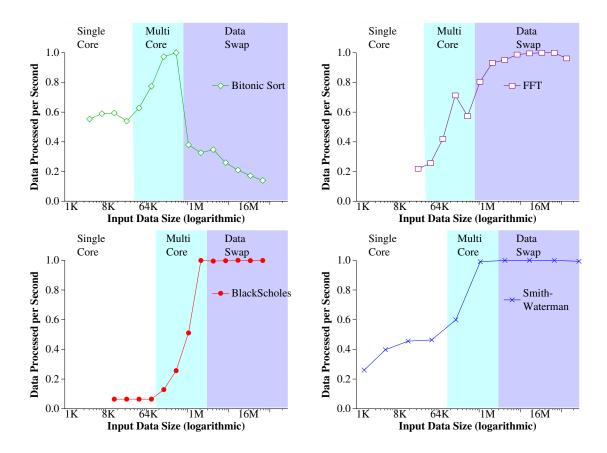

Chapter 3 measures a suite of five benchmarks on two high-end multi-core platforms, the Cell Broadband Engine processor and the NVIDIA GeForce 8800 GTX GPU. The benchmark tests make comparisons along two lines: first, they compare the two architectures; and second, they compare the performance of low-level vs. high-level programming abstractions. In particular, I compare platform-specific toolkits to RapidMind, a portable single program multiple data (SPMD) language. No platform emerges the winner; instead, each demonstrates strengths in certain areas and is found to be more suitable for certain benchmarks. Similarly, the SPMD abstraction proves very effective for some benchmarks and platforms, but less beneficial for others.

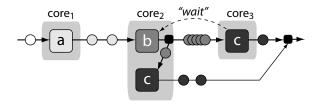

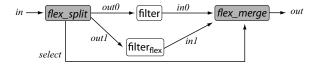

Chapter 4 presents flexible filters, a load-balancing optimization technique for stream programs. Flexible filters utilize the programmability of the cores in order to improve throughput of individual bottleneck tasks by "borrowing" resources from neighbors in the stream. An application-independent implementation of flexible filters is empirically evaluated on several stream benchmarks. The strength of flexible filters is in their simplicity. Their basic function is very straightforward, and they do not introduce heavy-weight runtime systems. Rather, all runtime load-balancing decisions are distributed among the cores and based on pipeline backpressure which is already present to prevent buffer overflows.

Chapter 5 proposes *Huckleberry*, a novel recursive programming abstraction based on data partitioning. Huckleberry abstracts the problem of breaking a program up into independent tasks, and instead requires explicit data partitioning with the Huckleberry partition library. Unlike stream programs, where all dependencies are the result of the stream structure (i.e., waiting to send or receive data along a communication channel), in recursive Huckleberry programs dependencies are detected dynamically at runtime and data movement is the result of the dependencies that are detected. Huckleberry's parallel code generator automatically parallelizes and

distributes recursive tasks which can locally detect dependencies between each other and synchronize accordingly.

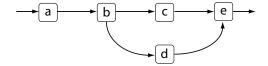

Chapter 6 proposes a unifying task graph framework for all data-driven programming abstractions together with a Petri net performance model that captures the behavior of programs. A task graph separates a program into tasks and the communication dependencies between those tasks.

Chapter 7 concludes and outlines future directions of possible research.

# Chapter 2

# Background

In order to effectively harness the resources of a multi-core system, there must be synergy among the architectural platform, the programming model and the application being executed. Great diversity characterizes all three of these key components. This chapter provides a survey of various platforms, programming models and benchmark applications in use today, several of which will be revisited in the experiments presented in later chapters.

### 2.1 Multi-Core Platforms

There are a wide range of multi-core platforms available both commercially and in research. These platforms vary based on the following architectural features:

• Cores. Homogeneous platforms replicate the same core across the chip, which reduces design time since architects only need to design the core once. Heterogeneous platforms specialize different cores to different types of tasks in order to optimize performance. The complexity of the cores is another facet of the design. Some platforms include a very large number of simple computing units, organizing them to accomplish complicated tasks; for example, GPUs and polymorphous platforms [35; 110].

- Memory Model. A multi-core platform's memory model may physically distribute level-1 caches and private scratch-pad memory banks to the cores, and the cores may share lower-level caches as well. Some multi-cores provide cache coherency while others leave coherency up to the software.

- Interconnect. The communication infrastructure on the chip is gaining importance in chip design as more computational units are added to the chip and need to communicate with each other. One example is a tiled packet-switched network; when one core wants to communicate with another, that core may route data across the chip through one of several possible paths depending on the current network traffic. Shared network resources maximize the use of overall bandwidth while reducing the space taken up by wires. There are many other interconnect possibilities. Compared to the communication networks of distributed parallel systems (e.g., clusters), on-chip interconnects have higher throughput and lower latency.

- Purpose. The degree to which a platform suits different application spaces also varies. At one extreme, general-purpose multi-cores can be used with the widest range of applications; however, multi-cores with a more narrow scope designed for a particular application space provide better performance in that space (e.g., Anton is specialized for large scale molecular dynamics simulations [114]).

The rest of this section examines four multi-core architectures representing heterogeneous architectures, graphics processing units, tiled architectures and generalpurpose architectures.

### 2.1.1 Heterogeneous Architectures: IBM/Sony/Toshiba Cell BE

The Cell Broadband Engine architecture is a heterogeneous multi-core system-onchip originally designed for high-performance embedded applications [71; 74; 98; 104]. Originally designed for the PlayStation 3 game console, Cell processors currently

Figure 2.1: Cell BE architecture.

| Cores        | 1 PowerPC, 8 SIMD                                  |

|--------------|----------------------------------------------------|

| Memory Model | 256KB private local memory per core; 512 L2 shared |

| Interconnect | 4 circuit-switched rings                           |

| Purpose      | gaming, high-performance computing                 |

Table 2.1: Cell BE details.

compose two thirds of the processors in IBM Roadrunner, the fastest supercomputer in the Top500's list in 2008 [8]. Both IBM and Mercury Computer Systems developed high-performance servers to host Cell chips, which are used for a wide variety of applications, from physics to finance [2; 85; 118]. Cell also shares many architectural similarities with chips used in Anton, including: 128-bit registers, SIMD operations, local scratch-pad memories and DMA transfers [114].

The Cell BE features eight synergistic processing elements (SPE) and one dual-threaded 64-bit PowerPC processor (PPE). Heterogeneous architectures specialize different cores to different tasks. In this case, the Cell architecture specializes the PPE

for sequential code, and the SPEs for vector operations. Each SPE contains a *single* instruction multiple data (SIMD) processor operating on entries of 128-bit registers; an operation may, for instance, organize a register as a vector of four 32-bit integers. Each SPE core operates on a local store memory of 256KB. Each core's local store holds both application data and code. The hardware does not supply cache coherency between the local stores; rather, software must manage data transfers between cores and to main memory via direct memory access (DMA) operations.

The Cell BE has a powerful on-chip network for inter-core communication, called the Element Interconnect Bus (EIB), made up of four circuit-switched rings [4; 79]. Two rings transfer data in one direction and two transfer data in the opposite direction, and the data arbiter only schedules data transfer circuits which take up half of a ring or less. Each ring supports up to three concurrent, non-overlapping data transfers. The EIB supports an on-chip communication bandwidth of over 200 GB/s, and the main memory uses an XDR RAM interface with a 25.6 GB/s bandwidth.

Much of the underlying architecture of Cell is exposed to the programmer, including the SIMD vector operations of the SPEs, the non-shared memory model, and the DMA data-transfer mechanisms. These features have made it notoriously difficult to program, but popular with programmers who seek extremely high performance because they can tune and optimize its resources at a very low level. I use the Cell in many of my experiments. In addition to being very flexible and tunable, the platform provides predictable performance results, in part because of the lack of hardware cache coherency operations and because the SPEs do not have complex branch prediction mechanisms.

#### 2.1.2 Graphics Processing Units: NVidia GeForce 8800 GTX

Graphics Processing Units are specialized for graphics applications and have massive floating-point computation performance. Though originally intended for applications such as 3D image rendering, GPUs are now programmable and able to be applied

Figure 2.2: GeForce 8800 architecture.

| Cores        | 128 "stream" processors clustered in 8 multiprocessors |

|--------------|--------------------------------------------------------|

| Memory Model | 16KB L1 per multiprocessor, L2 shared (size unknown)   |

| Interconnect | communicate through shared memory                      |

| Purpose      | graphics processing                                    |

Table 2.2: GeForce 8800 GTX details.

to any application that would benefit from their powerful computational abilities. Programming support (e.g., CUDA and OpenCL) is simultaneously being developed to open these platforms up to programmers who are not graphics specialists [33; 78], and general-purpose programming on GPUs (GPGPU) is gaining in popularity [84; 101]. The NVidia GeForce 8800 GTX is an example of a high-end programmable GPU with massive floating-point computation performance [35].

Figure 2.2 shows the high-level architecture of the GeForce 8800 GPU. It has 128 programmable processing units, called stream processors (SP), running at a clock rate of 1.5GHz. The GeForce 8800 architecture connects 768 MB of external memory

| Cores        | 64, tiled homogeneous                                 |

|--------------|-------------------------------------------------------|

| Memory Model | local L1 and L2 caches, virtual L3 combines L2 caches |

|              | (5MB on-chip cache total)                             |

| Interconnect | routed packet-switched network                        |

| Purpose      | stream processing, networking, multimedia             |

Table 2.3: TILE64 details.

to the SPs by several links with an aggregated maximum bandwidth of 86.4 GB/sec. The architecture divides the SPs into 16 groups, called multiprocessors, each with 8 SPs. The SPs in one group execute instructions in a SIMD fashion, i.e., at every clock cycle they execute the same instruction on different data. If a branch instruction changes the fetch direction of some, but not all of the SPs of the same group, the execution of instructions of the two different basic blocks will be serialized (leading some SPs to stall). The SPs of the same multiprocessor communicate with each other through on-chip shared memory. Global communication between processing units across multiprocessor boundaries is only possible through a shared location in the external memory. This limits the performance of applications that present complex communication patterns.

The large number of floating point units on GPUs offer massive parallelism and enable unconventional parallelization strategies. For example, the GPU thread manager (not shown in Fig. 2.2) may aggressively speculate by forking a separate thread for each branch, and then running them in parallel until it is known which branch is the correct one.

#### 2.1.3 Tiled Architectures: Tilera TILE64

Tilera's TILE64 architecture is an example of a tiled multi-core architecture. The Tilera Corporation descends from MIT's RAW processor project [36; 120]. Each tile

| Cores        | 2-8, homogeneous                                   |

|--------------|----------------------------------------------------|

| Memory Model | 32KB L1 instr, 32KB L1 data, 256KB L2 per core; 4- |

|              | 8MB L3 shared                                      |

| Interconnect | point-to-point                                     |

| Purpose      | general-purpose                                    |

Table 2.4: Core i7 details.

includes a processor, L1 and L2 caches, and a network switch. The tiled design and routed network interconnect simplify the design complexity (since the tiles which each include a core and network are replicas) and guarantee hardware scalability (since the percent of the chip devoted to the network scales linearly with the number of tiles). The RAW processor, an academic research platform, does not support hardware cache coherency, and can be programmed with C, Fortran and StreamIt [121]. The TILE64, in contrast, does provide hardware cache coherency and supports object-oriented C++ in addition to C. WaveScalar is another example of a tiled architecture [117].

#### 2.1.4 General-Purpose Architectures: Intel Core i7

General-purpose multi-core architectures build on single core general-purpose architectures, and include all of the platform features that are customarily available in their single core counterparts, including deeply pipelined cores, and multi-level caches with hardware cache coherency [92; 93]. These architectures support widely used thread libraries such as POSIX threads. In addition, though they tend to have fewer cores in comparison with GPUs and tiled architectures, the cores they do have are more powerful, performing very well on the sequential parts of applications.

### 2.2 Parallel Programming Models

Programming models (also called programming abstractions) for multi-core platforms exhibit as much variation as the architectures. Parallel programming has been used for many years in supercomputers, clusters, and multithreaded processors. What is different about multi-cores is the high-performance inter-core communication available to them. Inter-core communication achieves extremely low latency and high throughput compared to more traditional parallel systems, and thus parallel programming must be reconsidered with respect to the new balance of communication and computation present in these newer systems. Programming models may be realized as either a separate programming language (such as StreamIt [121]) or as a library or extension on top of an existing language (often C [14; 29; 47; 90]). As noted in the Chapter 1, I distinguish a programming model based on (1) what it requires of the programmer, (2) what its abstraction exposes to the programmer, and (3) what it hides.

A programming model might hide or expose aspects of the underlying architecture such as the number of cores, the memory model, and properties of the interconnect. More conceptually, the model may either hide or expose different kinds of parallelism. Data parallelism applies the same operation to many different data instances concurrently with no dependencies between them. Pipeline parallelism splits an operation into a sequence of pipelined tasks which may work at the same time on different data as the data passes through the pipeline. Last, task parallelism splits an operation into a data flow of tasks which may include complex control flow such as splits, joins, and feedback loops. Two tasks may work separately on different data that will later be joined in the final result.

Generally, high-level abstractions optimize programmer productivity, since they enable faster design and debugging of an application. But lower-level abstractions optimize performance, since they expose more of the capabilities of the underlying resources and are more flexible. However, although low-level abstractions may pro-

vide the *potential* for the best performance, that potential will remain untapped if programmers cannot manage the burden of orchestrating all of the lower-level details of an architecture. Thus, higher levels of abstraction may alleviate the increasing complexity of multi-core architectures. And high-level abstractions do not necessarily preclude high performance. In particular, the restrictions of domain-specific abstractions correspond exactly to the capabilities and resources that are *not* needed within the target domain. As a bonus, if the communication structure of an application from another domain does match that of an application within the target domain, then it may work equally well in that setting (e.g., GPUs for non-graphics applications [101]). A given parallel programming model will often match up well to a particular hardware platform (or family of platforms). Likewise, models also match better to certain applications than others, so that an implementation of an application is a three-way match between the application, the programming model, and the hardware architecture.

Each section below describes a general programming model, including languages and libraries that utilize that model. I do not attempt to be fully inclusive of the extensive literature on this topic, but to hit the main points, with an emphasis on data-driven models. That is, models that capture the data movement within an application. The prevalence across many applications of a focus on inter-task dependencies, the balance of communication and computation, and throughput-based performance metrics underscores the importance of data movement. Focusing on how models handle data movement also highlights similarities in the different models.

This survey of parallel programming models will begin with lower-level parallel-programming abstractions: threads and message passing, which are well developed, having been used for many years on parallel platforms other than multi-cores. I categorize them as "low-level" because they expose tools for composing concurrent tasks (mutex locks, messages, etc.) without providing abstraction to the programmer outside of the memory model: threads typically imply shared memory, while message

passing typically implies distributed memory. Higher-level parallel abstractions are sometimes built on top of these models.

#### 2.2.1 Threads

Many mainstream programming languages support threads, which provide one of the more expressive parallel programming models. Threads communicate through shared data structures, which abstract the underlying memory architecture from the programmer and work well for architectures with hardware cache coherency, but may not match well to other architectures. Threads traditionally require the programmer to explicitly program each parallel thread separately and to manage their synchronization, which can be cumbersome and error-prone. Synchronization primitives include locks, condition variables and semaphores. Many systems support POSIX threads (pthreads), the IEEE threads standard [19]. Several newer threading languages (Cilk, CUDA and Intel Threading Building Blocks) for multi-cores retain the parallel model of threads while abstracting away locks, synchronization, and other low-level details [14; 30; 66].

Cilk is a language specialized for dynamic, asynchronous parallelism [14]. The Cilk model expects the programmer to expose parallelism in an application while the compiler and run-time system manage performance details such as load balancing and managing the memory and inter-task communication. Cilk adds thread keywords such as *cilk*, *spawn* and *sink* to the C language. These keywords annotate C functions to expose parallelism. For example, the *cilk* keyword identifies parallelizable functions and the *spawn* keyword identifies subroutines that may potentially be forked off as separate threads. Removing all Cilk keywords produces a *C elision* of the code, i.e., a valid sequential C program. Thus, the programmer may annotate where the code may be forked as separate threads, but the runtime system manages the forking, joining and synchronization of threads.

The Compute Unified Device Architecture (CUDA) is a thread-based programming interface and environment developed by NVIDIA for general-purpose programming of its own GPUs [66]. The CUDA language abstracts the GPU hardware so that language features do not rely on a particular hardware configuration, and software may be easily ported to new GPU architectures. Programmers do not explicitly manage threads in a CUDA application; instead, they write with parallel operations through the CUDA API and the hardware thread manager handles the threading aspect of the program, which may reach thousands of threads. By handling the low level synchronization, the hardware guarantees that there are no deadlocks. For example, the SPMD CUDA operation SAXPY performs ax + y on two arrays x and y, with constant a. CUDA does expose tunability to programmers over the number of threads to be created and their division within and across the multiprocessor groups.

#### 2.2.2 Message Passing

Message passing is another widespread general-purpose approach, where parallel tasks communicate through messages which can act like communication pipes; this matches well to distributed memory architectures. Like threads, message passing also requires the programmer to be responsible for explicitly programming the parallel tasks. The Message Passing Interface (MPI) is a widely accepted standard for message passing that supports both point-to-point and collective communication operations [68]. The Cell Software Development Kit (SDK) supports Cell-specific message passing operations, and work has been done to implement the MPI standard on the Cell BE [100]; however the standard MPI library is not readily available on all multi-core architectures, for instance, on GPUs.

SHIM provides a deterministic concurrency message passing model which has been implemented for both shared memory and distributed memory multi-cores [43; 125]. SHIM's model guarantees that communication events between tasks occur in a

deterministic order, eliminating data races and simplifying the debugging of concurrency errors such as deadlocks.

#### 2.2.3 Graphics Languages

The Open Graphics Library (OpenGL) is a language specification for programming graphics hardware [112]. It is specialized to graphics functions, in particular, rendering into a framebuffer, and many of its function calls enable the programmer to draw different types of 2D and 3D objects such as lines and polygons.

The Open Computing Language (OpenCL) is a general-purpose language intended to help programmers take advantage of the impressive computing capabilities of GPUs for non-graphics applications [78]. Unlike CUDA, which only supports the family of NVIDIA GPUs, OpenCL provides an open standard, and supports a variety of heterogeneous systems, including non-GPU systems. In OpenCL, the programmer creates kernels, programs portable across OpenCL devices and host programs that run on a specific host. Before a kernel executes, the OpenCL runtime model defines the index space of a data set for each kernel instance, and breaks the index space up into separate work-groups. At runtime, the host executes a variety of operations, including kernel operations on work-groups, memory operations and synchronization operations. The flexibility of the programming model allows for different types of parallelism including data parallelism as well as task parallelism.

#### 2.2.4 SPMD

Single Program Multiple Data (SPMD) programming exploits the data-parallelism of an application by applying the same code in parallel on separate data, for example, the elements of an array. A pure SPMD operation involves no inter-core communication. Therefore this style of parallel programming has been applied to many parallel systems that do not have low latency inter-core communication, including wide-area distributed ones like SETI@home. Several startup ventures have designed

commercial SPMD programming languages in recent years for multi-core platforms (e.g., RapidMind [90] and PeakStream, acquired by Intel and Google, respectively).

RapidMind grew out of Sh, a tool for programming GPUs intended to both unify shader programs with their host programs and provide a more general-purpose programming platform for GPUs than was previously available [89]. RapidMind provides C++ libraries that add a few new types: Array, Value, and Program. A programmer may invoke a RapidMind program with a RapidMind array as input, and the program will execute separately on each array element. For example, consider the following snippet of C++ code:

```

main {

float a[N], b[N];

// ... initialize a[] and b[] ...

for(int i=0; i<N; i++) {

a[i] *= b[i];

}

}</pre>

```

The code above is rewritten in RapidMind by first creating a RapidMind Program, that can be called as a subroutine:

```

Program vector_mult = BEGIN {

In<Value1f>a;

In<Value1f>b;

a = a*b;

}

```

where Value1f indicates that a and b are each floats (Value4f would indicate a vector of four floats). Next, vector\_mult replaces the for loop, and a[] and b[] are defined with RapidMind types.

```

main {

Array<1,Value1f> A(N);

Array<1,Value1f> B(N);

// ... initialize values ...

A = vector_mult(A,B);

}

```

RapidMind automatically parallelizes and distributes the program over the target platform, hiding platform-specific thread management and data-transfer operations from the programmer. RapidMind also supports reduction functions, multi-dimensional Array types, and data views such as shifting or striping for manipulating the arrays.

#### 2.2.5 Stream Programming

Stream processing captures the data flow model of computation, and applies to a wide range of applications including high-performance embedded applications, signal processing, image compression, and continuous database queries [20; 42; 113]. The stream processing abstraction decomposes an application into a sequence of data items (tokens) and a collection of tasks (referred to as filters or kernels) that operate upon the stream of tokens as they pass through them. Filters communicate with each other explicitly by exchanging the tokens through point-to-point communication channels. Stream programs expose pipeline, data and task parallelism. StreamIt, a language from the research community, and Gedae, a commercial language, are described below.

StreamIt is a stream language and compiler developed at MIT [121]. A StreamIt program comprises stream tasks, called *filters*, which accommodate a single input and a single output and use *push*, *pop*, and *peek* operations to interact with the input and output data streams. The language also provides control flow filters to allow for splits and joins in the stream. StreamIt has been used as a foundation for research in compiler analysis and optimizations [3; 58; 122]. Other research stream

projects include the Brook stream language and the Imagine stream processor and programming model [18; 76].

Gedae [54] is a commercial stream language specialized for embedded signal processing applications. Similar to StreamIt, a Gedae application also comprises stream tasks, called *blocks* in Gedae, which communicate with each other through communication pipes. Gedae supports blocks that have more than one input and output stream. During runtime, a typical Gedae block will fire, consuming a fixed number of data tokens from its input and producing a fixed number on its output. The language also provides support for nondeterministic and dynamic streams where the number of tokens consumed or produced may vary.

Chapter 4 explores the stream abstraction further with flexible filters, a load-balancing optimization method for stream programs.

#### 2.2.6 Recursive Parallel Programming