# ESCUELA SUPERIOR DE INGENIERÍA

# **COMPUTER ENGINEERING**

# FPGA BASED EMBEDDED SYSTEM TO CONTROL AN ELECTRIC VEHICLE AND THE DRIVER ASSISTANCE SYSTEMS

Mario Márquez Luciano

June 5, 2014

# ESCUELA SUPERIOR DE INGENIERÍA

### COMPUTER ENGINEERING

# FPGA BASED EMBEDDED SYSTEM TO CONTROL AN ELECTRIC VEHICLE AND THE DRIVER ASSISTANCE SYSTEMS

- Departament: Systems and Automation Engineering, Electronic and Electronic Technology

- Supervisor: M<sup>a</sup> Ángeles Cifredo Chacón

- Author: Mario Márquez Luciano

Cádiz, June 5, 2014

Mario Márquez Luciano

## Aknowledgments

I would like to aknowledge the continuous support of my family during my years of student. Also I would like to thank the people of VDE group for giving me the oportunity of working in the E-Performance Kart. Of course I have to say thank you to my supervisors at the Karlsruhe Institut of Technoly, Michael Dreschmann and Falco Bapp, and to my supervisor at the University of Cádiz, Maria de los Ángeles Cifredo Chacón. And last but not less important to all my lifelong friends and to those who shared with me an unforgettable Erasmus experience in Karlsruhe.

# License

This document has been published under License GFDL 1.3 (GNU Free Documentation License). License terms are included at the end of this document.

Copyright (c) 2014 Mario Márquez Luciano.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.3 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

# List of Abbreviations

| ANSI  | American National Standards Institute             |

|-------|---------------------------------------------------|

| API   | Application Programming Interface                 |

| ASIC  | Application-specific Integrated Circuit           |

| AXI   | Advanced eXtensible Interface                     |

| CAN   | Controller Area Network                           |

| CU    | Control Unit                                      |

| DC    | Death Current                                     |

| DSP   | Digital Signal Processor                          |

| EDK   | Embedded Development Kit                          |

| FPGA  | Field Programmable Gate Array                     |

| IPC   | Industrial Personal Computer                      |

| IRT   | Isochronous Real-Time                             |

| ISE   | Integrated Software Environment                   |

| ITIV  | Institut für Technik der Informationsverarbeitung |

| KIT   | Karlsruher Institute für Technologie              |

| LED   | Light-emitting Diode                              |

| LUT   | Look-up Table                                     |

| PLB   | Processor Local Bus                               |

| POSIX | Portable Operating System Interface               |

| RAM   | Random Acess Memory                               |

| RPM   | Revolutions per minute                            |

| SDK   | Software Development Kit                          |

| TCS   | Traction Control System                           |

| VDE   | Verband der Elektrotechnik                        |

| VHDL  | VHSIC Hardware Description Language               |

| VHSIC | Very High Speed Integrated Circuit                |

| •     |                                                   |

# Contents

| 1 | Intr | oductio  | n                                            | 1    |

|---|------|----------|----------------------------------------------|------|

|   | 1.1  | Overvi   | iew                                          | 1    |

|   | 1.2  | Motiva   | ation                                        | 1    |

|   | 1.3  | Startin  | ng Point                                     | 2    |

|   | 1.4  | Proble   | em definition                                | 2    |

|   | 1.5  | Schedu   | ule                                          |      |

|   |      | 1.5.1    | System analysis                              |      |

|   |      | 1.5.2    | Hardware development                         |      |

|   |      | 1.5.3    | Software development                         |      |

|   |      | 1.5.4    | Verification process and tests               |      |

|   |      | 1.5.5    | Gantt chart                                  | 4    |

| 2 | The  | VDE K    | KART                                         | 5    |

|   | 2.1  | Overvi   | iew                                          | 5    |

|   | 2.2  | Main c   | components                                   | 5    |

|   |      | 2.2.1    | Siemens IPC 427                              | 5    |

|   |      | 2.2.2    | Motors                                       | 7    |

|   |      | 2.2.3    | Converters                                   | 8    |

|   |      | 2.2.4    | Control units                                | 8    |

|   |      | 2.2.5    | Wheel speed sensors                          | 8    |

|   |      | 2.2.6    | Supercapacitors                              | . 9  |

|   |      | 2.2.7    | Safety                                       | . 9  |

|   |      | 2.2.8    | Information leds                             | . 11 |

|   | 2.3  | Function | ions                                         | 12   |

|   |      | 2.3.1    | Torque Vectoring                             |      |

|   |      | 2.3.2    | Traction Control System                      | 13   |

|   |      | 2.3.3    | Brake balance                                | . 14 |

|   |      | 2.3.4    | Offline telemetry                            | . 14 |

| 3 | Invo | lved Te  | echnologies                                  | 15   |

|   | 3.1  | FPGA     |                                              | . 15 |

|   | 3.2  | ITIV's   | s custom Xilinx Spartan 6 board for VDE Kart | . 16 |

|   |      | 3.2.1    | Spartan 6 family                             | . 16 |

|   |      | 3.2.2    | Board features                               |      |

|   | 3.3  | Hardw    | vare description languages                   | . 18 |

|   |      | 3.3.1    | VHDL                                         | 18   |

|   |            | 3.3.2 Verilog                                                 |

|---|------------|---------------------------------------------------------------|

|   | 3.4        | Programming languages                                         |

|   |            | 3.4.1 C programming language                                  |

|   | 3.5        | CAN-bus                                                       |

|   |            | 3.5.1 Features                                                |

|   |            |                                                               |

| 4 | Desi       | gn of the system 21                                           |

|   | 4.1        | Hardware                                                      |

|   |            | 4.1.1 Xilinx Microblaze                                       |

|   | 4.2        | Sotfware                                                      |

|   |            | 4.2.1 Xilinx Standalone                                       |

|   |            | 4.2.2 Xilinx Xilkernel                                        |

|   | 4.3        | Restrictions                                                  |

|   |            | 4.3.1 Memory                                                  |

|   | 4.4        | Selected Software platform                                    |

|   | 4.5        | Advantages                                                    |

|   | 4.6        | Outlook                                                       |

| _ | <b>TT</b>  | lware development 29                                          |

| 5 |            |                                                               |

|   | 5.1        |                                                               |

|   | 5.2        | 5.1.1       Configuration       29         Block RAM       30 |

|   | 5.2        |                                                               |

|   |            |                                                               |

|   | 5.3        | 5.2.2       Configuration       31         PLB Bus       32   |

|   | 5.3<br>5.4 | Wishbone Bus         33                                       |

|   | 5.4<br>5.5 | PLB to WB Bridge         34                                   |

|   | 5.6        | PLB Wrapper                                                   |

|   | 5.0        | 5.6.1 Wrapper template generation                             |

|   |            | 5.6.2 Modifications to the template                           |

|   |            | 5.6.3 Peripherals to have the PLB wrapper                     |

|   | 5.7        | CAN transceiver                                               |

|   | 5.7        | 5.7.1 OpenCores CAN transceiver core                          |

|   |            | 5.7.2 Wrapper                                                 |

|   | 5.8        | Torque vectoring         38                                   |

|   | 5.0        | 5.8.1 Analysis                                                |

|   |            | 5.8.2 Design                                                  |

|   |            | 5.8.3 Implementation                                          |

|   |            | 5.8.4 Performance                                             |

|   | 5.9        | Traction Control System                                       |

|   | 0.7        | 5.9.1 Analysis                                                |

|   |            | 5.9.2 Design                                                  |

|   |            | 5.9.2 Design                                                  |

|   |            | 5.9.5 Impendentation                                          |

|   | 5.10       | Inputs/Outputs                                                |

|   | 2.10       | 5.10.1 Digital Inputs                                         |

|   |            |                                                               |

|   |      | 5.10.2                 | Digital Outputs            | 49       |

|---|------|------------------------|----------------------------|----------|

|   |      | 5.10.3                 | Analog Inputs              | 52       |

|   | 5.11 | Power                  | on reset                   | 57       |

|   |      | 5.11.1                 | Analysis                   | 57       |

|   |      | 5.11.2                 | Design                     | 57       |

|   |      | 5.11.3                 | Implementation             | 59       |

|   | 5.12 | System                 | n Timer                    | 59       |

|   | 5.13 | Interru                | pt Controller              | 59       |

|   | 5.14 | LEDS                   |                            | 59       |

|   |      | 5.14.1                 | GPIO                       | 60       |

|   | 5.15 | UART                   |                            | 60       |

|   |      | 5.15.1                 | XPS Uartlite               | 60       |

|   |      | 5.15.2                 | STDIO UART                 | 61       |

|   |      | 5.15.3                 | Communication UART         | 61       |

|   |      | 5.15.4                 | UART Enable GPIO           | 62       |

|   | 5.16 | Clock g                | generators                 | 62       |

|   |      | 5.16.1                 | System Clock Generator     | 62       |

|   |      |                        | •                          | 63       |

|   |      |                        | *                          | 65       |

|   | 5.17 |                        |                            | 66       |

|   |      |                        |                            | 67       |

|   |      |                        | -                          |          |

| 6 | Cont | trol Soft              | tware development          | 69       |

|   | 6.1  | System                 | n requirements             | 69       |

|   |      | 6.1.1                  | Functional requirements    | 69       |

|   |      | 6.1.2                  | Information requirements   | 70       |

|   |      | 6.1.3                  |                            | 70       |

|   | 6.2  | Softwa                 | re Life model              | 70       |

|   |      | 6.2.1                  | First iteration            | 70       |

|   |      | 6.2.2                  | Second iteration           | 71       |

|   |      | 6.2.3                  | Third iteration            | 71       |

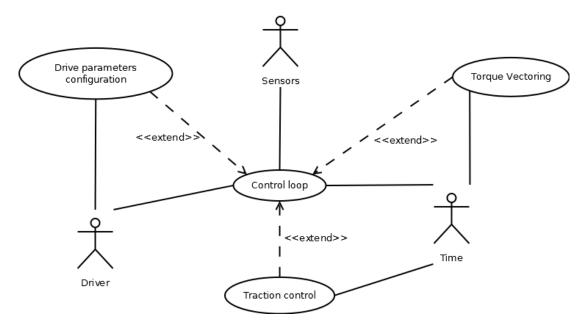

|   | 6.3  | Analys                 | sis                        | 71       |

|   |      | 6.3.1                  | Use Case model             | 71       |

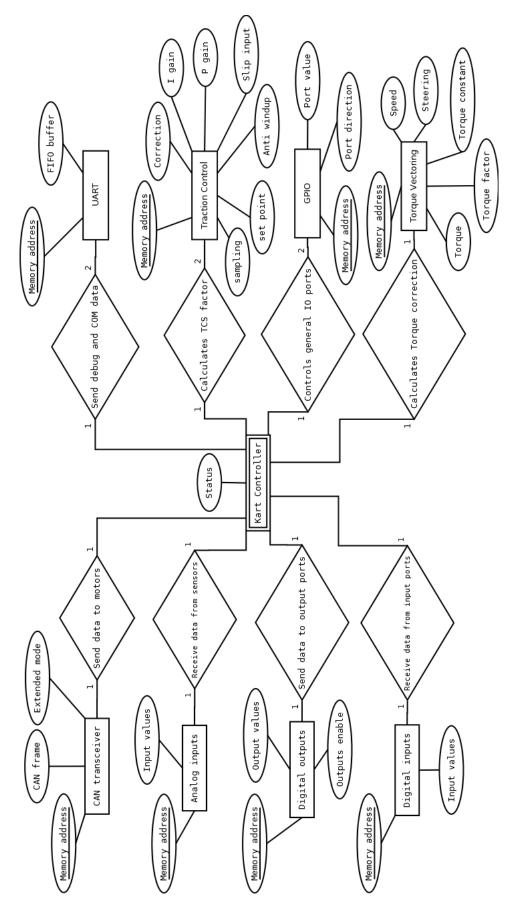

|   |      | 6.3.2                  | Data model                 | 74       |

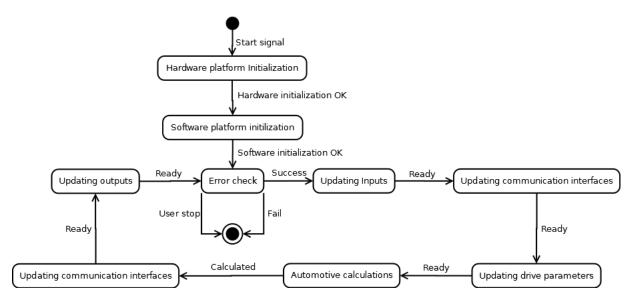

|   |      | 6.3.3                  | Behaviour model            | 77       |

|   |      | 6.3.4                  | External interfaces        | 78       |

|   | 6.4  | Design                 | 1                          | 80       |

|   |      | 6.4.1                  | System architecture        | 80       |

|   |      | 6.4.2                  | Behaviour model            | 81       |

|   | 6.5  | Implen                 | nentation                  | 84       |

|   |      | 6.5.1                  |                            | 84       |

|   |      | 6.5.2                  |                            | 85       |

|   |      | (52)                   | -                          | 05       |

|   |      | 6.5.3                  | Xilkernel Operating System | 85       |

|   |      | 6.5. <i>3</i><br>6.5.4 |                            | 83<br>87 |

| 7  | Test | Software development                                 | 89  |

|----|------|------------------------------------------------------|-----|

|    | 7.1  | Limitations and adopted solution                     | 89  |

|    | 7.2  | Industrial PC software                               | 89  |

|    |      | 7.2.1 RMOS3                                          | 89  |

|    |      | 7.2.2 UART communication                             | 90  |

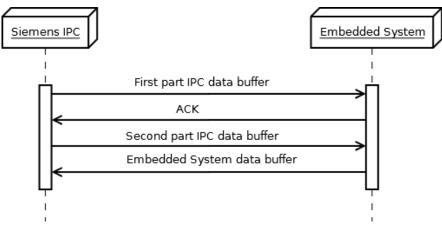

|    |      | 7.2.3 IO configuration                               | 91  |

|    |      | 7.2.4 UART timing                                    | 92  |

|    |      | 7.2.5 Synchronization switch                         | 92  |

|    |      | 7.2.6 Telemetry information                          | 92  |

|    | 7.3  | Test Software                                        | 92  |

|    |      | 7.3.1 Multi-threading                                | 92  |

|    |      | 7.3.2 Communication protocol                         | 93  |

| 8  | Test | and Validation                                       | 95  |

| Ū  | 8.1  | Hardware                                             | 95  |

|    | 011  | 8.1.1 Simulator                                      | 95  |

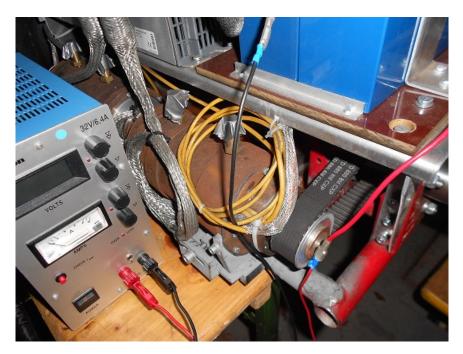

|    |      | 8.1.2 Testing platform                               | 96  |

|    | 8.2  | Software                                             | 96  |

|    |      | 8.2.1 Testing platform                               | 96  |

|    |      | 8.2.2 Modules                                        | 96  |

|    |      | 8.2.3 Integration                                    | 97  |

|    | 8.3  | System                                               | 97  |

|    | 0.0  | 8.3.1 Traction control                               | 97  |

|    |      | 8.3.2 Torque vectoring                               | 97  |

|    |      | 8.3.3 Testing environment                            | 99  |

| 9  | Con  | clusions 1                                           | .01 |

|    | 9.1  | Technical valoration                                 |     |

|    | 9.2  | Personal valoration                                  |     |

|    | 9.3  |                                                      | 02  |

|    | 7.5  |                                                      | 02  |

| A  | Deve | elopment tools 1                                     | .05 |

| GI |      |                                                      | 13  |

|    |      | PPLICABILITY AND DEFINITIONS                         |     |

|    | 2. V | ERBATIM COPYING 1                                    | 15  |

|    |      | OPYING IN QUANTITY   1                               |     |

|    |      | ODIFICATIONS                                         |     |

|    |      | OMBINING DOCUMENTS                                   |     |

|    |      | OLLECTIONS OF DOCUMENTS                              |     |

|    | 7. A | GGREGATION WITH INDEPENDENT WORKS                    | 18  |

|    | 8. T | RANSLATION                                           | 18  |

|    |      | ERMINATION                                           |     |

|    |      | FUTURE REVISIONS OF THIS LICENSE                     |     |

|    |      | RELICENSING                                          |     |

|    | ADI  | DENDUM: How to use this License for your documents 1 | 19  |

# **List of Figures**

| 1.1                                                                                             | Gantt chart                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1                                                                                             | VDE E-Performance Kart   6                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2                                                                                             | VDE E-Performance Kart System block diagram       6         Si       IDC 427                                                                                                                                                                                                                                                                                                                                        |

| 2.3                                                                                             | Siemens IPC 427         7           Siemens electric Motors         8                                                                                                                                                                                                                                                                                                                                               |

| 2.4<br>2.5                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.5                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.0                                                                                             | Lenor+Bauer speed sensor10E-Kart supercapacitors1010                                                                                                                                                                                                                                                                                                                                                                |

| 2.7                                                                                             | Custom security board                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.9                                                                                             | LEDs panel                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.7                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1                                                                                             | Xilinx's FPGA chip                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2                                                                                             | ITIV's Spartan 6 custom board                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.1                                                                                             | Microblaze Core block diagram                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2                                                                                             | Harvard Architecture                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3                                                                                             | Xilkernel Modules                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.4                                                                                             | System outlook                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1                                                                                             | Microblaze configuration in EDK                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.2                                                                                             | Microblaze System memory bus                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3                                                                                             | Xilinx PLB bus33Wishbone bus34                                                                                                                                                                                                                                                                                                                                                                                      |

| E 4                                                                                             | 34                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.5                                                                                             | PLB to Wishbone bridge                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.5<br>5.6                                                                                      | PLB to Wishbone bridge35EDK custom peripheral directory structure36                                                                                                                                                                                                                                                                                                                                                 |

| 5.5<br>5.6<br>5.7                                                                               | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38                                                                                                                                                                                                                                                                                                                     |

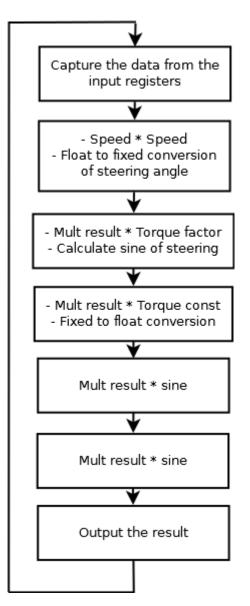

| 5.5<br>5.6<br>5.7<br>5.8                                                                        | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41                                                                                                                                                                                                                                                                        |

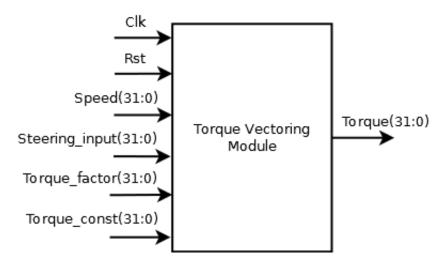

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                                 | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42                                                                                                                                                                                                                                          |

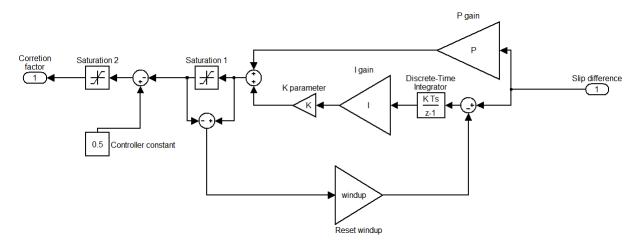

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                         | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42Simulink model of the Traction Control System43                                                                                                                                                                                           |

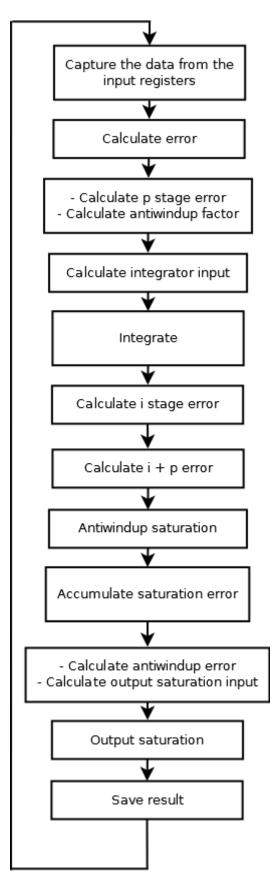

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                 | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42Simulink model of the Traction Control System43Flow Diagram of the Traction Control System module44                                                                                                                                       |

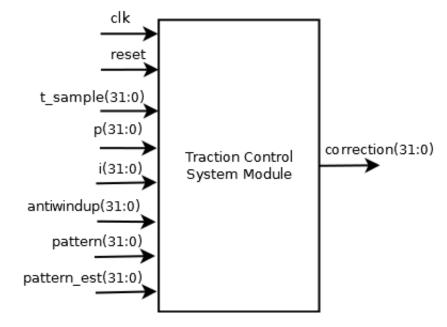

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                                         | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42Simulink model of the Traction Control System43Flow Diagram of the Traction Control System module44Traction Control System module core45                                                                                                  |

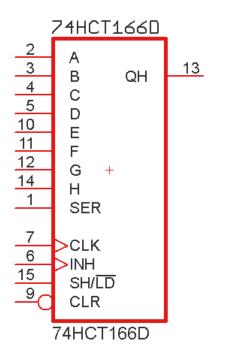

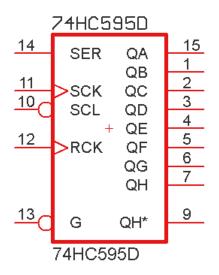

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                                 | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42Simulink model of the Traction Control System43Flow Diagram of the Traction Control System module44Traction Control System module4574HCT166D shiff register47                                                                             |

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14                         | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42Simulink model of the Traction Control System43Flow Diagram of the Traction Control System module44Traction Control System module4574HCT166D shitf register47                                                                             |

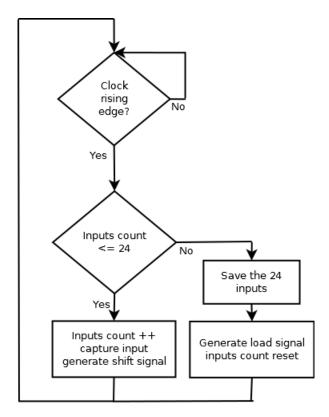

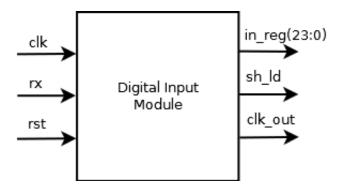

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15                 | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42Simulink model of the Traction Control System43Flow Diagram of the Traction Control System module44Traction Control System module core4574HCT166D shitf register47Flow Diagram of the Digital Inputs module48                             |

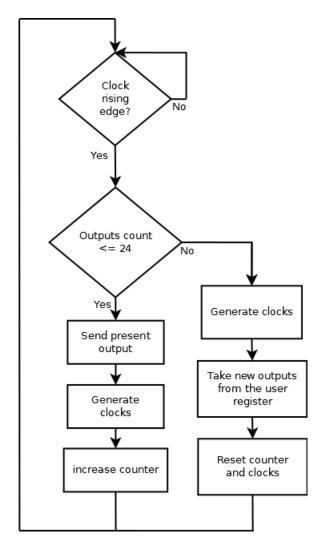

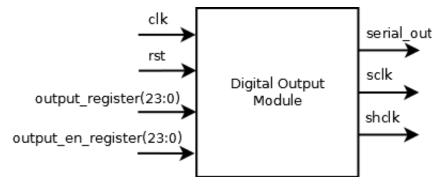

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17 | PLB to Wishbone bridge35EDK custom peripheral directory structure36CAN transceiver peripheral38Flow Diagram of the Torque Vectoring module41Torque Vectoring module core42Simulink model of the Traction Control System43Flow Diagram of the Traction Control System module44Traction Control System module core4574HCT166D shift register47Flow Diagram of the Digital Inputs module48Digital Inputs module core48 |

| 5.19 | AD7927 analog to digital converter           | 53  |

|------|----------------------------------------------|-----|

| 5.20 | AD7927 power up                              | 53  |

| 5.21 | AD7927 configuration and operation mode      | 54  |

|      | Flow Diagram of the Analog inputs module     | 55  |

| 5.23 | Analog inputs module core                    | 56  |

|      | Flow Diagram of the Power on Reset core      | 58  |

| 5.25 | Power on Reset core                          | 58  |

|      | Xilinx GPIO                                  | 60  |

| 5.27 | XPS UARTlite core                            | 61  |

| 5.28 | Clock Generator core                         | 62  |

| 5.29 | Flow Diagram of the Peripheral Clock Divider | 64  |

| 5.30 | Peripheral Clock Generator core              | 64  |

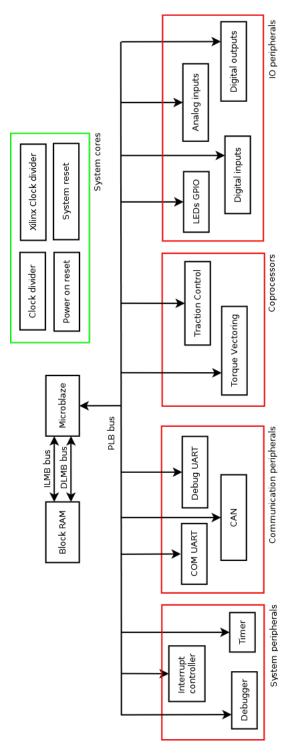

| 5.31 | Embedded System                              | 67  |

|      |                                              |     |

| 6.1  | Control software Use Case diagram            | 72  |

| 6.2  | Control software Data model diagram          | 75  |

| 6.3  | Control software State model diagram         | 78  |

| 6.4  | Control software Packet diagram              | 81  |

| 6.5  | DFD level 0                                  | 81  |

| 6.6  | DFD level 1                                  | 82  |

| 6.7  | DFD level 2 initialization                   | 82  |

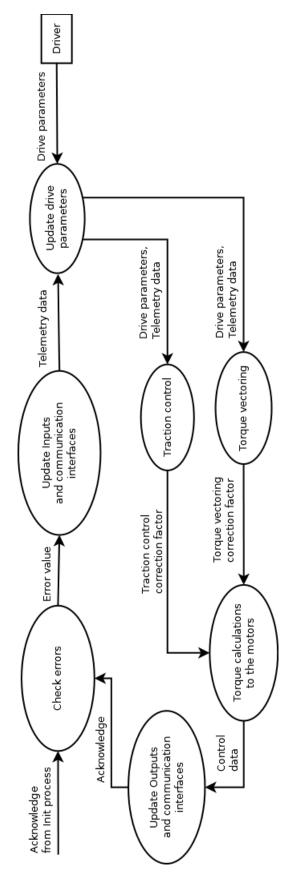

| 6.8  | DFD level 2 control                          | 83  |

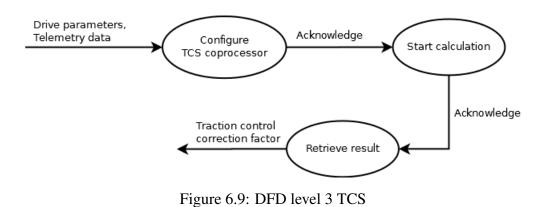

| 6.9  | DFD level 3 TCS                              | 84  |

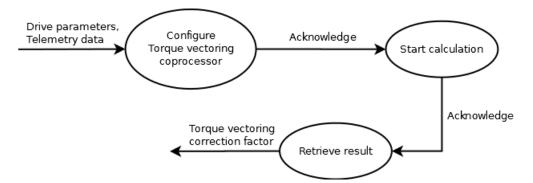

|      | DFD level 3 Torque Vectoring                 | 84  |

| 6.11 | Xilkernel configuration                      | 87  |

| 7.1  | Communication protocol                       | 94  |

| 0.1  |                                              | 00  |

| 8.1  | Traction Control simulation                  | 98  |

| 8.2  | Torque Vectoring simulation                  | 98  |

| 8.3  | Garage testing environment                   | 99  |

| 8.4  | Street testing set up                        |     |

| 8.5  | Street testing environment                   | 100 |

# **List of Tables**

| 2.1<br>2.2 |                              | 13<br>13 |

|------------|------------------------------|----------|

| 3.1<br>3.2 | 1                            | 17<br>18 |

| 4.1        | Soft processors              | 21       |

| 5.1        |                              | 40       |

| 5.2        |                              | 40       |

| 5.3        | <i>y b</i> 1                 | 43       |

| 5.4        |                              | 45       |

| 5.5        |                              | 49       |

| 5.6        |                              | 52       |

| 5.7        | Analog Inputs module signals | 56       |

| 5.8        |                              | 57       |

| 5.9        |                              | 58       |

| 5.10       |                              | 61       |

| 5.11       |                              | 62       |

| 5.12       |                              | 63       |

|            |                              | 65       |

| 5.14       |                              | 65       |

| 5.15       |                              | 65       |

|            |                              | 66       |

|            |                              | 66       |

| 6.1        | Actors of the system         | 71       |

| 6.2        | Entity: Digital Inputs       | 76       |

| 6.3        | Entity: Digital Outputs      | 76       |

| 6.4        |                              | 76       |

| 6.5        |                              | 76       |

| 6.6        |                              | 76       |

| 6.7        |                              | 77       |

| 6.8        | -                            | 77       |

| 6.9        | Entity: Torque Vectoring     | 77       |

| 6.10       |                              | 79       |

| 6.11       |                              | 79       |

|            | c                            | 85       |

| 6.13 | Control software loop shared data       | 85 |

|------|-----------------------------------------|----|

| 7.1  | Parameters to the RmIO Siemens function | 90 |

| 7.2  | Test software shared data               | 93 |

| 7.3  | Shared data format                      | 94 |

# **Chapter 1**

# Introduction

### 1.1 Overview

Several competitions deal with the area "electrification" and many engineers are currently researching this topic. In this background, the electric automobile exhibition in Aschaffenburg, Germany, takes place at the same time as a contest to award the best idea and implementation of electrification. This competition is aimed at students and student groups who have made a project in their own work. It can be an existing vehicle to be converted to electric drive or a whole new can be created. They will be announced alongside with the latest technical ideas in area electrification and tested in a 50 meters acceleration sprint [1].

Over the course of the past two and a half years and in collaboration with various institutes of the electrical and mechanical engineering faculties, the VDE<sup>1</sup> converted a go-kart to have a full- electrical engine. The project focuses on sportive and dynamic driving characteristics. Thus, a racing kart was chosen as platform to implement various applications of high-profile sports racing, e.g. torque vectoring and a traction control system. The team was able to complete a sprint race victoriously in fall of 2012.

This project shows that electric mobility is dynamic and fun and that having fun and to preserve costs and resources are not mutually exclusive. Many disadvantages of the conventional combustion engine don't play a role in the E-mobility (revs, turbo lag, oil changes) [1]. Because of this it is said that E-mobility is the future of the automotive industry and for testing purpouses racing is the best laboratory in order to transfer this advantages to street cars.

### **1.2** Motivation

Despite the kart has won the contest in his first participation in the Aschaffenburg exhibition and all the control systems of the kart work perfectly, the VDE group aims to improve the performance of their kart and because of this the present Master Thesis takes place. But not only improving the performance in terms of pure speed is important in this kind of project but also improving the overall efficiency of the system by developing smaller hardware, more

<sup>&</sup>lt;sup>1</sup>German electrical engineering association

efficient software and making them more generic, manufacter independent and easy to use. This Master Thesis could be seen as a perfect example of what hardware-software codesign is.

#### **1.3 Starting Point**

At the beginning of this Master Thesis, the VDE E-Kart was delivered as he had won the competition with the Siemens control unit, motors and converters, which means that it was necesary an initial analysis in order to gather requirements for the new system.

The vehicle's central data node, hosting the traction control system and remaining control implementations, is an industrial PC by SIEMENS (IPC 427C), running the real-time operating system RMOS3. To reduce weight while achieving equal or possibly higher processing speed, the IPC will be replaced by a custom FPGA board developed at ITIV institute for hosting the implementation of an embedded system including the software control part.

The board was in development in August 2013 and after exhaustive tests was delivered ready for use.

#### **1.4 Problem definition**

The main aim of this work is the design and implementation of an embedded system and his software part in order to replace the existing Siemens IPC unit, solving the problems described in the previous section and adding new functionalities to the system. All these new functionalities are developed to be the new basis control electronic for a future new version of the kart for long runs instead of short sprint races, which is going to be developed and constructed in the next years. The development of this Master Thesis has been divided in the following different tasks:

- Sensor data processing

- Acquisition and processing of all four wheel speeds for use in vehicle dynamics calculations: traction control and torque vectoring

- Acquisition, processing and output of further analog and digital signals, for instance throttle, steering, acceleration and dashboard switches

- Implementation of traction control system and torque vectoring using VHDL

- Direct VHDL coding based on matlab models

- Lightweight, FPGA-adjusted implementation

- Implementation of peripherals in VHDL to control the digital inputs and outputs and analog inputs

- Standard hardware interface for the peripherals, which simplifies the process of adapting them to any type of architecture and buses (PLB, Wishbone, AXI)

- Standard and plattform independent drivers for all the peripherals

- Equal or better performance than the previous system

- Structuring and simplification of code

- Use of a simpler and faster programming language (C instead of C++) to write low level drivers and control tasks

- Change of the Programming paradigm from Object Oriented Programming to Procedural Programming

- Abstraction layer for the peripherals's firmware in order to get plattform independence

- Well documented source code using documentation tools (Doxygen)

- Connection of converters (power electronics devices for motor control) via CAN bus

- Visualization and documentation of results

# 1.5 Schedule

In this section the different phases of this thesis are explained in detail and also a schedule plan is given.

#### 1.5.1 System analysis

In this stage, the actual system was analyzed, which means both Hardware and Software and all the requirements (hardware and software) for the future system were gathered. The next three stages compose the development of the system itself and were parallel executed.

#### 1.5.2 Hardware development

In this stage, the embedded system including all custom the components were developed based on the gathered requirements of the previous stage. This stage is known as the Hardware/Software codesign.

#### 1.5.3 Software development

The firmware of the developed peripherals and the control software were developed at this stage. The firmware development took place right after the hardware design worked properly in the simulator meanwhile the control software development had to wait until the hardware platform was tested and stable.

#### **1.5.4** Verification process and tests

All the developed components were tested exhaustively using the available tools for that, in this case the hdl simulator and custom test benchs. This stage took place parallel with both hardware and software development stages and was necessary in order to debug and improve the developed components.

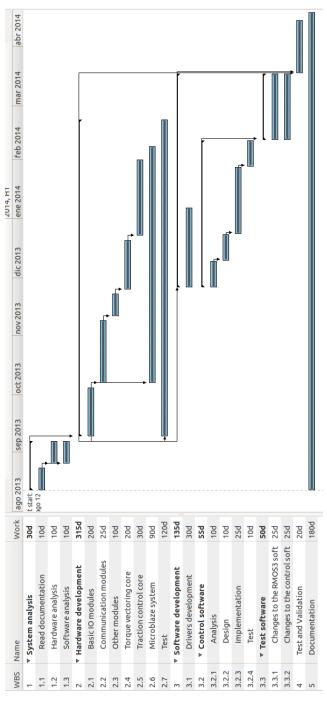

Figure 1.1: Gantt chart

Figure 1.1 shows the Gantt chart of this Thesis including all the previously explained phases. As can be seen, the total duration was 8 months, beginning in mid-August 2013 and ending in mid-April 2014.

# Chapter 2 The VDE KART

In this chapter, the VDE-Kart and all of the technologies involved are described so as to have a general idea of the requirements for the future system developed in this Master Thesis, which is going to replace the actual system. All these new functionalities are developed to be the new basis control electronic for a future new version of the kart for long runs instead of short sprint races, which is going to be developed and constructed in the next years. This car will have similar features, but adapted to the requirements of long runs (autonomy, power, gear ratio), compared with the sprint version of the kart, which is described in this chapter.

### 2.1 Overview

The choice of the vehicle platform, the drive concept and parts of the vehicle's structure was the target of a previous Bachelor Thesis. Due to the chassis' low weight and its maneuverability, given by the smaller wheels, it was decided to choose a kart platform for the electrification project. In addition, due to the low center of gravity and the fact that the construction of a kart allows for greater wheel loads on the rear axle, a kart platform has a lot of advantages for sprint races [2].

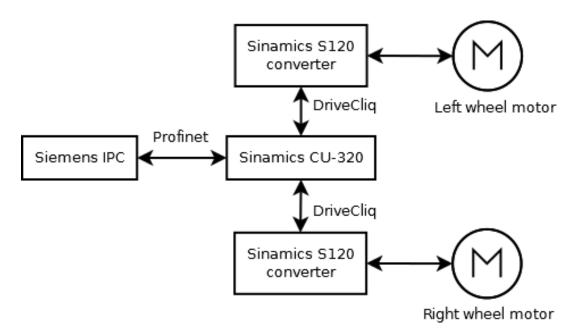

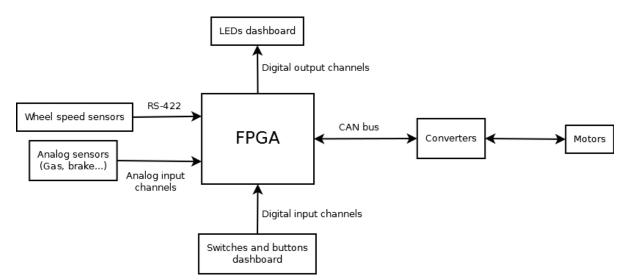

It has two electric drivetrains, each of them consisting of an electric motor and the necessary converter. Each drivetrain unit (Motor + Converter) is governed by a dedicated Siemens control unit. This control unit receives the necessary control data from a Siemens Industrial PC (IPC). Overall, the kart weighs about 166kg (without driver) and is equipped with similar tyres as the Formula Student cars. The motors are controlled by a fast and robust industrial PC [2].

Figures 2.1 and 2.2 shows how the E-Kart is but in order to get a more detailed view of the different components of the kart, they are described individualy in the next sections.

### 2.2 Main components

#### 2.2.1 Siemens IPC 427

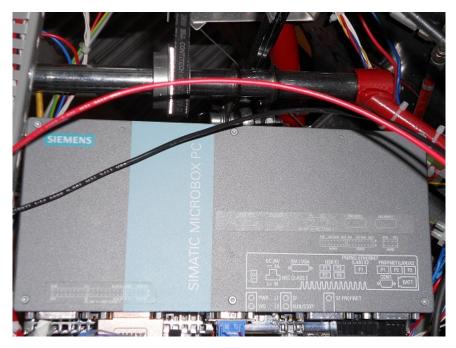

The complete vehicle is controlled by a robust Siemens Industrial PC 427 (see Figure 2.3). The Siemens IPC 427C monitors and controls the kart. He has 24 digital inputs, 16 digital outputs,

Figure 2.1: VDE E-Performance Kart

Figure 2.2: VDE E-Performance Kart System block diagram

Figure 2.3: Siemens IPC 427

8 analog inputs and outputs. In addition the IPC has 4 ports for rotary encoders for wheel's speed meassuring, RS-232 serial port and Ethernet ports, which are used for Profinet protocol and programming the IPC via ftp server.

The Siemens IPC is designed for real time tasks and in fact it has installed the real time operating system RMOS v3.50. It is suited to update all the signals every 50  $\mu s$  so the performance is guaranteed.

In addition, every 250 microseconds, new values such as measurements of road tests are stored in the RAM memory of the IPC, which can be recovered later via the serial interface. Between the IPC and the control of the converters works the Profinet IRT protocol [2].

#### 2.2.2 Motors

The kart is powered by two water-cooled permanent-magnet synchronous motors manufactured by Siemens. The Siemens motors 1FE1-042 deliver, (as can be seen in Figure 2.4), a nominal power output of 14.4 kW and a rated torque of 11 Nm, which can be up to 20 Nm in overload mode (operating mode S6-40%). The motors can reach a maximum of 18000 RPM. The overload capability is used in the race as a boost function and is controlled in the software [2].

Figure 2.4 shows the setup of the motors in the kart. As it can be seen, each of one is conected to an independent axle, which gives through a gearbox the power to each wheel. The gearbox is designed to achieve 140 Km/h at 18000 RPM, the maximum engine speed.

For more information about de electric motors, a detailed datasheet is provided in the Appendix.

Figure 2.4: Siemens electric Motors

#### 2.2.3 Converters

There are two SINAMICS Siemens S120 frequency converters installed in the vehicle, which are controlled by one Siemens Control Unit. Each of one controls one motor independently and the communication between the converters and the control unit is made via the Siemens "DriveCliq" protocol, which are not open published [2].

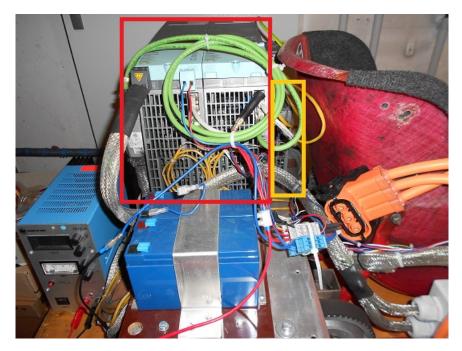

Figure 2.5 shows the converters' placement, which is marked in red colour.

#### 2.2.4 Control units

The Siemens Control Unit C320 is used to control the converters. The exchange of information between the CU and IPC occurs every 500  $\mu s$ . This exchange of information is made through the profinet IRT protocol and by this way, the controller can modify the values of the accelerator pedal and wheel speeds fast enough to ensure a good control of the motors [2].

Figure 2.5 shows the control unit's placement, which is marked in yellow colour.

#### 2.2.5 Wheel speed sensors

Is a prerequisite for the optimal work of the Traction Control System to keep the readout time of the sensor in the range below 1 ms. Further processing of the signals should be in the range below 5 to 10 ms and this condition was fulfilled successfully via using an inductive sensor of the company "Lenord+Bauer". The only limitation which has been found is that the sensor is only accurate from speeds above 10 km/h. Therefore, all the calculations concerning wheel

Figure 2.5: Siemens converters and control unit

speeds must be executed only with wheel speeds above 10 km/h [2].

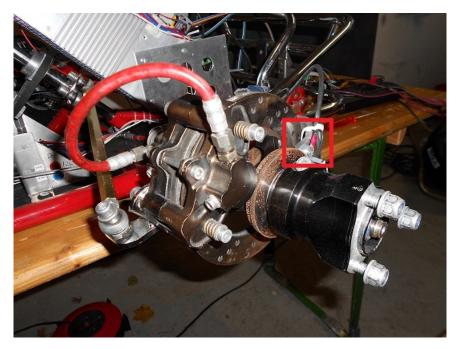

Figure 2.6 shows the Speed sensor's placement marked in red colour.

#### 2.2.6 Supercapacitors

In order to provide the needed electrical energy for the motors, two supercapacitors store this electrical energy and releases it when needed. They can be charged to a maximum of 380 Volts and at maximum power, the stored energy is enough to move the kart for the required 50 m sprint and a little bit more for the return to the start place, for a total of barely 100 meters of autonomy at maximum performance. For further information see [3]. Figure 2.7 shows the internal construction of the supercapacitors.

#### 2.2.7 Safety

#### **Current and voltage**

The main danger of this Kart is his DC link voltage of 600V, which increases in the intermediate circuit when braking. This high voltage requires special efforts to protect the driver and bystanders against electric shocks. The used components are protected against contact by applicable standards, so emerging risks of this interconnection are intercepted by safety circuits. During construction, measures have been taken to prevent that the user comes into contact with electrical voltage. Furthermore, an emergency shutdown system was installed, so at any time the energy storage can be separated from the remaining components of the kart and the DC link

Figure 2.6: Lenor+Bauer speed sensor

Figure 2.7: E-Kart supercapacitors

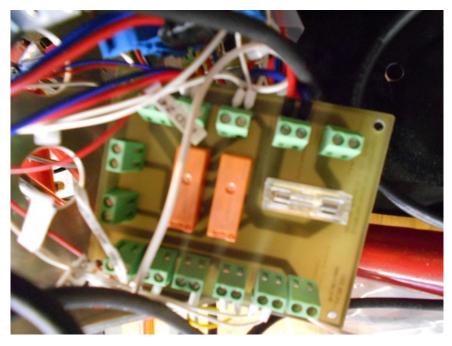

Figure 2.8: Custom security board

is discharged quickly. All components have been designed for long-term exposure to 5g forces.

Figure 2.8 shows the security custom board.

#### Kid's safe drive mode

The key switch "'VMAX" on the panel is used to protect inexperienced drivers. By using the Profinet communication, a speed limit of 50 Km/h should be sent to the CU320, corresponding to an engine speed of 6400 RPM. In addition, the torque vectoring is fixed to factor 0.2 (see 2.1), the braking force distribution and the response at Level 1 (see 2.2). The ASR should be active.

#### 2.2.8 Information leds

There is the LED panel in the cockpit right in front of the driver's view, which allows the driver to have at any time information about the different operating conditions and errors. Figure 2.9 shows the position of the different led lights in the cockpit [3].

This LED panel gives information about:

- 24V power supply on/off

- 600V power supply on/off

- Battery almost empty

- Battery empty

- PC error

- Motors hot/error

Figure 2.9: LEDs panel

#### 2.3 Functions

#### 2.3.1 Torque Vectoring

Torque vectoring is a new technology employed in automobile differentials. A differential transfers engine torque to the wheels. Torque vectoring technology provides the differential with the ability to vary the power to each wheel. This method of power transfer has recently become popular in all-wheel drive vehicles. Some newer front-wheel drive vehicles also have a basic torque vectoring differential. As technology in the automotive industry improves, more vehicles are equipped with torque vectoring differentials.

The torque vectoring idea builds on the basic principles of a standard differential. A torque vectoring differential performs basic differential tasks while also transmitting torque independently between wheels. This torque transferring ability improves handling and traction in almost any situation [4] [5].

#### Torque vectoring in constant corner drive

The torque vectoring function in executed in the control unit as a mathematical formula, which gives the percentage of torque that must be substracted to the interior wheel and added to the exterior wheel.

Equation 2.1 models the behaviour of the torque vectoring [2]:

$$\Delta MT or que Vectoring = v^2 \cdot \sin^2 \delta_l \cdot d \cdot 1.85736 \tag{2.1}$$

where v is the kart's speed in m/s,  $\delta_l$  is the steering angle in radians and d is factor which changes the sensibility of the torque vetoring. Table 2.1 shows the possible values of the "d"

| Torque vectoring switch | Factor d |

|-------------------------|----------|

| 5/5 (off)               | 0        |

| 6/4                     | 0.2      |

| 7/3                     | 0.3      |

| 8/2                     | 0.4      |

| 9/1                     | 0.5      |

Table 2.1: Torque Vectoring Factor

The torque vectoring does not work in case of an error in the selector switch and in case of Kid's safety function active the factor is set to 0.2. In both cases the error LED is activated. In order to know more about the calculations involving the torque vectoring function see [3].

#### Dynamic Torque Vectoring in the corner entry

At the transition from a straight line into a circular orbit and back special dynamics bring advantages in car racing. The faster the vehicle follows the specified steering movements, the sportier is the driving experience. Therefore, now when turning, the steering wheel selector "response" broughts into play.

In the actual corner entry, while the steering angle is still changing, a higher weighting factor "f" for the torque distribution is introduced to force the vehicle quicker to the desired circular path. If the kart returns to the constant steering angle, it changes again to the Torque Vectoring formula with the factor "d" (transition from corner entry to constant cornering).

Table 2.2 shows the possible values of the "f" factor:

| Response | Factor f |

|----------|----------|

| 1        | 0        |

| 2        | 0.2      |

| 3        | 0.4      |

| 4        | 0.6      |

| 5        | 0.8      |

| 6        | 1.0      |

Table 2.2: Torque Vectoring Response

#### 2.3.2 Traction Control System

Critical driving situations that arise especially on slippery road surfaces can cause that the driver responds incorrectly and the vehicle's behavior is unstable. The Traction Control System con-

factor:

cerns the start and acceleration of the vehicle and guarantees a stable behavior, securing that the physical limits are not exceeded.

The Traction Control System monitors the rotational speed of the wheels using wheel speed sensors. By comparing the driven and non-driven wheels, the system determines whether a wheel is spinning or not and calculates the slip. If the slip is too high, the torque is reduced und thus the slip is also reduced [2].

#### 2.3.3 Brake balance

The VDE E-Kart has a brake balance switch, that allows the driver to change the behaviour of brakes in that displacing more brake power to rear train or to front according to the driver's demand at any time.

#### 2.3.4 Offline telemetry

At car racing it is very important to have as many as possible information about all the systems of the car. This information can be transmited in real time from the car to the engineers, which is known as Live-Telemetry, and it is very usefull to do some checks in the car and if the telemetry is bidirectional make changes in real time to improve the performance or tell the driver if something is going wrong.

At the moment there is not Live-Telemetry in the VDE E-Kart but all the information is stored in the computer's RAM and can be retrieved via serial port when the kart has finished his run.

The most common telemetry information stored is:

- Wheel speeds and global speed

- Gas and brake percentage

- Lateral and vertical G-forces

- Battery charge

- Motor temperatures

# **Chapter 3**

# **Involved Technologies**

In this chapter the main technologies involved in this Master Thesis are explained.

#### 3.1 FPGA

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing, hence "field-programmable". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC) (circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare).

Contemporary FPGAs have large resources of logic gates and RAM blocks to implement complex digital computations. As FPGA designs employ very fast I/Os and bidirectional data buses it becomes a challenge to verify correct timing of valid data within setup time and hold time. Floor planning enables resources allocation within FPGA to meet these time constraints [6]. FPGAs can be used to implement any logical function that an ASIC could perform. The ability to update the functionality after shipping, partial re-configuration of a portion of the design and the low non-recurring engineering costs relative to an ASIC design (notwithstanding the generally higher unit cost), offer advantages for many applications.

FPGAs contain programmable logic components called "logic blocks", and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together" somewhat like many (changeable) logic gates that can be inter-wired in (many) different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory [7].

Figure 3.1: Xilinx's FPGA chip

### 3.2 ITIV's custom Xilinx Spartan 6 board for VDE Kart

A custom FPGA board developed at ITIV institute for hosting the implementation of an embedded system including the software control part was chosen as the replacement for the old Siemens computer.

The board, which is equiped with a Spartan 6 FPGA, was in development in August 2013 and after exhaustive tests was delivered ready for use.

#### 3.2.1 Spartan 6 family

The Spartan-6 family provides leading system integration capabilities with the lowest total cost for high-volume applications. The thirteen-member family delivers expanded densities ranging from 3,840 to 147,443 logic cells, with half the power consumption of previous Spartan families, and faster, more comprehensive connectivity. Built on a mature 45 nm low-power copper process technology that delivers the optimal balance of cost, power, and performance, the Spartan-6 family offers a new, more efficient, dual-register 6-input lookup table (LUT) logic and a rich selection of built-in system-level blocks.

These include 18 Kb (2 x 9 Kb) block RAMs, second generation DSP48A1 slices, SDRAM memory controllers, enhanced mixed-mode clock management blocks, SelectIO technology, poweroptimized high-speed serial transceiver blocks, PCI Express compatible Endpoint blocks, advanced system-level power management modes, auto-detect configuration options, and enhanced IP security with AES and Device DNA protection. These features provide a lowcost programmable alternative to custom ASIC products with unprecedented ease of use. Spartan-6 FPGAs offer the best solution for high-volume logic designs, consumer-oriented DSP designs, and cost-sensitive embedded applications. Spartan-6 FPGAs are the programmable silicon foundation for Targeted Design Platforms that deliver integrated software and hardware components that enable designers to focus on innovation as soon as their development cycle begins

#### Spartan 6 lx150

The FPGA model, that was chosen for the custom board was the spartan 6 1x150 and in Table 3.1 the main features of this model are enumerated:

| Logic cells              | 147,443  |

|--------------------------|----------|

| Slices                   | 23,038   |

| Flip-Flops               | 184,304  |

| Max distributed RAM      | 1,355 Kb |

| DSP48A1 Slices           | 180      |

| Block RAM 18 Kb          | 268      |

| Max RAM                  | 4,824 Kb |

| CMT(2 DCMs + PLL)        | 6        |

| Memory Controller Blocks | 4        |

| Max user I/O             | 576      |

Table 3.1: Spartan 6 lx150 features

#### **3.2.2 Board features**

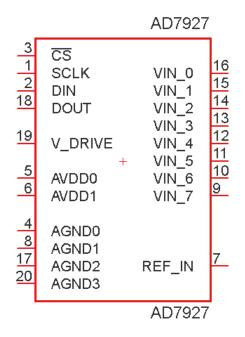

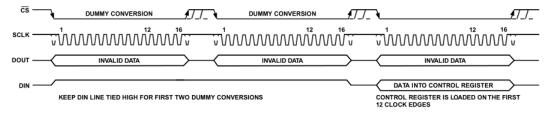

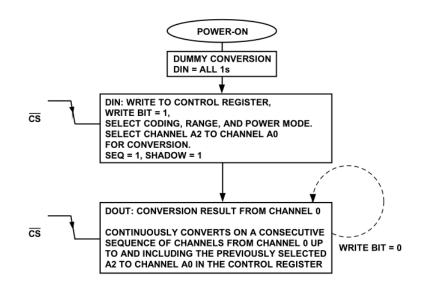

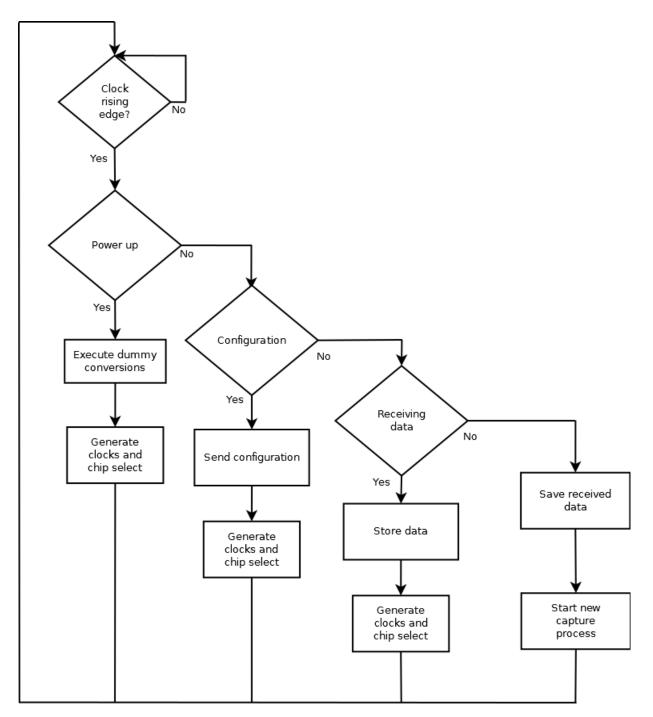

The custom FPGA based board developed in the ITIV, which is going to replace the present Siemens industrial PC, has de following features:

- Power suply between 12 and 24 Volts

- 8 analog inputs with 12 bits precission (AD7927) in range of 0 to 10 Volts

- 24 digital inputs in range of 0 to 24 volts

- 24 digital outputs in range of 0 to 24 volts with a maximum frequency of 2 KHz

- 4 RS-422 interfaces

- 2 CAN bus interfaces

- 2 RS-485 interfaces

- Ethernet interface

- GSM interface

- 2 x 512 Mb SDRAM

#### [12].

Table 3.2 resumes the elements of the onboard electronics (sensors, leds, etc) and the conections with the interfaces of the board.

| Interface       | Onboard electronics              |

|-----------------|----------------------------------|

| Analog inputs   | Analog sensors                   |

| Digital inputs  | Switches and buttons             |

| Digital outputs | LEDs and circuit release signals |

| RS-422          | Rotary encoders                  |

| CAN bus         | Frequency converters             |

Table 3.2: Physical interfaces on the board

Figure 3.2: ITIV's Spartan 6 custom board

### 3.3 Hardware description languages

There are two main hardware description languages, which are used to describe hardware circuits in a similar form of a programming language by using conditional statements, assign statements, loops and all the stuff present in the programming languages but it differs in the ways of describing the propagation of time and signal dependencies (sensitivity).

#### 3.3.1 VHDL

VHDL (VHSIC Hardware Description Language) is a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as fieldprogrammable gate arrays and integrated circuits. VHDL can also be used as a general purpose parallel programming language.

The IEEE Standard 1076 defines the VHSIC Hardware Description Language or VHDL. It was originally developed under contract F33615-83-C-1003 from the United States Air Force awarded in 1983 to a team with Intermetrics, Inc. as language experts and prime contractor, with Texas Instruments as chip design experts and IBM as computer system design experts. The language has undergone numerous revisions and has a variety of sub-standards associated with it that augment or extend it in important ways

## 3.3.2 Verilog

Verilog, standardized as IEEE 1364, is a hardware description language (HDL) used to model electronic systems. It is most commonly used in the design and verification of digital circuits at the register-transfer level of abstraction. It is also used in the verification of analog circuits and mixed-signal circuits.

The designers of Verilog wanted a language with syntax similar to the C programming language, which was already widely used in engineering software development. Like C, Verilog is case-sensitive and has a basic preprocessor (though less sophisticated than that of ANSI C/C++). Its control flow keywords (if/else, for, while, case, etc.) are equivalent, and its operator precedence is compatible.

# 3.4 Programming languages

## **3.4.1** C programming language

C is a general-purpose programming language initially developed by Dennis Ritchie between 1969 and 1973 at AT & T Bell Labs. Like most imperative languages in the ALGOL tradition, C has facilities for structured programming and allows lexical variable scope and recursion, while a static type system prevents many unintended operations. Its design provides constructs that map efficiently to typical machine instructions, and therefore it has found lasting use in applications that had formerly been coded in assembly language, most notably system software like the Unix computer operating system [8].

C is one of the most widely used programming languages of all time, and C compilers are available for the majority of available computer architectures and operating systems [9].

# 3.5 CAN-bus

CAN bus (for controller area network) is a vehicle bus standard designed to allow microcontrollers and devices to communicate with each other within a vehicle without a host computer. CAN bus is a message-based protocol, designed specifically for automotive applications but now also used in other areas such as aerospace, maritime, industrial automation and medical equipment.

Development of the CAN bus started originally in 1983 at Robert Bosch GmbH [10]. The protocol was officially released in 1986 at the Society of Automotive Engineers (SAE) congress in Detroit, Michigan. The first CAN controller chips, produced by Intel and Philips, came on the market in 1987. Bosch published the CAN 2.0 specification in 1991. In 2012 Bosch has specified the improved CAN data link layer protocol, called CAN FD, which will extend the ISO 11898-1.

CAN bus is one of five protocols used in the on-board diagnostics (OBD)-II vehicle diagnostics standard. The OBD-II standard has been mandatory for all cars and light trucks sold in the United States since 1996, and the EOBD standard has been mandatory for all petrol vehicles sold in the European Union since 2001 and all diesel vehicles since 2004 [11].

## 3.5.1 Features

- prioritization of messages

- guarantee of latency times

- configuration flexibility

- multicast reception with time synchronization

- system wide data consistency

- multimaster

- error detection and signalling

- automatic retransmission of corrupted messages as soon as the bus is idle again

- distinction between temporary errors and permanent failures of nodes and autonomous switching off of defect nodes

# **Chapter 4**

# **Design of the system**

In this chapter the chosen design of the final embedded system which is described focusing on the requirements, limitations and advantages. A widely description of each hardware component is done in the Chapter 5, *Hardware development* and for software components in the Chapter 6, *Software development*.

# 4.1 Hardware

Due to the FPGA based design of the final system, the main aproach to solve this task is to choose a main soft core, which acts as the main processor of the system and build around him an embedded system. There are a lot of possibilities in the field of soft cores. A soft microprocessor (also called softcore microprocessor or a soft processor) is a microprocessor core that can be wholly implemented using logic synthesis. It can be implemented via different semiconductor devices containing programmable logic (e.g., ASIC, FPGA, CPLD), including both high-end and commodity variations [13].

There are a lot of soft cores in the market, an the main options are showed in Table 4.1.

| Processor     | Developer        | Open Source? | Bus Support    | Word width |

|---------------|------------------|--------------|----------------|------------|

| OpenSPARC T1  | Sun (Oracle)     | Yes          | -              | 64-bit     |

| MicroBlaze    | Xilinx           | No           | PLB, OPB,      | 32-bit     |

|               |                  |              | FSL, LMB, AXI4 |            |

| Nios, Nios II | Altera           | No           | Avalon         | 32-bit     |

| LEON3/4       | Aeroflex Gaisler | Yes          | AMBA2          | 32-bit     |

| OpenRISC      | OpenCores        | Yes          | Wishbone       | 32-bit     |

#### Table 4.1: Soft processors

The selected soft core for the embedded system was the "'Microblaze". The reasons for using this soft processor are the following:

• FPGA Spartan 6: due to use of a Spartan 6 FPGA from Xilinx in the design of the custom board, it makes sense to use the soft processor of the same manufacter in order to exploit all the given advantages

- **Block RAM:** This type of RAM memory is inside the Xilinx FPGA chip and is easily configurable in the development tools

- Microblaze configurations: The Microblaze is a fully and easily configurable processor aiming area-optimized, performance and maximum frequency designs

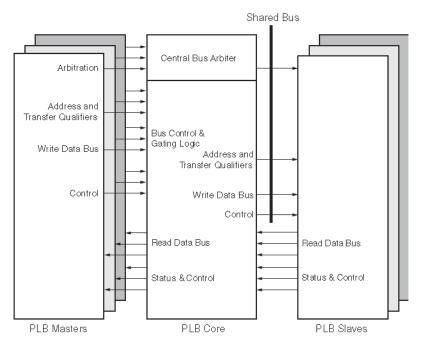

- Wide bus support: The Microblaze is compatible with different bus standards, which makes possible to include a huge amount of custom-made peripherals by the comunity in the system, even if there is not interface with this buses because it is possible to easily find a compatible bridge to join both interfaces

- Xilinx development tools: The xilinx Microblaze development tools offer a capable integrated development environment with both independent hardware and software development tools, each of one with their functionalities such as HDL simulator or timing reports in the case of the hardware tool and a debugger or block RAM memory initialization in the case of the software tool.

- Experience with the design tools: Experience with the design tools is another plus because the learning phase of the tools to get used to them can be avoided and instead of that it is possible to go faster and easier into development phase.

In the next section a detailed vision of the "Microblaze" is given.

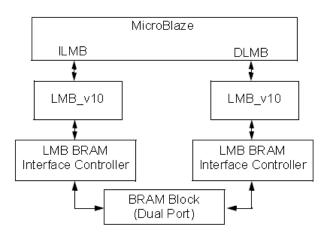

## 4.1.1 Xilinx Microblaze

MicroBlaze is the industry-leader in FPGA-based soft processors, with advanced architecture options like AXI or PLB interface, Memory Management Unit (MMU), instruction and dataside cache, configurable pipeline depth, Floating-Point unit (FPU), and much more. MicroBlaze is a 32-bit RISC Harvard architecture soft processor core that is included with both Vivado Design Edition and IDS Embedded Edition. Highly flexible architecture, plus a rich instruction set optimized for embedded applications, delivers the exact processing system you need at the lowest system cost possible [14].

#### **Microblaze features**

- Low Latency Interrupt Mode

- LMB BRAM memory with parity protection on internal BRAMs and caches

- IEEE 754 compatible Floating Point Unit (FPU)

- Instruction and Data Caches configurable: 2kB 64kB (Block RAM based)

- Branch Optimizations and prediction logic

- Data bus error and instruction bus error

- Divide and floating point exceptions

- Debug Logic

- JTAG control via a debug support core with up to 8 hardware break points

Instruction-side Data-side bus interface bus interface Memory Management Unit (MMU) UTLB DTLB ITLB 7 D-Cache DXCL M IXCL I-Cache ALU DXCL\_S IXCI Program Shift Counter Special Purpose Barrel Shift Registers Multiplier IPLB Divider IOPB FPU Bus Bus Instruction IF IF Buffer ILMB Instruction Decode MFSL 0..15 or DWFSL 0..15 Register File 32 X 32b SFSL 0..15 or DRFSL 0..15 Optional MicroBlaze feature Figure 1-1: MicroBlaze Core Block Diagram

In figure 4.1 it can be seen the main structure of the Microblaze Core:

Figure 4.1: Microblaze Core block diagram

#### Hardvard Architecture

A Microblaze processor system, unlike most desktop computers, is based on the Modified Harvard architecture (very common in DSPs and Microcontrollers), which has splitted memories for instructions and for data. Indeed, in a Microblaze processor system the data and instruction memory are physically the same because the block RAM memory is a dual port memory and Microblaze access instructions and data from different buses. Both buses are 32-bit wide, that means up to 4 GBytes of data and instructions are addressable. This memory is accessed by the Microblaze core via a block RAM memory controller connected to his Local Memory Bus. When loading the program into memory, the loader is responsible for separating the user data from the instructions.

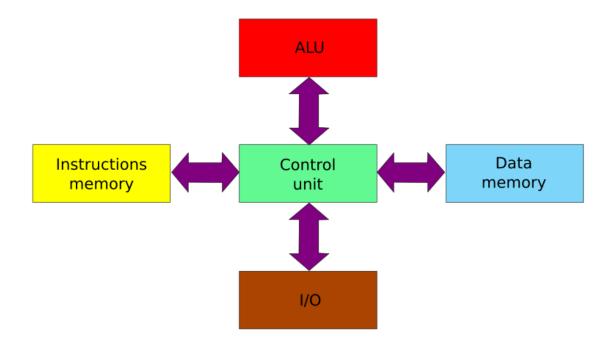

Figure 4.2: Harvard Architecture

# 4.2 Sotfware

The software options were evident given the selection of the hardware platform, which means that the software options were limited to those Microblaze-compatible. Xilinx offers the following software platforms for his Microblaze core integrated in his *Software Development Kit* tool:

- Xilinx Standalone

- Xilinx Xilkernel

- Linux

Between these three options, the Linux one was automatically discarded due to the higher memory requirements and the excessive and useless functionality for the system to be developed compared to the other two software platforms.

## 4.2.1 Xilinx Standalone

Standalone is the lowest layer of software modules used to access processor specific functions. Standalone is used when an application accesses board/processor features directly and is below the operating system layer [15].

Xilinx Standalone has the following features:

- Interrupt and Exceptions handling

- Data and Instruction Cache handling

- Fast Simplex Link interface macros

- File handling

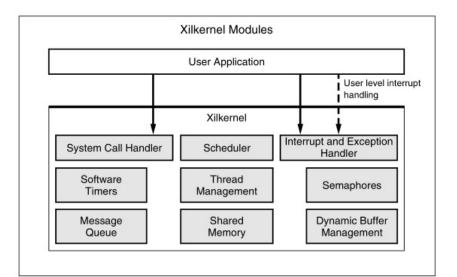

## 4.2.2 Xilinx Xilkernel

Xilkernel is a small, robust, and modular kernel. It is highly integrated with the Platform Studio framework and is a free software library that you receive with the Xilinx Embedded Development Kit (EDK) [15]. Xilkernel:

- Allows a very high degree of customization, letting you tailor the kernel to an optimal level both in terms of size and functionality.

- Supports the core features required in a lightweight embedded kernel, with a POSIX API.

- Works on MicroBlaze, PowerPC 405, and PowerPC 440 processors.

Xilkernel includes the following key features [15]:

- High scalability into a given system through the inclusion or exclusion of functionality as required.

- Complete kernel configuration and deployment within minutes from inside of Platform Studio.

- Robustness of the kernel: system calls protected by parameter validity checks and proper return of POSIX error codes.

- A POSIX API targeting embedded kernels, win core kernel features such as:

- Threads with round-robin or strict priority scheduling.

- Synchronization services: semaphores and mutex locks.

- IPC services: message queues and shared memory.

- Dynamic buffer pool memory allocation.

- Software timers.

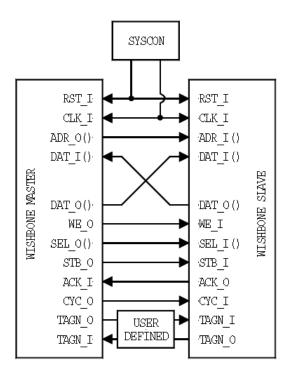

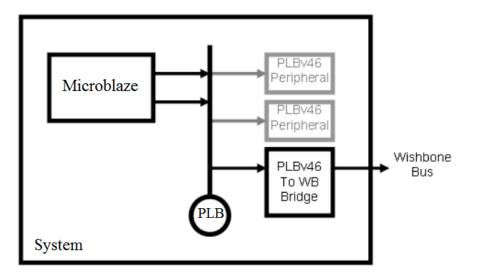

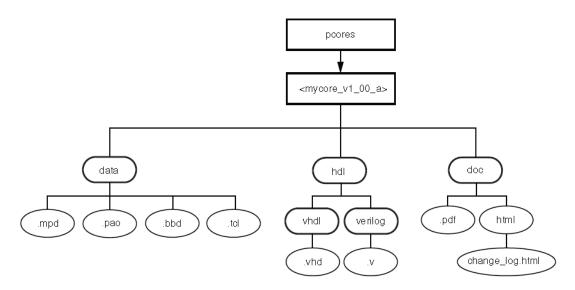

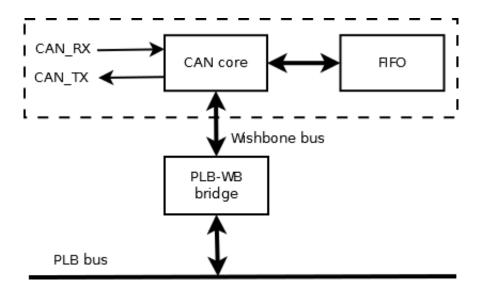

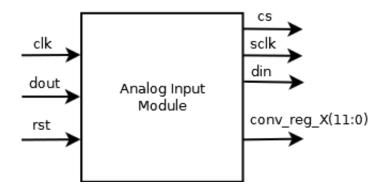

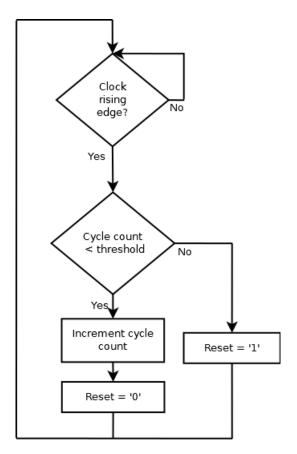

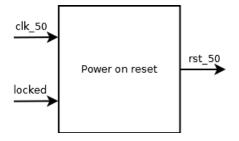

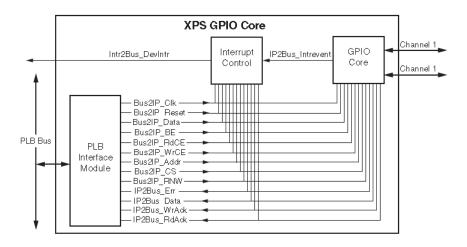

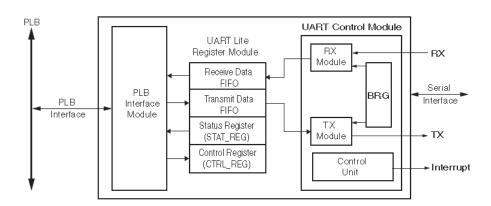

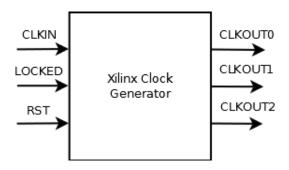

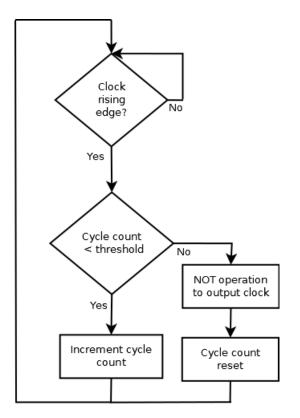

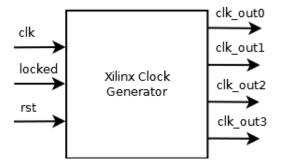

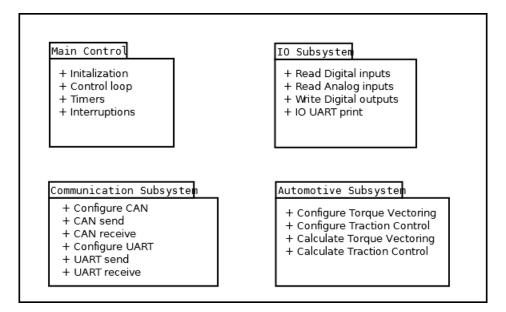

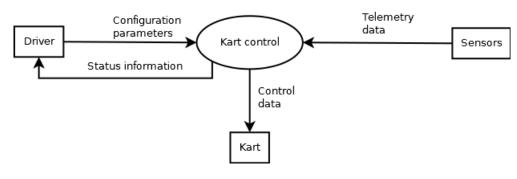

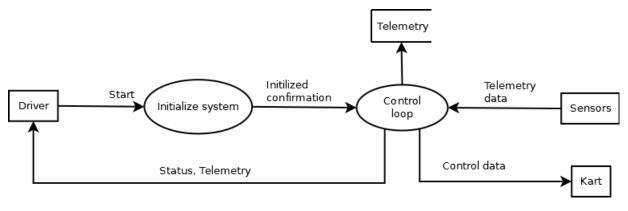

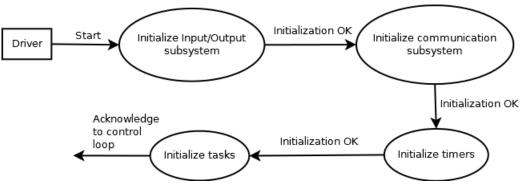

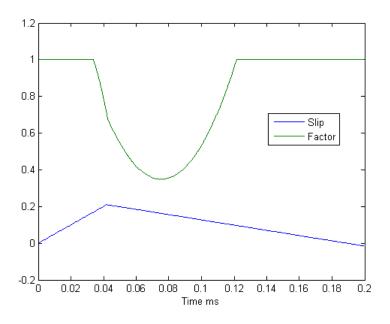

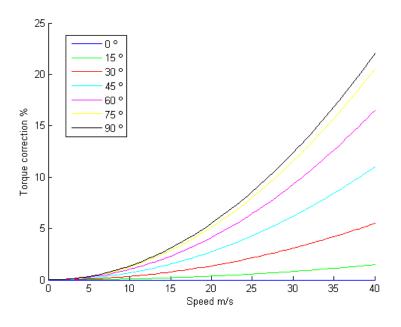

- User-level interrupt handling.