# A Novel Low-Voltage Reconfigurable ΣΔ Modulator for 4G Wireless Receivers

Alonso Morgado, Rocío del Río and José M. de la Rosa

Institute of Microelectronics of Seville (IMSE-CNM, CSIC) and Universidad de Sevilla Edif. CICA-CNM, Avda. Reina Mercedes s/n, 41012- Sevilla, SPAIN Phone: +34 95 5056666, Fax: +34 95 5056686, E-mail: {alonso|rocio|jrosa}@imse.cnm.es

Abstract – This paper presents a new adaptable cascade ΣΔ modulator architecture for low-voltage multi-standard applications. It uses two reconfiguration strategies: a programmable global resonation and a variable loop-filter order. These techniques are properly combined in a novel topology that allows to increase the effective resolution in a given bandwidth, whereas keeping relaxed output swing requirements and high robustness to mismatch and to non-linearities of the amplifiers. Time-domain simulations including the main circuit-level non-idealities are shown to demonstrate the benefits of the presented modulator when it is configured to cope with the requirements of GSM, UMTS, WLAN and Wi-Max. †

## I. INTRODUCTION

<u>Sigma-Delta Modulators</u> ( $\Sigma\Delta Ms$ ) are very suited for the implementation of reconfigurable <u>Analog-to-Digital Converters</u> (ADCs) required for the fourth generation (4G or Beyond-3G) of wireless hand-held devices [1]. Based on the combined use of oversampling and noise shaping,  $\Sigma\Delta Ms$  can adapt their dynamic ranges to different specifications with large hardware re-use, reduced power consumption and at the lowest cost [2]-[9].

Although changing the sampling frequency has been the reconfiguration strategy most commonly applied, the mandatory use of low  $\underline{O}\text{ver}\underline{S}\text{ampling}$   $\underline{R}\text{atios}$  (OSRs) in wideband communication standards has forced  $\Sigma\Delta Ms$  to achieve the required dynamic ranges by resorting to different strategies, including: high-order shaping [2][6][8][9], switchable cascade topologies [5][9]; programmable notches within the signal band [2][8]; and multi-bit embedded quantizers [3][7][9]. However, the efficient implementation of these techniques requires to explore new  $\Sigma\Delta M$  topologies capable of adapting their performance to as many specifications as possible while keeping high robustness to circuit errors.

The modulator presented in this paper is based on three strategies to adapt its functionality to different specifications. First, the modulator loop-filter order can be varied according to the required performance by connecting or disconnecting low-order stages in a cascade topology. Second, resonation is used to optimally distribute the zeroes of the Noise Transfer Function (NTF) within the required signal bandwidth. Third, a unity Signal Transfer Function (STF) is employed in all stages of the cascade for reducing the amplifier output swing requirements [10]. The above-mentioned strategies are combined in a novel reconfigurable cascade  $\Sigma\Delta M$  topology that maximizes the effective resolution within a given bandwidth with reduced circuit complexity, low sensitivity to element mismatches and high robustness with respect to opamp non-linearities.

# II. PROPOSED MODULATOR

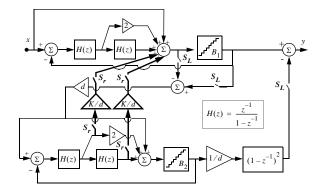

Fig.1 shows the proposed modulator architecture. It consists of a reconfigurable cascade topology that makes use of two concepts, namely: unity STF [10] and global resonation [11]. The former is implemented by the feedforward paths that connect the input of each stage with the corresponding quantizer inputs, whereas global resonation is achieved thanks to the inter-stage paths (highlighted in Fig.1) that feed back a delayed scaled version of the last-stage quantization error at the input of the first-stage quantizer. One important advantage of the proposed modulator is that, on the contrary to the one reported in [11], only Forward-Euler (FE)

Fig. 1: Proposed reconfigurable  $\Sigma \Delta M$  topology.

<sup>†.</sup> This work has been supported by the Spanish Ministry of Science and Education (with support from the European Regional Development Fund) under contract TEC2007-67247-C02-01/MIC and the Andalusian (Regional) Ministry of Innovation, Science and Enterprise under contract TIC-2532.

integrators are required, thus making its Switched-Capacitor (SC) implementation easier.

The modulator includes a number of switches to configure the NTF according to the required performance. On the one hand, by connecting the switchable error feedback paths from the last to the first stage —with switches  $S_r$  and  $S_L$  in ON mode—the global resonation scheme is enabled. On the other hand, the order of the cascade is also reconfigurable. Both reconfiguration strategies (adaptive global resonation and NTF order) can be used independently, thus giving more flexibility to the  $\Sigma\Delta M$  to adapt its functionality to the required performance. In a practical application, those components that are not used can be turned off by using a power-down control in order to save power consumption.

In case resonation is enabled and considering a linear model for the embedded quantizers, it can be shown that the NTF of the proposed architecture is given by:

$$NTF(z) = \frac{-(1-z^{-1})^2 \cdot [1 - (2-K) \cdot z^{-1} + z^{-2}]}{d}$$

(1)

where d stands for the inter-stage gain. Note that two of the NTF zeroes are a function of K, whose value can

be optimally chosen to maximize the <u>Signal-to-(Noise+Distortion)</u> Ratio (SNDR).

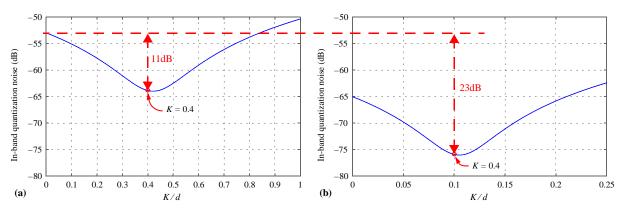

This effect is illustrated in Fig.2 for an *OSR* of 4 and embedded quantizers with 4-bit resolution. The optimum values of K/d for an inter-stage gain of 1 and 4 are roughly 0.4 and 0.1, which can be easily implemented using capacitor ratios of 2/5 and 1/10, respectively. If there is no signal scaling along the cascade (d=1), the resolution is increased in 11dB, whereas if d=4, an increment of 23dB is achieved.

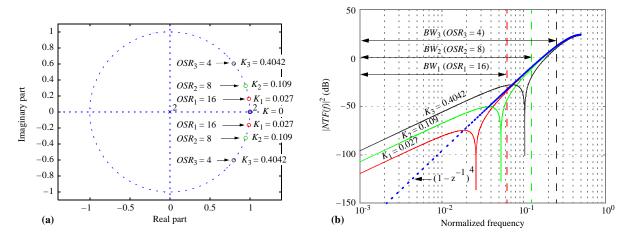

For the sake of completeness, Fig.3(a) shows the optimal location of the NTF zeroes in the unity-circle for oversampling ratios of 4, 8 and 16. The effect on the noise shaping is depicted in Fig.3(b) by representing the NTF for the different cases together with their corresponding signal <u>BandWidths</u> (*BWs*).

Note that an increase of d (to reduce the quantization noise) yields a reduction of the feedback coefficient K/d. In practice, this results in a smaller capacitor ratio, which makes the electrical implementation more difficult and prone to circuit non-idealities. However, the value of K/d can be easily implemented if the oversampling ratio is low enough because —as illustrated in Fig.3(a)—a reduction of the *OSR* means an increase of K. Therefore, the resonation provided by

Fig. 2: Variation of the in-band quantization noise with K/d for: (a) d=1, (b) d=4 (OSR = 4 and  $B_1=B_2=4$ ).

Fig. 3: Optimum distribution of NTF zeroes in the proposed resonation-based  $\Sigma \Delta M$  for different oversampling ratios: (a) Location of zeroes in the unit circle, (b) NTF vs. frequency (d = 1).

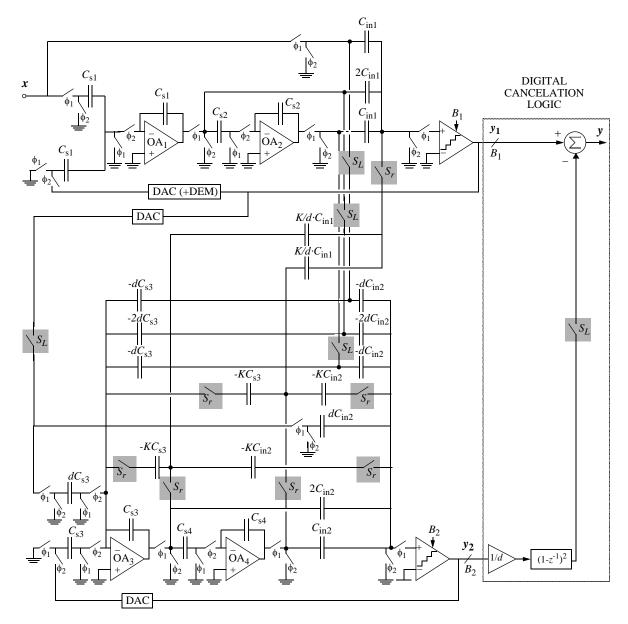

**Fig. 4:** SC schematic of the proposed reconfigurable  $\Sigma \Delta M$  (single-ended version).

the proposed architecture is specially suited for wideband applications with low *OSR*.

Fig.4 shows the conceptual SC implementation of the modulator in Fig.1, in which the required analog additions are implemented by passive SC networks in order to save power. The required analog coefficients are implemented as capacitor ratios using capacitors  $C_{\rm s1}$  to  $C_{\rm s4}$ ,  $C_{\rm in1}$  and  $C_{\rm in2}$ . Note that a number of capacitors in Fig.4 have negative values; in the actual fully differential implementation, the negative value would be implemented by swapping the corresponding capacitors in the positive and negative signal branches.

The use of passive SC analog additions involves a reduction of the full scale at the quantizer input and, consequently, a compression of the references and the quantizers voltage levels to be used [12]. For instance, if the distribution of the charge in the capacitors of the

first-stage analog adder during phase  $\boldsymbol{\phi}_1$  is considered, the resulting scaling factor is

$$\frac{C_{\rm in1}}{4C_{\rm in1}+2K/d\cdot C_{\rm in1}+C_{\rm quant}} \tag{2} \label{eq:2}$$

where  $C_{quant}$  stands for the input capacitance of the quantizer.

In order to get a robust modulator implementation it is desirable to have the same scaling regardless of the use of resonation. However, note from (2) that the denominator term  $2K/d \cdot C_{\rm in1}$  equals zero in case resonation is not employed, and thus the scaling factor varies from the one obtained with resonation. Let us assumed that  $C_{\rm in1}=2\rm pF$ , d=4, K=0.4, a 4-bit quantizer and 10-fF input capacitance for the quantizer comparators; then the corresponding scaling factor would be 0.234. If resonation is not employed

(K=0), the compression would be 0.245. In this example, a good choice for the reference compression in both cases is 0.25, thus making easier the implementation of the resulting voltage levels. Besides, thanks to the location of the addition in the modulator chain, a small variation of the scaling factor —as the one in this example— will have almost no impact on the modulator resolution. Note that the same applies to the second-stage analog addition.

## III. CASE STUDY

In order to show the reconfigurability of the proposed ΣΔM architecture, a case study is presented considering the specifications and standards listed in Table I. Table II shows the values of the modulator design parameters that are reconfigured for the different operation modes, namely: NTF order (L), resonation coefficient (K/d) and OSR. Note that different oversampling ratios -and their corresponding sampling frequencies  $(f_s)$ — are employed in order to cope with the required resolution of each signal bandwidth. Note that in those operation modes in which no resonation is used (GSM, UMTS and Wi-Max), the switches responsible for the last-stage error feedback (S<sub>r</sub> in Fig.1) are disconnected. Additionally, in GSM mode only the first stage is working —with switches  $S_r$  and  $S_L$  disconnected—whereas all the integrators and comparators of the second stage are turned off.

Global resonation is used only in WLAN mode. In this case, the rounded optimal feedback coefficient is K/d=0.1, resulting in a shift of two zeroes of the NTF from 0 to  $0.8\pm j0.6$ . Note that thanks to this optimum distribution of the NTF zeroes —together with the employment of an inter-stage scaling d=4 —, the in-band noise is minimized as shown in Fig.2(b).

TABLE I. SPECIFICATIONS FOR THE  $\Sigma\Delta M$  IN THE CASE STUDY

| Standard   | GSM | UMTS <sup>a</sup> | Wi-Max | WLAN |

|------------|-----|-------------------|--------|------|

| SNDR (bit) | 14  | 12                | 8      | 10   |

| BW (MHz)   | 0.2 | 4                 | 20     | 20   |

a. Although the bandwidth of UMTS is 3.84 MHz, it has been expanded to 4MHz in order to easily implement the sampling frequency.

TABLE II. RESONATION COEFF, MODULATOR ORDER,  $\mathit{OSR}$  AND d

| Standard             | GSM               | UMTS                  | Wi-Max <sup>a</sup> | WLAN |

|----------------------|-------------------|-----------------------|---------------------|------|

| Order (L)            | 2                 | 4                     |                     |      |

| Inter-stage gain (d) |                   | 4                     |                     |      |

| K                    | C                 | 0 (No resonation) 0.4 |                     |      |

| K/d                  | 0 (No resonation) |                       |                     | 0.1  |

| OSR                  | 100               | 10                    | 4                   |      |

| $f_s$ (MHz)          | 40                | 80                    | 160                 |      |

Note that resonation could also be employed in this case if a larger resolution is demanded.

#### IV. SIMULATION RESULTS

Several behavioral simulations have been performed using SIMSIDES, a Simulink-based time-domain simulator for  $\Sigma\Delta$  modulators [13]. In all operation modes, 4-bit internal quantizers and a 1-V reference voltage were considered. Additionally, kT/C noise, sampled by 0.25-pF sampling capacitors, is introduced at the first integrator in all simulations. The embedded Digital-to-Analog Converters (DACs) are assumed linear, although dynamic element matching will be required in practice at least in the first stage of the cascade.

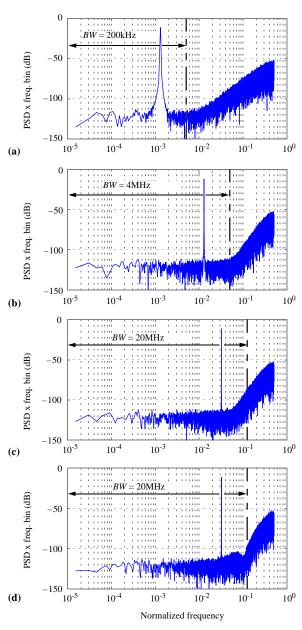

Fig.5 shows the modulator output spectra for all the operation modes. In GSM [Fig.5(a)], the in-band error is dominated by thermal noise, whereas in UMTS

Fig. 5: Modulator spectra of the different modes: (a) GSM, (b) UMTS, (c) Wi-Max, (d) WLAN (-6dBFS input level, 64k-point FFTs).

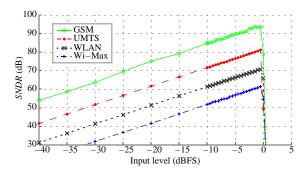

**Fig. 6:** Modulator *SNDR* versus input level (normalized to full scale).

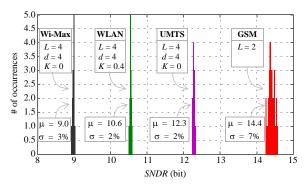

Fig. 7: SNDR variation considering a 0.1% capacitor mismatch (-6dBFS input level, 50-run Monte Carlo simulation).

[Fig.5(b)] the larger error term is not clearly defined between thermal or quantization noise. The effect of resonation can be clearly distinguished by comparing Fig.5(c) and (d), corresponding to Wi-Max and WLAN, respectively. Note that in WLAN, resonation reduces the in-band quantization error power as compared to Wi-Max. This is illustrated in Fig.6 where the *SNDR* is represented versus the input signal amplitude. Note that the effective resolution for WLAN is approximately 9dB larger than that for Wi-Max.

The sensitivity to noise leakages due to capacitor mismatch has been studied on the basis of Monte Carlo simulation. Fig.7 shows the *SNDR* at -6dBFS obtained for a 50-run Monte Carlo simulation considering a standard deviation of 0.1% in all capacitors. The mean [ $\mu$  (bits)] and the standard deviation ( $\sigma$ ) of the resulting effective modulator resolutions are also shown for each operation mode. Note that the use of resonation in the WLAN mode introduces no appreciable performance degradation when compared to the rest of operation modes.

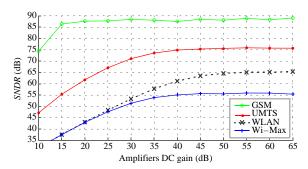

Fig.8 shows the effect of the amplifiers finite DC gain on the modulator effective resolution for all the operation modes. Note that the impact of the amplifiers gain on the modulator performance is considerably lower in GSM when compared to the rest of standards. This is due to the topology used for the  $\Sigma\Delta M$  in the former case (single loop), which does not present the sensitivity to noise leakages inherent to cascade

**Fig. 8:** *SNDR* vs. finite DC gain of the amplifiers (-6dBFS input level).

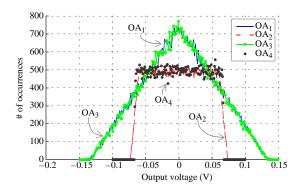

Fig. 9: Histogram of the integrators outputs.

topologies (used in the remaining standards). In the case of UMTS and Wi-Max, there is no appreciable degradation for amplifiers gains above 40dB. This value raises to 50dB for WLAN, which is still not a demanding requirement in practice.

An appealing advantage that comes from the use of unity STFs is the subsequent reduction of the amplifiers output swing. This is illustrated in Fig.9 by plotting the histogram of the integrators outputs obtained from the operation of the proposed modulator in all operation modes. Note that the required output swing is only  $\pm 0.15\,\mathrm{V}$  for the 1st and 3rd operational amplifiers (OA<sub>1</sub> and OA<sub>3</sub>), whereas it reduces to  $\pm 0.10\,\mathrm{V}$  for the 2nd and 4th ones (OA<sub>2</sub> and OA<sub>4</sub>). This translates into an excellent linearity behavior for the proposed architecture.

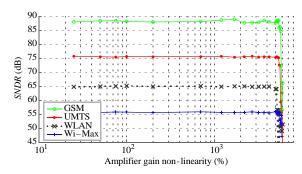

The latter is illustrated in Fig.10 by plotting the effect of the amplifier gain non-linearity on the modulator SNDR. In this simulation, a finite gain of 55dB is considered for all amplifiers, while varying the 2nd-order non-linearity of the DC gain for the amplifiers in the first stage of the cascade. Note that the robustness of the proposed  $\Sigma\Delta M$  to non-linearities is quite high, even if resonation is used to increase the effective modulator resolution.

**Fig. 10:** *SNDR* vs. non-linearity of the amplifier gain (-6dBFS input level, 55-dB amplifier gain).

#### V. CONCLUSIONS

A new multi-functional cascade  $\Sigma\Delta M$  architecture has been presented. This architecture is capable to reconfigure the order of the quantization noise filtering to resonate through switchable feedback inter-stage paths. Additionally, it achieves high linearity with reduced output swing requirements by using unity STFs in both cascaded stages. These characteristics make the proposed modulator very appropriate for the implementation of low-voltage multi-mode A/D conversion, where the resolution of wideband standards can be easily increased by means of adaptive global resonation. A case study covering GSM, UMTS, Wi-Max and WLAN standards has been discussed in order to show the capabilities of the proposed modulator to perform the A/D conversion in future 4G wireless multi-standard hand-held devices.

## VI. REFERENCES

- [1] X. Li and M. Ismail: Multi-standard CMOS wireless receivers: analysis and design. Kluwer Academic Publishers, 2002.

- [2] T. Burger et al.: "A 13.5mW 185-Msample/s ΔΣ Modulator for UMTS/GSM Dual-Standard IF Reception". IEEE J. of Solid-State Circuits, pp. 1868-1878, Dec. 2001.

[3] T.M.R. Miller et al.: "A Multibit Sigma-Delta ADC for

- [3] T.M.R. Miller et al.: "A Multibit Sigma-Delta ADC for Multimode Receivers". IEEE J. of Solid-State Circuits, pp. 475-482, March 2003.

- [4] G. Gomez et al.: "A 1.5V 2.4/2.9mW 79/50dB DR ΣΔ Modulator for GSM/WCDMA in 0.13μm Digital Process". Proc. of ISSCC, pp. 242-490, 2002.

[5] A. Dezzani et al.: "A 1.2-V Dual-Mode WCDMA/GPRS

- [5] A. Dezzani et al.: "A 1.2-V Dual-Mode WCDMA/GPRS ΣΔ Modulator". Proc. of ISSCC, pp. 58-59, 2003.

[6] J.H. Shim et al.: "A Third-Order ΣΔ Modulator in 0-18-μm

- [6] J.H. Shim *et al.*: "A Third-Order ΣΔ Modulator in 0-18-μm CMOS With Calibrated Mixed-Mode Integrators". *IEEE J. of Solid-State Circuits*, pp. 918-925, April 2005.

- [7] J. Lim et al.: "A Low-Power Sigma-Delta Modulator for Wireless Communication Receivers using Adaptive Biasing Circuitry and Cascaded comparator scheme". Analog Integrated Circuits and Signal Processing, pp. 359-365, Sept. 2006.

- [8] T. Christen et al.: "A 0.13μm CMOS EDGE/UMTS/WLAN Tri-Mode ΣΔ ADC with -92dB THD". Proc. of ISSCC, pp. 240-241, 2007.

[9] A. Morgado et al.: "An Adaptive ΣΔ Modulator for

- [9] A. Morgado et al.: "An Adaptive ΣΔ Modulator for Multi-Standard Hand-held Wireless Devices". Proc. of ASSCC, pp. 232-235, November 2007.

- [10] J. Silva et al.: "Wideband low-distortion delta-sigma ADC topology". IEE Electronics Letters, vol. 37, pp. 737-738, June 2001.

- [11] M. Sanchez-Renedo et al.: "A 2-2 Discrete Time Cascaded ΣΔ Modulator With NTF Zero Using Interstage Feedback". Proc. of ICECS, pp. 954-957, 2006.

- [12] J. Silva, *High-Performance Delta-Sigma Analog-to-Digital Converters*. Ph.D. Thesis, Oregon State University, 2004.

[13] J. Ruíz-Amaya *et al.*: "High-level synthesis of

- [13] J. Ruíz-Amaya et al.: "High-level synthesis of switched-capacitor, Switched-Current and Continuous-Time ΣΔ Modulators Using SIMULINK-Based Time-Domain Behavioral Models". IEEE Trans. on Circuits and Systems-I, vol. 52, pp. 1795-1810, Sept. 2005.