#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/107784

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Energy-Aware Performance Engineering in High Performance Computing

by

### Stephen Ian Roberts

A thesis submitted to The University of Warwick in partial fulfilment of the requirements  $\qquad \qquad \text{for admission to the degree of}$

**Doctor of Philosophy**

## Department of Computer Science

The University of Warwick

June 2017

#### **Abstract**

Advances in processor design have delivered performance improvements for decades. As physical limits are reached, however, refinements to the same basic technologies are beginning to yield diminishing returns. Unsustainable increases in energy consumption are forcing hardware manufacturers to prioritise energy efficiency in their designs. Research suggests that software modifications will be needed to exploit the resulting improvements in current and future hardware. New tools are required to capitalise on this new class of optimisation.

This thesis investigates the field of energy-aware performance engineering. It begins by examining the current state of the art, which is characterised by adhoc techniques and a lack of standardised metrics. Work in this thesis addresses these deficiencies and lays stable foundations for others to build on.

The first contribution made includes a set of criteria which define the properties that energy-aware optimisation metrics should exhibit. These criteria show that current metrics cannot meaningfully assess the utility of code or correctly guide its optimisation. New metrics are proposed to address these issues, and theoretical and empirical proofs of their advantages are given.

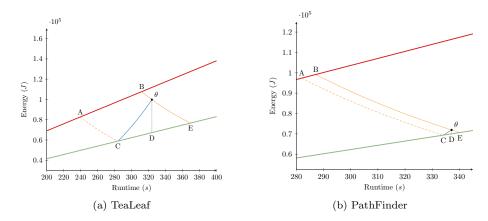

This thesis then presents the Power Optimised Software Envelope (POSE) model, which allows developers to assess whether power optimisation is worth pursuing for their applications. POSE is used to study the optimisation characteristics of codes from the Mantevo mini-application suite running on a Haswell-based cluster. The results obtained show that of these codes TeaLeaf has the most scope for power optimisation while PathFinder has the least.

Finally, POSE modelling techniques are extended to evaluate the systemwide scope for energy-aware performance optimisation. System Summary POSE allows developers to assess the scope a system has for energy-aware software optimisation independent of the code being run.

#### Acknowledgements

I am indebted to many people for their support, guidance and friendship during my time at the University of Warwick. It gives me great pleasure to acknowledge a small number of them here.

First and foremost I am grateful to my supervisor, Prof. Stephen Jarvis, who gave me the opportunity to undertake this research. He has remained a constant source of advice and encouragement throughout my Ph. D.

I am also extremely grateful to Dr. Suhaib Fahmy for his help and guidance. Suhaib has always gone the extra mile to help, and my research into optimisation metrics in particular would not have been possible without his input.

I would like to thank my lab partners and colleagues in the Department of Computer Science, including Dr. Steven Wright, Dr. Philip Taylor, Dr. Richard Bunt, Dr. Arshad Jhumka, Dr. Adam Chester, Tim Law, Huanzhou Zhu and Andrew Owenson. Their perspectives and insights have proven invaluable.

I also wish to thank the Center of Information Services and High Performance Computing (ZIH) at TU Dresden. Much of this work has benefited from access to their power instrumented supercomputing hardware. A special vote of thanks is owed to Thomas Ilsche for his patience and generosity.

Returning to academia from industry was a leap of faith which would not have been possible without the support of past colleagues. Special thanks in this regard go to Dr. Enrico Scalavino for our many discussions on the subject. Thanks also go to Zheng Huang, Nic Quilici and Amaury Chamayou.

Finally, I would like to thank my friends and family for their support and kindness. Mum, Dad, my cousins David, Dereck and William, my sister Annie and aunt Ann, and also to my uncle Grahame, who sadly left us before this work was finished. This thesis is dedicated to them, with love and gratitude.

#### **Declarations**

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has been composed by myself and has not been submitted in any previous application for any degree.

Parts of this thesis have been published by the author:

- [104] S. I. Roberts, S. A. Wright, D. Lecomber, C. January, J. Byrd, X. Oró, and S. A. Jarvis. POSE: A Mathematical and Visual Modelling Tool to Guide Energy Aware Code Optimisation. In *Proceedings of the 6th International* Green and Sustainable Computing Conference (IGSC '15), December 2015

- [105] S. I. Roberts, S. A. Wright, S. A. Fahmy, and S. A. Jarvis. Metrics for Energy-Aware Software Optimisation. Lecture Notes in Computer Science (LNCS), 10266:413–430, June 2017

- [103] S. I. Roberts, S. A. Wright, S. A. Fahmy, and S. A. Jarvis. The Power-Optimised Software Envelope. ACM Transactions on Architecture and Code Optimisation, in preparation

## Sponsorship and Grants

The research presented in this thesis was made possible in part by the support of the following benefactors:

• Technology Strategy Board project number 131197 (Energy-Efficiency Tools for High-Performance Multi- and Many-core Applications).

# Abbreviations

| ADP            | Area Delay Product                           |

|----------------|----------------------------------------------|

| $\mathbf{ALU}$ | Arithmetic Logic Unit                        |

| ATX            | Advanced Technology eXtended                 |

| CISC           | Complex Instruction Set Computing16          |

| CMOS           | Complimentary Metal Oxide Semiconductor      |

| CPU            | Central Processing Unit                      |

| CRCW           | Concurrent Read Concurrent Write29           |

| CREW           | Concurrent Read Exclusive Write              |

| DAG            | Directed Acyclic Graph24                     |

| DMM            | Distributed Memory Machine                   |

| DVFS           | Dynamic Voltage and Frequency Scaling        |

| EDD            | Energy Delay Distance                        |

| EDP            | Energy Delay Product                         |

| EDS            | Energy Delay Sum                             |

| ENIAC          | Electronic Numerical Integrator and Computer |

| ERCW           | Exclusive Read Concurrent Write              |

| EREW           | Exclusive Read Exclusive Write               |

| FLOPS          | Floating Point Operations per Second         |

| FoM            | Figure of Merit                              |

| FPE            | Feasible Performance Envelope                |

| FPGA           | Field-Programmable Gate Array                |

| GPU            | Graphics Processing Unit. 2                  |

| HDEEN          | 4 High Density Energy Efficiency Monitoring        |

|----------------|----------------------------------------------------|

| HPC            | High Performance Computing                         |

| IBS            | Instruction Based Sampling                         |

| IC             | Integrated Circuit                                 |

| ICC            | Intel C++ Compiler                                 |

| ILP            | Instruction Level Parallelism                      |

| IPS            | Instructions Per Second                            |

| ITUE           | Information Technology Power Usage Effectiveness17 |

| MIMD           | Multiple Instruction Multiple Data                 |

| MISD           | Multiple Instruction Single Data                   |

| MOO            | Multi-Objective Optimisation15                     |

| MSR            | Model Specific Register13                          |

| MTTF           | Mean Time To Failure                               |

| NASA           | National Aeronautics and Space Administration      |

| NUMA           | Non-Uniform Memory Access                          |

| PDP            | Power Delay Product                                |

| PEBS           | Precise Event-Based Sampling                       |

| POSE           | Power Optimised Software Envelope                  |

| PRAM           | Parallel Random Access Machine                     |

| PUE            | Power Usage Effectiveness                          |

| RAPL           | Running Average Power Limit                        |

| RISC           | Reduced Instruction Set Computing                  |

| SIMD           | Single Instruction Multiple Data                   |

| SISD           | Single Instruction Single Data                     |

| $\mathbf{SMM}$ | Shared Memory Machine                              |

| SMP  | Symmetric Multiprocessing                 |

|------|-------------------------------------------|

| SST  | Structural Simulation Toolkit             |

| STFC | Science and Technology Facilities Council |

| TCO  | Total Cost of Ownership4                  |

| TDP  | Thermal Design Power                      |

| TLP  | Thread Level Parallelism                  |

# Contents

| A                         | bstra | act                                | i            |

|---------------------------|-------|------------------------------------|--------------|

| D                         | edica | ation                              | ii           |

| $\mathbf{A}$              | ckno  | wledgements                        | ii           |

| D                         | eclar | ations i                           | $\mathbf{v}$ |

| $\mathbf{S}_{\mathbf{I}}$ | oonso | orship and Grants                  | v            |

| A                         | bbre  | viations                           | ⁄i           |

| Li                        | st of | Figures xi                         | v            |

| Li                        | st of | Tables x                           | v            |

| 1                         | Intr  | $\operatorname{roduction}$         | 1            |

|                           | 1.1   | Motivation                         | 3            |

|                           | 1.2   | Thesis Contributions               | 5            |

|                           | 1.3   | Thesis Overview                    | 6            |

| 2                         | Ene   | ergy-Aware Performance Engineering | 8            |

|                           | 2.1   | Architectures                      | 8            |

|                           | 2.2   | Measurement                        | 0            |

|                           | 2.3   | Benchmarking                       | 3            |

|                           | 2.4   | Metrics                            | 5            |

|                           |       | 2.4.1 Figure Of Merit Metrics      | 5            |

|                           |       | 2.4.2 Non-Figure of Merit Metrics  | 6            |

|                           | 2.5   | Profiling                          | 9            |

|                           | 2.6   | Modelling                          | 1            |

|   |     | 2.6.1      | Heuristic Modelling                      | 21 |

|---|-----|------------|------------------------------------------|----|

|   |     | 2.6.2      | Analytical Modelling                     | 28 |

|   |     | 2.6.3      | Simulation                               | 30 |

|   | 2.7 | Optim      | isation                                  | 31 |

|   |     | 2.7.1      | Energy-Aware Optimisation                | 32 |

|   | 2.8 | Summ       | ary                                      | 33 |

| 3 | Ene | ergy Ef    | ficiency in Computer Systems             | 34 |

|   | 3.1 | Fabric     | ation Technologies                       | 34 |

|   | 3.2 | CMOS       | S Digital Logic                          | 37 |

|   |     | 3.2.1      | Arithmetic Logic Unit Design             | 38 |

|   | 3.3 | CMOS       | S Power Draw                             | 40 |

|   | 3.4 | Archit     | ectural Energy Efficiency Features       | 42 |

|   |     | 3.4.1      | Multi-core Processors                    | 43 |

|   |     | 3.4.2      | Clock Gating                             | 43 |

|   |     | 3.4.3      | Dynamic Voltage and Frequency Scaling    | 44 |

|   |     | 3.4.4      | Heterogeneous Computing                  | 44 |

|   | 3.5 | Energ      | y Efficiency Trends                      | 45 |

|   | 3.6 | Summ       | ary                                      | 47 |

| 4 | Met | trics fo   | or Energy-Aware Software Optimisation    | 48 |

|   | 4.1 | Delay      | Product Metrics                          | 48 |

|   | 4.2 | Softwa     | are Optimisation Metrics                 | 51 |

|   | 4.3 | $Et^n \to$ | valuation                                | 54 |

|   |     | 4.3.1      | Justification of $Et^n$                  | 59 |

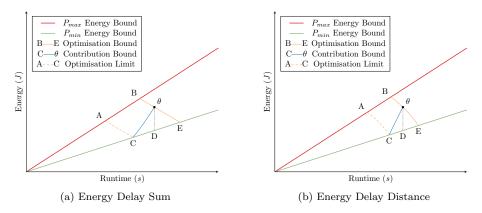

|   | 4.4 | Propo      | sed Metrics                              | 60 |

|   |     | 4.4.1      | Proposed Metric 1: Energy Delay Sum      | 60 |

|   |     | 4.4.2      | Proposed Metric 2: Energy Delay Distance | 63 |

|   | 4.5 | Case S     | Study                                    | 65 |

|   | 4.6 | Summ       | ary                                      | 68 |

| 5 | Pow | ver Op | timised Software Envelope Model           | 70  |

|---|-----|--------|-------------------------------------------|-----|

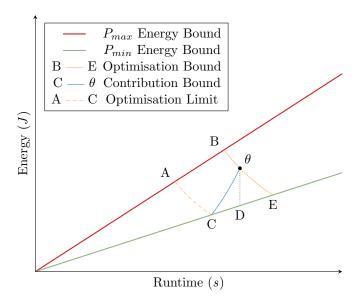

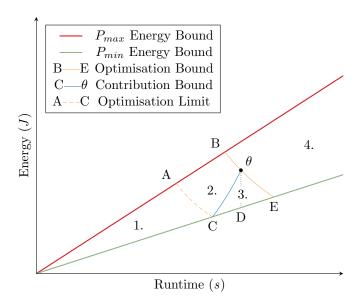

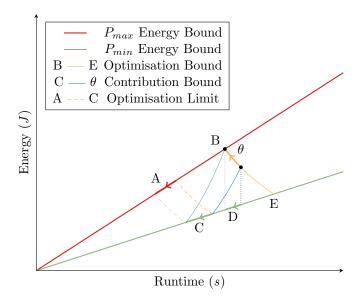

|   | 5.1 | Model  | Construction                              | 71  |

|   |     | 5.1.1  | Feasible Performance Envelope             | 71  |

|   |     | 5.1.2  | Optimisation Bound                        | 72  |

|   |     | 5.1.3  | Contribution Bound                        | 74  |

|   |     | 5.1.4  | Optimisation Limit                        | 77  |

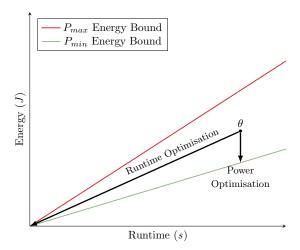

|   | 5.2 | POSE   | Insights                                  | 78  |

|   | 5.3 | POSE   | Models for Novel Metrics                  | 80  |

|   |     | 5.3.1  | Energy Delay Sum POSE                     | 82  |

|   |     | 5.3.2  | Energy Delay Distance POSE                | 85  |

|   | 5.4 | POSE   | Investigation                             | 90  |

|   |     | 5.4.1  | Feasible Performance Envelope             | 91  |

|   |     | 5.4.2  | POSE Models for Code Optimisation         | 93  |

|   |     | 5.4.3  | POSE Models for Frequency Scaling         | 95  |

|   |     | 5.4.4  | POSE Models for Distributed Codes         | 98  |

|   | 5.5 | Summ   | ary                                       | 99  |

| 6 | Sys | tem Sı | ummary POSE                               | 101 |

|   | 6.1 | System | n Summary POSE Derivation                 | 101 |

|   | 6.2 | System | n Summary POSE for Novel Metrics          | 105 |

|   |     | 6.2.1  | Energy Delay Sum System Summary POSE      | 106 |

|   |     | 6.2.2  | Energy Delay Distance System Summary POSE | 107 |

|   | 6.3 | System | n Summary POSE Investigation              | 108 |

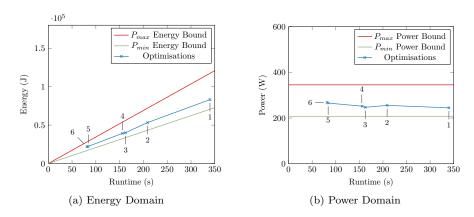

|   | 6.4 | Optim  | isation Study                             | 110 |

|   | 6.5 | Summ   | ary                                       | 113 |

| 7 | Con | clusio | ns and Future Work                        | 116 |

|   | 7.1 | Thesis | Limitations                               | 118 |

|   | 7.2 | Future | e Work                                    | 119 |

|   | 7.3 | Final  | Remarks                                   | 120 |

| Re           | References 122                           |     |  |

|--------------|------------------------------------------|-----|--|

| Aı           | Appendices 138                           |     |  |

| $\mathbf{A}$ | POSE Model Summary for Different Metrics | 138 |  |

|              | A.1 $Et^n$ POSE                          | 138 |  |

|              | A.2 Energy Delay Sum POSE                | 138 |  |

|              | A.3 Energy Delay Distance POSE           | 139 |  |

| В            | Mantevo Suite POSE Models                | 140 |  |

| $\mathbf{C}$ | Mantevo Benchmark Input Parameters       | 144 |  |

# List of Figures

| 2.1 | Crossbar Network Topology                        | 9  |

|-----|--------------------------------------------------|----|

| 2.2 | PowerMon Current Sense Resistor Circuit          | 11 |

| 2.3 | Amdahl's Law Speed-up Limits                     | 23 |

| 2.4 | Amdahl's Law Efficiency Limits                   | 23 |

| 2.5 | Work, Span and Maximum Cut                       | 25 |

| 2.6 | Example Roofline Model                           | 26 |

| 2.7 | Powerline Model                                  | 27 |

| 2.8 | PRAM Abstract Machine Model                      | 29 |

| 3.1 | Power Density Trends, based on data from [22]    | 36 |

| 3.2 | Synchronous Sequential Logic                     | 37 |

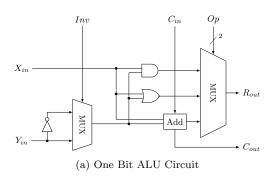

| 3.3 | One Bit ALU Schematic                            | 38 |

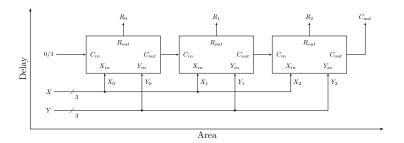

| 3.4 | Combinatorial ALU                                | 39 |

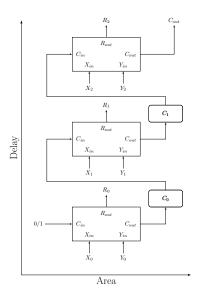

| 3.5 | Sequential ALU                                   | 40 |

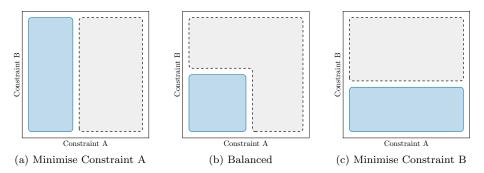

| 4.1 | Design Trade-Off Constraint Diagram              | 49 |

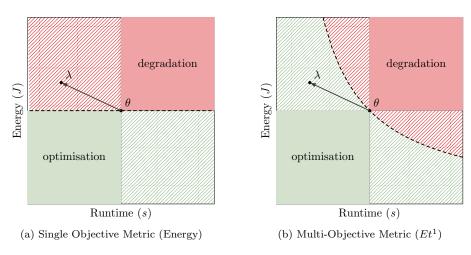

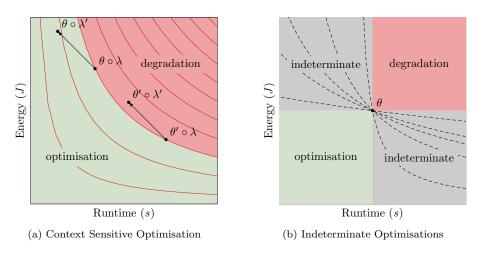

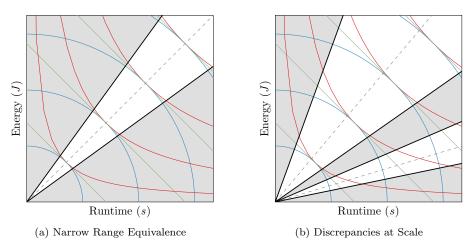

| 4.2 | Metric Optimisation Regions                      | 52 |

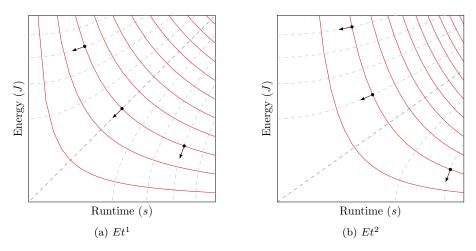

| 4.3 | $Et^n$ Metric Fitness Landscapes                 | 53 |

| 4.4 | $Et^n$ Optimisation Instability                  | 57 |

| 4.5 | Power-Limited Isometric Lines                    | 60 |

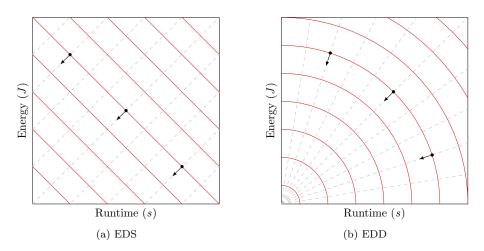

| 4.6 | Proposed Metrics Fitness Landscapes              | 61 |

| 4.7 | Energy Delay Distance Instability                | 65 |

| 5.1 | $Et^2$ Power Optimised Software Envelope         | 72 |

| 5.2 | $Et^2$ Power Optimised Software Envelope Regions | 79 |

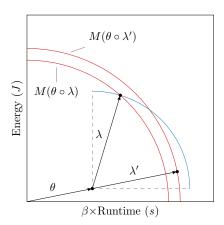

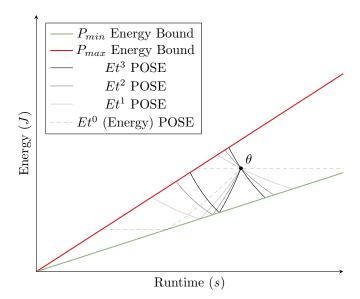

| 5.3 | $Et^n$ POSE Model Tunability                     | 81 |

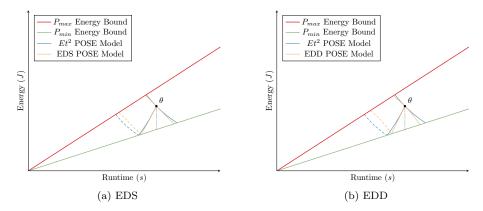

| 5 4 | POSE Models for Novel Metrics                    | 82 |

| 5.5 | Comparison of POSE Models for Different Metrics 89                |

|-----|-------------------------------------------------------------------|

| 5.6 | $Et^2$ POSE Comparison of TeaLeaf and PathFinder 96               |

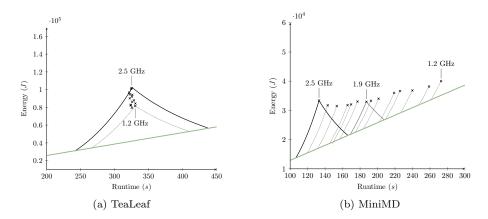

| 5.7 | $Et^2$ POSE for P-State Optimisation of TeaLeaf and MiniMD $$ 97  |

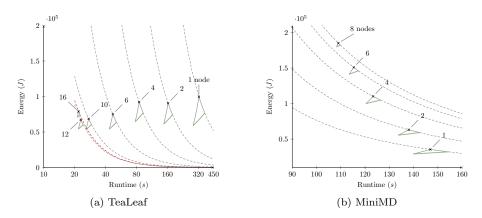

| 5.8 | $Et^2$ POSE for Multi-Node Runs of Tea<br>Leaf and MiniMD $\ $ 98 |

|     |                                                                   |

| 6.1 | $Et^2$ System Summary POSE Intuition                              |

| 6.2 | Optimisation Limits                                               |

| 6.3 | 1D Trapezoidal Decomposition                                      |

|     |                                                                   |

# List of Tables

| 3.1 | Pleiades CPU Upgrades                                          |

|-----|----------------------------------------------------------------|

| 4.1 | Single Node Code Costs                                         |

| 4.2 | MiniMD Multi-Node Costs                                        |

| 5.1 | Single Node Feasible Performance Envelope Parameters 93        |

| 5.2 | Code Metrics for $S=2.5\mathrm{GHz},C=24\ldots\ldots94$        |

| 5.3 | $Et^2$ POSE Model Summaries                                    |

| 5.4 | MiniMD POSE Models for Novel Metrics 95                        |

| 6.1 | Optimisation Impact                                            |

| B.1 | $Et^2$ POSE Model Summaries for Remaining Codes                |

| B.2 | EDS POSE Model Summaries ( $\alpha = 1, \beta = 900$ )         |

| В.3 | EDD POSE Model Summaries ( $\alpha = 1, \beta = 519.615$ ) 143 |

| C.1 | Application Run Parameters                                     |

## CHAPTER 1

#### Introduction

Scientific computing and numerical simulation have become indispensable tools in many areas of science and engineering. Simulations allow scientists to test their theories in domains where physical experimentation would be prohibitively costly, impractical, or dangerous. As a result, computational methods have joined theory and experiment as central pillars of scientific investigation [57].

Maximising performance is paramount in scientific computing. Higher performance means more calculations can be carried out, allowing scientists to increase the size, complexity or resolution of their simulations. This demand for performance has led to the development of *supercomputers*, large machines orders of magnitude more powerful than desktop computers.

Supercomputers are typically constructed by linking many smaller nodes together to form a *cluster*. Specialist tools and programming models are then used to write software that can be run on several nodes in parallel. These nodes communicate over an *interconnect* network, collaborating to run simulations and produce results faster than a single node could manage in isolation.

The field of High Performance Computing (HPC) exists to improve the performance of supercomputers and the software which they run. HPC covers a broad spectrum of disciplines. At one extreme, domain experts write high-level simulation software to model phenomena of interest. At the other, hardware engineers design the processors and other components that make up supercomputers. *Performance engineering* bridges the gap between these extremes, seeking ways to optimise software to make better use of the available hardware.

Moore's law states that transistor density doubles every 18-24 months [93]. This trend has delivered exponential increases in Central Processing Unit (CPU) performance for decades. Dennard scaling, which states that the power use of transistors is proportional to their size [28], kept energy consumption in check as increasing numbers of transistors were packed into CPUs. Together, these laws led to a period known as the "Free Lunch", when rising clock speeds delivered regular performance increases with no additional power cost.

Dennard scaling ended around 2006 [52], and Moore's law is also showing signs of failure [116]. Refinements to the same underlying technologies are yielding diminishing returns, and the "Free Lunch" is now over [115]. Energy consumption is rapidly becoming a limiting factor for continued progress in scientific computing as a result [109].

The end of Dennard scaling has forced hardware engineers to prioritise energy efficiency in their designs. This has lead to both modifications in existing platforms as well as the development of new HPC technologies. Some of these novel technologies are pre-existing products which have been repurposed for scientific computing. Examples of this kind include Field-Programmable Gate Arrays (FPGAs) [29], general purpose Graphics Processing Units (GPUs) [46] and Intel's Xeon Phi coprocessors [21]. Others, like NEC's Aurora Vector Engine, were designed specifically for the HPC market.

Performance engineers are also feeling the effects of this drive towards energy efficiency. One obvious example is the emergence of new programming models like OpenACC, OpenCL and CUDA which allow developers to target the novel energy-efficient accelerator technologies listed above. More subtly, research suggests that targeted modifications to existing software will be required to fully exploit the energy efficiency improvements in modern hardware [111]. New energy-aware performance engineering techniques are being developed to identify and capitalise on this new class of optimisation.

This work investigates how conventional performance engineering techniques can be adapted to support energy-aware software optimisation. It highlights challenges which must be overcome before this new class of optimisation can be widely exploited. It also seeks to quantify the benefits which can realistically be expected as a result of energy-aware optimisation.

#### 1.1 Motivation

Moore's law was first proposed in 1965 and quickly became a self-fulfilling prophecy as hardware manufacturers were forced to keep up with it or face being overtaken by their competition. This resulted in a doubling of transistor density every 18-24 months, fuelled by advances in Integrated Circuit (IC) fabrication, circuit design and processor architectures. Moore's Law has driven the development of computer hardware in this way for decades.

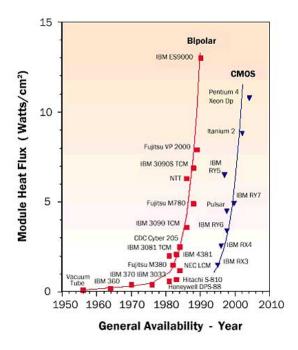

The area occupied by individual transistors halves with every doubling of transistor density. Power density (i.e. the rate of power consumption per unit area) remained constant under Dennard scaling, so the power consumed by each transistor was also halved. This in turn led to faster clock speeds as the maximum switching frequency of a transistor is inversely proportional to its peak power consumption [61].

Clock speeds increased exponentially with each new generation of processors while Dennard scaling persisted. The "Free Lunch" period resulted from this link between transistor density and processor speed. The link was broken when Dennard scaling ended, causing clock speeds to stagnate even as transistor densities continued to rise. Hardware designers now rely on architectural changes such as vectorisation, superscalar architectures and multiple cores to deliver performance improvements [95].

Higher clock speeds deliver performance improvements without developer input, hence the term "Free Lunch". Conversely, software modifications are required to take advantage of novel hardware features. New instructions are needed for Single Instruction Multiple Data (SIMD) vectorisation, for example, and applications must be parallelised to run on multiple cores. Although compilers can perform some of this work, performance engineers typically have to rewrite their applications in order to achieve maximum performance [75].

Processor power density has been rising since the end of Dennard scaling. This trend has been partially offset by one-off advances in fabrication processes and the use of exotic materials in transistors. Such advances only provide temporary reprieve, however, and the overall trend is expected to continue [37].

Rising power density poses a number of challenges to the field of HPC. First, energy costs are soaring as increased per-processor power draw is compounded by the growing number of processors used in modern supercomputers. These costs already represent a large share of the Total Cost of Ownership (TCO) for supercomputing systems and are expected to rise still further [108].

Secondly, higher power densities lead to increased operating temperatures, which can cause problems with hardware reliability [112]. At present, around 20% of the available compute time on large-scale supercomputers is lost due to hardware failures [34]. This trend is also exacerbated by high processor counts, as shortening the Mean Time To Failure (MTTF) of individual processors has a cumulative effect on the MTTF of machines as a whole.

Finally, power density cannot continue to grow indefinitely. There are limits to how much power can be delivered to processors and how quickly the resulting heat can be removed. If performance improvements cannot be decoupled from increasing power density then these too will come to an end.

Hardware designers are responding to these challenges by prioritising energy efficiency in their processor designs. Improving energy efficiency through architectural changes closely parallels the way in which performance improvements are currently delivered. The expected outcome is also the same; code changes will be needed in order to maximise the benefits of energy efficient hardware features. Energy-aware performance engineering techniques will therefore be required as power becomes a first-class constraint in HPC.

The US Department of Energy has identified energy efficiency as a primary constraint for exascale systems [109]. New performance engineering approaches will be required soon if the current rate of progress in HPC is to be maintained. Fortunately, performance engineers have built up a wealth of tools and experi-

ence adapting software to maximise performance on new hardware. This thesis aims to show how these existing tools and techniques can be updated to consider energy as well as runtime.

Energy-aware performance optimisation is still in its infancy, characterised by ad-hoc techniques and a lack of standardised metrics. This thesis contributes a set of metrics which are shown to be more suitable for use in guiding energyaware optimisation than current alternatives. It also presents a pair of related approaches for identifying the potential for energy-aware optimisation, one for individual codes and the other for entire systems.

The techniques described in this thesis are notable for their generality. They are not platform or application specific and impose very few prerequisites on their use. Despite this, they are able to provide immediate, actionable insights to performance engineers and software developers.

#### 1.2 Thesis Contributions

This thesis makes the following specific contributions:

- New metrics are developed to guide and assess energy-aware code optimisations. In the absence of better alternatives, performance engineers have turned to metrics developed by the hardware community. These hardware metrics are ill-suited to software optimisation, and the lack of standardisation makes comparing results between studies impossible. This thesis seeks to address both of these shortcomings by introducing a common set of metrics along with rigorous justification of their utility.

- This thesis presents the Power Optimised Software Envelope (POSE), a

model which helps performance engineers to determine whether energy

or runtime optimisation will provide the greatest benefits for their code.

The POSE model is platform agnostic, meaning it can be applied to any

hardware and at any scale.

• The POSE model is extended to provide a model for system-wide power optimisation characteristics. System Summary POSE is able to derive upper limits for the benefit of energy-aware software optimisation on a given system. This allows developers to determine how amenable a system is to energy optimisation and hence whether it may be worth pursuing on their chosen platform in general, independent of any specific codes.

#### 1.3 Thesis Overview

The remainder of this thesis is structured as follows:

Chapter 2 provides an account of core concepts, techniques and terminology employed in the field of HPC. Contemporary performance engineering tools and practices are described, and their suitability for energy-aware software optimisation is assessed. This chapter includes an overview of relevant performance engineering literature.

Chapter 3 details the evolution of parallel computing hardware with an emphasis on energy efficiency. The problems which motivate this work arise because hardware development is failing to maintain past trends in power consumption. This chapter provides a generalised model of hardware power consumption, and introduces features found in modern processors designed to minimise it. A key aim of this chapter is to highlight various ways in which performance engineers can influence energy efficiency.

Chapter 4 examines the metrics currently used to guide energy-aware performance optimisation. A good metric should provide meaningful values for a single experiment, allow fair comparison between experiments, and drive optimisation in a sensible direction. This chapter shows that established metrics are unable to fulfil these basic requirements then proposes new metrics which can.

Chapter 4 concludes with theoretical and empirical proofs of the advantages of these new metrics over established alternatives.

Chapter 5 introduces the POSE model. POSE serves as a preliminary "first cut" modelling technique intended to guide energy-aware optimisation efforts. This model presents an asymptotic analysis of the scope a code has for optimisation in both the power and runtime domains. By identifying the limits of each approach, POSE allows performance engineers to make informed decisions about where to focus their efforts in order to achieve the best results.

Chapter 6 builds on previous chapters by extending POSE to model system-wide optimisation criteria. Conventional POSE models use the runtime and energy costs of a code to calculate the scope that code has for power and runtime optimisation on a given system. Conversely, System Summary POSE is a meta-heuristic which determines the range of results POSE models could produce for a given system. This bound-of-bounds analysis places limits on the system-wide scope for power optimisation independent of any specific codes.

Chapter 7 concludes this work with a summary of results and contributions made, and discusses their implications for performance engineers. It also considers the future direction of energy-aware performance engineering and provides an overview of ongoing and future research.

## CHAPTER 2

#### Energy-Aware Performance Engineering

This chapter introduces core concepts, techniques and terminology in the field of High Performance Computing (HPC). These topics are divided into seven areas, namely: Architectures, Measurement, Metrics, Benchmarking, Profiling, Modelling, and finally Optimisation. Energy-aware performance engineering requires new developments to be made in each of these areas. Recent developments are discussed, and areas where progress is lacking are highlighted.

#### 2.1 Architectures

In simplest terms, supercomputers are nothing more than large collections of processing elements working together to solve complex problems [7]. This description is general enough to encompass the wide range of architectures which have been used to construct HPC systems over the years.

Flynn's taxonomy classifies computer architectures based on how many instructions and data items they can handle concurrently [39]. In this taxonomy, Single Instruction Single Data (SISD) architectures are those which do not exhibit any kind of parallelism. Single Instruction Multiple Data (SIMD) architectures execute their instructions sequentially, but each instruction operates on multiple data elements in parallel. Multiple Instruction Single Data (MISD) architectures execute multiple instructions on the same piece of data in parallel. Finally, Multiple Instruction Multiple Data (MIMD) architectures execute multiple instructions on their own independent data in parallel.

Modern supercomputers predominantly use MIMD architectures [102]. These systems can be divided into Distributed Memory Machines (DMMs) and Shared Memory Machines (SMMs), depending on how their memory is organised.

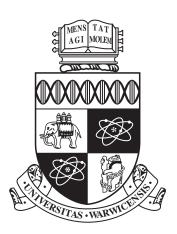

Figure 2.1: Crossbar Network Topology

DMMs consist of multiple compute nodes connected to each other through a shared interconnect. These nodes are independent units with their own processors, memory and peripherals. Data held by a node in local memory is private and cannot be accessed directly by other nodes. Explicit message passing protocols are used to allow groups of nodes to collaborate and share data.

SMMs consist of multiple processors all connected to a large pool of shared memory made up of many discrete memory modules. A common address space allows processors to access shared data transparently, regardless of its physical location. SMMs are further sub-divided into Symmetric Multiprocessing (SMP) and Non-Uniform Memory Access (NUMA) machines.

Processors in SMP machines have fast access to all areas of shared memory. Conceptually, all  $M \times N$  pairs of memory modules and processors are connected by a flat network topology like the crossbar network shown in Figure 2.1. The scalability of SMP machines is limited by resource contention and the need for expensive, densely connected interconnects.

NUMA systems improve scalability by giving processors faster access to their own local memory. Other machines can still access this memory, however they must do so over a network. This reduces contention for applications which exhibit data locality as only remote memory accesses travel over the network.

Flynn's taxonomy also applies at the level of individual processors. Modern CPUs support both SIMD and MIMD operations through vector instructions and multiple cores respectively. There are no MISD implementations in widespread use for HPC, however some Field-Programmable Gate Array (FPGA) design patterns come close [5].

An ongoing trend in HPC is the shift towards heterogeneous computing [77]. In addition to conventional CPUs, heterogeneous systems also incorporate specialised compute devices called accelerators or coprocessors to handle particular tasks. Devices like Graphics Processing Units (GPUs), FPGAs and Intel's Xeon Phi coprocessors can be used to speed up execution of computationally intensive codes while also reducing system energy consumption [35].

#### 2.2 Measurement

Accurate measurement is fundamental to performance engineering. Processors incorporate built-in clocks to maintain synchronisation and schedule interrupts. Engineers can use these clocks to measure the runtime performance of their code. Energy monitoring capabilities are also appearing in new processor designs.

Energy is the integral of power over time, or  $E = \bar{P}t$ . Energy consumption cannot be measured directly as a consequence, and must instead be calculated from measurements of power draw and time.

Various methods have been used to measure power draw in HPC systems, both at system and component levels. One approach uses thermal cameras to measure the temperature of different components and hence estimate their power draw. This works because the energy used by computers is converted to waste heat in accordance with the first law of thermodynamics. Mesa-Martinez et al. used thermal cameras and custom heat sinks to measure Central Processing Unit (CPU) power consumption [92], while Hackenberg et al. followed a similar approach to measure system-wide power consumption [48].

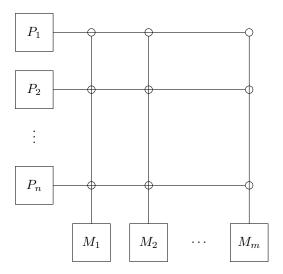

Figure 2.2: PowerMon Current Sense Resistor Circuit

The main advantage of this approach is its high spatial resolution; thermal imagery is able to show how power draw varies between components, and even across different areas of the same component. One disadvantage is poor temporal resolution; materials absorb heat and release it over time, meaning thermal emissions correspond to a moving average of power consumption. Another disadvantage is the requirement for expensive cameras and custom heat sinks, which makes this approach prohibitively costly when applied at scale.

Higher temporal resolution can be obtained at relatively low cost by instrumenting computing platforms with dedicated power sensors. Bedard et al. developed PowerMon, a scheme for measuring component-level power draw in commodity systems [10]. PowerMon works by measuring the voltage drop  $V_{drop}$  across resistors placed inline between the power supply and other system components. These resistors are calibrated to ensure they provide a particular resistance R (0.1  $\Omega$  is typical). Figure 2.2 shows a simplified circuit diagram for their apparatus.

$$I = \frac{V}{R} \tag{2.1}$$

PowerMon uses Ohm's law as stated in Equation 2.1 to calculate current flow I through a resistor based on  $V_{drop}$  and R. Resistors used to measure current

flow in this manner are referred to as 'sense' or 'shunt' resistors. The same amount of current flows through both the sense resistor and the component being measured because current is conserved throughout series circuits. Furthermore, supply voltage  $V_{\rm ref}$  takes on a known value depending on the type of component being powered. The Advanced Technology eXtended (ATX) standard mandates power supply output voltages of 12 V, 5 V, 3.3 V and -12 V, for example [23]. Component power draw can then be calculated as the product of I and  $V_{\rm ref}$  as per Equation 2.2.

$$P = IV (2.2)$$

Sense resistors have three major drawbacks when used in HPC systems. First, some energy is lost as heat within the resistor, increasing overall power draw. Secondly, their resistance varies with temperature, limiting accuracy and introducing non-linearities in their results. Finally, they require direct electrical connections to the power supply and the component being measured. Any short-circuits or other manufacturing defects could easily damage sensitive hardware.

An alternative approach to power measurement relies on the magnetic fields induced when current flows through a wire. Ampere's law for straight conductors, given by Equation 2.3, states that the magnetic field strength  $|\vec{B}|$  at distance r from the wire is proportional to the original current I. The constant  $\mu$  corresponds to the magnetic permiability of air.

$$|\vec{B}| = \frac{\mu I}{2\pi r} \tag{2.3}$$

Hall effect sensors measure magnetic field strength, and can therefore be used to determine current flow while remaining electrically isolated from the conductor. Laros et al. developed PowerInsight, a production quality power monitoring platform which uses Hall effect sensors rather than sense resistors to improve accuracy and reliability [81]. Equation 2.2 is again used to calculate power consumption from current measurements.

Hackenberg et al. instrumented a large HPC cluster called Taurus with commercial power sensors which exploit the Hall effect. The resulting High Density Energy Efficiency Monitoring (HDEEM) infrastructure can be used to measure component-level power and energy consumption across large numbers of nodes at high sample rates [51].

Intel introduced Running Average Power Limit (RAPL) to support power-aware frequency scaling in their Sandy Bridge Processors [27]. As a side effect, performance engineers gained access to an interface capable of reporting CPU power consumption. RAPL exposes a number of Model Specific Registers (MSRs) which can be read by user code to determine the rate of power draw. Early versions of RAPL were model based, but more recent processors incorporate dedicated power sensors.

Other manufacturers have also added power measurement capabilities to their hardware. AMD added a scheme similar to RAPL with equivalent functionality starting with their Bulldozer CPUs [1]. Similar schemes also exist for GPUs [18] and Xeon Phi [82] hardware.

HPC Vendors and system integrators are also beginning to include power monitoring capabilities in their products. Cray's XC line of supercomputers expose energy measurements through systems [55]. Similarly, IBM servers incorporate current measuring hardware based on sense resistors which can be read using their Amester tool [16].

#### 2.3 Benchmarking

Modern processors include hardware designed to accelerate specific operations. Vendors quote *peak performance* figures which assume that all these hardware features can be kept fully occupied. In practice, applications only perform a subset of the relevant operations, and memory bandwidth limits often prevent those features which are used from achieving maximum throughput.

Benchmarks are programs designed to collect real-world performance data.

Performance benchmarks serve a dual purpose. First, benchmarks can be used to measure and compare the performance realistically achievable by different machines and architectures. Secondly, benchmarks serve as good platforms to investigate the effects of different optimisations in a controlled manner.

Micro-benchmarks are simple programs designed to target specific aspects of system performance. Linpack is a well known micro-benchmark which measures a system's capacity for sustained floating point throughput [30]. Linpack results form the basis of the Top500 and Green500 supercomputer rankings [38]. Other micro-benchmarks include STREAM [90], which measures memory bandwidth; SKaMPI, which measures network performance [4]; and IOR, which measures file system performance [110].

Application benchmarks are larger programs which test how well systems handle complex applications. They are often built from simplified versions of production applications in order to ensure realistic workloads. The Mantevo project is a suite of application benchmarks developed at Sandia National Laboratories [56] and used extensively throughout this thesis.

Existing benchmarks can be repurposed for power and energy studies [72], and dedicated power benchmarks have also started to emerge. One example is FIRESTARTER [50], a micro-benchmark specifically designed to trigger nearpeak power consumption across a range of x86\_64 CPUs and NVIDIA GPUs. It contains hand optimised assembly routines which raise processor activity above the level attainable with high level languages. A small assembly microbenchmark designed to minimise power consumption while keeping CPUs active is also described in this thesis.

SPECpower is a commercial benchmarking suite which provides an application benchmark called "SPECPower\_ssj2008" along with a framework for measuring application energy efficiency and performance [79]. The SPECpower benchmark is a Java program which simulates a transactional workflow running under varying amounts of load. It is designed to mimic the behaviour of common enterprise computing applications such as web servers or relational databases which must handle bursts in utilization. SPECpower measures performance at 11 different target loads, starting at 100% utilization and reducing this in steps of 10% until it reaches idle.

#### 2.4 Metrics

Performance engineers use metrics to assess the performance of HPC hardware and software. Individual metrics capture particular properties of a system under investigation. Some of these properties can be measured directly, while others must be derived from multiple observations.

Metrics enable meaningful comparison between different platforms and can be used to quantify the effects of code changes. They can be divided into two categories depending on the types of comparison they allow; namely Figure of Merit (FoM) and Non-FoM metrics.

#### 2.4.1 Figure Of Merit Metrics

Some metrics act as utility functions which measure the cost of running different programs. These FoM metrics can be used to rank different implementations of the same algorithm in order to identify valid optimisations [53]. Runtime and energy consumption are both examples of FoM metrics.

Until recently, runtime optimisation was ubiquitous in HPC while energy optimisation has been confined to domains like embedded systems and mobile robotics. Although energy consumption is becoming a constraint for scientific computing, minimising runtime is still an important optimisation objective.

Optimising software according to multiple properties simultaneously is known as Multi-Objective Optimisation (MOO). MOO requires FoM metrics that strike the right balance between the potentially conflicting requirements imposed by different optimisation objectives.

Gonzalez et al. proposed Energy Delay Product, a FoM metric which combines the energy and runtime costs incurred by processors [45]. Martin et al.

generalised this into the  $Et^n$  family of FoM metrics, with parameters E and t corresponding to energy and time [88]. They argue that  $Et^2$  provides the best balance for microprocessor design. Srinivasan et al. reached the same conclusion, although for slightly different reasons [113].

Many authors have adopted these metrics from the hardware community and applied them to software optimisation problems. Vincent et al. describe a technique which minimises  $Et^1$  using CPU throttling [41]. Bingham and Greenstreet use  $Et^n$  metrics to analyse runtime constraints imposed by a fixed energy budget for various algorithms [12]. Laros et al. use  $Et^n$  metrics to assess a number of production applications and state that  $Et^3$  strikes the right balance between runtime and energy for HPC [80].  $Et^1$  has also been used extensively to quantify the efficiency of resource provisioning and scheduling in cloud computing environments [107, 122].

Bekas and Curioni further generalised  $Et^n$  metrics to the form  $E \cdot f(t)$ , a product between energy and an application dependent function of time [11]. They argue that this formalisation is able to drive software optimisation, assuming an appropriate application specific function f(t) can be identified.

Chapter 4 covers these metrics in more detail. In particular, it shows that metrics originating from the hardware community are not suitable for measuring software performance. It goes on to introduce new metrics which are designed to support energy-aware performance optimisation.

#### 2.4.2 Non-Figure of Merit Metrics

Although FoM metrics are required to identify optimisations, non-FoM metrics also play an important role in performance engineering.

Instructions Per Second (IPS) was an early measure of processor throughput. Although it makes intuitive sense, this metric does not allow comparison between different architectures. Reduced Instruction Set Computing (RISC) processors may need several instructions to perform the same operation as a single instruction on a Complex Instruction Set Computing (CISC) processor,

for example. RISC and CISC processors exhibit different levels of performance at the same IPS rate [66].

Floating Point Operations per Second (FLOPS) is a metric designed to address some of the deficiencies of IPS. It quantifies performance in a portable manner by counting basic arithmetic operations (addition, subtraction, multiplication, division and the like) rather than platform specific instructions. FLOPS captures the throughput of arithmetic operations, or equivalently the rate at which an application converts runtime into floating point results. As a result it can give a better indication of real world performance than IPS, especially on the numerically intensive codes common in HPC.

A related metric is FLOPS per Watt, which combines the number of Floating Point Operations per Second with the rate of power consumption. Despite its name, this metric is quoted in units of Operations per Joule (1 Joule is defined as 1 Watt-Second). While conventional FLOPS measures the number of operations carried out per second elapsed, FLOPS per Watt counts the number of operations carried out per Joule of energy consumed. In effect, FLOPS per Watt measures how effective an application is at converting energy into floating point results.

More recent developments in energy-aware metrics include Power Usage Effectiveness (PUE) and Information Technology Power Usage Effectiveness (ITUE). PUE is the ratio of energy used by computer hardware to total facility energy consumption, which also includes secondary functions like cooling, lighting and power supply losses [87]. A PUE of one is optimal as this would suggest that all energy is being used by computer hardware to complete primary tasks with none being lost to overheads.

A drawback of PUE noted by Patterson et al. is that it treats all energy consumed by computer hardware the same. They contend that this simplification is problematic for HPC, where large systems typically have extensive cooling and power delivery subsystems integrated within them. Their solution is to extend PUE to consider internal subsystems. They call their metric ITUE, which they

describe as "PUE inside the IT". ITUE is defined as the ratio of energy used for compute to total energy use by computer hardware [99].

Metrics are also used to measure the parallel performance and scalability of code. The speed-up  $S_n$  observed by running a program on n processors in parallel is defined as the ratio between its serial runtime  $T_1$  and parallel runtime  $T_n$  as shown by Equation 2.4:

$$S_n = \frac{T_1}{T_n} \tag{2.4}$$

A program that runs n times faster on n processors is said to exhibit *linear* speed-up. This is the maximum possible speed-up which can be attributed to increased processing power. Linear speed-ups are uncommon because they require a code which can be split into multiple independent tasks without any additional overhead being introduced.

Super-linear speed-ups sometimes occur when serial runtime is limited by factors other than processor throughput [120]. A typical example would be a large simulation exhausting memory and causing thrashing as data is repeatedly paged out to disk. Adding nodes will increase the available memory and reduce thrashing, resulting in a super-linear speed-up. It is worth noting that these super-linear speed-ups will cease once the entire simulation fits into memory.

Parallel efficiency measures how well a code makes use of the available hardware. This metric is calculated by dividing total speed-up by processor count, and can therefore be interpreted as per-processor speed-up:

$$E_n = \frac{S_n}{n} = \frac{T_1}{n \cdot T_n} \tag{2.5}$$

Most scientific computing workloads require communication and synchronization between tasks on different processors. These secondary operations increase runtime overheads without contributing to the calculation of results. Codes with low parallel overheads are said to be efficient, while codes which spend much of their time dealing with these overheads are said to be inefficient. The maximum value for efficiency is one, which corresponds to a linear speed-up.

#### 2.5 Profiling

Profilers are tools which measure performance characteristics over one or more runs of a target application. Software developers use these tools to identify performance bottlenecks in their code. Profilers are categorized as either eventbased or sampling, depending on their approach to collecting measurements.

Event-based profilers like VampirTrace [96] measure application state each time a specific event occurs. Samples may be taken when a specific function is called, or when memory is allocated, for example. Runtimes are calculated from timestamps within each sample. Additional metrics like performance counter readings or power consumption may also be recorded.

Profiling events can be specified in several ways. The most direct approach is for developers to manually instrument their code with profiling hooks. Other approaches perform instrumentation at compile time, link time, run time, or a combination of all three.

Event-based profilers take measurements every time a sampling event occurs, making them excellent for capturing detailed traces. Although they are good at timing specific functions, they are less useful for identifying which functions are causing performance issues in the first place. Doing so would require every function call to be instrumented, but this would severely impact performance and lead to skewed results [94].

Statistical profilers sample program state at regular intervals to build up a summary of program behaviour. How often a particular code path is encountered during sampling reflects its overall contribution to runtime.

The accuracy of statistical profilers depends on their sampling frequency. If this is set too high then application performance will suffer, invalidating the results. If it is too low then important details may be missed entirely. It is also important to prevent sampling periods from becoming synchronized with periodic events inside an application. One strategy to avoid these aliasing effects is to offset each sample by a random delay. Statistical profiling is not limited to working in the runtime domain. Some profilers can also operate in periods determined by hardware performance events like cache misses, instructions retired and memory writes. Tools like Perfmon2 [36] can be configured to take samples every time a set number of events has occurred. Intel and AMD chips include hardware support for this through their respective Precise Event-Based Sampling (PEBS) and Instruction Based Sampling (IBS) technologies [117].

The ability to sample in domains other than time allows performance engineers to analyse different aspects of their code's performance. For example, samples taken at fixed increments of cache misses will tend to cluster around code which stresses memory subsystems. If a performance engineer knows their code is memory bound, they can perform this kind of analysis to find optimisation targets which would otherwise be missed.

Statistical profilers operating in intervals of energy would be able to produce a breakdown of energy costs by code path. The PAPI library attempts to provide this functionality [118]. Because energy cannot be measured directly, however, this approach requires profilers to repeatedly sample power draw in order to calculate cumulative energy consumption. This is equivalent to taking samples at short runtime intervals, and then sub-sampling from these based on estimated energy consumption.

The sampling distribution observed from such 'hybrid' approaches is not representative of either energy consumption or runtime. Code paths missed by runtime sampling will never show up in the final results regardless of how much energy they consume. Higher sampling frequencies would reduce this source of error, but would increase sampling overhead leading to skewed results.

Stochastic samplers offer a possible solution which avoids the need to calculate energy altogether. Rather than relying on fixed sampling intervals, samples are taken with probability p < 1 each clock cycle. For fixed p, this scheme produces a runtime sampler with an average sampling interval of 1/p cycles. Alternatively, if p was proportional to instantaneous power draw, then the distri-

bution of samples would correspond to per-instruction power draw. Combining per-instruction power and runtime figures would produce an accurate picture of instruction-level energy consumption.

### 2.6 Modelling

Performance engineers use models to reason about the performance of their codes in a number of ways. First, they can help developers identify factors contributing to poor performance. Secondly, they can be used to predict application performance and scalability characteristics. Finally, they can be used to estimate the performance implications of new hardware architectures.

#### 2.6.1 Heuristic Modelling

Heuristic models provide simplified analogies which help developers understand the performance of their code. This is the most abstract approach to performance modelling as no attempt is made to faithfully represent real systems. Models in this category ignore implementation details in favour of generality, and usually focus on a single aspect of system behaviour.

Understanding how different factors impact performance is the first step towards targeted optimisation. Their ability to produce clear insights without extensive benchmarking or profiling means heuristic models are well suited to the early stages of optimisation.

Arguably the best known heuristic performance model is Amdahl's Law [8], which states that parallelisation gains are limited by the serial portions of a code. A program's serial runtime  $T_1$  can be broken down into  $W_s$  time spent performing inherently serial work and the remaining  $W_p$  time spent performing work which could be parallelised:

$$T_1 = W_s + W_p \tag{2.6}$$

Running a program across n processors in parallel will reduce  $W_p$  while leaving  $W_s$  unchanged, assuming the program is efficiently parallelisable. Excluding the possibility of super-linear speed-ups yields the following expression:

$$T_n \ge W_s + \frac{W_p}{n} \tag{2.7}$$

Amdahl's law is obtained by substituting Equation 2.6 and Equation 2.7 into the definition of speed-up given by Equation 2.4 to yield Equation 2.8 below. It can also be defined in terms of the serial fraction of a code  $f_s$ , where  $W_s = f_s T_1$  and  $W_p = (1 - f_s) T_1$ , resulting in Equation 2.9:

$$S_n \le \frac{W_s + W_p}{W_s + W_p/n} \tag{2.8}$$

$$\Leftrightarrow S_n \le \frac{1}{f_s + (1 - f_s)/n} \tag{2.9}$$

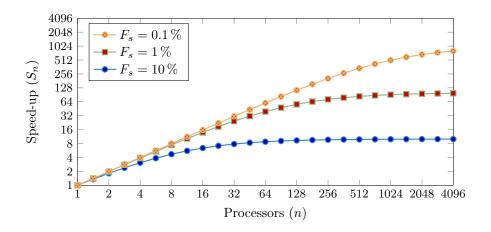

Amdahl's law states that parallel speed-up is limited for all codes with  $f_s > 0$ , even given access to an unlimited number of processors. Figure 2.3 shows how the speed-ups given by Equation 2.9 quickly reach a plateau even for codes with relatively tiny ( $f_s = 0.1\%$ ) serial portions.

Figure 2.4 illustrates an important corollary of Amdahl's law. The parallel efficiency (given by Equation 2.5) of any code with a serial portion will always decrease as more processors are added.

Amdahl's law only takes two parameters, yet despite this simplicity it is able to provide valuable insights into application scalability. If application performance follows Amdahl's law at high processor counts then serial code is the biggest barrier to scalability. Conversely, if observed performance is worse than predicted, then parallel overhead is likely to blame.

Amdahl proposed his law in 1967 to demonstrate "the continued validity of the single processor approach and of the weaknesses of the multiple processor approach" [8]. Despite this, the multiple processor approach went on to become a significant driver of performance improvements in HPC.

Figure 2.3: Amdahl's Law Speed-up Limits

Figure 2.4: Amdahl's Law Efficiency Limits

Gustafson resolved this apparent paradox by observing that problem sizes tend to grow to fill the available computing power [47]. This is because for many HPC codes larger data sets translate to improved resolution, accuracy or scale. Scientific computing workloads typically involve a serial setup phase followed by repeatedly performing the same calculation on each element of a dataset in parallel [9]. Most of the extra work associated with larger data sets can be parallelised, meaning  $W_p$  increases faster than  $W_s$ . A smaller fraction of runtime is spent on serial code when this observation holds, and speed-ups improve as a result.

Amdahl's and Gustafson's laws are both valid, and the choice of which to use depends on circumstances. That said, performance engineers are often tasked with optimising code for a specific platform and problem size. They cannot rely on arbitrarily large problem sizes and processor counts, and are therefore bound by the limits of Amdahl's law in most cases.

Amdahl's and Gustafson's laws only consider perfect parallelism, which applies when tasks can be executed independently and in any order. Imperfect parallelism happens when dependencies impose partial orderings on the tasks performed by a parallel algorithm. While tasks in the same sequence must be executed in order, multiple independent sequences can be processed in parallel.

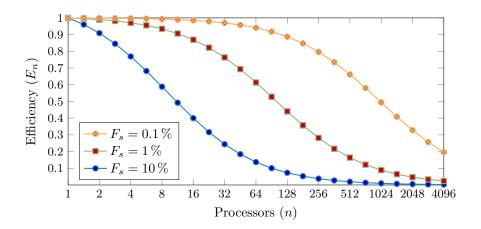

The work-span model represents algorithms as a set of tasks connected by their dependencies to form a Directed Acyclic Graph (DAG). Time  $T_1$  is called an algorithm's work; the cumulative runtime of all its sub-tasks. Time  $T_{\infty}$  is called an algorithm's span; the total runtime of its  $critical\ path$ . The critical path is the longest chain of tasks which must be executed sequentially. Algorithms can never run faster than  $T_{\infty}$ , even with access to unlimited processors.

Figure 2.5 shows an example of the work-span model in which all tasks take unit time. This example does 15 units of work, one for each task, and has a span of 6, one for each task on the critical path highlighted.

The work-span model provides two bounds on parallel performance. The

Figure 2.5: Work, Span and Maximum Cut

ratio of  $T_1$  and  $T_{\infty}$  provide the upper bound to speed-up shown by Equation 2.10:

$$S_n \le \frac{T_1}{T_{\infty}} \tag{2.10}$$

The bound given by Equation 2.11 comes from examining the best case scenario, that all  $T_1 - T_{\infty}$  work off the critical path can be perfectly parallelised.

$$T_{n} \geq T_{\infty} + \frac{T_{1} - T_{\infty}}{n}$$

$$\Leftrightarrow T_{n} \geq \frac{T_{1} + (n-1)T_{\infty}}{n}$$

$$\therefore S_{n} \leq \frac{nT_{1}}{T_{1} + (n-1)T_{\infty}}$$

(2.11)

Work span DAGs can also be used to find the maximum degree of parallelism exhibited by an algorithm. The maximum cut of the DAG (or more precisely of its conjugate, i.e. cutting across nodes rather than edges) corresponds to the largest number of tasks which can be executed concurrently. The red dashed line in Figure 2.5 shows that at most 5 processors can be kept active at any one time. Any processors added above this limit will remain idle.

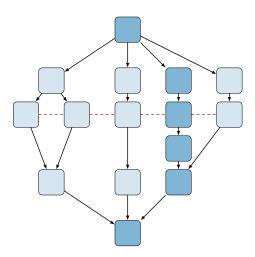

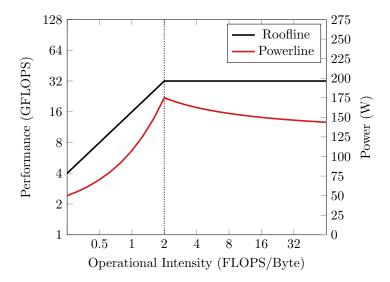

Roofline is a more recent heuristic model which frames application performance in terms of two system bottlenecks, namely off-chip memory bandwidth

Figure 2.6: Example Roofline Model

and floating point performance [121]. Operational intensity, the ratio between work done and memory traffic, is then used to determine whether a code is compute or memory bound.

Figure 2.6 shows an example of the Roofline model. Horizontal lines correspond to floating point performance limits and diagonal ones to memory bandwidth limits. A Roofline consists of one performance and one memory limit. Platforms can exhibit many different Rooflines depending on which hardware performance features can be used.

The Floating Point (FP) limits shown in Figure 2.6 are: Thread Level Parallelism (TLP), corresponding to the maximum performance of simple multi-threaded programs; TLP plus Instruction Level Parallelism (ILP), the maximum performance of multi-threaded programs which use hardware features like SIMD vectorization; and peak floating point performance, the maximum performance of threaded, vectorised programs with the right instruction mix to keep CPU functional units fully occupied.

The memory bandwidth limits shown in Figure 2.6 are: no prefetching, corresponding to random memory access patterns that cannot be predicted;

Figure 2.7: Powerline Model

hardware prefetching, whereby hardware is able to predict upcoming memory accesses and preload the data; and peak bandwidth, the maximum possible bandwidth attainable with perfect hardware prefetching and optimal memory layout and access patterns.

Roofline models are able to diagnose performance issues using easily obtainable information. Developers identify where their code appears on a Roofline diagram by measuring its operational intensity and floating point performance. This allows them to determine which performance limit their code is bounded by, and hence whether to look for runtime or memory optimisations.

In the example shown by Figure 2.6, improving the memory performance of codes with operational intensities above eight FLOPS per byte will not reduce their runtime. Even the lowest bandwidth limit is enough to keep a CPU fully supplied with data beyond this point. Conversely, memory bandwidth should be the sole optimisation target for codes with operational intensities under one FLOPS per byte. Between these limits the best course of action depends on the level of floating point performance observed.

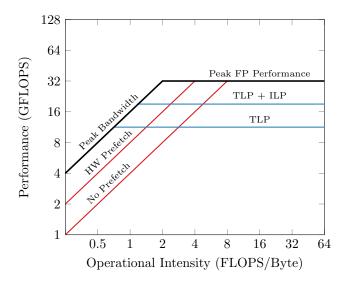

Choi et al. extended the Roofline model to identify the algorithmic condi-

tions necessary for trade-offs between runtime and energy [19]. Figure 2.7 shows the distinctive shape of their 'Powerline' model and how it compares to conventional Roofline analysis. In particular, it shows how power consumption peaks when operational intensity places equal demands on memory and floating point performance. This is because with both subsystems under equal load, neither one can become a bottleneck and force the other to enter an idle state waiting for more work. Idle subsystems draw less power, so power consumption drops off when either subsystem is forced to spend periods of time idle.

The Power Optimised Software Envelope (POSE) model developed in Chapter 5 is another example of energy-aware heuristic performance modelling.

#### 2.6.2 Analytical Modelling

Analytical models distil the structure and behaviour of a program into a set of parameterised mathematical expressions. Performance predictions are then obtained by solving these expressions for the required input parameters. Analytical models are able to predict the behaviour of real systems in a short amount of time, making them particularly suitable for parameter studies.

Early analytical modelling approaches created bespoke models specific to individual machines and applications. These approaches fell out of favour because of the considerable time and expertise required to model complex systems accurately. Furthermore, the resulting models were not portable and had to be completely rebuilt for each new platform. Modern approaches provide generalised model skeletons which can be tailored to individual applications.

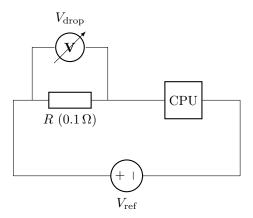

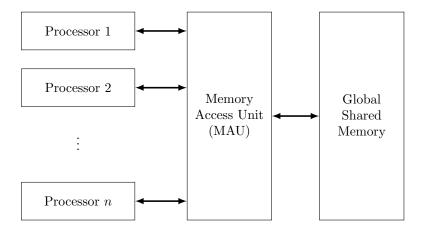

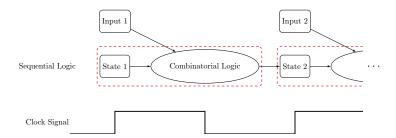

The Parallel Random Access Machine (PRAM) framework was one of the first modelling techniques to produce portable performance models. PRAM defines an idealised representation of SMP hardware consisting of n processors with perfectly synchronised clocks [40], as shown in Figure 2.8. Each processor has its own private memory and can access global shared memory through a common memory access unit. Processors perform one instruction each clock cycle, including potentially reading from or writing to shared memory.

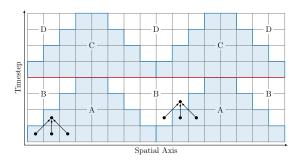

Figure 2.8: PRAM Abstract Machine Model

Conflict resolution policies define what happens when multiple processors access the same memory location simultaneously. There are four policies to choose from, namely: Exclusive Read Exclusive Write (EREW), Concurrent Read Exclusive Write (CREW), Exclusive Read Concurrent Write (ERCW), and Concurrent Read Concurrent Write (CRCW). Both ERCW and CRCW have sub-policies to determine which concurrent write access succeeds.

The PRAM model assumes that all processors are synchronised and communication between processors is free. These were reasonable assumptions when uniform memory access SMP machines were common in HPC. The scalability of these systems is limited by resource contention, however, and they have largely been replaced by NUMA and message-passing DMM approaches.

PRAM emphasised the importance of model portability, however its models are limited to SMP machines. The LogP model was devised to model parallel applications regardless of the computer architecture used [24].

LogP is named after its four system parameters: L, which models network latency; o, the overhead of sending and receiving messages; g, the minimum gap between messages, or equivalently the reciprocal of inter-node bandwidth; and P, the number of processors or nodes. LogGP extends the original model with G, a parameter which captures the higher bandwidth available for longer

messages and bulk transfers on many systems [6].

Some analytical models use hardware performance counters to estimate system power consumption. Power usage and performance events are recorded for a selection of benchmark programs. Regression analysis is then used to derive power costs for each category of performance event. This approach has been used to develop power models for components like CPUs [14, 69], GPUs [62], and Xeon Phi coprocessors [111], as well as entire supercomputer systems [13].

Despite its popularity, this approach has significant limitations. Processors can only monitor a small number of performance counters simultaneously, so many events will be missed. Furthermore, processor events are not standardised between processors, limiting the portability of these models. Lively et al. demonstrated this fact and proposed code-specific power models as a solution [86]. In effect, they suggested intentionally over-fitting models to particular target applications and platforms.

#### 2.6.3 Simulation

Analytical performance modelling involves constructing detailed models of application behaviour. Every application requires its own customised model, even with modern frameworks, and these models must be continually updated and revalidated in response to code changes. Simulators avoid these issues by taking applications themselves as input, either directly or in the form of profiler traces.

Simulators gather performance data by running some representation of the target application through a detailed model of a computer system. This shifts the burden of model construction and verification away from performance engineers and towards simulator designers. Once validated, a simulator can be used to model the performance of many different applications.

Simulators are categorised based on the granularity of their system models. Hardware simulators model the low-level operation of computer systems in as much detail as possible. Cycle-accurate simulators are able to mimic hardware down to the level of individual clock cycles. This amount of detail is useful when

designing new hardware or assessing the impact of exotic architectures.

Discrete event simulators operate at a higher level of abstraction, modelling system behaviour as a sequence of distinct states. State transitions are triggered by application events like network communications or synchronisation barriers. Profilers gather event traces for a target application, which are then passed as input to the simulator. Discrete event simulators are useful for 'what if' investigations which assess the likely outcomes of different scenarios.

Simulations are the most detailed approach to performance modelling, but this detail comes at significant runtime cost. Event-based approaches require traces to be gathered by running the original application in full. Hardware approaches take even longer as they run every application instruction through simulated hardware. Simulators like Sandia's Structural Simulation Toolkit (SST) offer a combined approach, providing hardware simulation for key components and falling back to an event based approach where less detail is required [67].

Hardware simulation is often used to model power consumption. Wattch is a popular framework for analysing and optimising microprocessor architectures for reduced power consumption [17]. McPAT is a similar tool which replaces the linear scaling assumptions in Wattch with non-linear power models, making it suitable for the post-Dennard era [85].

SST supports system power simulation via its modular architecture [64]. Existing component-level power simulators like McPAT are used as back-ends to model the power consumption of individual processors, which SST then aggregates to provide a system-level overview.

# 2.7 Optimisation

Performance optimisation involves modifying applications to improve properties like runtime or energy consumption. *Algorithmic optimisations* lead to more efficient algorithms irrespective of the platform used. Once these optimisations are exhausted, any further improvements come from tuning applications to better

exploit the underlying hardware.

Examples in the latter category include: Multi-threading, where multiple threads are run simultaneously on different CPU cores; cache blocking, where loop iterations are re-ordered to make more efficient use of the cache hierarchy; and vectorisation, where SIMD instructions are used to improve floating point throughput. Hand-optimising code using these techniques can produce large performance improvements, however the resulting applications are platform-specific and can be hard to maintain [32].

Performance portability is the idea that optimised code should remain as general as possible in order to perform well across different platforms. When following this approach, developers expose opportunities for parallelism within their code. It is then left for optimising compilers and libraries to map these opportunities on to specific hardware features [100].

One way to achieve performance portability is to use frameworks which abstract away details of the underlying platform. OP2 allows users to develop unstructured grid applications independently of the underlying hardware. Back ends then translate these high level implementations into low-level code which targets a specific platform [43, 44]. Other examples of this approach include Kokkos [32] and Charm++ [71].

Compiler directives offer a more direct approach in which developers annotate their source code with additional information and instructions. These directives expose opportunities for parallelism and allow compilers to use more aggressive optimisation strategies. OpenMP [26] provides directives to exploit TLP via the fork-join model, and ILP using SIMD instructions. OpenACC [119] uses directives to specify functions for offload to GPUs and other accelerators.

#### 2.7.1 Energy-Aware Optimisation

Energy use can be reduced either by shortening runtime or decreasing power consumption. The runtime optimisations described above are therefore also capable of reducing energy consumption. Power optimisation is less developed, however some progress has been made.

Dynamic Voltage and Frequency Scaling (DVFS) and sleep states are two hardware features often exploited by power optimisations. Briefly, DVFS allows processors to run at different clock speeds and supply voltages, while sleep states allow processors to power down during periods of inactivity.

The work-span model described in Section 2.6 suggests several strategies for power optimisation. Nodes off the critical path can use DVFS to lower their clock speeds and reduce power draw [31]. Alternatively, they can temporarily increase their clock speeds to finish their work quickly before entering into sleep states [33]. Finally, DVFS-aware scheduling algorithms can be used to pack applications onto fewer nodes [84].

# 2.8 Summary