#### WestminsterResearch

http://www.westminster.ac.uk/westminsterresearch

## Asynchrobatic logic for low-power VLSI design

## **David John Willingham**

School of Electronics and Computer Science

This is an electronic version of a PhD thesis awarded by the University of Westminster. © The Author, 2010.

This is an exact reproduction of the paper copy held by the University of Westminster library.

The WestminsterResearch online digital archive at the University of Westminster aims to make the research output of the University available to a wider audience. Copyright and Moral Rights remain with the authors and/or copyright owners.

Users are permitted to download and/or print one copy for non-commercial private study or research. Further distribution and any use of material from within this archive for profit-making enterprises or for commercial gain is strictly forbidden.

Whilst further distribution of specific materials from within this archive is forbidden, you may freely distribute the URL of WestminsterResearch: (http://westminsterresearch.wmin.ac.uk/).

In case of abuse or copyright appearing without permission e-mail repository@westminster.ac.uk

# ASYNCHROBATIC LOGIC FOR LOW-POWER VLSI DESIGN

# **David John WILLINGHAM**

A thesis submitted in partial fulfillment of requirements of the

University of Westminster for the degree of

Doctor of Philosophy

March 2010

# i. Table of Contents

| I.    | rab    | e of Contents                                             | I      |

|-------|--------|-----------------------------------------------------------|--------|

| ii.   | List   | of Abbreviations                                          | iv     |

| iii.  | List   | of Symbols                                                | vii    |

| iv.   | List   | of Figures                                                | viii   |

| ٧.    | List   | of Tables                                                 | Х      |

| vi.   | List   | of Equations                                              | хi     |

| vii.  | List   | of Publications                                           | xii    |

| viii. | Ackı   | nowledgements                                             | xiii   |

| ix.   | Abs    | tract                                                     | xiv    |

| Chap  | oter 1 | Introduction                                              | 1      |

| 1.1   |        | Aims and Motivation                                       | 1      |

| 1.2   |        | Original contributions                                    | 3      |

| 1.3   |        | Outline of thesis                                         | 4      |

| Chap  | oter 2 | An introduction to Adiabatic Logic                        | 7      |

| 2.1   |        | Introduction                                              | 7      |

| 2.2   |        | Physics and Computation                                   | 7      |

| 2.3   |        | A review of adiabatic logic families                      | 9      |

| 2.3.1 |        | Efficient Charge Recovery Logic (ECRL)                    | 16     |

| 2.3.2 | )<br>- | Improved Efficient Charge Recovery Logic (IECRL)          | 17     |

| 2.3.3 | 3      | Positive Feedback Adiabatic Logic (PFAL)                  | 18     |

| 2.3.4 |        | Efficient Adiabatic Charge Recovery Logic (EACRL)         | 19     |

| 2.4   |        | Systematic search for other potential adiabatic logic fam | nilies |

|       |        |                                                           | 20     |

| 2.5   |        | Adiabatic Power Supplies                                  | 21     |

| 2.6   |        | Reversible Computation                                    | 26     |

| 2.7   |        | Summary                                                   | 28     |

| Chap  | oter 3 | A review of asynchronous logic                            | 29     |

| 3.1   |        | Introduction                                              | 29     |

| 3.2   |        | Asynchronous signalling                                   | 31     |

| 3.3       | The Muller C-Element                                    | 33  |

|-----------|---------------------------------------------------------|-----|

| 3.4       | Asynchronous Multiplex and Demultiplex                  | 35  |

| 3.5       | Complexity issues in asynchronous systems               | 37  |

| 3.6       | Summary                                                 | 38  |

| Chapter 4 | Design methods for dual-rail data-paths                 | 39  |

| 4.1       | Introduction                                            | 39  |

| 4.2       | Adiabatic design methodologies                          | 39  |

| 4.3       | The design of logic functions                           | 42  |

| 4.4       | Summary                                                 | 49  |

| Chapter 5 | An introduction to Asynchrobatic Logic                  | 51  |

| 5.1       | Introduction                                            | 51  |

| 5.2       | The concept of Asynchrobatic Logic                      | 51  |

| 5.3       | The components of an Asynchrobatic Logic implementation | 53  |

| 5.4       | Design of Control Structures                            | 54  |

| 5.5       | Design of Stepwise Charging Logic                       | 55  |

| 5.6       | Design of data-path logic                               | 60  |

| 5.7       | Implementation of an Asynchrobatic pipeline             | 61  |

| 5.7.1     | Comparison of Asynchrobatic and asynchronous buffer cha | ins |

|           |                                                         | 61  |

| 5.8       | Potential for fully reversible operations               | 70  |

| 5.9       | Summary                                                 | 76  |

| Chapter 6 | Modelling and Simulating Asynchrobatic Logic            | 77  |

| 6.1       | Introduction                                            | 77  |

| 6.2       | Verilog modelling                                       | 78  |

| 6.3       | VHDL Modelling                                          | 82  |

| 6.4       | Circuit level simulation                                | 83  |

| 6.5       | Summary                                                 | 85  |

| Chapter 7 | Implementing Asynchrobatic Logic                        | 87  |

| 7.1       | Introduction                                            | 87  |

| 7.2       | The Twofish algorithm                                   | 87  |

| 7.3       | Binary Decision Diagram Optimisers                      | 89  |

| 7.4       | Layout Design                                           | 90  |

| 7.5        | Summary                                   | 103   |

|------------|-------------------------------------------|-------|

| Chapter 8  | A more complex Asynchrobatic system       | 104   |

| 8.1        | Introduction                              | 104   |

| 8.2        | Construction of the basic data-path cells | 105   |

| 8.3        | The Comparator                            | 108   |

| 8.4        | The Subtractor / Reverse Subtractor       | 110   |

| 8.5        | Control logic                             | 113   |

| 8.6        | Performance                               | 115   |

| 8.7        | Testing                                   | 117   |

| 8.8        | Simulation Results                        | 118   |

| 8.8.1      | Verilog                                   | 118   |

| 8.8.2      | SPICE                                     | 121   |

| 8.9        | Summary                                   | 126   |

| Chapter 9  | Conclusions and Future work               | 127   |

| 9.1        | Conclusions                               | 127   |

| 9.2        | Novelty claims and contributions          | 129   |

| 9.3        | Applications and future work.             | 131   |

| Chapter 10 | References and Bibliography               | 134   |

| 10.1       | References                                | 134   |

| 10.2       | Bibliography                              | 153   |

| Appendices | S                                         | ı     |

| A.         | Verilog source-code                       | 1     |

| A.1.       | Single-rail GCD                           | I     |

| A.2.       | Dual-rail GCD                             | XVII  |

| B.         | C source-code                             |       |

|            | XXXIX                                     |       |

| C.         | SPICE source-code                         | LI    |

| C.1.       | SPICE for q-boxes                         | LI    |

| C.2.       | LVS summaries                             | LXVII |

| C.3.       | SPICE for GCD                             | LXIX  |

#### ii. List of Abbreviations

123-DD 123 Decision Diagram **ADL** Adiabatic Dynamic Logic **ANSI** American National Standards Institute **ASWC** Asynchronous Stepwise Charging **BDD Binary Decision Diagram** CAL **CMOS Adiabatic Logic CCN** Controlled-Controlled-NOT CL Carry Look-ahead CLA Carry Look-ahead Adder **CMOS** Complementary Metal Oxide Semiconductor **CPAL** Complementary Pass-transistor Adiabatic Logic **CRL** Charge Recovery Logic **DAG Directed Acyclic Graph** DC **Direct Current DCVSL** Differential Cascode Voltage Switch Logic **DeMUX** De-Multiplexer **DPA Differential Power Analysis** DRC Design Rule Check **DTMOS** Dynamic Threshold MOS DUT **Device Under Test EACRL** Efficient Adiabatic Charge Recovery Logic **ECC** Elliptic Curve Cryptography **ECRL** Efficient Charge Recovery Logic **EEL Energy Efficient Logic ERC Electrical Rule Check FBDD** Free Binary Decision Diagram Field Effect Transistor FET **FSM** Finite State Machine **GCD Greatest Common Denominator GF** Galois Field

| HDL    | Hardware Description Language                       |

|--------|-----------------------------------------------------|

| HRKA   | Higher-Radix Knowles Adder                          |

| IECRL  | Improved Efficient Adiabatic Charge Recovery Logic  |

| IP     | Intellectual Property                               |

| LSB    | Least Significant Bit                               |

| LVS    | Layout Versus Schematic                             |

| MOS    | Metal Oxide Semiconductor                           |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor   |

| MSB    | Most Significant Bit                                |

| MUX    | Multiplexer                                         |

| MVL    | Multi-Valued Logic                                  |

| NMOS   | N-Type Metal Oxide Semiconductor                    |

| OBDD   | Ordered Binary Decision Diagram                     |

| OEIS   | Online Encyclopædia of Integer Sequences            |

| PAL    | Pass-transistor Adiabatic Logic                     |

| PFAL   | Positive Feedback Adiabatic Logic                   |

| PMOS   | P-Type Metal Oxide Semiconductor                    |

| PVT    | Process, Voltage and Temperature                    |

| RAM    | Random Access Memory                                |

| RERL   | Reversible Energy Recovery Logic                    |

| RF     | Radio Frequency                                     |

| RFBDD  | Reduced Free Binary Decision Diagram                |

| ROBDD  | Reduced Ordered Binary Decision Diagram             |

| ROR    | Rotate Right                                        |

| SCRL   | Split-level Charge Recovery Logic                   |

| SIMD   | Single Instruction Multiple Data                    |

| SOI    | Silicon on Insulator                                |

| SPICE  | Simulation Program with Integrated Circuit Emphasis |

| SRAM   | Static RAM                                          |

| SWC    | Stepwise Charging                                   |

| VHDL   | VHSIC Hardware Description Language                 |

| VHSIC  | Very High Speed Integrated Circuit                  |

| VLIW             | Very Long Instruction Word   |

|------------------|------------------------------|

| VLSI             | Very Large Scale Integration |

| $\mathbf{V}_{T}$ | Threshold Voltage            |

| XOR              | Exclusive-OR                 |

| XNOR             | Exclusive-NOR                |

|                  |                              |

## iii. List of Symbols

ΔE Error between sinusoidal and ideal waveforms

$\theta$  Normalised angle

φ Clock phase

$\tau$  Time

V<sub>pc</sub> Power-clock voltage

$V_{dd}$  Static power supply voltage  $!_T$  (Binary) tree factorial operator

!<sub>T(n)</sub> n-ary tree factorial operator

P<sub>D</sub> Dynamic power

f<sub>e</sub> Effective frequency

$C_L$  Capacitive load  $\overline{P}$  Average power  $t_1, t_2$  Time 1, Time 2

$i_{Vdd}$  Current flowing through power supply  $V_{dd}$

i(t) Instantaneous currentv(t) Instantaneous voltagex 8-bit input to q-box

y 8-bit output from q-box

$q_n[m]$  8-bit substitution function of q-box n

a<sub>0</sub>, a<sub>1</sub>, a<sub>2</sub>, a<sub>3</sub>, a<sub>4</sub> Internal, intermediate 4-bit functions of q-boxes b<sub>0</sub>, b<sub>1</sub>, b<sub>2</sub>, b<sub>3</sub>, b<sub>4</sub> Internal, intermediate 4-bit functions of q-boxes

$t_n[m]$  Look-up table, giving the  $m^{th}$  value of the  $n^{th}$  table

A, B Inputs to adder or subtractor

R Reverse subtraction selector

Z Output from adder or subtractor

F<sub>(n)</sub> The n<sup>th</sup> Fibonacci number

P An integer

w Width of the data-path  $\mathbb{Z}$  The set of integers

N The set of natural numbers

# iv. List of Figures

| 2.1  | An ECRL Buffer [Kram95] & [Moon95]                                     | .16 |

|------|------------------------------------------------------------------------|-----|

| 2.2  | An IECRL Buffer [Denk94]                                               | .17 |

| 2.3  | A PFAL Buffer [Vetu96]                                                 | .18 |

| 2.4  | An EACRL Buffer [Varg01a]                                              | .19 |

| 2.5  | Phase relationships of adiabatic power-clocks                          | .23 |

| 2.6  | Difference between Ideal and Sinusoidal waveforms                      | .24 |

| 2.7  | Stepwise Charging Waveforms                                            | .26 |

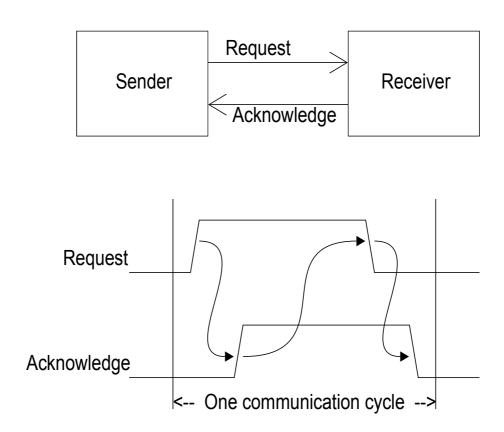

| 3.1  | Four-phase handshaking protocol [Pave94]                               | .32 |

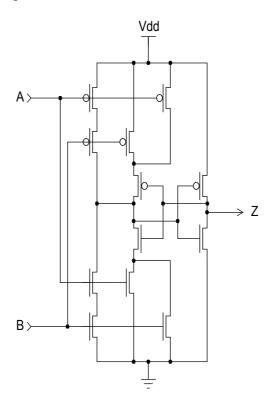

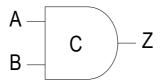

| 3.2  | Schematic of static C-Element [Spar01]                                 | .34 |

| 3.3  | C-Element symbol [Spar01]                                              | .35 |

| 3.4  | Asynchronous MUX for 4-phase bundled data [Spar01]                     | .36 |

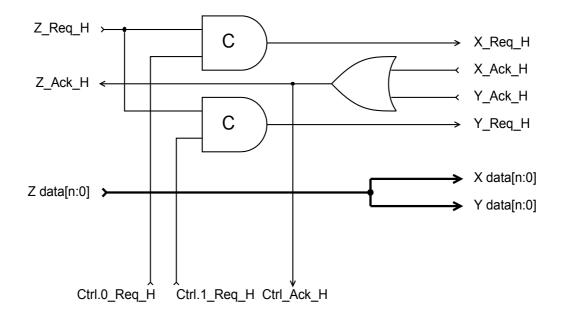

| 3.5  | Asynchronous DeMUX for 4-phase bundled data [Spar01]                   | .37 |

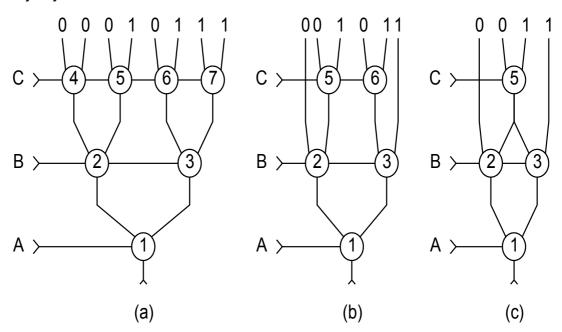

| 4.1  | An example of OBDD minimisation                                        | .44 |

| 4.2  | Effect of variable ordering in OBDDs                                   | .46 |

| 4.3  | Mapping a BDD node to a pair of NMOS devices                           | .47 |

| 4.4  | Possible implementations of a two-input AND function's pull-up logic . | .49 |

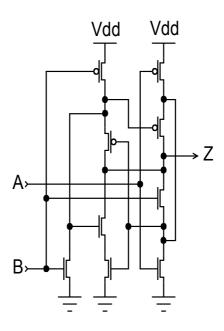

| 5.1  | Current-starved inverters as variable delay [West94]                   | .56 |

| 5.2  | Static CMOS 2-input XOR gate [MIT04]                                   | .57 |

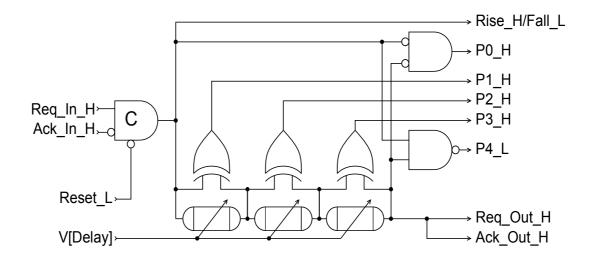

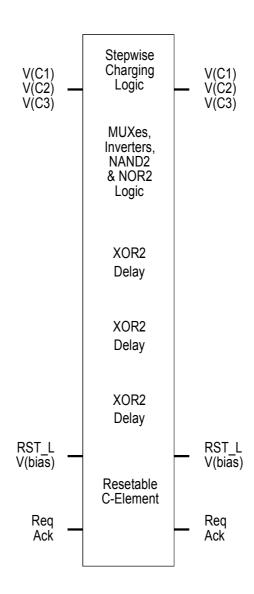

| 5.3  | An asynchronous stepwise charging controller [Will04]                  | .58 |

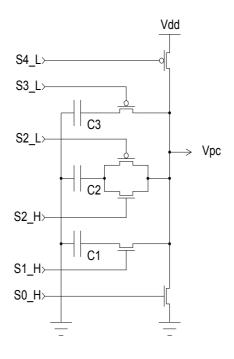

| 5.4  | A Stepwise Charging circuit [Sven94a]                                  | .59 |

| 5.5  | Floorplan of an Asynchronous Stepwise Charging Controller              | .62 |

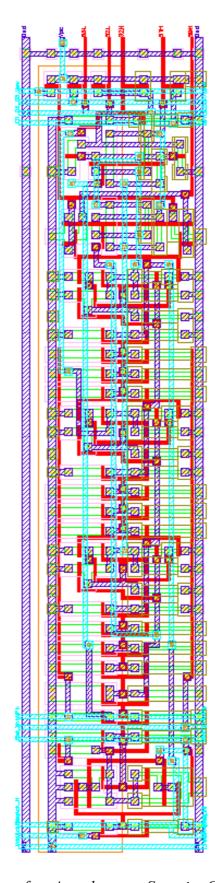

| 5.6  | Layout of an Asynchronous Stepwise Charging Controller                 | .63 |

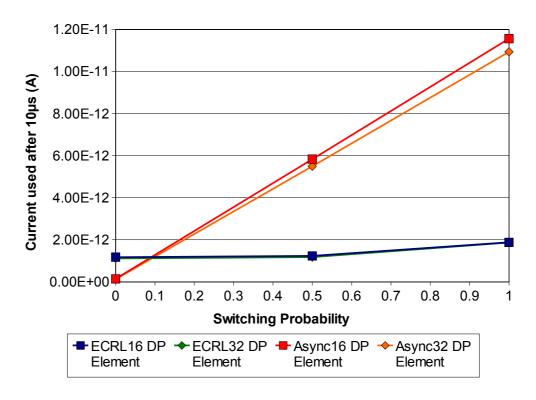

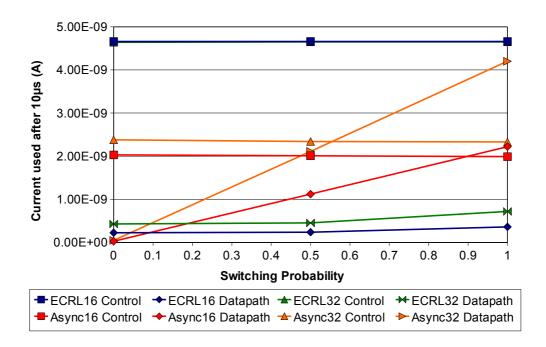

| 5.7  | Cumulative current consumption for data-path elements                  | .65 |

| 5.8  | Cumulative current for the control and data-path                       | .66 |

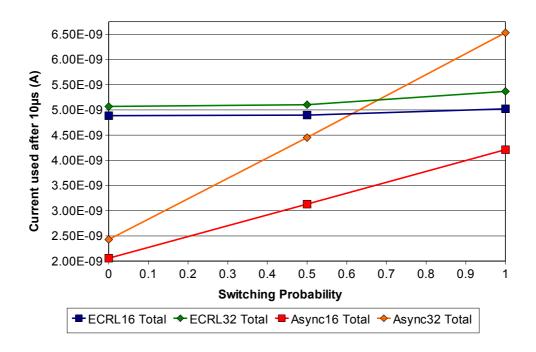

| 5.9  | Total cumulative current                                               | .67 |

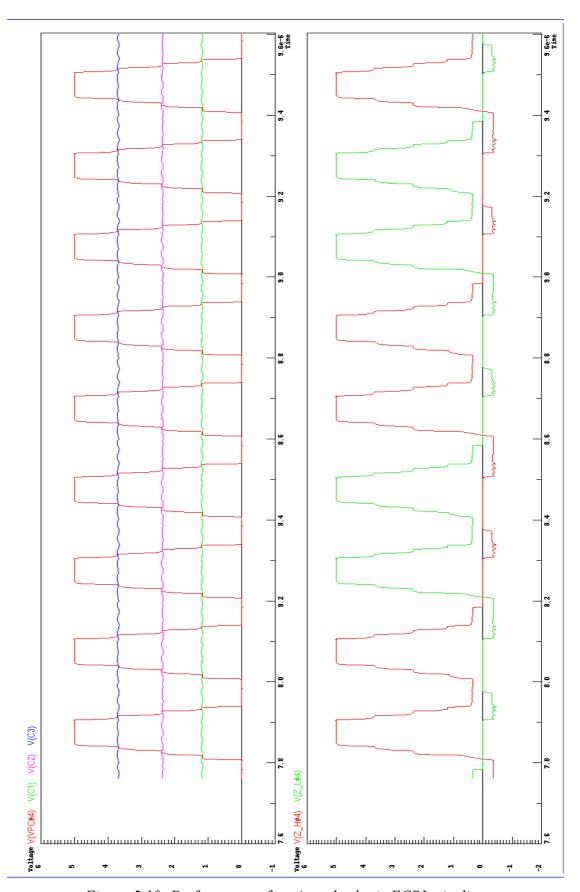

| 5.10 | Performance of an Asynchrobatic ECRL pipeline                          | .69 |

| 5.11 | Controlled-Controlled-NOT (CCN) or Toffoli Gate Symbol [Feyn00]        | .71 |

| 5.12 | Schematic of a PFAL Toffoli Gate [Will08b]                             | .72 |

| 5.13 | Evaluation tree for AND-XOR function [Will08b]                         | .73 |

| - 11 | Performance of reversible versus non-reversible PFAL gates             | 75  |

| 6.1  | Conceptualisation of a two-input AND gate for single-rail Asynchrobatic |     |

|------|-------------------------------------------------------------------------|-----|

|      | data-path simulation                                                    | 79  |

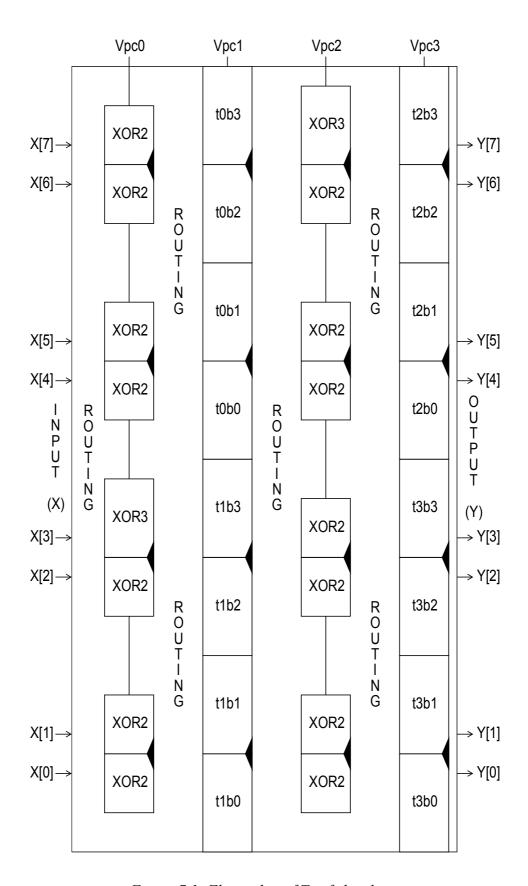

| 7.1  | Floor-plan of Twofish q-boxes                                           | 95  |

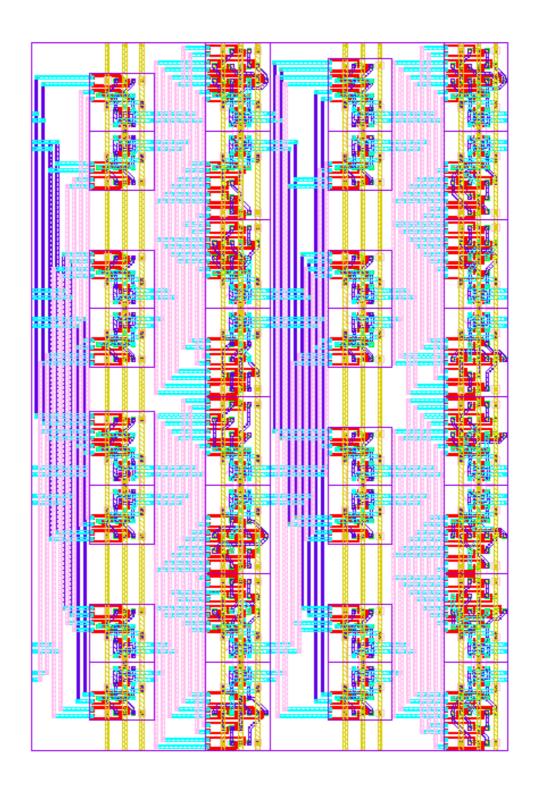

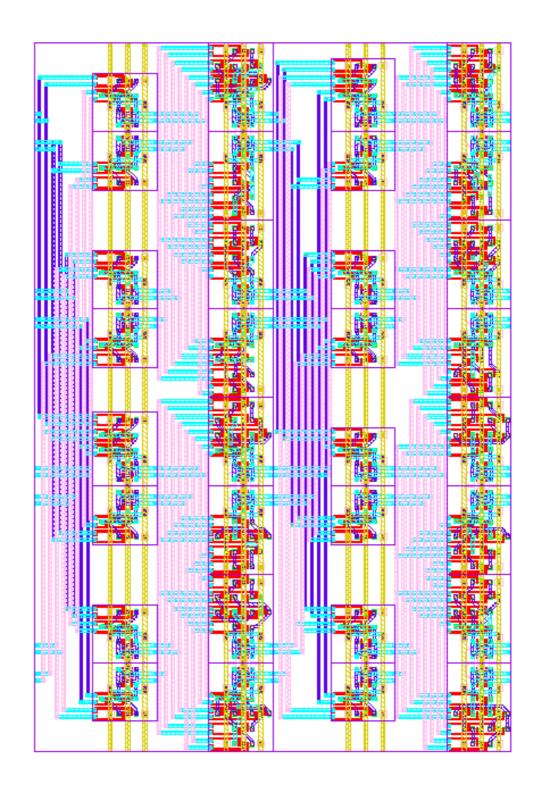

| 7.2  | Layout of Twofish q0 substitution box                                   | 96  |

| 7.3  | Layout of Twofish q1 substitution box                                   | 97  |

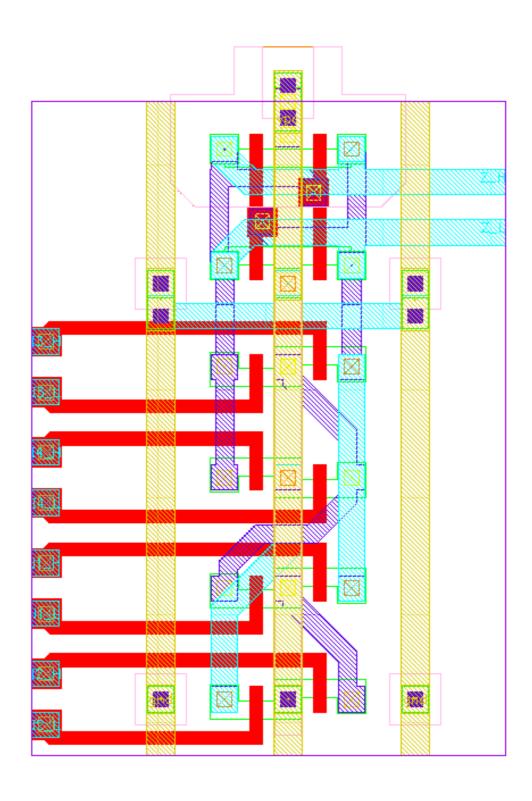

| 7.4  | Layout of q1t0b2 cell                                                   | 98  |

| 7.5  | q1t0b2 circuit diagram                                                  | 99  |

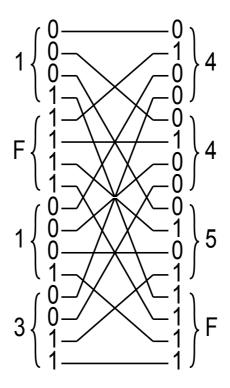

| 7.6  | A visual validation of variable reordering                              | 100 |

| 7.7  | A non-reordered, sub-optimal ROBDD implementation of q1t0b2             | 101 |

| 7.8  | A reordered, optimal ROBDD implementation of q1t0b2                     | 102 |

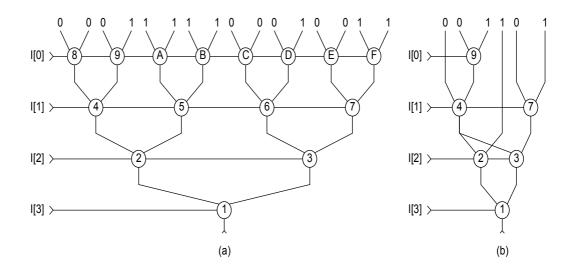

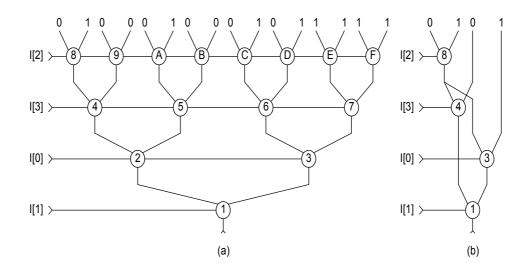

| 8.1  | NMOS tree of 4-input AND [Will08a]                                      | 106 |

| 8.2  | NMOS tree of 7-input (AND-OR)4 [Will08a]                                | 106 |

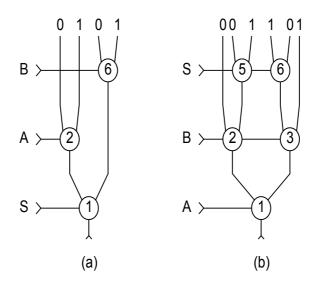

| 8.3  | NMOS tree of 2-input MUX                                                | 107 |

| 8.4  | NMOS tree of 2-input XOR [Will08a]                                      | 107 |

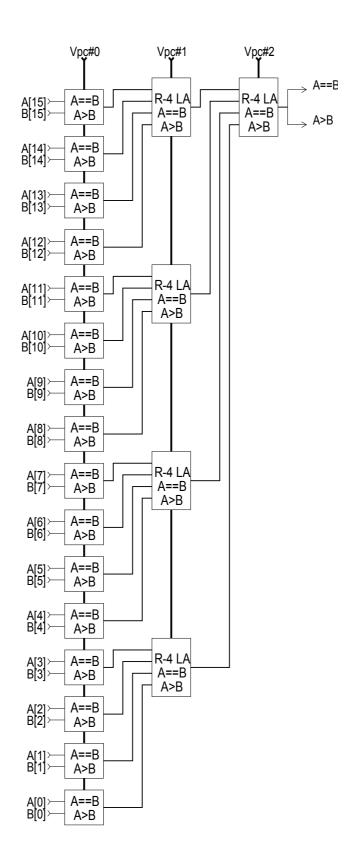

| 8.5  | Comparator for GCD                                                      | 109 |

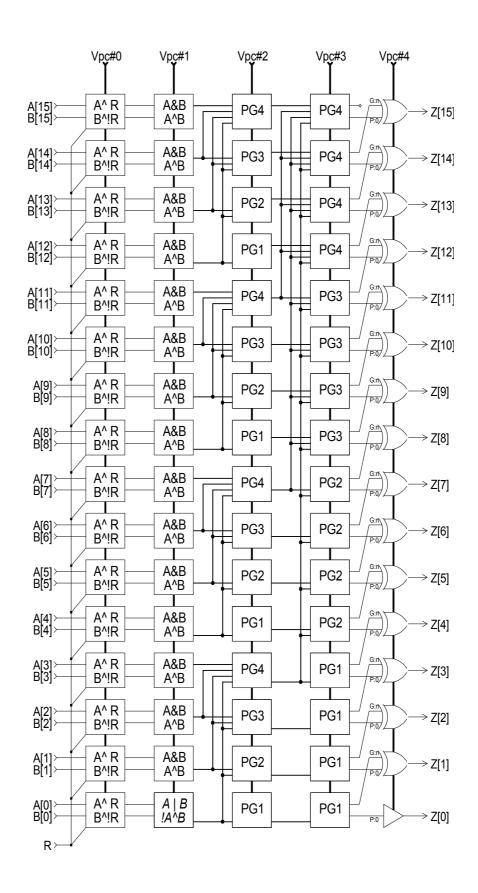

| 8.6  | Subtractor / Reverse subtractor for GCD [Will08a]                       | 112 |

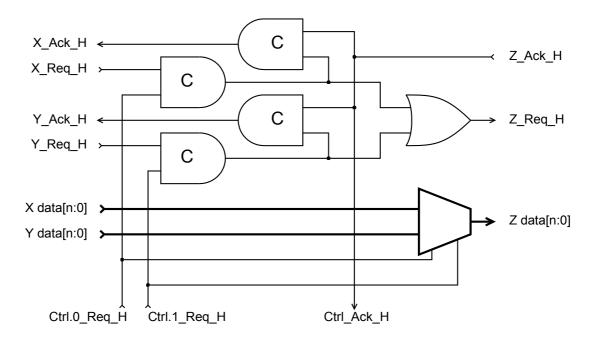

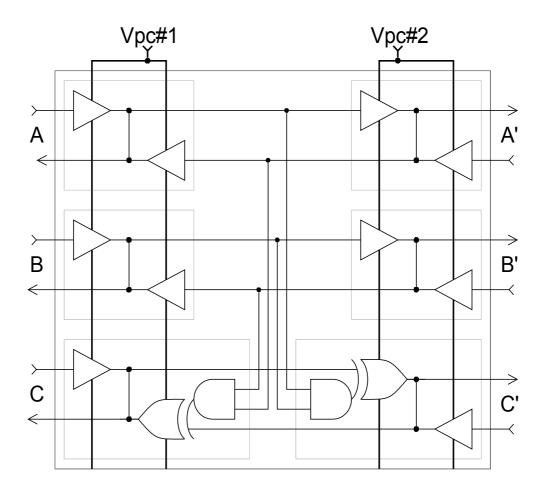

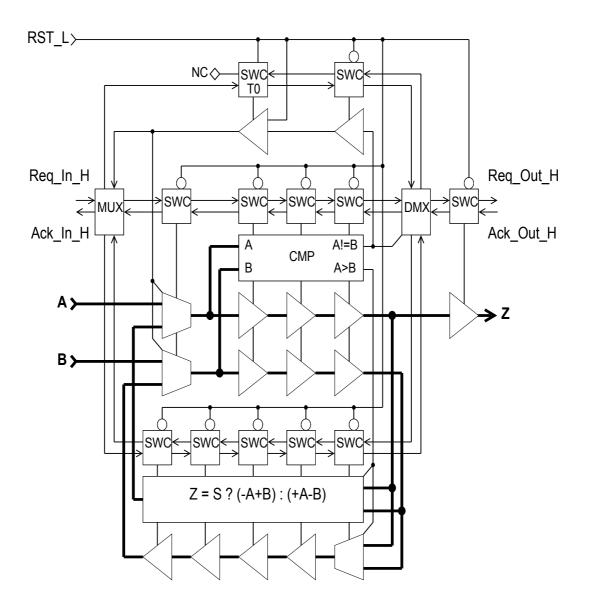

| 8.7  | Asynchrobatic GCD [Will08c]                                             | 115 |

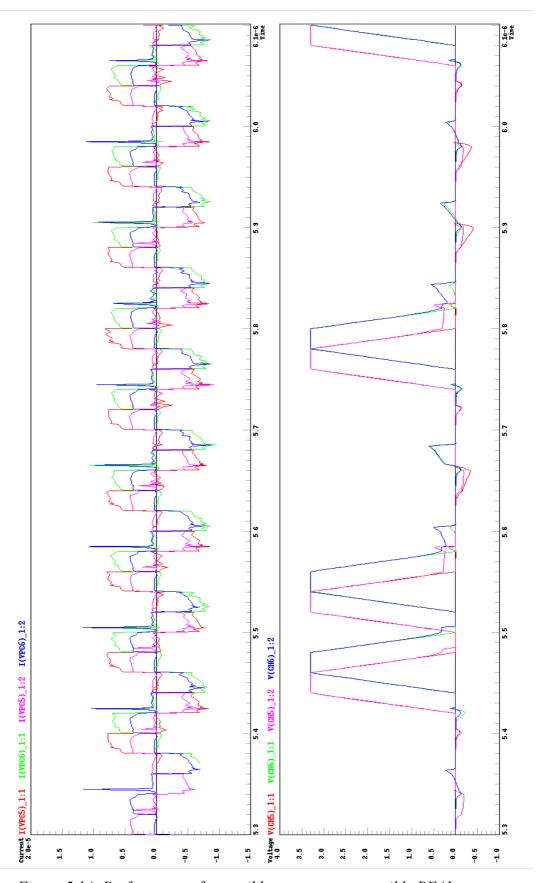

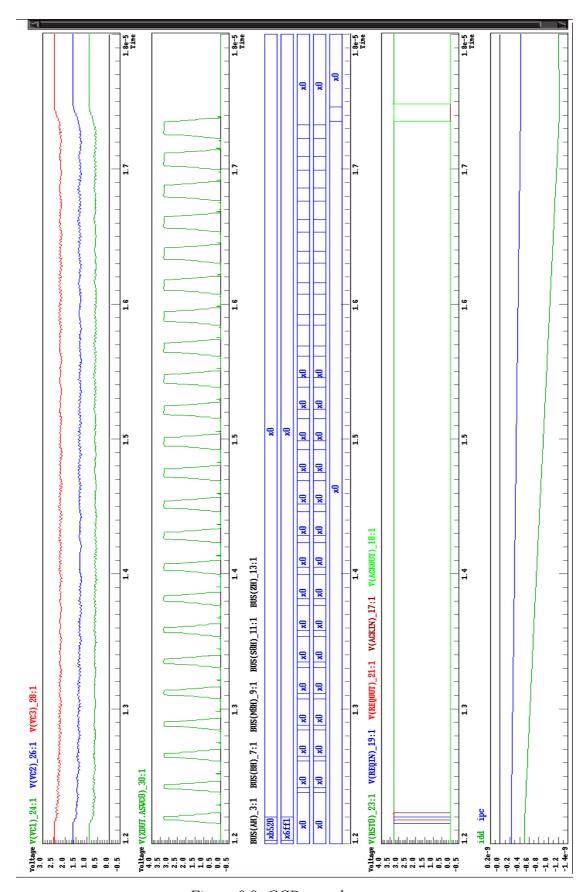

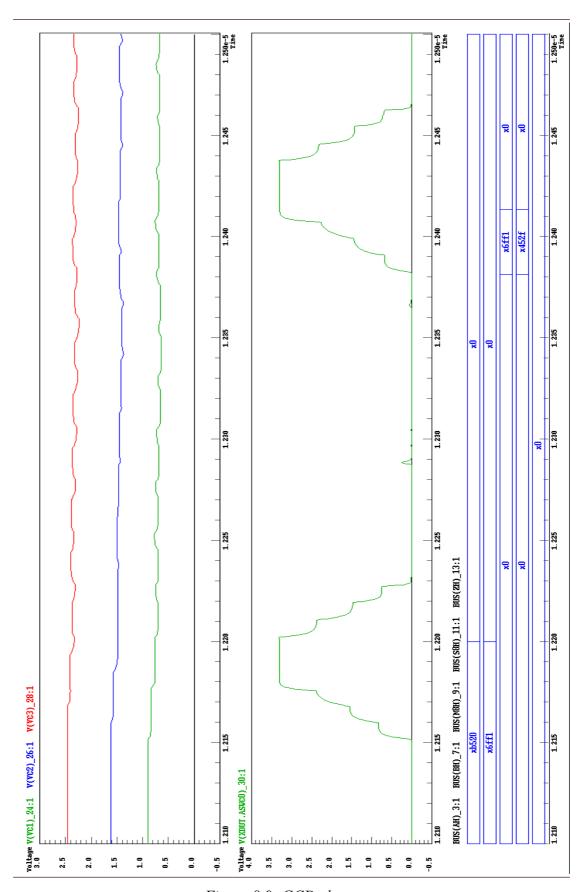

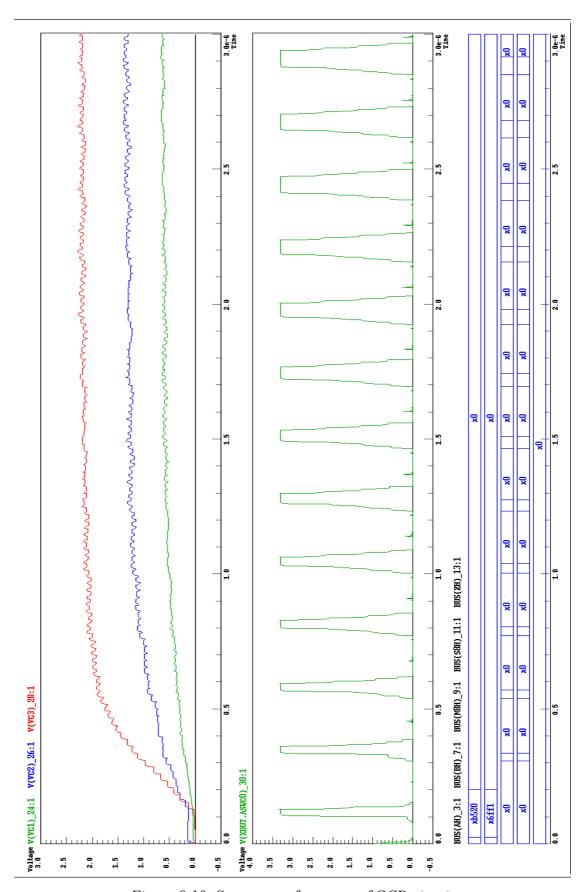

| 8.8  | GCD complete trace                                                      | 123 |

| 8.9  | GCD close-up                                                            | 124 |

| 8.10 | Start-up performance of GCD circuit                                     | 125 |

|      |                                                                         |     |

# v. List of Tables

| 2.1 | A list of adiabatic logic families                           | 11  |

|-----|--------------------------------------------------------------|-----|

| 2.2 | A systematic nomenclature for basic adiabatic logic families | 21  |

| 3.1 | State table of a C-Element [Mull59]                          | 33  |

| 4.1 | Growth of search space for OBDD and FBDD optimisers          | 41  |

| 4.2 | Effect of variable ordering in OBDDs                         | 45  |

| 5.1 | Truth-table for a Toffoli Gate [Feyn00]                      | 71  |

| 6.1 | Dual-rail logic states in Asynchrobatic Logic                | 77  |

| 7.1 | Look-up Tables for Twofish substitution q-boxes [Schn98]     | 88  |

| 7.2 | Paths and Path Lengths for a sub-optimal ROBDD minimisation  | 101 |

| 7.3 | Paths and Path Lengths for an optimal ROBDD minimisation     | 102 |

| 8.1 | Performance results for GCD circuit [Will08c]                | 116 |

| 8.2 | Simple test vectors for the GCD circuit                      | 117 |

## vi. List of Equations

- 2.1 Power consumption in static CMOS

- 2.2 Difference between a sinusoid and the Ideal waveform

- 3.1 Power consumption in static CMOS

- 4.1 Binary Tree Factorial (as a product)

- 4.2 Binary Tree Factorial (defined recursively)

- 4.3 n-ary Tree Factorial (as a product)

- 4.4 n-ary Tree Factorial (defined recursively)

- 6.1 Average power

- 6.2 Simplified average power

- 7.1 Functional description of Twofish q-boxes first part

- 7.2 Functional description of Twofish q-boxes second part

- 7.3 Functional description of Twofish q-boxes third part

- 7.4 Functional description of Twofish q-boxes fourth part

- 7.5 Functional description of Twofish q-boxes fifth part

- 7.6 Functional description of Twofish q-boxes final part

- 8.1 Subtract or reverse subtract

- 8.2 Inequality defining maximum unsigned integer for a bit-width

- 8.3 Maximum Fibonacci number for a given bit-width

#### vii. List of Publications

- David J. Willingham and İzzet Kale, "Asynchronous, quasi-adiabatic (Asynchrobatic) logic for low power very wide data width applications", Proceedings of the 2004 International Symposium on Circuits and Systems (ISCAS 2004), volume 2, pages II:257-260, Vancouver, Canada, 23<sup>rd</sup>-26<sup>th</sup> May 2004.

- David J. Willingham and İzzet Kale, "An Asynchrobatic, Radix-four, Carry Look-ahead Adder", Proceedings of Ph.D. Research in Microelectronics and Electronics (PRIME 2008), pages 105-108, İstanbul, Turkey, 22<sup>nd</sup>-25<sup>th</sup> June 2008.

- David J. Willingham and İzzet Kale, "Using Positive Feedback Adiabatic Logic to implement Reversible Toffoli Gates", Proceedings of NORCHIP 2008, pages 5-8, Tallinn, Estonia, 17<sup>th</sup>-18<sup>th</sup> November 2008.

- David J. Willingham and İzzet Kale, "A system for calculating the Greatest Common Denominator implemented using Asynchrobatic Logic", Proceedings of NORCHIP 2008, pages 194-197, Tallinn, Estonia, 17<sup>th</sup>-18<sup>th</sup> November 2008.

## viii. Acknowledgements

"I find television very educational. The minute somebody turns it on, I go to the library and read a good book." Groucho Marx.

I must thank my parents, Doug and Ann, and my partner Jacqueline for their support. Special thanks go to my father who claims to have ended up looking like Ben Turpin after his assistance proof-reading this thesis.

I would also like to thank my supervision team and other colleagues at the University of Westminster; Prof. İzzet Kale, Prof. Dik Morling, Dr. Ediz Çetin and Alan Wood. Special thanks must go to my Director of Studies, Prof. İzzet Kale, for his support, assistance, and understanding throughout the duration of my research.

Thanks also go to following libraries and their staff:

University of Westminster (New Cavendish Street, London),

British Library (St. Pancras, London),

Institution of Engineering and Technology Library (Savoy Place, London),

Barking Library (London Borough of Barking and Dagenham),

Cherry Hinton Library (Cambridgeshire),

Eastville Library (City and County of Bristol),

Ilford Central Library (London Borough of Redbridge).

And to the online research services of:

The British Computer Society (BCS),

The Institution of Engineering and Technology (IET) and

The Institution of Electrical and Electronic Engineers (IEEE).

Finally, I must acknowledge that this research was partially supported by a Quintin Hogg Research Scholarship from the University of Westminster.

#### ix. Abstract

In this work, Asynchrobatic Logic is presented. It is a novel low-power design style that combines the energy saving benefits of asynchronous logic and adiabatic logic to produce systems whose power dissipation is reduced in several different ways. The term "Asynchrobatic" is a new word that can be used to describe these types of systems, and is derived from the concatenation and shortening of **Asynchro**nous, Adiabatic Logic. This thesis introduces the concept and theory behind Asynchrobatic Logic. provides an introductory background to both underlying parent technologies (asynchronous logic and adiabatic logic). The background material continues with an explanation of a number of possible methods for designing complex data-path cells used in the adiabatic data-path. Asynchrobatic Logic is then introduced as a comparison between asynchronous and Asynchrobatic buffer chains, showing that for wide systems, it operates more efficiently. more-complex sub-systems are presented, firstly a layout implementation of the substitution boxes from the Twofish encryption algorithm, and secondly a front-end only (without parasitic capacitances, resistances) simulation that demonstrates a functional system capable of calculating the Greatest Common Denominator (GCD) of a pair of 16-bit unsigned integers, which under typical conditions on a 0.35µm process, executed a test vector requiring twenty-four iterations in 2.067µs with a power consumption of 3.257nW. These examples show that the concept of Asynchrobatic Logic has the potential to be used in real-world applications, and is not just theory without application. At the time of its first publication in 2004, Asynchrobatic Logic was both unique and ground-breaking, as this was the first time that consideration had been given to operating large-scale adiabatic logic in an asynchronous fashion, and the first time that Asynchronous Stepwise Charging (ASWC) had been used to drive an adiabatic data-path.

## **Chapter 1** Introduction

#### 1.1 Aims and Motivation

Until quite recently, the power consumption of VLSI computation devices had not been the major limiting factor in improvements and advances in microelectronic technology. Computers were static, powered by mains electricity, and even the most power hungry microprocessor of a desktop computer could be cooled using a fan-assisted heat-sink. Current processors can consume 140W, drawing over 100A of current in the process [AMD09]! However, the rise of portable consumer electronics, ubiquitous computing devices [Weis93], and implanted or wearable bio-medical electronics means that power efficient computation has become more important in widely deployed technologies, rather than being confined to niche and specialist areas. Also, as the dimensions of CMOS technologies have shrunk, so that for nanometre technologies the thickness of the gate dielectric is a countable number of atoms [Inte07], traditional power reduction techniques like voltage scaling have ceased to be as effective, and new issues like source-drain leakage and even gate leakage have become significant sources of power dissipation.

Depending upon the application, there are numerous methods that can be used to reduce the power consumption of VLSI circuits, these can range from low-level measures based upon fundamental physics, such as using a lower power supply voltage or using high threshold voltage transistors; to high-level measures such as clock-gating or power-down modes. The two that motivated this investigation were asynchronous logic [Mull59] & [Spar01] and adiabatic logic [Koll92]. These two technologies have been combined to create an Asynchronous, Adiabatic Logic methodology, called *Asynchrobatic* Logic [Will04], which is the subject of this thesis. The name is derived as a concatenation and shortening of **Asynchro**nous, Adiabatic Logic.

Although known from very early in the history of computation, asynchronous logic [Mull59] has until recently remained more a subject of academic research than commercial interest. However, in applications like RF-powered smart cards, asynchronous implementations of microprocessors normally used in embedded applications have found a commercially useful role [Spar01]. One of the properties of asynchronous systems that make them useful in these applications are that circuits include a built-in insensitivity to variations in power supply voltage, with a lower voltage resulting in slower operation rather than the functional failures that would be seen if traditional synchronous systems were used. Another major advantage is the fact that when an asynchronous system is idle there will be no ticking clock signals, whereas in synchronous systems, these clock signals are propagated throughout the entire system and convert energy to heat, often without performing any useful computations.

Adiabatic logic is a newer area of low-power research [Koll92]. It is focused on issues associated with the thermodynamics of computation. By taking this branch of physics, that usually looks at mechanical engines, and applying it to computing engines, research fields such as reversible computation as well as adiabatic logic have been created. By moving to a computing paradigm that is reversible, energy can be recovered from a computing engine, and reused to perform further calculations. The analogy of regenerative braking is a good example which illustrates this idea in the context of a familiar mechanical system. The low-power benefit of adiabatic logic is that energy can be recycled by being stored and reused, thus reducing the amount of energy drawn directly from the power supply. There are other low-power consequences of using certain realisations of adiabatic logic, but these are implementation specific rather than being directly due to the reversible nature of the logic.

The two research areas described above both had a different set of low-power benefits which they could bring to circuit design, and *Asynchrobatic* Logic was born out of the novel idea to attempt to find a way to unify the low-power benefits from these fields. When written succinctly as "unifying the low-power benefits of asynchronous logic and adiabatic logic", this idea may sound like a simple and innocuously easy task. However, when it is realised that one of the commonly used synonyms for adiabatic logic is "clock-powered logic", and that from its Greek etymology, "asynchronous" has evolved to mean without synchronised clocks, it can be seen that the task of merging anything from these two research areas is not going to be without substantial challenges. How a clock-powered logic can be operated without clocks appears initially to be an impossible and contradictory requirements specification.

## 1.2 Original contributions

The original contributions that this project has added to the state-of-theart can be summed-up as follows:

- The novel concept of Asynchrobatic Logic. That is, a processing circuit which operates both asynchronously and adiabatically. Prior to this, adiabatic processing had occurred synchronously, any self-timed adiabatic circuits only had applications as drivers, just capable of repeating a signal, but not performing any logical operation upon it, and asynchronous logic had been used with logic incapable of charge recovery or adiabatic operation.

- The application of capacitor-based, Asynchronous Stepwise Charging (ASWC) as a method for driving adiabatic data-path logic.

- The design and implementation of a simple system (of a pipeline of buffers) to act as proof of concept.

- The design and implementation of a complex system (a 16-bit GCD calculator), capable of fulfilling the concepts of Asynchrobatic Logic.

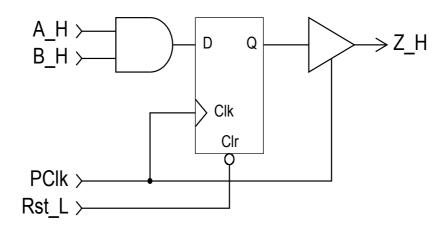

- A method for modelling Asynchrobatic Logic in Verilog, an industry standard Hardware Description Language (HDL), which in the behavioural paradigm can be easily extended to VHDL, another industry standard HDL.

- Systematic identification of other adiabatic logic families based around cross-coupled pairs of PMOS transistors. However, these did not show any extra low-power benefits over previously disclosed technologies.

- The realisation that the Positive Feedback Adiabatic Logic (PFAL) family can be used to implement complex reversible processing logic. Design and implementation of a Toffoli Gate [Feyn00] to demonstrate this, noting that the design was operated under ideal adiabatic conditions, but with the caveat that nothing would preclude Asynchrobatic operation of such a circuit.

- A proposal to extend the family of Knowles Adders from radix-two to higher-radices and the use of this as a solution to overcome the large fan-out or wiring density required for wide, radix-four, Asynchrobatic or adiabatic adders.

- A generalisation of results for the rate of growth of the search space for "Free n-ary Decision Diagrams". These sequences only appear to have been documented for binary and ternary decision diagrams, but could be usefully extended to Free Quaternary, Quinary or higher-order Decision Diagrams, with possible applications being the design of functions for Multi-Valued Logics (MVL).

#### 1.3 Outline of thesis

Asynchrobatic Logic is the result of a successful experiment that attempted to create a low-power CMOS logic structure that operated both asynchronously and adiabatically. It is therefore predicated upon prior-art from the fields of adiabatic logic and asynchronous logic, as well as more familiar ideas from the electronic engineering and computer science disciplines associated with VLSI design. The first two introductory chapters

provide explanations of both of these logic styles. This thesis has approached this idea from the perspective of implementing an asynchronous controller to drive adiabatic logic, and the majority of the focus was on the adiabatic logic, with the asynchronous controller using previously known and unremarkable The third introductory chapter examines the design implementations. methods for the dual-rail adiabatic logic families. The initial proof of concept that introduced Asynchrobatic Logic and demonstrated that it was viable, was an implementation of a chain of buffers [Will04]. These were compared against a similar structure implemented in standard asynchronous logic, and for a suitably wide data-path, with a reasonable switching probability, were shown to have a better power efficiency. Subsequent work demonstrated that more complex arithmetic functions could be implemented [Will08a] and ultimately that a complex system could be implemented. discovery, subsidiary to the main thrust of the work, was the realisation that this work had potential for use in fully reversible logic systems [Will08b].

This introduction will be followed by three introductory chapters, one that provides an in-depth introduction and background to adiabatic logic, and another that provides an overview of asynchronous logic, and a third that detail the design methods for dual-rail logic used in adiabatic data-paths. The chapters subsequent to this document the design details and other principles applied during the creation of *Asynchrobatic* Logic. The HDL modelling of *Asynchrobatic* Logic using Verilog, and issues surrounding physical implementation are considered. Finally, an *Asynchrobatic* implementation of Euclid's Greatest Common Denominator (GCD) algorithm is presented [Will08c]. Conclusions are drawn, including comparisons of *Asynchrobatic* Logic against other authors' works; future work and possible commercial applications are proposed and discussed; and bibliographic references are cited.

The appendices contain annotated source code. Appendix A contains Verilog source code for both the single-rail and dual-rail versions of the GCD algorithm. Appendix B contains the C source code for automated Ordered Binary Decision Diagram (OBDD) minimisation Appendix C contains the SPICE sources for the Twofish q-boxes and the GCD algorithm, along with Layout versus Schematic checking summaries for the Twofish q-boxes.

## **Chapter 2** An introduction to Adiabatic Logic

#### 2.1 Introduction

In this chapter, the basic concepts of Adiabatic logic will be introduced. "Adiabatic" is a term of Greek origin that has spent most of its history associated with classical thermodynamics. It refers to a system in which a transition occurs without energy (usually in the form of heat) being either lost to or gained from the system. In the context of electronic systems, rather than heat, electronic charge is preserved. Thus, an ideal adiabatic circuit would operate without the loss or gain of electronic charge. The first usage of the term "Adiabatic" in this context appears to be traceable back to a paper presented in 1992 at the Second Workshop on Physics and Computation [Koll92]. Although an earlier suggestion of the possibility of energy recovery was made by Bennett where in relation to the energy used to perform computation, he stated "This energy could in principle be saved and reused" [Benn82].

## 2.2 Physics and Computation

The introduction to this section details the etymology of the term "adiabatic logic". In this section, the underlying physics are considered. Because of the Second Law of Thermodynamics, it is not possible to completely convert energy into useful work. However, the term "Adiabatic Logic" is used to describe logic families that could theoretically operate without losses, and the term "Quasi-Adiabatic Logic" is used to describe logic that operates with a lower power than static CMOS logic, but which still has some theoretical non-adiabatic losses. In both cases, the nomenclature is used to indicate that these systems are capable of operating with substantially less power dissipation than traditional static CMOS circuits, which as is shown in equation (2.1) operates with a Power, P, that is proportional to both the Capacitive load, C<sub>L</sub> and the square of the Voltage, V.

$$P \propto C_L V^2 \tag{2.1}$$

The fact that these techniques take the operational power of adiabatic and quasi-adiabatic circuits below this threshold was emphasised by some initial works in this research area, which had titles proclaiming that they operated " $sub-CV^2$ " [Sven94b] & [Sven96].

The underlying principles of adiabatic logic can be traced back more than two centuries to the industrial revolution when James Clerk Maxwell proposed his paradoxical Dæmon [Maxw71]. This led to the conclusion during the latter part of the twentieth century that Maxwell's Dæmon cannot violate the Second Law of Thermodynamics as the erasure of information causes entropy to increase [Land61], [Benn73] & [Leff03]. This also led to the concept of a system that could be operated arbitrarily slowly such that its dissipation could asymptotically approach zero as its speed was reduced [Youn93].

There are several important principles that are shared by all of these low-power adiabatic systems. These include only turning switches on when there is no potential difference across them, only turning switches off when no current is flowing through them, and using a power supply that is capable of recovering or recycling energy in the form of electric charge.

To achieve this, in general, the power supplies of adiabatic logic circuits have used constant current charging (or an approximation thereto), in contrast to more traditional non-adiabatic systems that have generally used constant voltage charging from a fixed-voltage power supply.

The power supplies of adiabatic logic circuits have also used circuit elements capable of storing energy. This is often done using inductors [Moon96], which store the energy by converting it to magnetic flux, or, as in case of *Asynchrobatic* Logic, by using capacitors, which can directly store electric charge.

There are a number of synonyms that have been used by other authors to refer to adiabatic logic type systems, these include: "Charge recovery logic" [Youn93], "Charge recycling logic" [Kong96a], "Clock-powered logic" [Atha97], "Energy recovery logic" [Hinm93] and "Energy recycling logic" [De96c]. Because of the reversibility requirements for a system to be fully adiabatic, most of these synonyms actually refer to, and can be used interchangeably, to describe quasi-adiabatic systems. These terms are succinct and self-explanatory, so the only term that warrants further explanation is "Clock-Powered Logic". This has been used because many adiabatic circuits use a combined power supply and clock, or a "power-clock". This a variable, usually multi-phase, power-supply which controls the operation of the logic by supplying energy to it, and subsequently recovering energy from it.

The possibility of using adiabatic logic in larger systems has been shown to be viable with both clock-powered and adiabatic processors having been successfully implemented [Atha97], [Shin03] & [Shin04].

## 2.3 A review of adiabatic logic families

Over the last two decades many different adiabatic or quasi-adiabatic logic families have been proposed. A substantial list of these, in approximate chronological order, is shown below in Table 2.1.

| List of Adiabatic Logic families in approximate chronological order    |

|------------------------------------------------------------------------|

| Hot clock nMOS [Seit85]                                                |

| Retractile cascades [Hall92]                                           |

| Recovered Energy Logic (REL) [Hinm93]                                  |

| Charge Recovery Logic (CRL) [Youn93]                                   |

| Split-level Charge Recovery Logic (SCRL) [Youn94a] & [Youn94b]         |

| Pulsed Power Supply CMOS (PPS CMOS) [Gaba94a] & [Gaba94b]              |

| 2N-2N2D [Kram94]                                                       |

| Adiabatic Dynamic Logic (ADL) [Dick94] & [Dick95]                      |

| Adiabatic Pseudo-Domino Logic (APDL) [Wang95]                          |

| Clocked CMOS Adiabatic Logic (CAL) [Maks95], [Maks97a] & [Maks97b]     |

| Efficient Charge Recovery Logic (ECRL) [Moon95] & [Moon96] 1           |

| 2N-2P [Kram95] <sup>1</sup>                                            |

| 2N-2N2P [Denk94] & [Kram95] <sup>2</sup>                               |

| Quasi-Adiabatic Ternary CMOS Logic (QAT) [Mate96] & [Mate97]           |

| Positive Feedback Adiabatic Logic (PFAL) [Vetu96] <sup>3</sup>         |

| Transmission gate-interfaced APDL (T-APDL) [Lau96]                     |

| Fully Adiabatic MOS Logic (ADMOS) [De96a]                              |

| Complementary Adiabatic MOS Logic (CAMOS) [De96a] & [De96c]            |

| Dynamic Adiabatic MOS (DAMOS) [De96b] & [De96c]                        |

| Charge Recycling Differential Logic (CRDL) [Kong96a] & [Kong96b]       |

| Half Rail Differential Logic (HRDL) [Choe97]                           |

| Energy Efficient Logic (EEL) [Yeh97]                                   |

| Pass-transistor Adiabatic Logic (PAL) [Oklo97]                         |

| Quasi-Static Energy Recovery Logic (QSERL) [Ye97]                      |

| Improved Adiabatic Pseudo-Domino Logic (IAPDL) [Lau97]                 |

| True Single-Phase CRDL (TCRDL) [Kong97]                                |

| Forward body-bias MOS (FBMOS) [Kioi97]                                 |

| Reversible Energy Recovery Logic (RERL) [Lim98]                        |

| Feedback Reversible Energy Recovery Logic (fRERL) [Kwon98]             |

| Adiabatic Differential Cascode Pass-transistor Logic (ADCPL) [Lo98]    |

| PAL-2N [Liu98a] <sup>3</sup>                                           |

| Improved Efficient Charge Recovery Logic (IECRL) [Liu98b] <sup>2</sup> |

| Bootstrapped NMOS Charge Recovery Logic (BNCRL) [Yoo98]                |

| True Single-Phase Energy-Recovering Logic (TSEL) [Kim98]                            |

|-------------------------------------------------------------------------------------|

| Modified Half Rail Differential Logic (MHRDL) [Won98]                               |

| CMOS Pass-gate No-race Charge-recycling Logic (CPNCL) [Yoo99a]                      |

| No-race Charge-recycling Differential Logic (NCDL) [Yoo99b]                         |

| Source Coupled Adiabatic Logic (SCAL) [Kim99]                                       |

| Retractile Clock-Powered Logic (RCPL) [Tzar99]                                      |

| Adiabatic Dynamic CMOS Logic (ADCL) [Taka00]                                        |

| NMOS Energy Recovery Logic (NERL) [Kim00]                                           |

| Bootstrapped Charge-Recovery Logic (BCRL) [Li00]                                    |

| Adiabatic Differential Cascode Voltage Switch Logic (ADCVSL) [Suva00]               |

| Dynamic Threshold MOS (DTMOS) ADCVSL [Lega01] & [Lega03]                            |

| High Efficient Energy Recovery Logic (HEERL) [Hong01]                               |

| Dual-Swing Charge-Recovery Logic (DSCRL) [Li01]                                     |

| Efficient Adiabatic Charge Recovery Logic (EACRL) [Varg01a]                         |

| Improved Pass-Gate Adiabatic Logic (IPGAL) [Varg01b]                                |

| Complementary Pass-transistor Energy Recovery Logic (CPERL) [Chan02]                |

| Complementary Pass-transistor Adiabatic Logic (CPAL) [Hu03] & [Hu04]                |

| Improved Adiabatic Pseudo-Domino Logic 2 (IAPDL-2) [Widj03]                         |

| Unnamed modification to HEERL [Song04]                                              |

| Improved Positive Feedback Adiabatic Logic (IPFAL) [Fisc04] <sup>4</sup>            |

| Energy Recovery Capacitance Coupling Logic (ERCCL) [Qian04]                         |

| 2N-2N2P2D [He06]                                                                    |

| Quasi-Static Single-phase Energy Recovery Logic (QSSERL) [Li07]                     |

| Improved Positive Feedback Adiabatic Logic (IPFAL) [Vija07a] [Vija07b] <sup>4</sup> |

| <sup>1</sup> ECRL and 2N-2P are identical                                           |

| <sup>2</sup> IECRL is similar to the already proposed 2N-2N2P                       |

<sup>&</sup>lt;sup>2</sup> IECRL is similar to the already proposed 2N-2N2P

Table 2.1: A list of adiabatic logic families

The list in Table 2.1 does not claim to be exhaustive, but it does aim to provide a general idea of the progress made in this field, and to show how the design of adiabatic logic families has progressed over time. Critically, it is noteworthy that all of these adiabatic logic families used synchronous clocking. However, because they are early attempts or are some of the more

<sup>&</sup>lt;sup>3</sup> PAL-2N is similar to the already proposed PFAL

<sup>&</sup>lt;sup>4</sup> The IPFAL name is duplicated with different functionality

frequently cited adiabatic families that have been proposed, a number of these adiabatic logic families warrant to be given brief descriptions. For those actually given serious consideration for use in Asynchrobatic Logic, expanded descriptions are provided later in this chapter:

- Split-level Charge Recovery Logic (SCRL) [Youn94a] & [Youn94b],

- SCRL is a truly adiabatic logic family as it has a feedback path for logical recovery. Its topology resembles static CMOS gates followed by a transmission-gate, but it has both of its power rails replaced by power-clock signals, hence its description as "split-level". It has complex clocking, often with eight phases. It is an extension of a simpler adiabatic logic family called Charge Recovery Logic (CRL) [Youn93].

- 2N-2N2D [Kram94],

- 2N-2N2D is a diode-based complementary logic family. The diodes mean that it will have non-adiabatic losses and is therefore only quasi-adiabatic. The systematic naming of this logic family indicates that it uses pairs of NMOS devices (designated by "2N") and a pair diodes (designated by "2D").

- Adiabatic Dynamic Logic (ADL) [Dick94],

- ADL stages alternate between being constructed of NMOS and PMOS devices. As with 2N-2N2D recovery occurs through diodes, making it only quasi-adiabatic.

- Efficient Charge Recovery Logic (ECRL) [Moon95] & [Moon96],

- It appears to have been independently discovered by Kramer, who gave it the systematic name "2N-2P" [Kram95],

- ECRL and 2N-2P are identical, and are based upon the standard CMOS family called Differential Cascode Voltage Switch Logic (DCVSL) [Hell84]. This structure uses pairs of pull-down NMOS devices to evaluate functions (designated by the "2N") and a pair of cross-coupled PMOS devices (designated by the "2P") to hold state. It is frequently cited and has clearly been the inspiration for many

other similar adiabatic logic families. Complete recovery of the power-clock is not possible through the PMOS devices, so it is still only a quasi-adiabatic logic style. ECRL/2N-2P is described in more detail later in this section.

- 2N-2N2P [Denk94] & [Kram95],

- It was originally simply described by Denker as an "Adiabatic Logic Gate", systematically named by Kramer, and later called Improved Efficient Charge Recovery Logic (IECRL) [Liu98b]. IECRL differs very slightly from the previous description by specifically using the a PMOS device to form a pair of recovery diodes. The previous works do not document how the bulk terminals are connected.

- IECRL is very similar to ECRL, but with the addition of a pair of cross-coupled NMOS devices to give a better connection to ground when inputs have had their charge recovered. IECRL/2N-2N2P is also described in more detail later in this section.

- Clocked CMOS Adiabatic Logic (CAL) [Maks95],

- CAL is similar to 2N-2N2P, but has clocked NMOS devices between the NMOS decision tree and the outputs. These are driven by a square-wave clock to access to the evaluation logic. This allows it to use fewer clock-phases, but requires extra control signals.

- Positive Feedback Adiabatic Logic (PFAL) [Vetu96],

- Also later called PAL-2N [Liu98a],

- PFAL is very similar to IECRL, but has its evaluation tree connected between power-clock and outputs. It can achieve fully adiabatic operation when a recovery path is provided. PFAL is described in more detail later in this section.

- Energy Efficient Logic (EEL) [Yeh97],

- EEL is an extension of ECRL. It employs a pair of externally controlled, pulsed NMOS devices between power-clock and outputs to allow full charge recovery. However, it is not truly adiabatic because it is lacks logically reversibility.

- Pass-transistor Adiabatic Logic (PAL) [Oklo97],

- The topology of PAL resembles a PFAL gate without the pair of cross-coupled NMOS devices. The absence of pull-down NMOS devices means that this family lacks a good ground connection.

- Reversible Energy Recovery Logic (RERL) [Lim98],

- RERL holds its logic state using a pair of cross-coupled NMOS devices, but evaluation and recovery occurs through transmission gates, like SCRL it also requires complex, eight-phase clocking.

- Efficient Adiabatic Charge Recovery Logic (EACRL) [Varg01a],

- EACRL has a pair of cross-coupled PMOS devices, and duplicate sets of evaluation logic, one set is connected between ground and the outputs, whilst the other is connected (with an opposite assertion level) between the power-clock and the outputs. In the same way as PFAL, it too can be made fully adiabatic when a recovery path is provided. EACRL is the final family described in more detail later in this section.

- Complementary Pass-transistor Adiabatic Logic (CPAL) [Hu03],

- CPAL uses a PFAL inverter or buffer, with the main part of the evaluation tree constructed using pass-transistors to connect to the gates of the NMOS pull-ups.

Both Starosel'skii [Star02] and Amirante [Amir04] have provided good descriptions and classification in their works, and these works also provide an overview into some other adiabatic circuit styles. The earliest quasi-adiabatic styles such as ADL and 2N-2N2D used diodes, which means that they could not be loss-less. For this reason, no diode-based families were considered for *Asynchrobatic* implementation. Some of the later families were too complex, having a large implementation overhead. This overhead was either related to the number of devices required, which would increase the area requirements, or due to excessively complex constraints on power-clock phasing or additional control signalling. Consequently, these families were not considered for use with *Asynchrobatic* Logic.

The simple adiabatic logic families that are described below all share a common heritage that can be traced back to the static CMOS DCVSL family [Hell84]. For a designer, this is immensely useful, as the DCVSL family has been in use for over twenty years. This means that various design methodologies for more complex logic functions have been thoroughly investigated and published. These include a table-based Quine-McClusky method [Chu86], Ordered Binary Decision Diagram (OBDD) [Brya86] & [Karo95] methods, as well as various extensions thereto, including Free Binary Decision Diagram (FBDD) [Bern93] and 123-Decision Diagram (123-DD) [Arma98] methods. The OBDD of these design methodologies will be detailed in Chapter 4, and PFAL gate implementations resulting from use their are shown in Chapter 7.

ECRL, IECRL and PFAL are three of the simplest adiabatic or quasiadiabatic logic families that are suitable for use in Asynchrobatic Logic. EACRL, although more complex, is also a relatively simple derivative of these, and could be a potential candidate for use in Asynchrobatic Logic. Therefore, only these four logic families will be more fully detailed. It should be clear to someone au fait with this logic style that other families including EEL could be used, but they will not be described herein. This omission does not mean that these logic styles will not work nor that they cannot be made to work in an Asynchrobatic fashion, but merely that the requirements to achieve this are beyond the scope of this thesis. Each potential logic family would need to be evaluated to determine whether the compromise of silicon area for lower power or other benefits is worthwhile. Clearly, this should be done with reference to a base-line, which should be ECRL as this is the simplest of the four-phase DCVSL-based adiabatic logic families. Where the suggested adiabatic family has extra signals, other factors need to be considered. For example, with the EEL family, the question the designer must ask is; would any power-savings in the data-path be counteracted by the extra power and silicon area required to provide a second local signal to each pipeline stage?

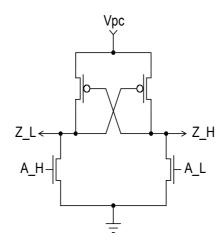

#### 2.3.1 Efficient Charge Recovery Logic (ECRL)

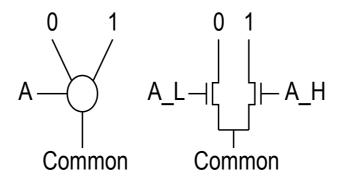

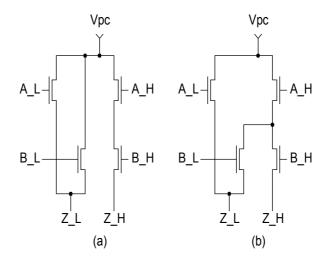

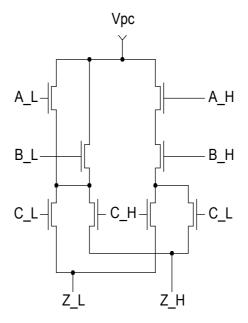

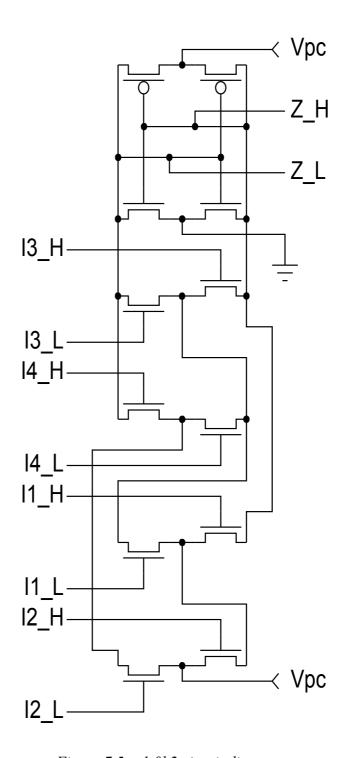

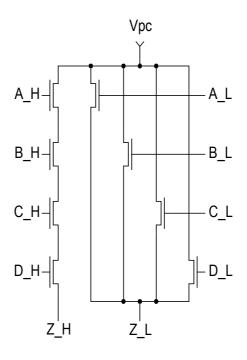

ECRL [Moon95] (also known as 2N-2P [Kram95]) is based around a pair of cross-coupled PMOS transistors. Their source terminals are connected to the power-clock, and the gate of each one is connected to the drain of the other. These nodes form the complementary output signals. The function is evaluated by a series of pull-down NMOS devices. In the original description, the connectivity of the PMOS transistors' bulk terminals was not specified. However, experimentation has shown that better power performance can be obtained by connecting the bulk to the power-clock, as the power-clock can be recovered to a lower voltage. This improvement is not without cost, as it introduces layout constraints that require the hot n-wells of each Asynchrobatic stage to be kept separated. One disadvantage of ECRL is that once the charge from the previous stage has been recovered from the gate of the NMOS devices, there is no pull-down path to ground. This has implications for noise susceptibility. Figure 2.1 shows an inverter/buffer (in buffer configuration) implemented using the ECRL style. The power-clock drives the terminal labelled "Vpc". The dual-rail input pair "A" and dual-rail output pair are shown with their high and low assertion levels indicated by the "\_H" and "\_L" suffixes.

Figure 2.1: An ECRL Buffer [Kram95] & [Moon95]

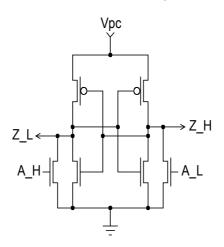

#### 2.3.2 Improved Efficient Charge Recovery Logic (IECRL)

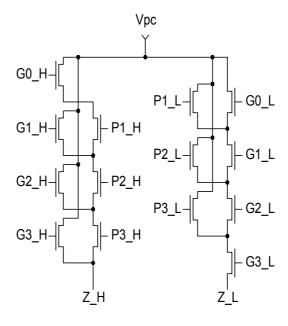

IECRL [Liu98b] (originally known as 2N-2N2P by Kramer *et al.* in [Kram95], but first described by Denker in [Denk94] improves ECRL with the addition of a pair of cross-coupled NMOS devices. This produces a logic family that is based around a pair of cross-coupled inverters, a structure that is identical to the storage elements in a Static RAM (SRAM). The cross-coupled NMOS devices are an improvement over ECRL because they provide a pull-down path to ground that remains even after the charge is recovered from the gates of the evaluation FETs. However, because of the two extra NMOS devices, it will require a larger area in which to be implemented. Figure 2.2. shows an inverter/buffer (also in buffer configuration) implemented using the IECRL style. This figure uses the same naming and assertion level conventions as the ECRL circuit shown on the previous page.

Figure 2.2: An IECRL Buffer [Denk94]

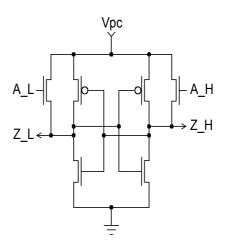

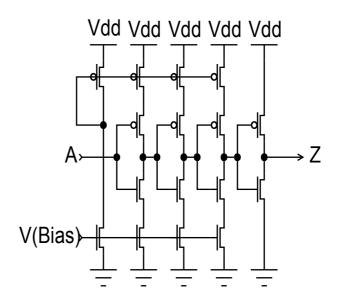

#### 2.3.3 Positive Feedback Adiabatic Logic (PFAL)

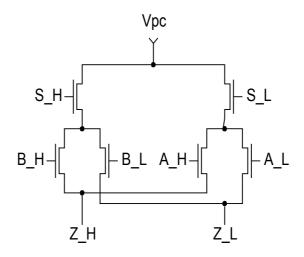

PFAL [Vetu96], like IECRL, is also based around a pair of crosscoupled inverters. However, whilst in IECRL the NMOS devices used to evaluate the function are connected between the outputs and ground, in PFAL, these evaluation NMOS devices are connected between the outputs and the power-clock. The similarities between PFAL and IECRL gates are such that IECRL gates can be easily converted into PFAL gates. This is done by re-labelling the outputs so that their assertion levels are swapped, and connecting the NMOS evaluation devices between the power-clock and the outputs rather than between ground and the outputs. This can be made as easy to achieve in layout as it is in abstract representations of the circuit. When the power-clock is in its recovery phase, the NMOS devices between the outputs and the power-clock can allow complete recovery of those This means that the low-power performance of PFAL can be outputs. enhanced by making it fully reversible [Vetu96] & [Will08b]. Figure 2.3 shows an inverter/buffer (again in buffer configuration, with identical signal naming conventions) implemented in the PFAL style.

Figure 2.3: A PFAL Buffer [Vetu96]

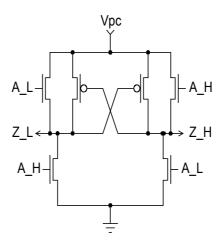

#### 2.3.4 Efficient Adiabatic Charge Recovery Logic (EACRL)

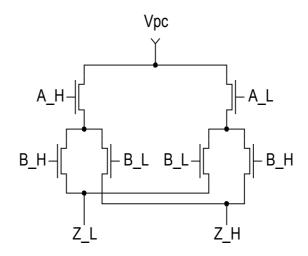

EACRL [Varg01a] is a mixture of ideas from ECRL and PFAL, as it too is based around a pair of cross-coupled PMOS devices. It uses both pull-up NMOS devices (like PFAL) and pull-down NMOS devices (like ECRL) to evaluate its function. Its main disadvantage is that for multi-input functions, there is a substantial overhead associated with the complete duplication of the evaluation logic. EACRL shares another minor disadvantage with ECRL, because like ECRL, it could also suffer from noise as EACRL does not have a pull-down path to ground after the charge on its inputs had been recovered. EACRL suggested incorporating a recovery path. An inverter/buffer (yet again in buffer configuration and with the same naming convention) implemented using the EACRL style is shown in Figure 2.4.

Figure 2.4: An EACRL Buffer [Varg01a]

A possible extension to EACRL is to add a cross-coupled pair of NMOS devices. This is the same design modification that improved ECRL to produce IECRL. This is likely to make the power consumption worse due to increased capacitive load, but in certain situations would increase the circuit's performance with respect to signal integrity in an electrically noisy environment.

Several of the papers proposing quasi-adiabatic logic families have alluded to design improvements that would render the designs either fully adiabatic or fully able to the outputs. These have included PFAL, EACRL and EEL. However, because the circuits used as demonstrators for these families have been either inverters or buffer, the full potential for these designs to be used to implement reversible logic gates appears to have been overlooked. It has now been shown that the PFAL design style can be used to implement fully-reversible logic gates [Will08b]. Although the paper only investigates Toffoli gates [Fred82], it is obvious to anyone appropriately skilled that reversible designs are not limited to these gates. This means that, theoretically, these gates can operate reversibly. Furthermore, it is also an obvious conclusion that this concept for the adiabatic data-path can be extended such that it can function under *Asynchrobatic* operation.

### 2.4 Systematic search for other potential adiabatic logic families

If a matrix of all potential constructions of simple adiabatic gates based upon a pair of cross-coupled PMOS devices is constructed, then simulations can be performed to determine which style has the lowest operational power. This also allows a more complete design space to be searched to ascertain if any other potential designs have been missed.

In this thesis, a more systematic nomenclature is proposed to classify these families. It is as follows:

2n<sub>d</sub>: indicates NMOS pull-down evaluation devices.

2n<sub>u</sub>: indicates NMOS pull-up evaluation devices.

2n: indicates a pair of cross-coupled NMOS devices.

2p: indicates a pair of cross-coupled PMOS devices.

This allows the acronyms of some of the adiabatic families to be replaced with systematic descriptions. Table 2.2 shows the possible

combinations, and identifies that there is one logic style that has not previously been presented.

| Original Acronym   | Systematic Nomenclature             | Notes              |  |

|--------------------|-------------------------------------|--------------------|--|

| ECRL               | 2n <sub>d</sub> -2p                 |                    |  |

| PAL                | 2n <sub>u</sub> -2p                 | No path to ground! |  |

| EACRL              | 2n <sub>d</sub> 2n <sub>u</sub> -2p |                    |  |

| IECRL              | 2n <sub>d</sub> -2n2p               |                    |  |

| PFAL               | 2n <sub>u</sub> -2n2p               |                    |  |

| Previously unknown | 2n₀2n₀-2n2p                         | New!               |  |

Table 2.2: A systematic nomenclature for basic adiabatic logic families

The contributions of this work beyond the previously known state of the art are to have fully explored the potential design space, and to have proved that arbitrarily complex reversible logic functions can be implemented in both the adiabatic and Asynchrobatic Logic styles. This allowed the discovery of the 2n<sub>d</sub>2n<sub>u</sub>-2n2p logic family. If the inputs were split so that the 2n<sub>d</sub> and 2n<sub>u</sub> functions were the forward and recovery functions respectively, this could have operated at a lower-power than PFAL, with the evaluation happening through the 2n<sub>d</sub> path and the recovery through the 2n<sub>d</sub> path. Unfortunately, in simulations, this new logic family did not achieve any better power However, where uniform power consumption, rather than performance. minimum power consumption is a target, the use of some of these less efficient design styles may be of further research interest. The proposed systematic nomenclature could also be extended to cover more recent ideas such as the pass-gate inputs used by CPAL, allowing further methodical exploration of this extended potential adiabatic design space.

## 2.5 Adiabatic Power Supplies

Unlike static CMOS logic, due to being clock-powered, the adiabatic logic families derived from static DCVSL require a separate power supply. It

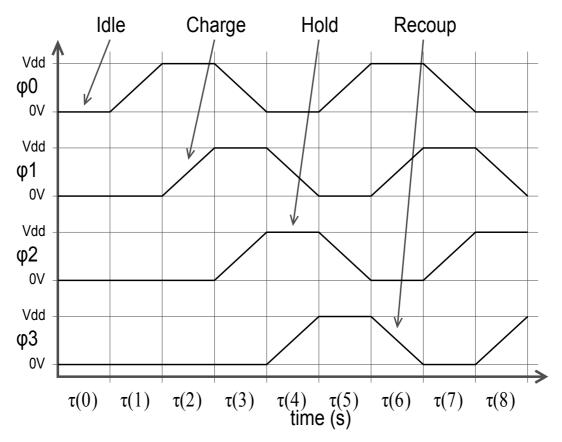

is necessary to consider these, and whilst brief details of inductor-based resonant clock-power supplies is necessary for completeness, the majority of this section will concentrate on the capacitor-based Stepwise Charging (SWC) methodology. Just as being able to design increasingly complex adiabatic logic families is futile if the only implementable components are buffers and inverters, it would be equally fruitless to design an adiabatic logic family that requires an excessive number of power-clocks, or has power-clocks which have unrealisable phasing or waveform requirements. The majority of the previously described adiabatic logic families have a requirement for a fourphase power-supply. The phase relationships of these ideal waveforms is shown in Figure 2.5. The four different power-clock phases are labelled from  $\phi 0$  to  $\phi 3$ , and the time periods are labelled  $\tau(0)$  to  $\tau(8)$ . Each power-clock moves from "Idle" to "Charge" to "Hold to "Recoup" and back to "Idle". Time periods  $\tau(0)$  to  $\tau(3)$  show how the power-clocks' phases are related during initial power-up and time periods  $\tau(4)$  to  $\tau(7)$  show how the power-clocks' phases are related during normal operation. It can be seen that time periods  $\tau(4) \& \tau(8)$  are identical, and therefore to continue operation can be achieved by repeating the sequence shown in time periods  $\tau(4)$  to  $\tau(7)$  ad infinitum.

Figure 2.5: Phase relationships of adiabatic power-clocks

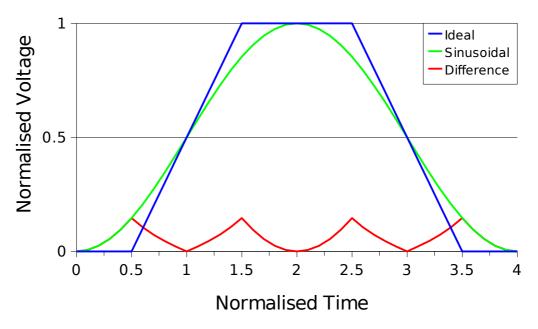

The early adiabatic logic families used inductor-based power supplies [Youn93]. These require off-chip inductors that are forced to resonate using relatively high-power MOSFET switches. As can be seen in the micrograph presented by Gabara *et al.* [Gaba95], the physical size of the inductor is similar to that of the silicon die! These were either synchronised by an external clock, or allowed to run freely at their resonant frequency. These generate sinusoidal waveforms that represent a reasonable approximation to the required four-phases. However, it is obvious that the sinusoid deviates from the ideal waveform substantially in the "*Idle*" and "*Hold*" phases. This can be quantified to an error of approximately 14.6% of the peak voltage, and because the ideal waveform is piecewise linear, for the "*Idle*" phase only, this error ( $\Delta$ E) is calculated from a normalised angle ( $\theta$ ) as shown in Equation (2.2).

$$\Delta E = \frac{1}{2} - \frac{1}{2} \cos(\theta) \tag{2.2}$$

This is derived by assuming that the normalised ideal waveform varies from 0V when in the "Idle" phase to 1V when in the "Hold" phase, and that the sinusoidal wave's minimum is at 0° and in the centre of the "Wait" phase. This means that the sinusoidal waveform will be defined by the negative cosine function, but to be normalised to 1V, it will need to be scaled by half and shifted up by half. Thus the maximum deviation of 14.6% from the ideal waveform will occur when ( $\theta$  = 45°), and although the function may be different, every 90° thereafter. There are four locations, halfway through each phase where the ideal sinusoid and the ideal waveform are identical. Figure 2.6 shows how the sinusoidal waveform compares with the ideal waveform, and also plots the absolute difference between these two waveforms. The error is important because during the "Idle" and "Hold" phases, the devices' power-clocks will not be driven to full-rail voltage potentially allowing leakage, and other power-consuming conditions to occur.

Figure 2.6: Difference between Ideal and Sinusoidal waveforms

There may be potential to achieve less difference if it is possible to slightly overdrive the sinusoidal waveform without exceeding the electrical tolerances of the fabrication process. However, whilst sinusoidal

power-clocks are used in adiabatic logic, such power-clocks do not feature in *Asynchrobatic* Logic, so no further investigations relating to them were performed.

An alternative, capacitor-based method that can be used as a charge recovering power supply is Stepwise Charging (SWC) [Sven94a] & [Sven94b]. It achieves a different approximation to the ideal waveform which, like the ideal waveform, but unlike that derived from a resonant power-clock, is static in its "Idle" and "Hold" phases. The waveform can be created by successively charging and discharging the capacitive load through various intermediate voltages by means of a series of sequentially switched tank capacitors. It is obvious that as the number of steps approaches infinity, the waveform becomes a progressively better approximation to the ideal waveform.

It has been shown that for a suitably large load, even a power supply with a single intermediate step can improve the efficiency of some systems [Hahm94]. A familiar macroscopic implementation of a system that uses the idea of a stepwise process is a flight of locks on a canal.

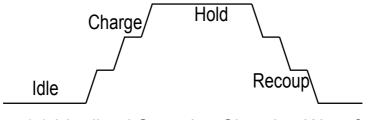

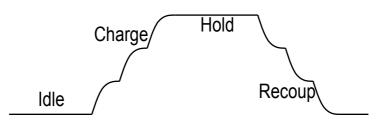

Stepwise charging waveforms are shown in Figure 2.7. Figure 2.7(a) shows an idealised stepwise charging waveform with three intermediate stages and Figure 2.7(b) shows the realised stepwise charging waveform. These deviate from the ideal, because each step charges the load capacitance using a constant voltage, resulting in the shown curve.

(a) Idealised Stepwise Charging Waveform

(b) Realisable Stepwise Charging Waveform

Figure 2.7: Stepwise Charging Waveforms

SWC has a number of properties that make it far more attractive than inductor-based designs for use in *Asynchrobatic* Logic:

- It has been shown to converge at start-up [Dhar96] & [Naka04].

- It has simple next-state logic that can easily be operated asynchronously.

- It can be implemented in a modular fashion allowing design reuse.

- It can be implemented using on-chip capacitors.

- It is static during the "Idle" and "Hold" phases.

- It does not require off-chip inductors.

### 2.6 Reversible Computation

In this introduction to adiabatic logic, it is essential to look at the closely related area of reversible computation. This requires that any computation could be performed both in a direction that would be thought of as forwards, processing the inputs to produce outputs **and** in the opposite, reverse direction, where the outputs are "de-processed" to produce the inputs. The

following simple example, which pays homage to Douglas Adams and his science-fiction writings [Adam79], will demonstrate why this seemingly simple concept can be problematic in practice.... If the answer is forty-two, what was the question? Even if it is known that the answer was obtained using six-bit unsigned integer addition, the question could be forty-one plus one or twenty plus twenty-two. This problem arises as a consequence of the destruction of information, and this information loss occurs in the majority of processing. An obvious way to make addition reversible is to preserve one of the inputs. This leads to the requirement for reversible systems to have the same number of inputs as outputs. For logic implementations, it is required that the function being used is invertible. So for any function of three-bits, each one of the eight possible input states would map to one of the eight possible output states.

A familiar application that is invertible, when thought of as a black-box, is a block cipher. Its forward operation is encryption and its operation reverse is decryption. For such a cryptosystem, the Key remains unchanged, but transforms the Plain Text into the Cipher Text or *vice-versa* without the loss of information. An in-depth *exposé* of the on-going theoretical work on Reversible Logic, Reversible Computation and associated subject areas is beyond the scope of this thesis, but interested readers are directed to, for example, the works of Kerntopf [Kern02].

The logical reversibility of an operation is an essential part of a truly adiabatic system, and therefore, the majority of systems that purport to be adiabatic would be better described as only quasi-adiabatic, as whilst charge recovery allows them to operate with more power efficiency than standard static CMOS, they still have not insignificant non-adiabatic losses. Clearly, there are some designs which are reversible where the non-adiabatic losses have been substantially reduced. However, just as friction prevents mechanical systems operating without some dissipation, relegating perpetual

motion machines to the realms of pseudo-science, electrical resistance prevents even these electronic systems operating without some dissipation.

## 2.7 Summary

In this chapter the concepts of adiabatic logic and quasi-adiabatic logic have been introduced. Details of a large number of adiabatic logic families have been presented. This has included providing an overview of twelve examples that are frequently cited, and expanded descriptions of the four candidate families: ECRL, IECRL, PFAL and EACRL, which are proposed to be used in *Asynchrobatic* Logic. A systematic exploration of the design space was conducted, and although this yielded a previously unknown design, it was not found to have any benefits over already known designs.

The concept of a power-clock has been introduced, detailing an ideal power-clock, and two possible realisable implementations. The generation of power-clocks using inductor-based resonant charging, and stepwise charging was introduced. Finally reversible computation was discussed, as unless a process is reversible, it can not be adiabatic, but only quasi-adiabatic.

# Chapter 3 A review of asynchronous logic

### 3.1 Introduction

In this chapter, the basic concepts of asynchronous logic will be introduced. Since this work was more focused upon adding a basic asynchronous controller to an adiabatic data-path, the depth of coverage of asynchronous logic is lower.

Like "Adiabatic", the term "Asynchronous" is also of Greek origin. It literally means "without alike time", but in the context of microelectronic design, its meaning has evolved to mean without a global time reference (a clock). Thus asynchronous logic is a logic design style that does not use a clock to synchronise the performance of operations. This is in stark contrast to the majority of digital circuits currently in existence, which have been designed using a synchronous design methodology. Unlike them, asynchronous logic does not use a ticking clock, but instead it uses a handshaking protocol to facilitate inter-stage communication.

This can have several benefits when compared against traditional synchronous designs. For *Asynchrobatic* Logic, the most important of these documented benefits are lower power and potential for design reuse. However, in some of the proposed applications, other benefits like lower electro-magnetic noise would also be of benefit [VBer94].

When compared to a synchronous system both asynchronous and *Asynchrobatic* systems will have the benefits of power-supply voltage tolerance, allowing lower voltage operation than would normally be possible for synchronous systems. This is because the synchronous design methodology requires its design elements, standard cells, to be characterised at fixed Process, Voltage and Temperature (PVT) conditions. The slowest of these is normally slowest process, lowest tolerable voltage and highest

temperature. Outside of the qualified range the circuits may fail due to violating setup-time requirements, with data-arriving too late to be correctly latched by a clock edge. This limits the voltage scaling that may be applied to a synchronous circuit. For both standard synchronous and standard asynchronous logic, the effect of lowering the voltage will reduce the power-consumption according to equation (3.1).

$$P_{D} = f_{e} C_{L} V_{DD}^{2} \tag{3.1}$$

in which:  $P_D$  is the dynamic power dissipation,

fe is the effective switching frequency,

C<sub>L</sub> is the capacitive load, and

$V_{DD}$  is the supply voltage.

Other low-power benefits can be illustrated by looking forward and considering a large Asynchrobatic system in comparison to an equivalently large asynchronous system and an equivalently large synchronous system. The lack of a global clock is also a major benefit. In the synchronous system, the ticking global clock would at minimum, reach a clock-gating element at the entry to each stage, and consequentially would waste energy. asynchronous and Asynchrobatic systems, the inactive states are just that, inactive, and as such, with no switching occurring, only leakage power will be consumed. However, in the Asynchrobatic system, there will be, on average, a quarter of the controllers in each of the charging states ("Idle", "Charge", "Hold", "Recoup"). The active states ("Charge" and "Recoup") require several operations, whilst the inactive states ("Idle", "Hold") require no operations. It should also be noted that for Asynchrobatic Logic, for any stage in the "Idle" state, the entire data-path has no potential difference across it from the powersupply, meaning that there is not even the possibility of having any sourcedrain leakage current through it! The only possible leakage current paths are gate-leakage from adjacent stages.

In his introduction Sparsø notes that research into asynchronous logic has been taking place since the 1950's [Spar01], and important theory had

been published by the end of that decade [Mull59]. However, probably the most influential development was Sutherland's invention of Micropipelines [Suth89]. These explain the control components required to implement asynchronous systems, but their hand-shaking protocol does not suit the adiabatic parts of an *Asynchrobatic* system. Asynchronous logic is more technologically mature than adiabatic logic, and as well as having been shown to be suitable for the implementation of complex processors [Pave94], commercial asynchronous processors are now available [Hand04].

## 3.2 Asynchronous signalling

There are two different types of asynchronous signalling conventions, two-phase and four-phase. Two-phase signalling simply reacts to a change of the signals, whilst four-phase signalling is dependent upon the levels of the signals. There are also two different methods for data transmission; bundled-data and dual-rail. For different reasons, the adiabatic data-path is already dual-rail, but the chosen implementation operates using principles far more akin to those of bundled-data. Whilst a brief background to both of the signalling styles and data transmission methods will be provided, this section will concentrate on, and elaborate more fully, the principles of systems based upon four-phase signalling with bundled-data. The asynchronous communication occurs between the Asynchronous Stepwise Charging controllers, and the bundled-data is held on the adiabatic data-path.

The handshaking protocols in asynchronous logic usually use two signals, a "request" from the sender to the receiver, and an "acknowledge" from the receiver to the sender.