# THE DESIGN AND DEVELOPMENT OF AN ORGANIC COMPARATOR FOR USE IN LOW COST SMART SENSOR SYSTEMS

Thesis submitted in accordance with the requirements of the University of Liverpool for the degree of Doctor in Philosophy

By

**RUTH WANJAU**

SEPTEMBER 2017

#### **ABSTRACT**

## The Design and Development of an Organic Comparator for use in Low Cost Smart Sensor Systems

Ruth Wanjau

This thesis chiefly examines ways of increasing the frequency response of circuits through using organic materials with high charge carrier mobility values as well as by reducing the overlap parasitic capacitances in thin film transistors (TFTs) by developing and optimizing of a self-aligned gap (SAG) fabrication process. The organic materials studied in this work include: Polytriarylamine (PTAA), Poly 3-hexylthiophene (P3HT), Poly [2, 5-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-b] thiophene] (PBTTT-C16) and Indacenodithiophene-co-benzothiadiazole (IDTBT-C16). The electrical characterisation of the above-mentioned polymers are carried out using Schottky diodes, OTFTs and saturated-load inverters. The analysis of these devices is done with the aid of appropriate organic models developed in this work, which assume an exponential approximation to the tail of the Gaussian Density of States (DOS). Key material parameters of the disordered models i.e. the Meyer Neldel energy (MNE), the characteristic temperature of the DOS  $(T_C)$ , the mobility prefactor (K) and the degree of disorder (m) are subsequently utilised in the design of organic circuits in Cadence design software.

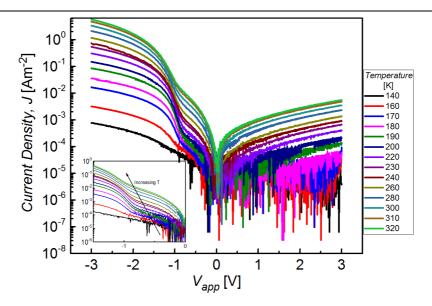

A temperature study of PBTTT-C16 and IDTBT-C16 polymers is carried out using vertical Schottky diode with the aim of investigating the conduction mechanisms present in the films. The values of  $T_0$ ,  $T_C$  and MNE of the PBTTT-C16 diode, obtained from the forward characteristics, are found to be 707.5 K, 523.6 K and 45 meV respectively and the values of the IDTBT-C16 diode are found to be

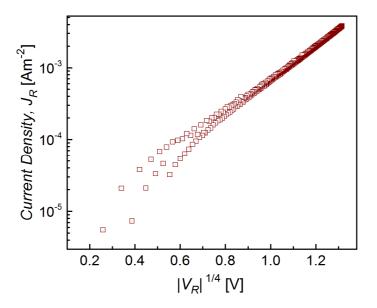

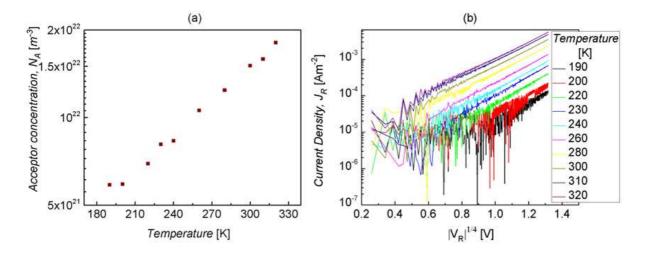

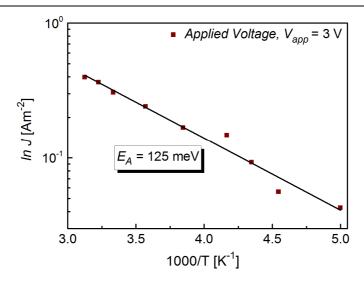

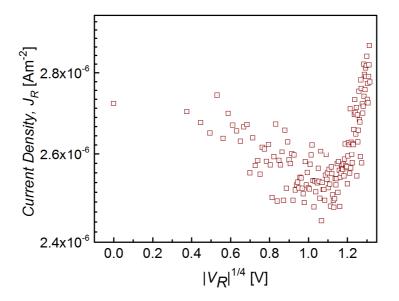

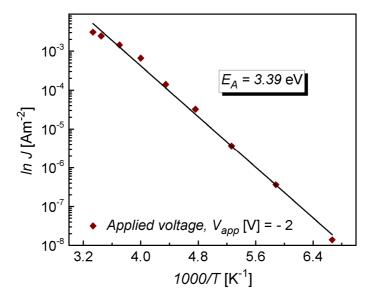

343.6 K, 382.7 K and 33.0 meV respectively. The acceptor density value,  $N_A$ , of the PBTTT-C16 diode is obtained from the semi-logarithmic plot of  $J_R$  versus  $V_R^{1/4}$  and found to be  $1.59\times10^{22}$  m<sup>-3</sup>. The activation energy,  $E_A$ , values of the PBTTT-C16 and IDTBT-C16 devices are 126 meV and 339 meV respectively, with the higher  $E_A$  value obtained for the IDTBT-C16 polymer being because of the large intermolecular  $\pi$ -stacking distances present in the polymer.

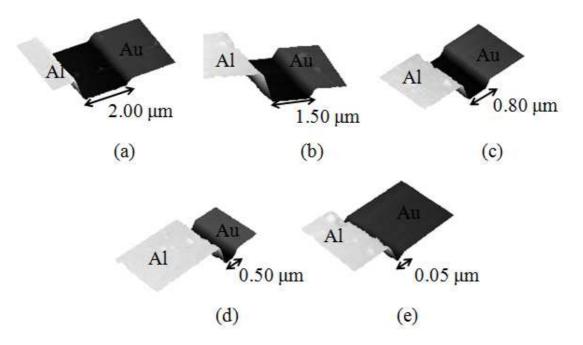

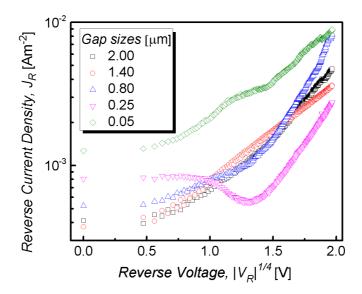

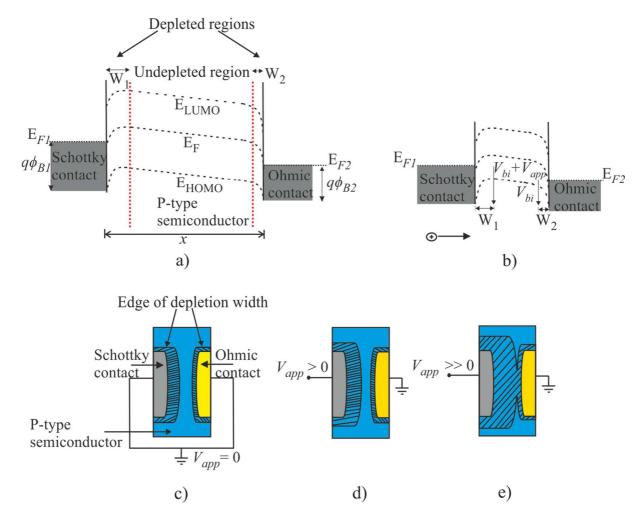

A SAG process that utilizes a bi-layer photoresist structure to create an undercut is developed. The size of the undercut formed from the process is found to vary inversely with the soft bake temperature and time. Utilizing the various gap sizes formed from the process, lateral PTAA diodes are fabricated and characterized accordingly. With the gap size increasing from 0.05  $\mu$ m to 2  $\mu$ m, the forward current density values decreases inversely from 15.86 Am<sup>-2</sup> to 0.31 Am<sup>-2</sup> due to an increase in the series resistance of the devices. Similarly, the conduction mechanism in the devices is found to be more limited by contact resistance effects as the gap size decreases. In addition, the  $N_A$  values obtained from the devices ranges from 2.33×10<sup>20</sup> m<sup>-3</sup> to 1.76×10<sup>21</sup> m<sup>-3</sup>. Interestingly enough, CV measurements and SILVACO simulations of these devices show that the modulation of the depletion layer in devices with a lateral topology is chiefly dependent on the electrode spacing and area of the active layer rather than the film thickness as is typically observed in vertical diodes.

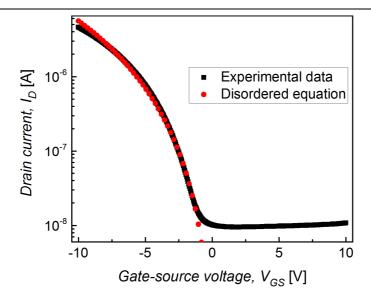

The parameters of a PBTTT-C16 self-aligned transistor with an aspect ratio of 50 are utilized in the design and modelling of organic circuits within this work. The device has a sub-threshold swing of -1.8 V/decade, an on/off

ratio of  $4.26 \times 10^2$ , a saturation field effect mobility value,  $\mu_{fe}$  of  $0.74~\rm cm^2~\rm V^{-1}~\rm s^{-1}$  and a threshold voltage,  $V_T$  of  $-1.5~\rm V$ . Utilizing the disordered model developed in this work, the values of m, K,  $T_C$  and MNE are 0.57,  $2.15 \times 10^{-16}~\rm AV^{-m}$ ,  $473~\rm K$  and  $41~\rm meV$  respectively. These parameters are subsequently used in Cadence design software to create a compatible OTFT model for subsequent design of an organic comparator. The comparator has a maximum gain of  $45.62~\rm dB$  and operates at a  $300~\rm Hz$  frequency. A PBTTT-C16 saturated load inverter with a gain of  $12.4~\rm dB$  and an average propagation delay of  $3.4~\rm ms$  is also fabricated using the Cadence mask designs developed for the SAG process. A study of the effect of varying the width of the driver transistor of the inverters as well as the use of materials with lower mobility values is also investigated. The challenges of the SAG process are also highlighted with possible methods to circumvent and in some cases eliminate them presented as well.

|       | 1  |      |    | 4   | 1                   |

|-------|----|------|----|-----|---------------------|

| - 1 ) | ed | II.  | റവ | 1   | $\Delta \mathbf{A}$ |

| IJ    | CU | יווו | La | . L | CU                  |

to

My Loving Family

## **ACKNOWLEDGEMENTS**

I would like to take this opportunity to thank God Almighty for giving me the strength and the provision to undertake this research degree for the last four years.

I would sincerely like to thank my supervisor, Dr.M. Raja, for giving me the opportunity to carry out research work with her. Your patience and tireless efforts throughout my research degree will forever be remembered and appreciated.

My sincerest appreciation is due to the Head of Department, Prof. A. Marshall, as well as the head of the BOSE group, Prof. S. Hall, for the provision of facilities and maintenance of clean room facilities. In addition, I would like to appreciate the past and present members of the BOSE group particularly Dr. D. Donaghy, Dr. J. Hanson, Dr. N. Sedghi and Dr. J. Jin for their patience, supervision and willingness to help me in and out of the clean room facilities. Furthermore, I am thankful to Prof. M. Heeney from Imperial College London for the provision of high quality polymers used in the fabrication of devices in this work.

Last but certainly not least, I would like to thank my family for being my rock and support system throughout this journey. I am truly thankful for your constant love and encouragement throughout the years and for continuously affirming to me, through words and actions, the saying "It takes a village to raise a child".

# TABLE OF CONTENTS

| LIST OF FIGURESXII                                                                                      |

|---------------------------------------------------------------------------------------------------------|

| LIST OF TABLESXVII                                                                                      |

| ABBREVIATIONSXVIII                                                                                      |

| SYMBOLSXXI                                                                                              |

| CHAPTER 1: INTRODUCTION                                                                                 |

| 1.1 INTRODUCTION TO ORGANIC SEMICONDUCTORS AND ORGANIC CIRCUIT                                          |

| TECHNOLOGY2                                                                                             |

| 1.2 ORGANISATION OF THE THESIS6                                                                         |

| 1.3 EXPERIMENTAL TECHNIQUES/CHARACTERISATION8                                                           |

| 1.4 CONTRIBUTIONS                                                                                       |

| 1.5 REFERENCES                                                                                          |

| CHAPTER 2: CHARGE TRANSPORT PROPERTIES OF ORGANIC SEMICONDUCTORS AND ITS APPLICATION IN ORGANIC DEVICES |

| 2.1 INTRODUCTION                                                                                        |

| 2.2 MATERIAL PROPERTIES AND CHARGE TRANSPORT IN ORGANIC                                                 |

| SEMICONDUCTORS                                                                                          |

| 2.2.1 ELECTRONIC STRUCTURE IN ORGANIC SEMICONDCUTORS17                                                  |

| 2.2.2 DENSITY OF STATES FUNCTIONS                                                                       |

| 2.2.3 CHARGE TRANSPORT IN ORGANIC SEMICONDUCTORS21                                                      |

| 2.3 FUNDAMENTAL THEORY OF SCHOTTKY DIODES AND THIN-FILM TRANSISTORS (TFTs)                              |

|                                                                                                         |

| 2.3.1 METAL/SEMICONDUCTOR CONTACTS - SCHOTTKY DIODES                                                    |

| 2.3.1 METAL/SEMICONDUCTOR CONTACTS - SCHOTTER DIODES                                                    |

| 2.3.2 THEORY OF TFTs                                                                                    |

|                                                                                                         |

| 2.3.2 THEORY OF TFTs                                                                                    |

| 3.1 INTRODUCTION                                  | 53                             |

|---------------------------------------------------|--------------------------------|

| 3.2 FABRICATION OF VERTICAL IDTBT-C16 AND I       |                                |

| 3.3 PBTTT-C16 SCHOTTKY DIODE                      | 59                             |

| 3.3.1 CURRENT DENSITY-VOLTAGE CHARACT             | ERISTICS OF PBTTT-C16 SCHOTTKY |

| DIODE                                             |                                |

| 3.3.2 TEMPERATURE-DEPENDENCE OF PBTTT             | -C16 SCHOTTKY DIODE 65         |

| 3.4 IDT-BT SCHOTTKY DIODE                         |                                |

| 3.4.1 CURRENT DENSITY-VOLTAGE CHARACTE            | ERISTICS OF IDTBT-C16 SCHOTTKY |

| DIODE                                             |                                |

| 3.4.2 TEMPERATURE DEPENDENCE OF IDTBT-            |                                |

| 3.5 CONCLUSIONS                                   |                                |

| 3.6 REFERENCES                                    | 83                             |

| CHAPTER 4: DEVELOPMENT AND OPTIMISA               | TION OF A SELF-ALIGNED GAP     |

| PROCESS FOR ORGANIC LATERAL DEVICES               | 85                             |

| 4.1 INTRODUCTION                                  | Qe                             |

| 4.2 THE STUDY OF A SELF-ALIGNED PROCESS US        |                                |

| 4.2.1 FABRICATION METHODOLOGY                     |                                |

| 4.2.2 CHARACTERISATION OF THE UNDERCU             |                                |

| 4.2.3 CURRENT-VOLTAGE CHARACTERISTICS             |                                |

| 4.2.4 PATTERNING SURVEY OF THE CURRENT            |                                |

| PTAA SCHOTTKY DIODES                              |                                |

| 4.3 SELF-ALIGNED THIN-FILM TRANSISTOR WITI        |                                |

| 4.3.1 FABRICATION METHODOLOGY                     |                                |

| 4.3.2 OUTPUT CHARACTERISTICS OF THE PBI           |                                |

| 4.3.3 TRANSFER CHARACTERISTICS OF THE P           | PBTTT-C16 TFT118               |

| 4.4 CONCLUSIONS                                   |                                |

| 4.5 REFERENCES                                    |                                |

| CHAPTER 5: DESIGN, DEVELOPMENT AND C              |                                |

| CIRCUITS USING A SELF-ALIGNED GAP PRO             | CESS129                        |

| 5.1 INTRODUCTION                                  | 130                            |

| 5.2 MODELLING AND DESIGNING OF ORGANIC CI         |                                |

| 5.2.1 CADENCE DESIGN MODEL                        |                                |

| 5.2.2 DESIGN AND SIMULATION OF AN ORGA            |                                |

| 5.3 CHARACTERISATION OF SAG ORGANIC CIRC          |                                |

| 5.3.1 FABRICATION METHODOLOGY                     |                                |

| 5.3.2 RESULTS AND ANALYSIS                        |                                |

| 5.4 CONCLUSIONS                                   |                                |

| 5.5 REFERENCES                                    |                                |

| CHAPTER 6: CONCLUSIONS AND RECOMME                | NDATIONS FOR FUTURE WORK       |

|                                                   |                                |

|                                                   |                                |

| 6.1 CONCLUSIONS                                   |                                |

| D / WHI (19/19/19/19/19/19/19/19/19/19/19/19/19/1 | 1.7.7                          |

| APPENDICES                                                    | <i>175</i> |

|---------------------------------------------------------------|------------|

| APPENDIX A: EXPRESSION FOR THE FREE CARRIER CONCENTRATION IN  | A P-TYPE   |

| DISORDERED ORGANIC SEMICONDUCTOR                              | 176        |

| APPENDIX B: EXPRESSION FOR THE EFFECTIVE MOBILITY IN TERMS OF |            |

| CONCENTRATION                                                 | 178        |

| APPENDIX C: EXPRESSION FOR THE FORWARD CURRENT DENSITY OF AN  | N ORGANIC  |

| DIODE AT LOW APPLIED BIAS                                     | 180        |

| APPENDIX D: EXPRESSION FOR THE FORWARD SPACE CHARGE LIMITED   | CURRENT    |

| (SCLC) DENSITY OF AN ORGANIC DIODE AT HIGHER APPLIED BIAS     | 182        |

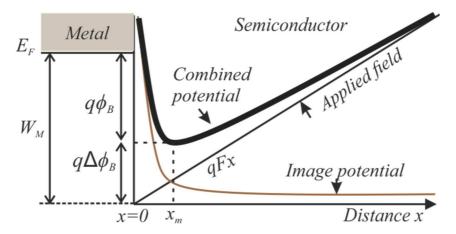

| APPENDIX E: EXPRESSION FOR $\Delta \phi_B$ IN SCHOTTKY DIODES | 185        |

| APPENDIX F: DISORDERED MODEL FOR AN ORGANIC THIN-FILM TRANSI  |            |

|                                                               | 189        |

| APPENDIX G: VERILOG CODE FOR OTFT MODEL                       |            |

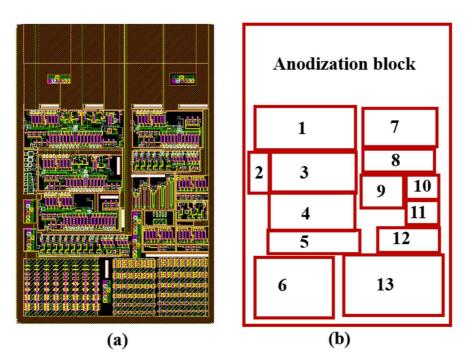

| APPENDIX H: DRC RULES FOR THE SELF-ALIGNED GAP (SAG) PROCESS  | 195        |

| APPENDIX I: MASK LAYOUT OF THE CIRCUIT DESIGNS                | 198        |

| APPENDIX J: CONFERENCE AND JOURNAL PAPERS                     |            |

# LIST OF FIGURES

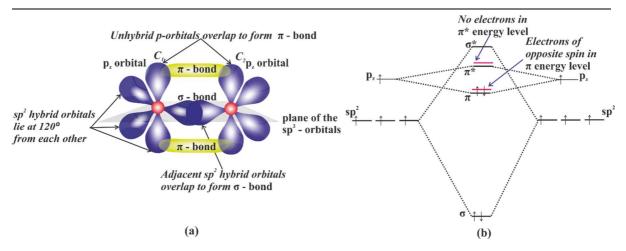

| Figure 2. 1: Illustration of the bonding between two adjacent carbon atoms, $C_1$ and $C_2(a)$ and the equivalent energy structure (b). The hybridised orbitals lie within 120° from each other whilst the unhybridised orbitals lie on the perpendicular plane. 18 Figure 2. 2: Illustration of the Gaussian DOS distribution and the exponential approximation at the tail of the Gaussian for a given energy range. 20                                                       | f |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

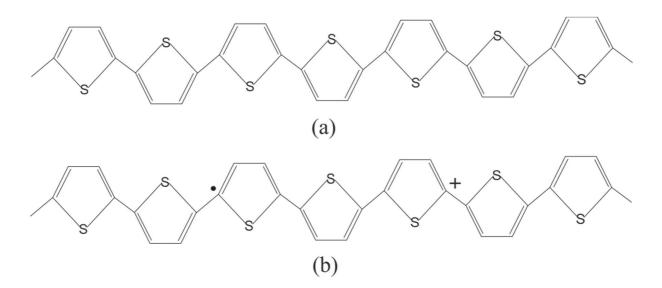

| Figure 2. 3: (a) Chemical structure of a polythiophene. (b) Change in the chemical structure of polythiophene after a polaron is formed                                                                                                                                                                                                                                                                                                                                         |   |

| Figure 2. 4: Illustration of the Multi-trap and release model. Filled circles represent charge carriers introduced through thermal excitation or injection                                                                                                                                                                                                                                                                                                                      |   |

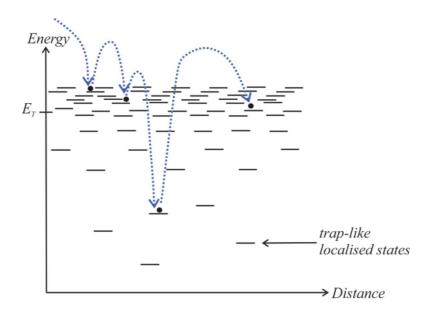

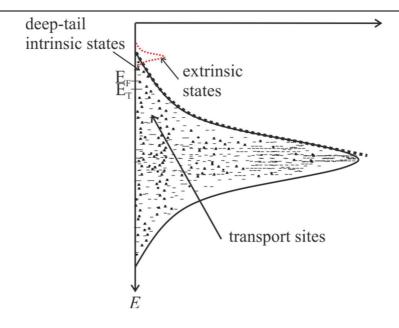

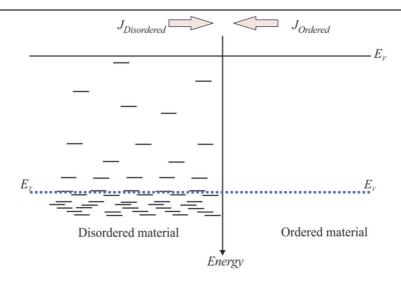

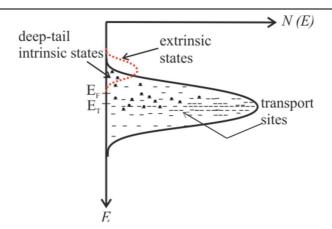

| Figure 2. 5: Illustration of an exponential approximation to the tail of the Gaussian DOS distribution for the lower energy range, where charge transport in organic devices typically takes place. Charge carriers above $E_F$ are trapped and do not contribute to conduction. At lower energies, close to $E_F$ , an increase in carrier concentration results in an increase in mobility due to the enhanced hopping rates                                                  |   |

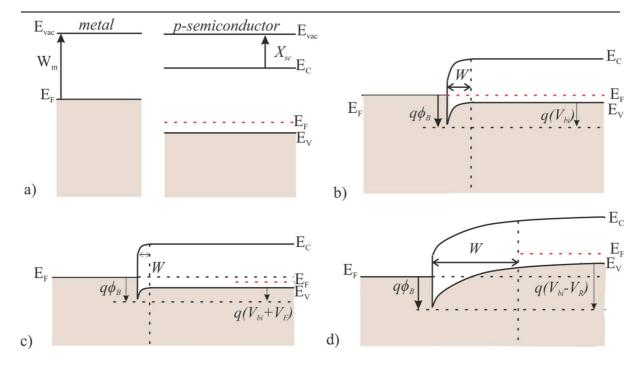

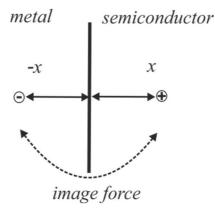

| equilibrium, for a p-type semiconductor. Band bending and trapped charges are assumed absent                                                                                                                                                                                                                                                                                                                                                                                    |   |

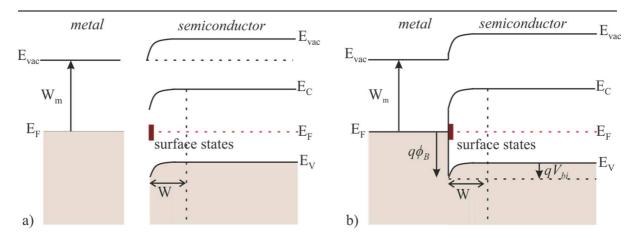

| Figure 2. 8: Energy band diagram of a p-type metal-semiconductor junction that is characterised by surface states at the interface of the metal and semiconductor: a) before contact formation and b) after contact formation                                                                                                                                                                                                                                                   | 7 |

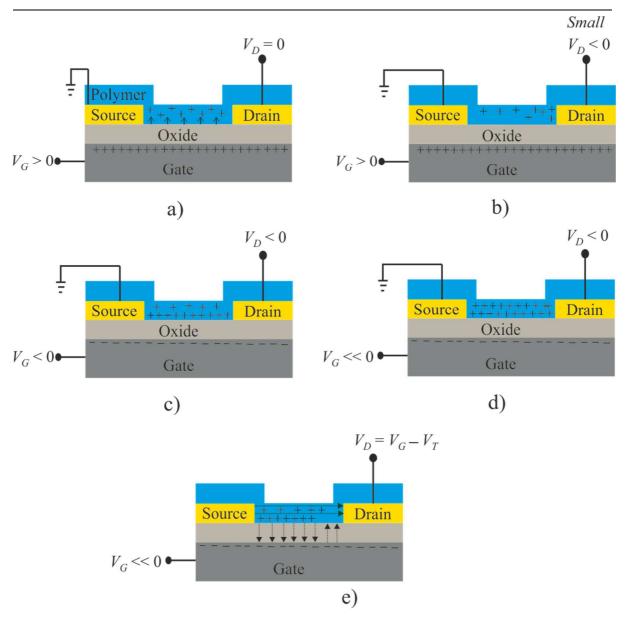

| Figure 2. 9: Basic theory of the operation of a TFT: a) Holes accumulate at the surface of the semiconductor with application of $V_G$ . b) Holes move toward the drain with application of small $V_D$ . c) Accumulation of holes at the oxide and semiconductor interface with negative $V_G$ . d) Increased accumulation of holes in the channel with injection of carriers at the drain. e) No carriers at the drain end when $V_D = V_G - V_T$ resulting in pinch off      | 2 |

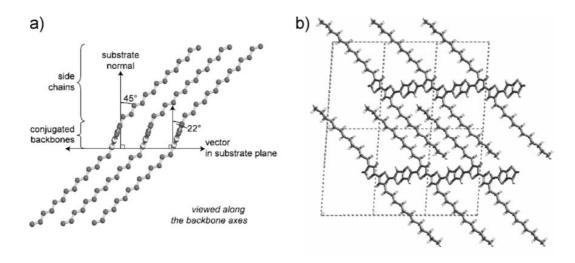

| Figure 3. 1: (a) Coplanar arrangement of the individual PBTTT monomer units lying along a monome backbone. (b) Structure of the interdigitated alkyl side chains resulting in closer $\pi$ - $\pi$ stacking. Image taken from [8]53                                                                                                                                                                                                                                             | r |

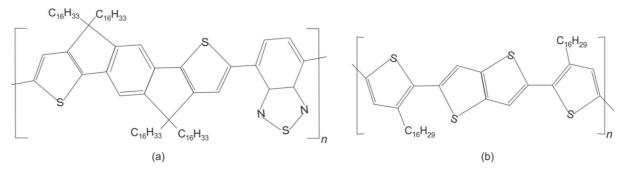

| Figure 3. 2: Structure of (a) Indacenothiophene–benzothiadiazole (IDTBT-C16) copolymer and (b) Poly                                                                                                                                                                                                                                                                                                                                                                             | , |

| [2, 5-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-b] thiophene] (PBTTT-C16) polymer                                                                                                                                                                                                                                                                                                                                                                                             |   |

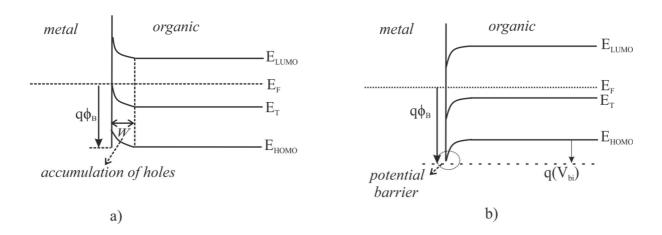

| Figure 3. 4: (a) The theoretical band diagram of a p-type semiconductor in contact with an Ohmic metal contact at thermal equilibrium. The accumulation layer width, W, depends on the intrinsic carrier concentration of the polymer. (b) The theoretical band diagram of a p-type semiconductor in contact with a Schottky metal at thermal equilibrium. The built-in potential and energy barrier form because of the differences in the work functions of the two materials |   |

| v v                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

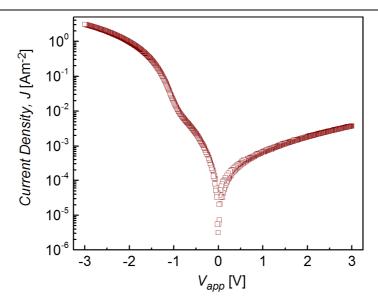

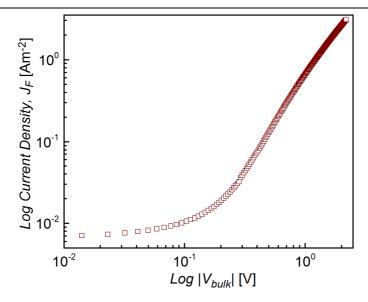

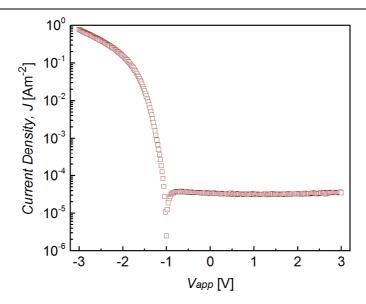

| Figure 3.5: Semi-logarithmic plot of the current density-voltage characteristics of PBTTT-C16 Schottky diode. The voltage is applied to the Schottky contact with respect to the Ohmic contact                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.6: Double-logarithmic plot of the forward characteristics versus bulk voltage of the PBTTT-C16 Schottley diede                                                                                                                                                                                              |

| Schottky diode                                                                                                                                                                                                                                                                                                       |

| Figure 3.8: Reverse current density against $ V_R ^{1/4}$ for the PBTTT-C16 Schottky diode. The deviation of the                                                                                                                                                                                                     |

| linearity at lower applied voltages is due to the $(V_{bi}-V_R-kT/q)$ term                                                                                                                                                                                                                                           |

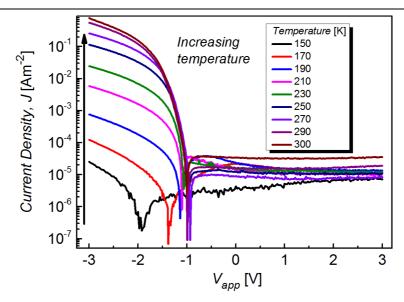

| Figure 3. 9: Semi-logarithmic plot of current density-voltage characteristics of PBTTT-C16 Schottky diode measured at a temperature range between 140 K and 320 K. The voltage is applied onto the Schottky contact while the Ohmic contact is grounded                                                              |

| Figure 3.10: (a) Variation of the acceptor concentration $N_A$ , with varying temperature. The values of $N_A$ are extracted from the semi-logarithmic plot of the slope of the reverse current density with $ V_R ^{1/4}$ as                                                                                        |

| shown in (b)                                                                                                                                                                                                                                                                                                         |

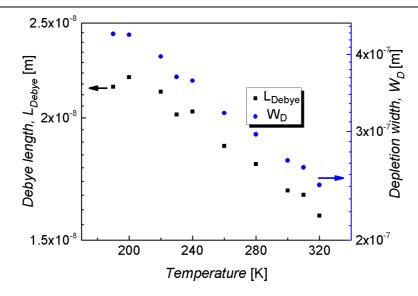

| Figure 3.11: Logarithmic plot of the depletion width, W and Debye length, $L_{Debye}$ with varying                                                                                                                                                                                                                   |

| temperature from 190 K to 320 K                                                                                                                                                                                                                                                                                      |

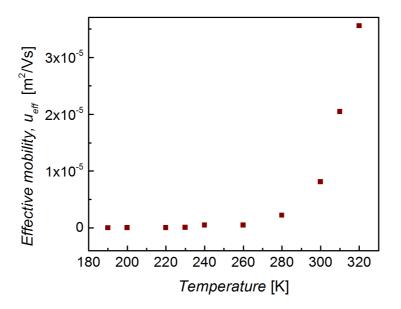

| Figure 3.12: Variation of the effective mobility with temperature                                                                                                                                                                                                                                                    |

| Figure 3.13: Arrhenius plot of the forward current density against 1000/T for PBTTT-C16. An activation energy of 126 meV is extrapolated from the slope                                                                                                                                                              |

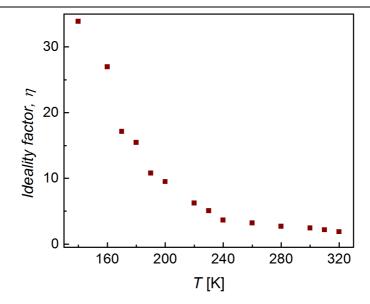

| Figure 3. 14: Variation of the ideality factor with temperature for PBTTT-C16 Schottky diode                                                                                                                                                                                                                         |

| Figure 3.15: Semi-logarithmic plot of current density-voltage characteristics of IDTBT-C16 Schottky                                                                                                                                                                                                                  |

| diode. The voltage is applied to the Schottky contact while the Ohmic contact is grounded                                                                                                                                                                                                                            |

| Figure 3.16: Reverse current density $J_R$ against $ V_R ^{t_A}$ of IDTBT-C16 Schottky diode                                                                                                                                                                                                                         |

| Figure 3.17: Semi-logarithmic plot of the current density-voltage characteristics of IDTBT-C16                                                                                                                                                                                                                       |

| Schottky diode measured for a given temperature range between 150 K and 300 K                                                                                                                                                                                                                                        |

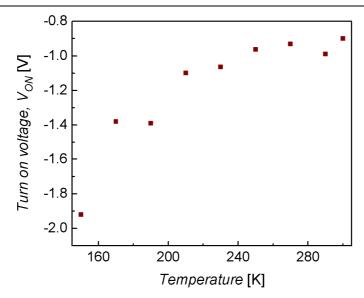

| Figure 3. 18: Variation of the turn-on voltage, V <sub>ON</sub> with temperature for IDBT-C16 Schottky diode 76                                                                                                                                                                                                      |

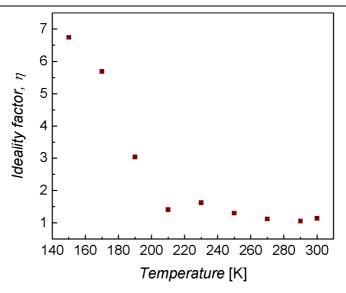

| Figure 3. 19: Variation of the ideality factor with temperature for IDTBT-C16 Schottky diode                                                                                                                                                                                                                         |

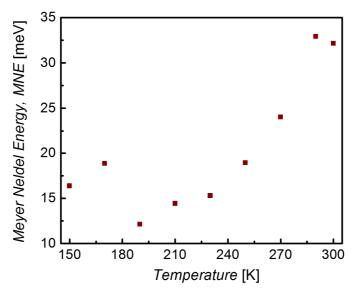

| Figure 3. 20: Variation of the Meyer Neldel Energy (MNE) extracted from the slope of the forward current density versus the bulk voltage taken at higher voltage values with temperature. (Slopes of greater than 2 are obtained corresponding to the presence of space charge effects with changes in temperature). |

| Figure 3.21: Arrhenius temperature plot of the forward current density against 1000/T of IDTBT-C16 Schottky diode. The activation energy is extrapolated from the slope and found to be 3.39 eV as shown                                                                                                             |

| inset                                                                                                                                                                                                                                                                                                                |

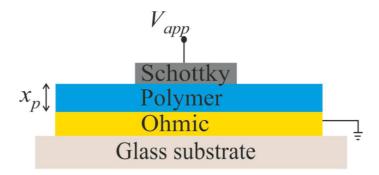

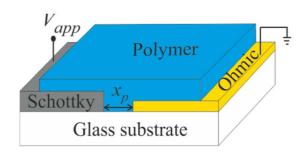

| contacts respectively. The electric field is intensified with smaller inter-electrode spacing defined by the gap, $x_p$ . The width of the Ohmic and Schottky contact is 1mm and the area of the patterned active layer is estimated to be around $0.3\mu m^2$ (i.e. 300 $\mu$ m by 1 mm polymer coverage)           |

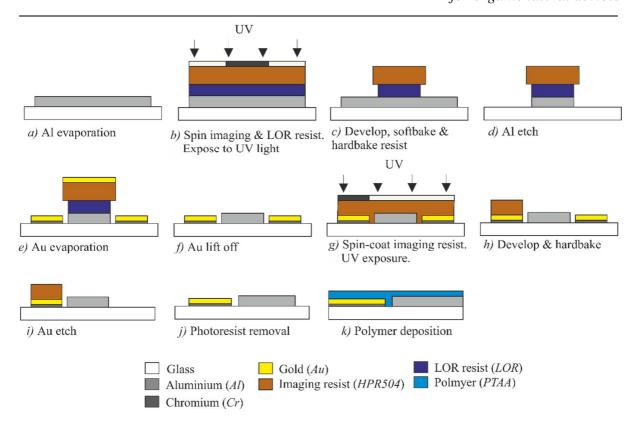

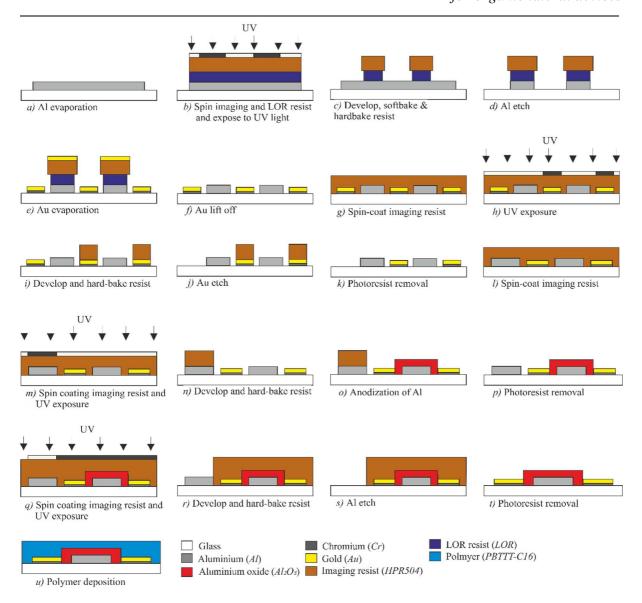

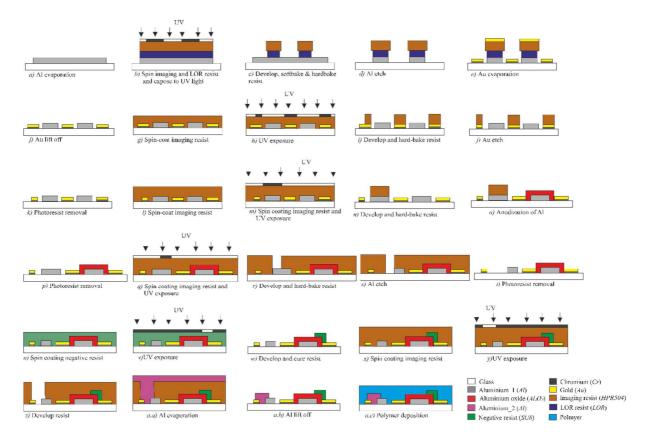

| Figure 4. 2: Overview of the fabrication of a lateral Schottky diode made using a SAG fabrication                                                                                                                                                                                                                    |

| processes                                                                                                                                                                                                                                                                                                            |

| fabrication processes                                                                                                                                                                                                                                                                                                |

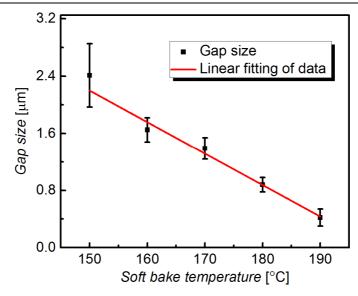

| Figure 4. 4: Variation of the gap size with respect to the soft bake temperature for a soft bake time of 225 seconds                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4. 5: Variation of the gap size with respect to the soft bake time for a soft bake temperature of 170 °C                                                                                                                                                                                                                                                                                                                                          |

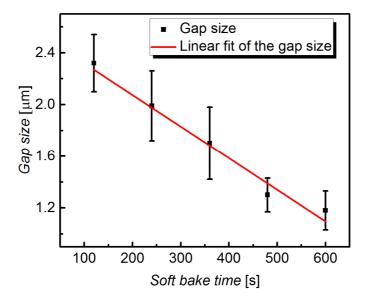

| Figure 4. 6: AFM images of the different gap sizes obtained by varying the soft bake temperature from 150 °C to 190 °C. The inter-electrode spacing between the Ohmic (Au) and Schottky (Al) contacts are as indicated by the arrow.                                                                                                                                                                                                                     |

| Figure 4. 7: Current density-voltage characteristics of spin coated lateral PTAA Schottky diodes with                                                                                                                                                                                                                                                                                                                                                    |

| different gap sizes. Measurements are taken at a step voltage of 50 mV                                                                                                                                                                                                                                                                                                                                                                                   |

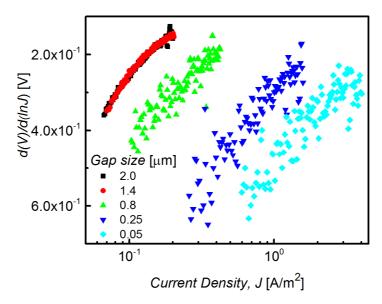

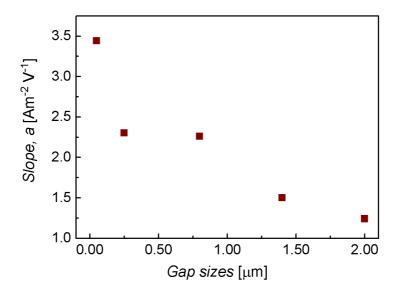

| Figure 4. 9: Quadratic variation of the slope a, with changes in gap sizes. The slope is calculated from current-voltage characteristics in the neutral region                                                                                                                                                                                                                                                                                           |

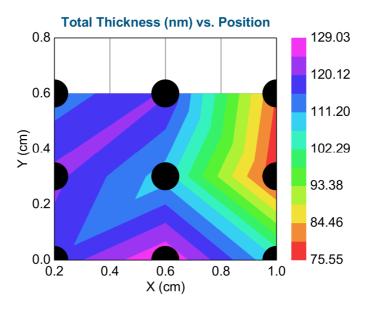

| Figure 4. 10: Ellipsometry characterisation of the variation of the film thickness of the PTAA polymer across a sample for a spin speed of 1000 rpm                                                                                                                                                                                                                                                                                                      |

| Figure 4. 11: Variation of the reverse current density against voltage, of the lateral PTAA diodes with different gap sizes                                                                                                                                                                                                                                                                                                                              |

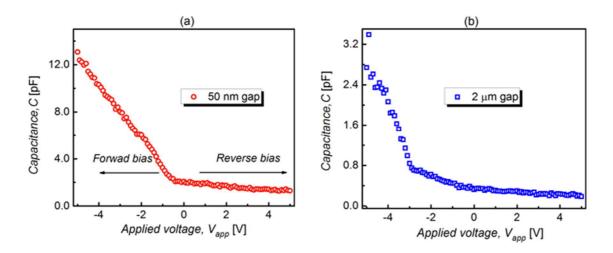

| Figure 4. 12: The capacitance voltage characteristics of two PTAA lateral Schottky diodes with a gap size of 50 nm (a) and 2 µm (b) respectively. The 100 Hz frequency of the small AC signal applied is held at 50 mV whilst the DC voltage is swept from -5 V to +5 V                                                                                                                                                                                  |

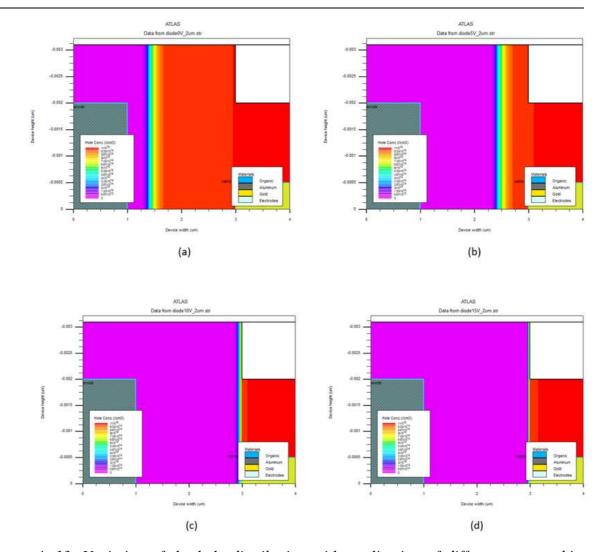

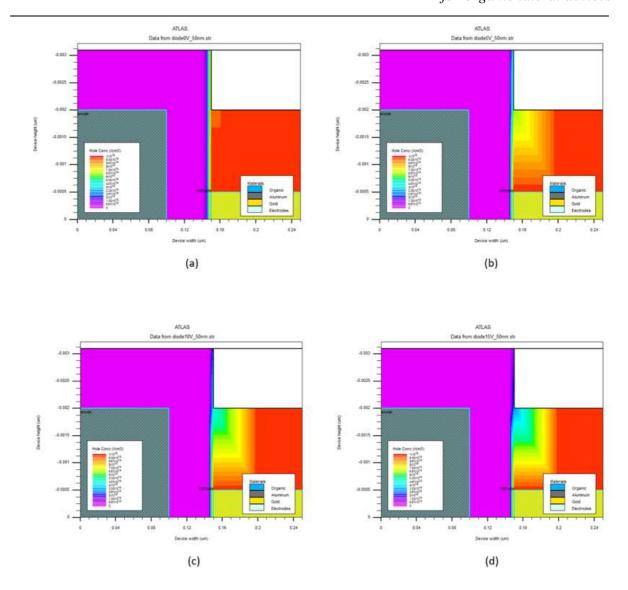

| Figure 4. 14: Variation of the hole distribution with application of different reverse bias voltages for the 0.05 µm lateral diode: (a) 0 V, (b) 5 V, (c) 10 V and (d) 15 V                                                                                                                                                                                                                                                                              |

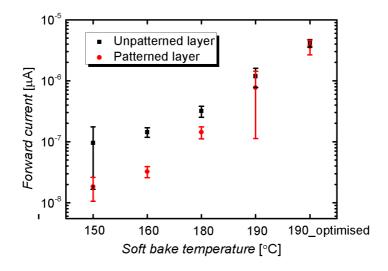

| Figure 4. 16: Variation of the forward currents of the lateral diodes, for both patterned and unpatterned samples, with varying gap sizes achieved by varying the soft bake temperature. The first four samples i.e. 150 °C, 160 °C, 180 °C and 190 °C are processed with the same soft bake time of 225 seconds whereas the 190_optimised sample denotes a sample processed with a soft bake temperature and time of 190 °C and 45 seconds respectively |

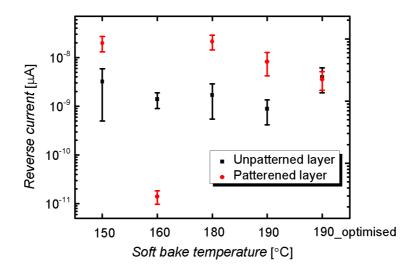

| patterned and unpatterned samples                                                                                                                                                                                                                                                                                                                                                                                                                        |

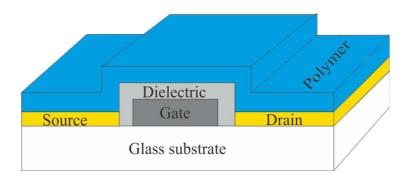

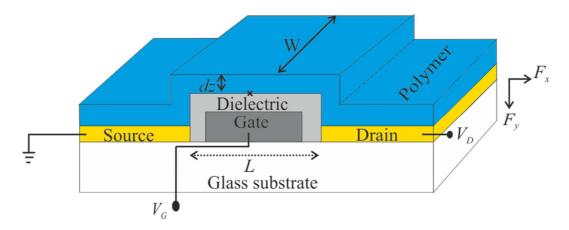

| drain contacts                                                                                                                                                                                                                                                                                                                                                                                                                                           |

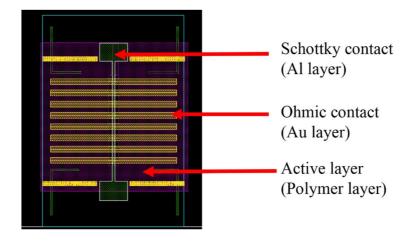

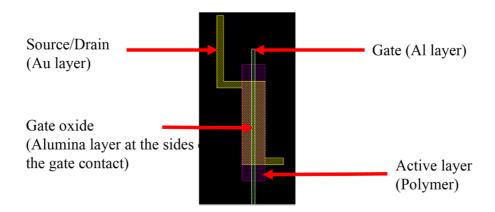

| Figure 4. 20: Sample layout of a SAG TFT fabricated in this work having a channel width and length of                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 500 μm and 20 μm respectively                                                                                                                                                                                                                                                                                                                                                    |

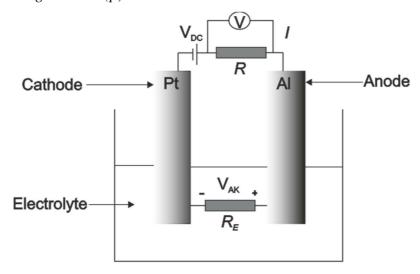

| Figure 4. 21: Setup for aqueous anodization of aluminium using a constant voltage method. The anode and cathode consists of the pre-patterned Aluminium layer and a platinum foil respectively, and the                                                                                                                                                                          |

| electrolyte is a 0.001 M citric acid solution                                                                                                                                                                                                                                                                                                                                    |

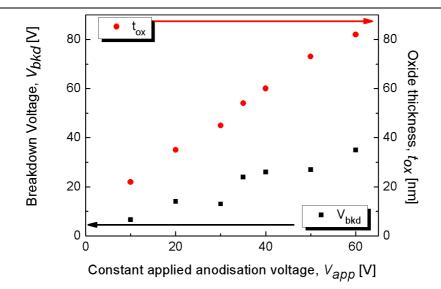

| Figure 4. 22: Variation of the oxide film thickness and breakdown voltage with the constant applied                                                                                                                                                                                                                                                                              |

| voltage. Adapted from [45]                                                                                                                                                                                                                                                                                                                                                       |

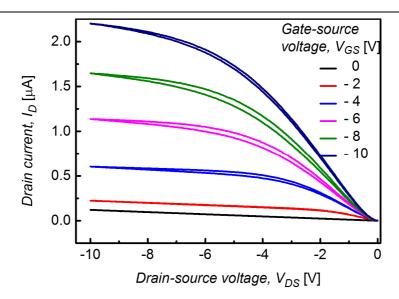

| Figure 4. 23: Output characteristics of the self-aligned PBTTT-C16 TFT. The thickness of the active layer and aluminium oxide is 65 nm and 50 nm respectively. The aspect ratio of the TFT is 50 (W/L=1000                                                                                                                                                                       |

| μm/20 μm)                                                                                                                                                                                                                                                                                                                                                                        |

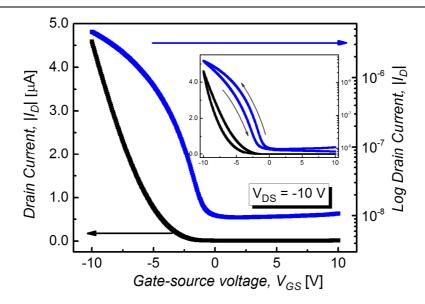

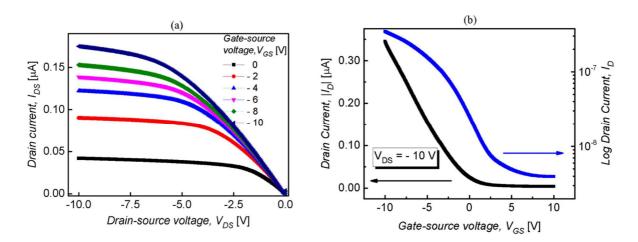

| Figure 4. 24: Linear and sub-threshold plots of spin-coated SAG PBTTT-C16 TFT swept from $V_{GS}$ of +10 V to -10 V at a $V_{DS}$ of -10 V. Inset: forward and reverse sweeps of the transfer characteristics. The thickness of the active layer and aluminium oxide dielectric is 65 nm and 50 nm respectively. The aspect ratio of the TFT is 50 (W/L=1000 $\mu$ m/20 $\mu$ m) |

| 120                                                                                                                                                                                                                                                                                                                                                                              |

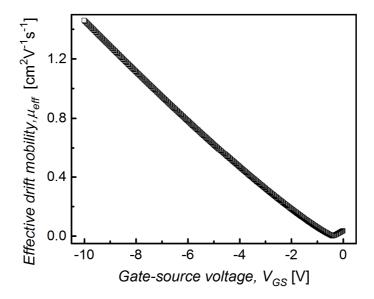

| Figure 4. 26: Variation of the effective mobility of the PBTTT-C16 SAG TFT, with changes in the applied gate voltage                                                                                                                                                                                                                                                             |

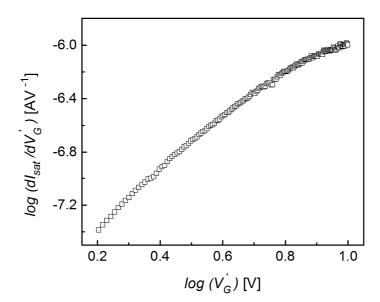

| Figure 4. 27: Transfer characteristics using the disordered equation (red dots), fitted to the experimental data (black squares) of PBTTT-C16 TFT of W/L=50, oxide thickness of 50 nm and applied drain voltage, $V_{DS} = -10 \text{ V}.$                                                                                                                                       |

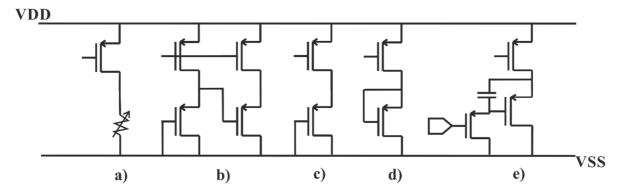

| Figure 5. 1: Different inverter topologies using only p-type transistors. From a) to e) the inverter configurations are a resistor load topology, a pseudo CMOS load topology, a saturated load topology, a zero- $V_{GS}$ topology and a bootstrapped topology respectively                                                                                                     |

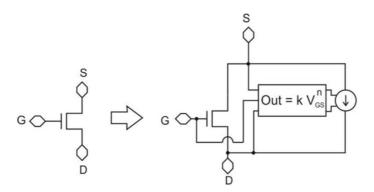

| Figure 5. 2: OTFT model consisting of a modified silicon p-type transistor. The new model consists of a                                                                                                                                                                                                                                                                          |

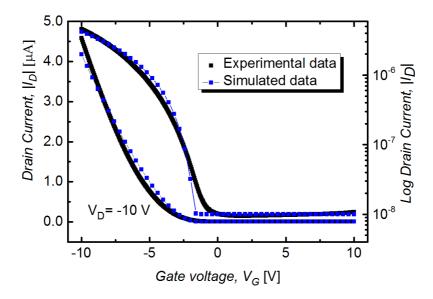

| VCCS that modifies the drain current expressions of the conventional transistor using a Verilog code. 132 Figure 5. 3: Linear and sub-threshold graphs of the measured and simulated SAG PBTTT-C16 TFT swept from $V_G$ of +10 V to -10 V at a $V_{DS}$ of -10 V. The thickness of the active layer and aluminium oxide                                                          |

| dielectric is 65 nm and 50 nm respectively. The aspect ratio of the TFT is 50 (W/L=1000 $\mu$ m/20 $\mu$ m) 134                                                                                                                                                                                                                                                                  |

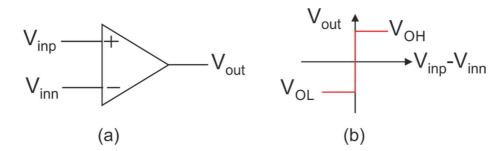

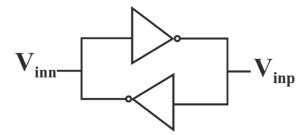

| Figure 5. 4: (a) Symbol of a comparator circuit and (b) the ideal transfer curve of a comparator 135 Figure 5. 5: Schematic of a latch consisting of two inverters connected back-to-back in a positive feedback topology                                                                                                                                                        |

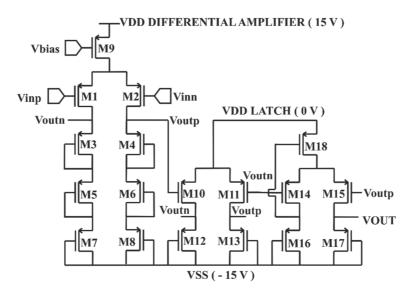

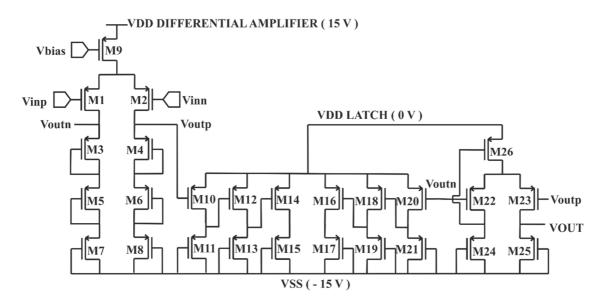

| Figure 5. 6: Schematic of the comparator design having a preamplifier consisting of a cascaded                                                                                                                                                                                                                                                                                   |

| differential amplifier, a latch stage consisting of a single set of cross-coupled saturated load inverters and                                                                                                                                                                                                                                                                   |

| a self-biased differential amplifier for the output stage                                                                                                                                                                                                                                                                                                                        |

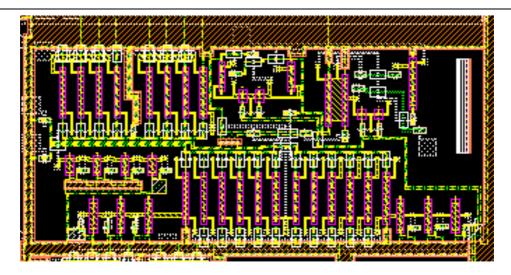

| Figure 5. 7: Layout of the schematic in Figure 5. 6 as designed in Cadence design software. Details of the Design Rule Check (DRC) layout rules and the mask containing the layout of the circuit can be found in                                                                                                                                                                |

| Appendix H and I respectively                                                                                                                                                                                                                                                                                                                                                    |

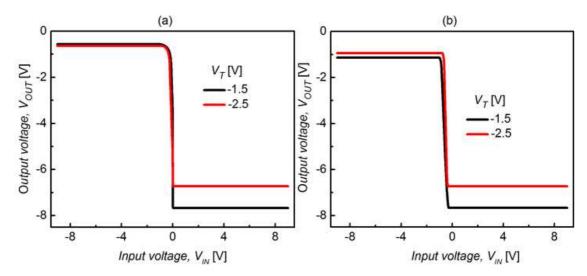

| Figure 5. 8: Transfer curves of the output voltage of the comparator connected to a (a) latch stage and (b) one without the latch stage connected. The positive terminal is swept from $-9~V$ to $+9~V$ while the negative                                                                                                                                                       |

| terminal is grounded                                                                                                                                                                                                                                                                                                                                                             |

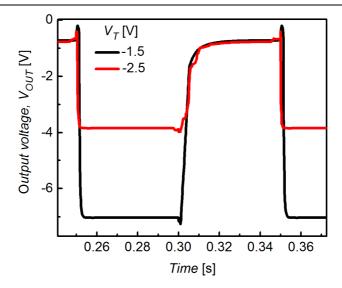

| Figure 5. 9: Transient response of the comparator with an input pulse of $\pm$ 1 V, period of 0.1 ms and rise/fall times of 0.01 ms. The input is applied to the input voltage (on the positive terminal) while the                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| negative terminal is grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 5. 10: Schematic design of the comparator circuit having two additional inverters at the latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <i>stage.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 5. 11: (a) Transfer curves of the output voltage of the comparator having two additional inverters at the latch stage. The positive terminal is swept from $-9 \text{ V}$ to $+9 \text{ V}$ while the negative terminal is                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| grounded. (b) Transient response of the same inverter. The input pulse has a magnitude of $\pm 1$ V, period of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1 s and rise/fall times of 1 ms. The input is applied to the input voltage (on the positive terminal) while the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| negative terminal is grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

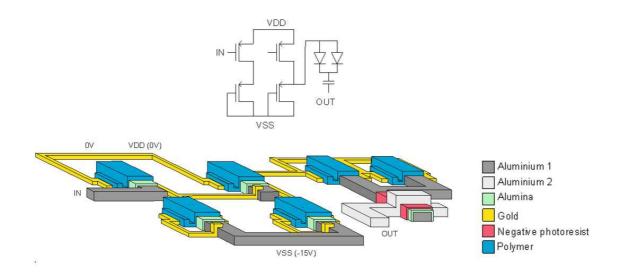

| Figure 5. 12: Structure of prospective circuit blocks and lateral devices processed on the same substrate,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| at the same time using the SAG fabrication process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 5. 13: Summary of the SAG fabrication process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

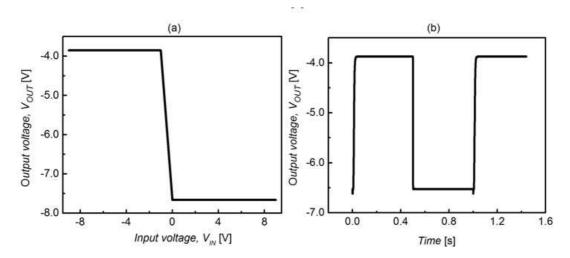

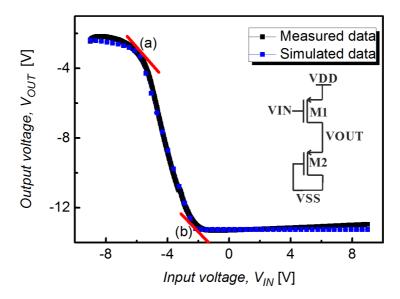

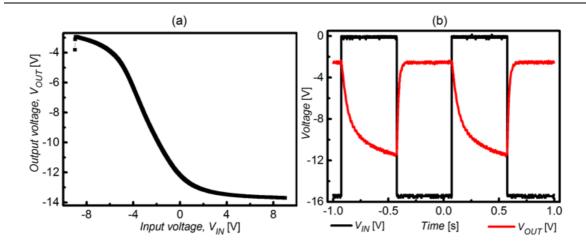

| Figure 5. 14: The measured and simulated Voltage Transfer Characteristics of a saturated load inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (inset) made using PBTTT-C16 polymer. The values of $V_{DD}$ and $V_{SS}$ are 0 and $-15$ V whereas the input voltage is swept from $-9$ V to $+9$ V. The channel length, $L=20$ $\mu$ m, is the same for all the transistors whereas the width of the driver ( $W_D$ ) and the width of the load ( $W_L$ ) are 500 $\mu$ m and 90 $\mu$ m respectively.                                                                                                                                                                                                                                                                                                                           |

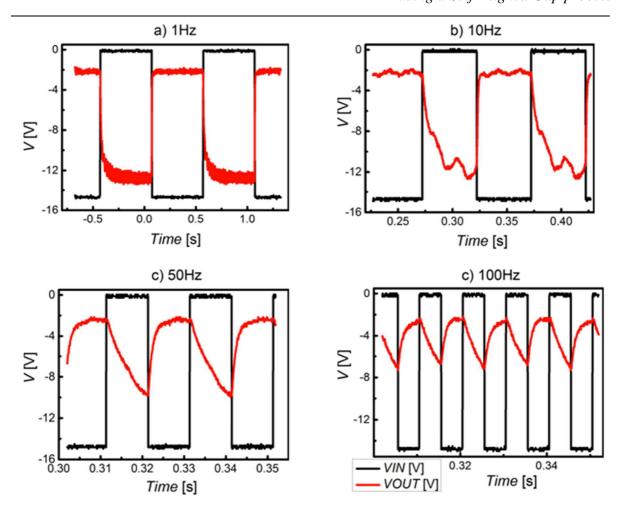

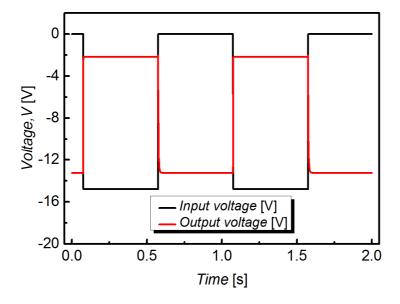

| Figure 5. 15: Transient response of a saturated load inverter with PBTTT-C16 polymer as the active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| layer. The frequency of the step pulse applied at the input terminal is varied from 1 Hz to 100 Hz as shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| in the figure from a) to d). The magnitude of the step pulse is 15 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

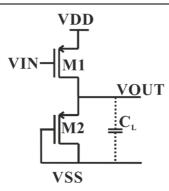

| Figure 5. 16: Structure of the saturated load inverter circuit used for the estimation of the load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 5. 17: The simulated transient response of a saturated load inverter. A 1 Hz step pulse with a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| magnitude of 15 V is applied at the input terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

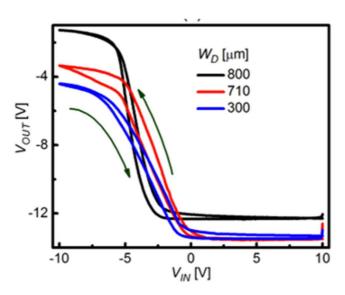

| Figure 5. 18: The VTC of a saturated load inverter with PBTTT-C16 polymer as the active layer. The value of the driver widths is 800 $\mu$ m, 710 $\mu$ m and 300 $\mu$ m whereas the width and length of the load and the driver transistors are kept constant at 90 $\mu$ m and 20 $\mu$ m respectively. The values of $V_{DD}$ and $V_{SS}$ are 0 and -15 V whereas the input voltage for the DC response is swept from -9 V to +9 V and vice versa 158 Figure 5. 19: Linear and sub-threshold plots of spin-coated SAG P3HT TFT swept from $V_{GS}$ of +10 V to -10 V at a $V_{DS}$ of -10 V. The thickness of the active layer and aluminium oxide dielectric is 70 nm and 50 |

| nm respectively. The aspect ratio of the TFT is 50 (W/L=1000 $\mu$ m/20 $\mu$ m)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5. 20: The VTC (a) and transient response (b) of a saturated load inverter with P3HT polymer as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| the active layer. The values of $V_{DD}$ and $V_{SS}$ are 0 and $-15$ V whereas the input voltage for the DC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| response is swept from –9 V to +9 V. For the transient response, the frequency of the step pulse applied at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| the input terminal is 1 Hz. The magnitude of the step pulse is 15 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

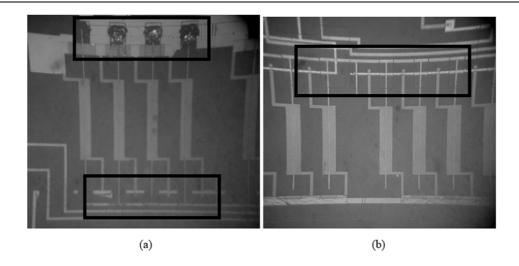

| Figure 5. 21: Section of a circuit block made using the SAG process with the gold layer peeling off during                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| the anodisation process due to lack of a gap between the gold and aluminium metal contacts 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 5. 22: Circuit section in the SAG process whereby part of the aluminium layer gets etched away by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| gold etchant when forming the source and drain contacts which are made from gold metal layer 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5. 23: (a) Part of the SU8 negative resist peeling off from a circuit block when dissolved in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| remover solution because of insufficient curing of the SU8 resist during processing. (b) A sample circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| nock with 508 resist tayer remaining intact after being exposed to remover solution; the tayer is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

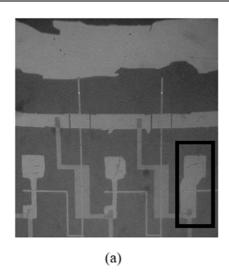

| in elevated temperature and time of 210 $^{\circ}$ C and 30 min respectively<br>Figure 5. 24: (a) A circuit section made using the SAG process where parts of the unwanted alumning the section of the contract of the life of the contract of | iinium |

| ayer remain on the substrate after lift-off. (b) A different circuit showing better aluminium lift off<br>of cleaning the substrate using UV ozone prior to aluminium deposition to remove unwanted cont                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| on the surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |