# Growth, Dielectric Properties, and Reliability of High-k Thin Films Grown on Si and Ge Substrates

A Thesis Submitted to

University of Liverpool

in Partial Fulfillment of the Requirements for

the Degree of Doctor of Philosophy

in the Department of Electrical Engineering and Electronics

by

Qifeng Lu

June 2017

BEng Electrical and Electronic Engineering

Xi'an Jiaotong-Liverpool University

& University of Liverpool, 2013

### **Abstract**

With the continuous physical size down scaling of Metal Oxide Semiconductor Field Effect Transistors (MOSFETs), silicon (Si) based MOS devices have reached their limits. To further decrease the minimum feature size of devices, high-k materials (with dielectric constants larger than that of silicon dioxide (SiO<sub>2</sub>), 3.9) have been employed to replace the SiO<sub>2</sub> gate dielectric. However, there are higher densities of traps in high-k dielectrics than in the near trap free SiO<sub>2</sub>. Therefore, it is important to comprehensively investigate the defects and electron trapping/de-trapping properties of the oxides. Also, germanium (Ge) has emerged as a promising channel material to be used in high-speed metal-oxide-semiconductor (MOS) devices, mainly due to its high carrier mobility compared with that of silicon. However, due to the poor interface quality between the Ge substrate and gate dielectrics, it is difficult to fabricate high-performance germanium based devices. Therefore, an effective passivation method for the germanium substrate is a critical issue to be addressed to allow the fabrication of high quality Ge MOSFETs.

To solve the above problems, the study of high-k materials and the passivation of germanium substrates was carried out in this research. In the first part of this work, lanthanide zirconium oxides (LaZrO<sub>x</sub>) were deposited on Si substrates using atomic layer deposition (ALD). The pulse capacitance-voltage (CV) technique, which can allow the completion of the CV sweep in several hundreds of microseconds, was employed to investigate oxide traps in the LaZrO<sub>x</sub>. The results indicate that: (1) more

traps are observed in the LaZrO<sub>x</sub> when compared with measurements using the conventional CV characterization method; (2) the time-dependent trapping/de-trapping is influenced by edge times, pulse widths and peak to peak voltages ( $V_{PP}$ ) of the gate voltage pulses applied. Also, an anomalous behavior in the pulse CV curves, in which the relative positions of the forward and reverse CV traces are opposite to those obtained from the conventional measurements, was observed. A model relating to interface dipoles formed at the high- $k/SiO_x$  is proposed to explain this behavior. Formation of interface dipoles is caused by the oxygen atom density difference between the high-k materials and native oxides. In addition, a hump appears in the forward pulse CV traces. This is explained by the current displacement due to the pn junction formed between the substrate and inversion layer during the pulse CV measurement.

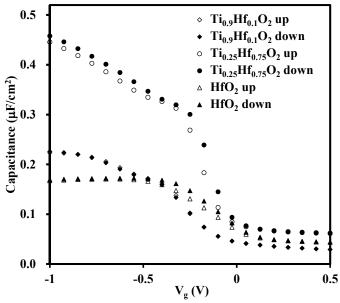

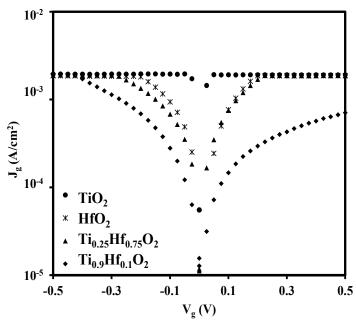

Secondly, hafnium titanate oxides (Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub>) with different concentrations of titanium oxide were deposited on p-type germanium substrates by ALD. X-ray Photoelectron Spectroscopy (XPS) was used to analyze the interface quality and chemical structure. The current-voltage (IV) and capacitance-voltage (CV) characteristics were measured using an Aglient B1500A semiconductor analyzer. The results indicate that GeO<sub>x</sub> and germinate are formed at the high-*k*/Ge interface and the interface quality deteriorates severely. Also, an increased leakage current is obtained when the HfO<sub>2</sub> content in the Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> is increased. A relatively large leakage current density (~10<sup>-3</sup> A/cm<sup>2</sup>) is partially attributed to the deterioration of the interface between Ge and Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> caused by the oxidation source from HfO<sub>2</sub>. The small band gap of

the TiO<sub>2</sub> also contributes to the observed leakage current. The CV characteristics show almost no hysteresis between the forward and reverse CV traces, which indicates low trap density in the oxide. Since deterioration of the interface quality was observed, an in-situ ZnO interfacial layer was deposited in the ALD system to passivate the germanium substrate. However, a larger distortion of the as-deposited sample was observed. Although the post deposition annealing (PDA) has a positive effect on the CV curves, there is an increase in frequency dispersion and the leakage current after PDA. Therefore, the ZnO interfacial layer is not an effective passivation layer for the germanium substrate. In addition, GeO is formed due to the reaction and GeO desorption from the gate oxide/Ge interface occurs, which also leads to the deterioration of the device performance.

In the final part of this work, to circumvent the problems explored above, 0.1 mol/L propanethiol solution in 2-propanol, 0.1 mol/L octanethiol solution in 2-propanol, and 20% (NH<sub>4</sub>)<sub>2</sub>S solution in DI water were used to passivate the n-type germanium substrates before HfO<sub>2</sub> dielectric thin films were deposited by ALD. The results show that an increase in the dielectric constant and a reduction in leakage current are obtained for the samples with chemical treatments. The sample passivated by octanethiol solution has the largest dielectric constant. The lowest leakage current density is observed for the sample passivated by (NH<sub>4</sub>)<sub>2</sub>S solution followed by the one passivated by octanethiol solution. In addition, effects of a TiN cap layer on the formation and suppression of GeO were investigated. It was found that the formation of GeO and

desorption of the GeO form gate oxides/Ge interface are suppressed by the cap layer. As a result, an increase in dielectric constant from 8.2 to 13.5 and a lower leakage current density for a negatively applied voltage are obtained. Therefore, the passivation of the substrates by octanethiol or (NH<sub>4</sub>)<sub>2</sub>S solutions followed by the TiN cap layer is a useful technique for Ge based devices.

### Acknowledgments

After years of Ph.D. study, it is the moment to finalize this chapter of my life. It is also the time to express my sincere gratitude to those who have helped me throughout this graduate research period. Without their kindly help and patient instruction, the study presented here would not have been possible.

First and foremost, I would like to offer my profound thanks to my supervisor, Prof. Ce Zhou Zhao, for providing the Ph.D. study chance and supporting my idea of carrying out a Ph.D. His research methodology and valuable guidance are extremely important for the research works. Besides the suggestions and supervision on my academic research, his attitude towards living and learning also influences me. It is a great pleasure working with him.

Also, I wish to express my sincere appreciation to my supervisors, Prof. Steve Taylor and Prof. Paul Chalker. They have encouraged me to expand my knowledge and helped my with my English express skills. They have offered help and support by all means.

Again, I would like to thank them for their patient guidance and encouragement.

I also deeply appreciate Dr. Sang Lam, Prof. Moncef Tayahi, Dr. Ivona Mitrovic, Dr. Li Yang, and Prof. Eng Gee Lim, They have provided their treasure advice and support on my academic research and life. This is one of the essential reasons for the successful completion of the research project here.

In addition, many thanks to my comrades: Dr. Chun Zhao, Dr. JingJin Wu, Mr. Yifei

Mu, Mr. Chenguang Lu, Ms. Yinchao Zhao, Mr. Yutao Cai, and Mr. Yuxiao Fang. Their assistance and encouragement filled my life with happiness during these years. I would like to express my best wishes to them and hope everything goes well with their future study and work.

Finally, special thanks to my family for their love, patience and support. They deserve the highest praise. Also, I owe my heartiest gratitude to my fiancée, who accompanies and encourages me. My heartiest appreciation goes to her for the infinite love that always keeps me moving forwards.

It would be difficult for me to adequately thank all those who have helped me during my Ph.D. study. However, I would like to express my sincere gratitude and best wishes to everyone involved.

Qifeng Lu

June 2017

## **Contents**

| Abs  | tract                                                               |                                                                        | ii    |

|------|---------------------------------------------------------------------|------------------------------------------------------------------------|-------|

| Ack  | now]                                                                | ledgments                                                              | vi    |

| Con  | tents                                                               |                                                                        | viii  |

| List | of F                                                                | igures                                                                 | X     |

| List | of Ta                                                               | ables                                                                  | xvii  |

| List | of S                                                                | ymbols                                                                 | xviii |

| List | of A                                                                | bbreviations and Acronyms                                              | XX    |

| 1.   | Cha                                                                 | pter 1: Introduction and Background Information                        | 1     |

|      | 1.1                                                                 | Research Background                                                    | 1     |

|      | 1.2                                                                 | Outline of Work                                                        |       |

|      | 1.3                                                                 | Aims and Objectives                                                    | 13    |

|      | 1.4                                                                 | Original Contribution                                                  | 14    |

|      | 1.5                                                                 | Published works                                                        | 15    |

|      | 1.6                                                                 | Chapter Outline                                                        | 19    |

|      | 1.7                                                                 | References                                                             | 21    |

| 2.   | Chapter 2: Methodology and Experimental Processes                   |                                                                        |       |

|      | 2.1                                                                 | Background Theory and Sample Preparation                               | 38    |

|      | 2.2                                                                 | Physical Characterization                                              |       |

|      | 2.3                                                                 | Electrical Characterization                                            | 48    |

|      | 2.4                                                                 | Basic Terms and Definitions                                            | 51    |

|      | 2.5                                                                 | Summary                                                                | 54    |

|      | 2.6                                                                 | Reference                                                              | 55    |

| 3.   | Chapter 3: Characterization of High-k Oxides on Silicon Substrates5 |                                                                        |       |

|      | 3.1                                                                 | Application of Pulse CV Technique                                      | 58    |

|      | 3.2                                                                 | Characterization of MOS Capacitors with LaZrO <sub>x</sub> dielectrics | 58    |

|      | 3.3                                                                 | Anomalous Hysteresis in Capacitance-Voltage Traces                     | 67    |

|      | 3.4                                                                 | Summary                                                                | 81    |

|      | 3.5                                                                 | References                                                             | 83    |

| 4    | Cha                                                                 | nter 4. Investigation of TivHft vO2 denosited on Germanium substrates  | 87    |

|     | 4.1                                                                  | Investigation of Ti <sub>x</sub> Hf <sub>1-x</sub> O <sub>2</sub> on Germanium Substrates   | 87     |

|-----|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------|

|     | 4.2                                                                  | Effect of PDA on Ti <sub>x</sub> Hf <sub>1-x</sub> O <sub>2</sub> Dielectric MOS Capacitors | 98     |

|     | 4.3                                                                  | Summary                                                                                     | 104    |

|     | 4.4                                                                  | References                                                                                  |        |

| 5.  | Chapter 5: Passivation of the Ge MOS devices with high-k dielectrics |                                                                                             |        |

|     | 5.1                                                                  | Deposition of High-k Dielectrics on Ge Wafers with Chemical Trea                            | tments |

|     |                                                                      | 112                                                                                         |        |

|     | 5.2                                                                  | Effect of TiN Cap Layer on the Performance of Ge MOS capacitors                             | 126    |

|     | 5.3                                                                  | Summary                                                                                     | 132    |

|     | 5.4                                                                  | References                                                                                  | 134    |

| 6.  | Cha                                                                  | pter 6: Conclusions and Future Works                                                        | 142    |

|     | 6.1                                                                  | Conclusions                                                                                 | 142    |

|     | 6.2 I                                                                | 6.2 Future Work                                                                             |        |

| Apj | pendix                                                               | Κ                                                                                           | 149    |

|     |                                                                      |                                                                                             |        |

# **List of Figures**

| Figure 1.1 The structure of a MOSFET                                                    |

|-----------------------------------------------------------------------------------------|

| Figure 1.2 The structure of MOS capacitor                                               |

| Figure 2.1 Schematic representation of reaction sequence in ALD deposition [2]40        |

| Figure 2.2 Conventional CV measurement system of MOS capacitors using Agilent           |

| 4284A LCR Meter                                                                         |

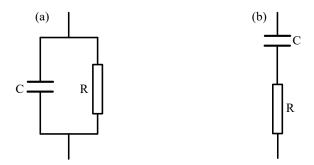

| Figure 2.3 Schematic representation for (a) parallel and (b) series model49             |

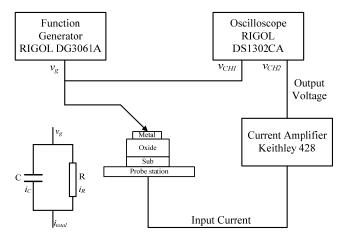

| Figure 2.4 The Pulse CV Measurement System Structure Chart [4]50                        |

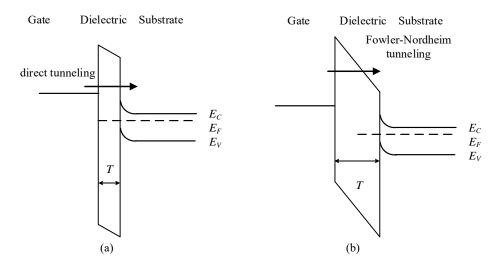

| Figure 2.5 Energy band diagrams of direction tunneling and Fowler-Nordheim              |

| tunneling51                                                                             |

| Figure 2.6 Typical CV characteristics of a MOS capacitor                                |

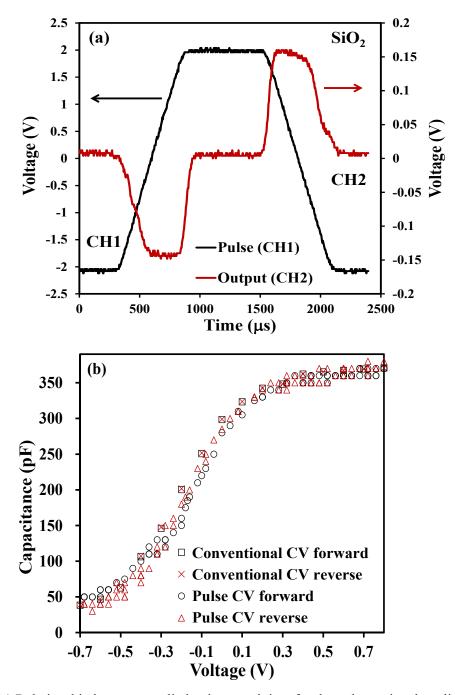

| Figure 3.1 (a) Relationship between applied voltage and time for the voltage signal     |

| applied to the MOS capacitor and output voltage of the amplifier; (b) Relationship      |

| between capacitance and voltage calculated using Formula (2.5) for the SiO <sub>2</sub> |

| MOS sample59                                                                            |

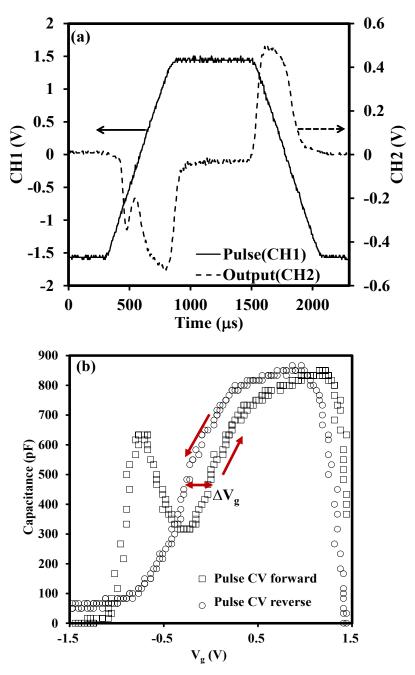

| Figure 3.2 (a) Relationship between applied voltage and time for the voltage signal     |

| applied to the MOS capacitor (CH1) and output voltage of the amplifier (CH2);           |

| (b) Relationship between capacitance and voltage calculated using Formula (2.5)         |

| for the MOS capacitor with LaZrO <sub>x</sub> dielectric60                              |

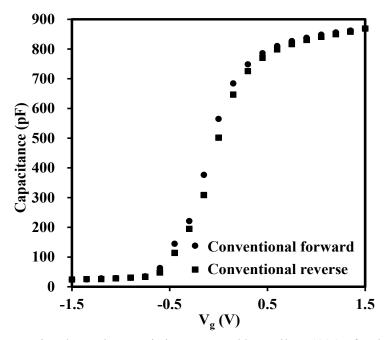

| Figure 3.3 Conventional CV characteristics measured by Agilent 4284A for the sample     |

| with the thickness of about 22 nm 62                                                    |

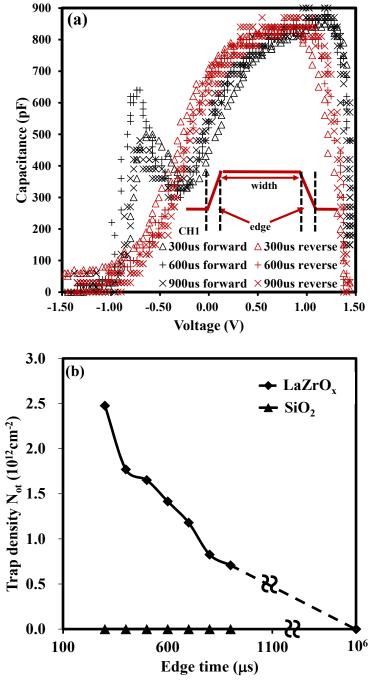

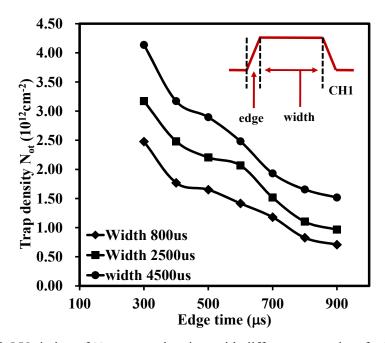

| Figure 3.4 (a) Capacitance versus gate voltage with various edge time for LaZrO <sub>x</sub> ; (b)                 |

|--------------------------------------------------------------------------------------------------------------------|

| Variation of Not versus edge time for LaZrO <sub>x</sub> and SiO <sub>2</sub> 64                                   |

| Figure 3.5 Variation of Not versus edge time with different stress time for LaZrOx66                               |

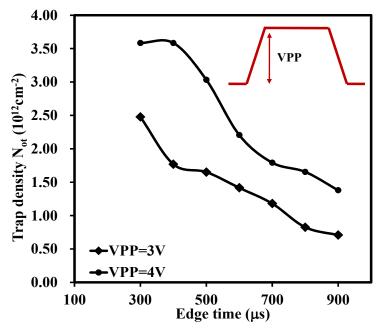

| Figure 3.6 Relationship between $N_{ot}$ and edge time with various $V_{PP}$ for $LaZrO_x$                         |

| dielectric MOS capacitors                                                                                          |

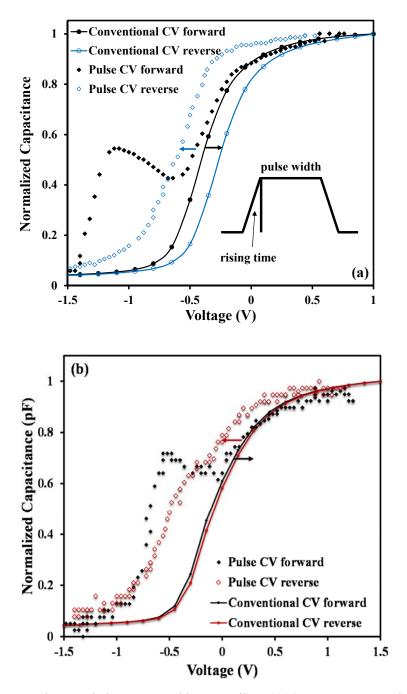

| Figure 3.7 CV characteristics measured by an Agilent 4284A LCR meter and a pulse                                   |

| CV system for (a) ZrO <sub>2</sub> and (b) HfO <sub>2</sub> dielectric MOS capacitors69                            |

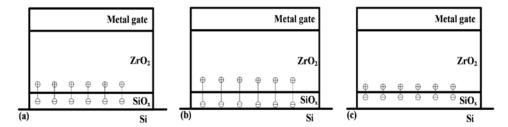

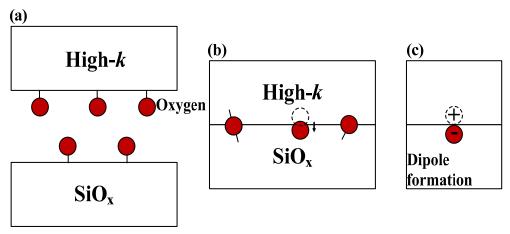

| Figure 3.8 The separation of interface dipoles for the as-deposited sample (a) during                              |

| conventional measurement, under pulse voltage sweep (b) from negative to                                           |

| positive and (c) from positive to negative [15]70                                                                  |

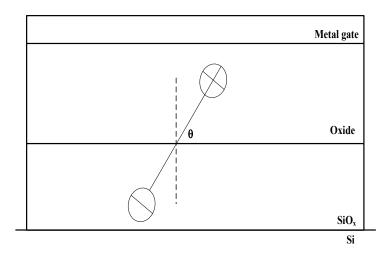

| Figure 3.9 The separation of interface dipoles with an angle between the dipole and                                |

| interface72                                                                                                        |

| Figure 3.10 The formation process of interface dipoles [15]72                                                      |

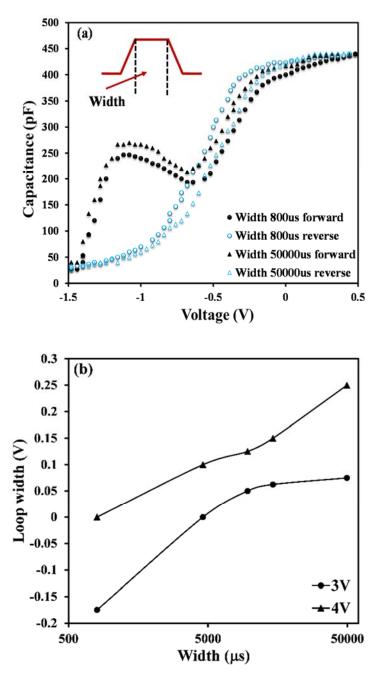

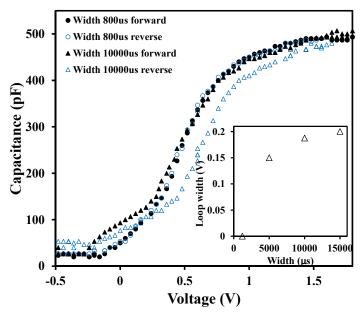

| Figure 3.11 (a) Two selected CV characteristics of the 200 °C as-deposited sample with                             |

| ZrO <sub>2</sub> dielectrics with different stress time. (b) The relationship between loop                         |

| width and pulse width under different V <sub>PP</sub> (3 V and 4 V). The pulse CV technique                        |

| was performed with various pulse width time at a constant rising edge of 400 $\mu$ s.                              |

| 74                                                                                                                 |

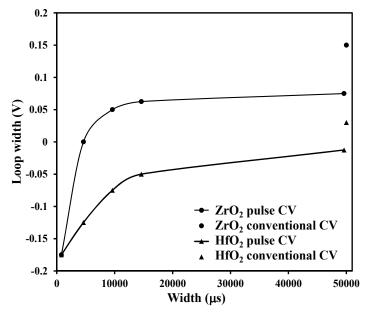

| Figure 3.12 The relationships between loop width and pulse width for the samples with                              |

| ZrO <sub>2</sub> and HfO <sub>2</sub> dielectrics under the V <sub>PP</sub> of 3 V and 4 V, respectively. The loop |

| width extracted from conventional CV is also presented for comparison75                                            |

| Figure 3.13 Pulse CV characteristics of the samples with ZrO <sub>2</sub> dielectric layers                                          |

|--------------------------------------------------------------------------------------------------------------------------------------|

| annealed in FG. The inset shows that the loop width increases with pulse width.                                                      |

| The pulse technique was performed with various pulse time with at a constant                                                         |

| rise time of 400 μs and V <sub>PP</sub> of 3 V77                                                                                     |

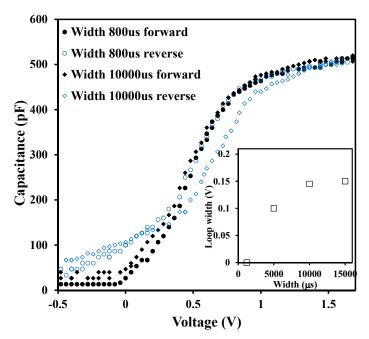

| Figure 3.14 Pulse CV characteristics of the samples with ZrO <sub>2</sub> dielectric layers                                          |

| annealed in nitrogen. The relationship between pulse width and loop width is                                                         |

| illustrated in the inset. The pulse CV technique was performed with various pulse                                                    |

| width time at a constant rise time of 400 µs and VPP of 3 V77                                                                        |

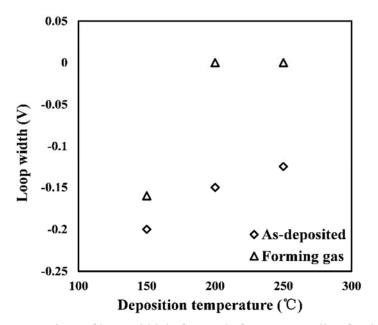

| Figure 3.15 The comparison of loop width before and after FG annealing for the                                                       |

| samples with ZrO <sub>2</sub> dielectric layer at various deposition temperatures78                                                  |

| Figure 3.16 The behavior of forward pulse CV trace with different rising time for HfO <sub>2</sub>                                   |

| dielectric sample. An applied voltage from -2 V to 1.5 V was used. (b) The model                                                     |

| for the pn junction formed between the p-type inversion layer and n-type substrate                                                   |

| 81                                                                                                                                   |

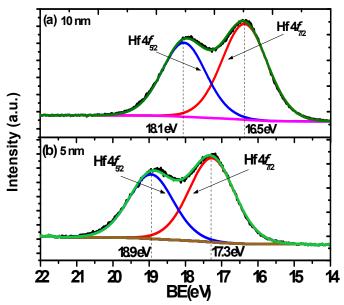

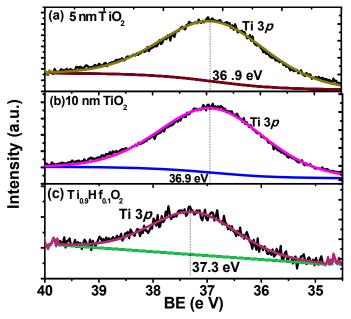

| Figure 4.1. The XPS line shape for HfO <sub>2</sub> thin films with a thickness of (a) 10 nm and                                     |

| (b) 5 nm89                                                                                                                           |

| Figure 4.2. The Ti 3p spectra from (a) 5 nm TiO <sub>2</sub> , (b) 10 nm TiO <sub>2</sub> , and (c) 5 nm                             |

| Ti <sub>0.9</sub> Hf <sub>0.1</sub> O <sub>2</sub> thin films89                                                                      |

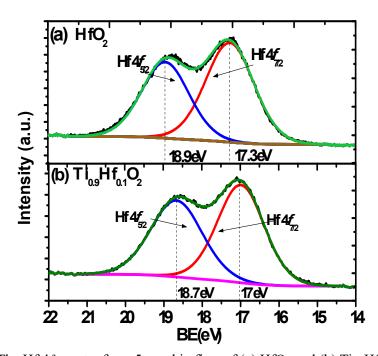

| Figure 4.3. The Hf 4f spectra from 5 nm thin fims of (a) HfO2 and (b) Ti <sub>0.9</sub> Hf <sub>0.1</sub> O <sub>2</sub> on          |

| Ge90                                                                                                                                 |

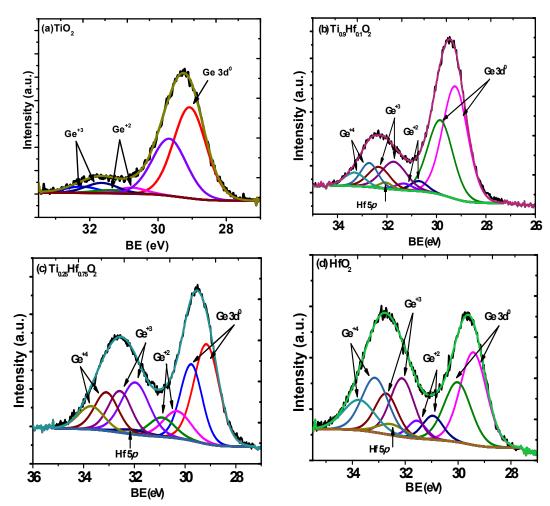

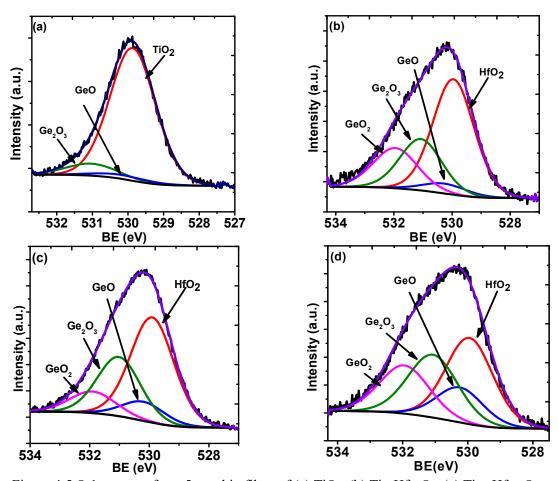

| Figure 4.4 Ge 3d spectra from 5 nm thin films of (a) TiO <sub>2</sub> , (b) Ti <sub>0.9</sub> Hf <sub>0.1</sub> O <sub>2</sub> , (c) |

| Ti <sub>0.25</sub> Hf <sub>0.75</sub> O <sub>2</sub> , and (d) HfO <sub>2</sub> samples92                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.5 O 1s spectra from 5 nm thin films of (a) TiO2, (b) Ti0.9Hf0.1O2, (c)                                                                                                                |

| Ti <sub>0.25</sub> Hf <sub>0.75</sub> O <sub>2</sub> , and (d) HfO <sub>2</sub> 93                                                                                                             |

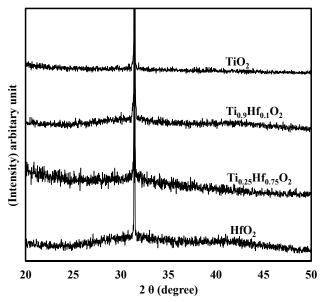

| Figure 4.6 XRD patterns for the 10 nm HfO <sub>2</sub> , Ti <sub>0.25</sub> Hf <sub>0.75</sub> O <sub>2</sub> , Ti <sub>0.9</sub> Hf <sub>0.1</sub> O <sub>2</sub> , and TiO <sub>2</sub> thin |

| films deposited on the germanium substrate94                                                                                                                                                   |

| Figure 4.7. CV characteristics of the samples with Ti <sub>0.9</sub> Hf <sub>0.1</sub> O <sub>2</sub> , Ti <sub>0.25</sub> Hf <sub>0.75</sub> O <sub>2</sub> , and HfO <sub>2</sub>            |

| dielectrics95                                                                                                                                                                                  |

| Figure 4.8. Gate leakage current density (Jg) versus gate voltage (Vg) for the samples                                                                                                         |

| with HfO <sub>2</sub> , Ti <sub>0.25</sub> Hf <sub>0.75</sub> O <sub>2</sub> , Ti <sub>0.9</sub> Hf <sub>0.1</sub> O <sub>2</sub> , and TiO <sub>2</sub> dielectrics97                         |

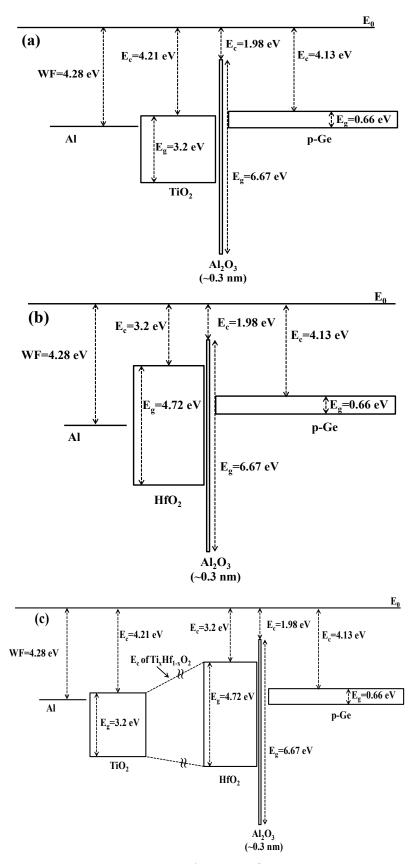

| Figure 4.9. Energy band diagrams for (a) TiO <sub>2</sub> , (b) HfO <sub>2</sub> , and (c) titanium doped                                                                                      |

| hafnium oxide99                                                                                                                                                                                |

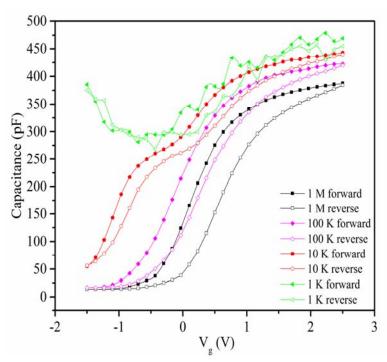

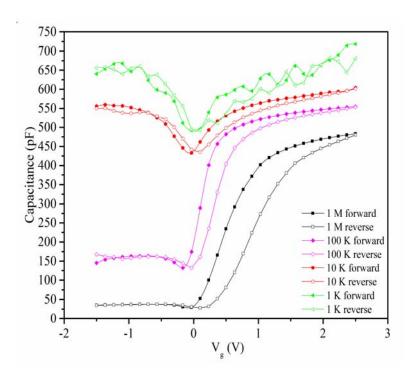

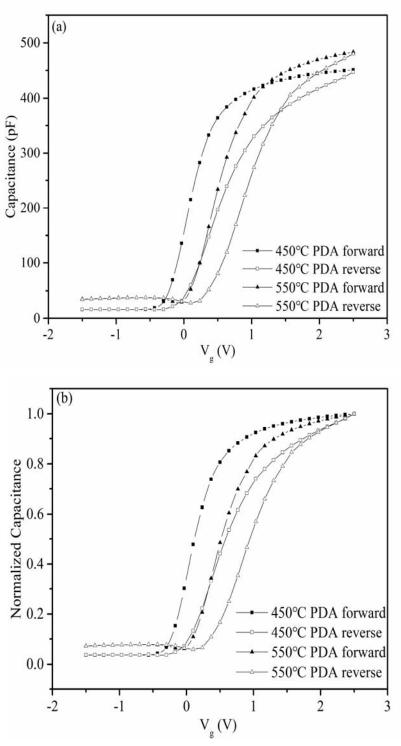

| Figure 4.10 CV characteristics of the Ti <sub>0.1</sub> Hf <sub>0.9</sub> O <sub>2</sub> dielectric MOS capacitor after 450 °C                                                                 |

| PDA for 30 seconds                                                                                                                                                                             |

| Figure 4.11 CV characteristics of the Ti <sub>0.1</sub> Hf <sub>0.9</sub> O <sub>2</sub> dielectric MOS capacitors after                                                                       |

| 550 °C PDA for 30 seconds                                                                                                                                                                      |

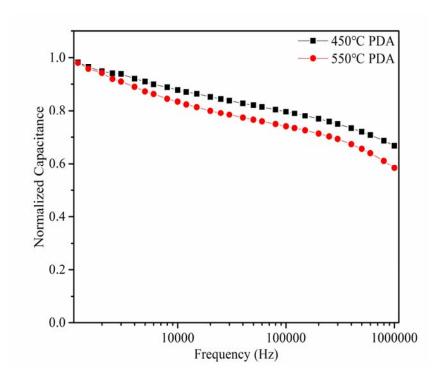

| Figure 4.12 Capacitance versus frequency for the 450 °C PDA and 550 °C PDA                                                                                                                     |

| samples                                                                                                                                                                                        |

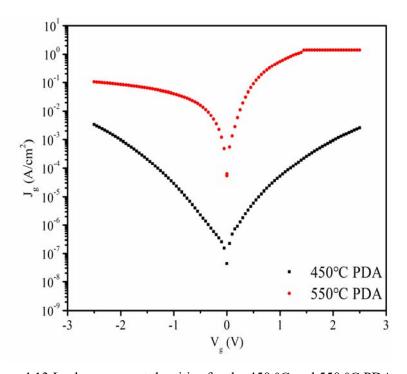

| Figure 4.13 Leakage current densities for the 450 °C and 550 °C PDA samples102                                                                                                                 |

| Figure 4.14 (a) Comparison of the CV characteristics extracted from the 450 °C PDA                                                                                                             |

| and 550 °C PDA sample and (b) The corresponding normalized CV                                                                                                                                  |

| characteristics 103                                                                                                                                                                            |

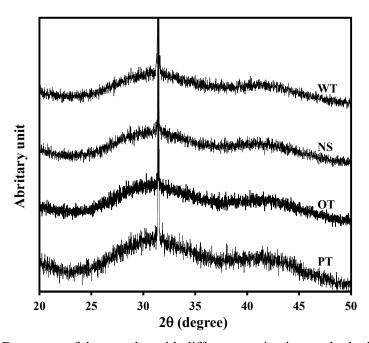

| Figure 5.1. XRD patterns of the samples with different passivation methods showing               |

|--------------------------------------------------------------------------------------------------|

| only the diffraction peak for the Ge substrate at 31.5°                                          |

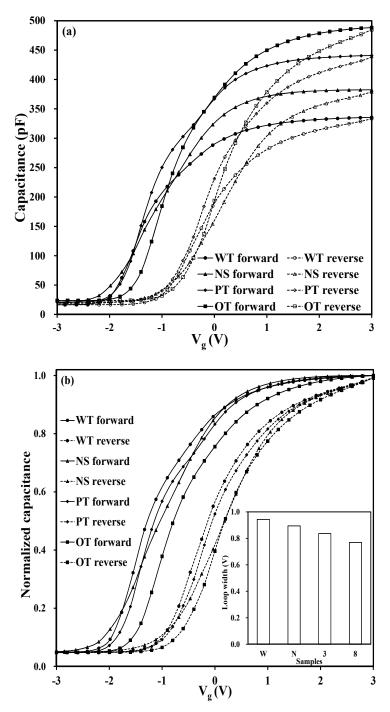

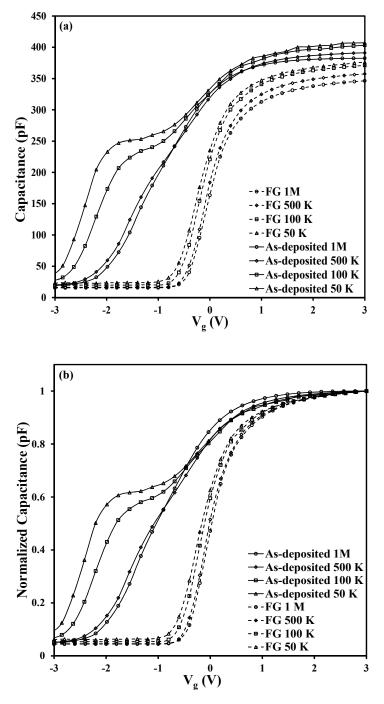

| Figure 5.2 (a) The CV characteristics and (b) corresponding normalized CV                        |

| characteristics extracted from the four samples                                                  |

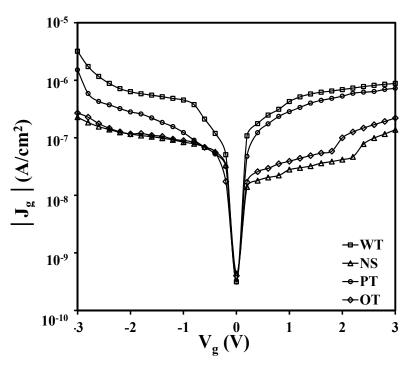

| Figure 5.3 Gate leakage current density $(J_g)$ versus gate voltage $(V_g)$ of the four samples  |

| 116                                                                                              |

| Figure 5.4 (a) The CV characteristics and (b) normalized ones of the sample with                 |

| (NH <sub>4</sub> ) <sub>2</sub> S pretreatment before and after FG annealing118                  |

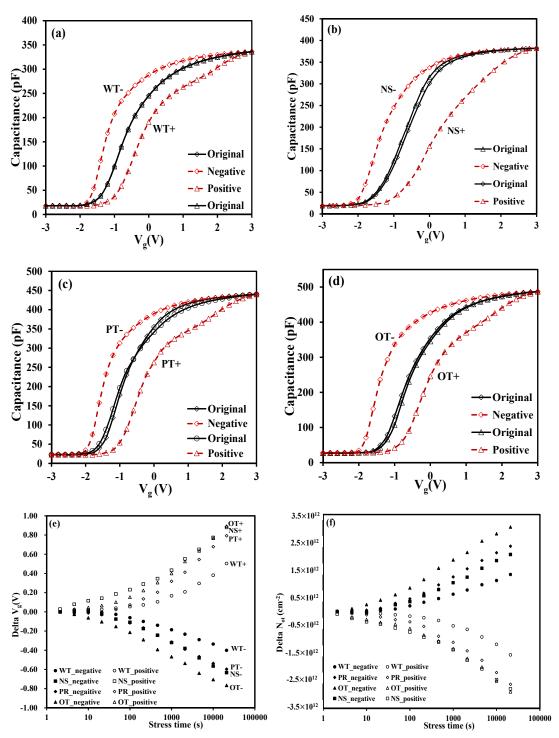

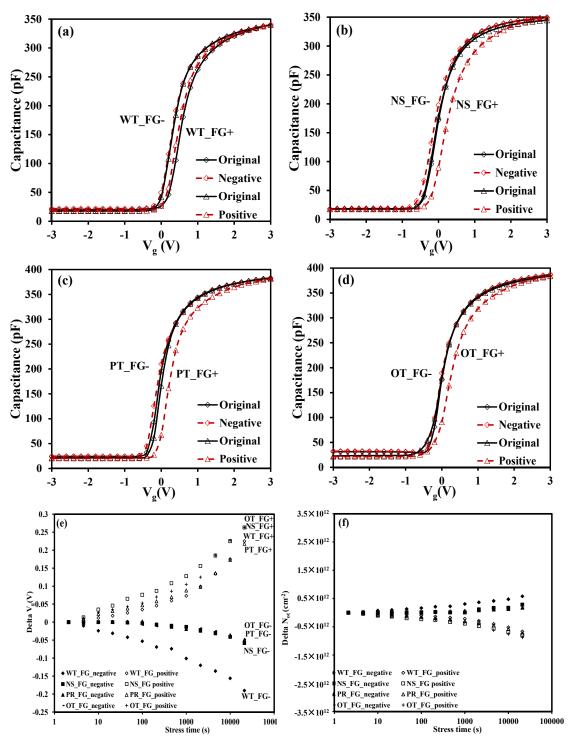

| Figure 5.5. The forward CV curves under positive and negative stress of                          |

| 21,000 seconds for as-deposited (a) WT (b) NS, (c) PT and (d) OT samples. The                    |

| variation of gate voltage shift and the corresponding variation of $N_{ot}$ for the              |

| samples with stress time are illustrated in (e) and (f), respectively120                         |

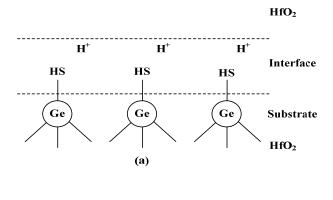

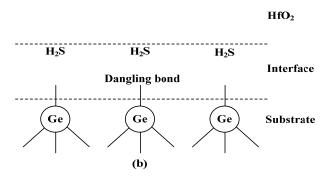

| Figure 5.6 Schematic diagram of the depassivation process: (a) The protons (H <sup>+</sup> ions) |

| move to the interface under the electric field; (b) the H <sup>+</sup> ions react with the -HS   |

| groups to form H <sub>2</sub> S121                                                               |

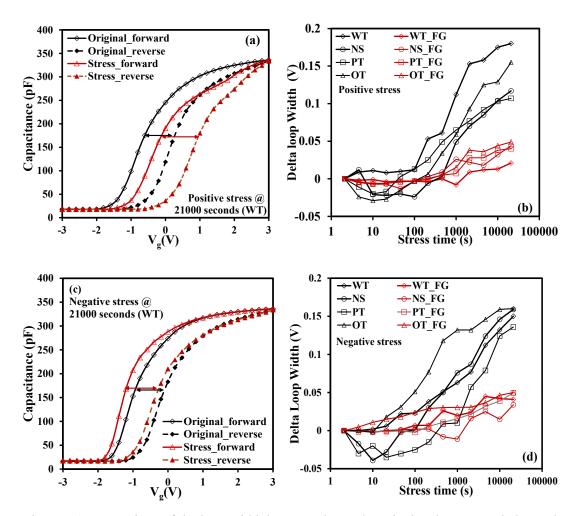

| Figure 5.7 Forward CV curves under positive and negative stress of 21,000 seconds for            |

| (a) WT_FG, (b) NS_FG, (c) PT_FG and (d) OT_FG samples, which underwent                           |

| FG annealing. The gate voltage shift and corresponding change of $N_{ot}$ for the                |

| samples with stress time are given in (e) and (f), respectively122                               |

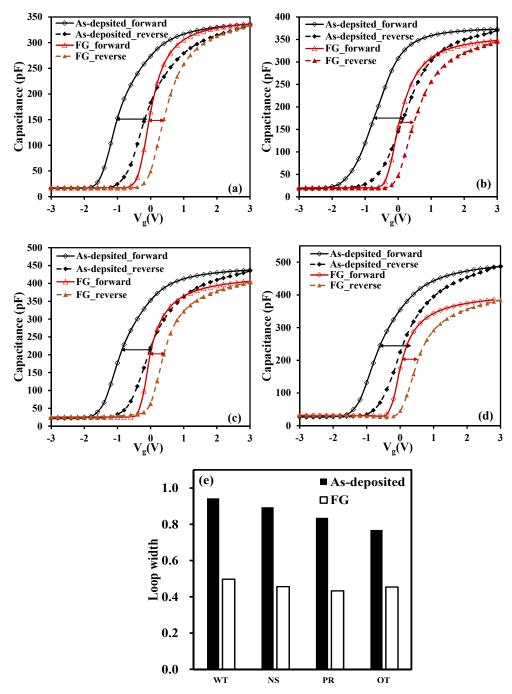

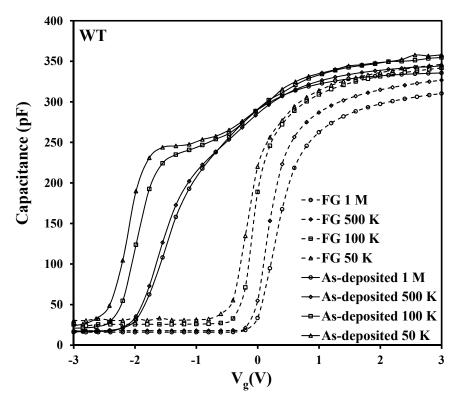

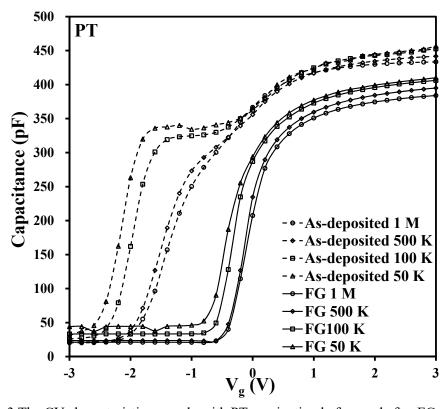

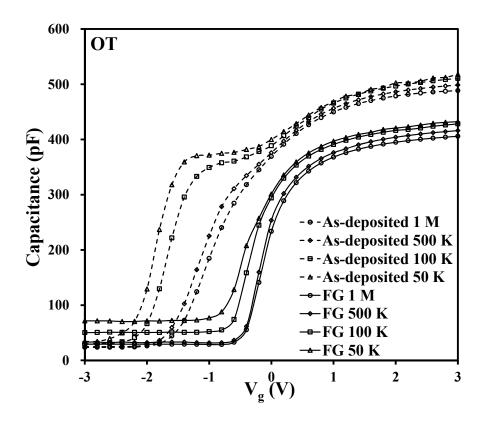

| Figure 5.8. Comparison of the loop width for (a) WT, (b) NS, (c) PT and (d) OT samples           |

| between the as-deposited and FG-annealed ones, with (e) summarizing the                          |

| change of the loop width123                                                            |

|----------------------------------------------------------------------------------------|

| Figure 5.9 Comparison of the loop width between the as-deposited and FG-annealed       |

| samples under positive (negative) stress. Subset (a) and (c) representatively show     |

| CV traces of the WT samples to indicate the change of the loop width under             |

| positive and negative stress for 21,000 seconds, respectively. The change of the       |

| loop widths under different stress time are summarized in (b) with positive stress     |

| and in (d) with negative stress for both the as-deposited and FG-annealed samples      |

| 125                                                                                    |

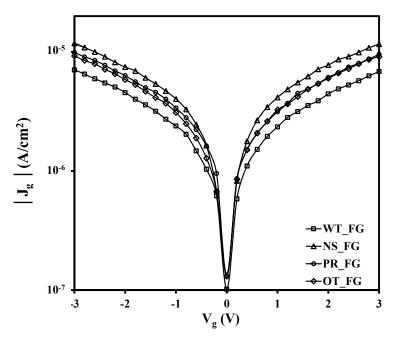

| Figure 5.10 Gate leakage current density (Jg) versus gate voltage (Vg) of the four     |

| samples after FG annealing126                                                          |

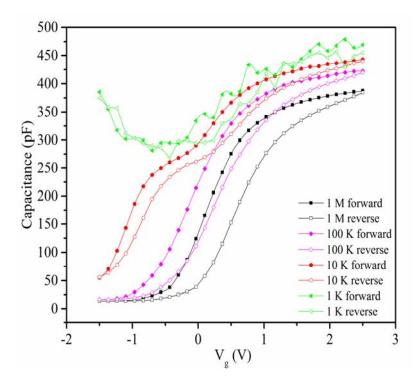

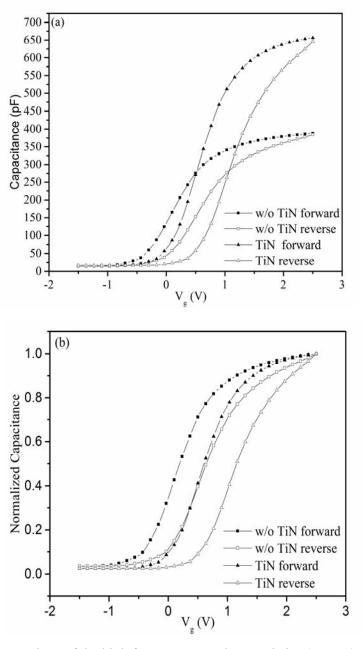

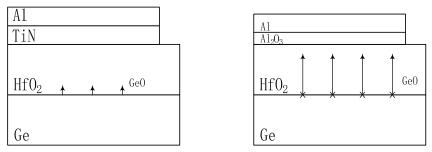

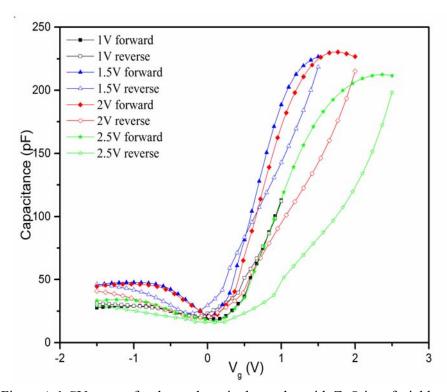

| Figure 5.11 The CV characteristics of the sample without TiN cap layer128              |

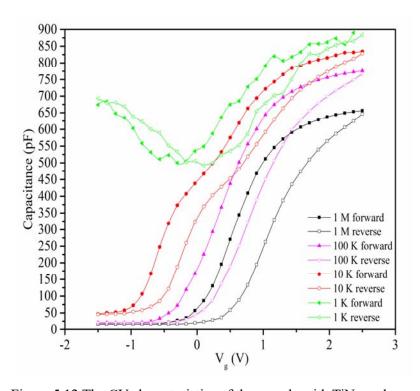

| Figure 5.12 The CV characteristics of the sample with TiN cap layer                    |

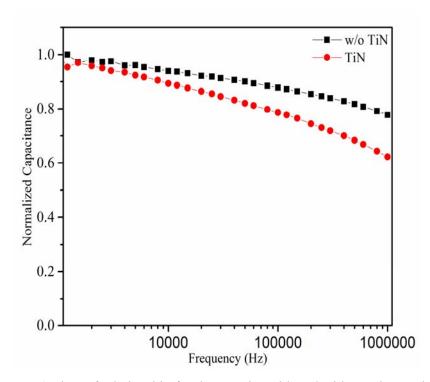

| Figure 5.13 The C-f relationship for the samples with and without TiN cap layer129     |

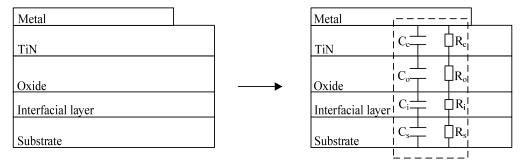

| Figure 5.14 Schematic model of the parasitic effect for the sample with TiN cap layer. |

| 129                                                                                    |

| Figure 5.15 (a) Comparison of the high frequency CV characteristics (1 MHz) extracted  |

| from the samples with and without TiN cap layer and (b) the normalized CV              |

| characteristics.                                                                       |

| Figure 5.16 Schematic model for the mechanism of cap layer to suppress GeO             |

| desorption. (a) TiN works as the cap layer to suppress the GeO desorption. (b) On      |

| the other hand. GeO diffuses out to the metal gate and reacted with Al132              |

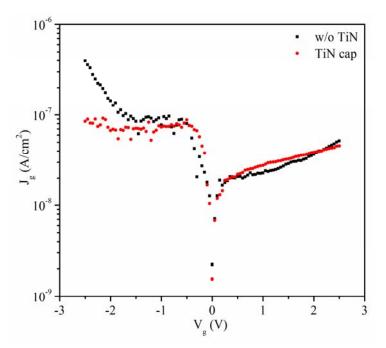

| Figure 5.17 Gate leakage current density (Jg) versus gate voltage (Vg) for samples with |  |

|-----------------------------------------------------------------------------------------|--|

| and without TiN cap layer132                                                            |  |

| Figure A.1 CV curves for the as-deposited samples with ZnO interfacial layer149         |  |

| Figure A.2 The CV characteristics of the control sample (WT) before and after FG        |  |

| annealing150                                                                            |  |

| Figure A.3 The CV characteristics sample with PT passivation before and after FG        |  |

| annealing150                                                                            |  |

| Figure A.4 The CV characteristics of the sample with OT passivation before and after    |  |

| FG annealing                                                                            |  |

## **List of Tables**

| Table 1-1 Electrical properties of high- <i>k</i> dielectrics [14-19]5                    |

|-------------------------------------------------------------------------------------------|

| Table 1-2 Electrical properties of potential channel materials for future nanoelectronic. |

| 8                                                                                         |

| Table 2-1 MO precursor and corresponding oxidation source for ALD deposition40            |

| Table 2-2 Purpose for the design of the samples                                           |

| Table 2-3 Summary of the samples used in this research                                    |

| Table 4-1 Compositions extracted from the line fits shown in Figure 4.4, relative to the  |

| bulk substrate Ge <sup>0</sup> peak for the four samples93                                |

# **List of Symbols**

| Symbol               | Definition                                                         |

|----------------------|--------------------------------------------------------------------|

| A                    | amplification factor                                               |

| C                    | capacitance                                                        |

| $C_{ m ox}$          | oxide capacitance                                                  |

| N                    | number of the measurement in the determination of $R_{rms}$        |

| $N_{ot}$             | oxide trap density                                                 |

| Q                    | charge of interface dipole per unit area                           |

| $oldsymbol{Q}_{dep}$ | depletion charge per unit area                                     |

| $Q_{it}$             | equivalent charge of interface state per unit area                 |

| $Q_{ot}$             | equivalent charge in the oxide                                     |

| R                    | resistance                                                         |

| $R_{rms}$            | root-mean-square roughness                                         |

| T                    | thickness of the dielectric oxide                                  |

| $V_{FB}$             | flat-band voltage                                                  |

| $V_{ m g}$           | bias voltage applied to a metal gate                               |

| $\Delta V_{ m g}$    | voltage shift of CV traces                                         |

| $V_{ m PP}$          | peak to peak voltage                                               |

| $W_f$                | loop width of forward pulse CV relative to that of conventional CV |

| $W_r$                | loop width of reverse pulse CV relative to that of conventional CV |

| $\mathbf{d}_1$               | the dipole separation in conventional CV measurement            |

|------------------------------|-----------------------------------------------------------------|

| $d_2$                        | the dipole separation of forward sweep under pulse measurements |

| $d_3$                        | the dipole separation of reverse sweep under pulse measurements |

| $oldsymbol{i}_{ m ac}$       | AC current through a capacitor                                  |

| iC                           | current through a capacitor                                     |

| $i_{ m R}$                   | current through a resistor                                      |

| $oldsymbol{i}_{	ext{total}}$ | total current through a device                                  |

| k                            | dielectric constant                                             |

| q                            | elemental charge                                                |

| t                            | time                                                            |

| $t_{high	ext{-}k}$           | thickness of high-k thin film                                   |

| VCH1                         | voltage signal of channel 1 of an oscilloscope                  |

| VCH2                         | voltage signal of channel 2 of an oscilloscope                  |

| $v_{ m ac}$                  | AC voltage applied on a capacitor                               |

| $ar{z}$                      | average height in the determination of $R_{rms}$                |

| Zn                           | measured height in the determination of $R_{rms}$               |

| $\epsilon_{ m SiO_2}$        | dielectric constant of silicon dioxide                          |

| Ehigh-k                      | dielectric constant of high-k thin film                         |

| $\epsilon_{ox}$              | dielectric constant of an oxide                                 |

| $\emptyset_F$                | The potential between fermi level and intrinsic fermi level     |

| $\theta$                     | angle between the dipole and interface                          |

# **List of Abbreviations and Acronyms**

| Term           | Initial Components of the Terms         |

|----------------|-----------------------------------------|

| Al             | Aluminum                                |

| ALD            | Atomic Layer Deposition                 |

| AFM            | Atomic Force Microscope                 |

| ALD            | Atomic Layer Deposition                 |

| a-Si:H         | Hydrogenated Amorphous Silicon          |

| CET            | Capacitance Equivalent Thickness        |

| C-f            | Capacitance-frequency                   |

| CMOS           | Complementary Metal Oxide Semiconductor |

| CV             | Capacitance-Voltage                     |

| Dy             | Dysprosium                              |

| DI water       | Deionized Water                         |

| DUT            | Device Under Test                       |

| $\Delta E_{c}$ | Conduction Band Offset                  |

| $\Delta E_v$   | Valance Band Offset                     |

| $E_g$          | Bandgap                                 |

| ЕОТ            | Equivalent Oxide Thickness              |

| Er             | Erbium                                  |

| FG             | Forming Gas                             |

GaAs Gallium Arsenide

Gd Gadolinium

Ge Germanium

GeO<sub>2</sub> Germanium Dioxide

GeO<sub>x</sub> Germanium OSxide

GeOI Germanium on Insulator

HBr Hydrobromic Acid

HCl Hydrogen Chloride

HF Hydrofluoric Acid

HI Hydrolodic Acid

H<sub>2</sub> Hydrogen

H<sub>2</sub>S Hydrogen Sulfide

Hf Hafnium

HfO<sub>2</sub> Hafnium Oxide

HfSiO<sub>4</sub> Hafnium Silicate

HSA Hemispherical Analyzer

InP Indium Phosphide

InSb Indium Antimonide

ITRS International Technology Roadmap for Semiconductors

IV Current-Voltage

La Lanthanum

La<sub>2</sub>O<sub>3</sub> Lanthanum Oxide

LaZrO<sub>x</sub> Lanthanide Zirconium Oxide

MNT Micro and Nano Technology

MO Metal-Organic

MOS Metal-Oxide-Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

N<sub>2</sub> Nitrogen

NS (NH<sub>4</sub>)<sub>2</sub>S

OH Hydroxyl

OT Octanethiol

PDA Post Deposition Annealing

PECVD Plasma Enhanced Chemical Vapor Deposition

PMA Post Metal Annealing

PT Propanethiol

RTA Rapid Thermal Annealing

SAED Selected Area Electron Diffraction

Si Silicon

Si<sub>3</sub>N<sub>4</sub> Silicon Nitride

SiO<sub>2</sub> Silicon Dioxide

SrTiO<sub>3</sub> Strontium Titanate

TEM Transmission Electron Microscope

Ta<sub>2</sub>O<sub>5</sub> Tantalum Oxide

Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> Hafnium Titanate oxide

TiN Titanium Nitride

TiO<sub>2</sub> Titanium Dioxides

UHV Ultra-High Vacuum

VT voltage-time

WT Without Treatment

XRD X-ray Diffraction

XPS X-ray Photoelectron Spectroscopy

Y<sub>2</sub>O<sub>3</sub> Yttrium Oxide

ZnO Zinc Oxide

ZrO<sub>2</sub> Zirconium Oxide

ZrSiO<sub>4</sub> Zirconium Silicates

### **Chapter 1: Introduction and Background Information**

#### 1.1 Research Background

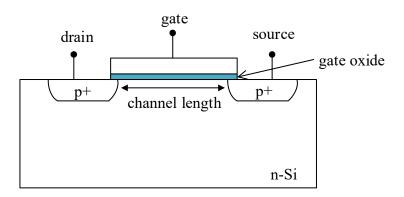

Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) are the key components of an integrated circuit (IC) and the structure of a MOSFET is shown in Figure 1.1. The device consists of a drain, a source, a gate, a gate oxide layer and a channel region beneath the gate oxide. Usually, the drain and source are the heavily doped p-type silicon (Si) if the n-type Si wafer is used as substrate or vice versa. Dielectric materials, such as silicon dioxide (SiO<sub>2</sub>) and hafnium dioxide (HfO<sub>2</sub>), have been used as gate oxide layers. The gate was made of poly-silicon in the early age of the IC though it is generally made of metal in modern times.

Figure 1.1 The structure of a MOSFET.

From Figure 1.1, it can be seen that two diodes are formed by the drain/substrate and source/substrate positioned connected back-to back when no gate voltage is applied. If a negative voltage is applied to the gate terminal (PMOS in this example), an inversion layer will be formed in the channel region and a current is able to flow between the

drain and source terminals. The voltage required to turn on the MOSFET is called the threshold voltage,  $V_t$ . It can be expressed as

$$V_{t} = V_{FB} + 2\phi_{F} - \frac{Q_{dep}}{C_{ox}} - \frac{Q_{ot} + Q_{it}}{C_{ox}}$$

(1.1)

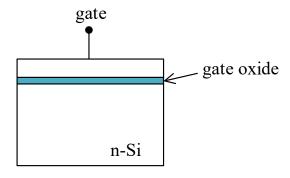

In Formula (1.1),  $V_{FB}$  is the flat-band voltage, controlled by the gate material and substrate material used.  $\emptyset_F$  is related to the doping concentration of the substrate material.  $Q_{dep}$  is the depletion charge per unit area and determined by the substrate material and body bias. The terms,  $Q_{ot}$  and  $Q_{tt}$  are related to the traps in the oxide and the interface between the oxide and substrate. In this research, the traps formed by the interaction of the materials used to manufacture the device will be investigated. As such a MOS capacitor structure, shown in Figure 1.2, will be used as it simplifies the manufacturing process, whilst providing all of the same material interfaces which can be tested for traps in a similar manner to the MOS transistor. Therefore, in the research, a MOS capacitor (shown in Figure 1.2) is a sufficient structure to investigate the performance of a device and the trapping/de-trapping behavior of the charges in the gate oxides.

Figure 1.2 The structure of MOS capacitor.

In order to integrate more MOSFETs within the unit area of a chip, over the years since its inception, the size of the MOSFET has been continuously scaled down. The process technology developed from 10 µm in the middle of the 20th century to state-of-the-art processes for 14 nm nowadays. It is believed that miniaturization of the device size will continue to drive the development of IC technology. However, the traditional SiO<sub>2</sub> dielectric based devices have reached their physical limitations due to the material properties of the oxide. When the thickness of the SiO<sub>2</sub> gate dielectric decreases below 1.2 nm, electron tunneling effects and leakage current (>10 A/cm²) become serious obstacles in relation to device operation and power consumption [1, 2]. To further decrease the size of devices, high-k materials, materials with dielectric constants larger than that of SiO<sub>2</sub>, 3.9, have been employed to replace the SiO<sub>2</sub> gate dielectrics. For example, in 2007, MOSFET technology substituted the SiO2 for a hafnium-based high-k material [3]. With the introduction of high-k materials, a smaller equivalent oxide thickness (EOT) is obtained from a greater physical thickness compared to that of the SiO<sub>2</sub> gate dielectric [4]. A small EOT is desired in order to scale down the size of devices and the large physical thickness is required to ensure a small leakage current. As reported by Nadimi, the leakage current densities for hafnium oxide (HfO<sub>2</sub>) and SiO<sub>2</sub> decrease by 0.31 decade/Å and 0.49 decade/Å, respectively, with the increase of oxide thickness [5]. The formula for calculation of EOT is shown in Formula (1.2).

$$EOT = \frac{t_{high-k} \cdot \epsilon_{SiO_2}}{\epsilon_{high-k}},$$

(1.2)

where  $t_{high-k}$  is the thickness of the high-k material,  $\varepsilon_{high-k}$  is the relative permittivity of the high-k material and  $\varepsilon_{SiO_2}$  is the relative permittivity of SiO<sub>2</sub>, 3.9.

Formula (1.2) shows that through the employment of high-k materials, gate dielectrics with a small EOT can be obtained without causing an increase in gate leakage current, which is one of the most significant issues related to device operation and power consumption [6-10]. A number of high-k materials, HfO<sub>2</sub>, ZrO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, and their silicates, have been widely studied due to their relatively high dielectric constants [11, 12]. In addition to increasing the dielectric constant of the gate oxide, it is also desired to have a larger band gap and band offset to that of the substrate material. If the conduction band offset ( $\Delta E_c$ ) from the substrate material for the gate oxide is much less than 1.0 eV, it will likely to preclude its use, since electron transport, either by thermal emission or tunneling, will lead to unacceptably high leakage currents [13]. As the  $\Delta E_c$ for a number of potential ternary gate dielectrics have not been reported previously, the closest and most readily attainable indicator of the band offset is considered to be the dielectric band gap ( $E_{\rm g}$ ). Usually, a large  $E_{\rm g}$  corresponds to a large  $\Delta E_{c}.$  In addition, the higher the dielectric constant the dielectric material has, the narrower the band gap it will have. Therefore, a tradeoff between the two factors should be considered when the potential dielectric material is selected. The electrical properties of some widely studied high-*k* materials are listed in Table 1-1.

From Table 1-1, the reported dielectric constants of the binary oxides with acceptable band gaps are not high enough (to scale down to EOT<0.5 nm), and hence would not allow further scaling of the MOSFETs [20, 21]. In order to overcome this problem, a number of trials have been carried out to further increase the permittivity of these dielectrics. For example, zirconium oxide (ZrO<sub>2</sub>) exhibits a wide range of crystal phases

each with a different dielectric constant, in theory, ranging from 16 for the monoclinic phase to 47 for the metastable tetragonal phase [22].

Table 1-1 Electrical properties of high-*k* dielectrics [14-19]

| Dielectric<br>Materials        | Dielectric<br>Constant | Band<br>Gap (eV) |

|--------------------------------|------------------------|------------------|

| Si <sub>3</sub> N <sub>4</sub> | 7.1                    | 5.3              |

| $Al_2O_3$                      | 8.5                    | 6.7              |

| $HfO_2$                        | 21                     | 4.7              |

| Ta <sub>2</sub> O <sub>5</sub> | 26                     | 4.4              |

| $ZrO_2$                        | 29                     | 5.8              |

| $Y_2O_3$                       | 15                     | 6.0              |

| $TiO_2$                        | 60                     | 3.2              |

| SrTiO <sub>3</sub>             | 120                    | 1.8              |

| HfSiO <sub>4</sub>             | 11                     | 6.5              |

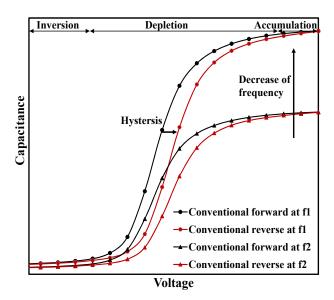

Some researchers have indicated that ZrO<sub>2</sub> with metastable tetragonal and cubic phases, with higher *k*-values, can be stabilized by adding small amounts of rare earth elements (such as lanthanum (La), Gadolinium (Gd), Dysprosium (Dy), Erbium (Er), *etc.*) [23-27]. Lightly lanthanum doped zirconium oxide is considered to be one potential candidate that could be used to reduce EOT and hence allow scaling of the transistor size. However, a significant dielectric relaxation accompanies the increase in dielectric constant for lanthanide zirconium oxide (LaZrO<sub>x</sub>) [28]. Generally, the dielectric relaxation represents the frequency dispersion of the dielectric material. In detail, the capacitance of the MOS capacitor will decrease with an increase in measurement frequency. This phenomenon is partially caused by extrinsic factors, such as series resistance, parasitic effects, lossy interfacial layers, leakage currents, and surface roughness of dielectric layers [29]. However, in the case of LaZrO<sub>x</sub>, the intrinsic factors are the main cause for the dielectric

relaxation. Three intrinsic causes for the dielectric relaxation are: 1) ion movement of interstitial La<sup>+</sup> or Zr<sup>+</sup> ions in the metal-oxide lattice [30]; 2) the combination of unbound metal ions with electron traps, generating dipole moments and inducing dielectric relaxation [31]; and 3) decrease in crystal grain size, causing an increase in the dielectric relaxation due to increased stresses [32, 33].

Besides doping with rare earth elements, another possible way of increasing the dielectric constant of the dielectrics is to mix the oxide with other dielectric materials of a higher relative permittivity, such as titanium oxide ( $TiO_2$ , which has  $k\approx60$ ). The high dielectric constant of the  $TiO_2$  originates from the soft phonons of titanium, and it increases the overall dielectric constant of the gate oxide [34-36]. Despite the increase in dielectric constant of the dielectric material through mixing it with  $TiO_2$ , the small band gap of  $TiO_2$  [37] will result in a large leakage current, this remains an issue to be considered [34]. Therefore, although the ternary oxides may be a solution to further reducing the EOT and hence scaling down the size of the transistor, more research needs to be carried out to address the accompanied problems and a great amount of attention has been attracted from both industrial and academic researchers [6, 30, 34, 36, 37].

Although EOT can be reduced by employing high-*k* materials, the quality of the high-*k* material is typically inferior to that of the conventional SiO<sub>2</sub> based gate dielectrics. High-*k* dielectrics exhibit a significant number of defects which have been proven to result in the instability of devices, such as threshold voltage instability [38-42]. Also, most of the charge traps in the bulk of the material are difficult to detect or probe using traditional CV/IV techniques due to the charge loss over the long time scales taken for the measurements [43, 44]. With regard to the photo IV technique, it is used to assess the spatial distribution of charges [45, 46], but the measurement is too slow to characterize defects near the interface because of fast de-trapping [47, 48].

Therefore, in order to investigate the effect of charge trapping/de-trapping by the defects and provide possible explanations for the phenomena caused by the defects, a number of fast measurement techniques, such as the charge injection and sensing technique [49], the pulse IV technique [50-53] and the pulse CV technique [54-56] have been developed. Over the course of this study, a pulse CV method, able to complete the CV sweep in several hundreds of micro seconds, was developed. The detailed working principle and mechanism of this measurement system will be discussed in Sections 2.3 and 3.1. Using this powerful method, more trapped charges can be detected in comparison to conventional methods. This improvement is attributed to the fast characterization of the pulse CV technique resulting in less de-trapping when compared with conventional methods, therefore, more traps can be measured. In addition, the time-dependent trapping/de-trapping of the traps can be traced by changing the edge time, width and peak to peak voltage (VPP) of the pulse applied.

As the transistor size becomes small enough (EOT<0.5 nm), the operation speed of a transistor is dominated by the injection velocity at the source region of a MOSFET rather than the saturation velocity [57, 58]. The injection velocity is the velocity of positively and negatively directed fluxes and is proportional to the mobility of the semiconductor material. Therefore, high-mobility channel materials offer one of possible option towards improving the performance of future nanoelectronic devices. The electrical properties of several potential channel materials are compared with Si at 300 K in Table 1-2 [58-60].

From the parameters in Table 1-2, germanium is seen to be a semiconductor material of great potential for the fabrication of MOSFETs. Firstly, both the electron and hole bulk motilities of Ge are higher than those of Si [58] and can also be enhanced by strain [61]. The smaller bandgap, E<sub>g</sub>, of Ge compared to that of Si allows the supply voltage to be

further reduced despite a significant increase in leakage current and reverse current density of a pn junction [62-64].

Table 1-2 Electrical properties of potential channel materials for future nanoelectronics.

|                                                                      | Ge    | Si    | GaAs  | InSb  | InP   |

|----------------------------------------------------------------------|-------|-------|-------|-------|-------|

| Bandgap (eV)                                                         | 0.66  | 1.12  | 1.42  | 0.17  | 1.35  |

| Electron affinity (eV)                                               | 4.05  | 4.0   | 4.07  | 4.59  | 4.38  |

| Hole mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )     | 1900  | 450   | 400   | 1250  | 150   |

| Electron mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 3900  | 1500  | 8500  | 80000 | 4600  |

| Lattice constant (nm)                                                | 0.565 | 0.543 | 0.565 | 0.648 | 0.587 |

| Dielectric constant                                                  | 16    | 11.9  | 13.1  | 17.7  | 12.4  |

| Melting points (°C)                                                  | 937   | 1412  | 1240  | 527   | 1060  |

Moreover, the process technology is compatible with the Si CMOS process technology. Therefore, Ge is considered to be one of the most promising channel materials for the future of nanoelectronics. However, due to the instability of germanium native oxides and the poor interface quality between germanium substrates and dielectric oxides [65, 66], selection of a suitable passivation technique presents a major technical hurdle to overcome before Ge can be used to make high-performance MOSFET devices. Generally, except for the interface quality of SiO2 on Si, the oxide layer (including native oxide) is insufficient to passivate the surface of semiconductor substrates [59]. With regard to the deterioration of the germanium interface, it has been widely conjectured to be attributed to the formation of GeO<sub>2</sub> at the interface between the Ge substrate and the deposited dielectric thin film [67, 68]. In addition, a typical reaction for a GeO<sub>2</sub>/Ge interface as shown by Formula (1.3), will lead to the reduction of GeO<sub>2</sub> and generation of volatile GeO [69, 70]. GeO desorption from the gate oxide/Ge interface and diffusion across the thin film will also deteriorate the quality of dielectric thin films.

$$GeO_2 + Ge \rightarrow 2GeO$$

(1.3)

Proof of this phenomenon has been supported by inspecting the thickness of the GeO<sub>2</sub> layer deposited on Ge and SiO<sub>2</sub>/Si substrates in published research [68]. The deterioration caused by the reaction between the GeO<sub>2</sub> layer and Ge substrate will lead to a large hysteresis (of around 1.5 V) in the measured CV curves as observed for the Ge/GeO<sub>2</sub> gate stacked MOS capacitor [67]. The hysteresis (also called loop width) is defined as the voltage shift between the reverse and forward CV traces. A detailed description of this phenomenon will be presented in Section 2.4.

The dielectric constant of the Ge oxide can be as low as 7, which limits the potential scaling of the MOS device. Therefore, the removal of Ge oxides from the Ge substrate prior to the deposition of a high-k thin film is a necessary step in achieving an EOT below 0.5 nm as required in the International Technology Roadmap for Semiconductors (ITRS) [71]. One effective method of decreasing the amount of Ge oxide is through the application of an acid pretreatment, using for example halogen acid (HF, HCl, HBr, and HI) [59, 72]. In addition, oxidizing the insoluble GeO<sub>x</sub> into soluble GeO<sub>2</sub> using oxidizing agents, such as O<sub>2</sub>, O<sub>3</sub>, and H<sub>2</sub>O<sub>2</sub>, has also been attempted for removal of the oxide. However, it should be emphasized that a certain amount of Ge oxide still remains due to inefficient acid treatment and the re-oxidation process during the transfer of samples. The residual germanium oxide will diffuse into the high-k film and deteriorate the quality of the device. Therefore, a cap layer technique has been proposed to suppress the desorption of the GeO from the gate oxide/Ge interface to the high-k oxides. An Si cap has been attempted in previous research, in which CV characteristics with less distortion were observed compared with that without the cap layer [75]. In the research work, a GeO2 dielectric layer was deposited on a Ge substrate. The reaction described

by Formula (1.3) occurred and GeO at the interface between the dielectric layer and substrate was formed. When the Si cap layer was placed on top of the GeO<sub>2</sub> thin film, it is considered that it blocks the diffusion of the GeO to the air and, therefore, the chemical potential of the GeO inside the film is increased. The reaction rate of GeO<sub>2</sub> at the interface, as described by Formula (1.3), decreases due to the equilibrium of the reaction. The mechanism is considered to suppress the formation of GeO [68].

Besides the cap layer technique, a number of other techniques have also been proposed to directly passivate the germanium surface after the removal of GeO to improve the electrical performance of the devices. These passivation techniques include NH<sub>3</sub> treatment [76], surface nitridation [77-81], SiH<sub>4</sub> treatment [82], AlN<sub>x</sub> passivation [83, 84], sulfur treatment [85-87], aluminum oxide passivation [21], high-quality GeO<sub>2</sub> passivation [88, 89].

In addition to the unwanted desorption of GeO due to the reaction of the GeO<sub>2</sub> and substrate, the relatively low dielectric constant of GeO<sub>2</sub> is also a fatal problem preventing further scaling of the MOS device. High-*k* material offers is a possible solution to this problem. However, for high-*k* materials deposited on Ge substrates, there are two main requirements: obtaining a small EOT (<0.5 nm) and a thermally stable property with the substrate (used as passivation layer or dielectric layer). Unfortunately, one of the most promising high-*k* materials tried on Si substrates, HfO<sub>2</sub>, is unsuitable for direct application onto a Ge substrate, since as reported by Van Elshocht [78] and Xie [90], the diffusion of Ge into the HfO<sub>2</sub> layer leads to poor electrical properties, unless a good interfacial layer or suitable passivation technique is used. So, stabilization of a high-*k*/Ge interface is a key issue for the fabrication of Ge MOS devices.

Detailed working principles of an effective passivation method for the Ge surface and the corresponding mechanism remain open questions. The criteria for selecting a high-k gate insulator to realize a good interface with the Ge substrate should be: (1) readily intermixable with interfacial Ge oxide only at the interface and a germinate with less defects is formed; and (2) an amorphous thin film is formed, which can restrict Ge diffusion into the high-k film and hence GeO desorption through the high-k thin film. However, in most cases, the native oxide cannot be completely removed and intermixing cannot be avoided during the deposition of dielectrics (or during subsequent treatments, such as post-deposition annealing (PDA)). An excess incorporation of Ge into the high-k layer quickly deteriorates electrical characteristics, such as forming an increase in hysteresis in the CV characteristics and mobility degradation [91]. In future research and industrial application, a variety of high-k materials will be applied. Criteria defined based on results and physical analysis will be helpful in the selection of the high-k dielectrics in the application of Ge substrate MOS devices.

In reality, there is comparatively less economic Ge than Si available and hence less production of bulk Ge wafers. Ge channels integrated on other substrates as thin surface layers, such as Ge-on-Insulator (GOI) [92-94], Ge-on-Si [95, 96], are considered to be some of the potential solutions to improving future device performance. SiGe substrates may also be a realistic option for obtaining relatively high mobility [97, 98].

#### 1.2 Outline of Work

The SiO<sub>2</sub> based device has reached its physical limit due to the rapid scaling of MOSFETs. In order to continue the scaling of MOSFETs, high-k oxides have been employed as gate oxides. However, the larger number of defects in high-k oxides

compared with those in SiO<sub>2</sub> leads to the instability of such MOS devices. A fundamental understanding of the traps in new dielectric materials is a critical issue. A high-k material, LaZrO<sub>x</sub>, was deposited on n-type silicon substrate and the corresponding MOS capacitor was fabricated. A pulse CV system was developed and employed to investigate the charge trapping/de-trapping behavior in the oxide. The pulse CV system is capable of completing the CV sweep in several hundreds of microseconds allowing more traps to be detected compared with conventional CV measurement systems. In addition, when the pulse CV measurements were performed on MOS capacitors with non-stoichiometric oxides native to the substrates, an anomalous behavior in the CV curves was observed. In order to explain this anomalous phenomenon in the CV curves, a hypothesis that successfully explains most of the abnormal features was proposed. Furthermore, the effects of deposition and annealing conditions on the pulse CV behavior were also explored. Additionally, a hump in the weak inversion region of the forward pulse CV trace was also observed and a corresponding explanation for this was provided.

Due to the higher carrier mobility of germanium, it has emerged as a promising candidate for the channel material in high-speed MOSFET devices [99, 100]. However, the unstable native oxide and the poor interface quality between the germanium substrate and dielectric oxide make it difficult to be applied in the fabrication of a MOSFET. Also, there is a debate on the impact of GeO<sub>x</sub> on the device performance. Therefore, research into the physical and electrical properties of Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> on germanium substrates was carried out. X-ray Photoelectron Spectroscopy (XPS) was used to investigate interfacial quality and chemical structure. The Agilent B1500A semiconductor device analyzer was used to measure the gate leakage current and CV characteristics. The correlation between the gate leakage current and interface quality

of the samples is studied. In addition, an in-situ ZnO interfacial layer in atomic layer deposition (ALD) was attempted to passivate the substrate and the effects of PDA were also explored.

An effective passivation technique for germanium surfaces is known to be a significant hurdle to overcome before Ge can be used to make high-performance MOS devices, due to the poor interface quality between high-k/Ge materials as described in Section 1.1. The deterioration of the germanium interface is widely believed to be due to the reaction of the dielectric oxides and germanium substrates and diffusion of GeO formed during the reaction. Therefore, two techniques were attempted to suppress the deterioration of germanium interface quality. Firstly, previous research outputs have reported that the introduction of sulfur in the GeO<sub>x</sub> can result in a superior Ge gate stack. Therefore, wet chemical treatments with both organic and inorganic solutions were performed on the germanium substrates to form a sulfur monolayer. Secondly, a TiN cap layer was deposited on the high-k oxide to suppress the formation of volatile GeO, which would otherwise degrade the quality of the dielectric thin film.

#### 1.3 Aims and Objectives

This research aims to fabricate Ge MOS capacitors with high-*k* dielectric materials using an effective passivation method, which is important for the application of Ge MOS devices. This will make a contribution to the development of ICs with germanium wafers. The following three objectives will be realized in achieving the aims of the thesis:

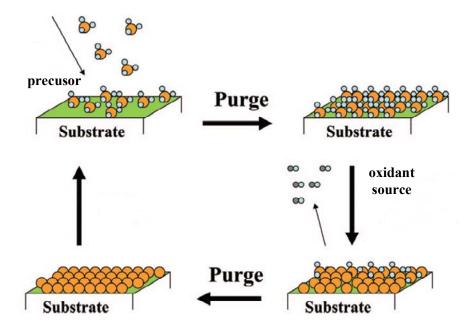

I. To deposit high-k dielectric thin films on Si substrates using ALD and to investigate the oxide traps in the dielectrics, including the number of traps and time-dependent trapping/de-trapping behavior of the charges, using a developed pulse CV system.

- Explanations for the behaviors in the pulse CV traces are to be provided.

- II. To deposit high-*k* thin films on Ge substrates and analyze the interface quality and chemical structure and their relationships to the CV/IV characteristics. To passivate the Ge substrate and investigate the CV/IV characteristics of the MOS capacitors with an in-situ passivation method.

- III. To analyze the effect of different wet chemical treatments on germanium substrates and investigate the impact of a cap layer on electrical properties of Ge MOS capacitors, including dielectric constant, frequency dispersion and leakage current.

Models related to the observed phenomenon are to be proposed.

# 1.4 Original Contribution

- I. A current probe was replaced by an amplifier connected to an oscilloscope in the developed pulse CV system. The system is more cost-effective and can be updated more easily when compared to the current probe. In addition, for the pulse CV characteristics, the relative positions of forward and reverse CV traces are opposite to those obtained from conventional measurements. A model related to interface dipoles was proposed to explain the anomalous behavior.

- II. There is a debate on the role and effect of the GeO<sub>x</sub> and germinate at the high-k/Ge interface and no solid conclusion has been determined. In this research, the formation of GeO<sub>x</sub> and germinate at the interface between Ge substrates and Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> gate oxides was observed and a severe deterioration of the interface

quality was detected by using XPS. The deterioration of the interface between Ge and Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> is caused by the oxidation source from HfO<sub>2</sub>, which leads to an increase in leakage current.

III. Propanethiol solution and octanethiol solutions were used to passivate the n-type germanium substrates for the first time. The results show that all the passivated samples have a larger dielectric constant and lower leakage current density when compared with the control sample. In addition, the TiN cap layer was employed to suppress the formation of volatile GeO, which was considered to deteriorate the quality of the gate oxides. As a result, the dielectric constant of the oxide layer increases from 8.2 to 13.5 and a lower leakage current density is obtained when a negative voltage is applied. Compared with the Si cap layer, no additional processes, such as ex-situ plasma enhanced chemical vapor deposition (PECVD), are required for the TiN cap layer.

## 1.5 Published works

### Journal Articles

[1] **Qifeng Lu**, Yifei Mu, Yinchao Zhao, Ce Zhou Zhao, Sang Lam, Yuxiao Fang, Li Yang, Chun Zhao, Steve Taylor and Paul R. Chalker, *Effect of Surface Passivation and Post-Metal Annealing on Electrical Performance of Ge MOS Devices with HfO*<sub>2</sub> *Gate Dielectric*, 17: 526 – 530, *IEEE Transactions on Device and Materials Reliability* (2017).

- [2] **Qifeng Lu**, Yanfei Qi, Ce Zhou Zhao, Chun Zhao, Stephen Taylor and Paul R. Chalker, Capacitance-Voltage Characteristics Measured Through Pulse Technique on High-k Dielectric MOS Devices, 140: (19-23), Vacuum (2016).

- [3] **Qifeng Lu,** Yifei Mu, Joseph W. Roberts, Mohammed Althobaiti, Vinod R. Dhanak, Jingjin Wu, Chun Zhao, Ce Zhou Zhao, Qian Zhang, Li Yang, Ivona Z. Mitrovic, Stephen Taylor and Paul R. Chalker, *Electrical Properties and Interfacial Studies of Hf<sub>x</sub>Ti<sub>1-x</sub>O<sub>2</sub> High Permittivity Gate Insulators Deposited on Germanium Substrates, 8: 8169–8182, <i>Materials* (2015).

- [4] **Qifeng Lu,** Chun Zhao, Yifei Mu, Ce Zhou Zhao, Stephen Taylor and Paul R. Chalker, Hysteresis in Lanthanide Zirconium Oxides Observed Using a Pulse CV Technique and including the Effect of High Temperature Annealing, 8: 4829-4842, **Materials** (2015).

- [5] Yifei Mu, Ce Zhou Zhao, **Qifeng Lu**, Chun Zhao, Yanfei Qi, Sang Lam, Ivona Z. Mitrovic, Stephen Taylor, and Paul R. Chalker, *Total Ionizing Dose Response of Hafnium-Oxide Based MOS Devices to Low-Dose-Rate Gamma Ray Radiation Observed by Pulse CV and On-site Measurements*, 99:1-1, *IEEE Transactions on Nuclear Science* (2016).

- [6] Jingjin Wu, Yinchao Zhao, Ce Zhou Zhao, Li Yang, **Qifeng Lu**, Qian Zhang, Jeremy Smith and Yongming Zhao, *Effects of Rapid Thermal Annealing on the Structural, Electrical, and Optical Properties of Zr-Doped ZnO Thin Films Grown by Atomic Layer Deposition*, 9 (8): 695, *Materials* (2016).

- [7] Yifei Mu, Ce Zhou Zhao, Yanfei Qi, Sang Lam, Chun Zhao, **Qifeng Lu**, Yutao Cai, Ivona Z. Mitrovic, Stephen Taylor and Paul R. Chalker, *Real-time and on-site* γ-ray radiation response testing system for semiconductor devices and its applications, 372:14-28, *Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials*

#### and Atoms (2016).

- [8] Way Foong Lim, Hock Jin Quah, **Qifeng Lu**, Yifei Mu, Wan Azli Wan Ismail, Bazura Abdul Rahim, Siti Rahmah Esa, Yeh Yee Kee, Zainuriah Hassan, Ce Zhou Zhao and Kuan Yew Cheong, *Effects of Rapid Thermal Annealing on Structural, Chemical, and Electrical Characteristics of Atomic-Layer Deposited Lanthanum Doped Zirconium Dioxide Thin Film on 4H-SiC Substrate*, 365: 296-305, **Applied Surface Science** (2016).

- [9] Chun Zhao, Ce Zhou Zhao, **Qifeng Lu**, Xiaoyi Yan, Stephen Taylor and Paul R. Chalker, Hysteresis in Lanthanide Aluminum Oxides Observed by Fast Pulse CV Measurement, 7: 49165, **Materials** (2014).

#### Conference Papers

- [1] Qifeng Lu, Sang Lam, Yifei Mu, Ce Zhou Zhao, Yinchao Zhao, Yuxiao Fang, Li Yang, Steve Taylor and Paul R. Chalker, Atomic Layer Deposition of HfO<sub>2</sub> Gate Dielectric with Surface Treatments and Post-metallization Annealing for Germanium MOSFETs, The 17th IEEE International Conference on Nanotechnology, 25-27 Jul 2017, Pittsburgh, USA.

- [2] Yanfei Qi, Yuxiao Fang, Chun Zhao, Qifeng Lu, Chenguang Liu and Ce Zhou Zhao, Influence of HfAlO Composition on Resistance Ratio of RRAM with Ti electrode, The 24<sup>th</sup> International Symposium on the Physical and Failure Analysis of Integrated Circuits, 4-7 Jul 2017, Chengdu, China.

- [3] Yanfei Qi, Chun Zhao, Yuxiao Fang, Qifeng Lu, Chenguang Liu and Ce Zhou Zhao, Compliance Current Effect on Switching Behavior of Hafnium Oxide based RRAM, The 24<sup>th</sup> International Symposium on the Physical and Failure Analysis of Integrated Circuits, 4-7 Jul 2017, Chengdu, China.

- [4] Yife Mu, Cezhou Zhao, **Qifeng Lu**, Yanfei Qi, Chun Zhao, Ivona Z. Mitrovic, Stephen Taylor, and Paul R. Chalker, *Total Ionizing Dose Response of Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>y</sub> Ge MOS Capacitors,*The 2017 International Workshop on Reliability of Micro- and Nano-Electronic Devices in Harsh Environment Electronics, 22-24 May 2017, Chengdu, China.

- [5] Q Lu, Y Mu, Yinchao Zhao, C Z Zhao, S Taylor and P R Chalker, *Investigation of the Electrical Performance of HfO*<sub>2</sub> *Dielectrics Deposited on Passivated Germanium Substrates,*The 7<sup>th</sup> International Conference On Key Engineering Materials, 11-13 Mar 2017, Penang,

Malaysia.

- [6] Qifeng Lu, Ce Zhou Zhao, Chun Zhao, Steve Taylor and Paul R. Chalker, Investigation of Anomalous Capacitance-Voltage Behavior Caused by Interface Dipoles and the Effect of Post-Metal-Annealing, International Conference of the Advancement of Materials and Nanotechnology IV, 9-11 Nov 2016, Langkawi, Malaysia.

- [7] Qifeng Lu, Yanfei Qi, Ce Zhou Zhao, Chun Zhao, Stephen Taylor and Paul R. Chalker, Anomalous Capacitance-Voltage Hysteresis in MOS Devices with ZrO<sub>2</sub> and HfO<sub>2</sub> Dielectric, The 5<sup>th</sup> International Symposium on Next-Generation Electronics, 4-6 May 2016 Hsinchu, Taiwan.

- [8] Yifei Mu, Ce Zhou Zhao, Qifeng Lu, Chun Zhao, Yanfei Qi, Sang Lam, Effects of Biased Irradiation on Charge Trapping in HfO<sub>2</sub> Dielectric Thin Films, International Conference of the Advancement of Materials and Nanotechnology IV, 9-11 Nov 2016, Langkawi, Malaysia.

## **Books**

[1] Cezhou Zhao, Zhou Fang and **Qifeng Lu** "An Introduction to Microelectronics" Science Press, Beijing, P. R. China, 2014

[1] **Qifeng Lu**, Jingjin Wu, Ce Zhou Zhao, A surface passivation method for Ge MOS device with ALD deposited high-k dielectrics. No. CN 205177850 U.

## 1.6 Chapter Outline

In Chapter 1, the background information, including the structure of the device, the advantage of the high-*k* materials, the updated CV characterization technique and the challenges faced by the Ge MOS devices, were presented. The aims and objectives of this thesis and the main contributions are also covered in this chapter.

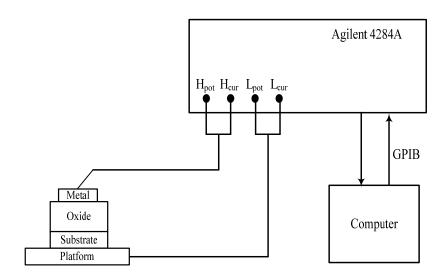

In Chapter 2, ALD is described together with the working mechanism. The E-beam evaporator used for the deposition of metal gates is introduced briefly. The fabrication processes and a summary of the samples used in this research are shown in Section 2.1. The physical and electrical characterization techniques are presented in Sections 2.2 and 2.3. The related technical terms used in following discussions are introduced in Section 2.4 in order to provide some background theory.

In Chapter 3, a pulse CV system which has been developed was employed to explore the CV behavior of MOS capacitors with LaZrO<sub>x</sub> gate oxides. The behavior of charge trapping/de-trapped was investigated and discussed in detail. An abnormal CV behavior was observed when the pulse CV technique was applied to MOS capacitors with some high-*k* dielectrics. In addition, a hump in the weak inversion region of the forward pulse CV trace was also observed. The corresponding models used to explain these phenomenon were proposed. The description and explanation for these two behaviors are presented in Section 3.3.

In Chapter 4, Ti<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> thin films, with different concentrations of titanium oxides, were deposited on p-type Ge substrates. XPS was employed to analyze the interface

quality and chemical structure. The results are presented in Section 4.1. Due to the deterioration of the interface for direct application of high-*k* materials on Ge substrates, in-situ ZnO thin films were used as the interfacial layer between the high-*k*/Ge interface. The effect of PDA on the device performance was also investigated. The results and discussions are presented in Section 4.2

In Chapter 5, propanethiol and octanethiol solutions were used to passivate the Ge substrates in Section 5.1. Also, forming gas (FG, 10% H<sub>2</sub> and 90% N<sub>2</sub>) annealing was performed and better interface quality and smaller delta loop width under long-time stress were obtained when the samples were annealed in a FG environment. Furthermore, since the diffusion of GeO into the high-*k* thin films is considered to be one of the factors resulting in the deterioration of the device performance, a TiN cap layer was fabricated to suppress the formation of violate GeO in Section 5.2. As a result, a higher dielectric constant and a lower leakage current density for negatively applied voltages were obtained.