Radboud University Nijmegen

# PDF hosted at the Radboud Repository of the Radboud University Nijmegen

The version of the following full text has not yet been defined or was untraceable and may differ from the publisher's version.

For additional information about this publication click this link. http://hdl.handle.net/2066/18759

Please be advised that this information was generated on 2017-12-05 and may be subject to change.

Gambling for Leadership: Verification of Root Contention in IEEE 1394

M.I.A. Stoelinga

Computing Science Institute/

CSI-R9904 March 1999

Computing Science Institute Nijmegen Faculty of Mathematics and Informatics Catholic University of Nijmegen Toernooiveld 1 6525 ED Nijmegen The Netherlands

# Gambling for Leadership: Verification of Root Contention in IEEE 1394

Mariëlle Stoelinga Computing Science Institute University of Nijmegen P.O. Box 9010, 6500 GL Nijmegen, The Netherlands marielle@cs.kun.nl

#### Abstract

This report presents a formal verification of root contention in IEEE 1394. Root contention is a simple yet realistic protocol that solves leader election for two processes, using coin flips.

The verification has been carried out in the probabilistic automaton model of [Seg95]. Correctness of an implementation automaton w.r.t. a specification automaton is defined as so-called fair trace distribution inclusion.

Similarly to the non-probabilistic setting, probabilistic simulation relations provide a technique for proving trace distribution inclusion. Then additional reasoning proves fair trace distribution inclusion. Our verification follows this strategy. We introduce two simulation relations, viz. probabilistic step refinements and probabilistic hyperstep refinements. These notions are not very complicated and are sufficient in our verification. They are special cases of the simulation relations from [Seg95].

The verification also involves non-probabilistic techniques. For instance, the invariants have been checked with the model checker SMV.

Key words and phases: IEEE 1394, leader election algorithms, communication protocols, probabilistic and distributed algorithms, formal verification, SMV, probabilistic automata.

**AMS Subject Classification:** 68Q10, 68Q22, 68Q60, 68Q75. **CR Subject Classification:** C.2.2, C.3, F.1.2, K.1.

# 1 Introduction

Recently, the analysis of probabilistic, distributed algorithms and protocols has gained new attention. Various methods and formalisms have been extended with probabilism and quite some case studies have been carried out using these formalisms, c.f. [Agg94, PSL97].

This report verifies a small sub-protocol of the IEEE 1394 protocol, called root contention. The IEEE 1394 high performance serial bus [IEE96, IEE98], also called FireWire, has been developed for interconnecting computer and consumer equipment, such as PCs, VCRs and CD players. The bus is "hot pluggable," which means that equipment can be added and removed at any time, and allows quick, reliable and inexpensive high-bandwidth transfer. This protocol probably becomes the new standard for connecting digital multimedia equipment. Various parts of IEEE have been verified formally, see [DGRV97, Sha98, Lut97]. However, as far as we know, root contention has not.

Root contention in IEEE 1394 is a simple but realistic protocol that involves both real-time and probabilistic aspects. As a first approach we abstract from the real-time aspects and model time passage by discrete actions. The verification in this report is carried out in the probabilistic automaton model from [Seg95]. Following the tradition, the correctness of the protocol is proven by establishing a probabilistic simulation relation between the implementation and the specification, both probabilistic automata.

The probabilistic simulation relations from [Seg95] are rather complex. In order to simplify the simulation proofs, this report introduces the notions of probabilistic step refinement and of probabilistic hyperstep refinement. These are rather obvious extensions of non-probabilistic simulations. However, it has taken some effort to find a formulation which makes the definition fit into the standard pattern of simulation relations.

The strategy followed in the simulation proof is the following. Given the protocol specification P and the abstract specification S, we define two intermediate automata, I and A. The automaton I abstracts from the message passing in Pbut keeps all probabilistic choices. The automaton A combines the probabilistic choices in I. Then we can separate our concerns. The simulation between P and I, a probabilistic step refinement, is easy from probabilistic point of view and mainly deals with traditional, non-probabilistic techniques like proving invariants. Therefore, existing tools for the analysis of non-probabilistic systems can be used. We have checked the invariants with the tool SMV. The probabilistic analysis is concentrated in the simulation relations between between I and A and between A and S. Since these automata are small, this is not so difficult any more.

Furthermore, we have proven inclusion of fair behaviour – technically: fair trace distribution inclusion – between the protocol specification P and the high level specification S. Therefore, we have developed a result that reduces reasoning about fair probabilistic executions to reasoning about fairness of (non-probabilistic) executions.

This report is organized as follows. Section 2 recalls some probability theory and Section 3 introduces the probabilistic automaton model. Section 4 provides automaton models of the implementation and the specifications of the root contention protocol. Then Sections 6 and 7 proves the simulation relations. Finally section 8 presents the conclusions and some topics for future research.

# 2 Probability theory

This section recalls some probability theory. We denote the set  $\mathbb{R} \cup \{\infty\}$  by  $[0, \infty]$ .

#### Summation over index sets

**Definition 2.1** Let  $\mathcal{I}$  be a(n index) set and  $x_i \in [0, \infty]$  for all  $i \in \mathcal{I}$ . Define  $\sum_{i \in \mathcal{I}} x_i$  by

- 1.  $\sum_{i \in \emptyset} x_i \stackrel{\mathrm{d}}{=} 0;$

- 2.  $\sum_{i \in \mathcal{I}} x_i \stackrel{d}{=} x_{i_1} + x_{i_2} + x_{i_3} + \dots + x_{i_n}$ , if  $\mathcal{I}$  is finite, nonempty and  $\mathcal{I} = \{i_1, i_2, i_3, \dots, i_n\};$

- 3.  $\sum_{i \in \mathcal{I}} x_i \stackrel{d}{=} \sup \{\sum_{i \in \mathcal{I}} x_i \mid \mathcal{J} \subseteq \mathcal{I} \text{ is finite }\}, \text{ if } \mathcal{I} \text{ is infinite.}$

Here supr X denotes the supremum, i.e. the smallest upper bound, of the set X. Notice that that  $\sum_{i \in \mathbb{N}} x_i = \sum_{i=0}^{\infty} x_i$  because the summation order is irrelevant, due to the fact that  $x_i \geq 0$ .

**Fact 2.2** Let  $\mathcal{I}, \mathcal{I}_1, \mathcal{I}_2, \ldots$  be sets,  $\mathcal{I} = \bigcup_{n \in \mathbb{N}} \mathcal{I}_n$  and  $x_i \in [0, \infty]$  for all  $i \in \mathcal{I}$ .

- 1. If  $\mathcal{I}_1 \subseteq \mathcal{I}_2$ , then  $\sum_{i \in \mathcal{I}_1} x_i \leq \sum_{i \in \mathcal{I}_2} x_i$ ;

- 2. If  $\mathcal{I}_1 \subseteq \mathcal{I}_2 \subseteq \mathcal{I}_3, \ldots$ , then  $\sum_{i \in \mathcal{I}} x_i = \lim_{n \to \infty} \sum_{i \in \mathcal{I}_n} x_i$ ;

- 3. If  $\mathcal{I}_1, \mathcal{I}_2, \mathcal{I}_3, \ldots$  are pairwise disjoint, then  $\sum_{i \in \mathcal{I}} x_i = \sum_{n \in \mathbb{N}} \sum_{i \in \mathcal{I}_n} x_i$ .

**Fact 2.3** Let  $\mathcal{I}$  be a set,  $x_i \in [0, \infty]$  for all  $i \in \mathcal{I}$  and  $\sum_{i \in \mathcal{I}} x_i < \infty$ . Then the set  $\{x_i \in [0, \infty] \mid x_i > \varepsilon, i \in \mathcal{I}\}$  is finite for every  $\varepsilon > 0$  and  $\{x_i \in [0, \infty] \mid x_i > 0, i \in \mathcal{I}\}$  is countable.

#### **Probability spaces and distributions**

**Definition 2.4** A probability space is a triple  $(\Omega, \mathcal{F}, \mathbf{P})$ , where

- $\Omega$  is a set, called the *sample space*,

- $\mathcal{F} \subseteq 2^{\Omega}$  is  $\sigma$ -field, i.e. a collection of subsets of  $\Omega$  which is closed under countable<sup>1</sup> union and complement and which contains  $\Omega$ ,

- $\mathbf{P}: \mathcal{F} \to [0, 1]$  is a probability measure on  $\mathcal{F}$ , which means that  $\mathbf{P}[\Omega] = 1$  and for any countable collection  $\{C_i\}_i$  of pairwise disjoint subsets in  $\mathcal{F}$  we have  $\mathbf{P}[\cup_i C_i] = \sum_i \mathbf{P}[C_i].$

If  $\{x\} \in \mathcal{F}$  then we write  $\mathbf{P}[x]$  for  $\mathbf{P}[\{x\}]$ . If  $\mathcal{P}$  is a probability space, we denote its sample space by  $\Omega_{\mathcal{P}}$ , its  $\sigma$ -field by  $\mathcal{F}_{\mathcal{P}}$  and its probability measure by  $\mathbf{P}_{\mathcal{P}}$ .

**Definition 2.5** A probability distribution (function) over a set X is a function  $\mu: X \to [0,1]$  such that

$$\sum_{x \in X} \mu(x) = 1.$$

Define the support of  $\mu$  by  $\operatorname{supp}(\mu) \stackrel{d}{=} \{ \mathbf{x} \in \mathbf{X} \mid \mu(\mathbf{x}) > 0 \}$ . By fact 2.3 this is a countable set. We denote the set of all probability distributions over X by  $\Pi(X)$ .

**Remark 2.6** A probability space  $(\Omega, \mathcal{F}, \mathbf{P})$  is discrete if  $\mathcal{F} = 2^{\Omega}$  and  $\mathbf{P}[C] = \sum_{x \in C} \mathbf{P}[x]$ , for all  $C \subseteq \Omega$ . A discrete probability space  $(\Omega, \mathcal{F}, \mathbf{P})$  determines a unique probability distribution  $f : \Omega \to [0, 1]$  by  $f(x) = \mathbf{P}[x]$ . Conversely, a probability distribution f determines a unique discrete probability space: take  $\Omega = X$ ,  $\mathcal{F} = 2^{\Omega}$  and  $\mathbf{P}[C] = \sum_{x \in C} f(x)$  for all  $C \subseteq \Omega$ .

We denote a (probability distribution) function f on a countable domain by enumerating it as a set of pairs. So, if  $\text{Dom}(f) = \{x_1, x_2 \dots\}$  then denote f by  $\{x_1 \mapsto f(x_1), x_2 \mapsto f(x_2) \dots\}$ . If the domain of f is known, then we often leave out elements of probability zero. For instance, the probability distribution assigning probability one to an element  $x \in X$  is denoted by  $\{x \mapsto 1\}$ , irrespective of X. Such distribution is called the *Dirac distribution* over x. The *uniform distribution* over a finite set, say  $\{x_1, \dots, x_n\}$ , is given by  $\{x \mapsto \frac{1}{n}, \dots, x_n \mapsto \frac{1}{n}\}$ .

**Definition 2.7** Let X and Y be sets. If  $\mu \in \Pi(X)$  and  $\nu \in \Pi(Y)$  then the *product*  $\mu \times \nu : X \times Y \to [0, 1]$  defined by

$$(\mu \times \nu)(x,y) \stackrel{\mathrm{d}}{=} \mu(x) \cdot \nu(y)$$

is a probability distribution over  $X \times Y$ .

<sup>&</sup>lt;sup>1</sup>In our terminology, countable objects include finite ones.

The operation above can also be defined for general probability spaces by a more complex definition, see [Seg95].

**Definition 2.8** Let  $\mathcal{P} = (\Omega, \mathcal{F}, \mathbf{P})$  be a probability distribution,  $\Omega'$  a set and  $f : \Omega \to \Omega'$  be a function. Define the *image space of*  $\mathcal{P}$  *under* f, notation  $f_*(\mathcal{P})$ , as the triple consisting of

- 1.  $f(\Omega)$ ;

- 2.  $\{X \in 2^{f(\Omega)} \mid f^{-1}(X) \in \Omega_{\mathcal{P}}\};\$

- 3.  $\mathbf{P} \circ f^{-1}$ .

It is not difficult to show that  $f_*(\mathcal{P})$  is a probability space indeed. If  $\mathcal{P}$  is discrete, then so is  $f_*(\mathcal{P})$ . We write  $f_*(\mu)$  to indicate the distribution function associated to  $f_*(\mathcal{P}_{\mu})$ , where  $\mathcal{P}_{\mu}$  is the distribution function associated to  $\mu$ .

**Lemma 2.9** The operations \* and  $\circ$  commute, that is  $(g \circ f)_* = g_* \circ f_*$  for all functions  $f: X \to Y$  and  $g: Y \to Z$ .

The below definition gives two formulations for choosing a probability space with a certain probability.

- **Definition 2.10** 1. If  $\{p_i\}_{i \in \mathcal{I}}$  is a collection of reals in [0, 1] such that  $\sum_i p_i = 1$  and  $\mu_i \in \Pi(X_i)$  for all  $i \in \mathcal{I}$ , then  $x \mapsto \sum_i p_i \cdot \mu_i(x)$  is a probability space over  $\bigcup_i X_i$ .

- 2. Let X be a set and  $\mu \in \Pi(\Pi(X))$ . Then  $\mu$  induces a probability distribution  $\mu_F$  on X, given by

$$\mu_F(x) = \sum_{\nu \in \Pi(X)} \mu(\nu) \cdot \nu(x).$$

for all  $x \in X$ . We call  $\mu_F$  the fold of  $\mu$ . The idea is that  $\mu_F$  chooses between all probability distributions the distribution  $\nu$  with probability  $\mu(\nu)$  and then elements x of X with probability  $\nu(x)$ .

**Example 2.11** Let x, y, z denote different elements.

1. If  $f : \{x, y\} \to Y$  for some set Y, then

$$f_*(\lbrace x \mapsto \frac{1}{3}, y \mapsto \frac{2}{3} \rbrace) = \begin{cases} \lbrace f(x) \mapsto 1 \rbrace & \text{if } f(x) = f(y), \\ \lbrace f(x) \mapsto \frac{1}{3}, f(y) \mapsto \frac{2}{3} \rbrace & \text{otherwise;} \end{cases}$$

3. If  $\mu\{x \mapsto \frac{1}{3}, y \mapsto \frac{2}{3}\} = \frac{1}{2}$  and  $\mu\{x \mapsto \frac{1}{2}, z \mapsto \frac{1}{2}\} = \frac{1}{2}$ , then  $\mu_F = \frac{1}{2} \cdot \{x \mapsto \frac{1}{3}, y \mapsto \frac{2}{3}\} + \frac{1}{2} \cdot \{x \mapsto \frac{1}{2}, z \mapsto \frac{1}{2}\}$  $= \{x \mapsto \frac{5}{13}, y \mapsto \frac{1}{2}, z \mapsto \frac{1}{4}\}.$

# 3 Probabilistic probabilistic automata

This section introduces probabilistic automata and their behaviour. Most of the concepts in 3.1 and 3.2 have been taken over from [Seg95]. However, we have reformulated their definitions to a form that we believe is more readable.

#### 3.1 The model

**Definition 3.1** A probabilistic automaton A consists of five components:

- 1. a set  $states_A$  of states;

- 2. a nonempty set  $start_A \subseteq states_A$  of start states;

- 3. an action signature  $sig_A = (ext_A, int_A)$ , consisting of external and internal actions respectively. Then define the set of actions as  $act_A \stackrel{d}{=} ext_A \cup int_A$ ;

- 4. a transition relation  $trans_A \subseteq states_A \times act_A \times \Pi(states_A)$ . We write  $s \xrightarrow{a}_A \mu$  if  $(s, a, \mu) \in trans_A$ ;

- 5. a *task partition tasks*<sub>A</sub>, which is a partial equivalence relation over  $act_A$  with countably many equivalence classes.

Sometimes, a more general definition of probabilistic automata is given by having  $trans_A \subseteq states_A \times \Pi(act_A \times states_A)$ . In this context the probabilistic automata from the definition are called *simple* probabilistic automata.

**Definition 3.2** Let A be a probabilistic automaton. The automaton  $A^-$ , the non-probabilistic variant of A, which behaves like A but discards all probabilistic information, is defined by

- 1.  $states_{A^-} \stackrel{d}{=} states_A;$

- 2.  $start_{A^-} \stackrel{\mathrm{d}}{=} start_A;$

- 3.  $sig_{A^-} \stackrel{\mathrm{d}}{=} sig_A;$

- 4.  $trans_{A^-} \stackrel{d}{=} \{s \stackrel{a}{\to}_{A^-} s' \mid \exists \mu \in \Pi(states_A) [s \stackrel{a}{\to}_A \mu \land \mu(s') > 0\};$

- 5.  $tasks_{A^-} \stackrel{d}{=} tasks_A$ .

**Definition 3.3** For a probabilistic automaton A define  $reach_A$ , the set of *reachable* states of A, by  $reach_A \stackrel{d}{=} reach_{A^-}$ .

**Definition 3.4** Let A be a probabilistic automaton and  $X \subseteq ext_A$ . The restriction of A to X, notation  $A \upharpoonright_X$ , is defined by

- 1.  $states_{A \upharpoonright x} \stackrel{d}{=} states_A;$

- 2.  $start_{A \upharpoonright x} \stackrel{d}{=} start_A;$

- 3.  $sig_{A \upharpoonright X} \stackrel{\mathrm{d}}{=} (X, act_A \setminus X);$

- 4.  $trans_{A \upharpoonright x} \stackrel{d}{=} trans_A;$

- 5.  $tasks_{A \uparrow x} \stackrel{d}{=} tasks_A$ .

**Fact 3.5** For all probabilistic automata A and  $X \subseteq ext_A$  we have  $A^- \upharpoonright_X = (A \upharpoonright_X)^-$ .

**Definition 3.6** Let  $A_1$  and  $A_2$  be two probabilistic automata.

- 1. Then  $A_1$  and  $A_2$  are *compatible* if

- (a)  $int_{A_1} \cap act_{A_2} = \emptyset$ ,  $act_{A_1} \cap int_{A_2} = \emptyset$  and

- (b) for all  $C_1 \in task_{A_1}$ ,  $C_2 \in task_{A_2}$ , either  $C_1 \cap C_2 = \emptyset$  or  $C_1 = C_2$ .

- 2. For  $A_1$  and  $A_2$  compatible define the *parallel composition* of  $A_1$  and  $A_2$ , notation  $A_1 \parallel A_2$ , by

- (a)  $states_{A_1||A_2} = states_{A_1} \times states_{A_2};$

- (b)  $start_{A_1||A_2} = start_{A_1} \times start_{A_2};$

- (c)  $sig_{A_1||A_2} = (ext_{A_1} \cup ext_{A_2}, int_{A_1} \cup int_{A_2});$

- (d)  $trans_{A_1||A_2}$  is the set of triples  $((s_1, s_2), a, \mu_1 \times \mu_2)$  such that for i = 1, 2, if  $a \in act_{A_i}$  then  $(s_i, a, \mu_i) \in trans_{A_i}$ , otherwise  $\mu_i = \{s_i \mapsto 1\}$ ;

- (e)  $tasks_{A_1||A_2} = tasks_{A_1} \cup tasks_{A_2}$ .

Informally, two probabilistic automata synchronize on their common actions and evolve independently on others. Whenever synchronization occurs, the state reached is obtained by choosing a state independently for both probabilistic automata. See Remark 3.24 for a comment on the treatment of task partitions.

# 3.2 The behaviour of probabilistic automata

**Definition 3.7** An execution (execution fragment, trace) of a probabilistic automaton A is an execution (execution fragment, trace) of  $A^-$ . The set of executions (execution fragments, traces) and finite executions (execution fragments, traces) of A are respectively denoted by execs(A)(frags(A), traces(A)) and by  $execs^*(A)$  (frags<sup>\*</sup>(A), traces<sup>\*</sup>(A)).

An execution fragment is the result of resolving both probabilistic and nondeterministic choices. A *probabilistic* execution fragment only resolves the nondeterministic choices. In any state of the probabilistic execution fragment, we choose probabilistically between the enabled transitions. We choose  $\delta$  to obtain a finite execution (with some probability). Each of these executions lead to a Markov chain, which allows us to compute the probabilities on the behaviour obtained by the specific choice of resolving the nondeterminism.

**Definition 3.8** A probabilistic execution fragment E of a probabilistic automaton A consists of three components.

- 1. A state space  $states_E \subseteq frags^*(A) \cup frags^*(A) \cdot \delta$ ;

- 2. A start state  $start_E \in states_E \cap frags^*(A)$ ;

- 3. A transition function  $trans_E : states_E \to \Pi(states_E)$  such that

- (a) for all  $\alpha \in states_E \cap frags^*(A)$  there is a  $\mu_{\alpha} \in \Pi(trans_A(last(\alpha)) \cup \{\delta\})$ satisfying

$$trans_{E}(\alpha)(\alpha\delta) = \mu_{\alpha}(\delta),$$

$$trans_{E}(\alpha)(\alpha as) = \sum_{\nu:(last(\alpha), a, \nu) \in trans_{A}} \mu_{\alpha}(a, \nu) \cdot \nu(s)$$

(b) and for all  $\alpha \in states_E \cap frags^*(A) \cdot \delta$

$trans_E(\alpha)(\alpha) = 1.$

Here  $trans_A(t)$  denotes  $\{(a, \nu) \mid (t, a, \nu) \in trans_A\}$ . Notice that  $trans_E(\alpha)$  indeed is a probability distribution over  $states_E$ . The idea is that  $\mu_{\alpha}$  chooses probabilistically between all transitions starting from  $last(\alpha)$  and  $\delta$ . Furthermore, we require that every state in  $states_E$  is reachable from  $start_E$  via the relation  $\{(\alpha, \alpha') \mid trans_E(\alpha)(\alpha') > 0\}$ .

A probabilistic execution E is a probabilistic execution fragment such that  $start_E \in start_A$ . The set of probabilistic execution (fragments) is denoted by pexecs(A) (pfrags(A)).

**Fact 3.9** 1. A probabilistic execution fragment E is a Markov chain over states<sub>E</sub>.

2. The state space states E is countable, due to the reachability condition.

A Markov chain allows us to compute the probability of reaching a state. Hence, we can compute the probability on (certain) sets of execution fragments, given a probabilistic execution. The following definition associates a probability space to a probabilistic execution fragment.

**Definition 3.10** The associated probability space  $E = (\Omega_E, \mathcal{F}_E, \mathbf{P}_E)$  of a probabilistic execution fragment E is defined by

- 1.  $\Omega_E$  is the limit closure of  $states_E$  under the prefix order  $\sqsubseteq$ ;

- 2.  $\mathcal{F}_E$  is the smallest  $\sigma$ -field that subsumes the set  $\{C_\alpha \mid \alpha \in states_E\}$ . Here  $C_\alpha$  is the cone on  $\alpha$ , defined by  $C_\alpha \stackrel{\mathrm{d}}{=} \{\beta \in \Omega_E \mid \alpha \sqsubseteq \beta\};$

- 3.  $\mathbf{P}_E$  is the unique measure on  $\mathcal{F}_E$  such that  $\mathbf{P}_E[C_\alpha]$  is the product of the probabilities on the (shortest) path starting in the start state of E and leading to  $\alpha$ . So  $\mathbf{P}_E[C_{s_0a_1s_1a_2...a_ns_n}] = trans_E(s_0) \cdot trans_E(s_0a_1s_1) \cdots trans_E(s_0a_1s_1...a_ns_n)$ .

The fact that  $(\Omega_E, \mathcal{F}_E, \mathbf{P}_E)$  is well-defined follows from standard measure theory arguments, see in [Seg95] for a similar case and [Hal50] for a more general treatment. When no confusion arises, we denote both the probabilistic execution fragment and its associated probability space by E.

The following definition allows us to compute the probability on (certain) sets of traces given a probabilistic execution.

**Definition 3.11** The *trace distribution* H of a probabilistic execution fragment E of A is the probability space given by

- 1.  $\Omega_H = ext_A^* \cup ext_A^\infty;$

- 2.  $\mathcal{F}_H$  is the smallest  $\sigma$ -field that subsumes the set  $\{C_\alpha \mid \alpha \in ext^*(A)\}$ . Now  $C_\alpha \stackrel{\mathrm{d}}{=} \{\beta \in \Omega_H \mid \alpha \sqsubseteq \beta\};$

3.

$$\mathbf{P}_H = \mathbf{P}_E \circ trace^{-1}$$

, that is  $\mathbf{P}_H[X] = \mathbf{P}_E[trace^{-1}(X)]$  for all  $X \in \mathcal{F}_H$ .

The fact that  $(\Omega_H, \mathcal{F}_H, \mathbf{P}_H)$  is well-defined follows from the fact that  $X \in \mathcal{F}_H \implies trace^{-1}(X) \in \mathcal{F}_E$ , see [PSL97] and [Hal50]. Notice that the probability space above is quite similar to the image space  $trace_*(E)$ , but that it may contain some more elements, which all have probability zero.

**Notation 3.12** The set of trace distributions of A is denoted by trdistr(A). If  $trdistr(A) \subseteq trdistr(B)$  then we write  $A \sqsubseteq_{TD} B$ . It is obvious that  $\sqsubseteq_{TD}$  is a partial order.

# 3.3 Step refinements and hyperstep refinements

This section introduces two new probabilistic simulation relations, viz. probabilistic step refinements and probabilistic hyperstep refinements. We show that these are sound for trace distribution inclusion.<sup>2</sup>

#### **Probabilistic step refinements**

**Definition 3.13** Let A, B be two probabilistic automata with the same external actions. A probabilistic step refinement is a function  $r : states_A \rightarrow states_B$  such that:

- 1. for all  $s \in start_A, r(s) \in start_B$ ;

- 2. for all  $s \in reach_A, a \in act_A, \mu \in \Pi(states_A)$ , if  $s \xrightarrow{a}_A \mu$  then either of the following conditions is met:

- (a)  $r(s) \xrightarrow{a}_{B} r_{*}(\mu)$  or

- (b)  $a \in int_A \wedge r(s) \xrightarrow{a'}_B r_*(\mu)$  for some  $a' \in int_B$  or

- (c)  $a \in int_A \wedge r_*(\mu) = \{r(s) \mapsto 1\}.$

We write  $A \sqsubseteq_{\text{PSR}} B$  if there is a probabilistic step refinement between A and B. Remark that the third condition is equivalent to  $a \in int_A \land \forall s' \in \text{supp}(\mu)[r(s') = r(s)].$

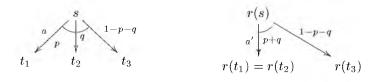

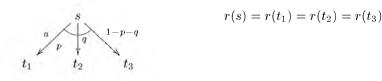

**Example 3.14** The following diagrams illustrate three typical situations that may occur if r is a probabilistic step refinement from A to B. The transitions on the left are steps of the probabilistic automaton A, those on the right of B.

Condition 2a. and  $r(t_1) \neq r(t_2) \neq r(t_3) \neq r(t_1)$ :

Condition 2b.,  $a \in int_A$ ,  $a' \in int_B$  and  $r(t_1) = r(t_2) \neq r(t_3)$ :

Condition 2c. and  $a \in int_A$ :

<sup>&</sup>lt;sup>2</sup>Concerning the terminology, we use the prefix *hyper* to refer to a probabilistic simulation of type  $states_A \times \Pi(states_B)$ . Our simulation relations abstract from internal computation, so one could could add the adjective "weak" to their names.

**Fact 3.15** If r is a probabilistic step refinement from A to B then it is a step refinement from  $A^-$  to  $B^-$  and a probabilistic step refinement from  $A \upharpoonright_X$  to  $B \upharpoonright_X$  for all  $X \subseteq ext_A$ .

**Theorem 3.16** The relation  $\sqsubseteq_{PSR}$  is a preorder, i.e. it is reflexive and transitive.

PROOF: Reflexivity is obvious. For transitivity, suppose r is a probabilistic refinement from A to B and u is one from B to C. We claim that  $u \circ r$  is a probabilistic step refinement from A to C. In fact the proof, which is spelled out below, is similar to the proof of transitivity for non-probabilistic step refinements. We only need that  $u_* \circ r_* = (u \circ r)_*$ .

**condition 1** Obviously, if  $s \in start_A$ , then  $(u \circ r)(s) \in start_C$ .

**condition 2** Assume  $s \xrightarrow{a}_{A} \mu$ . As r is a probabilistic step refinement from A to B we have the following cases.

- 1.  $a \in int_A$  and  $r_*(\mu) = \{r(s) \mapsto 1\}$ . Then  $(u_* \circ r_*)(\mu) = u_*(\{r(s) \mapsto 1\}) = u_*(\{r(s) \mapsto 1\}) = \{u(r(s)) \mapsto 1\};$

- 2.  $r(s) \xrightarrow{a}_{B} r_{*}(\mu)$ . As *u* is a probabilistic step refinement we are in either of the following cases:

- (a)  $a \in int_B$  and  $u_*(r_*(\mu)) = \{u(r(s)) \mapsto 1\}$ . Then  $a \in int_A$  by  $ext_A = ext_B$ and  $(u \circ r)_*(\mu) = \{u(r(s)) \mapsto 1\}$  by  $u_* \circ r_* = u \circ r$ . Therefore,  $u \circ r$  is a probabilistic step refinement from A to C;.

- (b)  $u(r(s)) \xrightarrow{a}_{C} u_*(r_*(\mu))$ . Then  $(u \circ r)(s) \xrightarrow{a}_{C} (u \circ r)_*(\mu)$  by  $(u \circ r)_* = u_* \circ r_*$  and therefore  $u \circ r$  is a probabilistic step refinement from A to C;

- (c)  $u(r(s)) \xrightarrow{a''}_{C} u_*(r_*(\mu))$  and  $a' \in int_B$  and  $a'' \in int_C$ : similarly to the case above;

- 3.  $r(s) \xrightarrow{a'}_{B} r_*(\mu), a \in int_A \text{ and } a' \in int_B$ : similarly to the above case.

Therefore,  $u \circ r$  is a probabilistic step refinement from A to C.  $\Box$

#### **Probabilistic hyperstep refinements**

**Definition 3.17** Let X, Y be sets and  $R \subseteq X \times \Pi(Y)$ . Define the *lifting of* R to  $\Pi(X) \times \Pi(Y)$ , notation  $R_{**}$ , as the set of pairs  $(\mu, \nu) \in \Pi(X) \times \Pi(Y)$  such that there exists a choice function  $r : \operatorname{supp}(\mu) \to \Pi(Y)$  for R, (i.e. a function such that  $(x, r(x)) \in R$  for all  $x \in \operatorname{supp}(\mu)$ ) satisfying

$$\sum_{x \in \text{supp}(\mu)} \mu(x) \cdot r(x) = \nu.$$

The idea is that we can obtain  $\nu$  by choosing the probability distribution r(x), which should be related to x, with probability  $\mu(x)$ . The above sum is a probability distribution by Definition 2.10.

**Fact 3.18** If R is a function – considered as a set of pairs – then so is  $R_{**}$  and for all  $\mu \in \Pi(X)$

$$R_{**}(\mu) = \sum_{x \in X} \mu(x) \cdot R(x) = \{R(x) \mapsto \mu(x) \mid x \in X\}_F.$$

**Example 3.19** Given a probabilistic automaton A and an action  $a \in act_A$ , we can lift the relation  $\xrightarrow{a}$  over  $states_A \times \Pi(states_A)$  to the relation  $\xrightarrow{a}_{**}$  over  $\Pi(states_A) \times \Pi(states_A)$ . For instance, if  $s_1 \xrightarrow{a} \mu_1$ ,  $s_2 \xrightarrow{a} \mu_2$  and  $s_1 \neq s_2$ , then

$$\{s_1 \mapsto \frac{1}{3}, s_2 \mapsto \frac{2}{3}\} \xrightarrow{a} ** \frac{1}{3} \cdot \mu_1 + \frac{2}{3} \cdot \mu_2.$$

Intuitively, if  $s_1 \xrightarrow{a} \mu_1$ ,  $s_2 \xrightarrow{a} \mu_2$  and the probability on being in  $s_1$  is  $\frac{1}{3}$  and on being in  $s_2$  is  $\frac{2}{3}$ , then we choose the next state according to  $\mu_1$  with probability  $\frac{1}{3}$  and according to  $\mu_2$  with probability  $\frac{2}{3}$ . If there is another *a*-transition, say  $s_2 \xrightarrow{a} \nu$ , then we can also choose the next state according to  $s_1$  with probability  $\frac{1}{3}$  and according to  $\nu$  with probability  $\frac{2}{3}$ . Hence

$$\{s_1 \mapsto \frac{1}{3}, s_2 \mapsto \frac{2}{3}\} \xrightarrow{a} * * \frac{1}{3} \cdot \mu_1 + \frac{2}{3} \cdot \nu.$$

We do *not* have

$$\{s_1 \mapsto \frac{1}{3}, s_2 \mapsto \frac{2}{3}\} \xrightarrow{a} ** \frac{1}{3} \cdot \mu_1 + \frac{1}{3} \cdot \mu_2 + \frac{1}{3} \cdot \nu.$$

Furthermore, if the sequence  $s_1, s_2, \ldots$  is such that  $s_i \xrightarrow{a} \mu_i$  and  $s_i \neq s_j$  for  $i \neq j$ , then we have that

$$\{s_i \mapsto \frac{1}{2^i} \mid i \in \mathbb{N}\} \xrightarrow{a}_{**} \sum_{i \in \mathbb{N}} \frac{1}{2^i} \cdot \mu_i.$$

Notice that in fact the tuple  $(\Pi(states_A), \{\{s \mapsto 1\} \mid s \in startA\}, sig_A, \rightarrow_{A^{**}})$  is in fact a non-probabilistic automaton. However, the moves of this automaton do not coincide with the lifting of the moves of the automaton A.

**Definition 3.20** Let A, B be two probabilistic automata with the same external actions. A probabilistic hyperstep refinement is a function  $R : states_A \to \Pi(states_B)$  such that:

- 1. for all  $s \in start_A$ ,  $R(s) = \{s' \mapsto 1\}$  for some  $s' \in start_B$ ;

- 2. for all  $s \in reach_A$ ,  $a \in act_A$  and  $\mu \in \Pi(states_A)$ , if  $s \xrightarrow{a}_A \mu$  then either of the following conditions hold

- (a)  $R(s) \xrightarrow{a}_{B^{**}} R_{**}(\mu)$  or

- (b)  $a \in int_A \land R(s) \xrightarrow{a'}_{B^{**}} R_{**}(\mu)$  for some  $a' \in int_B$  or

- (c)  $a \in int_A \wedge R(s) = R_{**}(\mu)$ .

We write  $A \sqsubseteq_{\text{PHSR}} B$  if there is a probabilistic hyperstep refinement between A and B.

The idea of the above notion is the following. If  $s \stackrel{a}{\to}_A \mu$  and  $R(s) = \nu$ , then the state  $s \in states_A$  is simulated by the state  $t \in states_B$  with probability  $\nu(t)$ . Consider case 2a. We require that, for t with  $\nu(t) > 0$ , there is a  $\nu'_t$  such that  $t \stackrel{a}{\to}_B \nu'_t$  and this transition is simulated with probability  $\nu(t)$  too: the requirement implies  $\nu \stackrel{a}{\to}_{B^{**}} \sum_t \nu(t) \cdot \nu'_t = \vartheta$  by definition of  $\to_{**}$ . As R is a simulation relation,  $\mu$  should be related to  $\vartheta$ , which means  $R_{**}(\mu) = \vartheta$ .

The following theorem establishes some relations between the preorders defined in this section. It implies that the simulations  $\sqsubseteq_{\text{PSR}}$  and  $\sqsubseteq_{\text{PHSR}}$  are sound for trace distribution inclusion. The proof is based on the soundness result for the simulation relation  $\sqsubseteq_{\text{PFS}}$  from [Seg95], where  $A \sqsubseteq_{\text{PFS}} B$  means that there is a probabilistic forward simulation from A to B. **Theorem 3.21** Let A, B be probabilistic automata with the same external actions.

- 1. If  $A \sqsubseteq_{\text{PSR}} B$  then  $A \sqsubseteq_{\text{PHSR}} B$ ;

- 2. if  $A \sqsubseteq_{\text{PHSR}} B$  then  $A \sqsubseteq_{\text{PFS}} B$ ;

- 3. if  $A \sqsubseteq_{\text{PFS}} B$  then  $A \sqsubseteq_{\text{TD}} B$ .

## 3.4 Fairness in probabilistic automata

This section introduces notions of fairness for executions, traces, probabilistic executions and trace distributions. We state a result that concludes inclusion of fair trace distributions from fair trace inclusion via a probabilistic step refinement.

**Definition 3.22** Let A be a (probabilistic) automaton.

- 1. An execution of A is called *(weakly)* fair if the following conditions hold for each class C of  $tasks_A$ :

- (a) if α is finite then none of the actions in C is enabled in the final state of α;

- (b) if  $\alpha$  is infinite, then  $\alpha$  contains either infinitely many actions from C or infinitely many occurrences of states in which no action in C is enabled;

2. a trace of A is *fair* in A if it is the trace of a fair execution.

The sets of fair executions and fair traces of A are denoted by fexecs(A) and ftraces(A) respectively.

**Lemma 3.23** Let  $A_1, A_2$  be (probabilistic) automata and let  $\alpha$  be an execution of  $A_1 \parallel A_2$ . If the projections of  $\alpha$  on A and B are both fair, then  $\alpha$  is fair.

PROOF: Let  $\alpha = s_0 a_1 s_1 \ldots = (s_{0,1}, s_{0,2}) a_1(s_{1,1}, s_{1,2}) a_2(s_{2,1}, s_{2,2}) a_3 \ldots$  be an execution of  $A_1 \parallel A_2$ . Let C be a task class from  $tasks_{A_i \parallel A_2}$ . Then  $C \in tasks_{A_i}$ , for i = 1 or i = 2. We prove that  $\alpha$  is fair with respect to C by distinguishing between the following cases.

- 1. If  $\alpha$  is finite, then the projection of  $\alpha$  on  $A_i$  is finite. Then C is not enabled in the last state of the projection, so neither is C is enabled in the last state of  $\alpha$ . Therefore,  $\alpha$  is fair with respect to C.

- 2. If  $\alpha$  is infinite, then distinguish between two more cases: If the projection of  $\alpha$  to  $A_i$  is finite, then let  $s_{k,i}$  be its last state. Then C is not enabled in  $s_{k,i}$ . The execution  $\alpha$  does not contain actions from  $A_i$  after  $s_k$ . More precisely,  $a_n \notin act_A$  for  $n \geq k$ . But then  $s_{k,i} = s_{n,i}$  for all  $n \geq k$ , which implies that C is disabled in  $s_n$  for all  $n \geq k$ . So, C is infinitely often disabled. Therefore,  $\alpha$  is fair with respect to C.

If the projection of  $\alpha$  to  $A_i$  is infinite, then either the projection contains infinitely many actions in C, in which case  $\alpha$  contains infinitely many infinitely many actions in C, or C is infinitely often disabled in the projection, in which case it is infinitely often disabled in  $\alpha$ . Therefore,  $\alpha$  is fair with respect to C. **Remark 3.24** The definitions of compatible and of task partition we have given here induce a notion of fairness which is different from that of literature, see for example [Lyn96]. In particular, our notion of fairness does not satisfy the properties with respect to compositionality from literature, viz. the converse of 3.23. However, Proposition 7.6 shows that the automaton model P of the protocol does meet this property. The same trivially holds for the other automata defined in this report.

**Lemma 3.25** Let  $E = (\Omega_E, \mathcal{F}_E, \mathbf{P}_E)$  be a probabilistic execution of a probabilistic automaton A. Then fexecs $(A) \cap \Omega_E \in \mathcal{F}_E$ .

**PROOF:** Similar to the proof of the corresponding result in [PSL97].  $\Box$

- **Definition 3.26** 1. A probabilistic execution  $E = (\Omega_E, \mathcal{F}_E, \mathbf{P}_E)$  is called *fair* if  $\mathbf{P}_E[fexces(A) \cap \Omega_E] = 1$

- 2. A trace distribution H is called *fair* if it is the distribution of a fair execution.

**Notation 3.27** The set of fair probabilistic executions of A is denoted by fpexecs(A) and the set of fair trace distributions by ftrdistr(A). If  $ftrdistr(A) \subseteq ftrdistr(B)$  then we write  $A \sqsubseteq_{\text{FTD}} B$ . It is obvious that  $\sqsubseteq_{\text{FTD}}$  is a partial order.

## Fairness and probabilistic step refinements

**Lemma 3.28** Let A and B be probabilistic automata with the same external actions. Let  $r : states_A \rightarrow states_B$  be a probabilistic step refinement Then r induces a relation  $\overline{r} \subseteq frags(A) \times frags(B)$  as follows: if  $\alpha = s_0 a_1 s_1 \ldots \in fragsA$ , index( $\alpha$ ) is the index set of  $\alpha$ ,  $\beta = t_0 b_1 t_1 b_2 \ldots \in frags(B)$  and index( $\beta$ ) is the index set of  $\beta$ , then  $\alpha \overline{r} \beta$  holds if and only if there exists a surjective, nondecreasing index mapping  $m : index(\alpha) \rightarrow index(\beta)$ , such that for all  $i \in index(\alpha)$ ,  $j \in index(\beta)$ ,

- 1. m(0) = 0;

- 2.  $r(s_i) = t_{m(i)};$

- 3. if i > 0 then either of the following conditions holds

- (a)  $a_i = b_{m(i)} \wedge m(i) = m(i-1) + 1$  or

- (b)  $a_i \in int_A \land b_{m(i)} \in int_B \land m(i) = m(i-1) + 1$  or

- (c)  $a_i \in int_A \wedge m(i) = m(i-1)$ .

**Fact 3.29** For each probabilistic step refinement r, the relation  $\tilde{r}$  has the following properties: For all  $\alpha \in frags(A)$  and  $\beta \in frags(B)$

- 1.  $\alpha \tilde{r}\beta \implies \ln \alpha \ge \ln \beta;$

- 2.  $\alpha \tilde{r}\beta \implies trace(\alpha) = trace(\beta)$ .

**Claim 3.30** ([SV99a]) Let A and B be probabilistic automata with the same external actions and let  $r : states_A \rightarrow states_B$  be a probabilistic step refinement. Then rinduces a function  $\tilde{r} : pfrags(A) \rightarrow pfrags(B)$  with the following properties:

- 1. For all  $E \in frags(A)$ , E and  $\tilde{r}(E)$  have the same trace distribution;

- 2. Assume that  $\forall \alpha \in frags(A), \beta \in frags(B)[\alpha \text{ is fair } \land \alpha \tilde{r}\beta \implies \beta \text{ is fair}].$ Then  $\forall E \in pfrags(A)[E \text{ is fair } \implies \tilde{r}(E) \text{ is fair}].$

**Claim 3.31** ([SV99a]) Let A and B be probabilistic automata with the same external actions and let  $r : states_A \rightarrow states_B$  be a probabilistic step refinement.

- 1.  $A \sqsubseteq_{\text{TD}} B$ .

- 2. If  $\forall \alpha \in frags(A), \beta \in frags(B)[\alpha \text{ is fair } \land \alpha \tilde{r}\beta \implies \beta \text{ is fair}], \text{ then } A \sqsubseteq_{\text{FTD}} B.$

# 4 Root contention in IEEE 1394

The IEEE 1394 protocol is a high performance serial bus protocol, developed for interconnecting consumer equipment such as PCs, VCRs and CD players. The lowest level of this protocol runs a phase, called the Tree Identify Phase, which elects a leader among the components. The leader serves as a bus manager in subsequent phases of the protocol.

The components and their connections are represented respectively as nodes and edges in an undirected graph. In the Tree Identify Phase, the protocol checks whether the graph is a(n undirected) tree and, if so, it identifies a root c.q. leader. The root is elected by directing all edges of the tree. The nodes, starting with the leaves, send requests for being a child, that is to direct the edge from the sender (c.q. child) to the receiver (c.q. parent). Then they wait for acknowledgments.

If all edges but one have been directed, a situation called *root contention* may occur. Two nodes are in root contention if they have both sent a request to each other. In this situation, it is not clear which of them should be the root. At this moment a part of the protocol is executed which resolves this root contention. The aim of this paper is to verify this part of IEEE 1394 formally.

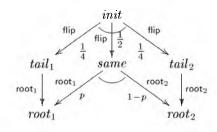

Informally, the part of IEEE 1394 [IEE96] that solves root contention is described as follows. A process in root contention first flips a coin. If head comes up, then it waits a short time between 0.76 and  $0.80\mu s$  (micro seconds). If tail comes up, then it waits a long time; between 1.60 and  $1.64\mu s^{-3}$  Then the processes, regardless the values of their coins, check whether input has arrived. If so – then this can only be a request and the process has not yet sent one – the process sends an acknowledgment and declares itself root. If no input has arrived, then the process sends a request itself and waits for reply. If it receives an acknowledgment then it declares itself child. If it receives a request, – then both processes have sent requests and are in root contention again – the procedure starts all over again. The delay on the communication is 0.22 nano seconds per meter and the communication wires are at most 16 meter.

Informally, the processes in root contention behave as follows. The protocol elects the slowest process as root. This is so because the slower process receives a request before it checks its input and then becomes the root. Therefore, if one of the processes' coin flips yields head and the other yields tail, the tail process is elected as root. If the outcomes of both coin flips are the same then the the processes flip check input and send requests almost simultaneously. Then they both send and receive requests, so root contention occurs again. However, it can be the case that one of the processes is somewhat faster that the other, e.g. if one process takes a delay of  $0.76\mu s$  and the other of 0.80. The the first process receives a request when checking its input. As it has not sent a request, it becomes the root. Which of the two scenario's is actually carried out depends on physical circumstances such as temperature and processor speed.

The key idea of the protocol is that, eventually the coin flips in both processes will yield a different result with probability one: the probability that the first n

<sup>&</sup>lt;sup>3</sup>These figures have been taken from the IEEE 1394a standard [IEE98]; the IEEE 1394 standard [IEE96] provides respectively 0.26, 0.30, 0.60 and  $0.64 \mu s$ .

coin flips are the same is  $\frac{1}{2^n}$ . Therefore, the probability that eventually a root is elected equals one.

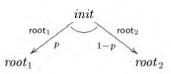

# 4.1 The probabilistic automaton specification of root contention

This section presents an automaton specification of the root contention protocol in IEEE 1394. We firstly specify the automaton in precondition-effect style and then we explain the model informally.

## Choices in the model

As a first approach to IEEE 1394, we use an untimed model, in which the passage of a time unit time is modeled by a discrete action tick. We observe that the long delay, between 1.60 and  $1.64\mu s$ , is almost twice as long as the short delay, between 0.76 and  $0.80\mu s$ . Therefore, we model the short delay as the passage of one time unit and the long delay as the passage of two time units.

As time is a global notion, which elapses with the same speed for both processes, the processes should synchronize on tick actions. This approach is similar to the treatment of time in the timed automaton model from [LV96].

The delay on the communication channels, 0.22 nano seconds per meter is relatively small when compared to the delays mentioned above. We model the communication between the processes by instantaneous actions.

## The model

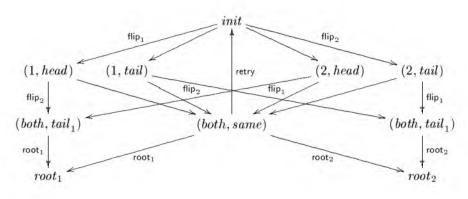

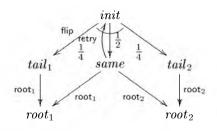

As root contention only occurs in two (adjacent) nodes of the network the specification discards all other nodes and only describes the two processes  $P_1$  and  $P_2$  in root contention. The protocol specification P is defined by

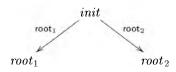

$P \stackrel{\mathrm{d}}{=} (P_1 \parallel P_2) \upharpoonright_{\mathsf{root}_1, \mathsf{root}_2}.$

A

Below the specification of  $P_i$  is given in precondition-effect style. Let  $P_j$  be the other process, i.e.  $i, j \in \{1, 2\}, i \neq j$ . A more intuitive explanation follows.

We define an auxiliary automaton  $P_{flip}$  for technical reasons in the correctness proof.

$$P_{flip} \stackrel{\text{d}}{=} (P_1 \parallel P_2) \restriction_{\mathsf{flip}_1, \mathsf{flip}_2, \mathsf{root}_1, \mathsf{root}_2}.$$

| variables               | range                               | initially |

|-------------------------|-------------------------------------|-----------|

| $status_i$              | init, waiting, checked, root, child | init      |

| $coin_i$                | head, tail                          |           |

| $\mathrm{clock}_i$      | $0, 1, 2, \infty$                   | 0         |

| $delay_i$               | 1, 2                                |           |

| $\operatorname{in}_i$   | empty, ack, req                     | empty     |

| $\operatorname{port}_i$ | empty, ack, req                     | empty     |

| $\operatorname{sent}_i$ | empty, ack, req                     | empty     |

The **external actions** of  $P_i$  are flip<sub>i</sub>, tick, root<sub>i</sub>, send<sub>i</sub>(*req*), send<sub>i</sub>(*ack*), send<sub>j</sub>(*req*) and send<sub>j</sub>(*ack*) and the **internal actions** poll\_once<sub>i</sub>, poll\_many<sub>i</sub>, child<sub>i</sub> and retry<sub>i</sub>. The **task partition** consists of two classes, {tick} and {flip<sub>i</sub>, poll\_once<sub>i</sub>, poll\_many<sub>i</sub>, send<sub>i</sub>(*req*), send<sub>i</sub>(*ack*), root<sub>i</sub>, child<sub>i</sub>, retry<sub>i</sub>}.

| $ \begin{array}{ccc} {\rm flip}_i & {\rm status}_i = init & {\rm status}_i := waiting \\ & {\rm coin}_i := \begin{cases} head & \frac{1}{2} \\ tail & \frac{1}{2} \\ tail & \frac{1}{2} \\ \\ tick & {\rm cock}_i := head \\ \\ {\rm then} \; delay_i := 1 \\ \\ else\; delay_i := 2 \\ {\rm fi} \\ \\ \\ {\rm tick} & {\rm status}_i = waiting \wedge \\ \\ {\rm clock}_i < delay_i \\ \\ \\ {\rm port}_i = empty \wedge \\ \\ {\rm port}_i = empty \wedge \\ \\ {\rm sent}_i = req \\ \\ \\ \\ {\rm tick} & {\rm status}_i = root \vee \\ \\ {\rm status}_i = child \\ \\ {\rm status}_i = child \\ \\ {\rm status}_i = child \\ \\ \\ {\rm clock}_i := delay_i \wedge \\ \\ {\rm in}_i := port_i \\ \\ {\rm in}_i := port_i \\ \\ {\rm in}_i := empty \wedge \\ \\ {\rm sent}_i = empty \wedge \\ \\ {\rm sent}_i = empty \wedge \\ \\ {\rm sent}_i = req \\ \\ \\ \\ \\ \\ {\rm sent}_i = req \\ \\ \\ \\ \\ {\rm send}_i(req) & {\rm status}_i = checked \wedge \\ \\ {\rm in}_i = empty \wedge \\ \\ {\rm sent}_i = req \\ \\ \\ \\ \\ \\ \\ \\ \\ {\rm sent}_i = empty \wedge \\ \\ \\ {\rm sent}_i = req \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | action                 | precondition                                 | effect                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------|-----------------------------------------------------------------------------------|

| $\begin{aligned} & \mbox{if } \cosh_i = head \\ & \mbox{then } \operatorname{delay}_i := 1 \\ & \mbox{else} \operatorname{delay}_i := 2 \\ & \mbox{fi} \end{aligned} \\ \hline \mbox{tick} & \mbox{status}_i = waiting \wedge \\ & \mbox{clock}_i <= \operatorname{clock}_i + 1 \\ & \mbox{in}_i = empty \wedge \\ & \mbox{sent}_i = req \end{aligned} \\ \hline \mbox{tick} & \mbox{status}_i = child \\ & \mbox{status}_i := checked \wedge \\ & \mbox{status}_i := checked \wedge \\ & \mbox{status}_i := checked \wedge \\ & \mbox{in}_i := port_i \\ & \mbox{in}_i := port_i \\ & \mbox{in}_i := empty \\ \hline \mbox{poll\_many}_i & \mbox{status}_i = checked \wedge \\ & \mbox{in}_i := empty \\ \hline \mbox{poll\_many}_i & \mbox{status}_i = checked \wedge \\ & \mbox{in}_i := empty \\ \hline \mbox{sent}_i = req \\ \hline \mbox{sent}_i = req \\ \hline \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \ \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = ack \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{status}_i = child \\ & \mbox{in}_i = req \\ \hline \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = mpt \\ & \mbox{sent}_i = mpt \\ & \mbox{sent}_i = mpt \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ & \mbox{sent}_i = empty \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = mpty \\ & \mbox{sent}$                                                                                                                                                                                                                                                                                                                          | flip <sub>i</sub>      | $status_i = init$                            | $status_i := waiting$                                                             |

| $\begin{aligned} & \mbox{if } \cosh_i = head \\ & \mbox{then } \operatorname{delay}_i := 1 \\ & \mbox{else} \operatorname{delay}_i := 2 \\ & \mbox{fi} \end{aligned} \\ \hline \mbox{tick} & \mbox{status}_i = waiting \wedge \\ & \mbox{clock}_i <= \operatorname{clock}_i + 1 \\ & \mbox{in}_i = empty \wedge \\ & \mbox{sent}_i = req \end{aligned} \\ \hline \mbox{tick} & \mbox{status}_i = child \\ & \mbox{status}_i := checked \wedge \\ & \mbox{status}_i := checked \wedge \\ & \mbox{status}_i := checked \wedge \\ & \mbox{in}_i := port_i \\ & \mbox{in}_i := port_i \\ & \mbox{in}_i := empty \\ \hline \mbox{poll\_many}_i & \mbox{status}_i = checked \wedge \\ & \mbox{in}_i := empty \\ \hline \mbox{poll\_many}_i & \mbox{status}_i = checked \wedge \\ & \mbox{in}_i := empty \\ \hline \mbox{sent}_i = req \\ \hline \mbox{sent}_i = req \\ \hline \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \ \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = ack \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{status}_i = child \\ & \mbox{in}_i = req \\ \hline \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = mpt \\ & \mbox{sent}_i = mpt \\ & \mbox{sent}_i = mpt \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ & \mbox{sent}_i = empty \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = mpty \\ & \mbox{sent}$                                                                                                                                                                                                                                                                                                                          |                        |                                              | $\int head \frac{1}{2}$                                                           |

| $\begin{aligned} & \mbox{if } \cosh_i = head \\ & \mbox{then } \operatorname{delay}_i := 1 \\ & \mbox{else} \operatorname{delay}_i := 2 \\ & \mbox{fi} \end{aligned} \\ \hline \mbox{tick} & \mbox{status}_i = waiting \wedge \\ & \mbox{clock}_i <= \operatorname{clock}_i + 1 \\ & \mbox{in}_i = empty \wedge \\ & \mbox{sent}_i = req \end{aligned} \\ \hline \mbox{tick} & \mbox{status}_i = child \\ & \mbox{status}_i := checked \wedge \\ & \mbox{status}_i := checked \wedge \\ & \mbox{status}_i := checked \wedge \\ & \mbox{in}_i := port_i \\ & \mbox{in}_i := port_i \\ & \mbox{in}_i := empty \\ \hline \mbox{poll\_many}_i & \mbox{status}_i = checked \wedge \\ & \mbox{in}_i := empty \\ \hline \mbox{poll\_many}_i & \mbox{status}_i = checked \wedge \\ & \mbox{in}_i := empty \\ \hline \mbox{sent}_i = req \\ \hline \mbox{sent}_i = req \\ \hline \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = empty \\ \hline \ \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{sent}_i = ack \\ \hline \mbox{ret}_i & \mbox{status}_i = checked \wedge \\ & \mbox{status}_i = child \\ & \mbox{in}_i = req \\ \hline \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = mpt \\ & \mbox{sent}_i = mpt \\ & \mbox{sent}_i = mpt \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = req \\ & \mbox{sent}_i = empty \\ & \mbox{sent}_i = empty \\ & \mbox{sent}_i = empty \\ \hline \mbox{sent}_i = mpty \\ & \mbox{sent}$                                                                                                                                                                                                                                                                                                                          |                        |                                              | $\operatorname{coin}_i := \left\{ \begin{array}{c} 2\\ tail \end{array} \right\}$ |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                              |                                                                                   |

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |                                              |                                                                                   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                              | · •                                                                               |

| tickstatus_i = waiting \land<br>clock_i < delay_iclock_i := clock_i + 1<br>clock_i < delay_itickstatus_i = checked \land<br>in_i = empty \land<br>port_i = empty \land<br>sent_i = reqclock_i := clock_i + 1<br>else clock_i := clo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                                              |                                                                                   |

| $\begin{array}{c c c c c c c c c } \hline {\rm clock}_i < {\rm delay}_i \\ \hline {\rm tick} & {\rm status}_i = checked \wedge & {\rm clock}_i := {\rm clock}_i + 1 \\ & {\rm in}_i = empty \wedge & \\ & {\rm port}_i = empty \wedge & \\ & {\rm sent}_i = req \\ \hline {\rm tick} & {\rm status}_i = root \vee & {\rm if \ clock}_i < 2 \\ & {\rm then \ clock}_i := {\rm clock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i + 1 \\ & {\rm else \ clock}_i := {\rm cock}_i \\ & {\rm in}_i := {\rm empty} \wedge \\ & {\rm sent}_i = {\rm empty} \\ & {\rm sent}_i = {\rm checked} \wedge \\ & {\rm status}_i = {\rm checked} \wedge \\ & {\rm status}_i = {\rm checked} \wedge \\ & {\rm status}_i := {\rm coid} \\ & {\rm in}_i = {\rm ack} \\ \hline & {\rm clock}_i := 0 \\ & {\rm sent}_i = {\rm checked} \wedge \\ & {\rm status}_i = {\rm checked} \wedge \\ & {\rm status}_i := {\rm child} \\ & {\rm in}_i = {\rm req} \\ & {\rm sent}_i := {\rm empty} \\ & {\rm sen$                                                                                                                                                                                                                                                                                                                     | tick                   | $status = waiting \Lambda$                   |                                                                                   |

| $\begin{tabular}{ c c c c c } \hline tick & status_i = checked \land & clock_i := clock_i + 1 \\ & in_i = empty \land & \\ & port_i = empty \land & \\ & sent_i = req & & & \\ \hline tick & status_i = root \lor & if clock_i < 2 & \\ & status_i = child & & then clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := clock_i + 1 & \\ & else clock_i := 0 & \\ & sent_i = empty & \\ & sent_i = empty & \\ & sent_i := empty & \\ & sent_i := empty & \\ & sent_i = checked \land & \\ & status_i := checked \land & \\ & s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LICK                   | - 0                                          | $\operatorname{clock}_i := \operatorname{clock}_i + 1$                            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tick                   |                                              |                                                                                   |

| $\begin{array}{c c c c c c c c c } \operatorname{port}_i &= empty \wedge &&\\ &\operatorname{sent}_i &= req &&\\ \hline \operatorname{tick} & \operatorname{status}_i &= root \vee && \operatorname{if} \operatorname{clock}_i < 2 &&\\ &\operatorname{status}_i &= child && \operatorname{then} \operatorname{clock}_i := \operatorname{clock}_i + 1 &&\\ &\operatorname{else} \operatorname{clock}_i &:= \operatorname{chocked} &&\\ &\operatorname{clock}_i &= \operatorname{delay}_i \wedge && \operatorname{status}_i := \operatorname{checked} &&\\ &\operatorname{clock}_i &= \operatorname{delay}_i \wedge && \operatorname{port}_i &:= \operatorname{empty} &&\\ &\operatorname{sent}_i &= empty \wedge && \operatorname{port}_i &:= empty &&\\ &\operatorname{sent}_i &= empty \wedge && \operatorname{port}_i &:= empty &&\\ &\operatorname{sent}_i &= empty \wedge && \operatorname{port}_i &:= empty &&\\ &\operatorname{sent}_i &= empty \wedge && \operatorname{port}_i &:= empty &&\\ &\operatorname{sent}_i &= empty \wedge && \operatorname{sent}_i &:= req &&\\ &\operatorname{in}_i &= empty \wedge && \operatorname{sent}_i &:= req &&\\ &\operatorname{in}_i &= empty \wedge && \operatorname{sent}_i &:= req &&\\ &\operatorname{in}_i &= empty \wedge && \operatorname{sent}_i &:= ack &&\\ &\operatorname{in}_i &= req \wedge && \operatorname{sent}_i &:= ack &&\\ &\operatorname{in}_i &= req \wedge && \operatorname{sent}_i &:= chocked \wedge && \operatorname{status}_i &:= root &&\\ &\operatorname{sent}_i &= empty &&\\ &\operatorname{sent}_i &= checked \wedge && \operatorname{status}_i &:= root &&\\ &\operatorname{sent}_i &= checked \wedge && \operatorname{status}_i &:= child &&\\ &\operatorname{in}_i &= ack &&\\ &\operatorname{retry}_i && \operatorname{status}_i &= checked \wedge && \operatorname{status}_i &:= child &&\\ &\operatorname{in}_i &= req \wedge && & \operatorname{clock}_i &:= 0 &&\\ &\operatorname{sent}_i &= req && &\operatorname{in}_i &:= empty &&\\ &\operatorname{sent}_i &= empty && & & \operatorname{sent}_i &:= empty &&\\ &\operatorname{sent}_i &= req && &\operatorname{in}_i &:= empty &&\\ &\operatorname{sent}_i &= rep && &\operatorname{in}_i &:= empty &&\\ &\operatorname{sent}_i &= empty && & & \operatorname{sent}_i &:= empty &&\\ &\operatorname{sent}_i &= empty && & & & \operatorname{sent}_i &:= empty &&\\ &\operatorname{sent}_i &= empty && & & & & & & & & & & & & & & & & & $                                                                                                                                                      | LICK                   | -                                            | $\operatorname{clock}_i := \operatorname{clock}_i + 1$                            |