Efficient Domain Partitioning for Stencil-based Parallel Operators

### Gaurav Saxena

Submitted in accordance with the requirements for the degree of Doctor of Philosophy

The University of Leeds School of Computing August 2018

The candidate confirms that the work submitted is his/her own, except where work which has formed part of a jointly authored publication has been included. The contribution of the candidate and the other authors to this work has been explicitly indicated below. The candidate confirms that appropriate credit has been given within the thesis where reference has been made to the work of others.

Some parts of the work presented in Chapters 1, 4, 5 and 6 have been published in the following articles:

- Saxena, G., Jimack, P.K. and Walkley, M.A., 2016, July. A Cache-aware Approach to Domain Decomposition for Stencil-based Codes. In *High Performance Computing & Simulation* (HPCS), 2016 International Conference on (pp. 875-885). IEEE.

- Saxena, G., Jimack, P.K. and Walkley, M.A., 2017, December. A Cache-aware Approach to Adaptive Mesh Refinement in Parallel Stencil-based Solvers. In High Performance Computing and Communications; IEEE 15th International Conference on Smart City; IEEE 3rd International Conference on Data Science and Systems (HPCC/SmartCity/DSS), 2017 IEEE 19th International Conference on (pp. 364-371). IEEE.

- Saxena, G., Jimack, P.K. and Walkley, M.A., 2018. A Quasi-cache-aware Model for Optimal Domain Partitioning in Parallel Geometric Multigrid. *Concurrency and Computation: Practice and Experience*, 30(9), p.e4328.

The above publications are primarily the work of the candidate.

This copy has been supplied on the understanding that it is copyright material and that no quotation from the thesis maybe published without proper acknowledgement. ©2018 The University of Leeds and Gaurav Saxena

Acknowledgements

It has always been my dream to become a good researcher and I could not have chosen a better path than to pursue this PhD as the first step to achieving this goal. In this long, tough and fruitful journey, it has been an absolute honour and pleasure to have worked under the supervision of Professor *Peter K. Jimack* and *Dr. Mark A. Walkley*. Together, they form a perfect team. Besides being brilliant researchers, they are amazing human beings who make every effort to understand the needs and problems of the student. Though one's imagination is unlimited, it is not possible for me to imagine better supervisors than them. From the bottom of my heart, I profusely thank them for their guidance, care and encouragement. Thank you for letting me pursue my dream and I really hope this journey blossoms into a life-long academic collaboration.

My heartfelt thanks to Dr. Karim Djemame for taking out the time for my yearly progress meetings and supplying some extremely interesting ideas. His constructive feedback has helped me to expand the scope of the future work outlined in this thesis. My thanks to Dr. Brandon Bennett for very timely approving the travel grants for conferences. From the day I walked in, Judi Drew has constantly helped me to adjust to the life of the department. The number of times she has helped me book tickets, register for conferences and forwarded changes in flight schedules, qualifies for a world-record. Thank you to Dr. Peter Bollada for all the interesting conversations from across the table. His pleasant personality, jovial nature and helping attitude is certainly contagious. Despite the deficiency of grey cells in my right brain, I have been able to enjoy many conversations with Dr. Thomas Ranner. Beyond doubt, he is an excellent academician and person. Many thanks to Mark Dixon for the constant support he offered regarding the hardware and software on ARC2/ARC3. His knowledge of hardware is unparalleled. Thanks to Martin Callaghan for making all the training sessions extremely interesting. I am very grateful to Ann S. Almgren for taking out the time to meet me in the SIAM conference in Atlanta, US, to solve my doubts regarding BoxLib. Thanks to Weigun Zhang for helping me understand some specific subroutines in BoxLib. Meng-Huo Chen (Alan) happily shared his PhD experience and wisdom with me whenever we had the time to look away from the screen. I really enjoyed these breaks. My thanks to all the anonymous reviewers for their time and suggestions which helped us to improve the work in this thesis. Many thanks to myteachers at the University of Edinburgh who sparked my monotonically increasing interest in High Performance Computing. A big thanks to Dr. Sanjeev Singh and Dr. M. K. Das for helping and having faith in me in the worst of times. I am very grateful to Sanjay Batra sir, Dr. Harmeet Kaur, Dr. Baljeet Kaur, Negi sir, Anita maam, Dr. Manoj Aggarwal, Sanjay sir, Ajit ji, Amit ji, Bharat ji and Shakti ji for accepting me as a member of the HRC family. My stay at HansRaj college was one of the happiest times I ever had and it was because of you all.

Thanks is a very small word for my wonderful friend Sabby who, beyond doubt, is the finest human being I ever came across. My amazing friend Sachin taught me the value of hard work and set an example on how to survive despite extreme adversities. Thanks to my good friend Anshu whose amazing sense of humour and spiritual knowledge is beyond this realm. Swapnil Laxman Gaikwad has constantly shared, advised, helped and encouraged me in this tough journey and forever will I remain indebted to him. I profusely thank my super-amazing friends Rahul Arora, Divya Jain, Rashmi Shakya and Pranav Kumar Singh who have a golden heart and a hand that is always ready to help. I must thank Swapnil Sahu for his timely help and all the good times we shared. A super big thanks to Kanika Malik for being a wonderful friend and making time to meet me every time I was about to start a new session at work. Thanks to Jyoti Balwani for reminding me again and again that I am a good person. My wonderful childhood friend Vasuda Arora, who has been a constant source of support, deserves a big chunk of the thank-you cookie.

Little did I know that my grandfather's predictions about my education would turn out to be true. A big thanks to him for gifting my brother and me with a never-ending supply of books. I thank my supremely talented *uncle* who has always been an amazing friend to me. Love and thanks to my *nephews* for loving me even when I have not been able to do anything for them. A huge thanks to my *sister-in-law* for completing our family and making me feel at home during my visit. A big thanks to my *brother* for his intermittent yet excellent streams of advice and for easing my financial burdens. My grandmother forged my character and I am thankful to the universe that I was loved by the most noble soul ever to walk on earth. Thanks is a small word for my father who stood like a rock in front of me when I needed him the most. Last and the most, I take this opportunity to thank my mother who was with me every step of this journey. If I have achieved anything in this life, it is because of her. I have not met anyone as learned and educated as her. Although she is too humble to accept but she has an honorary doctorate in a very rare subject called ... Life.

#### Abstract

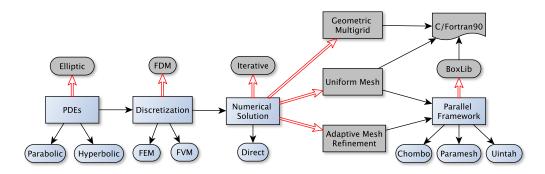

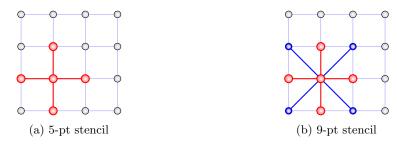

Partial Differential Equations (PDEs) are used ubiquitously in modelling natural phenomena. It is generally not possible to obtain an analytical solution and hence they are commonly discretized using schemes such as the Finite Difference Method (FDM) and the Finite Element Method (FEM), converting the continuous PDE to a discrete system of sparse algebraic equations. The solution of this system can be approximated using iterative methods, which are better suited to many sparse systems than direct methods.

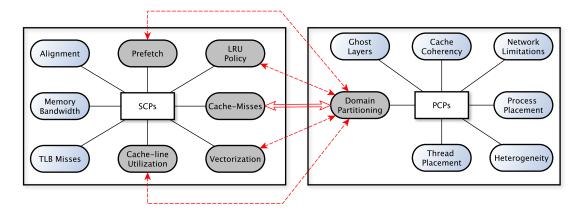

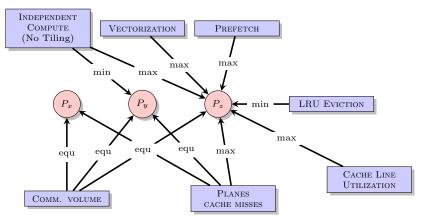

In this thesis we use the FDM to discretize linear, second order, Elliptic PDEs and consider parallel implementations of standard iterative solvers. The dominant paradigm in this field is distributed memory parallelism which requires the FDM grid to be partitioned across the available computational cores. The orthodox approach to domain partitioning aims to minimize only the communication volume and achieve perfect load-balance on each core. In this work, we re-examine and challenge this traditional method of domain partitioning and show that for well load-balanced problems, minimizing only the communication volume is insufficient for obtaining optimal domain partitions. To this effect we create a high-level, quasi-cache-aware mathematical model that quantifies cache-misses at the sub-domain level and minimizes them to obtain families of high performing domain decompositions. To our knowledge this is the first work that optimizes domain partitioning by analyzing cache misses, establishing a relationship between cache-misses and domain partitioning.

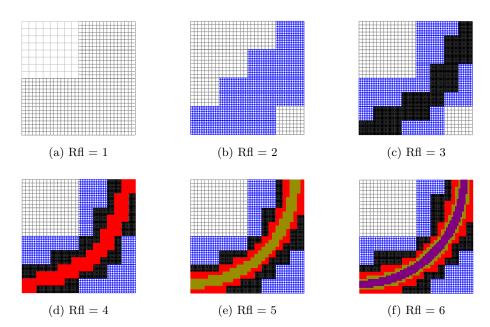

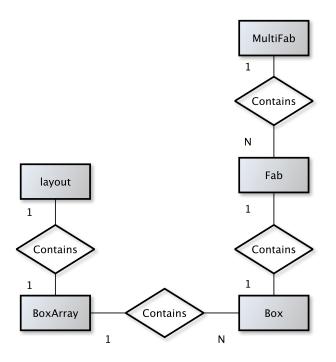

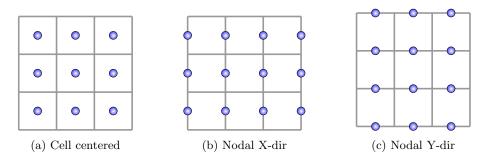

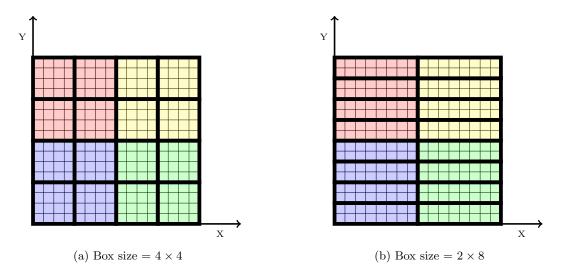

To place our model in its true context, we identify and qualitatively examine multiple other factors such as the Least Recently Used policy, Cache Line Utilization and Vectorization, that influence the choice of optimal sub-domain dimensions. Since the convergence rate of point iterative methods, such as Jacobi, for uniform meshes is not acceptable at a high mesh resolution, we extend the model to Parallel Geometric Multigrid (GMG). GMG is a multilevel, iterative, optimal algorithm for numerically solving Elliptic PDEs. Adaptive Mesh Refinement (AMR) is another multilevel technique that allows local refinement of a global mesh based on parameters such as error estimates or geometric importance. We study a massively parallel, multiphysics, multi-resolution AMR framework called BoxLib, and implement and discuss our model on single level and adaptively refined meshes, respectively.

We conclude that "close to 2-D" partitions are optimal for stencil-based codes on structured 3-D domains and that it is necessary to optimize for both minimizing cache-misses and communication. We advise that in light of the evolving hardware-software ecosystem, there is an imperative need to re-examine conventional domain partitioning strategies.

# Contents

| 1        | Intr | roduction                                                                                          | 1 |

|----------|------|----------------------------------------------------------------------------------------------------|---|

|          | 1.1  | Our Focus                                                                                          | 2 |

|          | 1.2  | Thesis Contribution                                                                                | 5 |

|          | 1.3  | Thesis Outline                                                                                     | 6 |

| <b>2</b> | Bac  | kground and Related work                                                                           | 7 |

|          | 2.1  | Partial Differential Equations                                                                     | 8 |

|          | 2.2  | Discretization                                                                                     | 0 |

|          |      | 2.2.1 Finite Difference Method                                                                     | 1 |

|          |      | 2.2.2 Finite Element Method                                                                        | 2 |

|          |      | 2.2.3 Other Schemes                                                                                | 4 |

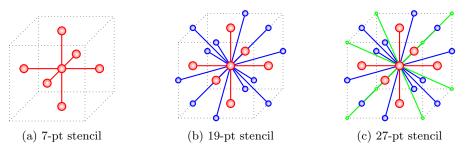

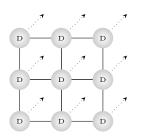

|          |      | 2.2.4 Stencils and Sparse Matrices                                                                 | 5 |

|          | 2.3  | Solution of Sparse Linear Systems 1                                                                | 7 |

|          |      | 2.3.1 Direct methods                                                                               | 8 |

|          |      | 2.3.2 Iterative methods                                                                            | 8 |

|          |      | 2.3.2.1 Jacobi                                                                                     | 9 |

|          |      | 2.3.2.2 Gauss-Seidel                                                                               | 0 |

|          |      | 2.3.2.3 Other Iterative Methods                                                                    | 2 |

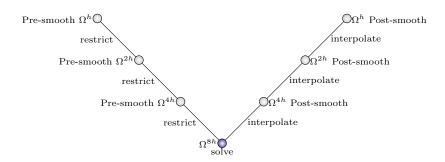

|          |      | 2.3.2.4 Multilevel Iterative Methods                                                               | 2 |

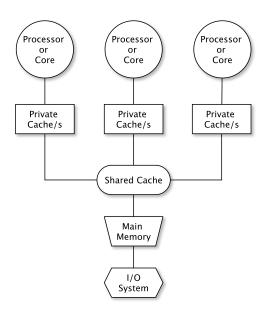

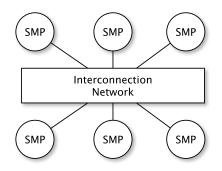

|          | 2.4  | Parallel Computing                                                                                 | 3 |

|          |      | 2.4.1 Models for representing Parallel Computation                                                 | 4 |

|          |      | 2.4.2 Parallel Performance                                                                         | 5 |

|          |      | 2.4.3 MPI                                                                                          | 6 |

|          |      | 2.4.4 Hybrid Programming using MPI and OpenMP                                                      | 6 |

|          |      | 2.4.5 Domain Decomposition/Domain Partitioning                                                     | 7 |

|          |      | 2.4.6 Sub-domains $\ldots \ldots 3$ | 2 |

|          |      | 2.4.7 Overlapping Communication with Computation                                                   | 2 |

|          | 2.5  | Multigrid                                                                                          | 3 |

|          |      | 2.5.1 Type of Multigrid methods                                                                    | 4 |

|          |      |                                                                                                    |   |

| CONTENTS |

|----------|

|----------|

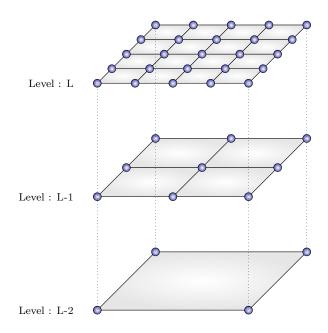

|   |                   | 2.5.2                                                                                                                                          | Parallelization and Coarser Grids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | 2.6               | Adapt                                                                                                                                          | ive Mesh Refinement (AMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|   |                   | 2.6.1                                                                                                                                          | Structured and Unstructured AMR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|   |                   | 2.6.2                                                                                                                                          | Software Packages for SAMR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|   |                   | 2.6.3                                                                                                                                          | BoxLib                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   |                   | 2.6.4                                                                                                                                          | Error Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

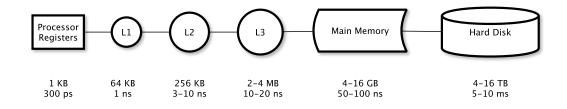

|   | 2.7               | Cache                                                                                                                                          | Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   | 2.8               | Stenci                                                                                                                                         | Codes: Metrics and Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|   | 2.9               | Summ                                                                                                                                           | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 3 | Test              | t Platf                                                                                                                                        | orm: Hardware and Software 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

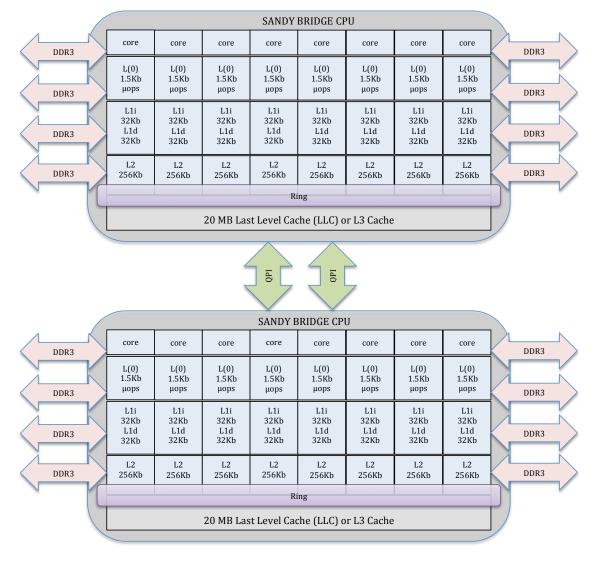

|   | 3.1               | Archit                                                                                                                                         | ecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   |                   | 3.1.1                                                                                                                                          | ARC2 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   |                   |                                                                                                                                                | 3.1.1.1 Theoretical FLOPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|   |                   |                                                                                                                                                | 3.1.1.2 Theoretical Memory Bandwidth of ARC2 node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|   |                   | 3.1.2                                                                                                                                          | ARC3 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   |                   |                                                                                                                                                | 3.1.2.1 Theoretical Memory Bandwidth of ARC3 node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|   | 3.2               | Softwa                                                                                                                                         | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|   |                   | 3.2.1                                                                                                                                          | ARC2 Compilers and MPI Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   |                   |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|   |                   | 3.2.2                                                                                                                                          | ARC3 Compilers and MPI Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   |                   | 3.2.2<br>3.2.3                                                                                                                                 | ARC3 Compilers and MPI Implementations54Other Tools55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

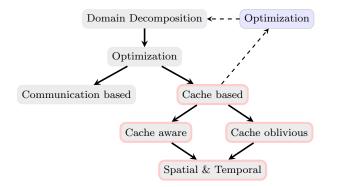

| 4 | Cac               | 3.2.3                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 4 | <b>Cac</b><br>4.1 | 3.2.3<br>che-awa                                                                                                                               | Other Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 4 |                   | 3.2.3<br><b>:he-awa</b><br>Introd                                                                                                              | Other Tools   55     are Domain Partitioning   57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 4 | 4.1               | 3.2.3<br><b>:he-awa</b><br>Introd<br>Motiva                                                                                                    | Other Tools    55      are Domain Partitioning    57      uction    57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 4 | 4.1<br>4.2        | 3.2.3<br><b>:he-awa</b><br>Introd<br>Motiva                                                                                                    | Other Tools       55         are Domain Partitioning       57         uction       57         aution and Contribution       59                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

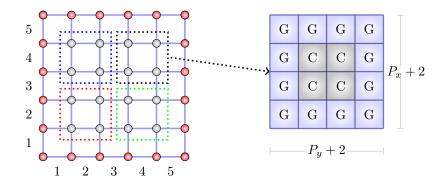

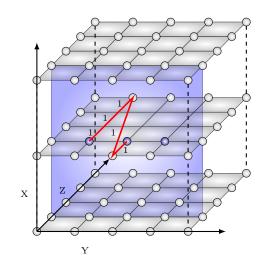

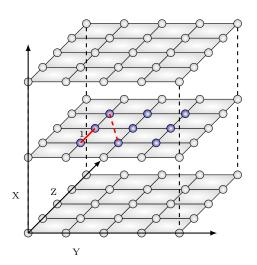

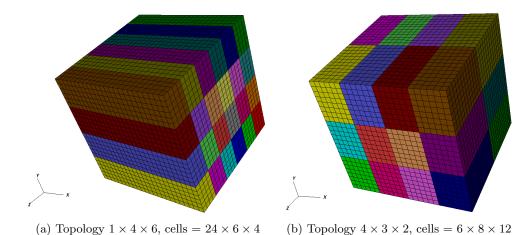

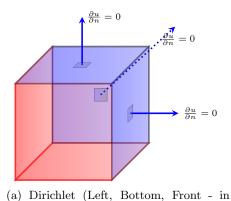

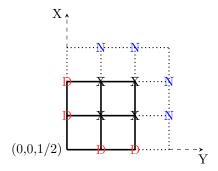

| 4 | 4.1<br>4.2        | 3.2.3<br><b>:he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1                                                                                  | Other Tools       55         are Domain Partitioning       57         uction       57         ation and Contribution       59         roblem       60                                                                                                                                                                                                                                                                                                                                                                                                                |  |

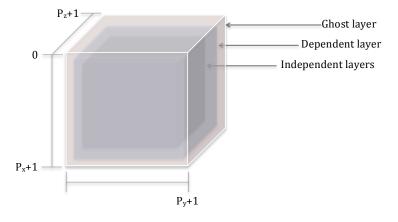

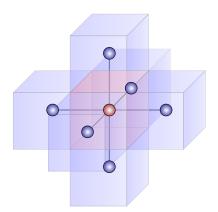

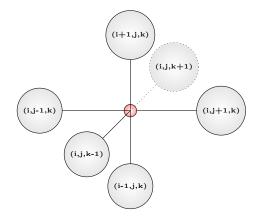

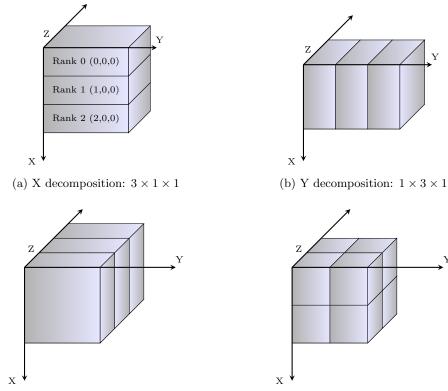

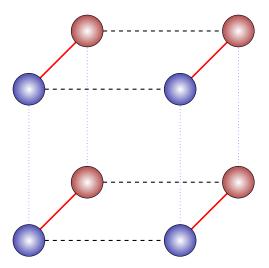

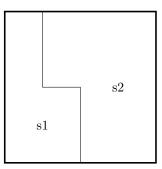

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>:he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1                                                                                  | Other Tools       55         re Domain Partitioning       57         uction       57         tion and Contribution       59         roblem       60         Notation and Reference Figure       63                                                                                                                                                                                                                                                                                                                                                                   |  |

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>:he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati                                                                        | Other Tools       55         are Domain Partitioning       57         uction       57         auction and Contribution       57         roblem       60         Notation and Reference Figure       63         ng a Model for Prediction       68                                                                                                                                                                                                                                                                                                                    |  |

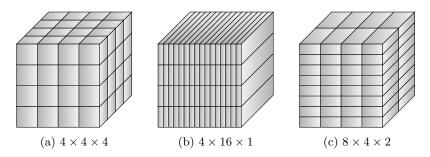

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>:he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1                                                               | Other Tools       55         re Domain Partitioning       57         uction       57         ution and Contribution       57         oblem       59         roblem       60         Notation and Reference Figure       63         ng a Model for Prediction       68         Parallel Numerical Solution of a Discretized PDE       69                                                                                                                                                                                                                              |  |

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2                                                       | Other Tools55are Domain Partitioning57uction57uction and Contribution57toton and Contribution59roblem60Notation and Reference Figure63ng a Model for Prediction68Parallel Numerical Solution of a Discretized PDE69Reiterating Assumptions70                                                                                                                                                                                                                                                                                                                         |  |

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2                                                       | Other Tools       55         Are Domain Partitioning       57         uction       57         uction and Contribution       59         roblem       60         Notation and Reference Figure       63         ng a Model for Prediction       68         Parallel Numerical Solution of a Discretized PDE       69         Reiterating Assumptions       70         Dependent Planes       71                                                                                                                                                                        |  |

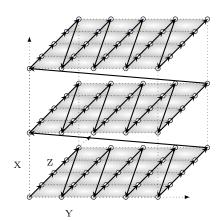

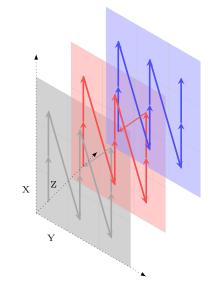

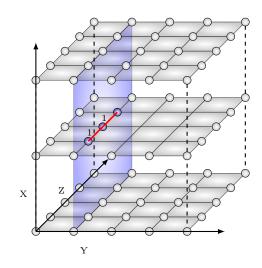

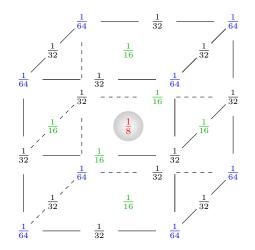

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2                                                       | Other Tools55are Domain Partitioning57uction57uction and Contribution57toton and Contribution59roblem60Notation and Reference Figure63ng a Model for Prediction68Parallel Numerical Solution of a Discretized PDE69Reiterating Assumptions70Dependent Planes714.4.3.1Z-Plane71                                                                                                                                                                                                                                                                                       |  |

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2                                                       | Other Tools55Are Domain Partitioning57uction57uction and Contribution59roblem60Notation and Reference Figure63ng a Model for Prediction68Parallel Numerical Solution of a Discretized PDE69Reiterating Assumptions70Dependent Planes714.4.3.1Z-Plane714.4.3.2X-Plane74                                                                                                                                                                                                                                                                                               |  |

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2<br>4.4.3                                              | Other Tools       55         re Domain Partitioning       57         uction       57         ution and Contribution       59         roblem       60         Notation and Reference Figure       63         ng a Model for Prediction       68         Parallel Numerical Solution of a Discretized PDE       69         Reiterating Assumptions       70         Dependent Planes       71         4.4.3.1       Z-Plane       74         4.4.3.3       Y-Plane       75                                                                                            |  |

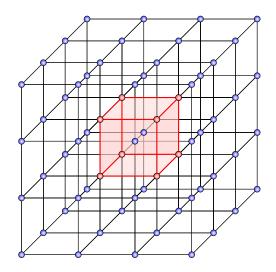

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>:he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                                    | Other Tools       55         rre Domain Partitioning       57         uction       57         uction and Contribution       59         roblem       60         Notation and Reference Figure       63         ng a Model for Prediction       68         Parallel Numerical Solution of a Discretized PDE       69         Reiterating Assumptions       70         Dependent Planes       71         4.4.3.1       Z-Plane       74         4.4.3.3       Y-Plane       75         Independent Computation       77                                                 |  |

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.3                                     | Other Tools       55         are Domain Partitioning       57         uction       57         ution and Contribution       59         roblem       60         Notation and Reference Figure       63         ng a Model for Prediction       68         Parallel Numerical Solution of a Discretized PDE       69         Reiterating Assumptions       70         Dependent Planes       71         4.4.3.1       Z-Plane       74         4.4.3.3       Y-Plane       75         Independent Computation       77         Packing, Unpacking and Updating       78 |  |

| 4 | 4.1<br>4.2<br>4.3 | 3.2.3<br><b>he-awa</b><br>Introd<br>Motiva<br>The P<br>4.3.1<br>Creati<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>4.4.7 | Other Tools55re Domain Partitioning57uction57uction and Contribution59roblem60Notation and Reference Figure63ng a Model for Prediction68Parallel Numerical Solution of a Discretized PDE69Reiterating Assumptions70Dependent Planes714.4.3.1Z-Plane714.4.3.2X-Plane744.4.3.3Y-Plane75Independent Computation77Packing, Unpacking and Updating78Minimization of Cache-Misses78                                                                                                                                                                                        |  |

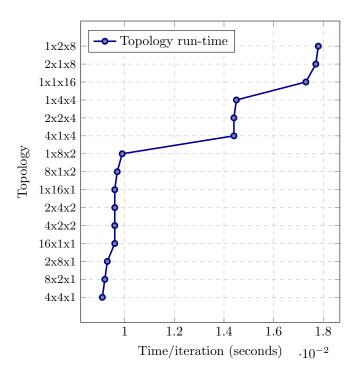

|   |                   | 4.6.1          | Performance Metric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

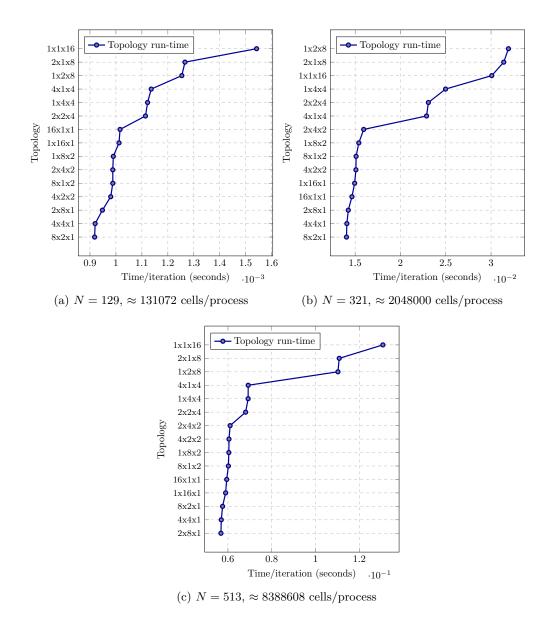

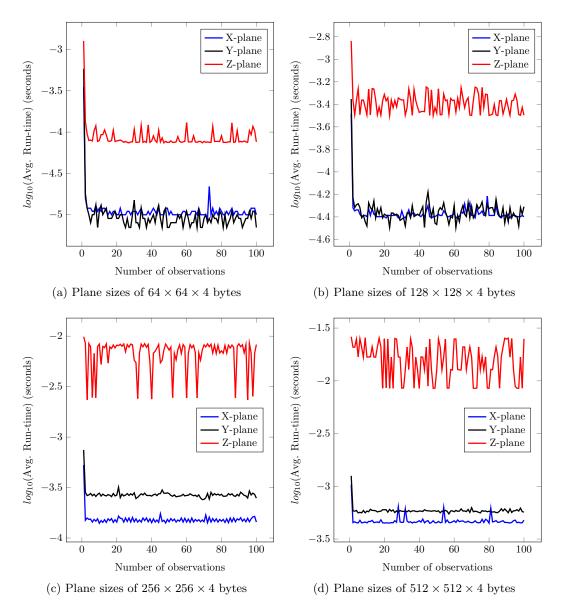

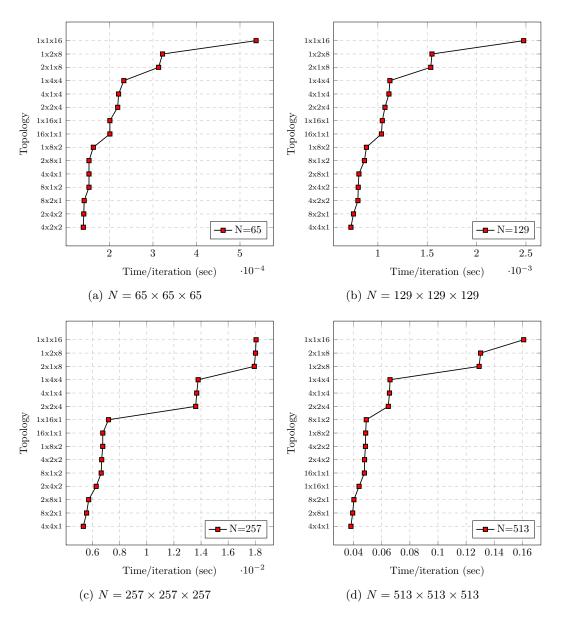

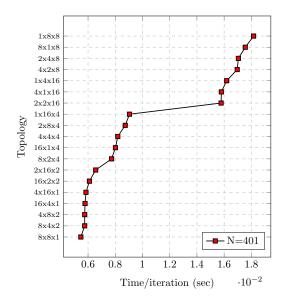

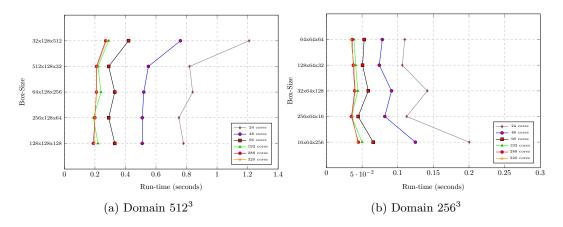

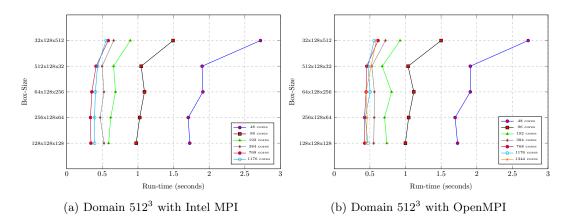

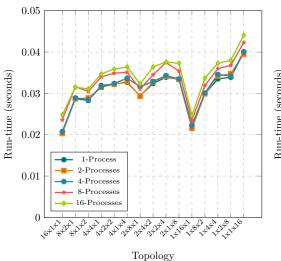

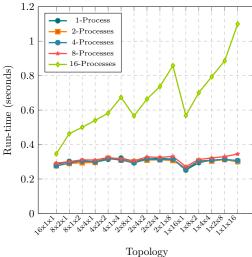

|   |                   | 4.6.2          | Single Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

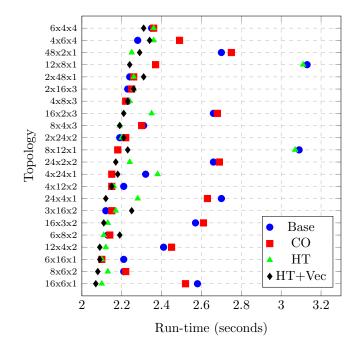

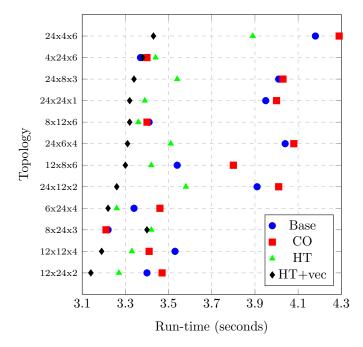

|   |                   |                | 4.6.2.1 Compiler Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

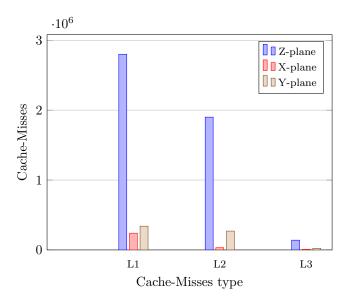

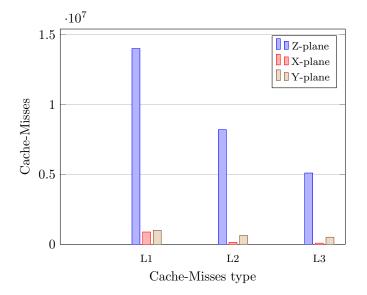

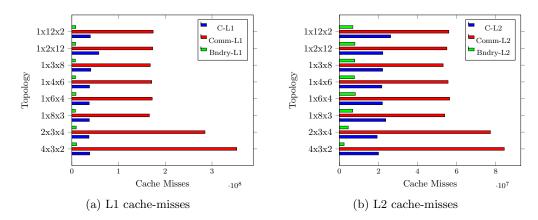

|   |                   |                | 4.6.2.2 Cache-Misses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

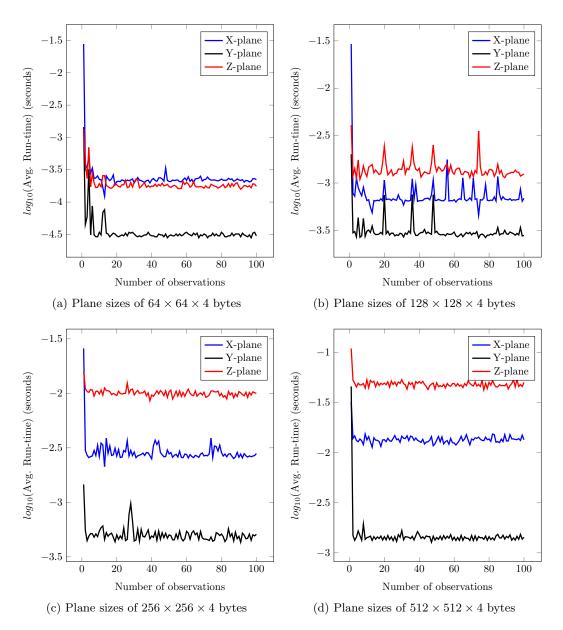

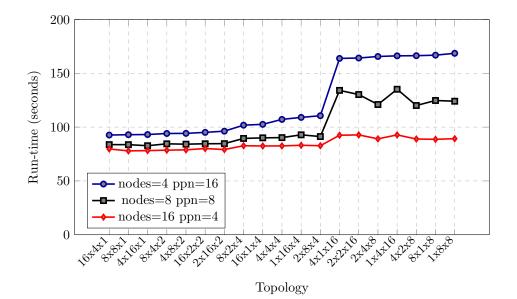

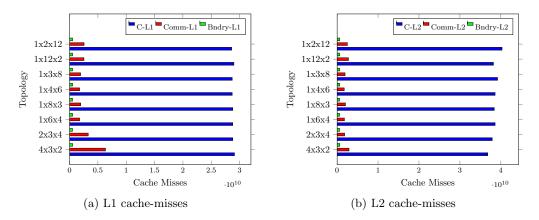

|   |                   | 4.6.3          | Multiple Nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

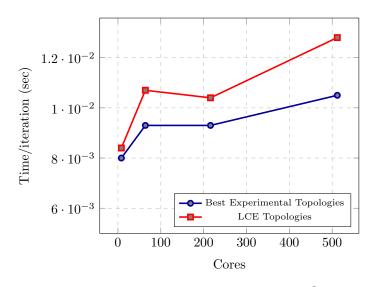

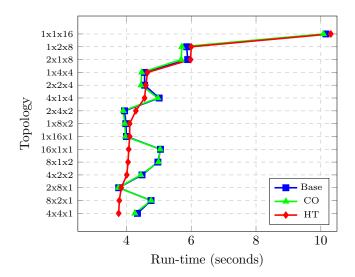

|   |                   |                | 4.6.3.1 Weak Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

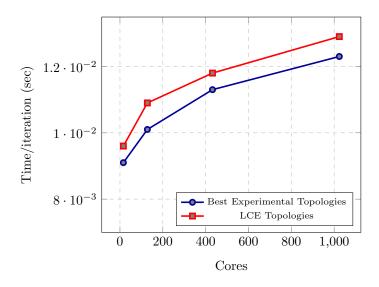

|   |                   |                | 4.6.3.2 Strong Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

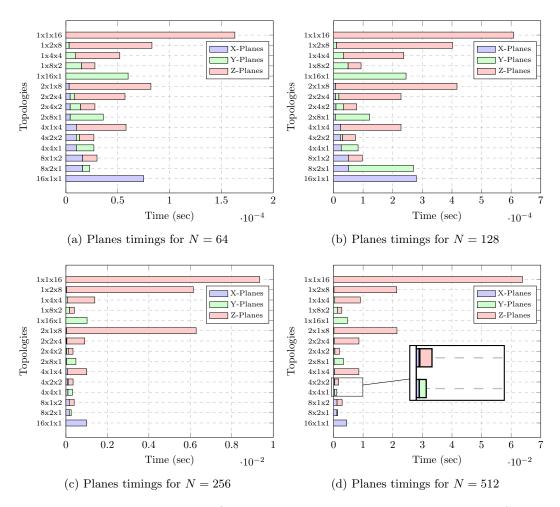

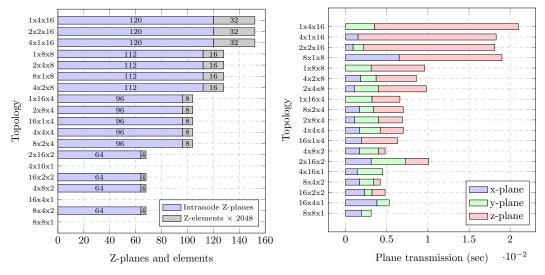

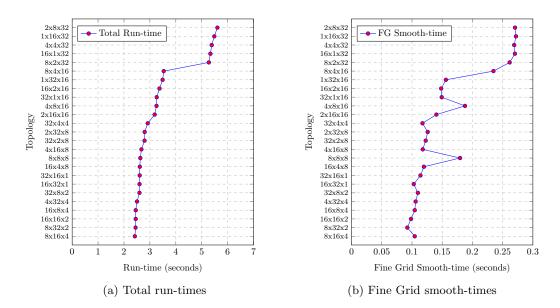

|   |                   |                | 4.6.3.3 Communication Times of Planes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

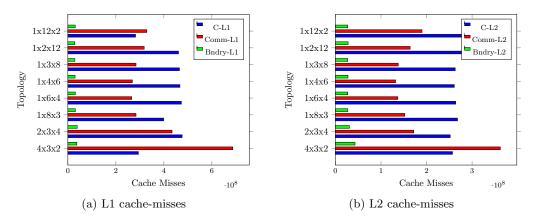

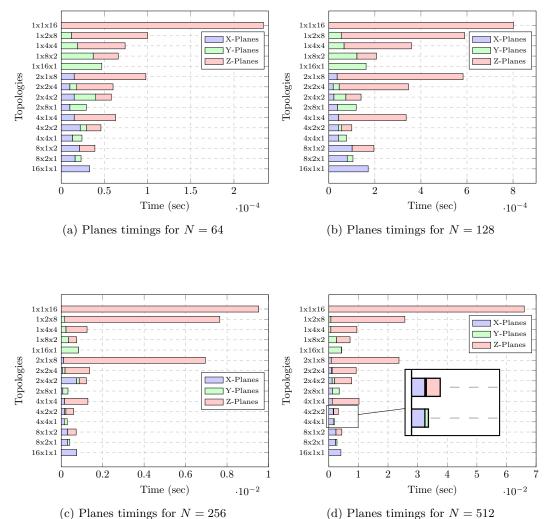

|   |                   |                | 4.6.3.4 Planes Update Cache-Misses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

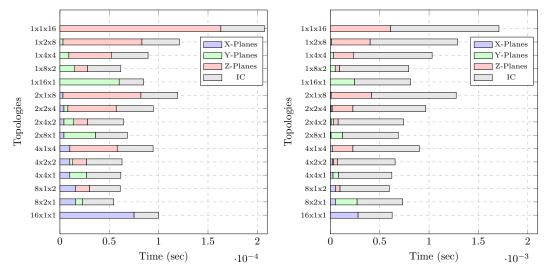

|   |                   |                | 4.6.3.5 Increasing Bandwidth-per-core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |