A. Galhardo <sup>1</sup>, J. Goes <sup>2</sup>, B. Vaz <sup>2</sup>, N. Paulino <sup>2</sup>

<sup>1</sup> ISEL – DEEA Av. Emídio Navarro, nº 1 1949 – 014 Lisboa – PORTUGAL E-mail: galhardo@deea.isel.ipl.pt DEE/UNINOVA – CRI

Campus da Faculdade de Ciências e Tecnologia

2825 – 114 Monte da Caparica – PORTUGAL

E-mail: jg@uninova.pt

Este trabalho apresenta a aplicação de um controlo de fase única a um conversor concorrencial de baixa tensão. Com vista à validação da análise e conclusão teóricas, um conversor concorrencial de 10-bit 4 MS/s foi projectado e simulado. Foi primeiramente simulado com um controlo clássico de 6 fases, e posteriormente com um esquema de fase única. Os resultados de simulação mostram que as características globais são mantidas, apontando para que o uso de esquemas de fase única em conversores de baixa tensão seja uma solução que reduz a complexidade dos sistemas clássicos não sobrepostos.

## Introdução

Os circuitos de condensadores e amplificadores comutados são projectados recorrendo basicamente a dois sinais de controlo,  $\Phi_1$  e  $\Phi_2$ , ou seja a duas fases. Evita-se assim que os condensadores, nomeadamente os de amostragem, percam carga devido a eventuais situações de condução simultânea dos interruptores, controlando-os por  $\Phi_1$  e  $\Phi_2$ .

Além disso, e para evitar perda de sinal devido à injecção de carga dos interruptores situados à entrada dos amplificadores, é comum o uso de sinais de controlo não sobrepostos com os primeiros, avançados no tempo,  $\Phi_{1a}$  e  $\Phi_{2a}$  [1]. Acrescente-se ainda que o uso simultâneo de interruptores NMOS e PMOS força a aplicação de sinais complementares a  $\Phi_1$ ,  $\Phi_2$ ,  $\Phi_{1a}$  e  $\Phi_{2a}$ , pelo que é vulgar a utilização de esquemas com seis ou oito fases. Também é usual a sua utilizações em circuitos de amplificadores comutados (SO) [2][3], onde se encontram todos os interruptores ligados a fontes ou nós com baixa impedância, como  $V_{LO}$  ( $\sim V_{SS}$ ) ou  $V_{HI}$  ( $\sim V_{DD}$ ).

Este trabalho descreve a utilização de esquemas de controlo de fase única em conversores concorrenciais de baixa tensão. A técnica explora a diferença e não sobreposição entre os valores das condutâncias dos transístores PMOS e NMOS quando operando em circuitos de baixa tensão e controlados por sinais de relógio com transições rápidas, que actualmente são possíveis nas tecnologias avançadas. Os resultados das simulações fazem prever que não mais serão necessários esquemas complexos de controlo em larga gama de conversores A/D. As vantagens são diversas, não só o ruído do substrato será minimizado, como a área e a complexidade, mantendo-se ou sendo melhoradas as características dinâmicas, SFDR e THD.

A nova técnica foi simulada num conversor de 10-bit 4 MS/s, alimentado nominalmente a 1.5V (± 20%), projectado em tecnologia CMOS de 0.18 μm, e os resultados obtidos comparados com os obtidos com o mesmo circuito mas controlado por um esquema clássico de seis fases. Os resultados da análise FFT mostram que com alimentação reduzida o novo esquema proposto melhora a SFDR do circuito em 6 dB.

# Selecção da Arquitectura

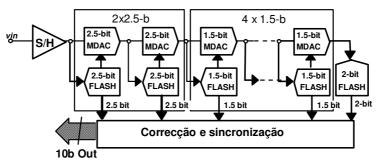

A arquitectura geral do conversor está apresentada na Figura 1 e foi projectada e optimizada como referido em [4].

Fig. 1: Arquitectura do conversor concorrencial de 10-b.

O circuito é composto por um amplificador S/H, seguido de dois andares de 2.5-bit e de 4 de 1.5-bit cada, e por fim um quantificador paralelo (FLASH). Cada andar por sua vez é composto de um MDAC e por um quantificador. Utilizaram-se andares iniciais de 2.5-bit por ser a arquitectura mais indicada [5] para projectos com baixos valores de tensão de alimentação.

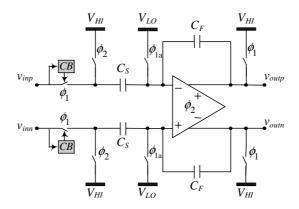

### A) Sample-and-hold

A Figura 2 apresenta a implementação do circuito S/H. Num esquema clássico, quando a fase de amostragem  $\Phi_{1a}$  (avançada no tempo em relação a  $\Phi_{1}$ ) está activa, as entradas do amplificador SO são colocada a  $V_{LO}$  ( $\sim V_{SS}$ ). Simultaneamente as saídas do amplificador estão no estado de alta impedância e colocadas a  $V_{HI}$  ( $\sim V_{DD}$ ). Os sinais de entrada são amostrados nos condensadores unitários  $C_S = C_u$  através de dois interruptores controlados por circuitos aumentadores (CB), e os condensadores de realimentação  $C_F$  carregados a  $V_{HI}$ .

Quando a fase de armazenamento  $\Phi_2$  está activa um terminal de  $C_S$  é ligado a  $V_{HI}$  e a carga entretanto armazenada é transferida para  $C_F$ . São usados valores de  $C_u$  = 1 pF.

Fig. 2: Implementação do S/H.

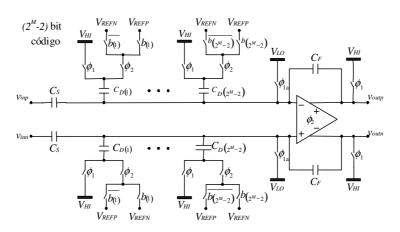

#### B) MDAC de 1.5-b e 2.5-b

A Figura 3 apresenta a implementação do amplificador SO dos MDAC. De igual modo durante a fase de amostragem o sinal diferencial é amostrado em  $C_S$ , e quer o condensador  $C_F$  quer os 6 condensadores unitários  $C_{D(i)} = C_u$ , são carregados a  $V_{HI}$ .

Fig. 3: Implementação dos MDACs.

Durante a fase  $\Phi_2$ , o resíduo obtido na subtracção entre o valor do sinal armazenado e o valor fornecido pela conversão D/A, efectuada pelos condensadores  $C_{D(i)}$ , do código fornecido pelo quantificador, é armazenado nos condensadores  $C_F$ . São usados valores de  $C_u = 150$  fF nos MDACs de 2.5-b, e valores de  $C_S = 2^3 \cdot C_u$  e  $C_F = 2 \cdot C_u$ . A implementação dos MDACs de 1.5-b usa apenas dois condensadores  $C_{D(i)} = C_u = 50$  fF em vez de seis. Os valores de  $C_S$  e  $C_F$  são calculados por  $C_S = 2^2 \cdot C_u$  e  $C_F = 2 \cdot C_u$ .

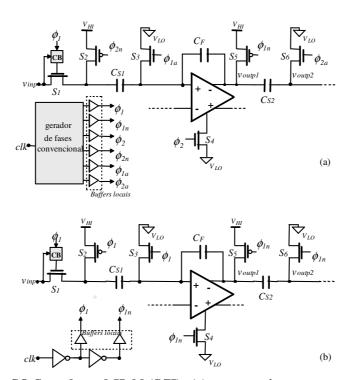

# A Técnica da Fase Única

A ideia da utilização de uma fase única proposta em [6] realiza-se controlando todos os interruptores do bloco utilizando apenas uma fase  $\Phi_l$  e a sua complementar  $\Phi_{ln}$ . De modo a exemplificar o funcionamento da técnica é apresentado na Figura 4 um circuito amplificador diferencial. Somente metade do circuito diferencial é apresentado, primeiramente utilizando seis sinais de controlo e seguidamente a nova técnica com dois sinais, um complementar do outro.

Fig. 4: Amplificador SO Sample-and-Hold (S/H): (a) – com os interruptores controlados por um conjunto convencional de seis fases; (b) –com os interruptores controlados por fase única,  $\phi_1$  e complementar  $\phi_{1n}$ .

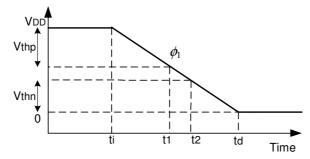

Assuma-se que os interruptores  $S_2$  e  $S_3$ , PMOS e NMOS, controlados inicialmente por  $\Phi_{2n}$  e  $\Phi_{1a}$  são controlados apenas por  $\Phi_1$ , cuja transição de tensão está representada na Figura 5.

Durante o tempo de transição  $\Delta t = t_d - t_i$  a condutância  $g_n$  do interruptor NMOS decresce desde o seu valor máximo  $g_{on}$  até zero em  $t_2$ , quando o valor da tensão de porta seja inferior ao valor  $V_{thn}$ . Enquanto isso o valor da condutância  $g_p$  do interruptor PMOS aumenta desde zero, em  $t_1$  quando o sinal de porta começa a ser inferior a  $V_{DD} - V_{thp}$ , até ao valor máximo  $g_{op}$ .

Fig. 5: Transição do sinal de controlo dos interruptores NMOS e PMOS.

O condensador  $C_{SI}$  descarrega se as condutâncias dos dois interruptores não forem nulas. Essa descarga é função da resistência equivalente da série das resistências dos dois interruptores,  $S_2$  e  $S_3$ , ou seja do paralelo ou soma das sua condutâncias.

A condutância total  $g_{TOT}$  terá o máximo centrado entre  $t_1$  e  $t_2$ , e estender-se-á por um tempo função do tempo de transição do sinal de controlo.

O integral no tempo da condutância total Qv quantifica a descarga do condensador  $C_{SI}$ , tendo as mesmas unidades de um condensador, C/V ou F. Um cálculo simplificado da grandeza pode ser efectuado com base na equação seguinte, tendo-se assumido que  $V_{thn} \sim V_{thp} \sim V_{th}$  e  $g_{on} \sim g_{op} \sim g_{o}$ .

$$Qv\left(C/V\right) \approx \frac{\left[g_o \cdot \Delta t \cdot (V_{DD} - 2 \cdot V_{th})^2\right]}{\left[6 \cdot V_{DD} \cdot (V_{DD} - V_{th})\right]} \quad (1)$$

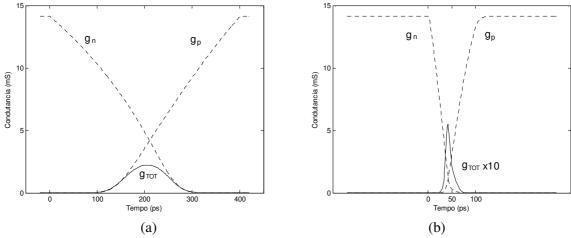

Na Figura 6 estão representadas em (a) as evoluções das condutâncias dos dois interruptores, assim como a global, para um tempo de transição de 400ps. Em (b) estão representadas as mesmas grandezas, para os mesmos interruptores mas para um tempo de 100ps, e com  $g_{TOT}$  ampliado dez vezes.

Fig. 6: Transição do sinal de controlo dos interruptores NMOS e PMOS: (a) –tempo de descida de 400ps; (b) –tempo de descida de 100ps.

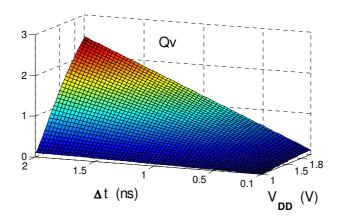

Na Figura 7 está representada a evolução de Qv em função do tempo de transição e da tensão de alimentação.

A representação foi normalizada para a situação de  $V_{DD}$ =1.8V e  $\Delta t$ =1ns.

Observa-se que no uso de tecnologias CMOS modernas, com reduzidos valores de tempo de transição e de tensão de alimentação, a degradação do sinal devido a estarem simultaneamente em condução os dois interruptores pode ser negligenciada.

Fig. 7: Evolução de Qv.

Como demonstrado em [6] o sinal amostrado é afectado pela perda da carga do condensador  $C_{SI}$  aproximadamente por:

Loss (dB) =

$$20 \cdot \log_{10} \{e^{(-Qv/C_{SI})}\}$$

(2)

Existem várias vantagens no uso de um esquema de fase única quando comparado com um esquema convencional. O gerador de sinais de controlo é reduzido a dois inversores, como representado na Figura 4 (b), reduzindo a complexidade do circuito e da distribuição dos sinais de controlo, e reduzindo o ruído.

## Resultados das Simulações

O amplificador apresentado na Figura 4 (a) com os interruptores controlados por um esquema convencional de seis fases, usando  $C_{SI} = C_{FI} = 1.0$  pF e  $C_{S2} = 1.4$  pF, foi projectado e simulado em tecnologia CMOS de  $0.18 \mu m$ , com  $V_{thn} = 0.50$  V e  $V_{thp} = -0.52$  V.

O mesmo amplificador foi simulado em condições análogas, mas sendo apenas controlado pelos dois sinais  $\Phi_1$  e  $\Phi_2$ . Dois inversores CMOS de tamanho médio ( $Wp \sim 24 \ \mu m$  e  $Wn \sim 8 \ \mu m$ ) foram utilizados no isolamento dos sinais de controlo,  $\Phi_1$  e  $\Phi_2$ , com tempos de subida e descida da ordem de algumas centenas de pico-segundos.

Foi obtida a FFT dos resultados da simulação da saída diferencial do segundo bloco ( $v_{outp2}$ - $v_{outn2}$ ), usando  $V_{DD} = 1.5 \text{ V}$ ,  $V_{LO} = V_{SS} = 0 \text{ V}$ ,  $V_{HI} = V_{DD}$  e desvios de 10% no tamanho dos interruptores. A frequência de amostragem foi  $F_S = 4$  MS/s para ambos os geradores, e um sinal diferencial ( $v_{inp}$ - $v_{inn}$ ) de frequência  $f_{in} = 2.31$  MHz e amplitude  $A_{in} = \pm 500$  mV foi aplicado às entradas diferenciais do amplificador.

Usando o novo esquema a perda de sinal é inferior a 0.0015 dB (0.1 mV, correspondendo a uma precisão de 13 bits) e a THD, dominada pela terceira harmónica, é mesmo melhorada de -93.8 dB para -98.4 dB. É certo que para valores mais elevados de  $V_{DD}$  até 2 V,  $g_{TOT}$  aumenta, mas a THD mantém-se reduzida.

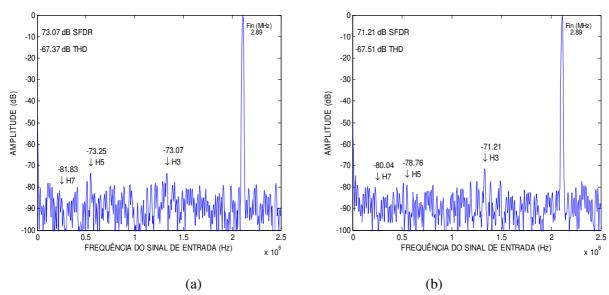

Posteriormente um conversor concorrencial de 10-b 4 MS/s foi projectado e simulado. A Figura 8 apresenta a FFT dos resultados da saída digital do conversor A/D, usando o esquema convencional e o novo esquema.

Fig. 8: FFT do sinal digital de saída: (a) -esquema convencional; (b) -novo esquema.

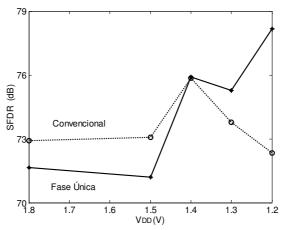

Foram efectuadas diversas simulações e obtidas as FFT da saída digital do conversor A/D. A Figura 9 apresenta a SFDR obtido em função de diferentes valores de  $V_{DD}$ , de 1.2 V a 1.8 V (1.5 V  $\pm$  20%), para ambos os esquemas. Pode ser observado que para valores mais reduzidos da tensão de alimentação o SFDR é melhorado em cerca de 6 dB.

Fig. 9: SFDR dos dois esquemas em função do valor de  $V_{DD}$ .

## Conclusões

Foi demonstrado neste trabalho que a utilização de um esquema de fase única no controlo de conversores concorrenciais de baixa tensão pode ser efectuada sem degradação das características dos mesmos. Foram apresentados e analisados resultados de simulações, utilizando um esquema convencional e utilizando o novo esquema. Os resultados obtidos pelas simulações de um conversor concorrencial completo, de 10-bit 4 MS/s, mostram que a integridade do sinal é mantida com o novo esquema, e que a SFDR é melhorada para baixos valores da tensão de alimentação.

### Referências

- [1] D. G. Haigh and B. Singh, "A Switching Scheme for Switched-Capacitor Filters, Which Reduces Effect of Parasitic Capacitances Associated with Control Terminals", *Proc. IEEE Int. Symposium on Circuits and Systems*, Vol. 2, pp. 586-589, June 1983.

- [2] A. Baschirotto, Rinaldo Castello, "A 1V 1.8MHz CMOS Switched-Opamp SC Filter with Rail-to-Rail Output Swing", *Proc. International Solid-State Circuits Conference*, pp. 58-59, Feb. 1997.

- [3] M. Steyaert, et. al., "Switched-Opamp, A Technique for Realising Full CMOS Switched-Capacitor Filters at Very Low Voltages", *Proc.* 19<sup>th</sup> European Solid-State Circuits Conference, pp. 178-181, Sep. 1993.

- [4] B. Vaz, J. Goes, R. Piloto, J. Neto, R. Monteiro, N. Paulino, "A Low-Voltage 3 mW 10-bit 4MS/s Pipeline ADC in Digital CMOS for sensor Interfacing", *Proc. IEEE International Symposium on Circuits and Systems*, May, 2005.

- [5] B. Vaz, N. Paulino, J. Goes, et. al., "Design of low-voltage CMOS pipelined ADC's using 1 pico-joule of energy per conversion", *IEEE International Symposium on Circuits and Systems*, No. 1, pp. 921-924, May 2002.

- [6] J. Goes, B. Vaz, N. Paulino, H. Pinto, R. Monteiro, A.S. Garção, "Switched-Capacitor Circuits using a Single-Phase Scheme", *Proc. IEEE International Symposium on Circuits and Systems*, May, 2005.