#### FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

## **Self-Calibrated Current Reference**

Bruno Miguel da Silva Teixeira

FOR JURY EVALUATION

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor: Vítor Grades Tavares

Synopsys Supervisor: Joaquim Machado

#### MESTRADO INTEGRADO EM ENGENHARIA MIEEC ELETROTÉCNICA E DE COMPUTADORES

2014/2015

#### A Dissertação intitulada

"Self Calibrated Current Reference"

foi aprovada em provas realizadas em 22-07-2015

o júri

Presidente Professor Doutor José Alberto Peixoto Machado da Silva

Professor Associado do Departamento de Engenharia Eletrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto

Conto trateus trends

Professor Doutor Paulo Mateus Mendes Professor Auxiliar do Departame<u>nto Ele</u>trónica Industrial da Universidade do Minho

Professor Doutor Vitor Manuel Grade Tavares

Professor Auxiliar do Departamento de Engenharia Eletrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto

O autor declara que a presente dissertação (ou relatório de projeto) é da sua exclusiva autoria e foi escrita sem qualquer apoio externo não explicitamente autorizado. Os resultados, ideias, parágrafos, ou outros extratos tomados de ou inspirados em trabalhos de outros autores, e demais referências bibliográficas usadas, são corretamente citados.

Autor - Bruno Miguel da Silva Teixeira

Faculdade de Engenharia da Universidade do Porto

### Resumo

Uma referência é um bloco essencial em muitas aplicações de sinal misto e radiofrequência, como conversores de informação, PLL e conversores de energia. A implementação mais usada em CMOS para referências de tensão é o circuito Bandgap, devido não só á sua previsibilidade, mas também á sua baixa dependência da temperatura e tensão de alimentação.

Correntes de referências estão também a ganhar um papel importante em sistemas elétricos devido á sua maior velocidade. O processamento de sinais em forma de corrente é executado de forma mais rápida do que sinais em forma de tensão. Portanto, para uma certa tecnologia, circuitos analógicos desenhados em modo de corrente operam mais rapidamente do que os de tensão.

Este trabalho estuda a referência bandgap. Uma das topologias mais utilizadas em ambientes de baixa tensão foi analisada e desenhada. Os problemas e métricas mais pertinentes associadas a este circuito, incluindo precisão, rejeição de ruido e comportamento da temperatura foram também discutidos. As limitações deste sistema devido a variações de processo foram estudadas e vários métodos de compensação foram sugeridos e aplicados.

Um segundo bloco foi também desenvolvido para efetivamente converter a tensão do circuito de bandgap para uma corrente de referência. Uma topologia baseada em reguladores de tensão foi proposta e desenvolvida. Devido a grandes variações de processo desta topologia, uma resistência programável e respetivo bloco de calibração foram desenvolvidos de modo a atingir a precisão desejada.

Todos estes circuitos foram implementados em tecnologia CMOS TSMC 40nm.

### **Abstract**

A constant reference is a pivotal block in several mixed-signal and radio-frequency applications, like for instance, data converters, PPLs and power converters. The most used CMOS implementation for voltage references is the Bandgap circuit due to its high-predictability, and low dependence of the supply voltage and temperature of operation.

Current references are also gaining an important role in electric systems due to the increased speed. Processing current signals is done faster than voltage signals and, therefore, for a given technology, analog circuits designed in current mode operate faster than their voltage mode counter parts

This work studies the bandgap voltage reference. One of the most relevant topologies for low voltage environments is designed and analyzed. The most relevant issues and performance metrics for BGR, including accuracy, PSRR and temperature behavior are also discussed. The limitations of this system due to process variations are studied and several methods for correction are proposed and employed.

A second block was designed in order to effectively act as a converter between the voltage reference into a current reference. A topology based on low dropout regulator was proposed and developed. Due to heavy process variation, a programmable resistor coupled with a calibration block was designed in order to achieve the desired accuracy.

All of these circuits were implemented in TSMC 40nm CMOS technology.

# Acknowledgments

I would like to express my gratitude to:

My family, especially my mother, for all the support they gave me. It was only through their help that I had the opportunity to study and invest in my career.

To my friends who turned my attention away from my thesis when I felt like hitting my head against the walls.

To all the people at Synopsys, especially my friends in the Analog Team: Bruno, Dénis, Hugo, Nuno and Patricio that always gave me good advice and of course, supplied the best tea and cookies.

My supervisor at FEUP, Vítor Grade Tavares for the great opportunity to work with him. He always gave me valuable guidance and support.

To my supervisor at Synopsis, Joaquim Machado that allowed me to developed my thesis in the great environment of Synopsys and opening a few moments in his busy schedule to share some of his knowledge. Without him I wouldn't be able to finish my work.

And finally to FEUP, for giving me some of the best years of my life.

Bruno Teixeira

"However strong you become, never seek to bear everything alone.

If you do, failure is certain."

Itachi Uchiha

# **Contents**

| 1 | Intr | troduction                                       |      |  |  |  |  |  |    | 1  |

|---|------|--------------------------------------------------|------|--|--|--|--|--|----|----|

|   | 1.1  | 1 Motivation                                     |      |  |  |  |  |  |    | 1  |

|   | 1.2  | 2 Specifications and Objectives                  |      |  |  |  |  |  |    | 2  |

|   | 1.3  | 3 Structure of the Document                      |      |  |  |  |  |  |    | 2  |

| 2 | Bacl | ackground and State of the Art                   |      |  |  |  |  |  |    | 5  |

|   | 2.1  | 1 Mosfet Fundamentals                            |      |  |  |  |  |  |    | 5  |

|   |      | 2.1.1 Threshold Voltage                          |      |  |  |  |  |  |    | 7  |

|   |      | 2.1.2 Carrier Mobility                           |      |  |  |  |  |  |    | 8  |

|   |      | 2.1.3 Zero Temperature Coefficient Point         |      |  |  |  |  |  |    | 10 |

|   | 2.2  | 2 BJT Fundamentals                               |      |  |  |  |  |  |    | 11 |

|   |      | 2.2.1 Base-Emitter Voltage                       |      |  |  |  |  |  |    | 11 |

|   | 2.3  | Resistor Architectures                           |      |  |  |  |  |  |    | 13 |

|   |      | 2.3.1 Switched-Capacitor Resistor                |      |  |  |  |  |  |    | 15 |

|   | 2.4  | 4 Process Corners and MonteCarlo                 |      |  |  |  |  |  |    | 18 |

|   | 2.5  | 5 State of the Art                               |      |  |  |  |  |  |    | 18 |

|   |      | 2.5.1 Traditional Bandgap Voltage Reference      |      |  |  |  |  |  |    | 18 |

|   |      | 2.5.2 MOS Biased Bandgap Voltage Reference       |      |  |  |  |  |  |    | 19 |

|   |      | 2.5.3 Low-Voltage Voltage Reference              |      |  |  |  |  |  |    | 20 |

|   |      | 2.5.4 Current Reference Architecture             |      |  |  |  |  |  |    | 21 |

|   |      | 2.5.5 Switched-Capacitor Current Reference       |      |  |  |  |  |  |    | 22 |

|   |      | 2.5.6 All MOSFET, Two Resistor Current Reference |      |  |  |  |  |  |    | 24 |

|   |      | 2.5.7 Resistorless Current Reference             |      |  |  |  |  |  |    | 25 |

|   |      | 2.5.8 4-Bits Trimmed CMOS Bandgap Reference      |      |  |  |  |  |  |    | 26 |

|   |      | 2.5.9 Overview                                   |      |  |  |  |  |  |    | 27 |

| 3 | Ban  | andgap Voltage Reference Design                  |      |  |  |  |  |  |    | 29 |

|   | 3.1  |                                                  | re . |  |  |  |  |  |    | 30 |

|   | 3.2  | 3                                                |      |  |  |  |  |  | 32 |    |

|   |      | 3.2.1 Increasing Supply Rejection                |      |  |  |  |  |  |    | 36 |

|   | 3.3  |                                                  |      |  |  |  |  |  |    | 38 |

|   |      | 3.3.1 Bias Circuit                               |      |  |  |  |  |  |    | 38 |

|   |      | 3.3.2 Folded Cascode Amplifier                   |      |  |  |  |  |  |    | 41 |

|   | 3.4  |                                                  |      |  |  |  |  |  |    | 46 |

|   | 3.5  | -                                                |      |  |  |  |  |  |    | 48 |

|   | 3.6  | 3                                                |      |  |  |  |  |  |    | 50 |

|   | 2.0  | 3.6.1 Current Consumption                        |      |  |  |  |  |  |    | 50 |

|   |      | 3.6.2 Temperature Behaviour                      |      |  |  |  |  |  |    | 53 |

xii CONTENTS

|   |             | 3.6.3     | Line Regulation                                     |

|---|-------------|-----------|-----------------------------------------------------|

|   |             | 3.6.4     | PSRR                                                |

|   |             | 3.6.5     | Overview                                            |

|   | 3.7         | Error S   | ources                                              |

|   |             | 3.7.1     | Process Variation and Mismatch                      |

|   |             | 3.7.2     | Mosfet Mismatch                                     |

|   |             | 3.7.3     | Resistor Mismatch                                   |

|   |             | 3.7.4     | BJT Mismatch                                        |

|   |             | 3.7.5     | BJT Variation                                       |

|   |             | 3.7.6     | Operational Amplifier Offset                        |

|   |             | 3.7.7     | Overview                                            |

|   | 3.8         |           | Considerations                                      |

|   | 3.9         |           | ary                                                 |

|   | 3.7         | Summe     |                                                     |

| 4 | Cur         | rent Ref  | Gerence Design 6                                    |

|   | 4.1         |           | ys of the voltage to current converter topology     |

|   | 4.2         |           | of the voltage to current converter topology        |

|   |             | 4.2.1     | Programmable Resistor Network                       |

|   |             | 4.2.2     | Non-Ideal Switches                                  |

|   |             | 4.2.3     | Calibration System                                  |

|   |             | 4.2.4     | Calibration Algorithm                               |

|   |             | 4.2.5     | Calibration Block                                   |

|   | 4.3         |           | S                                                   |

|   | т.Э         | 4.3.1     | Current Consumption                                 |

|   |             | 4.3.2     | Post-Calibration Variation                          |

|   |             | 4.3.3     |                                                     |

|   |             |           | C                                                   |

|   | 4.4         | 4.3.4     |                                                     |

|   | 4.4         | Summa     | ary                                                 |

| 5 | Dyn         | amic De   | evice Mismatch Compensation 8                       |

|   | 5.1         |           | ic Offset Cancellation Techniques                   |

|   |             | 5.1.1     | Auto-Zeroing Technique                              |

|   |             | 5.1.2     | Chopping                                            |

|   |             | 5.1.3     | Chopped Operational Amplifier                       |

|   |             | 5.1.4     | Chopped Amplifier Results                           |

|   |             | 5.1.5     | Bandgap Voltage Reference with Chopped Amplifier    |

|   | 5.2         |           | ic Matching of the Bandgap Core                     |

|   |             | 5.2.1     | Jumping Bandgap Core with Chopped Amplifier Results |

|   | 5.3         |           | ary                                                 |

|   | 0.0         | S 0111111 |                                                     |

| 6 | Con         | clusions  | and Future Work                                     |

|   | 6.1         | Summa     | ary of the work developed                           |

|   | 6.2         | Future    | Work                                                |

|   | <b>.</b> ~= |           |                                                     |

| A |             |           | ation Results 103                                   |

|   | A.1         |           | darameter Results - Pre-Layout Simulations          |

|   | A.2         |           | darameter Results - Post-Layout Simulations         |

|   | A.3         |           | Cascode Amplifier                                   |

|   | A.4         | Folded    | Cascode Amplifier (Post-Layout)                     |

| CONTENTS | xiii |

|----------|------|

|          |      |

|   | A.5 Sources of Error of the Bandgap Voltage Reference | 109 |

|---|-------------------------------------------------------|-----|

| В | V-to-I Simulation Results                             | 111 |

|   | B.1 Calibration Module                                | 111 |

|   | B.2 Calibration Codes                                 | 115 |

|   | B.3 Results                                           | 116 |

| C | <b>Chopping Simulation Results</b>                    | 119 |

|   | C.1 Offset Behavior                                   | 119 |

|   | C.2 Dynamic Bandgap Voltage Reference                 | 122 |

| D | Layout of the Folded Cascode Amplifier                | 123 |

| E | Layout of the Bandgap Voltage Reference               | 127 |

xiv CONTENTS

# **List of Figures**

| 2.1  | Silicon Energy Bandgap vs. Temperature                                                 | 6  |

|------|----------------------------------------------------------------------------------------|----|

| 2.2  | Absolute value of the threshold voltage variation of a typical PMOS and NMOS           |    |

|      | transistor (W/L=1u/1u). FreePDK 45nm CMOS Technology                                   | 8  |

| 2.3  | Electron mobility versus temperature for different doping levels. High purity to       |    |

|      | increased doping levels respectively (reprinted from the link above)                   | 9  |

| 2.4  | ZTC bias point for both PMOS and NMOS respectively in typical conditions. $I_D$        |    |

|      | vs $V_{GS}$ at different temperatures                                                  | 10 |

| 2.5  | Base-Emitter voltage temperature variation of diode connected BJT biased at 5u.        |    |

|      | $256um^2$ BJT and $8x256um^2$ BJT                                                      | 12 |

| 2.6  | Resistor variation versus temperature over typical, slow and fast corner               | 14 |

| 2.7  | Switched Capacitor                                                                     | 15 |

| 2.8  | Non-overlapping clock generator                                                        | 16 |

| 2.9  | Parasitic Capacitances of Mosfet                                                       | 16 |

| 2.10 | Channel Charge Injection                                                               | 17 |

| 2.11 | Simplified Brokaw bandgap voltage reference circuit (Brokaw, 1974)                     | 19 |

|      | Self Biased BGR Architecture (From [19])                                               | 20 |

| 2.13 | Low-Voltage Voltage Reference (From [17])                                              | 21 |

| 2.14 | Current Reference Architecture (From [12])                                             | 22 |

| 2.15 | Switched-Capacitor Current Reference Schematic ((From [11]))                           | 23 |

| 2.16 | All MOSFET, Two Resistor Current Reference Schematic (From [13])                       | 24 |

| 2.17 | Resistorless Current Reference (From [8])                                              | 25 |

| 2.18 | 4-bit trimmed CMOS Voltage Reference (From [6])                                        | 27 |

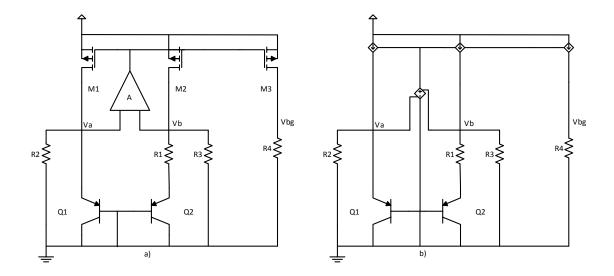

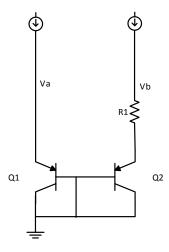

| 3.1  | a) Current Mode Bandgap Voltage Reference b) Ideal MOSFETs and OPAMP                   | 30 |

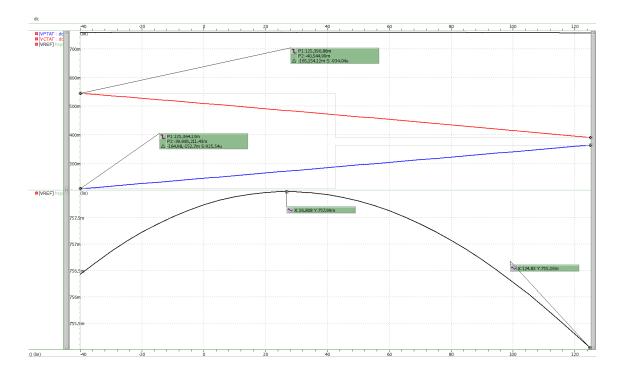

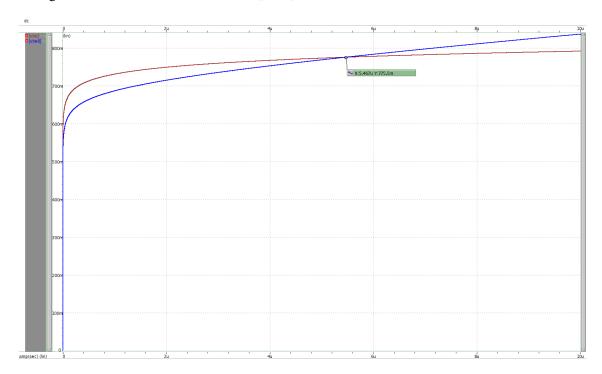

| 3.2  | CTAT + PTAT Voltages at 1.62 supply voltage                                            | 32 |

| 3.3  | BJT bias current measurement scheme                                                    | 33 |

| 3.4  | Base-Emitter Voltage biased with different currents                                    | 34 |

| 3.5  | Output Bandgap Voltage Reference                                                       | 36 |

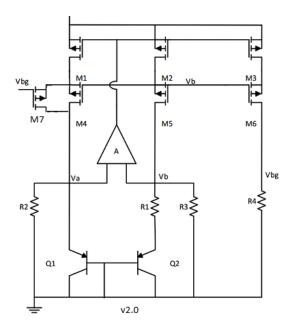

| 3.6  | Final Topology of the Current-Mode Bandgap Voltage Reference                           | 37 |

| 3.7  | Output voltage with no cascode transistors (left) and with cascode transistors (right) | 37 |

| 3.8  | Constant-Transconductance Bias Circuit (startup not shown)                             | 39 |

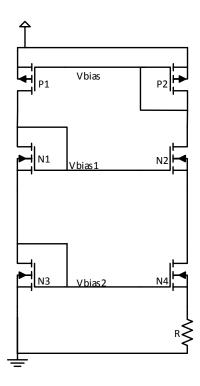

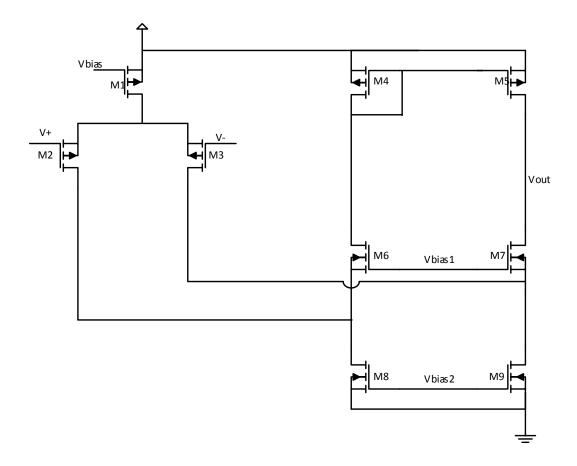

| 3.9  | Folded Cascode Amplifier                                                               | 41 |

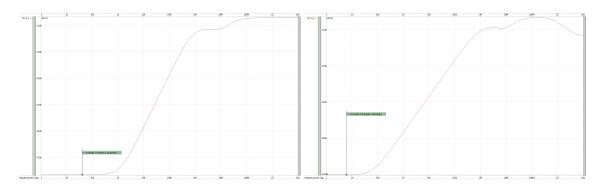

| 3.10 | Differential input voltage across several supply voltages at typical corners and 27°C  | 42 |

|      | Half circuit for voltage gain analysis                                                 | 43 |

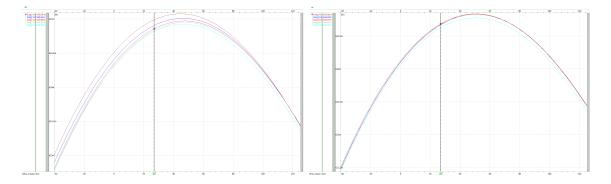

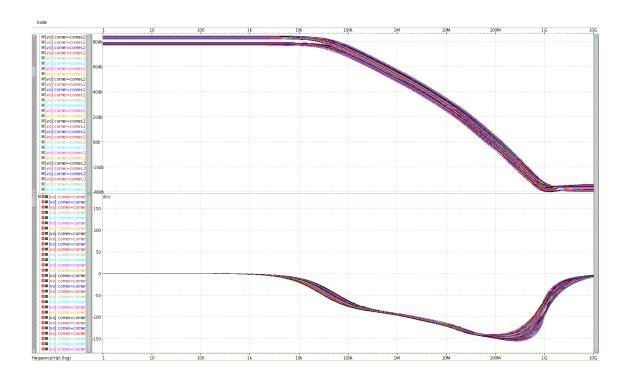

|      | Frequency response of the cascode amplifier                                            | 44 |

| 3.13 | Base-Emitter Voltage biased with different currents                                    | 46 |

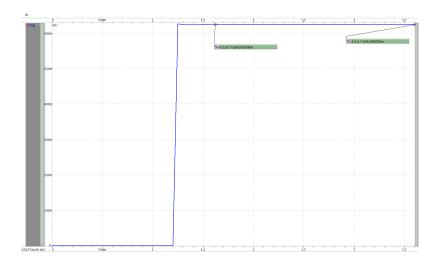

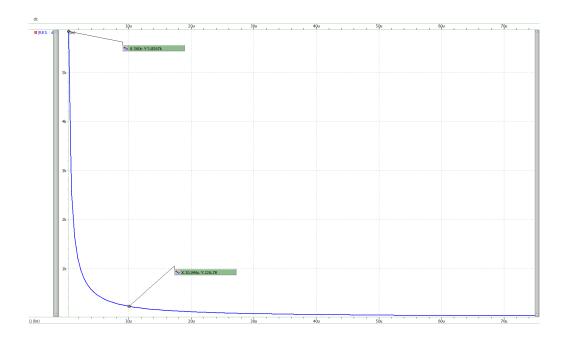

| 3.14 | Startup response                                                                       | 47 |

| 3.15 | Bandgap circuit feedback loops                                                         | 48 |

xvi LIST OF FIGURES

|      | Bandgap circuit feedback loops                                                    | 50  |

|------|-----------------------------------------------------------------------------------|-----|

| 3.17 | Multiple inflection points                                                        | 54  |

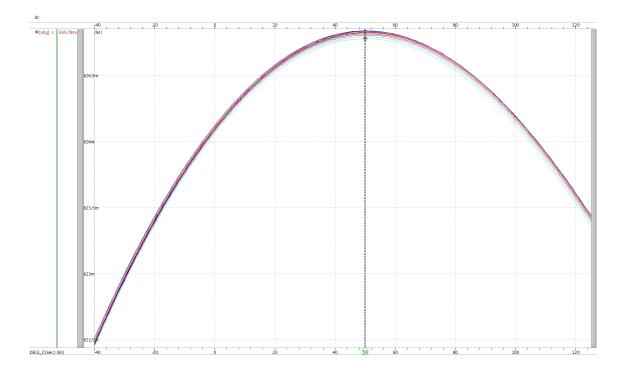

| 3.18 | Temperature behavior at typical corners, Vdd=1.62                                 | 55  |

| 3.19 | Test-bench for bandgap voltage reference line regulation                          | 56  |

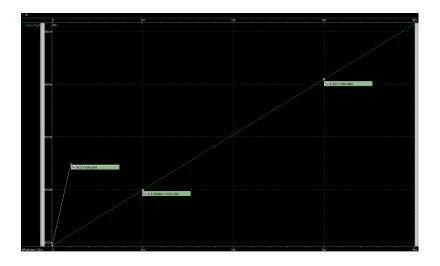

| 3.20 | Line regulation for typical corners at 27°C                                       | 57  |

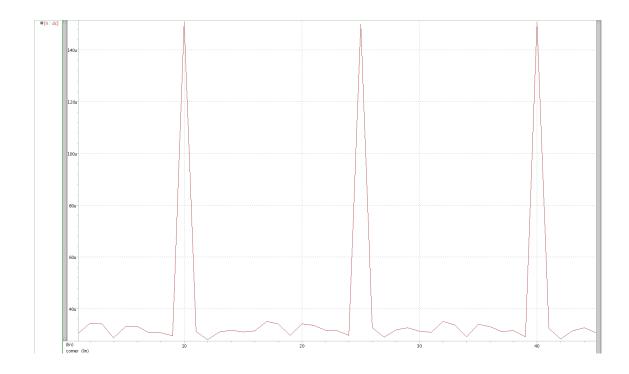

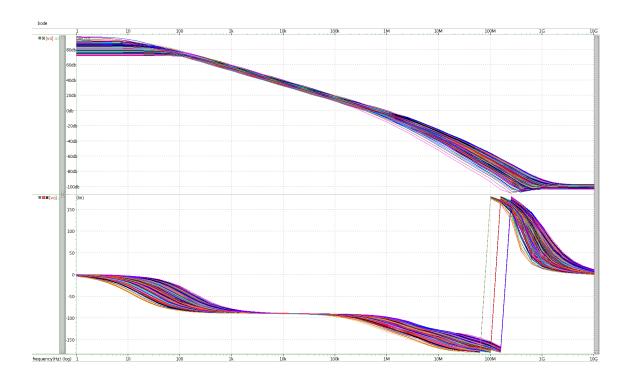

| 3.21 | PSRR at 27°C and Supply voltage 2V                                                | 58  |

|      | Output variation due to offset voltage                                            | 63  |

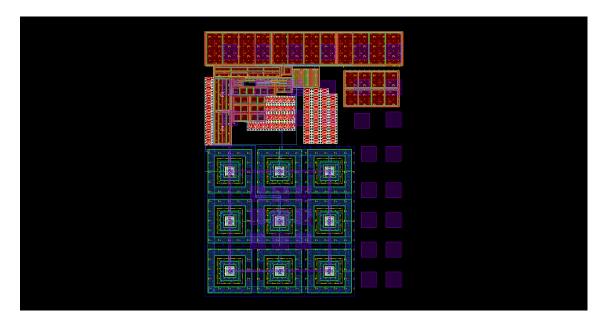

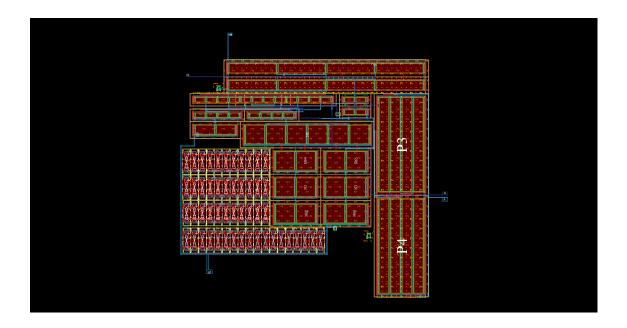

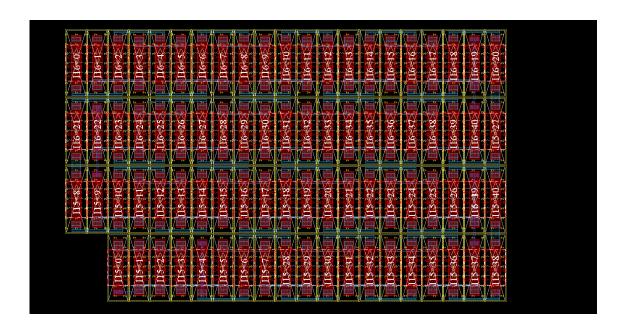

|      | Complete Layout of the Bandgap Voltage Reference                                  | 65  |

|      |                                                                                   |     |

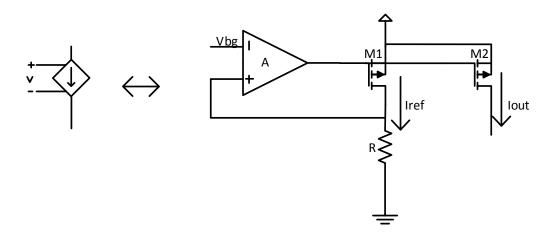

| 4.1  | Voltage to Current Converter                                                      | 68  |

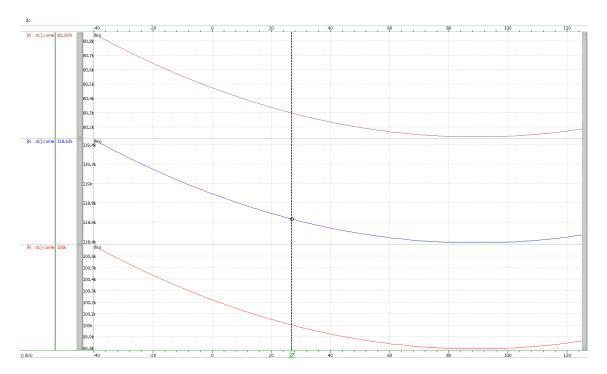

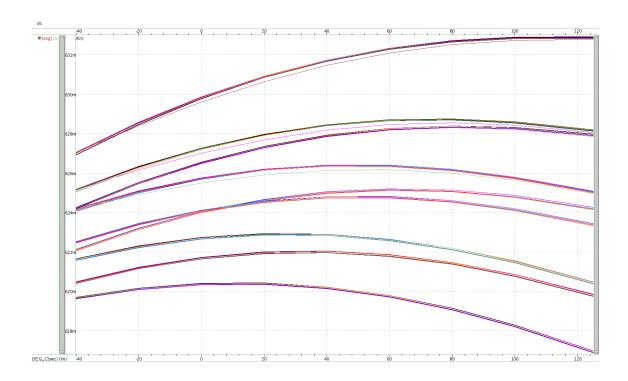

| 4.2  | $100k\Omega$ resistor temperature variation at fast, slow and typical corners     | 69  |

| 4.3  | Programmable resistor topology                                                    | 71  |

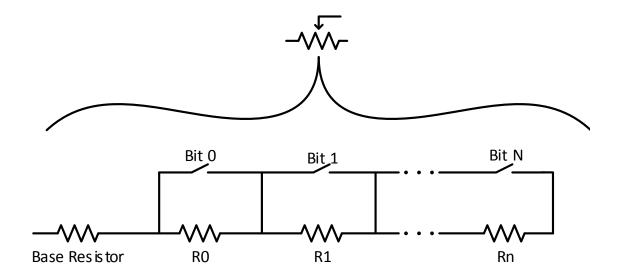

| 4.4  | On Resistance variation with increasing W at typical corners                      | 74  |

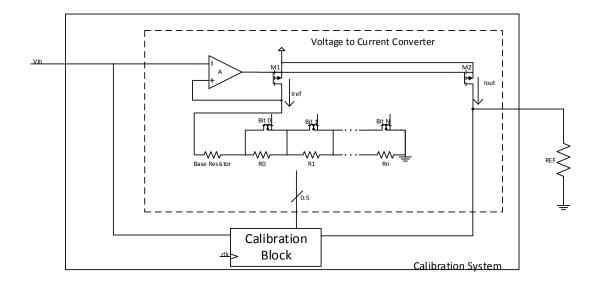

| 4.5  | Voltage to Current Converter System                                               | 75  |

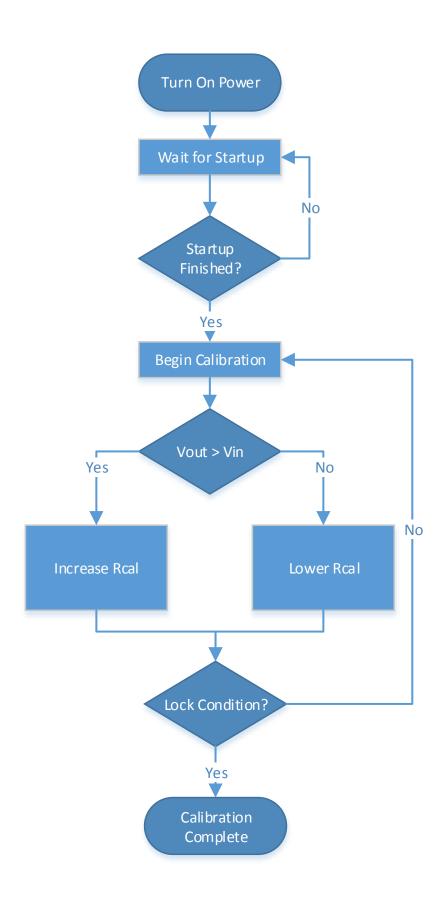

| 4.6  | Calibration Algorithm                                                             | 77  |

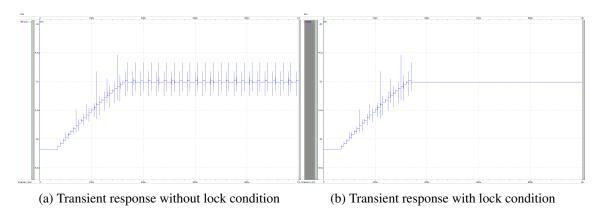

| 4.7  | Transient response at typical corner, supply voltage 2.5V and room temperature    | 78  |

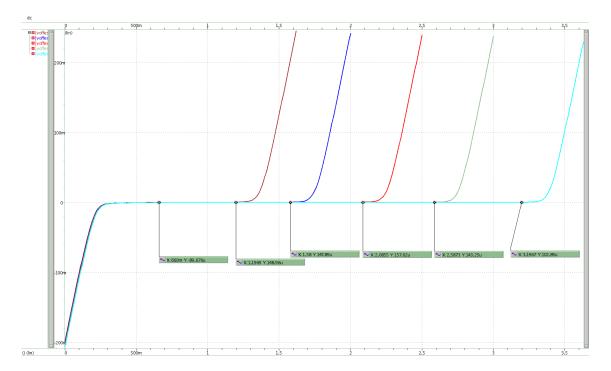

| 4.8  | Calibration Block Module                                                          | 79  |

| 4.9  | Post-Calibration variation with temperature and supply                            | 82  |

| 4.10 | Output current shift due to load variation                                        | 84  |

| 5.1  | Auto-zeroing with offset storage                                                  | 88  |

| 5.2  | Basic Chopper Technique                                                           | 88  |

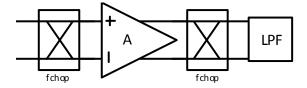

| 5.3  |                                                                                   | 89  |

| 5.4  | Folded cascode amplifier with choppers                                            | 90  |

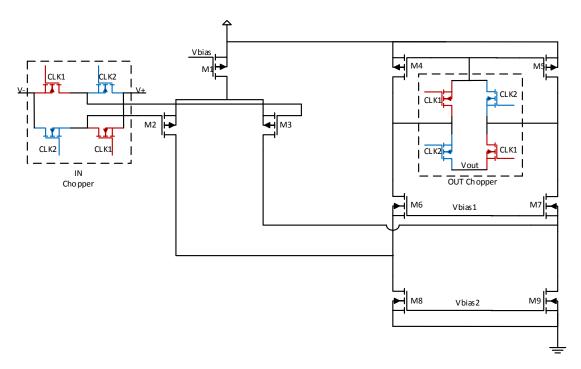

| 5.5  | Chopping Stages                                                                   | 90  |

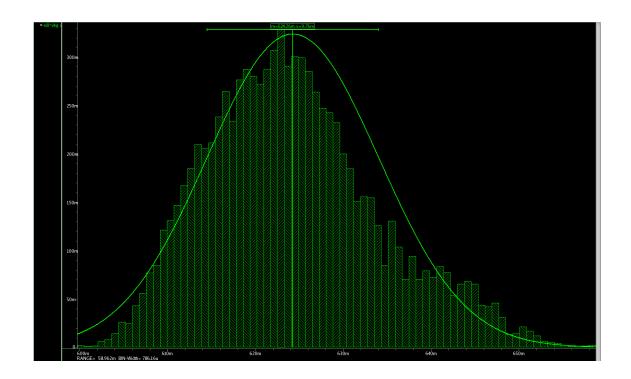

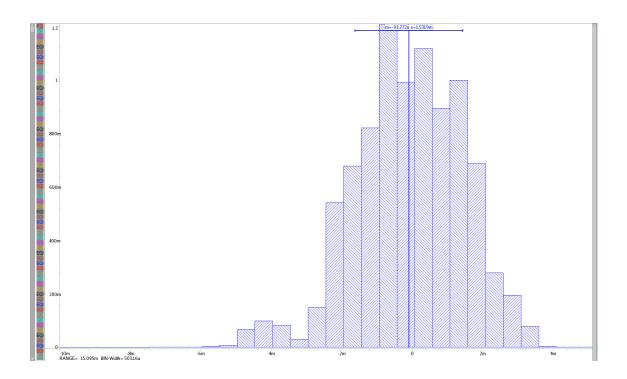

| 5.6  | Voltage drift from nominal value (0.7V) at 27°C, supply = 1.62 V, all corners and | 91  |

| 3.0  | 200 MC                                                                            | 92  |

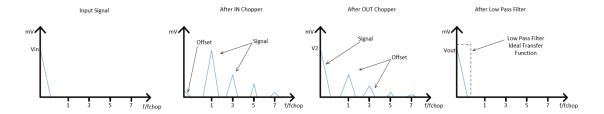

| 5.7  | Output voltage behavior due to chopping amplifier                                 | 94  |

| 5.8  | Jumping Bandgap Voltage Core with Chopped Amplifier                               | 96  |

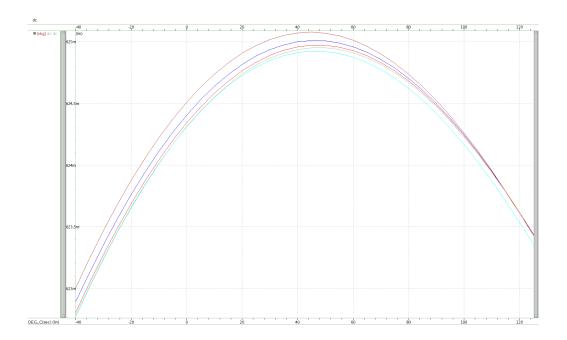

| 5.9  | Output Voltage Variation of the Jumping Bandgap under PVT                         | 97  |

|      |                                                                                   | 101 |

| A.1  | Output Voltage Variation with Temperature and Supply Voltage at Typical Corners   | 101 |

| A.2  | Output Voltage Variation at all corners                                           | 102 |

| A.3  | Output Voltage Variation under PVT                                                | 102 |

| A.4  | Line Regulation at all corners                                                    | 103 |

| A.5  | Line Regulation under PVT                                                         | 103 |

| A.6  | Line Regulation under PVT                                                         | 104 |

| A.7  | Output Voltage Variation with Temperature and Supply Voltage at Typical Corners   | 104 |

| A.8  | Power Consumption under PVT                                                       | 105 |

| A.9  | Gain and Phase Margin under PVT                                                   | 106 |

|      | Gain and Phase Margin under PVT                                                   | 106 |

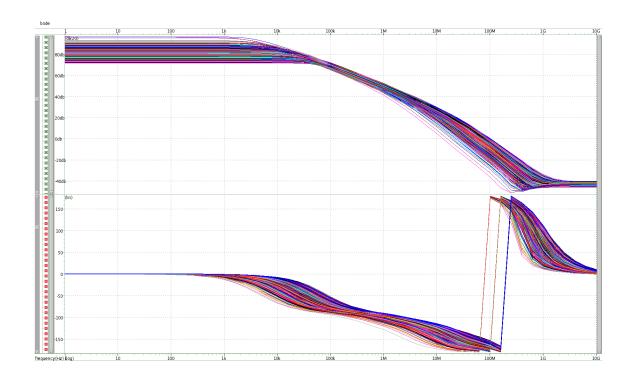

|      | Gain and Phase Margin under PVT with Mosfet Load                                  | 107 |

|      | Input Offset under PVT                                                            | 107 |

|      | Power Consumption under PVT                                                       | 108 |

|      | PSRR under PVT                                                                    | 108 |

|      | BJT Mismatch under PVT                                                            | 109 |

|      | Mosfet Mismatch under PVT                                                         | 109 |

|      | Resistor Mismatch under PVT                                                       | 110 |

| A.18 | Amplifier Offset under PVT                                                        | 110 |

| LIST OF FIGURES | xvii |

|-----------------|------|

|                 |      |

| B.1 | Overall Precision under Device Mismatch                            | 116 |

|-----|--------------------------------------------------------------------|-----|

| B.2 | PSRR under PVT                                                     | 116 |

| B.3 | Calibration under All Corners                                      | 117 |

| C.1 | Offset Behavior after Low Pass Filter                              | 119 |

| C.2 | Offset before chopping under PVT 1000 MC                           | 120 |

| C.3 | Offset after chopping under PVT 1000 MC                            | 120 |

| C.4 | Offset under PVT                                                   | 121 |

| C.5 | Bandgap Voltage Variation with Chopped Amplifier under PVT         | 121 |

| C.6 | Dynamic Bandgap Voltage Variation with Chopped Amplifier under PVT | 122 |

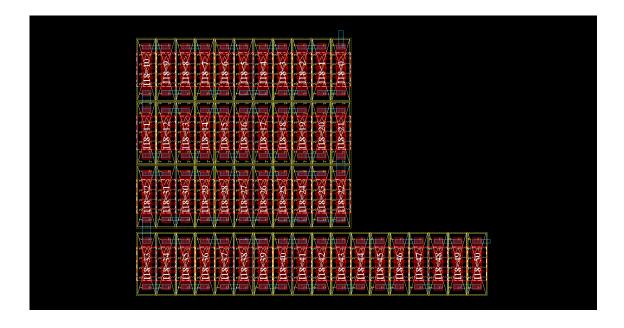

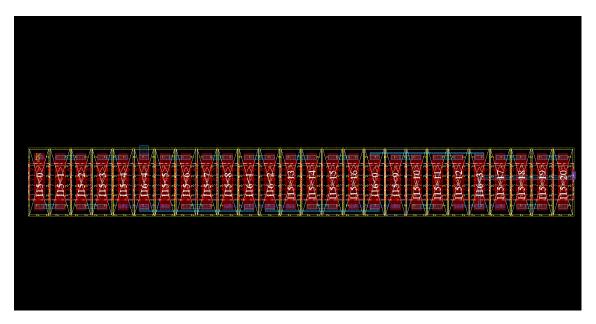

| D.1 | Layout of the PMOS input differential pair                         | 123 |

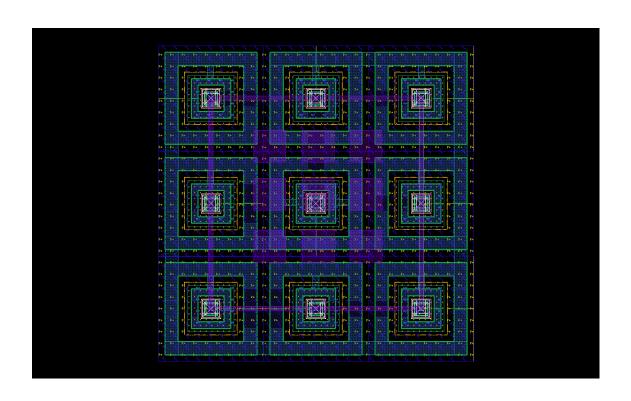

| D.2 | Layout of the bias current mirror                                  | 124 |

| D.3 | Layout of the bias resistor                                        | 124 |

| D.4 | Layout of the Folded Cascode Amplifier                             | 125 |

| E.1 | Layout of the BJT devices                                          | 127 |

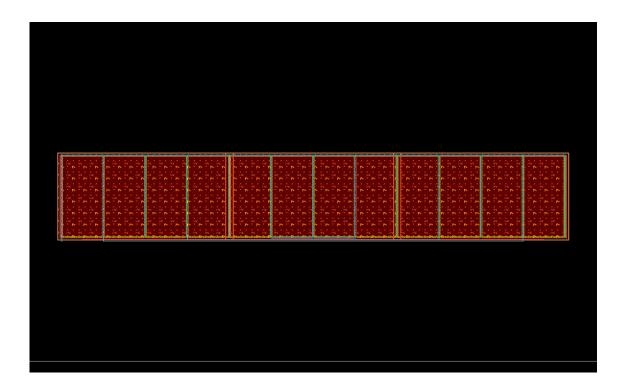

| E.2 | Layout of the PMOS current mirrors                                 | 128 |

| E.3 | Layout of the resistors R2 and R3                                  | 128 |

| E.4 | Layout of the resistors R1 and R4                                  | 129 |

xviii LIST OF FIGURES

# **List of Tables**

| 2.1  | Comparison between Current & Voltage References                                    | 28  |

|------|------------------------------------------------------------------------------------|-----|

| 3.1  | Constant-Transconductance Bias Circuit Element Values                              | 40  |

| 3.2  | Folded Cascode Amplifier Element Values                                            | 42  |

| 3.3  | Folded Cascode Amplifier Parameters                                                | 45  |

| 3.4  | Folded Cascode Amplifier Parameters (Post-Layout Simulations)                      | 45  |

| 3.5  | Calculated current usage vs. Simulated values                                      | 52  |

| 3.6  | Current usage for worst and best scenarios for typical corners                     | 52  |

| 3.7  | Temperature Coefficients for worst, typical and best cases                         | 55  |

| 3.8  | Line regulation coefficients for worst, typical and best case scenarios at typical |     |

|      | corners                                                                            | 57  |

| 3.9  | Temperature Coefficients for worst, typical and best cases                         | 58  |

| 3.10 | PSRR at DC                                                                         | 59  |

|      | PSRR at 1 kHz                                                                      | 59  |

|      | Bandgap Voltage Reference Parameters                                               | 59  |

|      | Bandgap Voltage Reference Parameters (Post-Layout Simulations)                     | 60  |

|      | Sources of Error. Analytical Values vs. Simulated Values                           | 63  |

| 3.15 | Relative magnitude of the various sources in the overall error                     | 64  |

| 4.1  | Comparison between calibration methods                                             | 76  |

| 4.2  | Calculated current usage vs. Simulated value                                       | 81  |

| 4.3  | Variation with bandgap reference for worst, typical and best corners               | 82  |

| 4.4  | Variation with bandgap reference for worst, typical and best corners               | 83  |

| 4.5  | Characteristics of the Voltage to Current converter with bandgap voltage reference | 85  |

| 5.1  | Chopped Folded Cascode Amplifier Parameters                                        | 93  |

| 5.2  | Bandgap Voltage Reference with Chopped Amplifier Results                           | 94  |

| 5.3  | Jumping Bandgap Core with Chopped Amplifier Results                                | 97  |

| B.1  | Calibration Codes for all corners                                                  | 115 |

xx LIST OF TABLES

# **Abbreviations and Symbols**

$\beta = u_n C_{ox}$  Beta of the mosfet

$C_{ov}$  Overlap Capacitance per unit width  $C_{ox}$  Gate-Oxide Capacitance Per Unit Area CTAT Complementary to Absolute Temperature

$E_{eff}$  Average Transverse Electric Field

$E_g$  Energy Bandgap

*DEM* Dynamic Element Matching

fchopChopping Frequency $G_m$ Transconductance $\gamma$ Body-Effect Constant $I_D$ Mosfet Drain Current $I_C$ BJT Collector Current $I_S$ BJT Saturation Current

$\phi_F$  Fermi Potential

$\phi_{ms}$  Metal-Silicon Work Function

$K_b$  Boltzmann Constant L Channel Length MC MonteCarlo

$N_A$  Acceptor Concentration  $N_c$  Extrinsic Carrier Concentration

$N_D$  Donor Concentration

$n_i$  Intrinsic Carrier Concentration PTAT Proportional to Absolute Temperature  $Q_{ss}$  Surface-State Charge Density Per Unit Area  $\rho$  BJT process dependent temperature constant  $S_{LR,T(nom)}$  Line Regulation at nominal temperature

T.C.Temperature Coefficient **Gate-Oxide Thickness**  $t_{ox}$ **Impurity Scattering**  $\mu_{cb}$ Carrier Mobility  $u_{n/p}$ Lattice Vibration  $\mu_{ph}$ Base-Emitter Voltage  $V_{BE}$ Bandgap reference voltage  $V_{bg}$  $V_{DS}$ Drain-Source Voltage Mosfet Saturation Voltage  $V_{DSAT}$

$V_{G0}$  Bandgap Voltage of the silicon at 0K

$V_{GS}$  NMOS Gate-Source Voltage

$V_{OV}$  Override Voltage

*V<sub>SG</sub>* PMOS Source-Gate Voltage

$V_T$  Thermal Voltage  $V_{TH}$  Threshold Voltage W Channel Width  $Z_{out}$  Output Pole

ZTC Zero Temperature Coefficient Point

### Chapter 1

### Introduction

#### 1.1 Motivation

Most, if not all electrical circuits, use a reference, be it voltage or current. A reference in a circuit establishes a stable point used by other sub-circuits to generated predictable and repeatable results. This reference point should not change significantly under various operating conditions. Temperature is an important parameter which affects the performance of references. Special attention should therefore be paid by the designer to the temperature behavior of the reference.

Current references are used in most of the basic building blocks. Usually, the current in different basic blocks results from mirroring of one or more references. Therefore, it is important that the master current of the system to be PVT independent and designed with the required accuracy.

Voltage references have been used in various fields of application, for example in digital to analog (D/A) converters, the automotive industry and in battery-operated DRAMs. In D/A converters, depending on the digital input signal, the analog voltage is a fraction of the internal reference voltage. As for many applications this digital to analog conversion should not depend on temperature, so the reference voltage has to be temperature-independent. Nowadays, high resolution D/A converters are being used and consequently the reference voltage must be very stable as each variation in the reference voltage is directly sensed in the D/A-converter output.

In the automotive industry, electronic circuits are used to realize larger systems with more functions. However, the automotive environment is very extreme and the temperature variations can be in the range of -40°C to 125°C. Similarly, in battery-operated DRAMs, voltage references are used for power-supply voltage stabilization. In this case, the power consumption is of prime importance.

Bandgap voltage references are the most popular precise references used in various circuits. A bandgap voltage reference (BGR) has high power rejection and its output voltage is very stable against temperature and process variations. It can be implemented using available, vertical or lateral BJTs in any standard CMOS technology [11], [17]. However, when the supply voltage falls below 1 V, the performance of a conventional bandgap reference degrades.

2 Introduction

As an alternative, voltage references can also be implemented in MOS technology using the threshold voltage difference [22]. But this solution requires multi-threshold transistors, often recurring to use the threshold voltages of a PMOS and NMOS.

#### 1.2 Specifications and Objectives

Before we begin, it is necessary to understand in what technology and conditions we will be working with, but also the goals to achieve with this work.

This work was built with 40nm CMOS technology. During our work, we will be using high voltage mosfets with minimum dimensions of W = 0.36um and L = 0.27um. Bipolar junction transistors will be of PNP-type and have a fixed area of  $256um^2$ . Process resistors were built with polysilicon material over P-type substrate.

We wish to achieve a precision of  $\pm 5\%$  variation over PVT conditions. To reach this objective, we will be resorting to topologies robust to process variations, calibration blocks and dynamic process compensation methods.

| Objective          | Process | Voltage        | Temperature    |

|--------------------|---------|----------------|----------------|

| $\Delta < \pm 5\%$ | 40nm    | 1.62V to 3.63V | -40°C to 125°C |

#### 1.3 Structure of the Document

This document as the following structure:

- Chapter 2 provides a theoretical background regarding the basic properties of semiconductors, the temperature behavior of several parameters of the mosfets with particular focus on the bipolar transistors. It also includes an introduction to switched capacitors and other resistor architectures. All of these concepts are introduced in this chapter in order to familiarize the reader to some of the specific topics used in this work. This chapter also presents the bibliographical review on voltage and current references. This chapter includes several topologies and an overall comparison between all studied articles.

- In Chapter 3, the steps behind the design of a bandgap voltage reference are presented along with detailed analysis of the behavior of several parameters that constitute the used topology. The results of the simulation are also contained in this chapter.

- Chapter 4 presents the voltage to current converter stage and shows the steps and decisions

made in the design of this module. The simulation results along with extensive analysis are

also presented.

- Chapter 5 presents dynamic compensation techniques for random process deviations. This

chapter provides the steps to designing a dynamically offset compensated amplifier along

with detailed analysis of the topology and results obtained once this amplifier has been

3

integrated in the voltage reference. It also integrates the same techniques on the bandgap and shows the overall results.

• Chapter 6, which is the final chapter, presents the conclusion obtained in this work along with proposals for future improvements in the developed circuits.

4 Introduction

### Chapter 2

# **Background and State of the Art**

In this chapter, we consider some basics properties of semiconductor materials with particular emphasis on temperature dependence. This will be followed by a focus on temperature dependency of the threshold voltage and carrier mobility of the MOS transistor, and particular focus on the temperature behavior of the bipolar transistor.

This will be followed by a brief description of process corners and MonteCarlo iterations which will be used extensively in this work. Several resistor architectures are also explored since these components will be required in this work as well.

Finalizing, this chapter will contain the current state of the art regarding both voltage and current references and their development through the years.

#### 2.1 Mosfet Fundamentals

In this section we will be reviewing the basic properties of mosfet devices.

• Energy Bandgap: The difference in energy between the valence band and the conduction band is called energy bandgap or simply bandgap, and is represented by  $E_g$ .  $E_g$  is the necessary energy in eV to create an electron/hole and is calculated by [14]

$$E_g(T) = E_g(0) - \frac{\alpha T^2}{T + \beta}$$

(2.1)

where  $E_g(0)$  is the energy bandgap at 0 K, T is the absolute temperature in K,  $\alpha$  and  $\beta$  are material constants. For the particular case of silicon, these values are 1.17,  $4.73 \times 10^{-4}$  and 636 respectively, as shown below.

$$E_g(T) = 1.17 - \frac{4.73 \times 10^{-4} T^2}{T + 636}$$

(2.2)

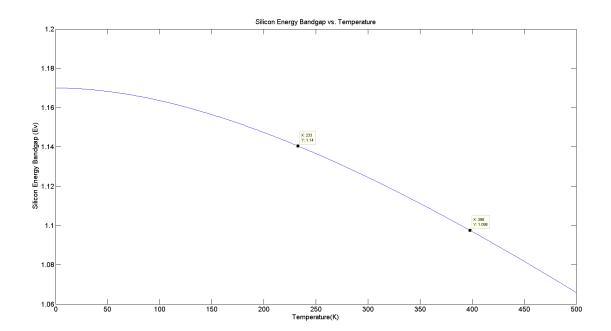

Figure 2.1: Silicon Energy Bandgap vs. Temperature

Figure 2.1 shows the energy bandgap variation with temperature. It can be seen from the plot that the energy value at 0K is roughly 1.17V, since the additional factor is small and can be neglected at this temperature. The two highlighted values correspond to the specific temperature range being considered in this work. As it can be seen, even for a broad temperature range -40°C to  $125^{\circ}$ C,  $E_g$  has a weak temperature dependence.

**Intrinsic Carrier Concentration:** The intrinsic carrier concentration,  $n_i$ , is the concentration of electrons in the conduction band per unit volume, at a given temperature T, in a semiconductor that is completely free of impurities or defects.

This concentration is given by

$$n_i = N_s e^{\left(-\frac{E_g}{2K_bT}\right)} \tag{2.3}$$

where  $E_g$  is the energy bandgap,  $K_b$  is the Boltzmann constant and T is the temperature in Kelvin. It is worth noting that the concentration of electrons in the conduction band is equal to the concentration of holes in the valence band. For the particular case of silicon, a commonly accepted value is  $9.65 * 10^9 cm^{-3}$  at room temperature (300 K). [1]

Extrinsic Carrier Concentration: The extrinsic carrier concentration,  $N_c$ , comes from the introduction of different atoms, called *dopant* atoms, into the previously pure material and can be expressed as

$$N_C = \begin{cases} \frac{N_D - N_A}{2} + \sqrt{\left(\frac{N_D - N_A}{2}\right)^2 + n_i^2}, & \text{n-type (electron concentration)} \\ \frac{N_A - N_D}{2} + \sqrt{\left(\frac{N_A - N_D}{2}\right)^2 + n_i^2}, & \text{p-type (hole concentration)} \end{cases}$$

(2.4)

2.1 Mosfet Fundamentals 7

where  $N_D$  and  $N_A$  are the donor and acceptor concentration, respectively. As long as the impurity concentration  $|N_A - N_D|$  is much large than  $n_i$ , the intrinsic carrier concentration, will be approximately equal to the subtract doping.

**Fermi Level:** For an intrinsic semiconductor, the Fermi level lies around midway between the valence and conduction bands. For n-type materials, the Fermi level is closer to the conduction bands while for p-type material it is closer to the valence band. The value of the Fermi level depends on temperature due to the temperature dependence of  $n_i$  and the thermal voltage,  $V_T = \frac{kT}{q}$  and is given by

$$\phi_F = \pm \frac{kT}{q} ln(\frac{n_c}{n_i(T)}) \tag{2.5}$$

where the positive or negative sign refers to the n-type of p-type material, respectively.

#### 2.1.1 Threshold Voltage

A commonly used expression for the threshold voltage of the MOS transistor is given by

$$V_{th} = \phi MS \pm \frac{Q_{ss}}{C_{ox}} + 2\phi_F \pm \gamma (\sqrt{|V_{SB} + 2\phi_F|} - \sqrt{|2\phi_F|})$$

(2.6)

where the positive and negative signal refers to n-channel or p-channel MOS devices, respectively. In this equation,  $\phi_{ms}$  is the metal-silicon work function,  $Q_{ss}$  is the surface-state charge density per unit area,  $C_{ox}$  is the gate-oxide capacitance per unit area,  $\phi_F$  is the Fermi potential and  $\gamma$  is the body-effect constant that depends on the subtract doping  $N_s$ , the gate-oxide thickness  $t_{ox}$ , the channel length L and the width W.

The gate-semiconductor work function,  $\phi_{MS}$ , is expressed as

$$\phi_{MS}(T) = \begin{cases} -\frac{kT}{q} ln(\frac{N_s N_p}{n_i^2}), & (NMOS) \\ -\frac{kT}{q} ln(\frac{N_s}{N_p}), & (PMOS) \end{cases}$$

$$(2.7)$$

where  $N_p$  is the carrier concentration in the polysilicon gate. The temperature dependent terms are the intrinsic carrier concentration,  $n_i$ , and the thermal voltage,  $\frac{kT}{a}$ .

From a first look at the threshold voltage and taking into account both the Fermi level equation (2.5) and the  $\phi_{MS}$  work function, we can see that the bigger contributors for the threshold voltage variation with temperature are the Fermi level,  $\phi_F$ , and the gate-semiconductor work function,  $\phi_{MS}$ .

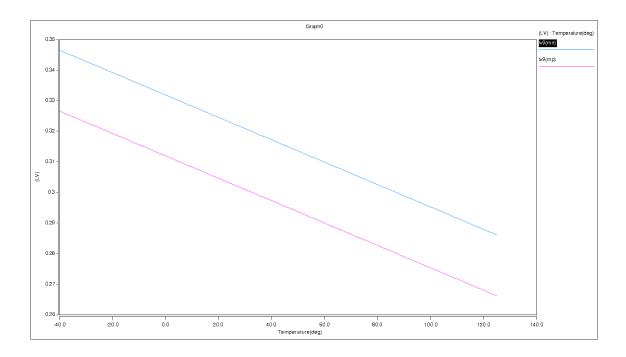

Figure 2.2: Absolute value of the threshold voltage variation of a typical PMOS and NMOS transistor (W/L=1u/1u). FreePDK 45nm CMOS Technology

It can be seen from figure 2.2 that the threshold voltage decreases almost linearly with temperature in both cases. Although this non-linearity is fairly small, and usually ignored in the first order approximations, is still noticeable. A careful analysis of the difference between both thresholds voltages (NMOS and PMOS) shows a PTAT behavior. There are in fact voltage and current references based on this very same behavior. [22] [18]

#### 2.1.2 Carrier Mobility

We pay particular attention to the temperature dependence of the mobility as it is one of two main factors (the other is threshold voltage) in the temperature behavior of a mosfet. The carrier mobility,  $\mu(cm^2/Vs)$ , describes the drift velocity of a particle in an applied electrical field. The carrier mobility has a very complex temperature dependence, defined by the interplay of several parameters. The two major contributors are the lattice vibration,  $\mu_{ph}$ , and impurity scattering,  $\mu_{cb}$ . [7] [21]

The temperature behavior of the lattice vibration is given by

$$\frac{1}{\mu_{ph}} \propto T^{\frac{3}{2}} E_{eff}^{\frac{1}{3}} \tag{2.8}$$

and the impurity scattering is

$$\frac{1}{\mu_{cb}} \propto T^{-1} E_{eff}^{-2}$$

(2.9)

where T is the absolute temperature in Kelvin and  $E_{eff}$  is the average transverse electric field.

2.1 Mosfet Fundamentals 9

Lattice vibration results from thermal vibrations of the atoms at any temperature higher than absolute zero (0 K). As the temperature increases, the carrier move faster and thus this factor dominates. Thus, at high temperatures, the mobility,  $\mu$ , will be proportional to  $T^{\frac{3}{2}}$ . On the other side, at lower temperatures the atoms have low kinetic energy and thus impurity scattering dominates.

Based on 2.8 and 2.9 we can finally write the temperature behavior of the carrier mobility as the sum of both factors.

$$\frac{1}{\mu} \propto \frac{1}{\mu_{cb}} + \frac{1}{\mu_{ph}} \tag{2.10}$$

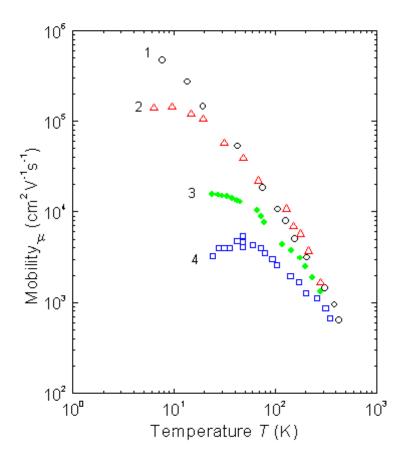

.http://www.ioffe.ru/SVA/NSM/Semicond/Si/electric.html#Hall

Figure 2.3: Electron mobility versus temperature for different doping levels. High purity to increased doping levels respectively (reprinted from the link above)

From figure 2.3, it is clearly visible the previous assumptions. We have four different doping levels represented. From high purity (1,2) to increased doping levels (3,4). They all converge to the

same value at high temperatures, proving that lattice vibration dominates at higher temperatures. Please note that the temperature behavior appears linear due to the use of a logarithmic scale.

#### 2.1.3 Zero Temperature Coefficient Point

The Zero Temperature Coefficient Point or simply ZTC point is a certain voltage level that when applied to the gate of a MOS device will internally nullify temperature variation. Both the threshold voltage and the carrier mobility of a mosfet are dependent on temperature, as seen in previous sections [2]. For carefully sized MOS transistors with channel doping concentration on the vicinity of 10<sup>15</sup> the output current becomes temperature independent in the ZTC point.

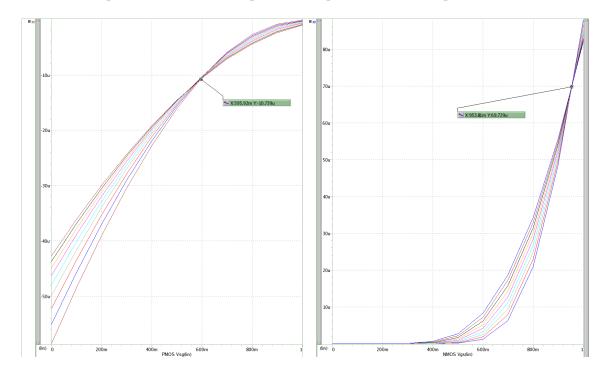

Figure 2.4: ZTC bias point for both PMOS and NMOS respectively in typical conditions.  $I_D$  vs  $V_{GS}$  at different temperatures

As we can see in the figure above, by biasing the gate voltage of a mosfet at approximately 0.605 V, the device will provide a current that is invariant to temperature shifts. This type of compensation works similarly to the PTAT and CTAT sum since with precise sized mosfets, the internal temperature dependences cancel each other out.

The mosfet current is modeled by

$$I_d = \frac{u_n C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(2.11)

In equation 2.11, the carrier mobility,  $\mu$ , and the threshold voltage,  $V_{TH}$ , are the major temperature dependent parameters. Both of these quantities diminish as the temperature goes up. However, they have an opposite effect on the drain current. As the mobility goes down, so does

2.2 BJT Fundamentals

the current. But, as the threshold voltage goes down, the drain current goes up due to the  $V_{GS} - V_{TH}$  difference.

The ZTC bias point is a certain voltage level in which the changes in electron mobility and threshold voltage compensate each other. A transistor biased at this point will have minimal variation in its saturation current over temperature.

As it is visible in figure 2.4, a PMOS and NMOS biased at approximately 595mV and 953mV respectively, will be fairly independent of temperature due to mutual compensation.

#### 2.2 BJT Fundamentals

In this section we will be reviewing the basic properties of BJT devices.

#### 2.2.1 Base-Emitter Voltage

In voltage references, the BJT (Bipolar Junction Transistor) is usually connected in the diode configuration (i.e., the base terminal and the collector terminal are tied together), such that the Base-Emitter Voltage,  $V_{BE}$ , is used to provide a fixed junction voltage. However, the junction voltage is temperature dependent and cannot be used as a voltage reference by itself.

Neglecting the Early effect, the collector current density of a NPN transistor biased in the forward active region is given by,

$$J_C(T)A_E = J_S(T)A_E e^{(\frac{V_{BE}}{V_T})}$$

(2.12)

where  $A_E$  is the emitter area,  $J_S$  is the saturation current density, T is the absolute temperature in Kelvin,  $J_C$  is the current density and  $V_T$  is the thermal voltage,  $V_T = \frac{kT}{q}$ . Since the emitter area is constant we usually consider the collector current as,

$$I_C(T) = I_S(T)e^{(\frac{V_{BE}}{V_T})}$$

(2.13)

where  $I_C$  is the collector current and  $I_S$  is the saturation current.

Without going into further details of semiconductor physics we quote the base-emitter voltage from [20].

$$V_{BE}(T) = V_{G0}(1 - \frac{T}{T_0}) + V_{BE}(T_0) - \frac{\rho kT}{q} ln(\frac{T}{T_0}) + \frac{kT}{q} ln(\frac{J_C(T)}{J_C(T_0)})$$

(2.14)

where,  $V_{G0}$  is the bandgap voltage of the silicon at 0K, which is around 1.17V but subjected to the technology in use,  $V_{BE}$  is the bandgap voltage at temperature  $T_0$  and  $\rho$  is a process dependent temperature constant.

Figure 2.5: Base-Emitter voltage temperature variation of diode connected BJT biased at 5u.  $256um^2$  BJT and  $8x256um^2$  BJT

Figure 2.5 shows the behavior of the base-emitter voltage of two diode connected BJT biased at the same current but with different areas. It stands to reason that the BJT with higher area has a lower  $V_{BE}$ . Looking at the last term of 2.14,  $\frac{kT}{q}ln(\frac{J_C(T)}{J_C(T_0)})$ , the current density is the current divided by the area, and since both BJT are biased with the same current, the BJT with higher area would produce a smaller base-emitter voltage.

We can clearly see that the temperature variation is not linear since the difference between both BJT clearly increases. However, in the first order approximation we consider this voltage linear. To the process in cause, the slope is approximately -1.5mV/°C.

Such temperature characteristic is called Complementary to Absolute Temperature (CTAT), where the rate of change of base-emitter voltage against the temperature is negative.

**Differential Base-Emitter Voltage:** This voltage is heavily used in bandgap voltage references. The key factor to understand is that while  $V_{BE}$  goes down with temperature (CTAT), the difference between both  $V_{BE}$  seems to increase with temperature. We call this characteristic, Proportional To Absolute Temperature (PTAT), since the rate increases with temperature.

Let's look at equation 2.14 and assume that both BJT are biased with same current but the second BJT has a higher emitter area. We will call this area difference N, such that  $A_{E2} = NA_{E1}$

$$V_{BE1}(T) - V_{BE2}(T) = V_{G0}(1 - \frac{T}{T_0}) + V_{BE}(T_0) - \frac{\rho kT}{q} ln(\frac{T}{T_0}) + \frac{kT}{q} ln(\frac{J_{C1}(T)}{J_{C1}(T_0)}) - [V_{G0}(1 - \frac{T}{T_0}) + V_{BE}(T_0) - \frac{\rho kT}{q} ln(\frac{T}{T_0}) + \frac{kT}{q} ln(\frac{J_{C2}(T)}{J_{C2}(T_0)})]$$

(2.15)

2.3 Resistor Architectures

Looking at 2.15 we can see that the only difference is the last term because the second BJT has a higher area than the first. If both BJT have the same current but one of them has higher area, it stands to reason that the bigger one will have smaller current density. Taking this into account we can narrow this difference to,

$$V_{BE1}(T) - V_{BE2}(T) = \frac{kT}{q} ln(\frac{J_{C1}(T)}{J_C(T_0)}) - \frac{kT}{q} ln(\frac{J_{C2}(T)}{J_C(T_0)})$$

(2.16)

13

Now changing the current density into current using the BJT area we get,

$$V_{BE1}(T) - V_{BE2}(T) = \frac{kT}{q} \left[ ln(\frac{I_{C1}}{A_{E1}}) - ln(\frac{I_{C2}}{A_{E2}}) \right]$$

(2.17)

But both  $I_{C1}$  and  $I_{C2}$  are equal. Thus we get,

$$V_{BE1}(T) - V_{BE2}(T) = \frac{kT}{a} ln(\frac{A_{E2}}{A_{E1}}) = \frac{kT}{a} ln(N)$$

(2.18)

As we can see from 2.18, the difference between the  $V_{BE}$  of two BJT with different areas but biased with equal currents is clearly PTAT. If we take the derivate of 2.18 against temperature,

$$\frac{\delta \Delta V_{BE}}{\delta T} = \frac{k}{q} = \frac{1.3806 * 10^{-23}}{1.602 * 10^{-19}} \approx 0.09 mV/^{\circ}C$$

(2.19)

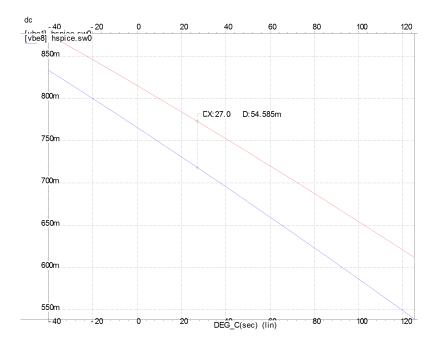

where k is the Boltzman constant and q is electrical charge on the electron. It we look back at 2.5 we see the highlighted difference between both  $V_{BE}$  at 27°C, which equals 54.585 mV.

Taking equation 2.18 and calculating with with N = 8 and  $T = 300K(27^{\circ}C)$  we get,

$$V_{PTAT} = \frac{1.3806 * 10^{-23}}{1.602 * 10^{-19}} ln(8) \approx 53.76 mV$$

(2.20)

This theoretical value is very close to the simulated one.

The main idea behind bandgap voltage references is adding these two voltages in order to eliminate the temperature dependence. We will be seeing this in the next chapter.

#### 2.3 Resistor Architectures

Either we wish or not, this type of circuits will always need some type of resistor to produce the desired current. There are three solutions for this problem. The first solution is using a MOSFET in ohmic mode, thus the name of this region. A MOSFET can operate as variable resistor although there are several drawbacks. The linearity is poor and is dependent of the biasing voltage.

If  $V_{GS} > V_{TH}$  and  $V_{DS} < V_{GS} - V_{TH}$ , and the mosfet will operate in triode region, also called ohmic region. The resistance of the channel is modeled by (assuming  $V_{DS} << V_{GS} - V_{TH}$ ),

$$r_{DS} = \frac{1}{\mu_n C_{ox}(\frac{W}{L})(V_{GS} - V_{TH})}$$

(2.21)

The second solution is simply using a physical resistor. There are a few disadvantages with using a resistor in high level integrations. Take for example a supply voltage of 1.25 V, like the standard bandgap reference, and you wish an output current of 1uA. This would require a  $1.25M\Omega$  which would take a lot of area in the die. Not to mention the resistors are non-linear and the tolerances are large.

Process resistors have the advantage of not requiring any voltage level to create the resistance unlike mos resistors. Therefore, creating precision resistors using triode mosfet devices is more difficult.

Figure 2.6: Resistor variation versus temperature over typical, slow and fast corner.

Looking at figure 2.6, we see that the temperature variation of the resistor is fairly linear, only changing 0.8% over 165 degrees. However, the resistance varies a lot over process corners. The figure shows a  $15k\Omega$  typical resistor at all three corners. It can be seen that at typical conditions the resistor maintains the desired value. However, there is nearly a 25% difference between the typical and fast corner.

#### 2.3.1 Switched-Capacitor Resistor

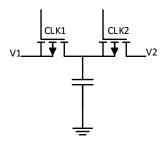

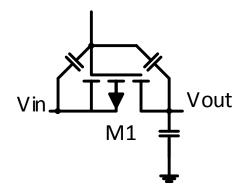

Figure 2.7: Switched Capacitor

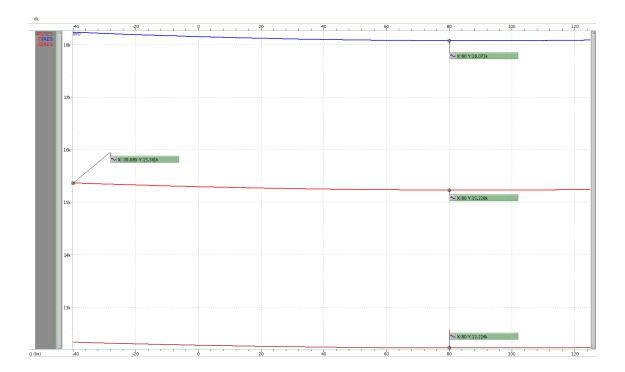

The other option, and the most obvious solution to large resistors, is the use a switched-capacitor resistor, shown in figure 2.7. Instead of using a physical resistor, we can "simulate" one by controlling the charge and discharge of a capacitor. This circuit simulates the behavior of a normal resistor, with a few added benefits. [11] [4] [9]

The capacitor ratios can be tightly controlled, providing a more stable current overall, and by controlling the signal going into  $\phi 1$  and  $\phi 2$ , we can control the value of the resistor and thus, change the current output.

Although this is a viable solution to higher levels of integration, it also brings a few more parameters to take into account during the development, like clock feedthrough and charge injection, not to mention the necessity of an external signal to clock the capacitors.

$$R_{eq} = \frac{1}{C_1 f} \tag{2.22}$$

The equivalent resistor value of the figure 2.7 is given by the inverse of capacitance times the switching frequency. If we want a  $1.25M\Omega$ , we would simply need a 10MHz clock and a capacitor with 80fF. Both MOSFETs used in the previous schematic are used as switches to control the charge and discharge of the capacitor. MOSFETs are considered good switches because of two main reasons:

- Off-resistance near  $G\Omega$  range (subjected to technology). At lower nodes leakage increases so it must be taken into account.

- On-resistance in  $100\Omega$  to  $5k\Omega$  range, depending on transistor sizing.

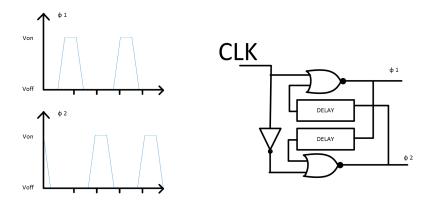

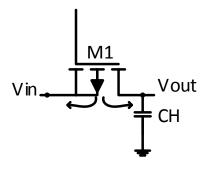

These type of circuits requires non-overlapping signal to both switches, requiring another component to the system. Figure 2.8 shows such component. Both  $\phi 1$  and  $\phi 2$  need to be non-overlapping to properly control that charge and discharge of the capacitor.

Figure 2.8: Non-overlapping clock generator

### **Clock Feedthrough**

One of the main disadvantage of this resistor architecture are the parasitic capacitances between the gate-drain and gate-source. Depicted in figure 2.9, the effect introduces an error in the samples output voltage.

Figure 2.9: Parasitic Capacitances of Mosfet

Assuming that the overlap capacitance is constant, we have an error of,

$$\Delta V = V_{ck} \frac{WC_{ov}}{WC_{ov} + C_h} \tag{2.23}$$

where  $C_{ov}$  is the overlap capacitance per unit width. The error  $\Delta V$  is independent of the input level, manifesting itself as a constant offset in the input/output characteristic.

#### **Channel Charge Injection**

Another problem we face with this architecture is the charge injection when the MOSFET is "turned off".

Figure 2.10: Channel Charge Injection

As depicted in figure 2.10, the charge injected to the left side is absorbed into the input source, creating no error. On the other hand, the charge injected to the right side will be deposited on Ch, introducing an error voltage stored on the capacitor. This error is modelled approximately by

$$\Delta V = \frac{WLC_{ox}(V_{dd} - V_{in} - V_{TH})}{2C_h} \tag{2.24}$$

A practical way to solve this problem would be using low input voltages, slow rising and falling edge switching, and larger capacitors. Another possible answer would be using complementary switches instead of a single MOS device to decrease the resistance.

#### **Thermal Noise**

Since one of main goals of this work is to minimize PVT variations we also need to take into account the thermal noise. The on-resistance of MOSFET switch will introduce thermal noise at the output and, when switch turns off, this noise is stored on the capacitor. This voltage is given by equation 2.25 and can be controlled by employing larger capacitors.

$$Noise = \sqrt{\frac{kT}{C}} \tag{2.25}$$

Like the previous effects, larger capacitors would require smaller frequencies, so it would be a trade-off between speed and precision.

#### 2.4 Process Corners and MonteCarlo

In semiconductor manufacturing, a process corner is an example of a design-of-experiments technique that refers to a variation of fabrication parameters used in applying an integrated circuit design to a semiconductor wafer. Process corners represent the absolute extremes of these parameter variations within which a circuit that has been fabricated on the wafer will achieve. A circuit running on devices fabricated at these process corners may run slower or faster than specified and at lower or higher temperatures and voltages.

In our case, we will have the typical, fast and slow corners for each device in use, mosfets, BJT and resistors. This gives a total of 5x3x3 = 45 corner combination in our simulations. One thing to note is that the worst case corners neglect the within-die fluctuations of the individual devices. The corner variation will apply equally to all devices.

Even in the absence of any process variations, there are limits on the accuracy with which devices can be fabricated. MonteCarlo simulations on the other hand, account for the individual shift in the parameters of the devices. These simulations are random in nature and tend to model the variations and mismatch between individual devices.

Take for example the threshold voltage of a PMOS transistor. In the slow corner case, every single transistor in the circuit would have the same threshold voltage behavior, although they would all be in the slow corner. With MonteCarlo simulations, each device has its own behavior.

The combinations of worst case corners and MonteCarlo provides good models for process variations and the within-die variations and mismatch of process parameters.

#### 2.5 State of the Art

In this section, we will be presenting the state of the art solutions to the problems explained in the introduction. Some of the solutions here exposed will sometimes sacrifice a precision in one element in favor of another. A high precision circuit like this should always have in mind the system in which it will be integrated.

#### 2.5.1 Traditional Bandgap Voltage Reference

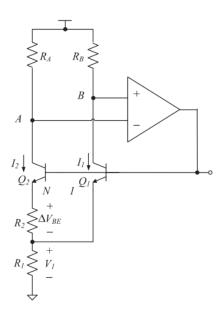

We begin our research with the simplest and one of the oldest model of BGR (Bandgap Reference), depicted in the figure below. It is worth noting that while this design was released a long time ago it still is one of the most used today or, at least, the general idea behind it. [3]

2.5 State of the Art

Figure 2.11: Simplified Brokaw bandgap voltage reference circuit (Brokaw, 1974)

This architecture uses the concept explained in section 2.2.1. To compensate the temperature it extracts the CTAT voltage from  $V_{BE}$  of the bipolar transistor, and the PTAT from the  $\Delta V_{BE}$  of both BJTs. Thus, by adding these two voltages we arrived at a voltage level with very low dependency on temperature. The operational amplifier forces the voltages levels at  $V_A$  and  $V_B$  to be equal. If both resistors  $R_A$  and  $R_B$  are matched then the same current flows on both branches of the schematic. Since  $R_1$  is the sum of two identical currents, we can write:

$$V_1 = 2IR_1 <=> V_1 = 2R_1 \frac{\Delta V_{BE1,2}}{R_2}$$

(2.26)

Since  $V_{REF} = V_{BE1} + V_1$ , thus:

$$V_{REF} = V_{BE1} + \left(\frac{2R_1 ln(N)}{R_2}\right) V_T \tag{2.27}$$

Where N is the ratio between the bipolar transistors and  $V_T$  is the thermal voltage. By adjusting the relation between R1 and R2 but also the areas of both BJT we can adjust the slope of the PTAT voltage to better eliminate temperature dependency. This design is also highly insensitive to supply changes because we are extracting a physical parameter of the device.

#### 2.5.2 MOS Biased Bandgap Voltage Reference

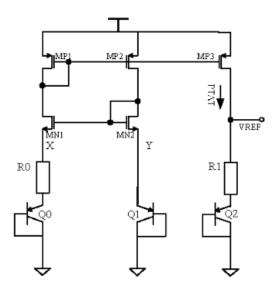

Another familiar model is presented in [19]. It replaced the bias resistors and amplifier with a self-biased current mirror as it is shown below. It works similar to that of figure 2.11 with the exception that the feedback loop was replaced by the transistors  $M_{P1}$ ,  $M_{P2}$ ,  $M_{N1}$  and  $M_{N2}$ .

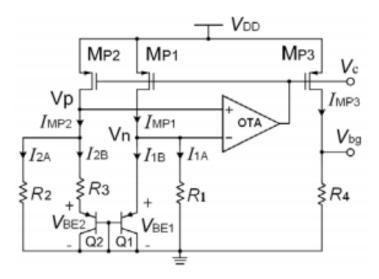

Figure 2.12: Self Biased BGR Architecture (From [19])

Since  $M_{P1}$  and  $M_{P2}$  have the same  $V_{GS}$ , by selecting SP1 = SP2, we shall obtain  $ID_{MP1} = ID_{MP2}$ . As a result, the currents flowing through  $M_{N1}$  and  $M_{N2}$  should be the same. If we do not consider the channel modulation effect, the drain voltages of  $M_{P1}$  and  $M_{P2}$  will be the same. Since the gates of  $M_{N1}$  and  $M_{N2}$  are connected together, by selecting  $SM_{N1} = SM_{N2}$ , we shall obtain  $ID_{MP1} = ID_{MP2}$ . As a result,  $I_X = I_Y$  which yields,

$$V_{EB1} = V_{EB0} + R_0 I_X (2.28)$$

$$I_X = \frac{V_{EB1} - V_{EB0}}{R_0} = \frac{\Delta V_{EB1,0}}{R_0}$$

(2.29)

Since,  $I_X = I_{Q0}$  and  $I_Y = I_{Q1}$ , and the emitter area ratio between both BJT transistors is N then,

$$I_X = I_Y = \frac{V_T ln(N)}{R_0} (2.30)$$

Finally, since  $I_{PTAT} = Ix$  we can write

$$V_{REF} = I_X R_1 + V_{EB2} (2.31)$$

As we go into higher integration, the self-biased mirror would suffer from channel modulation, thus highly increasing supply dependency.

#### 2.5.3 Low-Voltage Voltage Reference

A slight improvement over both the previous references is the one presented here. This improvement comes in the way of lowering the supply voltage necessary to produce the PVT voltage. Of course this also lowers the bandgap voltage itself to around half of the theoretical value. [17]

2.5 State of the Art

Figure 2.13: Low-Voltage Voltage Reference (From [17])

The output of this bandgap reference is 611.9 mV with a variation of 0.8mv. Using lower voltages in higher levels of integration will slightly lower the short channel effects of the MOS devices but also increase devices longevity by lowering their stress limit.

This improvement comes from folding the conventional BGR circuit to ground on nodes  $V_p$  and  $V_n$ . If resistors R1 and R2 are matched, then the same current will flow from both branches,  $I_{2A} = I_{1A}$ . The operational amplifier also clamps both  $V_p$  and  $V_n$  to equal voltage levels. Since,

$$V_p = V_n = V_{BE1}, V_{r3} = V_{BE1} - V_{BE2}, I_{MP2} = I_{2A} + I_{2B}$$

(2.32)

$$I_{MP2} = \frac{V_{BE1}}{R_2} + \frac{\Delta V_{BE}}{R_3} = \frac{V_{BE1}}{R_2} + \frac{V_T ln(N)}{R_3}$$

(2.33)

Thus we can write,

$$Vbg = m(\frac{V_{BE1}}{R_1} + \frac{V_T ln(N)}{R_3})R_4$$

(2.34)

Where m is ratio between  $M_{P2}$  and  $M_{P3}$ . By properly adjusting the values of the resistors and BJT areas we can achieve 611.9 mV with an accuracy of 0.3%.

#### 2.5.4 Current Reference Architecture

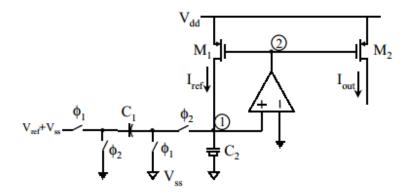

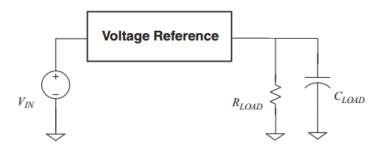

A current architecture to generate a current reference is shown below. This architecture refers only to the conversion between a voltage level and its current supply. This topology requires a bandgap reference and works by controlling a certain dump of energy in node 1. [12]

Figure 2.14: Current Reference Architecture (From [12])

During  $\phi 1$ ,  $C_1$  charges to  $V_{REF}$ . During  $\phi 2$  this charge is dumped on node 1. Thus, the ripple voltage is

$$\Delta V = -(\frac{2C_1}{C_1 + 2C_2})V_{REF} \tag{2.35}$$

The ripple voltage can be lowered by increasing the value of  $C_2$ . However, a larger  $C_2$  reduces the ripple at the expense of increased die area. The current delivered by the switched-capacitor is approximately

$$I_{REF} = C_1 V_{REF} F_{clk} (2.36)$$

This architecture offers an accuracy of 0.029%. Further improvement to this topology can be made by placing an amplifier connected in  $M_2$  to increase the output resistance. Another improvement can be achieved through the addition of a filter between the amplifier output, node 2, and the gate of  $M_2$ .

#### 2.5.5 Switched-Capacitor Current Reference

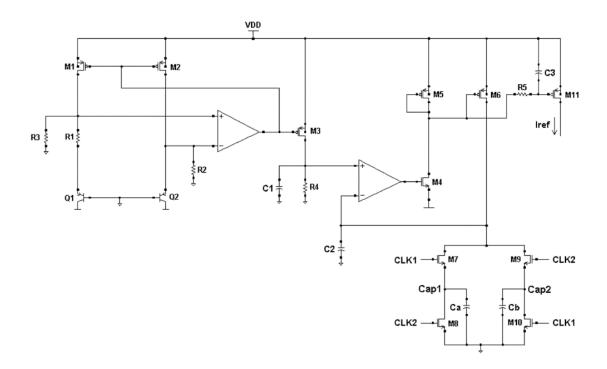

A realization of a current source using the bandgap reference presented in section 2.13 and a modification of 2.14 is shown below. One of the latest available types of current references with low variation over PVT parameters uses the above described components. According to [11], a low dependence PVT circuit is presented. It was designed using 0.13um CMOS technology and provides an overall precision of  $\pm 3\%$  over PVT conditions.

One factor that we must take into account when using switched-capacitors is the frequency response of the system. This model has an 8us settling time, meaning that once this circuit was powered, its output is only reliable after the settling time has been reached.

2.5 State of the Art

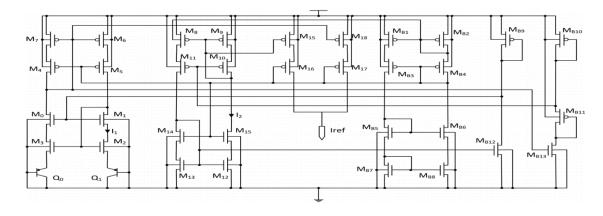

Figure 2.15: Switched-Capacitor Current Reference Schematic ((From [11]))

This architecture is depicted in figure 2.15 and we can easily identify the three general blocks that compose this system. At the top left we have the traditional bandgap voltage reference to provide PVT invariant voltage, this version is the low voltage topology discussed in section 2.13. This reference voltage is fed into a voltage to current converter on the top right. The final piece of this schematic is the switched-capacitor resistor on the bottom right. This resistor is controlled by the CLK1 and CLK2 signals used to adjust the resistor value and output current. This current reference uses the PTAT and CTAT currents from the bipolar transistors, generating a voltage insensitive to both temperature and supply voltage.

It is worth noting that the current source here applied uses a filter between  $M_6$  and  $M_{11}$  to reduce the ripple voltage.

$$I_{REF} = 2C_a V_{bo} F_{ref} (2.37)$$

The output current is given by the previous equation in which,  $V_{bg}$  is the bandgap voltage,  $C_a$  is the value of the capacitor and  $F_{ref}$  is the working frequency. The factor 2 comes from the simulated parallel resistors of  $C_a$  and  $C_b$ . If both capacitors have the same value, then the resistance is cut in half. This topology has a 3% variation over PVT. This error is mainly dependent of the offset voltage from the operational amplifiers and the ripple voltage.

#### 2.5.6 All MOSFET, Two Resistor Current Reference

There have been many proposed current references through the years, and as we go into higher integrations, the resistors do not scale as well as MOSFETs. The next logical step in current reference construction was the idea of trying to eliminate virtually all resistors, resorting only to transistors.

To minimize production costs, this architecture uses no BJTs, external components or trimming procedures. This circuit was designed for 22nm technology and simulations results show a PVT tolerance of around 10%. The main advantages of this circuit is the low voltage operation, suitable for sub-micron applications due to reduced electrical stress limit. [13]

Figure 2.16: All MOSFET, Two Resistor Current Reference Schematic (From [13])

The architecture is shown in figure 2.16. In the schematic, we can see some of the basic modules like the PTAT circuit whose current is generated by a Beta multiplier reference with the exception of MN7 and MN8 being in weak-inversion and the startup circuit necessary for setting the operating point.

Since transistors MN7 and MN8 are working in weak-inversion, their current is governed by a different equation from before. In weak-inversion the current is given by,

$$I_{n8} = I_0 W_{n8} / L_{n8} e^{\frac{V_{gs8} - V_{th}}{nV_T}}$$

(2.38)

Using N8 = AN7, and Vgs8 = Vr+Vgs7 we can write the current in MN8 as,

$$I_{n8} = I_0 W_{n7} / L_{n7} e^{\frac{V_{g87} - V_{th}}{nV_T}} <=> I_{n8} = A e^{\frac{V_r}{nV_T}}$$

(2.39)

$$V_r = nV_T \left( \frac{S_{n7}}{S_{n8}} * \frac{S_{p10}}{S_{p9}} \right) \tag{2.40}$$

Solving for Vr, we arrive at voltage value that is clearly PTAT and very similar to the differential base emitter voltage of two BJT. The slope of the voltage can be adjusted using the size ratios of the four transistors.

2.5 State of the Art

The CTAT current generated to eliminate the temperature dependency is the difference of two others. To eliminate the process dependency, the MOSFET seven and eight were properly scaled to arrive at a theoretical 0% process dependency.

This topology is viable to high integrations as this architecture is technology independent and allows integration into 22nm and beyond. However, it suffers from low accuracy by working in sub-threshold region of operation. In this region temperature dependence suffers from high non-linearity and thus reports only an accuracy of 10% over PVT.

A suggestion to be analyzed further in order to improve this circuit would be replacing the resistor R by a switched-capacitor resistor, lowering its variation and providing a more accurate PTAT current.

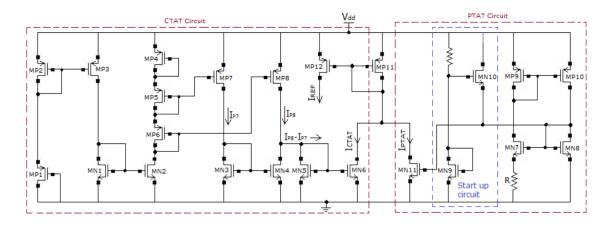

#### 2.5.7 Resistorless Current Reference

The last step in current reference architecture would be a Resistorless current reference. A resistorless circuit allows for higher integrations while simplifying the circuit layout and area consumption. A resistorless current reference source is depicted in figure 2.17. [8]

This circuit uses cascode structures to improve the power supply rejection ratio. The reference current source has been designed in 65 nm technology. The presented circuit achieves 55 ppm/ $^{\circ}$ C temperature coefficient over range of -40  $^{\circ}$ C to 125  $^{\circ}$ C. Reference current susceptibility to process parameters variation is  $\pm 3\%$ . The power supply rejection ratio without any filtering capacitor at 100 Hz and 10 MHz is lower than -127 dB and -103 dB, respectively. The current reference source presented here consists of MOSFETs and vertical PNP bipolar transistors. It is designed for 3.3 V supply voltage with low sensitivity to process variation and small temperature coefficient.

Temperature independence is achieved by obtaining appropriate temperature coefficients of the summed currents I1, the PTAT current, and I2, the CTAT current. Low sensitivity to supply voltage bases on using cascode structures. Transistors MB1-MB13 form the bias block, which provides the bias voltage to cascode structures and bulk node of M8. Moreover, transistors MB9-MB13 work as start-up circuit.

Figure 2.17: Resistorless Current Reference (From [8])

That PTAT current is achieved using the difference between the base emitter voltages of Q0 and Q1. This current can be easily adjusted be changing the sizes of both M3 and M2 but also the areas of both BJTs. This current is given by,

$$I_{ptat} = \frac{uC_{ox}}{2} * \frac{\left(\frac{kT}{q}ln(\frac{A_0}{A_1})\right)^2}{\left(\sqrt{\frac{L_3}{W_3}} - \sqrt{\frac{L_2}{W_2}}\right)^2}$$

(2.41)

The CTAT current is formed by transistor M8-M15 and is based on threshold voltage difference. The difference is obtained by using the body effect.

$$I_{d8,9} = \frac{uC_{ox}}{2} * \frac{W_{8,9}}{L_{8,9}} (V_{gs} - V_{th})^2$$

(2.42)

Since  $V_{gs}=V_{gs8}=V_{gs9}$ , and solving  $V_{gs9}$  and substituting in  $V_{gs8}$  we arrive at:

$$I_{ctat} = \frac{uC_{ox}W_8W_9(V_{th8} - V_{th9})^2}{2(\sqrt{L_8W_9} - \sqrt{L_9W_8})^2}$$

(2.43)

The summation of both currents is made in the transistors M15-M18. The variation in this architecture comes from the non-linearity of both currents.

#### 2.5.8 4-Bits Trimmed CMOS Bandgap Reference

Every single architecture we have seen until now relied primarily on analog design. The matching of transistors with proper weighing, the sum of CTAT and PTAT currents and cascodes structures. However, there is another type of architectures. In these topologies, we use a more digital approach by adding trimming procedures.

Although these trimming procedures usually increase the accuracy of the architecture, they also have several disadvantages like the increase in die consumption and the need of external digital signals to drive the latches.

2.5 State of the Art

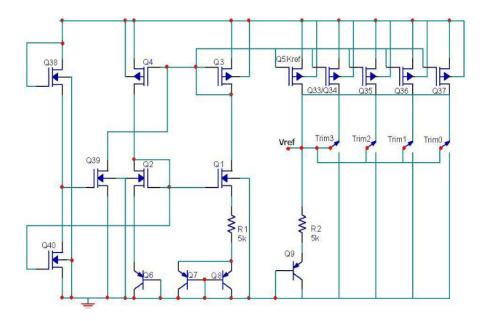

Figure 2.18: 4-bit trimmed CMOS Voltage Reference (From [6])

Before we head into the trimming procedures let us first observe the remaining circuit. The bandgap voltage core is identical to that of section 2.12. They extract CTAT from  $V_{BE}$  and PTAT from the differential base emitter voltage of BJT. A small difference is Q7 and Q8 are split into two, parallel connected BJTs instead of a single transistor, to slightly lower process dependency.

Trimming is the concept of shutting down parts of the circuit in order to benefit the overall goal. In this design, we use the standard bandgap voltage reference with Q1-Q8. Q38-Q40 represent the startup circuit. The last four mosfets (Q34-Q37) can be disconnected from the circuit in order to improve process independence.

Let us assume that we have an ideal output of 1.2V and the worst case of expected variation is 5%. The number of trimming bits necessary is given by,

$$n_{bits} = \log_2(\frac{1.2}{0.05 * 1.2} + 1) \ge 3.41 = 4bits$$

(2.44)

Transistors Q34-Q37 are parallel connected to Q5, the mosfet responsible by driving  $\Delta V_{BE}$  into R2. By switching Q34-Q37 to on or off states we can adjust the current flow through R2. Since there are 4 available bits, this gives us 16 levels.

#### 2.5.9 Overview

From the relevant architectures and compensation techniques we have seen, it should be pointed out that every circuit regarding insensitive temperature relies always on the same technique, that one being the sum of two, opposed scaling, temperature dependent currents to remove the variance.

Another technique is called the ZTC point. Instead of summing two currents, we try to bias the MOS device at a specific voltage in which its internal parameters automatically cancel each other out, temperature wise of course. However, sometimes such bias point is difficult or even impossible to find.

Supply independence can be achieved mostly by two ways. The first is using the traditional bandgap reference. The voltage reference is achieved by extracting the bandgap silicon voltage, this value being independent of the supply itself seeing it is a physical constant of the silicon itself. The other solution is the use of cascode structures to increase the PSRR (Power Supply Rejection Rate), like the Wilson current mirror that offers very small supply dependence.

Process compensation is difficult to do. The techniques are usually based on optimal transistor matching and intelligent layout design. Prioritizing circuit symmetry is usually the best way to go.

| Ref. | Tech    | Techniques          | Devices       | Comp. | Output   | Area  | Accuracy |

|------|---------|---------------------|---------------|-------|----------|-------|----------|

|      |         | Used                | Devices Comp. |       | Output   | mm^2  | (%)      |

| [1]  | 0.13 um | PTAT+CTAT           | MOSFET        | PVT   | 16.07 uA | -     | 0.61     |

|      |         | Switched-Capacitor  | BJT           |       |          |       |          |

| [12] | 0.18 um | Switched-Capacitor  | MOSFET        | PVT   | 6.88 uA  | -     | 0.029    |

| [11] | 0.35 um | PTAT+CTAT           | MOSFET        | PVT   | 612 mV   | 0.117 | 0.327    |

|      |         |                     | BJT           |       |          |       |          |

| [9]  | 22 nm   | PTAT+CTAT           | MOSFET        | PVT   | 82 uA    | -     | 5        |

| [10] | 65 nm   | PTAT+CTAT           | MOSFET        | PVT   | 6.46 uA  | -     | 3        |

|      |         | Cascodes Structures | BJT           |       |          |       |          |

| [2]  | 0.5 um  | PTAT+CTAT           | MOSFET        | VT    | 2.670 V  | 0.01  | 1        |

| [3]  | 0.25 um | PTAT+CTAT           | MOSFET        | VT    | 10.45 uA | 0.002 | 1        |

|      |         | Cascodes Structures |               |       |          |       |          |

| [13] | 0.18 um | PTAT+CTAT           | MOSFET        | PVT   | 58 uA    | -     | 1,38     |

| [14] | 0.18 um | ZTC                 | MOSFET        | PT    | 144.3 uA | -     | 7        |

|      |         |                     | BJT           |       |          |       |          |

| [18] | 0.35 um | Trimming            | BJT           | PVT   | 1,23V    | 0.140 | 1        |

|      |         |                     |               |       |          |       |          |

Table 2.1: Comparison between Current & Voltage References

# Chapter 3

# Bandgap Voltage Reference Design

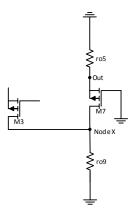

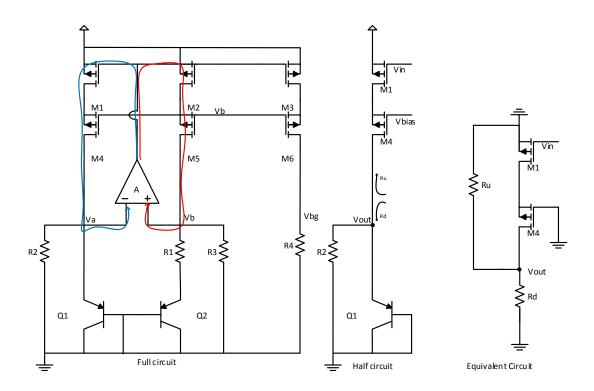

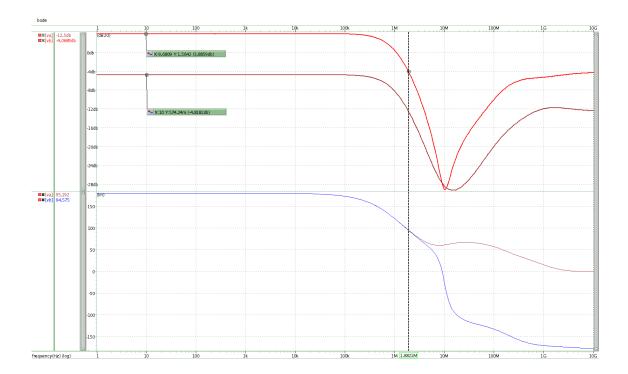

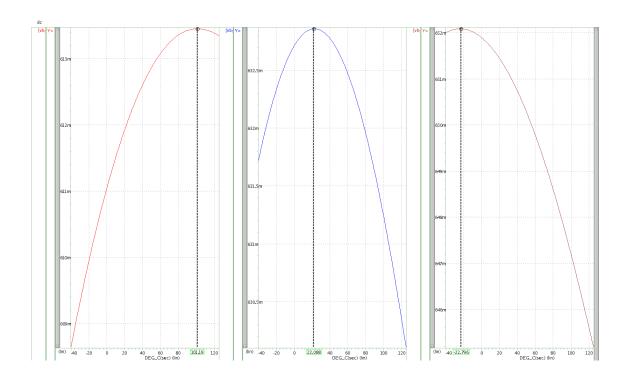

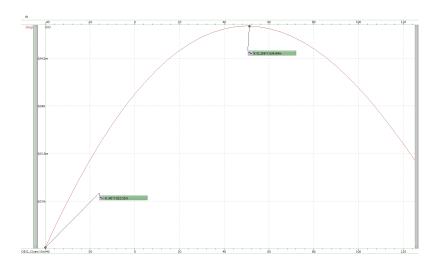

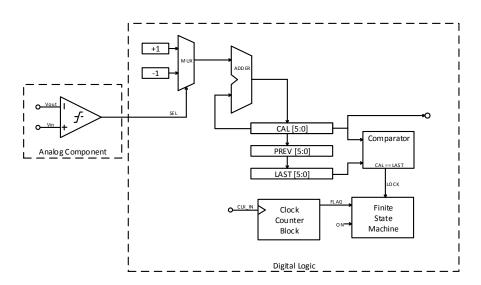

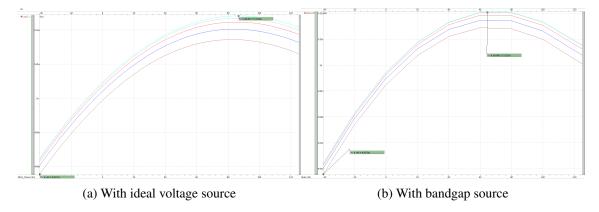

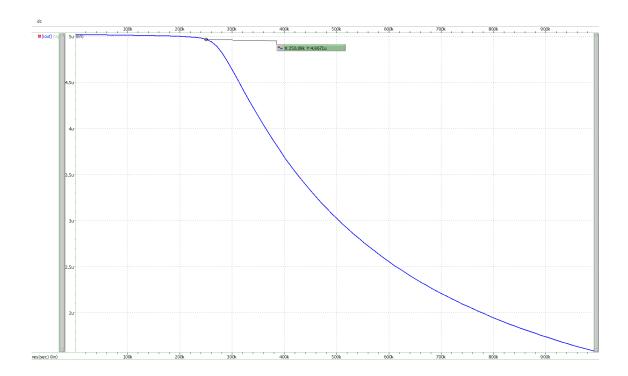

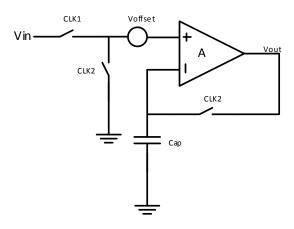

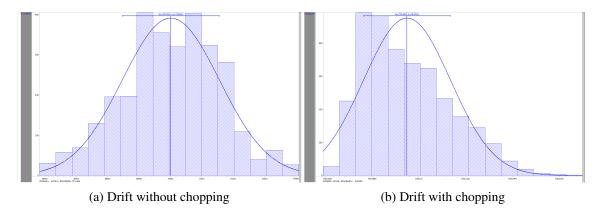

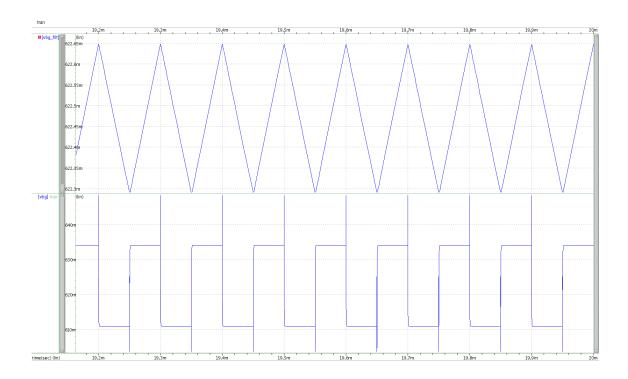

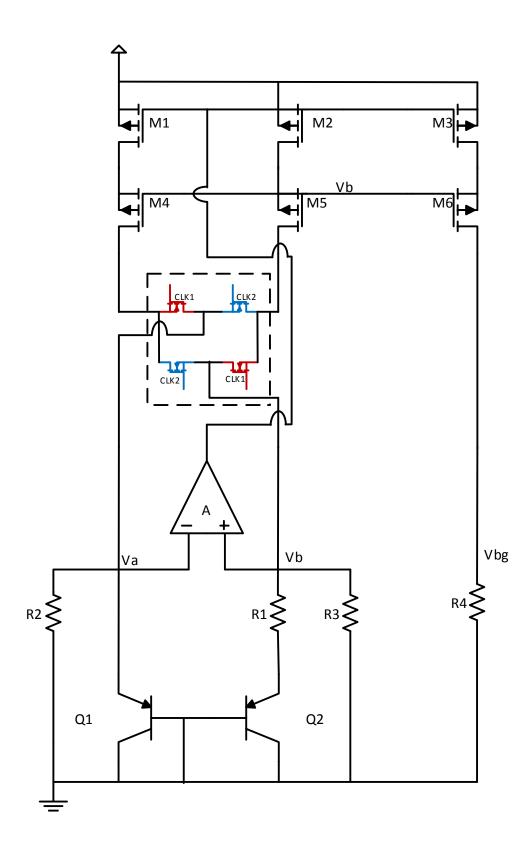

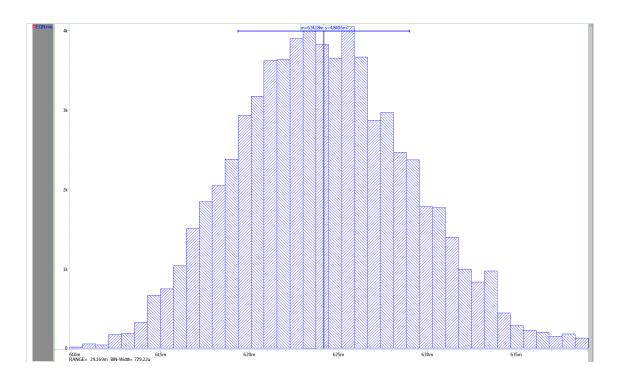

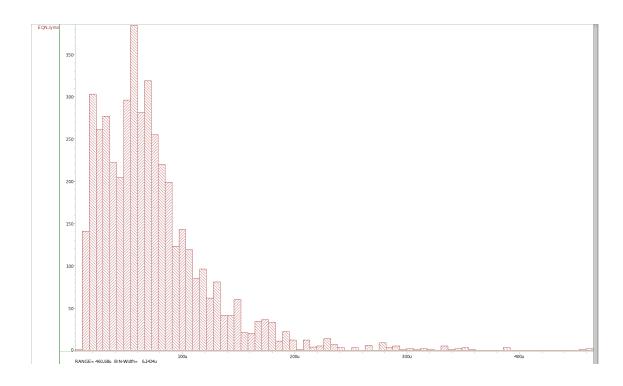

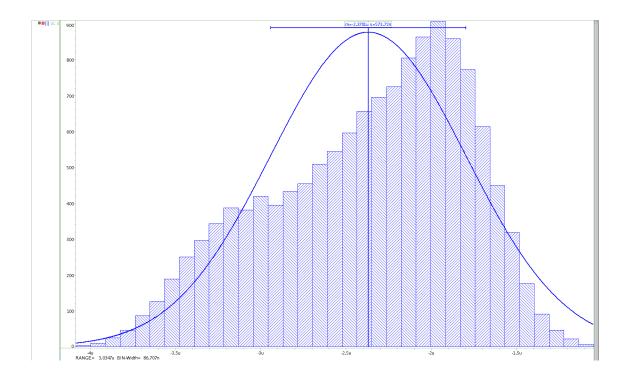

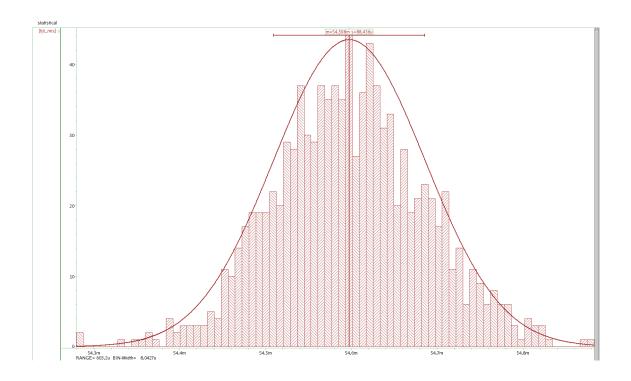

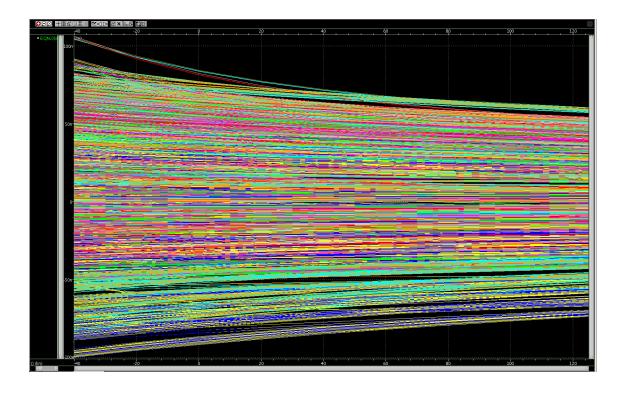

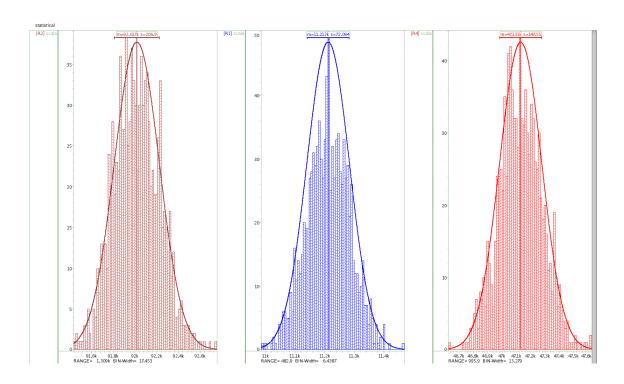

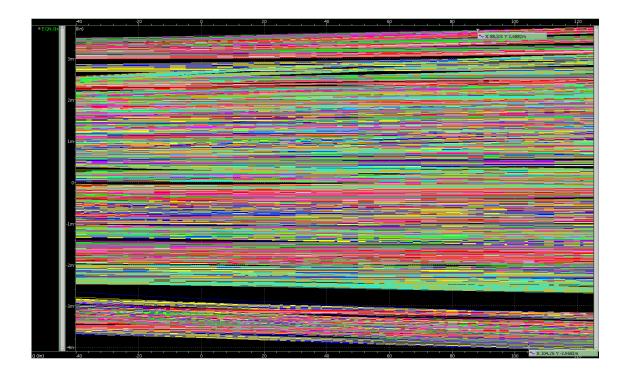

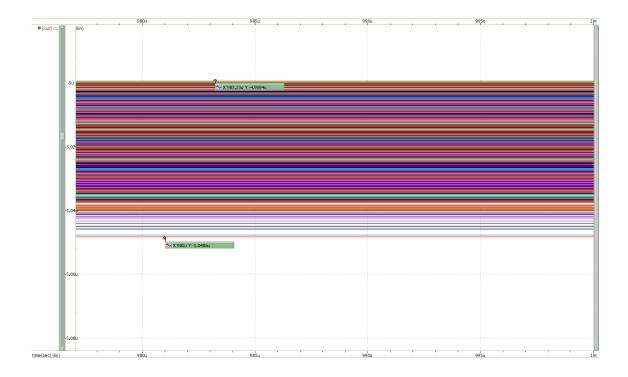

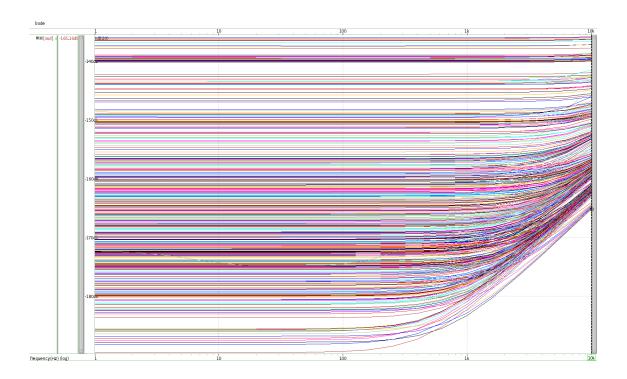

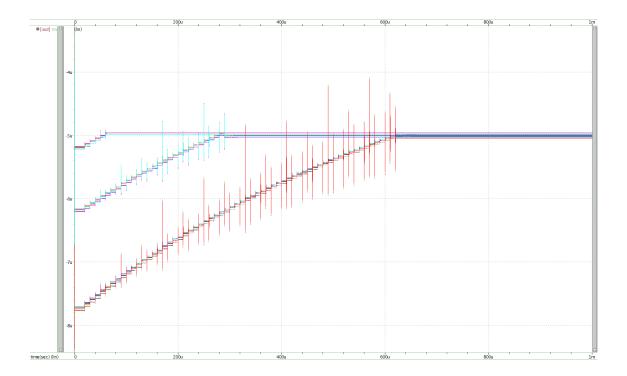

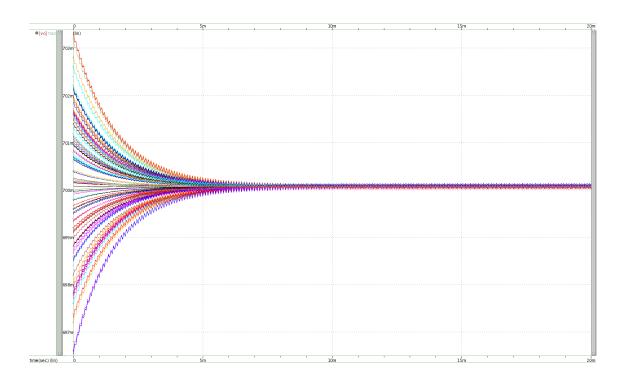

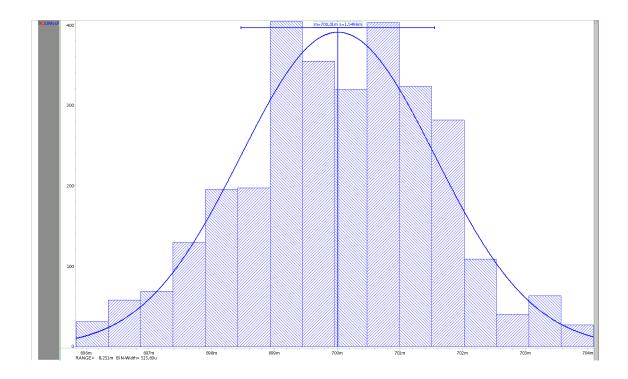

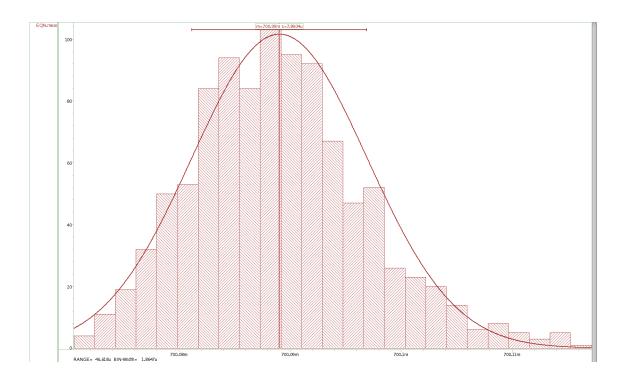

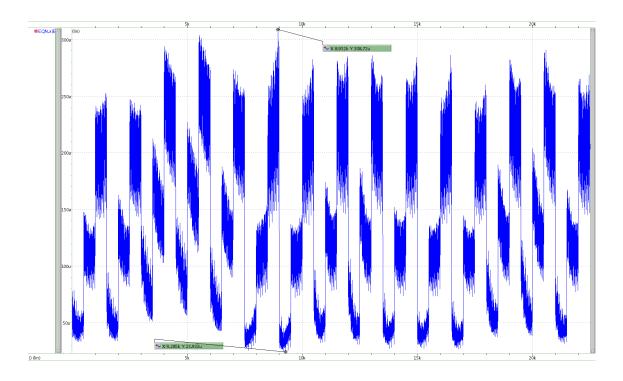

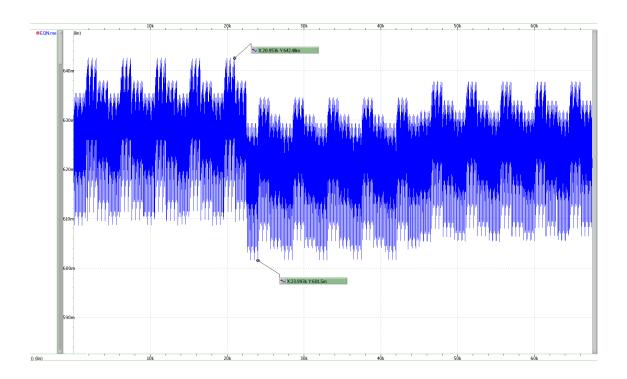

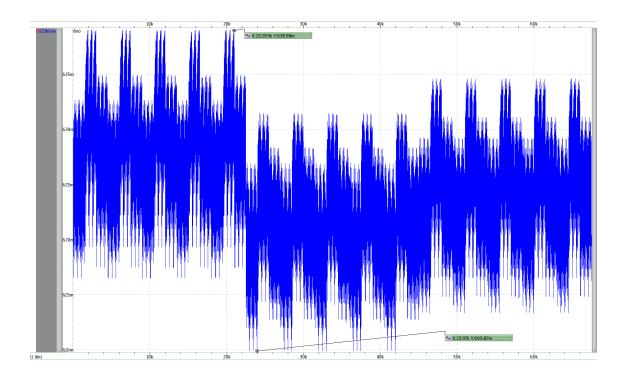

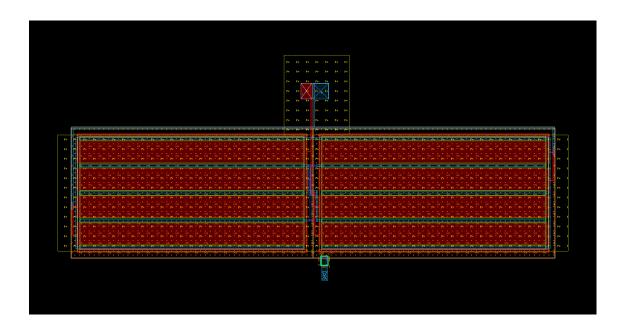

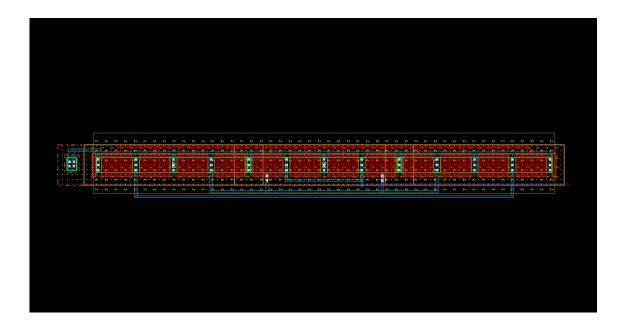

Voltage references find applications in a variety of circuits and systems including linear and switching regulators, Analog to Digital (A/D) and Digital to Analog (D/A) converters, voltage to frequency converters, power supply supervisory circuits, power converters and other circuits requiring an accurate reference voltage. An ideal voltage reference must be, inherently, well-defined and its output voltage should be independent of temperature, power supply variations, load variations and other operating conditions.