### Characteristics of gate-all-around silicon nanowire field effect transistors with asymmetric channel width and source/drain doping concentration

Chang-Ki Baek, Sooyoung Park, Myung-Dong Ko, Taiuk Rim, Seongwook Choi, and Yoon-Ha Jeong

Citation: Journal of Applied Physics 112, 034513 (2012); doi: 10.1063/1.4745858 View online: http://dx.doi.org/10.1063/1.4745858 View Table of Contents: http://scitation.aip.org/content/aip/journal/jap/112/3?ver=pdfcov Published by the AIP Publishing

#### Articles you may be interested in

Statistical variability study of random dopant fluctuation on gate-all-around inversion-mode silicon nanowire fieldeffect transistors Appl. Phys. Lett. 106, 103507 (2015); 10.1063/1.4914976

Vertical gate-all-around junctionless nanowire transistors with asymmetric diameters and underlap lengths Appl. Phys. Lett. 105, 102105 (2014); 10.1063/1.4895030

Investigating the impact of source/drain doping dependent effective masses on the transport characteristics of ballistic Si-nanowire field-effect-transistors J. Appl. Phys. 115, 124502 (2014); 10.1063/1.4869495

Electronic transport mechanisms in scaled gate-all-around silicon nanowire transistor arrays Appl. Phys. Lett. 103, 263504 (2013); 10.1063/1.4858955

Random telegraph signal noise in gate-all-around silicon nanowire transistors featuring Coulomb-blockade characteristics

Appl. Phys. Lett. 94, 083503 (2009); 10.1063/1.3089240

# Characteristics of gate-all-around silicon nanowire field effect transistors with asymmetric channel width and source/drain doping concentration

Chang-Ki Baek,<sup>1</sup> Sooyoung Park,<sup>1,a)</sup> Myung-Dong Ko,<sup>2</sup> Taiuk Rim,<sup>2</sup> Seongwook Choi,<sup>3</sup> and Yoon-Ha Jeong<sup>1,2</sup>

<sup>1</sup>Department of Creative IT Excellence Engineering and Future IT Innovation Laboratory (i-Lab), Pohang University of Science and Technology (POSTECH), Pohang 790-784, Korea <sup>2</sup>Department of Electrical Engineering, Pohang University of Science and Technology (POSTECH), Pohang 790-784, South Korea <sup>3</sup>School of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-744, South Korea

(Received 23 March 2012; accepted 17 July 2012; published online 13 August 2012)

We performed 3D simulations to demonstrate structural effects in sub-20 nm gate-all-around silicon nanowire field effect transistors having asymmetric channel width along the channel direction. We analyzed the differences in the electrical and physical properties for various slopes of the channel width in asymmetric silicon nanowire field effect transistors (SNWFETs) and compared them to symmetrical SNWFETs with uniform channel width. In the same manner, the effects of the individual doping concentration at the source and drain also have been investigated. For various structural conditions, the current and switching characteristics are seriously affected. The differences attributed to the doping levels and geometric conditions are due to the electric field and electron density profile. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4745858]

#### I. INTRODUCTION

The gate-all-around silicon nanowire field effect transistor (GAA SNWFET) is a leading candidate for nanoscale devices due to its superior short-channel effect immunity and ballistic transport properties.<sup>1–7</sup> To achieve high densities in nanoscale complementary metal oxide semiconductor (CMOS) applications, a very large number of transistors need to be designed and fabricated in the memory and logic array. Vertically stacked SNWFETs have been considered for use in high device density integrated circuits.<sup>8–12</sup> However, it has been reported that an asymmetric channel structure with inhomogeneous width should be expected for vertically stacked SNWFETs fabricated using a conventional top-down process.<sup>13</sup> In the previous studies, the electrical properties of FinFETs and Double Gate FETs (DGFETs) with an asymmetric channel have been investigated using experimental and simulation methods;<sup>14,15</sup> however, to date these studies have not been performed for GAA SNWFETs.

In this work, the electrical properties of SNWFET structures with an asymmetric channel width are investigated using a 3D simulation to analyze the physical phenomena in the devices. This work examines the slope associated with different channel diameters and the choice of the source and/or drain between the narrow and wide side of the wire. From the viewpoint of feasibility, the effect of asymmetric source and drain doping is also analyzed by comparing with devices of equal doping; this allows us to ascertain the improvement of the electric characteristics of the inhomogeneous channel width SNWFET. Finally, we report details of the physical simulation results for the structural effect and the operation mechanism.

#### II. DEVICE STRUCTURE AND SIMULATION METHOD

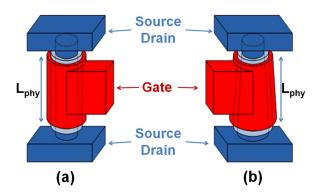

Fig. 1 shows the device structure of the n-type GAA SNWFET used in our simulation. The electric characteristics of the symmetric gate (SG) and asymmetric gate (AG) shown in Figs. 1(a) and 1(b), respectively, are compared in Sec. III A. The device structural parameters are commonly determined for both devices: the physical gate length  $(L_{phy})$ is 80 nm, the effective gate length ( $L_G$ ) is 20 nm, the gate oxide thickness (Tox) is 2 nm, the channel doping concentration (p-type) is  $10^{15}$  cm<sup>-3</sup>, and the source and drain doping (n-type) is  $10^{19}$  cm<sup>-3</sup>. The diameter of the wire (D<sub>NW</sub>) varies from 7 nm to 12 nm for the SG SNWFET. For the AG devices, the diameter  $D_{NW}$  at the wide side is fixed at 12 nm, and at the other side it is varied to adjust for the slope of the channel width, i.e., the ratio between the D<sub>NWS</sub> of the wide side and the narrow side. In Sec. III B, the effects of asymmetric source/drain doping (AD) are compared with those of symmetric doping (SD) in view of the electric characteristics of the AG SNWFET. The source/drain doping concentration is varied from  $10^{19}$  to  $10^{20}$  cm<sup>-3</sup>. The doping density on each contact side is individually controlled to determine the performance enhancement of the AG devices. The simulations are performed by a 3D device numerical simulator, Sentaurus<sup>TM</sup>, and a density gradient model is used to account for quantum effects.

#### **III. SIMULATION RESULTS**

## A. Comparison of symmetric gate and asymmetric gate SNWFETs

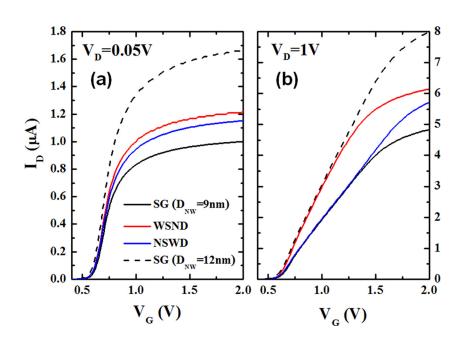

The relations of the drain current  $(I_D)$  vs. gate voltage  $(V_G)$  for SG and AG SNWFETs are compared and shown in Figs. 2(a) and 2(b), for the linear condition and saturation conditions, respectively. The black solid and dashed lines are

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: sooyoungpark@postech.ac.kr.

FIG. 1. The schematic for the simulation (a) SG and (b) AG SNWFET. AG SNWFETs can be classified as two different types: wide source—narrow drain and narrow source—wide drain, according to the diameter  $(D_{NW})$  where the source and drain contacts are located.

for the SG SNWFET with  $D_{NW} = 9$  and 12 nm, respectively. The colored lines result from AG SNWFET with the narrowest  $D_{NW} = 9$  nm and widest  $D_{NW} = 12$  nm considering realistic top-down fabrication processes. Among the colored lines, the red line represents the AG SNWFET with "wide source  $(D_{NW} = 12 \text{ nm}) - \text{narrow drain} (D_{NW} = 9 \text{ nm})$ " (WSND) and the blue line represents "narrow source  $(D_{NW} = 9 \text{ nm}) - \text{wide}$ drain  $(D_{NW} = 12 \text{ nm})$ " (NSWD).

As seen in Fig. 2, the  $I_D$  level of AG SNWFET is located between the SG SNWFETs having  $D_{NW} = 9$  and 12 nm, which are the minimum and maximum  $D_{NWS}$  in the AG SNWFETs, respectively. Little difference is seen between WSND and NSWD in the linear condition ( $V_D = 0.05$  V, Fig. 2(a)); however, the difference increases in the saturation condition ( $V_D = 1$  V, Fig. 2(b)). Even though  $I_Ds$  of the two AG SNWFETs have similar values at high  $V_G$  (near 2 V), the current drivability of the WSND is apparently higher than it is for the NSWD with moderate  $V_G$ . For example, the  $I_D$  of WSND is 50% higher than that of NSWD at  $V_G = 1$  V under the saturation condition (Fig. 2(b)).

To compare the electrical characteristics between WSND and NSWD SNWFETs, the threshold voltage  $(V_{th})$

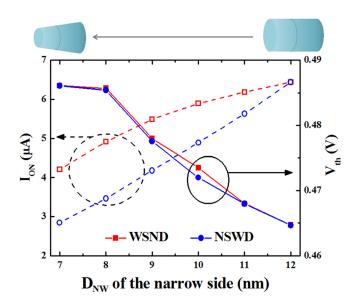

FIG. 3.  $I_{ON}$  and  $V_{th}$  vs.  $D_{NW}$  of the narrow side for AG SNWFET with  $L_G = 20$  nm. The dashed line and open symbols are  $I_{ON}$ ; the solid line and filled symbols are  $V_{th}$ . Two types of the AG SNWFET are compared and the red and blue colors indicate WSND and NSWD, respectively. At the top of the plot, a schematic for the change in the device geometry is shown.

and drain on current ( $I_{ON} = I_D$  at  $V_G \gg V_{th}$ ) vs.  $D_{NWs}$  for the narrow side are shown in Fig. 3. The extraction of  $V_{th}$  is based on the constant current method, and  $I_{on}$  is measured at the saturation condition, i.e.,  $V_G = 1.5 V$  and  $V_D = 1 V$ . For two cases of AG SNWFETs, the  $D_{NW}$  of the wide side is fixed at 12 nm and diameter of the other side is varied from 7 nm to 12 nm. As is well known,  $V_{th}$  increases as  $D_{NW}$ decreases in SNWFETs; this is shown in the figure, although our case considers AG SNWFETs. The two cases of AG SNWFETs show very similar behavior since  $V_{th}$  is determined by the amount of the inversion charge under gate control only, and the geometric shapes of the two devices are exactly the same. In contrast, the difference in the  $I_{ON}$  of the AG SNWFETs is quite clear. The  $I_{ON}$  of NSWD is more drastically decreased than  $I_{ON}$  of WSND, as the  $D_{NW}$  of the

FIG. 2.  $I_D$  vs.  $V_G$  of SNWFETs ( $L_G = 20 \text{ nm}$ ) under the drain bias ( $V_D$ ). (a)  $V_D = 0.05 \text{ V}$ ; (b)  $V_D = 1 \text{ V}$ . The black solid and dashed lines are SG SNWFET with  $D_{NW} = 9$  and 12 nm, respectively. The red line is WSND AG SNWFET with  $D_{NW} = 12 \text{ nm}$  for the source and 9 nm for the drain. The blue line is NSWD with the order of  $D_{NW}$  reversed from the red case.

I his article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to J IP: 141.223.173.110 On: Tue. 26 May 2015 08:30:28

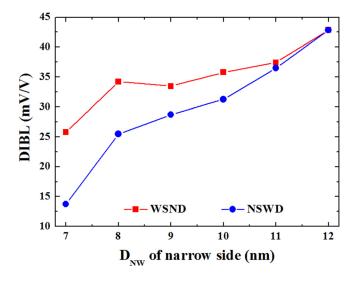

FIG. 4. DIBL value vs.  $D_{NW}$  of the narrow side for AG SNWFET with  $L_G = 20$  nm. Two types of the AG SNWFET are compared, and the red and blue colors indicate WSND and NSWD, respectively. The DIBL values are extracted at  $V_D = 0.05$  and 1 V.

narrow side is decreased even though the  $V_{th}$  change profiles are nearly the same. Considering the fluctuation due to the fabrication process of the vertical SNWFETs, the NSWD AG SNWFET is expected to be a much more delicate structure in the design of an integrated circuit with vertical SNWFET due to this  $I_{ON}$  property. Also, we predict the WSND structure to be advantageous as far as the current drivability, operation speed, and  $I_{ON}$  distribution due to its fabrication fluctuation.

To examine the short channel effect (SCE), Fig. 4 shows the drain-induced barrier lowering (DIBL) as in Fig. 3. Both of the AG SNWFETs have the tendency to decline as the  $D_{NW}$  of the narrow side decreases, and the DIBL of WSND has a somewhat higher value than that of NSWD. This is because the drain side  $D_{NW}$  of the WSND device is narrower and the drain resistivity is higher than for NSWD, so the drain controllability of the WSND device is higher than for NSWD and SG SNWFETs.

1.0

Regarding SCE, a recent report<sup>13</sup> showed that measurement results for the fabricated WSND AG SNWFET had lower DIBL than that for NSWD, in contrast to our results. However, this could be induced by the difference in  $L_G$  (for our device,  $L_G = 20$  nm; in Ref. 13,  $L_G$  was over 100 nm) and the structural constitution of the junction between the channel and source/drain, since the channel length and junction play important roles in DIBL behavior. At this point, an additional analysis on the effect of the junction constitution is needed rather than a direct comparison to the result of Ref. 13. Therefore, in the following section III B, the change in electric characteristics due to the doping concentration profile at the source/drain is investigated to determine the feasibility of performance enhancement in the case of WSND AG SNWFET.

### B. Effect of asymmetric doping profile with AG SNWFETs

As depicted in Sec. III A, a SNWFET is assumed to be fabricated with the shape of an asymmetric channel and its geometric effects are investigated. In this section, the additional structural properties of AG SNWFETs are analyzed with the source and drain doping concentration. A considerable improvement could be made to the electrical characteristics with asymmetric contact doping, since the fabrication of vertical SNWFETs needs two-step implantations for the source and drain junction, and there is the possibility of a doping concentration mismatch.

To perform this analysis, n-type WSND structures having  $D_{NW} = 12 \text{ nm}$  for the source and 9 nm for the drain are simulated with individually varying source and drain doping concentrations. The doping profile is a gradual Gaussian shape, with  $L_G = 20 \text{ nm}$  and the other key structural parameters the same as in Sec. III A. In the asymmetric doping case, the source doping concentration (N<sub>SRC</sub>) and the drain doping concentration (N<sub>DRN</sub>) have different values that are compared to the symmetric doping case (N<sub>SD</sub> = N<sub>SRC</sub> = N<sub>DRN</sub>).

The  $I_D$  vs.  $V_G$  characteristics of AD and SD are shown in Fig. 5. Here, the AD is classified as a "low source – high

5.0

V<sub>D</sub>=0.05V V<sub>D</sub>=1V 0.9 4.5 0.8 4.0 0.7 3.5 0.6 3.0 (M) 0.5 2.5 **–**<sup>–</sup>0.4 2.0 (b) (a) 0.3 1.5 SD 1.0 0.2 WSND LSHD 0.1 0.5  $(D_{NW} = 12 \rightarrow 9nm)$ HSLD 0.0 0.0 0.5 1.0 1.5 2.0 0.5 1.0 1.5 2.0  $V_{G}(V)$  $V_{G}(V)$

FIG. 5.  $I_D$  vs.  $V_G$  under (a)  $V_D = 0.05$  V and (b)  $V_D = 1$  V. For all curves, WSND AG SNWFET ( $L_G = 20$  nm,  $D_{NW} = 12$  nm for source and 9 nm for drain side) is simulated and compared for each doping condition. The black solid lines are the SD case with  $N_{SD} = 10^{19}$  cm<sup>-3</sup> for both contacts. The red line is LSHD with  $N_{SRC} = 10^{19}$  cm<sup>-3</sup> and  $N_{DRN} = 10^{20}$  cm<sup>-3</sup>. The blue line is HSLD with the order of  $N_{SRC}$  and  $N_{DRN}$  reversed from the red case.

I his article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to J IP: 141.223.173.110 On: Tue. 26 May 2015 08:30:28

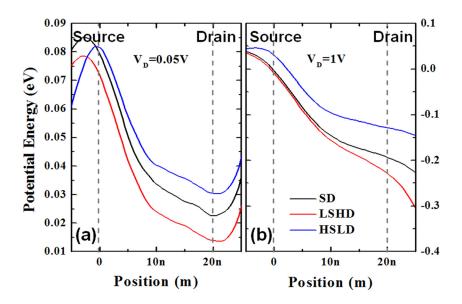

FIG. 6. 1D potential energy profile along the channel direction with different  $V_D$  for  $V_G = 1 V$ . (a)  $V_D = 0.05 V$ ; (b)  $V_D = 1 V$ . The black solid lines are the SD case with  $N_{SD} = 10^{19} \text{ cm}^{-3}$  for the both contacts. The red line is LSHD with  $N_{SRC} = 10^{19} \text{ cm}^{-3}$  and  $N_{DRN} = 10^{20} \text{ cm}^{-3}$ . The blue line is HSLD with the order of  $N_{SRC}$  and  $N_{DRN}$  reversed from the red case.

drain doping case" (LSHD,  $N_{SRC} < N_{DRN}$ ) and a "high source – low drain doping case" (HSLD,  $N_{SRC} > N_{DRN}$ ). Both AD cases show higher I<sub>D</sub> under both linear (Fig. 5(a)) and saturation (Fig. 5(b)) bias conditions than the SD case due to the reduction in the series resistance induced by the higher contact of the concentration.

In the case of HSLD, the overall trend and gradient of  $I_D$  is very similar to the SD case but the amplitude of  $I_{ON}$  is greatly improved, especially in the strong inversion region. In the LSHD case, there is a slightly lower  $I_{ON}$  than in HSLD, but it is still higher than in the SD case. However, the incremental trend of  $I_D$  as  $V_G$  increases is very steep, so the operating speed of the device is excellently suitable for a switch operation.

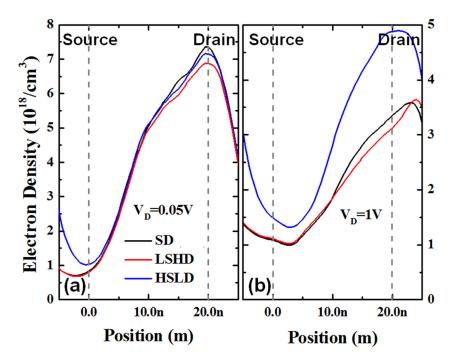

For a more detailed investigation, the 1D potential energy and electron density profile are shown in Figs. 6 and 7 under two different bias conditions (linear and saturation). Under the linear bias, the potential energy profiles for each case (Fig. 6(a)) show somewhat different values but the gradients representing the electric fields in the channel look very similar. Moreover, the electron density profiles (Fig. 7(a)) are also similar in the channel. With the linear operation, the total current depends on the drift component, and the drift is proportional to the product of the electron density inserted into the channel from the source and the electric fields in the channel. With this consideration, the similar current characteristics and variance in the current value for all cases in Fig. 5(a) are reasonable.

In contrast, the current characteristics (Fig. 5(b)), potential energy (Fig. 6(b)), and electron density (Fig. 7(b)) show large differences between the SD, LSHD, and HSLD SNWFETs under the saturation bias. For the LSHD device, the voltage drop in the channel is largest due to its low parasitic drain resistance, and it induces a large electric field which helps to increase the drift current. As mentioned, the drift current is proportional to the product of the injected electron and the electric field, and the number of electrons mainly depends on  $N_{SRC}$ . Thus, the change in the electric field in the channel

FIG. 7. 1D electron density profile along the channel direction with different  $V_D$  for fixed  $V_G = 1 V$ . (a)  $V_D = 0.05 V$ ; (b)  $V_D = 1 V$ . The black solid lines are the SD case with  $N_{SD} = 10^{19} \text{ cm}^{-3}$  for both contacts. The red line is LSHD with  $N_{SRC} = 10^{19} \text{ cm}^{-3}$  and  $N_{DRN} = 10^{20} \text{ cm}^{-3}$ . The blue line is HSLD with the order of  $N_{SRC}$  and  $N_{DRN}$  reversed from the red case.

[This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to ] IP: 141.223.173.110 On: Tue. 26 May 2015 08:30:28 determines the switching characteristics of the devices, so that the relatively large electric field in the LSHD device can be considered a reason why its gate controllability is higher than the other cases under the saturation bias.

Along with the drift component, the diffusion current should also be considered under the saturation condition; this leads to the large variance of potential and electron density along the channel direction. As shown in Fig. 7(b), the electron density profile presents the diffusion component flowing in the reverse direction to the total current. For the LSHD SNWFET, the gradient of the electron density along the channel direction representing the diffusion component is less than in any other cases. Therefore, the large electric field and low electron diffusion competitively affects the high sensitivity for the gate control, and the magnitude of  $I_{ON}$  is maintained at a certain level since the number of injected electrons is limited by  $N_{SRC}$ .

For the HSLD case, the voltage drop in the channel is the lowest even though  $N_{DRN}$  is the same as in the SD case and the electric field is lowest in the channel. However, the number of injected electrons is over 50% larger than for the other cases, so the drift current is quite large. For the reverse diffusion current, the gradient of the electron density along the channel direction representing the diffusion component is also high. Thus, the I<sub>D</sub> vs. V<sub>G</sub> characteristic of HSLD is a compromise between the two current components and the higher I<sub>ON</sub> value, with a similar tendency to the SD case as shown in Fig. 5(b).

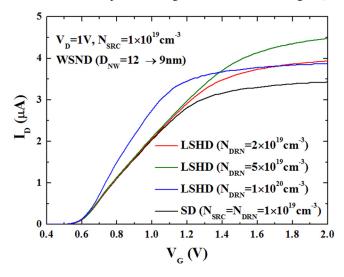

In addition to comparing LSHD and HSLD, we examined the effect of the doping difference between  $N_{SRC}$  and  $N_{DRN}$  as shown in Fig. 8. The devices used in Fig. 8 are WSND and LSHD with various  $N_{DRN}$  values. When the difference between  $N_{SRC}$  and  $N_{DRN}$  is not too large, a large  $I_{ON}$  phenomenon as seen in the HSLD case in Fig. 5 occurs even with the LSHD doping condition. This means that the overall trend is influenced by whether  $N_{DRN}$  or  $N_{SRC}$  has a higher value as well as by the difference in the doping value between both ends. As an example, to design the WSND with high  $I_{ON}$ ,

FIG. 8.  $I_D$  vs.  $V_G$  with  $V_D = 1 V$ . For all curves, WSND AG SNWFETs ( $L_G = 20 \text{ nm}, D_{NW} = 12 \text{ nm}$  for source and 9 nm for drain) are simulated and compared for each  $N_{DRN}$ . The black solid lines are the SD case with  $N_{SD} = 10^{19} \text{ cm}^{-3}$  for both contact sides, whereas the colored lines are the LSHD cases with the fixed value of  $N_{SRC} = 10^{19} \text{ cm}^{-3}$ . The red, green, and blue lines are for  $N_{DRN} = 2 \times 10^{19}$ ,  $5 \times 10^{19}$ , and  $10^{20} \text{ cm}^{-3}$ , respectively.

then HSLD is needed, or alternatively, LSHD with a low difference between  $N_{DRN}$  and  $N_{SRC}$  should be considered. Thus, according to the purpose and operating range of the AG SNWFET, the device design should include a careful understanding of the influence of  $N_{DRN}$  and  $N_{SRC}$ , since the transport characteristics greatly vary with the difference between  $N_{DRN}$  and  $N_{SRC}$ .

#### **IV. CONCLUSION**

We performed a 3D simulation to demonstrate the structural effects in sub-20 nm AG and SG SNWFETs. We analyzed the difference in the electrical and physical properties for various slopes of the channel width in the AG SNWFET. The WSND structure is predicted to be advantageous to the current drivability, operation speed, and  $I_{ON}$  distribution. Additionally, the effect of the difference between  $N_{DRN}$  and  $N_{SRC}$  has been investigated in the same manner as with AG and SG. For various doping conditions,  $I_{ON}$  and the switching characteristics are seriously affected. The results are caused by the electric field and electron density profile, so the device design should include a careful understanding of the influence of  $N_{DRN}$  and  $N_{SRC}$ .

#### ACKNOWLEDGMENTS

This research was supported by the "IT Consilience Creative Program" support program supervised by the NIPA (National IT Industry Promotion Agency) (C1515-11221-0003), the National Research Foundation of Korea Grant funded by the Korean Government (2010-0028110) and in part by the Korea Institute for Advanced Study (KIAS) in Korea.

- <sup>1</sup>J.-P. Colinge, Solid-State Electron. 48, 897 (2004).

- <sup>2</sup>S. Bangsaruntip, G. M. Cohen, A. Majumdar, Y. Zhang, S. U. Engelmann, N. C. M. Fuller, L. M. Gignac, S. Mittal, J. S. Newbury, M. Guillorn *et al.*, Tech. Dig. - Int. Electron Devices Meet. **2009**, 297.

- <sup>3</sup>J. Chen, T. Saraya, K. Miyaji, K. Shimizu, and T. Hiramoto, Jpn. J. Appl. Phys. **48**, 011205 (2009).

- <sup>4</sup>J. Chen, T. Saraya, K. Miyaji, K. Shimizu, and T. Hiramoto, Dig. Tech. Pap. - Symp. VLSI Technol. **2008**, 32.

- <sup>5</sup>J. Chen, T. Saraya, and T. Hiramoto, Tech. Dig. Int. Electron Devices Meet. 2008, 757.

- <sup>6</sup>C. Dupré, A. Hubert, S. Bécu, M. Jublot, V. Maffini-Alvaro, C. Vizioz, F. Aussenac, C. Arvet, S. Barnola, J.-M. Hartmann *et al.*, Tech. Dig. - Int. Electron Devices Meet. **2008**, 1.

- <sup>7</sup>K. Tachi, M. Cassé, S. Barraud, C. Dupré, A. Hubert, N. Vulliet, M. E. Faivre, C. Viziozl, C. Carabasse, V. Delaye *et al.*, Tech. Dig. Int. Electron Devices Meet. **2010**, 784.

- <sup>8</sup>H. Takato, K. Sunouchi, N. Okabe, A. Nitayama, K. Hieda, F. Horiguchi, and F. Masuoka, Tech. Dig. Int. Electron Devices Meet. **1988**, 222.

- <sup>9</sup>K. Sunouchi, H. Takato, N. Okabe, T. Yamada, T. Ozaki, S. Inoue, K. Hashimoto, K. Hieda, A. Nitayama, F. Horiguchi *et al.*, Tech. Dig. - Int. Electron Devices Meet. **1989**, 23.

- <sup>10</sup>B. Yang, K. D. Buddharaju, S. H. G. Teo, N. Singh, G. Q. Lo, and D. L. Kwong, IEEE Electron Device Lett. **29**, 791 (2008).

- <sup>11</sup>M. T. Bjork, O. Hayden, H. Schmid, H. Riel, and W. Riess, Appl. Phys. Lett. **90**, 142110 (2007).

- <sup>12</sup>H. T. Ng, J. Han, T. Yamada, P. Nguyen, Y. P. Chen, and M. Meyyappan, Nano Lett. 4, 1247 (2004).

- <sup>13</sup>S. Sato, K. Kakushima, K. Ohmori, K. Natori, K. Yamada, and H. Iwai, Appl. Phys. Lett. **99**, 223518 (2011).

- <sup>14</sup>T. Schulz, W. Xiong, C. R. Cleavelin, K. Schruefer, M. Gostkowski, K. Matthews *et al.*, Proc. IEEE Int. SOI Conf. **2005**, 154.

- <sup>15</sup>C. Lee, A. Afzalian, I. Ferain, R. Yan, N. D. Akhavan, W. Xiong, and J.-P. Colinge, Solid-State Electron. 54, 226–230 (2010).