Queen's University Belfast

To be completed by Student

| Degree: |  |

|---------|--|

|---------|--|

PhD

## Charalampos Chalios

Thesis title:

Full Name:

## Software-defined Significance-Driven Computing

Summary: (max. 300 words)

Approximate computing has been an emerging programming and system design paradigm that has been proposed as a way to overcome the power-wall problem that hinders the scaling of the next generation of both high-end and mobile computing systems. Towards this end, a lot of researchers have been studying the effects of approximation to applications and those hardware modifications that allow increased power benefits for reduced reliability. In this work, we focus on runtime system modifications and task-based programming models that enable software-controlled, user-driven approximate computing.

We employ a systematic methodology that allows us to evaluate the potential energy and performance benefits of approximate computing using as building blocks unreliable hardware components. We present a set of extensions to OpenMP 4.0 that enable the programmer to define computations suitable for approximation. We introduce task-significance, a novel concept that describes the contribution of a task to the quality of the result. We use significance as a channel of communication from domain specific knowledge about applications towards the runtime-system, where we can optimise approximate execution depending on user constraints. Finally, we show extensions to the Linux kernel that enable it to operate seamlessly on top of unreliable memory and provide a user-space interface for memory allocation from the unreliable portion of the physical memory. Having this framework in place allowed us to identify what we call the refresh-by-access property of applications that use dynamic random-access memory (DRAM). We use this property to implement techniques for task-based applications that minimise the probability of errors when using unreliable memory enabling increased quality and power efficiency when using unreliable DRAM.

#### To be completed by Examiner EXAMINER CERTIFICATION OF SUBMITTED WORK

I hereby certify that this is the final accepted copy of the submitted work and that all required amendments have been completed and submitted within the required deadline.

Name of Examiner: Dr. Ivor Spence

Signature of Examiner:

Date: 11/12/2017

## To be completed by Student **Student Declaration**:

I give permission for my thesis to be made available, under regulations determined by the University, for inclusion in the University Library, consultation by readers in the School, inter-library lending for use in another library and to be photocopied, electronically reproduced and to be stored and made available publicly in electronic format Please tick as appropriate:

| i)     | Immediately 🗹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                 |                    |                    |                 |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|--------------------|--------------------|-----------------|--|--|

| ii)    | Or<br>After an embargo period of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 year 🔲       | 2 years         | 3 years            | 4 years            | 5 years         |  |  |

| Reaso  | on for embargo: (applies to both p<br>The thesis is due for publication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | ,               | or as a monogra    | oh                 |                 |  |  |

|        | The thesis includes material tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t was obtained | l under a prom  | ise of confidentia | ality              |                 |  |  |

|        | Would substantially prejudice the second s | ne commercial  | interests of th | e author, the Un   | iversity or an ext | ternal company  |  |  |

|        | Contains information which ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | y endanger the | e physical/men  | tal health or pers | sonal safety of a  | n individual(s) |  |  |

| l wish | I wish to embargo the e-thesis copy permanently: (applies to e-thesis only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                 |                    |                    |                 |  |  |

|        | The thesis contains material whether the material electronically would compromise the thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                 |                    |                    |                 |  |  |

#### CONFIRMATION OF DATA/HUMAN TISSUE SAMPLES HANDOVER

All research involving human participants, their tissue (e.g. blood, saliva, urine) or their data (interviews, consent forms, questionnaires) must be retained by the University for at least five years. These sources must be handed over to your supervisor. Please confirm, by ticking the appropriate box, that:

I have provided my supervisor with all laboratory notebooks and/or primary source material pertaining to the study, including electronic data.

I have identified for my supervisor the location of stored human tissue samples and provided an inventory of these.

Due to the nature of the project I am not required to handover any data or samples relating to my thesis.

Signature of Student:

ά

Date:

10/12/2017

To be completed by Supervisor SUPERVISOR CONFIRMATION AND APPROVAL

I approve any embargo request above and confirm that the information given regarding Data/Human tissue samples is correct and that, where applicable<sup>\*</sup>, the final copy of the thesis has also been made available in electronic format (e-thesis) via PURE.

Name of Supervisor:

**Prof Dimitrios S. Nikolopoulos**

Signature of Supervisor:

Desider

Date: 11/12/2017

\* RCUK funded students and <u>all</u> students who commence research from September 2016 must also submit an electronic copy of their thesis via Pure

# Software-defined Significance-Driven Computing

**Charalampos Chalios**

A thesis presented for the degree of Doctor of Philosophy

School of Electronics, Electrical Engineering and Computer Science Queen's University of Belfast United Kingdom Wednesday 20<sup>th</sup> December, 2017

I dedicate this to my family, my friends and my teachers.

### Acknowledgements

The research included in this thesis was conducted during my stay in the School of Electronics, Electrical Engineering and Computer Science of Queen's University of Belfast in United Kingdom. Queen's welcomed me and offered me everything a young researcher needs in order to be able to carry out the challenging task of doing research and writing a thesis for the degree of Doctor of Philosophy. Moreover, I have to acknowledge the Department of Employment and Learning for my scholarship and the European Commission which through EU projects funded my research.

I would like to express my deep gratitude for my mentor Professor Dimitrios S. Nikolopoulos who was the first person to believe in me, in my life as a researcher, and gave me the opportunity to develop my skills and knowledge. He has been a role model for me as a researcher and through his guidance I believe I have become a better scientist. Moreover, I would like to thank my supervisor Dr. Hans Vandierendonck who has been a true teacher to me. His clarity of thought, technical integrity and most importantly his inexhaustible patience in transferring knowledge has been invaluable during the course of my studies.

I would like also to thank my colleagues in Belfast and Athens who have been great collaborators and friends. From the CSLAB of the School of ECE of the National and Technical University of Athens, Dr. Nikos Anastopoulos, Dr Kostis Nikas and Dr Georgios I. Gkoumas that were the people that first stirred in me the interest in research and till today have been helping me in every step of my research. Dr. Giorgis Georgakoudis, who was the first friend I made in Belfast and has been there for me from the first day of my PhD till now. Our discussions, more often than not heated, have been particularly inspiring and moments of true relaxation during the burdens of the academic life. Finally, I would like to thank Dr. Lev Mukhanov, Dr Kiril Dichev, (soon to be Dr.) Kosta Tovletoglou and Dr. Georgios Karakonstantis for the collaboration and the nice moments we had over that pint of Guinness after work.

I feel sincerely grateful for all the beautiful people I met during this trip, who honoured me with their friendship. Life in Belfast would not have been the same were it not for number 13 Chadwick Street. I would like to thank Davide, Ioanna, Leonardo and Lisa for their friendship, their tolerance of my anti-sociality, the dinners, the games, the trips and the BBQs. Athanasia thank you for showing me, even maybe without realizing it, that there are few things you cannot do if you really love them. You are a beautiful person and valuable friend. Miguel you are one of the most clever, humorous, creative and good-hearted people I have ever met. Stephania, thank you for some of the most insteresting, constructive and heated discussions I have had over a glass of wine. Vincenzo and Giuliano I am really greateful for all the beautiful moments and the fact that you made Belfast look a bit more like home. Mauro, thanks for the relaxing and creative nights on this red sofa under the Bob Marley painting. Finally, Ntina thanks a lot for your hospitality and really good heart. No matter how far away, I am really happy you are my friends.

Circumstances made a lot of us to move around the world, in order to find whatever it is we were looking for. Even if we weren't physically close to each other, I need to thank these people that over the years we didn't let distance to keep us apart. Taso, Panteli and Odyssea, in a sense if it weren't for you I would probably be still back to Athens trying to pass that SAE course. Polyzo, Kosma, Vasili, Riga and Mike thanks for the studying, drinking, eating, playing, etc. during these beautiful 7 years. Mikou, special thanks to you for all the early coffees and late drinks. Finally, Athina, Thoma, Alexandre (Takou), thank you for these, brief but beautiful, moments we spent together in "our house" and out of it, and deeply changed who I am.

Many thanks I owe to my parents, Kostas and Rodokleia, and my brothers Stratos and Giorgos for their unconditional love and support throughout my life. You have been always there for me through good and bad moments and I know that I would never have achieved as much in life if it were not for you.

This whole journey has been even more beautiful because of one person. Paola, my life partner, has been there every single step of the way. Somehow, she managed to make these three years the most beautiful years of my life. Being the most strong person I have ever met, she helped me keep going, during the most difficult and hard moments of this endeavour. Thank you for all your support and patience.

### Abstract

### Software-defined Significance-based Computing

by

Charalampos Chalios A thesis presented for the degree of Doctor of Philosophy

School of Electornics, Electrical Engineering and Computer Science Queen's University of Belfast April 2017

Approximate computing has been an emerging programming and system design paradigm that has been proposed as a way to overcome the power-wall problem that hinders the scaling of the next generation of both high-end and mobile computing systems. Towards this end, a lot of researchers have been studying the effects of approximation to applications and those hardware modifications that allow increased power benefits for reduced reliability. In this work, we focus on runtime system modifications and task-based programming models that enable software-controlled, user-driven approximate computing.

We employ a systematic methodology that allows us to evaluate the potential energy and performance benefits of approximate computing using as building blocks unreliable hardware components. We present a set of extensions to OpenMP 4.0 that enable the programmer to define computations suitable for approximation. We introduce task-significance, a novel concept that describes the contribution of a task to the quality of the result. We use significance as a channel of communication from domain specific knowledge about applications towards the runtime-system, where we can optimise approximate execution depending on user constraints. Finally, we show extensions to the Linux kernel that enable it to operate seamlessly on top of unreliable memory and provide a user-space interface for memory allocation from the unreliable portion of the physical memory. Having this framework in place allowed us to identify what we call the refresh-by-access property of applications that use dynamic random-access memory (DRAM). We use this property to implement techniques for task-based applications that minimise the probability of errors when using unreliable memory enabling increased quality and power efficiency when using unreliable DRAM.

## **Related publications**

- Charalampos Chalios, Dimitrios S. Nikolopoulos, Sandra Catalán, and Enrique S. Quintana-Ortí. Evaluating fault tolerance on asymmetric multicore systemson-chip using iso-metrics. *IET Computers & Digital Techniques*, 10(2):85–92, 2016.

- [2] Vassilis Vassiliadis, Charalampos Chalios, Konstantinos Parasyris, Christos D. Antonopoulos, Spyros Lalis, Nikolaos Bellas, Hans Vandierendonck, and Dimitrios S. Nikolopoulos. Exploiting significance of computations for energyconstrained approximate computing. *International Journal of Parallel Programming*, 44(5):1078–1098, 2016.

- [3] Philipp Gschwandtner, Charalampos Chalios, Dimitrios S. Nikolopoulos, Hans Vandierendonck, and Thomas Fahringer. On the potential of significance-driven execution for energy-aware HPC. *Computer Science - R&D*, 30(2):197–206, 2015.

- [4] Vassilis Vassiliadis, Charalampos Chalios, Konstantinos Parasyris, Christos D. Antonopoulos, Spyros Lalis, Nikolaos Bellas, Hans Vandierendonck, and Dimitrios S. Nikolopoulos. A significance-driven programming framework for energy-constrained approximate computing. In Napoli et al. [5], pages 9:1–9:8.

- [5] Claudia Di Napoli, Valentina Salapura, Hubertus Franke, and Rui Hou, editors. Proceedings of the 12th ACM International Conference on Computing Frontiers, CF'15, Ischia, Italy, May 18-21, 2015. ACM, 2015.

- [6] José Ignacio Aliaga, Sandra Catalán, Charalampos Chalios, Dimitrios S. Nikolopoulos, and Enrique S. Quintana-Ortí. Performance and fault tolerance of

preconditioned iterative solvers on low-power ARM architectures. In Joubert et al. [7], pages 711–720.

- [7] Gerhard R. Joubert, Hugh Leather, Mark Parsons, Frans J. Peters, and Mark Sawyer, editors. *Parallel Computing: On the Road to Exascale, Proceedings of the International Conference on Parallel Computing, ParCo 2015, 1-4 September* 2015, Edinburgh, Scotland, UK, volume 27 of Advances in Parallel Computing. IOS Press, 2016.

- [8] Vassilis Vassiliadis, Konstantinos Parasyris, Charalambos Chalios, Christos D. Antonopoulos, Spyros Lalis, Nikolaos Bellas, Hans Vandierendonck, and Dimitrios S. Nikolopoulos. A programming model and runtime system for significance-aware energy-efficient computing. In Cohen and Grove [9], pages 275–276.

- [9] Albert Cohen and David Grove, editors. Proceedings of the 20th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPoPP 2015, San Francisco, CA, USA, February 7-11, 2015. ACM, 2015.

- [10] Charalampos Chalios, Dimitrios S. Nikolopoulos, and Enrique S. Quintana-Ortí. Evaluating asymmetric multicore systems-on-chip using iso-metrics. *CoRR*, abs/1503.08104, 2015.

- [11] Vassilis Vassiliadis, Konstantinos Parasyris, Charalambos Chalios, Christos D. Antonopoulos, Spyros Lalis, Nikolaos Bellas, Hans Vandierendonck, and Dimitrios S. Nikolopoulos. A programming model and runtime system for significance-aware energy-efficient computing. *CoRR*, abs/1412.5150, 2014.

## **Table of contents**

| Re | lated   | publica                              | ations                                                      | xi   |

|----|---------|--------------------------------------|-------------------------------------------------------------|------|

| Li | st of f | igures                               |                                                             | xvii |

| Li | st of t | ables                                |                                                             | xxi  |

| 1  | Intr    | oductio                              | n                                                           | 1    |

|    | 1.1     | Motiva                               | ution                                                       | 1    |

|    | 1.2     | Approx                               | ximate Computing                                            | 5    |

|    | 1.3     | Contril                              | bution - Synopsis                                           | 6    |

| 2  | Bacl    | kground                              | 1                                                           | 9    |

|    | 2.1     | Near T                               | Threshold Voltage Computing                                 | 9    |

|    | 2.2     | Approximate Computing                |                                                             | 13   |

|    |         | 2.2.1                                | Application-based Fault Tolerance                           | 14   |

|    |         | 2.2.2                                | Parallel Approximation Frameworks                           | 15   |

|    |         | 2.2.3                                | Other Approximation Frameworks                              | 16   |

|    | 2.3     | DRAM Reliability and Fault Tolerance |                                                             | 18   |

|    |         | 2.3.1                                | Pessimism of Auto-Refresh Operation                         | 20   |

|    |         | 2.3.2                                | Related Work on Relaxing the Refresh-Rate and Open Issues   | 21   |

|    |         | 2.3.3                                | Refresh-by-access                                           | 23   |

| 3  | Use     | Cases fo                             | or Approximate Computing                                    | 25   |

|    | 3.1     | On the                               | Potential of Significance-Driven Execution for Energy-Aware |      |

|    |         | High-p                               | performance Computing                                       | 25   |

|    |         | 3.1.1                                | Introduction                                                | 25   |

|    |         | 3.1.2                                | Significance                                                | 27   |

|   |      | 3.1.3     | Methodology                                                | 31 |

|---|------|-----------|------------------------------------------------------------|----|

|   |      | 3.1.4     | Results                                                    | 35 |

|   |      | 3.1.5     | Conclusion                                                 | 40 |

|   | 3.2  | Evalua    | ting Fault Tolerance on Asymmetric Multicore Systems-on-   |    |

|   |      | Chip u    | sing iso-metrics                                           | 41 |

|   |      | 3.2.1     | Introduction                                               | 41 |

|   |      | 3.2.2     | Experimental Setup                                         | 43 |

|   |      | 3.2.3     | High Performance vs Low Power                              | 45 |

|   |      | 3.2.4     | Energy Cost of Reliability                                 | 51 |

|   |      | 3.2.5     | Conclusions                                                | 55 |

| 4 | Expl | loiting t | he Significance of Computations for Energy-constrained Ap- |    |

|   | prox | ximate (  | Computing                                                  | 57 |

|   | 4.1  | Introdu   | uction                                                     | 57 |

|   | 4.2  | Progra    | mming Model                                                | 60 |

|   | 4.3  | Runtin    | ne                                                         | 64 |

|   |      | 4.3.1     | Runtime API Extension                                      | 64 |

|   |      | 4.3.2     | Runtime Support for Approximate Computing                  | 65 |

|   |      | 4.3.3     | Global Task Buffering (GTB)                                | 65 |

|   |      | 4.3.4     | Local Queue History (LQH)                                  | 66 |

|   | 4.4  | Experi    | mental Evaluation of the Runtime System                    | 67 |

|   |      | 4.4.1     | Approach                                                   | 68 |

|   |      | 4.4.2     | Experimental Results                                       | 71 |

|   | 4.5  | Model     | ling and Prediction of Application Energy Footprint        | 76 |

|   |      | 4.5.1     | Analytical Model of Execution Time                         | 77 |

|   |      | 4.5.2     | Analytical Model of Power and Energy Consumption           | 78 |

|   |      | 4.5.3     | Offline Profiling and Model Fitting                        | 79 |

|   | 4.6  | Experi    | mental Evaluation of Approximate Computing Framework       | 80 |

|   |      | 4.6.1     | Benchmarks                                                 | 80 |

|   |      | 4.6.2     | Experimental Methodology                                   | 83 |

|   |      | 4.6.3     | Experimental Evaluation and Discussion                     | 84 |

|   | 4.7  | Conclu    | ision                                                      | 89 |

| 5  | DAI                             | RE: Dat   | ta-Access Aware Refresh via Spatial-Temporal Application- | •   |  |  |  |

|----|---------------------------------|-----------|-----------------------------------------------------------|-----|--|--|--|

|    | Resi                            | ilience o | on Commodity Servers                                      | 91  |  |  |  |

|    | 5.1                             | Introd    | uction                                                    | 91  |  |  |  |

|    | 5.2                             | The D     | ARE Approach                                              | 94  |  |  |  |

|    |                                 | 5.2.1     | Refresh-by-access Memory Model                            | 95  |  |  |  |

|    |                                 | 5.2.2     | Access-aware Scheduling                                   | 97  |  |  |  |

|    | 5.3                             | Realiz    | ting DARE on a Commodity Server                           | 99  |  |  |  |

|    |                                 | 5.3.1     | Hardware Platform                                         | 99  |  |  |  |

|    |                                 | 5.3.2     | Software Stack                                            | 102 |  |  |  |

|    | 5.4 Evaluation                  |           |                                                           |     |  |  |  |

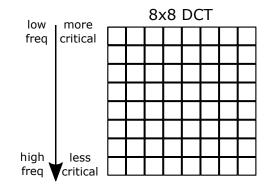

|    |                                 | 5.4.1     | JPEG and Discrete Cosine Transform (DCT)                  | 105 |  |  |  |

|    |                                 | 5.4.2     | Sobel filter                                              | 108 |  |  |  |

|    |                                 | 5.4.3     | Pochoir Stencil Algorithms                                | 110 |  |  |  |

|    | 5.5                             | Concl     | usions                                                    | 111 |  |  |  |

| 6  | Conclusions and Future Work 113 |           |                                                           |     |  |  |  |

|    | 6.1                             | Summ      | nary of Contributions                                     | 114 |  |  |  |

|    |                                 | 6.1.1     | Evaluating Approximate Computing Using iso-metrics        | 114 |  |  |  |

|    |                                 | 6.1.2     | Programming Models for Approximate Computing              | 115 |  |  |  |

|    |                                 | 6.1.3     | Memory Reliability and System Level Management of Ap-     |     |  |  |  |

|    |                                 |           | proximate Computing                                       | 116 |  |  |  |

|    | 6.2                             | Future    | e Work                                                    | 117 |  |  |  |

| Re | eferen                          | ices      |                                                           | 119 |  |  |  |

# List of figures

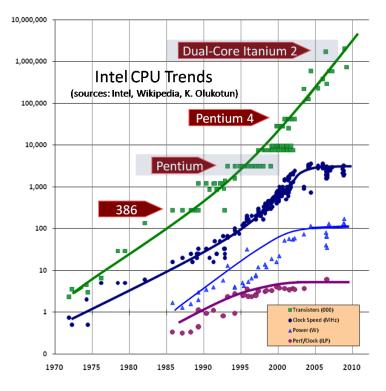

| 1.1 | Intel CPU introductions, clock speed and power consumption [83]           | 2  |

|-----|---------------------------------------------------------------------------|----|

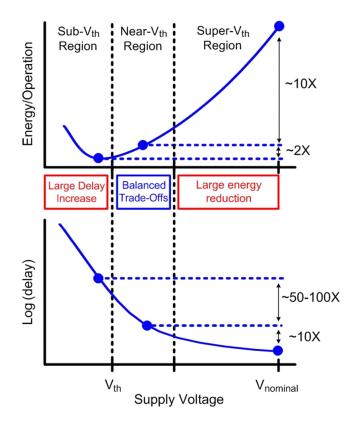

| 2.1 | Energy and delay in different supply voltage operating regions [19].      | 10 |

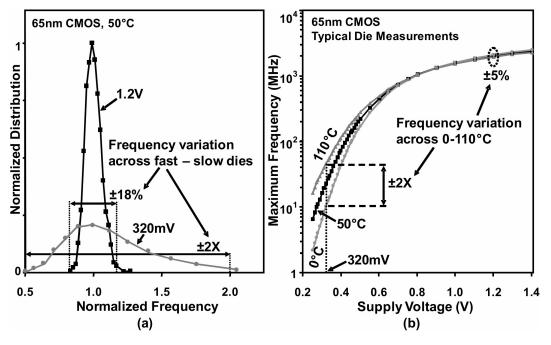

| 2.2 | Modeling and measurements of variation [42]                               | 11 |

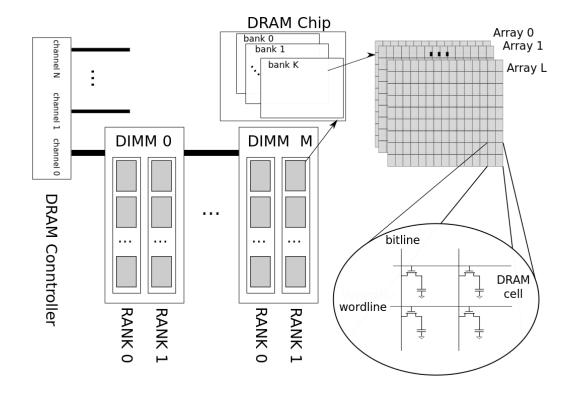

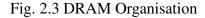

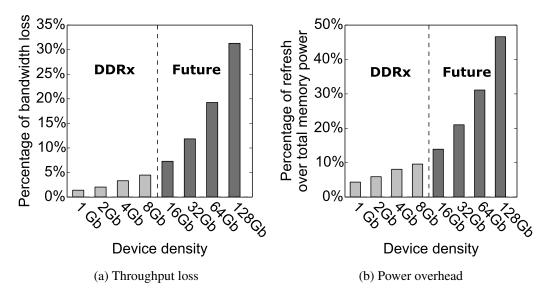

| 2.3 | DRAM Organisation                                                         | 19 |

| 2.4 | Power and performance overheads on current and future DRAM                |    |

|     | technologies [48]                                                         | 19 |

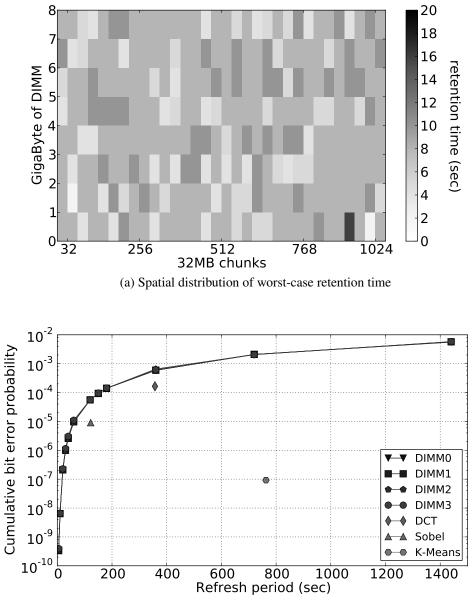

| 2.5 | Retention Time Characterisation on a Commodity Server with Server-        |    |

|     | Grade DRAMs                                                               | 21 |

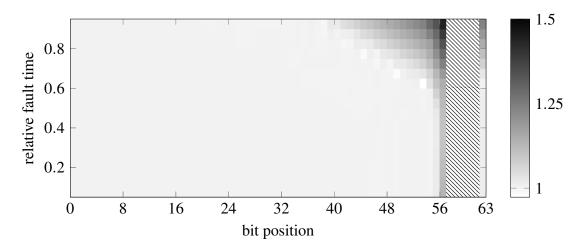

| 3.1 | Relative time overhead of Jacobi for faults in A at various iterations,   |    |

|     | averaged over all matrix positions, for all bit positions ( $N = 1000$ ). |    |

|     | The hatched bar denotes divergence.                                       | 27 |

| 3.2 | Relative time overhead of Jacobi for faults in A at all matrix positions, |    |

|     | averaged over all bit positions ( $N = 10$ )                              | 29 |

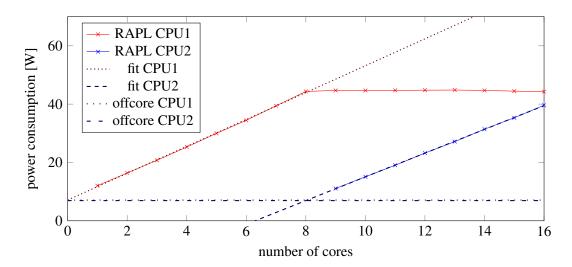

| 3.3 | Power consumption per number of cores on two Intel Xeon E5-4650           |    |

|     | for a weakly scaling Jacobi run as measured by RAPL, and offcore          |    |

|     | amount as inferred via linear fitting.                                    | 33 |

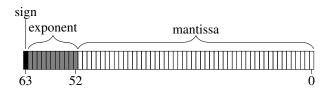

| 3.4 | IEEE 754 binary64 format.                                                 | 35 |

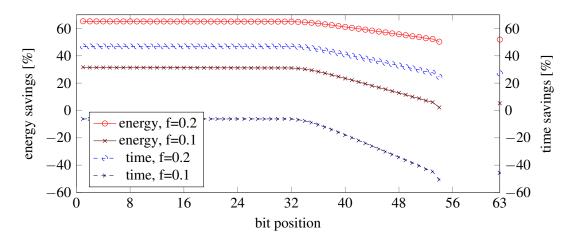

| 3.5 | Relative energy and time savings of an unreliable, parallel run of        |    |

|     | Jacobi on 16 cores compared to a reliable, sequential one. The            |    |

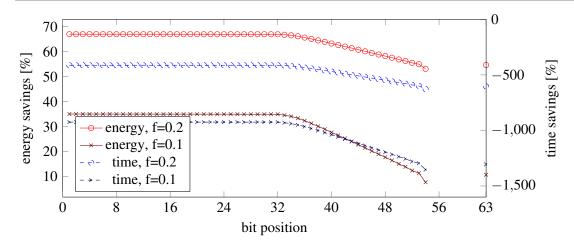

|     | missing data at bits 55–62 denote divergence                              | 38 |

| 3.6 | Relative energy and time savings of an unreliable, parallel run of        |    |

|     | Jacobi compared to a reliable, parallel run on 16 cores. The missing      |    |

|     | data at bits 55–62 denote divergence                                      | 39 |

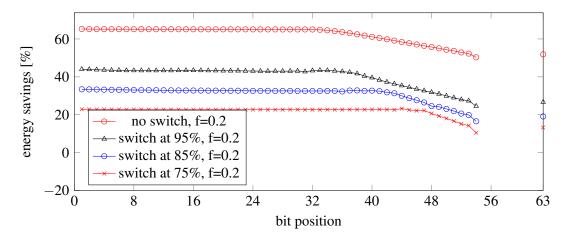

| 3.7  | Relative energy savings of an adaptive reliable/unreliable run of Ja-<br>cobi on 16 cores compared to a reliable, sequential one, for switching<br>to reliable hardware at 75%, 85%, and 95% runtime. The missing                                         |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | data at bits 55–62 denote divergence                                                                                                                                                                                                                      | 40 |

| 3.8  | Relative time savings of a hybrid reliable/unreliable run of Jacobi on 16 cores compared to a reliable, sequential one, for switching to reliable hardware at 75%, 85%, and 95% runtime. The missing data at bits 55–62 denote divergence.                | 41 |

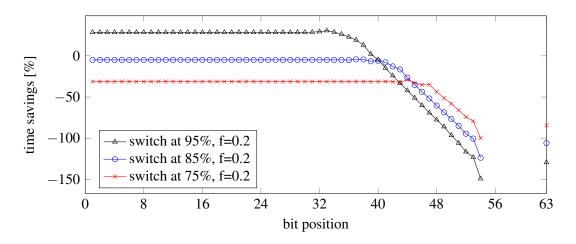

| 3.9  | Evaluation of performance, power, and energy on the target archi-<br>tectures using multi-threaded implementations of the CG method on<br>both the on-chip and off-chip problems.                                                                         | 47 |

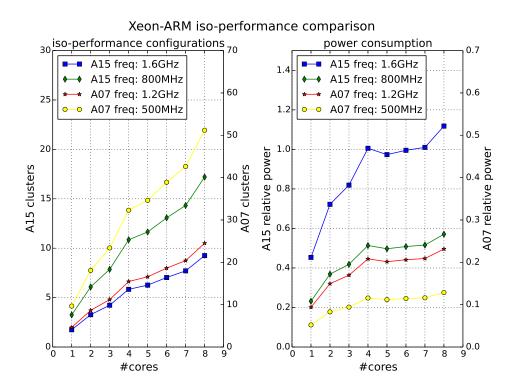

| 3.10 | Evaluation of iso-performance. Left: Number of A15 or A7 clus-<br>ters required to match the performance of a given number of Xeon<br>cores at 2.0 GHz. Right: Comparison of power rates dissipated for<br>configurations delivering the same performance | 50 |

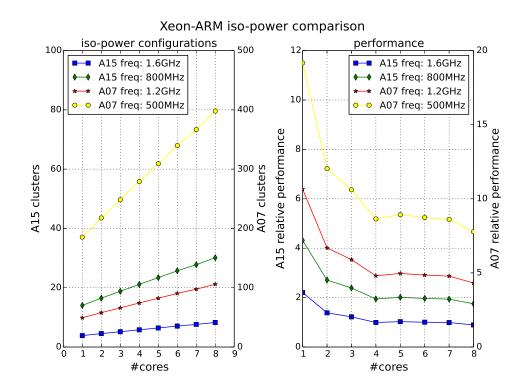

| 3.11 | Evaluation of iso-power. Left: Number of A15 or A7 clusters that<br>match the power dissipated by a given number of Xeon cores at<br>2.0 GHz. Right: Comparison of performance rates attained for<br>configurations dissipating the same power rate       | 51 |

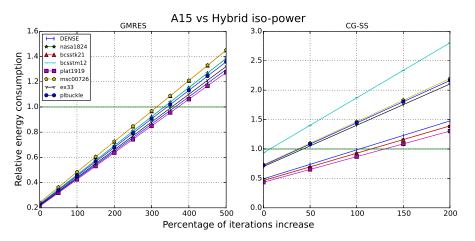

| 3.12 | Iso-performance ETS for the original CG (right) and GMRES (left) methods executed by A15 at the highest frequency (reliable mode) and the SS variant of CG executed by NA15/A7 under unreliable conditions that degrade convergence.                      | 54 |

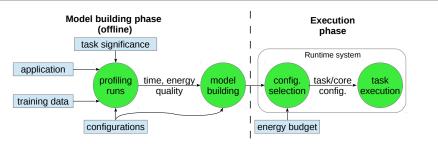

| 4.1  | Our methodology to maximise the output quality of applications that<br>approximate computations while respecting a user-specified energy<br>constraint to gracefully trade off output quality for energy reduction.                                       | 58 |

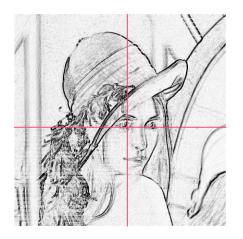

| 4.2  | Different levels of approximation for the Sobel benchmark                                                                                                                                                                                                 | 68 |

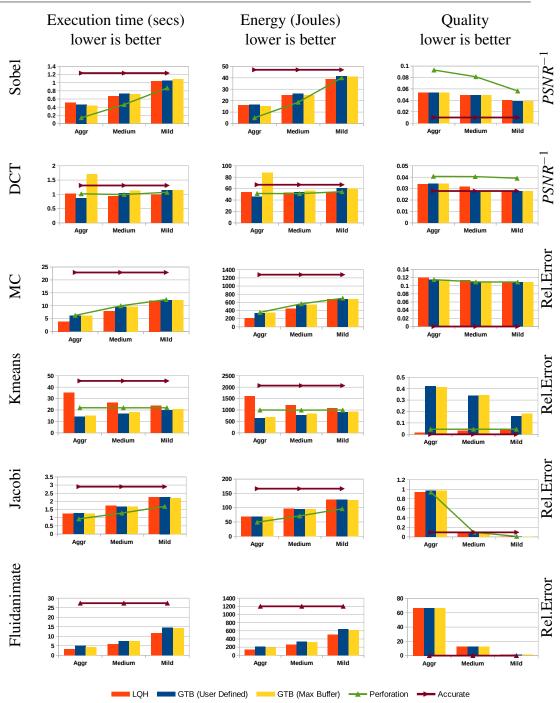

| 4.3 | Execution time, energy, and quality of results for the benchmarks                           |

|-----|---------------------------------------------------------------------------------------------|

|     | used in the experimental evaluation under different runtime policies                        |

|     | and degrees of approximation. In all cases, lower is better. Quality is                     |

|     | depicted as PSNR $^{-1}$ for Sobel and DCT, relative error (%) is used                      |

|     | in all other benchmarks. The accurate execution and the approxi-                            |

|     | mate execution using perforation are visualised as lines. Note that                         |

|     | perforation was not applicable for Fluidanimate                                             |

| 4.4 | Different levels of perforation for the Sobel benchmark. Accurate                           |

|     | execution, perforation of 20%, 70%, and 100% of loop iterations                             |

|     | on the upper left, upper right, lower left, and lower right quadrants                       |

|     | respectively                                                                                |

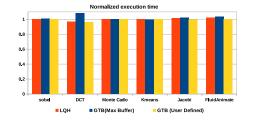

| 4.5 | Normalised execution time of benchmarks under different task cate-                          |

|     | gorisation policies with respect to that over the significance-agnostic                     |

|     | runtime system                                                                              |

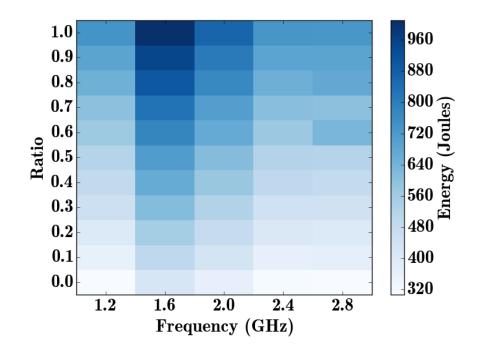

| 4.6 | Energy footprint of the <i>fisheye</i> benchmark under different (CPUF requency, TaskRatio) |

|     | configurations                                                                              |

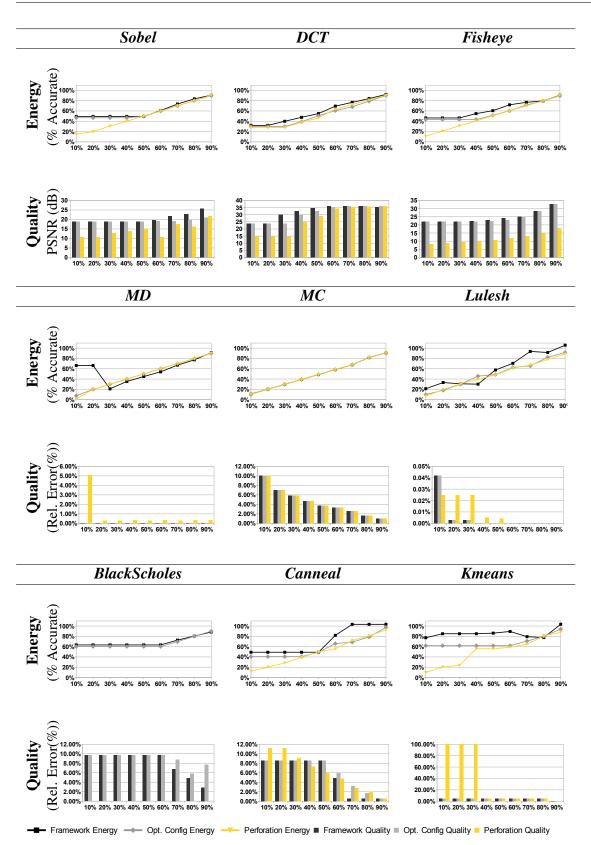

| 4.7 | Quality and energy metrics for different energy targets (as a per-                          |

|     | centage of the most energy-efficient accurate execution). Energy                            |

|     | and quality plots show the results achieved by our system, an oracle                        |

|     | selecting the optimal configuration, and loop perforation 85                                |

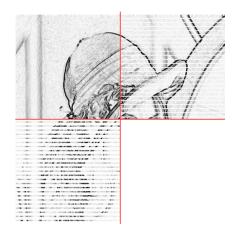

| 4.8 | Lena portrait compressed and decompressed using DCT with a ratio                            |

|     | of 0.3                                                                                      |

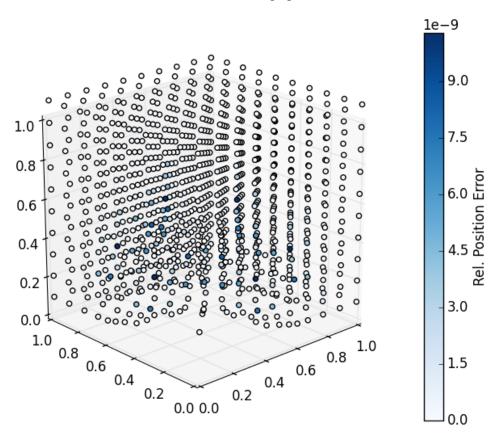

| 4.9 | Final positions of particles for an approximate execution with ratio                        |

|     | 0.2. Particles have been coloured according to the relative error of                        |

|     | their position with respect to an accurate execution                                        |

| 5.1 | Example of harnessing refresh-by-access in order to reduce the                              |

|     | expected number of errors                                                                   |

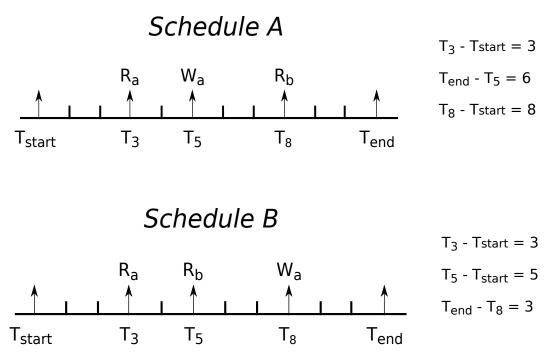

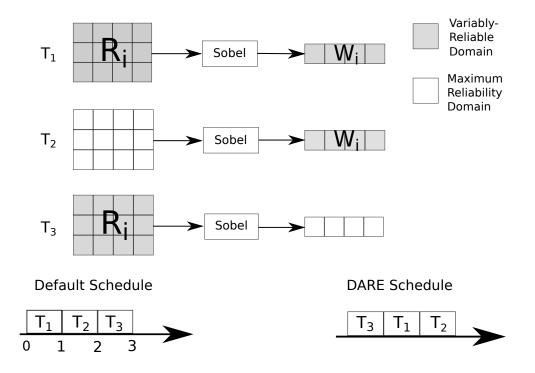

| 5.2 | Default and DARE scheduling                                                                 |

| 5.3 | Software refresh controller                                                                 |

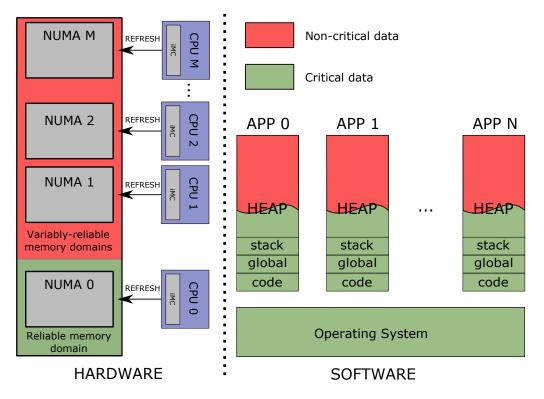

| 5.4 | Hardware and software setup for variably-reliable memory 101                                |

|     |                                                                                             |

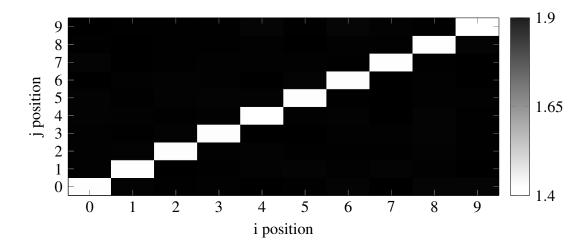

| 5.5 | Data criticality within an $8 \times 8$ DCT block                                           |

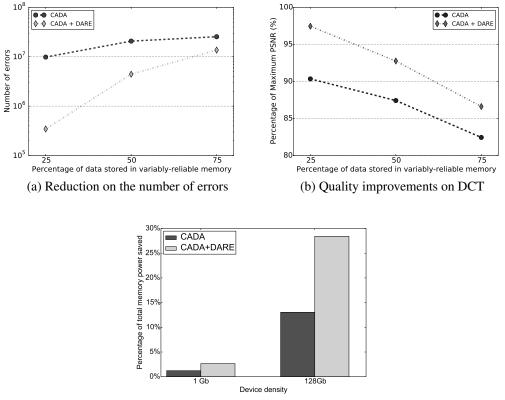

| 5.6 | Comparison of application resilience techniques for DCT using        |

|-----|----------------------------------------------------------------------|

|     | variably-reliable memory without refresh                             |

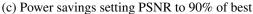

| 5.7 | Comparison of application resilience techniques for Sobel using      |

|     | variably-reliable memory without refresh                             |

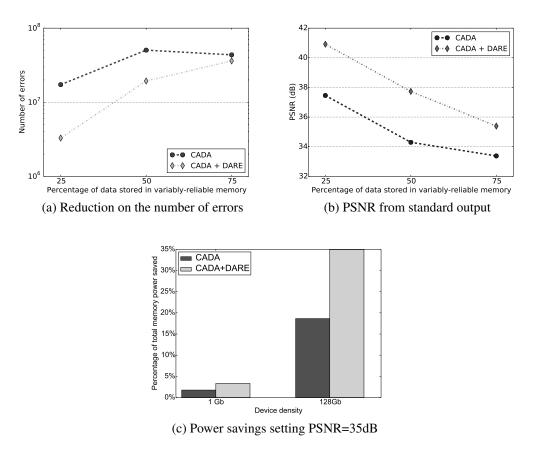

| 5.8 | DARE trapezoidal decomposition applied in the Pochoir compiler . 111 |

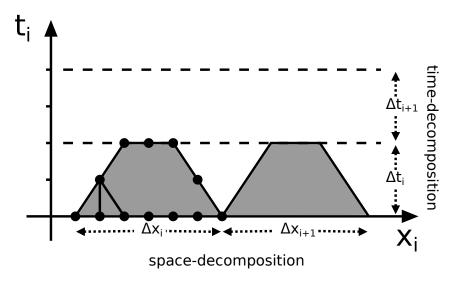

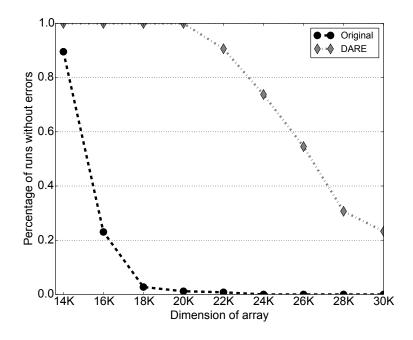

| 5.9 | Comparison of DARE Pochoir versus the original                       |

## List of tables

| 3.1 | Hardware specifications of the target architectures                                                                                                                                                                                                                                            | 44 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Sparse matrices from UFMC employed in the evaluation                                                                                                                                                                                                                                           | 45 |

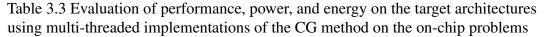

| 3.3 | Evaluation of performance, power, and energy on the target archi-                                                                                                                                                                                                                              |    |

|     | tectures using multi-threaded implementations of the CG method on                                                                                                                                                                                                                              |    |

|     | the on-chip problems                                                                                                                                                                                                                                                                           | 48 |

| 3.4 | Iso-performance of reliable A15 cluster vs unreliable NA15/A7                                                                                                                                                                                                                                  | 54 |

| 4.1 | Benchmarks used for the evaluation. For all cases, except Jacobi, the approximation degree is given by the percentage of accurately executed tasks. In Jacobi, it is given by the error tolerance in convergence of the accurately executed iterations/tasks $(10^{-5} \text{ in the native})$ |    |

|     | version)                                                                                                                                                                                                                                                                                       | 68 |

| 4.2 | Degree of accuracy of the proposed policies                                                                                                                                                                                                                                                    | 75 |

## Chapter 1

## Introduction

### 1.1 Motivation

The unprecedented increase in computing capabilities that we experienced in the past decades was founded in mainly two principles. First, the number of transistors that we can fit into an integrated circuit doubles approximately every two years. This property, which is commonly known as the "Moore's Law", stems from the ability of material scientists to halve the size of metal-oxide semiconductor field-effect transistor (MOSFET) transistors, used for manufacturing central processing units (CPUs), every two years. At the same time, Dennard scaling indicates that, as transistors get smaller, their power consumption in proportion to their area stays constant (i.e., approximately every two years, we pack twice the number of transistors in the same chip, consuming the same amount of power as before).

These trends have translated into significant performance improvements with every new generation of processors, since hardware architects have scaled the CPU clock without significantly increasing the power consumption of the chip. The CPU frequency increase along with the architectural optimisations are made possible by the abundance of transistors in the chip, boosting applications without the need for major software optimisations. However, in the middle of the last decade, we experienced the end of the Dennard scaling era. In small manufacturing processes, the leakage current, which could previously be ignored, now poses significant challenges to hardware designers.

Fig. 1.1 Intel CPU introductions, clock speed and power consumption [83].

Leakage current consumes non-negligible static power and contributes significantly to the heating of the chip, which further burdens the power budget of the processor. To restrict static power consumption due to leakage, designers kept the supply voltage of the chip high, and at the same time, the switching frequency stopped following the increasing trends of previous generations. Thus, while our needs for computing and memory capacity continue to increase, our ability to build systems that cover those needs is hindered by the unsustainable power consumption these devices would require, a problem that was named the 'power-wall'. Consequently, the power-wall significantly hurt the performance of the processors, which already suffer from the saturation of the instruction-level parallelism (ILP). The free lunch was over.

This trend is depicted in Figure 1.1. Although the number of transistors in the chip keeps increasing as predicted by Moore's law, the increase of both the ILP and frequency have halted. Consequently, architects started using the extra transistors to fit more processing elements (cores) into one chip, causing a revolution in the computer science world. People from the software layers, systems software, and applications needed to put effort to take advantage of more cores found in the

processors to make up for the performance loss due to the CPU clocks not scaling as they did previously. Thus, new programming models and advanced operating and runtime systems were created in the software labs of academia and industry.

However, the electrical power that is required to operate all the cores of the CPU concurrently can exceed the available power budget of the chip. This means that only some of the available cores can operate simultaneously. This phenomenon is called 'dark silicon'. Part of the cores (silicon) are powered off during operation to not exceed the available power budget. This new reality makes power consumption a problem that we cannot expect the semiconductor technology to solve for us in the near future. Instead, both academia and industry focus on holistic approaches where power consumption is a first-order concern for everyone from the hardware architect and software developer to the system administrator.

According to Dennard scaling, reduction of supply voltage has been the most useful tool. Hardware designers must reduce the power consumption of complementary metal-oxide semiconductor (CMOS)-based chips. Lately, hardware vendors have allowed software mechanisms to control CPU voltage and frequency. These mechanisms were used in the core of several tools that tried to take advantage of opportunities for voltage scaling in situations where the CPU is idle. Several researchers [19, 54] have pointed out that the most energy-efficient voltage region of operation for CMOS transistors lies in the sub-threshold voltage region. However, operating in the sub-threshold region comes with significant performance reduction due to aggressive scaling of the CPU frequency. Thus, it is deemed more beneficial to operate in the near-threshold voltage (NTV) region, sacrificing a small amount of energy efficiency to maintain some of the performance. This system design is called near-threshold voltage computing (NTVC). Even in the NTV region, CMOS operation poses significant challenges related to system reliability due to the increased process variation. Consequently, a lot of research focuses on tackling the reliability challenges connected with NTVC.

Problems with reliability do not appear only in NTV operation. State-of-the-art systems consume a considerable amount of power to ensure correct operation of logic and memory circuits. Manufacturers apply pessimistic guard bands to circuits to ensure correct operations. This pessimistic approach is exacerbated due to process variation, which has worsened in current technologies. Process variation (i.e., the variation of the transistor characteristics during the manufacturing process) creates a spread in the optimal operating point (e.g., supply voltage) across transistors in the chip. This means that, to avoid incorrect operation of some of the transistors, we need to select a supply voltage higher than required for most transistors. In other words, the requirement for reliability (high voltage margins) clashes with the significant objective of power efficiency.

Similarly, dynamic random access memory (DRAM) specifications define the average refreshing period to be uniform for all DRAM cells, regardless their retention time (i.e., the time after which the cell will lose the information it holds if it does not get refreshed). For example, the double data rate fourth generation (DDR4) specification defines that the whole memory should refresh every 64 ms, whereas studies have shown that, for many DRAM devices, we observe a worst-case scenario retention time of approximately 1 s. Therefore, DRAM devices pessimistically consume an amount of power that, in future DRAM generations, is projected to be a significant proportion of the total DRAM power consumption.

The requirements for high reliability and accuracy also affect performance. Moreover, CPU overclocking has been known to increase the probability of timing failures within paths of the processor. Supply voltage determines the length of the critical path of the circuit. The critical path, in turn, determines the maximum frequency that we can use without timing violations. Similarly, refresh operations in DRAM interfere with normal memory accesses. When a refresh operation is on-the-fly in a bank of the DRAM chip, this bank is unavailable for loads and stores, which decreases the effective bandwidth of the main memory. There is an obvious trade-off between reliability and power consumption and performance.

The struggle between reliability against power consumption and performance is not restricted to the hardware domain. Software developers often must compromise power and/or performance to ensure sufficiently accurate computations. For example, using higher precision floating-point data types (e.g., double vs float) increases the execution time and the amount of memory we need to store the representation of our data. Recently, researchers have proposed relaxing the requirements for correctness and accuracy of computing systems, when this is acceptable, as a step towards overcoming the power-wall problem. Many applications can tolerate reduced accuracy in their output, while studies also show that it is possible to handle errors at the hardware level within the software stack. Thus, these observations triggered a great amount of research related to how we can systematically harness approximation to save other precious resources (e.g., power consumption and CPU cycles) and opened the way to a new computing paradigm, called approximate computing.

### **1.2** Approximate Computing

Approximate computing is a computing paradigm that allows an acceptable amount of inaccuracy in the result of a computation in exchange for reduction in the resources required for that computation. What makes approximate computing useful is the existence of applications that can afford bounded levels of inaccuracy in their results (e.g., the human eye can perceive up to a certain frame rate while watching a video). As a result, a video decoder can drop frames, as long as it ensures this critical frame rate is achieved.

Approximation can be realised both at the software and hardware level. Software schemes substitute a code block with an alternative implementation that produces the same result semantically, only with reduced accuracy. However, the approximate version of the computation consumes less resources in terms of power consumption or CPU time. For example, the loop perforation technique skips some of the iterations of a loop when this does not affect the quality significantly. Similar algorithmic approaches are followed by hardware designers. Alternative hardware implementations of an algorithm trade off accuracy for power consumption, execution time, or area. However, hardware approximation can be also implemented in general purpose CPUs as well as memory systems, such as DRAM or static random access memory (SRAM).

To cope with technological limitations, hardware designers enforce strict guard bands in the operating points of chips to minimise the failure probability of computing systems. Approximate computing allows chips to be configured outside the nominal operating points (e.g., CPU is undervolted or overclocked, an SRAM cache undervolted, and a DRAM chip refreshed less frequently). The consequence is increased failure probability, meaning that the probability of an error happening during the lifetime of an application is a possibility that can no longer be neglected. The responsibility of dealing with the errors that will occur due to operating the hardware in unsafe configurations is left to the software layers.

Since the burden of dealing with errors shifts towards the software stack, a significant amount of research has been carried out for studying application-specific methods to handle errors or algorithmic-based fault tolerance (ABFT). The ABFT approaches are methods specific to each algorithm that ensure the correct (or approximate) termination of the algorithm, even in the presence of errors or inaccuracies. Despite the strength of ABFT methods for dealing with errors, for approximate computing to become a prominent computing paradigm, there must be more general and systematic ways to handle errors. Towards this end, researchers have made efforts towards designing system-wide solutions for fault tolerance.

### **1.3** Contribution - Synopsis

The rest of the thesis is organised as follows. In Chapter 2, we discuss the background of approximate computing. We present the fundamental problem approximate computing attempts to solve and the different paths and research related to this field. Furthermore, we show how the work presented in this thesis deviates from this research.

In Chapter 3, we present an experimental evaluation of fault-tolerance characteristics of a popular iterative solver, Jacobi. We present a first case study of the energy efficiency of Jacobi when executed on an NTV processor. For our evaluation of NTVC, we account for the consequences of unreliability in the execution time of Jacobi. We show that it is possible to attain energy savings between 35% and 67% compared to a system operating at nominal voltage ranges. Next, we present a more systematic approach to evaluate the energy efficiency of an NTV system, using two additional iterative solvers, conjugate gradient (CG) and the generalised minimal residual method (GMRES). We use the concept of isometrics to show that it is theoretically possible to build a system based on NTV components that is more energy efficient than a state-of-the-art high-end Xeon processor. In our evaluation, we consider the performance penalty of unreliability. We show that a system using unreliable NTV components can provide better energy to solution (ETS) for performance penalty, due to unreliability between 7% and 129% for a fault tolerant version of the CG algorithm and between 178% and 359% of the GMRES algorithm, compared to execution with an off-the-shelf server at nominal operating points.

In Chapter 4, we show a programming model based on OpenMP 4.0 tasks that allows the programmer to express approximation in task-based parallel applications and the detailed implementation of a runtime system that implements the semantics of the programming model. We introduce the concept of task significance, which describes the contribution of a task to the quality of the result of the algorithm. Significance describes the semantics of approximation systematically and allows the runtime system to optimise the execution by enabling acceptable, according to the programmer, trade-offs between accuracy and energy efficiency. Moreover, we present a framework that optimises approximate execution based on application profiles and a runtime-defined energy budget. We compare our framework to *loop perforation*, a well-known approximation technique, for many selected benchmarks. We show that our framework can achieve similar energy savings to loop perforation. However, we also achieve a graceful degradation of the quality, depending on the enforced level of approximation, a feature that loop perforation cannot achieve due to the lack of information regarding the approximation characteristics of the application.

In Chapter 5, we study the potential for energy savings by relaxing the requirements for refreshing the DRAM memory. Requirements for refreshing the DRAM of devices are often pessimistic and are predicted to be a roadblock for the next generation, higher density devices. We design and implement a system architecture that can reliably operate on top of DRAM devices that are refreshed less frequently than nominal or are even not refreshed at all. From the point of view of software, we identify a novel property, *refresh-by-access* that allows us to minimise the errors occurring during the lifetime of an application because of the relaxed refresh rate. We design a scheduling policy for task-based applications on top of the *refreshby-access* property that manages to reduce the number of DRAM errors observed by applications up to an order of magnitude. Our policy enables additional energy savings since it doubles the amount of data we can store unreliably for a given level or user-defined quality of output.

Finally, Chapter 6 concludes the thesis. We discuss the potential and prerequisites of approximate computing to emerge as a useful computing paradigm. We also discuss potential future work.

## Chapter 2

## Background

### 2.1 Near Threshold Voltage Computing

Traditionally, voltage scaling has been the most prominent means of reducing the power consumption of CPUs. Dennard scaling allowed manufacturers to reduce the supply voltage of chips and provide abundance of computational power, remaining within the available power budget. Moreover, when the power-wall started becoming a visible obstacle, vendors implemented mechanisms for dynamic voltage and frequency scaling (DVFS). These mechanisms were the building blocks of several techniques and tools for system administrators and software developers to reduce the power consumption of their systems without sacrificing significant performance [16, 29, 43, 50, 62, 69, 92, 93].

The CMOS transistors can operate, even using supply voltage  $V_{dd}$  below the threshold voltage  $V_{th}$ , with a theoretical minimum being determined as early as 1972 [84]. However, reducing  $V_{dd}$  does not come without a penalty. To avoid timing errors within the CMOS circuit, the operating frequency needs to scale proportionally to  $V_{dd}$ , which diminishes performance. However, because power consumption depends quadratically on voltage, scaling down  $V_{dd}$  while in the super- $V_{th}$  region ( $V_{dd} > V_{th}$ ) saves energy. When moving in the sub-threshold region ( $V_{dd} < V_{th}$ ), leakage energy increases exponentially with  $V_{dd}$ . The leakage energy eventually dominates, and a sweet spot for energy consumption forms (Figure 2.1).

Scaling  $V_{dd}$  from the super- $V_{th}$  region to the NTV region ( $V_{dd} \approx V_{th}$ ) yields an energy reduction of 10× with a performance penalty of the same order of magnitude.

In contrast, further scaling  $V_{dd}$  towards the sub- $V_{th}$  region and the point of minimum energy consumption provides only an additional  $2\times$  improvement in energy efficiency with a significant increase of performance degradation of an additional  $50 - 100 \times$ . Thus, several researchers [19, 54] have proposed that operation in the NTV region is a good trade-off between energy efficiency of the CMOS chip and performance degradation.

Fig. 2.1 Energy and delay in different supply voltage operating regions [19]

The requirement to scale the operating frequency of CMOS-based chips proportionally to the voltage scaling stems from the need to produce robust chips. Voltage scaling increases the delays of CMOS circuits, so without equivalent scaling of the frequency, timing errors will occur within the circuits, harming their correct operation. Moreover, decreased  $V_{dd}$  is responsible for increased failure probability of SRAM memory cells, a 5× increase of bitcell failure rate when operating at near- $V_{th}$  region according to [19]. To make things worse, reliability issues are further exacerbated due to increased process variation [19, 42, 64, 78] when operating at the sub- $V_{th}$  region. Figure 2.2 shows a  $\pm 2 \times$  frequency variation of a chip operating when operating in the near- $V_{th}$  region as opposed to a  $\pm 18\%$  at the super- $V_{th}$  region. Moreover, chips operating in the near- $V_{th}$  region are increasingly sensitive to temperature variations, which hinders their robustness.

Fig. 2.2 Modeling and measurements of variation [42]

The attractiveness of NTVC has given rise to a significant amount of research to address the challenges that NTVC presents. [19, 54] have established that operating in NTV presents a nice trade-off between energy efficiency and performance loss. [54] proposed yielding some of the energy savings of the sub- $V_{th}$  region to gain back some of the performance, and simultaneously, they utilised a new family of logic circuits to further increase energy savings. [19, 41, 42, 64] suggested that the lost performance due to frequency reduction in NTVC will be recovered by manycore architectures. They proposed using group silicon islands, and depending on the variation, they presented and applied different operating frequencies, instead of applying a worst-case scenario universal frequency across the die. [19, 40, 78] also tried to apply circuit-level optimisations to reduce the variability for chips operating in the near- $V_{th}$  region, while [12] examined various SRAM designs considering the process variation under NTVC to increase the yield of SRAM-based chips. The common ground of this research line is that they tried to optimise chip designs for NTVC to cope with the parametric variations and avoid errors.

On the other hand, over the past couple of decades, there have been researchers that have attempted to understand how errors at the circuits reflect at the microarchitectural level. For example, [72] studied the effect of errors from the perspective of individual hardware units within microprocessors, nonetheless, without examining their consequences for the software. Moreover, [15, 45] proposed allowing errors to occur in selected hardware units instead of struggling to harden microprocessors against errors, using pessimistic, worst-case scenario guard bands and fault-tolerance mechanisms within the microarchitecture. Their proposal is based on the observation that there are applications that can tolerate these errors without compromising much of their output quality. They focus on the so-called recognition, mining, and synthesis (RMS) applications that present algorithmic and cognitive resilience. Algorithmic resilience stems from the fact that imprecision in their computations does not significantly affect the result. Cognitive resilience relates to the fact that imprecision at the algorithm's result is acceptable as long as this is acceptable for human users.

Therefore, we are presented a novel and interesting trade-off, one of reliability versus energy efficiency and performance. To build robust hardware, we need to forsake potential for additional energy savings and performance improvements. For example, we retain the  $V_{dd}$  and high frequency of chips to avoid issues with process variation and timing errors. Alternatively, we could try to design systems that relax the requirement for reliability in a controlled way to allow energy and performance optimisation opportunities.

In this thesis, we propose a methodology based on isometrics for evaluating the viability of NTVC as an efficient computing paradigm. We assume an architecture that exposes the software layer to faults occurring at the microarchitecture level and consider the effect of these errors on the execution time of the applications running on the unreliable platform. In our study, we focus on iterative solvers in which errors might slow convergence, but our methodology can be extended to applications where the overhead of unreliability can occur from other sources as well (e.g., checkpointing and restarting).

We introduce isometrics[82] as a framework for comparing two platforms regarding their energy efficiency. We use a low-power ARM Cortex-A7 processor as an emulation of an NTV processor. Cortex-A7 features very low power consumption and a very simple in-order pipeline. This design is in line with the description of an NTVC single core in the literature [40], where advanced microarchitecture features are sacrificed for simplicity and stability against process variation. We assume a manycore architecture built of many such cores and compare it against a more powerful ARM Cortex-A15 processor and a high-end Xeon processor. We extend the concept of isometrics to account for the performance overhead that is a consequence for using unreliability.

# 2.2 Approximate Computing

Approximate computing is the system design and programming paradigm that can perform a computation in an imprecise way, if the quality of the result of the computation is acceptable by the final user of the system or the application. The approximation can originate at the hardware level, where some of the hardware units operate in an unreliable way, or at the software level where programmers define parts of the application that will use a less accurate algorithm to perform a task.

Approximation is inherent in many applications (e.g., probabilistic algorithms or algorithms that produce a result in which the quality depends on the perception of the user of the algorithm). For example, video decoding applications are required to produce a fixed number of frames per second depending on the quality requirements of the decoded video. Even if the system can provide enough throughput to produce a higher frame rate (better quality) it is acceptable that the decoder does not compute the extra frames to save resources (e.g., power consumption in embedded devices). Moreover, there are algorithms that present fault-tolerance properties that allow them to produce acceptable results even in the presence of errors. For example, iterative solvers repeatedly improve the accuracy of the output across iterations; thus, the effect of an error can be mitigated by subsequent iterations of the algorithm.

These observations have led to the advent of research that studies fault-tolerant and approximation properties of algorithms that enable the use of approximate frameworks. These frameworks are based either in the relaxed reliability of the hardware or the explicit substitution of certain computations with equivalent code blocks that perform the same task semantically, only with reduced accuracy. In both cases, the goal is to reduce resource utilisation, that being power consumption or CPU time. As a result, research regarding approximate computing can be separated into two categories:

- 1. Application-based fault tolerance that studies the effects of errors on applications and methods to minimise those and

- Approximate computing frameworks that endeavours to create programming models that allow programmers to develop approximate applications and runtime systems that manage the approximation-related information provided by the programmers to optimise execution.

### 2.2.1 Application-based Fault Tolerance

Application fault tolerance has been of interest for researchers and engineers for decades. Computing systems of any scale, from embedded devices to the highest ranked supercomputers, presents hardware failures despite the efforts of system designers to protect them from those using advanced error protection mechanisms within the hardware (e.g., error detection and correction codes, high guard bands in voltage and frequency, high refresh rate in DRAM memories, etc.). Thus, researchers of software-level error mitigation techniques have proposed methods that primarily rely on periodically checkpointing the state of applications and restarting from the latest saved state when an error has been detected [30]. Other methods [21] replicate the state of the algorithm to be able to detect errors, such as silent data corruption. [53] proposed more advanced replication schemes that enable both detection and recovery from such errors.

Apart from system-level methods for software resilience, there are solutions [1, 13, 20, 28, 57, 61, 76] that investigate algorithmic properties that we can presume upon to increase the resilience of the algorithm. This body of work can be exploited to enable the adoption of a system design paradigm that allows increased error probability in selected hardware components. For example, [28, 76] made use of certain algorithmic properties of two iterative solvers, GMRES and CG, to enable selective reliability. The algorithms are split in two parts, one that is allowed to run on hardware with relaxed reliability and a second one that always runs reliably. Even if an error occurs during the execution of the former, it is guaranteed that,

once the latter part is executed reliably, it will bring the algorithm back on track for convergence. However important, this method makes no assumption regarding the effect of the error on the convergence rate of the algorithms (i.e., the algorithm will converge, albeit, it might take a significantly increased number of iterations to do so, negating any energy gains due to operating in NTVC.

The ABFT presents solutions that are inherently application-specific and applied in an ad-hoc manner. For approximate computing to become a useful programming paradigm, there is the need for a systematic method of expressing possibilities for approximation during the implementation of an algorithm.

In this thesis, we design a programming model and runtime system that provides the required abstractions for the programmer to express approximation semantics for the developed algorithm. We opt for an OpenMP-like task parallel programming model because: a) parallelism is inevitable when performance is required. The NTVC system designs suggest that performance loss due to reduced frequency will be regained by massively parallel systems, and b) tasks present an intuitive abstraction level for describing approximation. A task is a well-defined block of computation to which the programmer can attribute approximation properties, such as *this task is a good/bad candidate for approximation*. In this way, we can decouple *what* is a candidate for the approximation from *how* it will be approximated.

We introduce the property of *task significance*, which, in our context, describes how much a task contributes to the quality of the results. Consequently, a significant task should always run accurately, whereas a non-significant or less-significant task is a candidate for approximation. Finally, the level of approximation is defined by user-defined constraints, which include the level of accuracy required from the computation and the available energy budget. We call this programming paradigm *significance-driven computing*.

# 2.2.2 Parallel Approximation Frameworks

Quickstep [56] is a tool that approximately parallelises sequential programs. The parallelised programs are subjected to statistical accuracy tests for correctness. Quickstep tolerates races that occur after removing synchronisation operations that would otherwise be necessary to preserve the semantics of the sequential program. Quickstep thus exposes additional parallelisation and optimisation opportunities via approximating the data and control dependencies in a program. On the other hand, Quickstep does not enable algorithmic and application-specific approximation, which is the focus of our work, and does not include energy-aware optimisations in the runtime system.

Variability-aware OpenMP [68] and variation tolerant OpenMP [67] are sets of OpenMP extensions that enable a programmer to specify blocks of code that can be computed approximately. The programmer may also specify error tolerance in terms of the number of most significant bits in a variable that are guaranteed to be correct. We follow a different scheme that allows approximate –in our context, not significant– tasks to be selectively dropped from execution and dynamic error checks to detect and recover from errors via selective task restarting. Variability-aware OpenMP applies approximation only to specific floating-point unit (FPU) operations, which execute on specialised FPUs with configurable accuracy. Our framework applies selective approximation at the granularity of tasks, using the significance abstraction. Our programming and execution model thus provides additional flexibility to drop or approximate code, while preserving output quality. Furthermore, our framework does not require specialised hardware support and runs on commodity systems.

# 2.2.3 Other Approximation Frameworks

Several frameworks for approximate computing discard parts of code at runtime, while asserting that the quality of the result complies with the quality criteria provided by the programmer. Green [4] is an application programming interface (API) for loop-level and function approximation. Loops are approximated with a reduction of the loop trip count. Functions are approximated with multi-versioning. The API includes calibration functions that build application-specific quality of service models for the outputs of the approximated blocks of code as well as recalibration functions for correcting unacceptable errors that may be incurred due to approximation. Sloan et al. [81] provided guidelines for manual control of approximate computation and error checking in software. These frameworks delegate the control of approximate code execution to the programmer. We explore an alternative approach where the programmer uses a higher level of abstraction for approximation, namely, computa-

tional significance, while the system software translates this abstraction into energyand performance-efficient approximate execution.

Loop perforation [79] is a compiler technique that classifies loop iterations as critical and non-critical. The latter can be dropped, as long as the results of the loop are acceptable from a quality standpoint. Input sampling and code versioning [97] also use the compiler to selectively discard inputs to functions and substitute accurate function implementations with approximate ones. Similar to loop perforation and code versioning, our framework benefits from task dropping and the execution of approximate versions of tasks. However, we follow a different approach whereby these optimisations are driven from user input on the relative significance of code blocks and are used selectively in the runtime system to meet user-defined quality criteria for energy saving and performance gain. While these approaches demonstrate aggressive performance optimisation due to approximation, they do not consider parallelism in execution. Furthermore, these techniques operate at a granularity different from parallel tasks or specific runtime energy optimisation opportunities, which are exposed through approximation.

Several software and hardware schemes for approximate computing follow a domain-specific approach. ApproxIt [96] is a framework for approximate iterative methods, based on a lightweight quality control mechanism. Unlike our task-based approach, ApproxIt uses coarse-grain approximation at a minimum granularity of one solver iteration. Gschwandtner et al. used a similar iterative approach to execute error-tolerant solvers on processors that operate with NTVC and reduce energy consumption by replacing cores operating at nominal voltage with NTVC cores [24]. Schmoll et al. [77] presented algorithmic and static analysis techniques to detect variables that must be computed reliably and variables that can be computed approximately in an H.264 video decoder. Although we follow a domain-agnostic approach in our approximate computing framework, we provide sufficient abstractions for implementing the application-specific approximation methods.