## Analog/Digital Hybrid Delay-Locked-Loop for K/Ka Band Satellite **Retrodirective Arrays**

Ding, Y., Buchanan, N. B., Fusco, V. F., Baggen, R., & Martínez-Vázquez, M. (2018). Analog/Digital Hybrid Delay-Locked-Loop for K/Ka Band Satellite Retrodirective Arrays. IEEE Transactions on Microwave Theory and Techniques, 66(7), 3323-3331. DOI: 10.1109/TMTT.2018.2829714

#### Published in:

IEEE Transactions on Microwave Theory and Techniques

**Document Version:** Peer reviewed version

### Queen's University Belfast - Research Portal:

Link to publication record in Queen's University Belfast Research Portal

Publisher rights © 2018 IEEE. This work is made available online in accordance with the publisher's policies. Please refer to any applicable terms of use of the publisher.

#### General rights

Copyright for the publications made accessible via the Queen's University Belfast Research Portal is retained by the author(s) and / or other copyright owners and it is a condition of accessing these publications that users recognise and abide by the legal requirements associated with these rights.

#### Take down policy

The Research Portal is Queen's institutional repository that provides access to Queen's research output. Every effort has been made to ensure that content in the Research Portal does not infringe any person's rights, or applicable UK laws. If you discover content in the Research Portal that you believe breaches copyright or violates any law, please contact openaccess@qub.ac.uk.

# Analog/Digital Hybrid Delay-Locked-Loop for K/Ka Band Satellite Retrodirective Arrays

Yuan Ding, Neil Buchanan, Vincent Fusco, Fellow, IEEE, Rens Baggen, Marta Martinez-Vazquez, Fellow, IEEE, Maarten van der Vorst

Abstract—An analog/digital hybrid delay-locked-loop (DLL) phase conjugator (PC) for use in retrodirective array (RDA) applications is proposed, implemented and measured. Compared with previous phase-locked-loop (PLL) PC solutions, the proposed DLL PC has a number of unique features which make it superior to previous solutions in many applications. These features include 1) the ability to hold the phases of conjugated outputs even when input pilots disappear; 2) the ability to track the changing rate of phases of input pilots even when the pilot signals with dynamic phases disappear for a short period of time, i.e., the implemented RDAs can constantly track a moving target for re-transmission even when the incoming pilots are not available due to deep channel fading or time division duplex (TDD) operation; 3) the DLL PC can be flexibly configured as voltage controlled phase shifters for use in traditional phased beam-steering arrays; 4) the DLL PC can indicate direction of arrival (DOA) of incoming signals without recourse to any baseband algorithms; 5) the DLL PC is unconditionally stable. The operation of the DLL PC is articulated in this paper, prototypes are built and their performance and functions are tested. In addition, a K/Ka band RDA demonstrator for satellite communications (SATCOM), based on the proposed DLL PC architecture, is implemented and measured, validating the 'retro-direct' functionality over a wide view angle. To our best knowledge, this is the first time that a DLL has been used for PC, and it is the first time that a K/Ka band RDA based on this technology has been experimentally demonstrated.

*Index Terms*—Delay-locked-loop (DLL), K/Ka band, phase conjugator, retrodirective array (RDA), satellite communications (SATCOM).

#### I. INTRODUCTION

A RETRODIRECTIVE array (RDA) has the capability to re-transmit a signal back along the spatial direction(s)

Manuscript received Sep. 26, 2017. This work was sponsored by the European Space Agency Project "Retrodirective Antenna, Artes 5.1, 7C.014".

Yuan Ding is with the Institute of Sensors, Signals and Systems (ISSS), Heriot-Watt University, Edinburgh, United Kingdom, EH14 4AS (phone: +44(0)1314513029; e-mail: yuan.ding@hw.ac.uk)

Neil Buchanan and Vincent Fusco are with the Institute of Electronics, Communications and Information Technology (ECIT), Queen's University of Belfast, Belfast, United Kingdom, BT3 9DT (e-mail: n.buchanan@ecit.qub.ac.uk; v.fusco@ecit.qub.ac.uk).

Rens Baggen and Marta Martinez- Vazquez are with IMST, Carl-Friedrich-Gauss Str.2, D-47475 Kamp-Lintfort, Germany (e-mail: baggen@imst.de).

Maarten van der Vorst is with the European Space Agency, Keplerlaan 1, 2201 AZ Noordwijk, The Netherlands (e-mail: Maarten.van.der.Vorst@esa.int) along which the array was illuminated by the incoming signals without the need for a-priori knowledge of their points of origin [1], [2]. This automatic tracking characteristic makes RDA technology useful in many applications, including long-range radio frequency identification (RFID) [3], microwave power transmission [4], physical-layer wireless spatial encryption [5]–[7], and mobile satellite communications (SATCOM) [8], [9], etc.

There are a variety of RDA architectures. These largely fall into two categories, i.e., passive and active. Passive solutions normally refer to 'Van Atta' type structures [10], which retrodirect wavefronts using symmetrical delay lines positioned between array radiating elements. While active solutions usually involve phase conjugating circuits [11]. In this category 'Pon'-type phase conjugator (PC) structures [12] have been extensively investigated. These mixer-based arrangements [12]–[15] make the RDA more flexible, in terms of its physical layout [16], receive and re-transmit frequency offsets [17], and re-transmitted signal capability [18]. However, inherent weaknesses associated with this 'Pon'-type approach include low and non-flat mixer conversion gain, undesired mixing frequency leakage components, and lack of receiver array factor gain. These negative attributes have hindered RDA deployment in the field.

These problems have recently been largely solved by introducing phase-locked-loop (PLL) based PCs [19]–[24], which have the capability of providing low spurious phase conjugated signals at constant magnitude. In addition, they have the ability to provide array factor gains on both transmit and receive using simple intermediate frequency (IF) summing circuits.

However, the PLL PC approach is not suitable in some important applications, including the scenarios 1) where the receive signals or pilot tones are not constantly available, which for example may be the result of deep channel fading or time division duplex (TDD) operation, such as are associated with SATCOM systems of the type in [25]; 2) where the information about directions of arrival (DOAs) of incoming pilots are required; 3) where the flexibility of reconfiguring PC units into phase shifters for classical phased arrays is an additional requirement.

Respectively the above weaknesses associated with the PLL PCs are rooted in the fact that the output phase adjustments are achieved by altering the frequency of local oscillators (LOs) during the loop locking process. This leads to 1) frequency asynchronization when the incoming pilots, which act as the PLL frequency references, are unavailable; 2) the identical locking status, i.e., frequency synchronization, for different DOAs; 3) no chance of configuring frequency asynchronized PLLs into phase shifters. Naturally if only the phases, rather than the frequencies, of LOs in PLL PC are used to adjust the loop states, the above mentioned inherent PLL PC issues can be sufficiently addressed, and the resulting 'PLLs' are essentially turned into delay-locked-loops (DLLs) [26]. In addition, the proposed DLL based PC architecture can provide significant extra useful features and functionalities when a light touch digital module is utilized.

This paper is organized as follows; In Section II the architecture of the proposed DLL PC is presented, and its unique features are summarized. Detailed DLL PC design considerations are elaborated in Section III. The measured DLL PC performance and the demonstration of its functionalities are provided in Section IV at around 2.2 GHz due to the availability of the off-the-shelf components, while also facilitating performance comparison with previously reported PLL PC solutions. In Section V, an RDA using the constructed DLL PCs deployed for K/Ka band SATCOM applications is constructed. The experiment, for the first time, validates the 'retro-direct' functionality in K/Ka band in a full-duplex fashion. Conclusions on the work presented are finally drawn in Section VI.

#### II. DELAY-LOCKED-LOOP PHASE CONJUGATOR

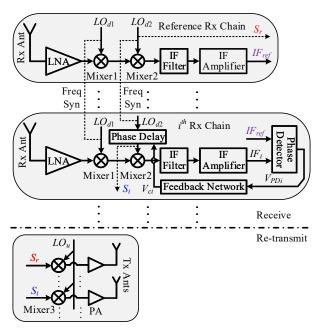

Fig. 1. Proposed DLL PC enabled RDA architecture.

The architecture of the proposed DLL PC enabled RDA is given in Fig. 1. It should be noted that although full digital RDA solutions using FPGA technology can be versatile, they lack real-time response due to their required digital signal processing power and computational speed restrictions [27]. In addition, the full digital version is also power hungry, especially when transmission data rates are high, e.g., at a data rate of 20 Mbit/s, digital and analog versions require 600 mW and 89 mW per element, respectively [27]. In the analog/digital hybrid DLL solution presented here only low-power low-frequency micro-controllers with simple computational capabilities are necessary. They are used in the feedback network shown in Fig. 1. The associated design details are presented in Section III.

In Fig. 1 only the reference and the  $i^{th}$  (i = 2, ..., N) chains are depicted for an N-element RDA. Unlike the PLL PC solutions where LOs in each receive chain used for driving down-conversion mixers, i.e., Mixer1 and Mixer2, are derived from their own frequency references, thereby resulting in phase-unlocked LOs in open loop states, the corresponding LO pairs in DLL PCs share a common frequency reference, i.e.,  $LO_{d1}$  (and  $LO_{d2}$ ), and consequently every receive chain in the array is automatically frequency synchronized. Since LO frequencies are fixed, in order to lock the loop in the  $i^{th}$  receive chain a controllable phase delay, which can be placed along either the first or the second down-conversion LO paths, is required. In Fig. 1 and the following discussions and in the experimental work presented in this paper this variable phase delay is inserted to alter the phase of the  $LO_{d2}$  at the second stage frequency down-conversion.

To facilitate formulation and further discussion, notations of frequencies and phases of various signals involved in the DLL PCs are listed in Table I, from which it is obvious that  $f_{in\_ref} = f_{in\_i} = f_{in\_f} f_{d1\_ref} = f_{d1\_i} = f_{d1}, f_{d2\_ref} = f_{d2\_i} = f_{d2}, f_{u\_ref} = f_{u\_i} = f_{u\_i}$  and  $f_{IF\_ref} = f_{IF\_i} = f_{IF\_}$ .

|                                                  |                                                             | Frequency               | Phase                           |

|--------------------------------------------------|-------------------------------------------------------------|-------------------------|---------------------------------|

| Received incoming pilots                         | The reference chain<br>The <i>i</i> <sup>th</sup> chain     | fin_ref<br>fin_i        | $\phi_{in\_ref} \ \phi_{in\_i}$ |

| $LO_{d1}$                                        | The reference chain<br>The <i>i</i> <sup>th</sup> chain     | fd1_ref<br>fd1_i        | $\phi_{d1\_ref} \ \phi_{d1\_i}$ |

| <i>LO</i> <sub>d2</sub> at input ports of Mixer2 | The reference chain<br>The <i>i</i> <sup>th</sup> chain     | fd2_ref<br>fd2_i        | $\phi_{d2\_ref} \ \phi_{d2\_i}$ |

| The IF signals                                   | The reference chain $IF_{ref}$<br>The $i^{th}$ chain $IF_i$ | f_IF_ref<br>f_IF_i      | $\phi_{IF\_ref} \ \phi_{IF\_i}$ |

| LOu                                              | The reference chain<br>The <i>i</i> <sup>th</sup> chain     | $f_{u\_ref} \ f_{u\_i}$ | $\phi_{u\_ref} \ \phi_{u\_i}$   |

TABLE I. NOTATIONS OF SIGNALS IN DLL PCS

The system should be configured as in (1),

$$f_{IF} = f_{d2} - (f_{d1} - f_{in}), \tag{1}$$

so that

$$\phi_{IF_{\text{ref},i\}}} = \phi_{d2_{\text{ref},i\}}} - (\phi_{d1_{\text{ref},i\}}} - \phi_{in_{\text{ref},i\}}}). \tag{2}$$

From (2) we can obtain

$$(\phi_{d2\_i}-\phi_{d2\_ref}) = -(\phi_{in\_i}-\phi_{in\_ref}) + (\phi_{d1\_i}-\phi_{d1\_ref}) + (\phi_{IF\_i}-\phi_{IF\_ref}).$$

(3)

For the system in Fig. 1 the phase differences between  $LO_{d1}$  in the *i*<sup>th</sup> and the reference receive chains, i.e., the second term on the right-hand side in (3), are fixed. When the DLL in the *i*<sup>th</sup> receive chain is locked, as will be discussed in Section III, the phase difference of two inputs of the phase detector, i.e., the third term on the right-hand side in (3), is constant. As a result, we can rewrite (3) as

$$(\phi_{d2\_i} - \phi_{d2\_ref}) = -(\phi_{in\_i} - \phi_{in\_ref}) + \Delta_i, \tag{4}$$

where  $\Delta_i$  is a constant for each *i*.

From (4) it is noticed that the phase  $\phi_{d2_i}$  of the *i*<sup>th</sup> DLL output  $S_i$  equals the conjugated phase of the incoming pilot, i.e.,  $-\phi_{in_i}$ , when using their counterparts in the reference chain as references, and when the constant phase  $\Delta_i = 0$ . The method used to calibrate  $\Delta_i$  out is discussed in Section III. After the phase conjugated  $S_i$  is obtained this can be frequency up-converted to re-transmit, in retro-directive fashion, signals back towards the distant source where the pilot is originated.

The introduction of the DLL PC solution endows the constructed RDAs with a number of desirable capabilities that are not possible with previous PLL PC architectures. These are summarized as follows;

- The conjugated outputs of DLLs can be held even when the incoming pilots, assuming static phases, disappear. This enables the constructed RDA to continue pointing towards the pilot source direction even when the pilot signals are not available, e.g., due to deep channel fading and/or TDD operation. This is not possible with PLL solutions since when the receive pilots are lost, there is no chance to synchronize the frequencies of LOs in each receive branch as feedback-control DC voltages are lost. Therefore, the re-transmitted directions become arbitrary in terms of both modulation frequencies and spatial beam pointing directions.

- 2) The conjugated outputs of DLLs can keep tracking the phases of incoming pilots by assuming constant phase rate of change, over a short period when the pilot signals disappear. This endows the constructed RDA the ability of predictively tracking a moving target even when the acquisition pilot radiated from the target disappears, thereby avoiding the repeated phase acquisition processes associated with fading channels and/or TDD systems.

- 3) The DLL PCs can be configured as variable phase shifters by simply opening the feedback loop in Fig. 1. In this way, the RDA operates as a traditional phased beam-steering array.

- 4) Unlike PLL solutions, when the DLL PC is locked, the feedback DC voltages,  $V_{ci}$  in Fig. 1, used to set required phase delays can be exploited as an indicator of the incoming signal DOA.

- 5) In order to compensate a fixed phase error, only a first order DLL is required, which is unconditionally stable, compared to a second order conditionally stable PLL required to achieve the same purpose [26].

#### **III. DESIGN CONSIDERATIONS**

Before presenting the DLL PC implementation and the RDA experiment in Sections IV and V, some important design

considerations need to be elaborated in regard to RDA design for SATCOM application.

#### A. Receive and Re-transmit Antenna Arrays

In order to broaden the field of view of an RDA, the chosen antennas in both the receive and re-transmit arrays need to have active element patterns with wide beams. Usually microstrip patch antennas are adopted. For some particular applications, such as SATCOM [9], [28], circular polarization is preferred. Receive and re-transmit arrays can share a same antenna aperture, e.g., when receiving and re-transmitting at the same frequency a duplexer is added for system to work in TDD mode, or when frequency-division duplex (FDD) is adopted multi-band or wideband antenna elements are required in the arrays. In FDD mode the conjugated phases need to be scaled according to the receive and re-transmit frequency ratios, as studied in [29]–[31]. Alternatively, receive and re-transmit can use separate antenna apertures with conjugated phases adjusted according to the electric distance between array elements.

#### B. IF Filter and IF Amplifier

As seen in Fig. 1, an IF filter is added, whose bandwidth is normally around hundreds of Hz, in order to improve receive sensitivity levels associated with SATCOM applications, typically below -120 dBm. Following the IF filter an IF amplifier with high gain is used, in order to drive the phase detector above its threshold voltage at very low received power levels.

#### C. Phase Detector

There are various types of phase detectors that can be used for the proposed DLL PCs in Fig. 1. Among these the exclusive OR type, which operates effectively with both sinusoid and square wave inputs, corresponding to low and high (saturation occurs after IF amplifier) receive power respectively, is preferred. This amplitude independent characteristic greatly enhances the dynamic range of the receiver. This property is validated in the experiment in the next section.

#### D. Variable Phase Delay

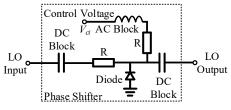

A controllable phase delay covering 360° is required to alter the phase  $\phi_{d2_i}$  of the  $LO_{d2}$  used for the Mixer2, seen in Fig. 1. This phase delay can be directly implemented at the LO frequency  $f_{d2}$ , or be implemented at a lower frequency, then multiplied up to the required  $f_{d2}$ . In our experiment in Sections IV and V, we choose the latter approach, because 1) a small fraction of phase shifts could span 360° after frequency

Fig. 2. Voltage-controlled phase shifter at low frequency.

multiplication, so that the most linear region of the variable phase shifter could be selected, 2) the magnitude of the  $LO_{d2}$  can be kept constant irrespective of the phase delay. The variable phase shifter at a low frequency, 10 MHz chosen in our experiment, is constructed using the simple circuitry shown in Fig. 2.

#### E. Feedback Network

The feedback network is the key module that endows the DLL PCs new and useful functionalities, i.e., those described in 1) to 4) in Section II.

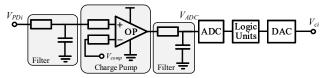

Fig. 3. Schematic of feedback network implementation.

This feedback network used in our design is an analog/digital hybrid circuitry, depicted in Fig. 3. A simple first order loop filter, sufficient to correct phase errors in the DLL, is placed after each phase detector. This is followed by an operational amplifier (OP-Amp) voltage comparator that functions as a charge pump. The reference voltage, V<sub>comp</sub>, seen in Fig. 3, determines the constant phase differences between  $IF_i$  and  $IF_{ref}$ , i.e.,  $\phi_{IF} = -\phi_{IF}$ , when the loop is locked. It can be adjusted to make  $\Delta_i = 0$ , enabling phase conjugation as discussed in Section II. The provision of the  $V_{comp}$  provides a simple and effective approach for calibrating each receive chain. The filtered charge pump output is then sampled by a low frequency analog to digital converter (ADC) to allow basic logical operations in the digital domain. Finally, a digital to analog converter (DAC) transforms digital bits back into an analog DC voltage  $V_{ci}$ , which is fed back to set the phase delay of the  $LO_{d2}$  in the  $i^{th}$ receive chain.

The functionalities of the logic units are now described. Here only very basic logic operations are involved, and they can be readily fulfilled with a low-cost low-power digital micro-controller.

- 1) The array can be easily configured as a traditional phased beam-steering array by selecting from a pre-stored lookup table the digital bits sent to the DAC inputs to generate the DC voltages  $V_{ci}$  for required progressive phase delay distributions across the array. In this mode, the feedback loop is opened.

- 2) For RDA mode, the initial pilot signal phase acquisition is achieved as follows; Scan the input bits of the DAC from **a** to **b** while monitoring the input voltages  $V_{ADC}$  of the ADC. Digital bits **a** and **b** correspond to two values of  $V_{ci}$  that set two phase delays separated by 360°. Two possible locking points, where middle ranged ADC inputs  $V_{ADC}$  are detected, can then be identified. Either locking point can be used. However, this cannot change after selection. Different choices of the locking points result in the different  $V_{comp}$  that is tuned to eliminate  $\Delta_i$  in (4). A phase delay scanning range of greater than 360° may lead to more than two possible

locking points and should be avoided.

- For RDA mode, after successful initial phase acquisition, the digital modules perform the following two tasks;

- The two digital bits around the locking bit (corresponding to the locking point obtained in the acquisition stage) are repeatedly applied at the input of the DAC. If they lead to high (or low) and low (or high)  $V_{ADC}$ , respectively, at the input of the ADC, we know that the locking point is remaining constant. If both lead to either high or low  $V_{ADC}$ , we know the input bits of the DAC should be increased or decreased to re-gain the locking point. The new locking bit could be obtained with little effort because it lies not far from the previous locking bit. The changing patterns of the locking bits against time are recorded. It should be pointed out that the phase wrapping issue associated with DLLs can be readily solved with the help of the digital module, because with the availability of the look-up table mapping  $V_{ci}$  and phase delays the feedback network knows when and how the phases should be wrapped. As an additional benefit, the knowledge of  $V_{ci}$  can provide DOA information.

- The output  $V_{PDi}$  of the phase detector is repeatedly checked. This can be done using another ADC. When the  $V_{PDi}$  falls into a pre-determined small region, it indicates the pilot signal disappears. The choice of  $V_{comp}$  should be kept far away from this pre-determined region, which is measured and stored in advance, in order to avoid the confusion between the loop locking state and the state when the pilot disappears. Once the system notices the

#### Algorithm 1

#### **Phase Acquisition:**

Sweep input digital bits of DAC from a to b, until

- For the input bit c-1,  $V_{ADC}$  is low (or high)

- For the input bit  $\mathbf{c}$ ,  $V_{ADC}$  is middle ranged

- For the input bit  $\mathbf{c}+1$ ,  $V_{ADC}$  is high (or low)

- c is the locking bit, and go to **Phase Tracking**.

#### **Phase Tracking:**

Check locking bit:

- 1) *If*

- For the input bit c-1,  $V_{ADC}$  is low (or high)

- For the input bit **c**+1, *V*<sub>ADC</sub> is high (or low) Go to **1**)

- **2)** *Elseif* (For the input bit  $\mathbf{c}$ -1,  $V_{ADC}$  is high (or low) ) Assign  $\mathbf{c}$ +1 to  $\mathbf{c}$ ; Go to **1**);

- **3)** *Elseif* (For the input bit  $\mathbf{c}+1$ ,  $V_{ADC}$  is low (or high) ) Assign  $\mathbf{c}-1$  to  $\mathbf{c}$ ; Go to  $\mathbf{1}$ );

- Store the previous locking bits versus time.

#### **Pilot Signal Detection:**

- Repeatedly check the existence of the pilot signal:

- *If* (Pilot signal is unavailable)

- Assign **c** according to the patterns of previously stored locking bits;

Elseif

Go to 1).

absence of the pilot signal, the DLL will open the loop and assign the input bits of the DAC according to the previously stored patterns of locking bits. So that the constructed RDA can automatically hold the re-transmission direction along the pilot source, or continuously steer the re-transmission beam to track the moving pilot source (when the pilot source is in motion before the pilot disappears) in the period when the pilot signal is not available.

The algorithm used for RDA mode operation, implemented using the digital modules, is now described in Algorithm 1.

In our prototype, we chose the micro-controller PSoC4 [32] from Cypress, because of its low power consumption, easy programming, and its integration of 12-bit multi-channel ADC, two current-type 7-bit DACs, two OP-Amps, and ample logic resources. In other words, it contains all the components that are needed for the feedback network shown in Fig. 3.

#### IV. DLL PC PROTOTYPES

Prototypes of the proposed DLL PCs were fabricated to evaluate their performance and validate their functionalities.

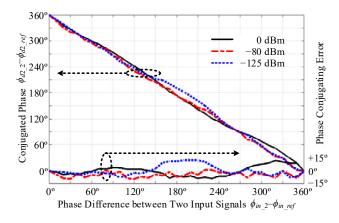

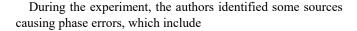

In order to assess performance, the entire receive chain, shown in Fig. 1, from low noise amplifier (LNA) to output  $S_i$  is required. For this purpose, a modular prototype with two entire receive chains was constructed. The inputs of the two chains were directly connected to two 10 MHz phase synchronized signal generators both generating 2.194 GHz signals. One chain was selected as reference, while the  $S_2$  (phase delayed  $LO_{d2}$ seen in Fig. 1) in the second DLL PC enabled receive chain was measured. The phases  $(\phi_{d2} \ _2 - \phi_{d2} \ _{ref})$  (after  $\Delta_2$  being calibrated out) against the phase differences between two input signals  $(\phi_{in 2} - \phi_{in ref})$  were measured and are depicted in Fig. 4 for various input signal power levels. It can be concluded from Fig. 4 that over a large dynamic range of 125 dB (from 0 dBm to -125 dBm) the phases of the input signals can be conjugated using the proposed DLL PC structure with worst case phase errors of less than 14°.

Fig. 4. Phase conjugation experimental results for various receive signal power levels.

- 1) the spurious and phase noise of the frequency synthesizer, i.e., ADF4360-1 used in the prototype, for  $LO_{d2}$  could generate low-magnitude IF signals at the frequency  $f_{IF}$  at the input ports of the phase detector, as the results of coupling and circuit non-linearity. The phases of these IF signals do not linearly dependent on the phases of  $S_r$  and  $S_i$ , affecting the correctness of the calibrated  $\Delta_i$  in (4), especially when the power of input pilot signals is low, and, hence, the conjugated phases. These resultant IF signals, with unpredictable magnitudes and phases, have different impacts on phase errors when the phase differences of input pilot signals vary. This phenomenon can be more severe when multiple DLL PCs operate closely in space, and this is an important factor that limits the sensitivity of the designed DLL PCs;

- 2) the resolution and speed of the DAC in the feedback network can affect the phase noise of  $LO_{d2}$ . Thus, through the same mechanism described above in 1), phase errors occur.

In order to reduce the phase errors and further enhance the DLL PCs' sensitivity down to -130 dBm, the authors plan to test a series of options, e.g., choosing frequency synthesizers with better spectrum purity and phase noise, redesigning circuit layout to reduce coupling, constructing phase shifters directly at  $f_{d2}$  without frequency synthesizers, and selecting high-speed high-resolution DACs with reasonable power consumption. Future results on performance improvement and system integration will be reported timely.

The feedback control voltage  $V_{c2}$  was also measured and is plotted in Fig. 5. Once the control voltage  $V_{c2}$ , and hence the associated phase difference, is obtained, the DOA  $\theta$  (measured from the array boresight) can be calculated through

$$\sin\theta = (\phi_{in \ 2} - \phi_{in \ ref}) \cdot d/k, \tag{5}$$

where k is the wave number in free space, and d is the antenna spacing. In Fig. 5 it can also be seen that the voltage can be automatically wrapped when the pre-defined boundaries, e.g., 0.7 V and 1.2 V (corresponding to the DAC input bits **a** and **b**) used in the above experiment, are reached, indicating

Fig. 5. Measured feedback DC voltage  $V_{c2}$  against phase differences  $(\phi_{in,2}-\phi_{in,ref})$  between two input signals for various input signal power levels.

|                                     | Components                                                                                                                                       | Notes                                                                                               |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Rx antenna array                    | IMST-designed 1-by-4 microstrip patch array                                                                                                      | See photograph in Fig. 6; LTCC technology;<br>Element spacing: 10.5 <i>mm</i> ; Polarization: RHCP. |  |

| Tx antenna array                    | IMST-designed 1-by-4 microstrip patch array                                                                                                      | See photograph in Fig. 6; LTCC technology;<br>Element spacing: 7 <i>mm</i> ; Polarization: LHCP.    |  |

| LNA                                 | CHA2092B                                                                                                                                         |                                                                                                     |  |

| Mixer1                              | НМС292                                                                                                                                           | Measured conversion gains at 20 GHz were around 12 to 14.5 dB @ $-15$ dBm input.                    |  |

| Mixer2                              | MAX2680                                                                                                                                          | Measured conversion gains at 2.2 GHz were around 7 dB $@-60$ dBm input.                             |  |

| Mixer3                              | НМС329                                                                                                                                           | Measured conversion gains at 29.75 GHz were around 8.5 to 13.5 dB $@$ -10 dBm input.                |  |

| PA after Mixer3                     | CHA2092B                                                                                                                                         |                                                                                                     |  |

| IF amplifier                        | Two LMH6646                                                                                                                                      |                                                                                                     |  |

| Phase detector                      | SL74HC4046                                                                                                                                       |                                                                                                     |  |

| Frequency synthesizer for $LO_{d2}$ | ADF4360-1                                                                                                                                        |                                                                                                     |  |

| Frequency setup                     | $f_{in} = 20 \text{ GHz}; f_{d1} = 22195.81 \text{ MHz}; f_{d2} = 2.2 \text{ GHz}; f_{u} = 31.7 \text{ GHz}^{a}; f_{Tx} = 29.5 \text{ GHz}^{b}.$ |                                                                                                     |  |

TABLE II. INFORMATION ABOUT IMPLEMENTED DLL PC ENABLED K/KA BAND RDA AND ITS FREQUENCY SETUP

*a.*  $f_u$  denotes the frequency of  $LO_u$  used for up-conversion before transmission. *b.*  $f_{Tx}$  denotes the frequency of signals fed into transmit antennas, here  $f_{Tx} = f_u - f_{dZ}$ .

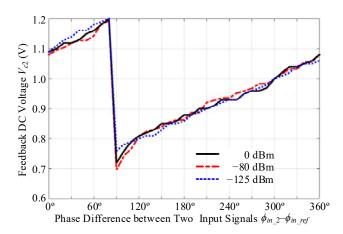

Fig. 6. Block diagram of DLL PC enabled K/Ka band RDA experiment setup.

continuous phase tracking ability unconstrained by the limited phase range of the phase delay circuitry.

Next, four integrated DLL boards targeting for K/Ka band SATCOM applications were designed and fabricated. For function demonstration purpose, one reference board and one DLL board were measured. Here the frequency of the input signal, which is the signal before the Mixer2 in Fig. 1, and the  $f_{d2}$  were set to be 2195.81 MHz and 2.2 GHz respectively, resulting in  $f_{IF} = 4.19$  MHz.

The video of the experiment can be accessed in [33]. In the video, it can be seen that

• The DLL works for both continuous wave (CW) and QPSK modulated (PN sequence) input signals;

- The DLL can hold the phases of the output signals when the input signals with static phases disappear. This confirms the claim 1) in Section II;

- The DLL can continuously track the phases of the input signals even when the input signals with changing phases disappear for a short period of time. This confirms the claim 2) in Section II.

#### V. DLL PC ENABLED K/KA BAND RDA

A fully functional K/Ka band RDA based on the proposed DLL PC was designed and assembled. We chose K/Ka band because RDA equipped ground terminals can provide great benefits for the fast-growing K/Ka band satellite broadband connections [28], e.g., RDA user transceivers on moving vehicles can automatically beamform towards the target satellites.

The detailed design information about the DLL PC enabled K/Ka band RDA is provided in Table II.

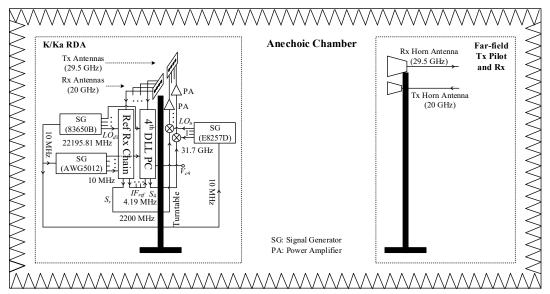

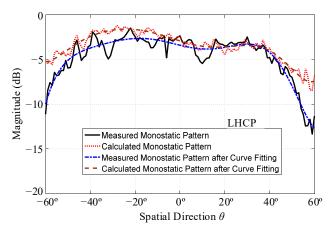

The block diagram and the photograph of the DLL PC enabled K/Ka band RDA experiment setup in an anechoic chamber are shown in Fig. 6 and Fig. 7, respectively. In Fig. 6, the DLL PC module has the same structure as that shown in Fig. 1, except for the  $LO_{d2}$  which is generated using the frequency synthesizer ADF4360-1 (sharing a common 10 MHz reference). The reference receive chain is similar to the DLL PC module, but without the feedback network and the phase Measured monostatic pattern of the RDA shifter. re-transmissions is given in Fig. 8. With repeated measurements and individual antenna test, we noticed that the ripples on the measured and calculated monostatic patterns were mainly caused by the unwanted radiation from coaxial cables connecting antenna elements and RF circuits. Thus, smoothed fitting curves are also provided in Fig. 8. This issue will be fixed in the future by integrating antennas and RF circuits on a single board.

Fig. 7. Photograph of DLL PC enabled K/Ka band RDA experiment setup.

In Fig. 8 it can be clearly seen that the implemented K/Ka band RDA was capable of retrodirecting the pilot source over a wide spatial range, i.e., from  $-50^{\circ}$  (or  $-55^{\circ}$ ) to  $40^{\circ}$  (or  $50^{\circ}$ ) for gain flatness of about 3 dB (or 5 dB). The calculated monostatic pattern, obtained using measured antenna active element patterns, also plotted in Fig. 8, has slightly higher gains when compared with its measured counterpart. This is mainly caused by the non-ideally calibrated  $\Delta_i$  in the monostatic pattern measurements, leading to beam pointing errors and reduced beamforming gains [34]. It is noted that when wider steering angles are required, other types of antenna elements with broader active element patterns and/or other array arrangements, e.g., curved arrays, can be considered.

Fig. 8. Comparison between the measured RDA monostatic pattern and calculated monostatic pattern. Receive at 20 GHz and re-transmit at 29.5 GHz.

#### VI. CONCLUSION

In this paper, we have proposed a new type of phase conjugating architecture based on an analogue/digital hybrid DLL. The proposed DLL PC solution has a number of useful features that are not available with the previously reported PC solutions. The prototypes of the DLL PCs, and its first ever K/Ka band RDA demonstrator, were successfully implemented and measured to assess their superior phase conjugation performance, e.g., the large input dynamic range of 125 dB and the input signal sensitivity down to as low as -125 dBm, and to validate their unique functionalities, such as holding or tracking the conjugated phases even when the incoming pilots are lost. The proposed analog/digital hybrid DLL PCs should find many applications where robust and flexibly reconfigurable RDA/phased array deployment are required.

#### ACKNOWLEDGMENT

The authors thank Mr. Kieran Rainey for the assistance on the K/Ka band RDA experiment.

#### REFERENCES

- V. Fusco and N. Buchanan, "Developments in retrodirective array technology," *IET Microw., Antennas Propag.*, vol. 7, no. 2, pp. 131–140, May 2013.

- [2] O. Malyuskin and V. Fusco, "Ultracompact retrodirective antenna arrays with superdirective radiation patterns," *IEEE Trans. Antennas Propag.*, vol. 64, no. 7, pp. 2923–2935, Jul. 2016.

- [3] P. Chan and V. Fusco, "Bi-static 5.8GHz RFID range enhancement using retrodirective techniques," in *Proc. 41st Eur. Microw. Conf. (EuMC)*, Oct. 2011, pp.976–979.

- [4] C. Rodenbeck, M. Li, and K. Chang, "A phased-array architecture for retrodirective microwave power transmission from the space solar power satellite," in *Proc. IEEE MTT-S Int. Microw. Symp. Digest*, Jun. 2004, vol. 3, pp. 1679–1682.

- [5] V. Fusco and N. Buchanan, "Retrodirective antenna spatial data protection," *IEEE Antennas Wireless Propag. Lett.*, vol. 8, pp. 490–493, Jun. 2009.

- [6] Y. Ding and V. Fusco, "A synthesis-free directional modulation transmitter using retrodirective array," *IEEE J. Sel. Topics Signal Process.*, vol. 11, no. 2, pp. 428–441, Mar. 2017.

- [7] Y. Ding, J. Zhang, and V. Fusco, "Retrodirective assisted secure wireless key establishment," *IEEE Trans. Commun.*, vol. 65, no. 1, pp. 320–334, Jan. 2017.

- [8] P. Brennan, "An experimental and theoretical study of self-phased arrays in mobile satellite communications," *IEEE Trans. Antennas Propag.*, vol.

37, no. 11, pp. 1370-1376, Nov. 1989.

- [9] N. Buchanan, V. Fusco, and M. Vorst, "SATCOM retrodirective Array," *IEEE Trans. Microw. Theory Tech.*, vol. 64, no. 5, pp. 1614–1621, May 2016.

- [10] Electromagnetic reflector, by L. C. Van Atta. (1959, Oct. 6). US Patent 2908002. [Online]. Available: http://www.google.co.uk/patents/ US2908002

- [11] L. Chen, Y. Guo, X. Shi, and T. Zhang, "Overview on the phase conjugation techniques of the retrodirective array," *Int. J. Antennas Propag.*, vol. 2010, pp. 1–10, Apr. 2010, article ID 564357.

- [12] C. Y. Pon, "Retrodirective array using the heterodyne technique," *IEEE Trans. Antenna Propag.*, vol. 12, no. 2, pp. 176–180, Mar. 1964.

[13] T. Brabetz, V. Fusco, and S. Karode, "Balanced subharmonic mixers for

- [13] T. Brabetz, V. Fusco, and S. Karode, "Balanced subharmonic mixers for retrodirective-array applications," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 3, pp. 465–469, Aug. 2002.

- [14] J. Park and T. Itoh, "A 60-GHz 4th subharmonic phase-conjugated retrodirective array," in *Proc. 34th Eur. Microw. Conf. (EuMC)*, Oct. 2004, pp. 1277–1280.

- [15] D. Goshi, K. Leong, and T. Itoh, "A retrodirective array with interference rejection capability," in *Proc. IEEE MTT-S Int. Microw. Symp. Digest*, Jun. 2005, pp. 395–398.

- [16] D. Ah Yo, W. Forsyth, and W. Shiroma, "A 360° retrodirective self-oscillating mixer array," in *Proc. IEEE MTT-S Int. Microw. Symp. Digest*, Jun. 2000, vol. 2, pp. 813–816.

- [17] N. Buchanan, T. Brabetz, and V. Fusco, "A 62/66 GHz frequency offset retrodirective array," in *Proc. IEEE MTT-S Int. Microw. Symp. Digest*, Jun. 2002, vol. 1, pp. 315–318.

- [18] K. Leong, Y. Wang, and T. Itoh, "A full duplex capable retrodirective array system for high-speed beam tracking and pointing applications," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 5, pp. 1479–1489, May 2004.

- [19] N. Buchanan and V. Fusco, "Triple mode PLL antenna array," in Proc. IEEE MTT-S Int. Microw. Symp. Digest, Jun. 2004, vol. 3, pp.1691–1694.

- [20] V. Fusco, C. Soo, and N. Buchanan, "Analysis and characterization of PLL-based retrodirective array," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 2, pp. 730–738, Feb. 2005.

- [21] N. Buchanan and V. Fusco, "Quadrant switching PLL phase conjugator for retrodirective antenna applications," in *Proc. IEEE MTT-S Int. Microw. Symp. Digest*, Jun. 2008, pp. 791–794.

- [22] V. Fusco and N. Buchanan, "High-performance IQ modulator-based phase conjugator for modular retrodirective antenna array implementation," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 10, pp. 2301–2306, Oct. 2009.

- [23] N. Buchanan, V. Fusco, and M. Vorst, "A high performance analogue retrodirective phase conjugation circuit with RX array factor combination ability," in *Proc. IEEE MTT-S Int. Microw. Symp. Digest*, Jun. 2011, pp. 1–4.

- [24] N. Buchanan, and V. Fusco, "Pilot tone reference-less phase conjugator for phase-modulated retrodirective antenna applications," *IEEE Antennas Wireless Propag. Lett.*, vol. 15, pp. 298–300, Feb. 2016.

- [25] Iridium Global Network. [Online]. Available: https://iridium.com/About/ IridiumGlobalNetwork.aspx

- [26] C. Yang, "Delay-locked loops—an overview," in *Phase-Locking in High-Performance Systems from Devices to Architectures*, B. Razavi, Ed. New York: Wiley/IEEE Press, pp. 13–22.

- [27] N. Buchanan, V. Fusco, M. Vorst, N. Williams, and C. Winter, "New retrodirective antenna techniques for mobile terminal applications," in *32nd Antenna Workshop, ESA/ESTEC*, Noordwijk, The Netherlands, Oct. 2010, pp. 1–4.

- [28] H. Zhou, M. Jong, and G. Lo, "Evolution of satellite communication antennas on mobile terminals," *Int. J. Antennas Propag.*, vol. 2015, Article ID 436250, 14 pages, 2015.

- [29] N. Buchanan, V. Fusco, and M. Vorst, "Phase conjugating circuit with frequency offset beam pointing error correction facility for precision retrodirective antenna applications," in *Proc. Eur. Radar Conf. (EuRAD)*, Oct. 2011 pp. 393–395.

- [30] L. Chen, T. Zhang, S. Liu, and X. Shi, "A bidirectional dual-frequency retrodirective array for full-duplex communication applications," *IEEE Antennas Wireless Propag. Lett.*, vol. 11, pp. 771–774, Jun. 2012.

- [31] A. Winterstein, L. Greda, and A. Dreher, "A PLL-based retro-directive antenna system for communications with arbitrary frequency gaps," in *Proc. 9th Eur. Conf. on Antennas Propag. (EuCAP)*, Lisbon, Portugal, Apr. 2015, pp. 1–5.

- [32] PSoC 4200 Family Datasheet Programmable System-on-Chip. [Online]. Available: http://www.cypress.com/documentation/datasheets/psoc-4-

psoc-4200-family-datasheet-programmable-system-chip-0

- [33] Experiment of DLL demonstrator. [Online]. Available: <u>https://youtu.be/sIBhAcomt2w</u>, last accessed 16 May 2017.

- [34] B. Toh, V. Fusco, and N. Buchanan, "Assessment of performance limitations of Pon retrodirective arrays," *IEEE Trans. on Antennas Propag.*, vol. 50, no. 10, pp. 1425–1432, Oct. 2002.

Yuan Ding received his Bachelor's degree from Beihang University (BUAA), Beijing, China, in 2004, received his Master's degree from Tsinghua University, Beijing, China, in 2007, and received his Ph.D. degree from Queen's University of Belfast, Belfast, UK, in 2014, all in Electronic Engineering.

He was a radio frequency (RF) Engineer in Motorola R&D Centre (Beijing, China) from 2007 to 2009, before joining Freescale Semiconductor Inc. (Beijing, China) as an RF Field Application Engineer, responsible for high power base-station

amplifier design, from 2009 to 2011. He is now an Assistant Professor at the Institute of Sensors, Signals and Systems (ISSS) in Heriot-Watt University, Edinburgh, UK. His research interests are in antenna array, physical layer security, and 5G related areas.

Dr. Ding was the recipient of the IET Best Student Paper Award at LAPC 2013 and the recipient of the Young Scientists Awards in General Assembly and Scientific Symposium (GASS), 2014 XXXIst URSI.

Neil B. Buchanan received a B.Eng. Hons degree from the Queens University of Belfast in 1993. In July 2000, he graduated with a Ph.D. entitled "Phase Locked Millimetre Wave HEMT Oscillators" from the Queens University of Belfast. Dr Buchanan's research interests include novel phase conjugating architectures for self-steered antennas, mm-wave MMIC design and innovative mm-wave transceivers. At present, he is employed by Queens' University Belfast as a Lecturer. Dr Buchanan has published over 70 scientific papers in major journals and in refereed international

conferences. He has been involved in several world-class research projects, and has recently led a research activity with the European Space Agency (ESA) to produce a TRL5 self-steered antenna for use with satellite broadband services. In October 2010 Neil Buchanan was presented with the "ESA Young Antenna Engineer Prize" at the ESA Antennas workshop for Space applications. In 2018, he was awarded the mobile world congress scholar gold award for applications of satellite antennas towards 5G.

Vincent F. Fusco (S'82–M82–SM'96– F'04) received the bachelor's (Hons.) degree in electrical and electronic engineering, the Ph.D. degree in microwave electronics, and the D.Sc. degree from Queen's University Belfast (QUB), Belfast, U.K., in 1979, 1982, and 2000, respectively.

His work was focused on advanced front-end architectures with enhanced functionality. He is Chief Technology Officer (CTO) of the ECIT at QUB. He has authored over 450 scientific papers in major

journals and in referred international conferences. He has authored two textbooks, holds patents related to self-tracking antennas, and has contributed invited papers and book chapters. His current research interests include active antenna and front-end MMIC techniques.

Prof. Fusco is a fellow of the Institute of Electrical and Electronics Engineers, the Institution of Engineering and Technology, the Royal Academy of Engineers, and the Royal Irish Academy. In 2012, he received the IET Senior Achievement Award and the Mountbatten Medal. He serves on the Technical Program Committee of various international conferences, including the European Microwave Conference.

#### **Rens Baggen**

Marta Martínez-Vázquez (FIEEE, 2017) was born in Santiago de Compostela, Spain, in 1973. She obtained her MSc. and PhD. degrees in Telecommunication Engineering from the Universidad Politécnica de Valencia, Spain, in 1997 and 2003, respectively. In 1999 she was granted a fellowship from the Pedro Barrié de la Maza Foundation for postgraduate research at, in Germany. In 2000 she joined the Antennas and EM Modelling department of IMST GmbH in Germany, where she works as senior engineer and project manager.

Her research interests include the design and applications of antennas for mobile devices, planar arrays, sensors, and RF systems.

She has been the chair of the COST IC1102 Action "Versatile, Integrated and Signal-aware Technologies for Antennas (VISTA) and the vice-chair of the COST IC0603 Action "Antenna Sensors and Systems for Information Society Technologies." Previously, she was a member of the Executive Board of the ACE (Antennas Centre of Excellence) Network of Excellence and the leader of its small antennas activity.

Dr. Martínez-Vázquez is currently the vice-chair of the Board of Directors of the European Association of Antennas and Propagation (EurAAP) and a member of the IEEE AP-S Education Committee. She is also a former member of the Administrative Committee of the IEEE Antennas & Propagation Society and served as a Distinguished Lecturer for the IEEE AP-S.

She is currently a feature Editors of the IEEE Antennas & Propagation Magazine and a Associate Editor of the IET Microwaves, Antennas & Propagation Journal. She has over 90 publications, including books, book chapters, journal and conference papers and patents.

Dr. Martínez-Vázquez has been awarded the 2004 Best Ph.D. award of the Universidad Politécnica de Valencia and the 2013 IEEE AP-S Lot Shafai Mid-Career Distinguished Achievement Award.

#### Maarten van der Vorst