Fan, H., Li, D., Kelin, Z., Cen, Y., Feng, Q., Qiao, F. and Heidari, H. (2018) A 4channel 12-bit high-voltage radiation-hardened digital-to-analog converter for low orbit satellite applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 65(11), pp. 3698-3706 (doi:10.1109/TCSI.2018.2856851).

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

http://eprints.gla.ac.uk/165450/

Deposited on: 17 July 2018

Enlighten – Research publications by members of the University of Glasgow\_ http://eprints.gla.ac.uk

# A 4-Channel 12-Bit High-Voltage Radiation-Hardened Digital-to-Analog Converter for Low Orbit Satellite Applications

Hua Fan, Member, IEEE, Dagang Li\*, Kelin Zhang, Yuanjun Cen,

Quanyuan Feng, Senior Member, IEEE, Fei Qiao, Member, IEEE, Hadi Heidari, Senior Member, IEEE

Abstract—This paper presents a circuit design and implementation of a 4-channel 12-bit digital-to-analogue converter (DAC) with high-voltage operation and radiation-tolerant attribute using a specific CSMC H8312 0.5-µm BiCMOS technology to achieve the functionality across a wide-temperature range from -55°C to 125°C. In this work, an R-2R resistor network is adopted in the DAC to provide necessary resistors matching which improves the DAC precision and linearity with both the global common centroid and local common centroid layout. Therefore, no additional, complicated digital calibration or laser-trimming are needed in this design. The experimental and measurement results show that the maximum frequency of the single-chip 4channel 12-bit R-2R ladder high-voltage radiation-tolerant DAC is 100 kHz, and the designed DAC achieves the maximum value of differential non-linearity (DNL) of 0.18 LSB, and the maximum value of integral non-linearity (INL) of -0.53 LSB at 125°C, which is close to the optimal DAC performance. The performance of the proposed DAC keeps constant over the whole temperature range from  $-55^{\circ}$ C to  $125^{\circ}$ C. Furthermore, an enhanced radiation-hardened design has been demonstrated by utilising a radiation chamber experimental setup. The fabricated radiation-tolerant DAC chipset occupies a die area of 7mm imes7mm in total including pads (core active area of 4mm  $\times$  5mm excluding pads) and consumes less than 525 mW, output voltage ranges from -10 V to +10 V.

Manuscript received YYY, 2018; accepted XXX, 2018. Date of publication QQQ, 2018; date of current version ZZZ.

The work of Hua Fan was supported by the National Natural Science Foundation of China (NSFC) under Grant 61771111, as well as supported by China Postdoctoral Science Foundation under grant 2017M612940 and Special Foundation of Sichuan Provincial Postdoctoral Science Foundation.

The work of Quanyuan Feng was supported by the National Natural Science Foundation of China (NSFC) under Grant 61531016, supported by the project of Science and Technology Support Program of Sichuan Province under Grant 2018GZ0139, and in part by the Sichuan Provincial Science and Technology Important Projects under Grant 2017GZ0110.

The work of Hadi Heidari was supported by the Glasgow Knowledge Exchange (GKE) Fund 2017/18 at the University of Glasgow, United Kingdom. The associate editor coordinating the review of this paper and approving it

for publication was Prof. XXXX.

\* Corresponding author: dagang@csmsc.com

Hua Fan is with State Key Laboratory of Electronic Thin Films and Integrated Devices, School of Electronic Science and Engineering, University of Electronic Science and Technology of China, Chengdu, China (e-mail: fanhua7531@163.com).

Dagang Li, Kelin Zhang and Yuanjun Cen are with Chengdu Sino Microelectronics Technology Co.,Ltd, Chengdu, China (e-mail: dagang@csmsc.com, kl\_zhang@csmsc.com, cen@csmsc.com).

Quanyuan Feng is with the school of information science and technology, Southwest Jiaotong University, Chengdu, China (e-mail: fengquanyuan@163.com).

Fei Qiao is with Department of Electronic Engineering, Tsinghua University, Beijing, China (e-mail: qiaofei@tsinghua.edu.cn).

Hadi Heidari is with the School of Engineering, University of Glasgow, G12 8QQ, Glasgow, UK (e-mail: hadi.heidari@glasgow.ac.uk)

Digital Object Identifier 10.1109/TCSI.2018.xxxxxx

Index Terms—Analog-to-Digital Converter (ADC), Digital-to-Analog Converter (DAC), Mismatch Calibration, R-2R ladder, Single Event Effects (SEE).

### I. INTRODUCTION

VER the past decades, various technologies and methodologies have been proposed to improve the system on chip (SoC) resilience to the radiation effects in space and nuclear applications, hostile domain electronics, medical equipments and high-energy physics experiments, etc. This work is oriented to avionics applications, where radiation tolerance mainly refers to circuits and system's ability to resist any number of undesirable radiation-induced phenomena in the case of extreme environments, including wide temperature, intense radiation, high pressure or strenuous vibration, etc. In order to avoid the traditional bulky and costly protective "warm boxes" or "electronics vaults", newly-designed electronics systems must robustly operate over a wide temperature range in extreme environments. The single event effect (SEE) caused by atmospheric radiation has been recognised in recent years as a design issue for avionics systems. There are various types of single event effects, which are the result of a single particle depositing sufficient energy, causing a disturbance in an electronic device; on the other hand, total-dose effects arisen from the leakage currents, which are related to transistor edge effects and field-oxide trapped charges is another important issue for radiation-tolerant circuit design [1].

Due to the increased need of radiation-tolerant analog and mixed-signal circuits in recent years, the development of precision analog circuits becomes more important. For instance, as an interface between analog and digital worlds, Digital-to-Analog Converter (DAC), which converts the signal from "0" and "1" is expressed in digital expressions to a continuous amplitude value of the analog, is an indispensable module in the whole electronic system. At present, DACs and Analogto-Digital Converters (ADCs) are very prevalent in modern electronic devices; however, their performance is often a bottleneck for practical applications [2]–[6]. The goal for engineers is to design and manufacture high performance radiation-tolerant DAC and ADC by using commercial processes that are inexpensive and widely available in the industry.

In this work, we report a design and implementation of a monolithic 4-channel 12-bit high-voltage radiation-tolerant DAC chip, which can satisfy the circuit specifications for low orbit satellite application to tolerate single event effects and

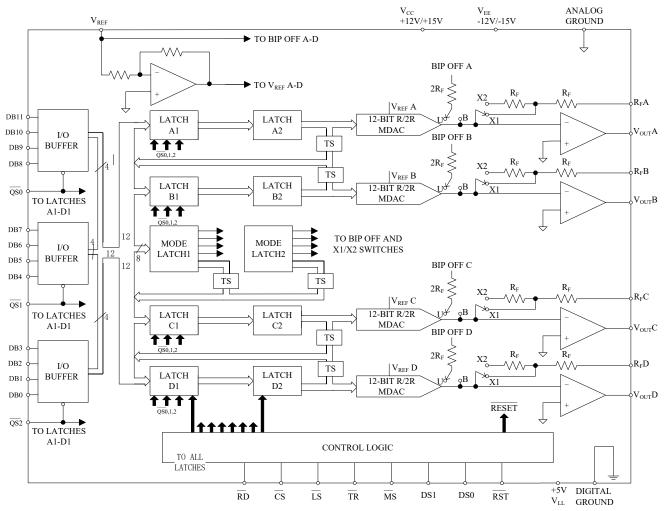

Fig. 1. The overall structure of the single-chip 4-channel 12-bit high-voltage radiation-hardened DAC [7].

to resist total ionising dose of 10 krad (Si). It is fabricated by using a custom designed CSMC H8312 0.5- $\mu$ m BiCMOS technology, which integrates high-voltage (HV) bipolar, HV and low-voltage (LV) CMOS devices. It is worth mentioning that  $V_{GS}$  and  $V_{DS}$  of MOS can reach as high as 30V, also,  $V_{CE}$  of bipolar can reach 30V.

The contributions of this work can be summarized as follows:

(i) Conventional DAC with R-2R resistor network usually adopts a complex thin-film resistor process and laser-trimming to achieve necessary matching of resistors. Mechanical stress during packaging and long-term drift of laser-trimming components often pose serious problems to such R-2R converters. In this work, a novel and reasonable resistive array layout and wiring method are well-designed and characterised. In detail, both the global common centroid and local common centroid layout have been fully implemented. Therefore, no additional, complicated digital calibration or trimming are needed in this work;

(ii) Guard rings are the key techniques in the radiationhardened design. In this work, both valid and invalid guard ring designs have been demonstrated at the radiation chamber, which is of great inspiration for both industry and academia;

(iii) It is worth mentioning that the 4-channel 12-bit DAC

with high-voltage operations and radiation-tolerant attribute proposed in this work is a milestone and exhibits a great impact on the aerospace industry of China.

The paper is organised as follows: A brief overview of DAC design is presented in Section II. Section III describes the circuit design and the main features of the proposed DAC. Section IV discusses the collected experimental results, while the key outcomes are finally summarised in Section V.

#### **II. SYSTEM OVERVIEW**

The overall structure of the proposed single-chip 4-channel 12-bit R-2R high-voltage radiation-hardened DAC with readback capability is shown in Fig. 1. In general, it provides four voltage-output DACs on one chip to offer the highest density. The output range of each DAC is fully and independently programmable. Readback capability allows to verify the contents of the internal data registers, which is obtained by setting the address of the DAC (DS0, DS1) and Quads (QS0, QS1, QS2) on the address pins and bringing the RD and CS pins low.

The analog portion consists of four DAC cells, four output amplifiers, a control amplifier and switches. The positive and negative power supply voltages of analog part reach as high as  $\pm 15$ V. High-voltage, low-threshold transistors are applied whose safe operating voltage can reach as high as 30V. In

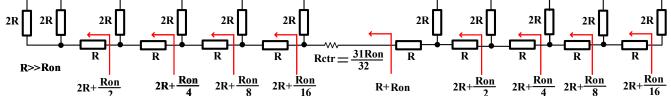

Fig. 3. The equivalent circuit of simplified R-2R structure.

other words,  $V_{GS}$ ,  $V_{DS}$  of MOS and  $V_{CE}$  of bipolar can reach as high as 30V. High-precision poly resistor is chosen in this work, which can meet the requirements of high voltage operations.

Each 12-bit DAC cell is an inverting R-2R type. The output current from each DAC is switched to the on-board application resistors and output amplifier. The output range of each DAC cell is programmed through the digital I/O port and may be set to unipolar or bipolar range with a gain of one or two times the reference voltage. All DACs can operate from a single external reference, and the output range of each DAC is fully and independently programmable. Each DAC offers flexibility, accuracy and good dynamic performance, in which a novel layout of R-2R resistive array can satisfy the demands of DAC linearity. It is worth mentioning that no calibration or laser-trimming are applied to the resistive array. The performance of each DAC is guaranteed to be monotonic and stable over the full operating temperature range from  $-55^{\circ}$ C to  $125^{\circ}$ C.

The power supply voltage of digital portion is only 5V, DB0  $\sim$  DB11 are the inputs of DAC. An asynchronous RESET-TO-ZERO control pin is provided to allow a user to simultaneously reset all DAC outputs to zero, regardless of the contents of the input latch, and the asynchronous reset signal can be asserted at any time.

#### **III. CIRCUITS DESIGN**

#### A. 12-Bit R-2R DAC design

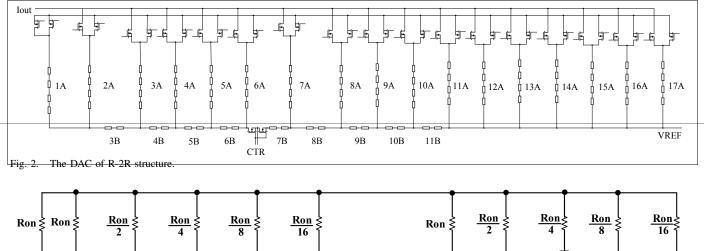

As shown in Fig. 2, DAC is the core component of the 4-Channel 12-Bit radiation-hardened DAC. The DAC uses segmentation to reach higher resolutions, thermometer codes are applied to the MSB, as shown for the last seven resistors on the right from 11A to 17A in Fig. 2, which can overcome the undesired glitch impulse effectively [8], [9]. Split switch CTR in the centre splits the lower 6 bits and the higher 6 bits.

In this work, the value of resistor of R-2R ladder is much larger than the on-resistance of the switch. Fig. 3 shows the equivalent simplified R-2R ladder.

In R-2R ladder, the linearity of the R-2R ladder is sensitive to the matching of the resistive networks [10]–[14]. Conventionally, the R-2R structure is fabricated from thin-film resistors which are laser-trimmed to achieve high linearity and guarantee monotonicity. In the traditional layout of resistive array, the resistors are always interconnected by multi-layer metal. Not only the routing is complicated, but also the gain error calibration becomes more complex. Furthermore, traditional layout of resistive array usually focuses on the matching accuracy between MSB resistors, but ignores the matching between LSB and MSB resistors and the matching between LSB resistors.

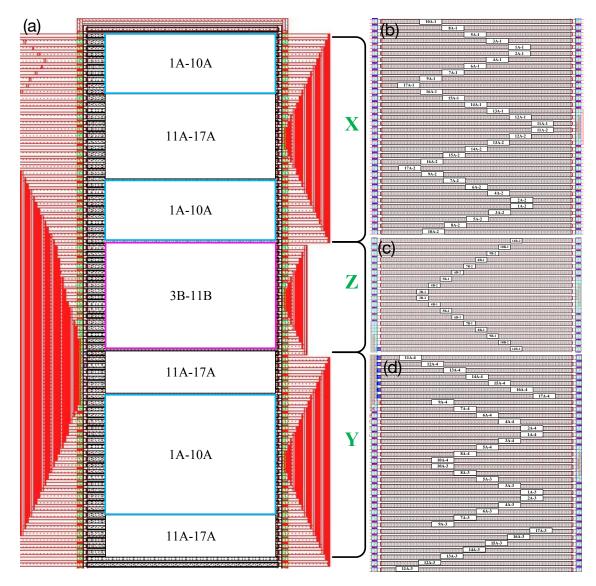

In this work, a novel layout technique considers not only the matching between MSB and LSB resistors, but also the matching between LSB resistors. Therefore, it can significantly improve the matching of resistive array, as well as the precision and linearity of DAC. The resistors of each channel are split into a different number of resistors with the same size, which is able to minimise the device mismatches and the parasitic resistance and capacitance. Likewise, the resistors in the R-2R are symmetrically aligned with only single metal interconnection wire so as to minimise the effects of the parasitic resistances of the metal interconnects. In Fig. 2, the resistors of one channel have been marked from No. 1 to 17, and then divide them into section A and section B according to the locations of the resistors. In the following, Fig. 4(a) shows the global distribution of the resistors, while Fig. 4(b-d) illustrate the detailed local distributions of X region, Z region and Y region. Both global and local common centroid can be ensured with this proposed layout.

In Fig. 4(a), the resistors of section B are only placed in

Fig. 4. (a) The overall distribution of resistive array. The distribution of resistors in (b) X region, (c) Z region, and (d) Y region.

the centre of the whole array, while the resistors of section A are divided into two parts: 11A to 17A (higher bits) and 1A to 10A (lower bits). Higher bits and lower bits are arranged in cross type to ensure centroid symmetry. Meanwhile, the resistors of section A are placed on both sides of section B. Then, obviously, the resistors of both section A and B have realised the common centroid distribution in this way. Next, the resistive array which is already arranged in a global common centroid is divided into three regions: X region, Y region and Z region. The resistors of section B belong to Z region (in the centre), and the resistors of section A belong to both X and Y regions. For example, the resistor 1A is separated into four equal parts: 1A-1, 1A-2, 1A-3 and 1A-4, where 1A-1 and 1A-2 are located in X region, while 1A-3 and 1A-4 in Y region. All the resistive array must realise local centroid distribution in X, Y and Z regions respectively.

The distribution of the resistors in X region is shown in Fig. 4(b) in details. Resistors 1A to 10A are divided into two groups and the two groups are placed symmetrically with each other. For example, the resistor 1A is divided into 1A-1 and

1A-2. In general, 1A and 2A are symmetrical, 3A and 4A are symmetrical, 5A and 6A are symmetrical until 7A, which is placed on the side of 6A rather than 5A, then 8A and 10A are placed on the side of 5A, 9A is placed after 6A and 7A. In the centre, 11A-1 to 17A-1 and 11A-2 to 17A-2 are symmetrically placed on both sides of the axle wire in X region in order.

The distribution of the resistors in Y region is shown in Fig. 4(d), which is similar with that of the resistors in X region in Fig. 4(b). Resistors from 1A to 10A are divided into two groups and the two groups are placed symmetrically with each other. For example, resistor 1A is divided into 1A-3 and 1A-4. In general, 1A and 2A are symmetrical, 3A and 4A are symmetrical, 5A and 6A are symmetrical until 7A, which is placed on the side of 6A rather than 5A, then 8A and 10A are placed on the side of 5A, 9A is placed after 6A and 7A. In the centre, 11A-1 to 17A-1 and 11A-2 to 17A-2 are symmetrically placed on both sides of the axle wire in the Y region in order. 1A-3 to 10A-3 and 1A-4 to 10A-4 are placed on both sides of the axle wire in Y region.

The resistors in Z region contain all resistors of group B.

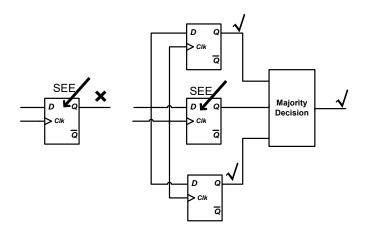

Fig. 5. D-latch with triple modular redundancy design.

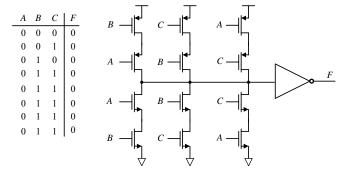

Fig. 6. Truth table and majority voter

The distribution of the resistors is shown in Fig. 4(c): the resistors from 3B to 11B are divided into two groups and these two groups are placed symmetrically with respect to the centre.

Finally, such a layout distribution is not only globally common centroid in the whole array, as shown in Fig. 4(a), but also common centroid in every local region respectively (X, Z and Y regions in Fig. 4(b-d)). Therefore, the resistor mismatch caused by stress and temperature gradients can be decreased to the most extent. Moreover, in this design, the connection between the entire resistive arrays uses only the same metal (layer-M1) without holes and multi-layer interconnects. Therefore, the system mismatch caused by holes and multilayer interconnects is dramatically decreased. Afterward, the wire length of every resistor from 1A to 17A is balanced. For example, the resistor 1A includes 1A-1, 1A-2, 1A-3 and 1A-4, Fig. 4(b) shows that the wire from 1A-1 to 1A-2 is long, but in Fig. 4(d), wire from 1A-3 to 1A-4 becomes shorter. The same case with resistor 17A, wire from 17A-1 to 17A-2 is short (Fig. 4(b)), but 17A-3 to 17A-4 becomes longer (Fig. 4(d)). In this way, the length of the interconnection of every resistor may be roughly equal.

#### B. Design issues about Reliability

In this design, analog block adopts a HV design, and the digital block contains both HV and LV designs. In the analog block, the length of the HV MOS is larger than  $3\mu m$ , which can ensure single-event tolerance of the device [15]. However,

the total ionizing dose tolerance is poor. Hence, in order to improve the tolerance of total ionising dose, guard rings are applied to substrate to a large extent.

In this design, PMOS is located in N-well, which has a N+ N-well guard ring inside. Meanwhile, N-well is surrounded by the P+ P-sub guard ring. Finally, outside of P+ P-sub guard ring is a HV N-well, whose function is to isolate two P-sub substrates between inner and outside. NMOS is surrounded by the P+ P-sub guard ring, outside of which is also the HV N-well. Therefore, the number of the P+ P-sub guard rings is about twice of N+ N-well guard rings.

Redundancy is also a common mitigation strategy to achieve system safety and reliability. In digital circuits, triple modular redundancy design is adopted to improve the ability to resist single event upset (SEU). However, it occupies more area and sacrifices speed. In some cases, the speed becomes 80% of conventional designs with about 3.2 times of increase in the resource and power. Therefore, the triple modular redundancy is used only in the crucial sub-blocks. For example, Fig. 5 shows a D-latch with triple modular redundancy [16], where three same Latches and majority voter constitute one Dlatch. Fig. 6 shows the truth table and majority voter. Special radiation resilience experiments of D-latch have been carried out at the radiation chamber facilities of the China Institute of Atomic Energy in Beijing, China, which will be introduced in details in Section IV.

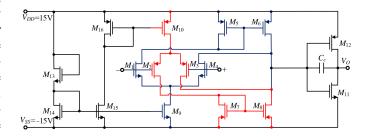

#### C. Operational Amplifiers Design

The output operational amplifier is one of the most challenging parts of DAC. In order to reduce power consumption, the operational amplifier used in this design is a simple two-stage amplifier. Compared with the bipolar operational amplifier, CMOS operational amplifier shows higher input

Fig. 7. The two-stage operational amplifier.

TABLE I

PERFORMANCE SUMMARY OF OPERATIONAL AMPLIFIER

| Corner | Temperature<br>(°C) | Gain  | Gain bandwidth<br>(MHz) | Supply voltage (V) |  |

|--------|---------------------|-------|-------------------------|--------------------|--|

|        | (-C)                | (dB)  | (MHZ)                   | (v)                |  |

| tt     | -55                 | 139.4 | 1.2                     | ±15                |  |

| tt     | 125                 | 125.4 | 1.2                     | ±15                |  |

| SS     | -55                 | 139.3 | 1.2                     | ±15                |  |

| SS     | 125                 | 130.0 | 1.1                     | ±15                |  |

| ff     | -55                 | 140.4 | 1.3                     | ±15                |  |

| ff     | 125                 | 115.4 | 1.2                     | ±15                |  |

| fs     | -55                 | 139.2 | 1.1                     | ±15                |  |

| fs     | 125                 | 116.1 | 1.2                     | ±15                |  |

| sf     | -55                 | 139.9 | 1.3                     | ±15                |  |

| sf     | 125                 | 123.7 | 1.2                     | ±15                |  |

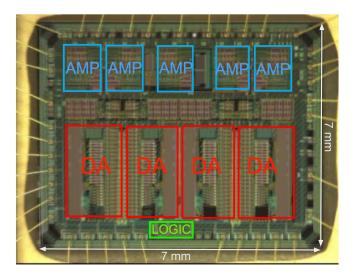

Fig. 8. The fabricated 4-channel 12-bit DAC microphotograph: whole chip including pads (with back-annotated layout).

impedance, smaller static power consumption [17]. In this design, the power supply is  $\pm 15V$ , operational amplifier with high open loop gain, sufficient phase margin, high common mode rejection ratio and large input/output swing is demanded.

For the radiation-hardened design, it is necessary to take measures to improve the noise immunity of the operational amplifier. It is found that most of the noise in the circuit blocks comes from the input level. Therefore, complementary input and differential structure are used to suppress the noise.

The two-stage operational amplifier used in this work is shown in Fig. 7, where M1-M4 constitute the input stage, M5-M8 act as active loads, M9 and M10 are tail current sources, M11 and M12 constitute output stage, and miller capacitor Cc provides for the frequency compensation [18]– [22]. The DC gain of the operational amplifier is greater than 110 dB, and the gain bandwidth (GBW) is greater than 1 MHZ, the high open loop gain of the operational amplifier in a negative feedback configuration is sufficient to compensate for the expected fluctuations.

Table I summarises the performance of the operational amplifier.

#### **IV. MEASUREMENT RESULTS**

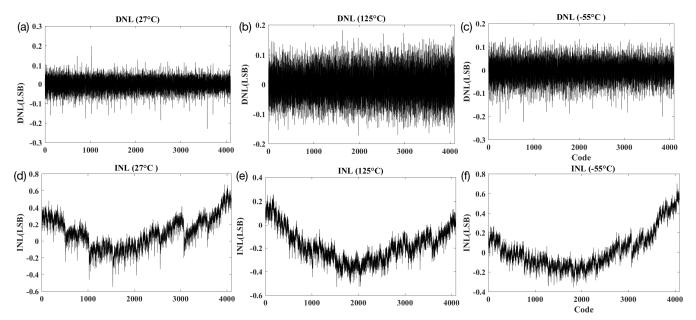

The 4-channel 12-bit DAC is manufactured on one monolithic IC chip by 0.5- $\mu$ m BiCMOS technology (CSMC H8312). Fig. 8 shows the layout and chip photo. The whole area of prototype is 7mm × 7mm including pads (core area is 4mm × 5mm), and the maximum frequency of the DAC is 100 kHz. Measurement results show that: the power consumption of the 12-bit DAC is less than 525 mW. As a commercial product, 525 mW signifies the power consumption under the extreme case, which includes both analog and digital power. For the analog part, the positive and negative power supplies reach as high as ±15V, considering 10% of fluctuation , the maximum current of analog power supplies is 15 mA, leading to 495 mW of analog power consumption; On the other hand, the power supply of digital portion is only 5V, also considering 10% of fluctuation, the maximum current of digital power supply is 5.45 mA, therefore, the total power consumption is 525 mW. Differential non-linearity (DNL) at 27°C, 125°C and -55°C are [-0.23 LSB, 0.2 LSB], [-0.17 LSB, 0.18 LSB] and [-0.23 LSB, 0.14 LSB], respectively (Fig. 9(a-c)), and integral non-linearity (INL) at 27°C, 125°C and -55°C are [-0.55 LSB, 0.67 LSB], [-0.53 LSB, 0.26 LSB] and [-0.35 LSB, 0.7LSB], respectively (Fig. 9(d-f)). In conclusion, DNL and INL are well within 1 LSB in all cases, close to the performance of ideal DAC. The number of samples for DNL/INL measurements is 400, all of these samples achieve the similar performance, which demonstrate that the novel layout adopted in this work gives a good matching performance.

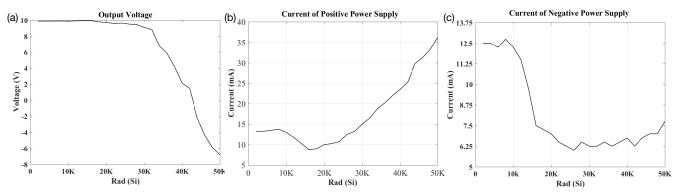

Fig. 12(a-c) reflect the resilience to total-dose effects. In these experiments, the chip was irradiated by a  $^{60}$ Co source at room temperature at dose rate of 0.0064 rad (Si)/s. Fig. 12(a) shows that the chip loses validity at the total-dose of more than 20 krad (Si). Fig. 12(b-c) show that the currents of positive power supply and negative power supply fluctuate rapidly at total-dose up to 30 krad and 10 krad (Si), respectively. Results of Fig. 12(a-c) demonstrate that the 12-Bit radiation-hardened DAC can satisfy demands for low orbit satellite applications.

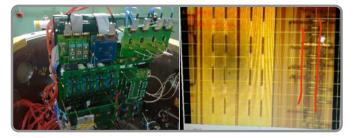

A special set of single event latch-up (SEL) experiments are performed at the radiation chamber of China Institute of Atomic Energy in Beijing. 4 samples were irradiated by  ${}^{35}Cl^{14+}$  (5 MeV/amu) and  ${}^{74}Ge^{20+}$  (3 MeV/amu) sources within 3 cm beam width in vacuum environment. In total, every sample received  $1 \times 10^7$  ions/cm<sup>2</sup> at 22°C, with a  ${}^{35}Cl^{14+}$ flux of  $1.1 \times 10^4$  ions/cm<sup>2</sup>/s and a  ${}^{74}Ge^{20+}$  flux of  $1.2 \times 10^4$ ions/cm<sup>2</sup>/s, respectively. The linear energy transfer (LET) for  ${}^{35}Cl^{14+}$  ions is 13.3 MeV cm<sup>2</sup>/mg, while the LET for  ${}^{74}Ge^{20+}$ ions is 37.5 MeV cm<sup>2</sup>/mg.

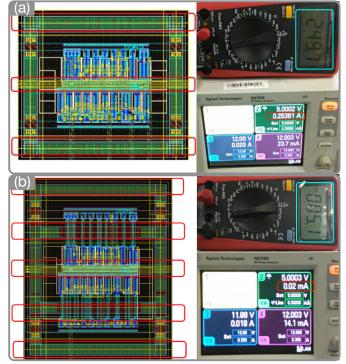

Laser pulse was applied to simulate radiation source (white point in Fig. 10) for failure analysis, in order to find the failure node. When exposed to laser pulse at the radiation chamber, as expected, D-latch with three guard rings and D-latch with five guard rings show different single-event latch-up effects. Here, three-channel oscilloscope including channel 2, 3 and 4 and multimeter are used to observe and analyze the latch-up phenomenon together. On the left of Fig. 11(a), the D-Latch layout includes three guard rings, located at the top, middle, and bottom, as identified with red boxes. At the right side of Fig. 11(a), 0.25 A current of the 5V digital power supply (corresponding to channel 2) demonstrates that the chip loses validity, because the thyristor between PMOS and NMOS (the region between the two red lines in Fig. 10) has been triggered by the laser pulse. In this case, two more guard rings have been added, as shown at left of Fig. 11(b). At right of Fig. 11(b), the current reduces to 0.02 mA by using 5 guard rings, which demonstrates that latch-up disappears and five guard rings function well under radiation of  ${}^{35}\text{Cl}^{14+}$  and  ${}^{74}\text{Ge}^{20+}$ sources. Therefore, for the sake of designing radiation-tolerant integrated circuits, it is vital to separate NMOS and PMOS completely.

However, guard rings sacrifice the chip area. In Fig. 11 (a), the area of the conventional layout of D-latch with three guard rings is 97  $\mu$ m × 110  $\mu$ m, while the area of the improved

Fig. 9. Measured DNL of the fabricated 12-bit DAC at (a)  $27^{\circ}$ C, (b)  $125^{\circ}$ C and (c)  $-55^{\circ}$ C. Measured INL of the fabricated 12-bit DAC at (d)  $27^{\circ}$ C, (e)  $125^{\circ}$ C and (f)  $-55^{\circ}$ C.

Fig. 10. Radiation test setup utilising the radiation chamber facilities of the China Institute of Atomic Energy in Beijing, China.

layout of D-latch with five guard rings is 238  $\mu$ m × 150  $\mu$ m (Fig. 11 (b)), then 0.025 mm<sup>2</sup> of area overhead for one D-latch. There are in total 64 D-latches, leading to 1.6 mm<sup>2</sup> of area overhead for all of the D-latches.

Some similar commercial products are compared with the proposed 4-channel 12-bit DAC, as shown in Table II. The proposed novel layout of resistive array can ensure enough static linearity and obviate the calibration of R-2R DAC, superior to all the other four products (all need laser-trimming). Among all the products, AD 7837 achieves the best DNL and INL only with 2 channels. For 4-channels products, the proposed design in this paper shows very good static linearity. Finally, only the proposed DAC considers the resilience to radiation, which makes it suitable for broader applications compared with others.

## V. CONCLUSION

This paper uses a 0.5- $\mu m$  HV BiCMOS process to design a monolithic 4-channel 12-bit high-voltage radiation-tolerant DAC chip, output voltage ranges from -10 V to +10 V. The experiment results show that the power consumption is less than 525 mW. Both the DNL and INL are well within 1 LSB, close to the ideal performance of DAC.

Fig. 11. (a) Conventional layout of D-latch with three guard rings and 0.25 A of 5V digital power supply demonstrates that the latch-up occurs. (b) Improved layout of D-latch with five guard rings and 0.02 mA of 5V digital power supply demonstrates that the latch-up disappears.

#### VI. ACKNOWLEDGMENTS

The authors would like to thank Professor Franco Maloberti and Associate Professor Edoardo Bonizzoni at the University of Pavia, Italy, for their helpful and valuable discussions and suggestions.

Fig. 12. Measured results of the fabricated 12-bit DAC: (a) Output Voltage, (b) Current of Positive Power Supply, and (c) Current of Negative Power Supply.

| INDEE II                             |                 |  |  |  |  |  |  |  |

|--------------------------------------|-----------------|--|--|--|--|--|--|--|

| COMPARISON OF PERFORMANCE ON SEVERAL | COMMERCIAL DACS |  |  |  |  |  |  |  |

|                                | This work                     | AD664<br>[7]   | DAC8412<br>[23]               | AD7837<br>[24] | AD8522<br>[25] |

|--------------------------------|-------------------------------|----------------|-------------------------------|----------------|----------------|

| Resolution (bits)              | 12                            | 12             | 12                            | 12             | 12             |

| Technology                     | BICMOS                        | BICMOS         | BICMOS                        | CMOS           | CBCMOS         |

| Number of Channels             | 4                             | 4              | 4                             | 2              | 2              |

| Temperature Range (°C)         | [-55, 125]                    | [-55, 125]     | [-55, 125]                    | [-55, 125]     | [-55, 125]     |

| DNL (LSB)                      | 0.23                          | 0.75           | 1                             | 0.1            | 1              |

| INL (LSB)                      | 0.67                          | 0.75           | 1                             | 0.2            | 1.5            |

| Calibration of R-2R DAC        | no                            | laser-trimming | laser-trimming                | laser-trimming | laser-trimming |

| Resilience to radiation design | yes                           | no             | no                            | no             | no             |

| Package                        | CQFJ44                        | DIP28          | LCC28                         | DIP24          | SOIC14         |

| $(mm \times mm \times mm)$     | $16.5 \times 16.5 \times 1.8$ | 36.6×13.5×9    | $11.2 \times 11.2 \times 2.4$ | 31.1×6.6×3.25  | 8.65×3.9×1.55  |

#### References

- M. Baghbanmanesh, F. Maloberti, and U. Gatti, "A 10-Bit Radiation-Hardened by Design (RHBD) SAR ADC for Space Applications," in 2017 New Generation of CAS (NGCAS), 2017, pp. 53–56.

- [2] H. Fan and F. Maloberti, "High-Resolution SAR ADC with Enhanced Linearity," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 10, pp. 1142–1146, 2017.

- [3] H. Fan, J. Yang, F. Maloberti, Q. Feng, D. Li, D. Hu, Y. Cen, and H. Heidari, "High Linearity SAR ADC for High Performance Sensor System," in *IEEE Int. Symposium on Circuits and Systems (ISCAS)*, 2018, pp. 1–4.

- [4] H. Fan, H. Heidari, F. Maloberti, D. Li, D. Hu, and Y. Cen, "High Resolution and Linearity Enhanced SAR ADC for Wearable Sensing Systems," in *IEEE Int. Symposium on Circuits and Systems (ISCAS)*, 2017, pp. 180–183.

- [5] H. Fan, J. Li, Q. Feng, X. Diao, L. Lin, K. Zhang, H. Sun, and H. Heidari, "Exploiting smallest error to calibrate non-linearity in sar adcs," *IEEE Access*, 2018.

- [6] J. Ahn et al., "Design issues for a radiation-tolerant digital-to-analog converter in a commercial 2.0-/spl μm BiCMOS process," in European Conf. Radiation and Its Effects on Components Systems (RADECS). IEEE, 1997, pp. 120–125.

- [7] Analog Devices AD664, "Monolithic 12-Bit Quad DAC," www.analog.com.

- [8] M. Krämer, E. Janssen, K. Doris, and B. Murmann, "A 14-bit 30-MS/s 38-mW SAR ADC using noise filter gear shifting," *IEEE Trans. Circuits* and Systems II: Express Briefs, vol. 64, no. 2, pp. 116–120, 2017.

- [9] A. D. Mohapatra and M. N. Sahoo, "Modelling of a Fibonacci Sequence 8-bit Current Steering DAC to Improve the Second Order Nonlinearities," in *Progress in Advanced Computing and Intelligent Engineering*. Springer, 2018, pp. 533–543.

- [10] B. Hu, Y. Du, R. Huang, J. Lee, Y.-K. Chen, and M.-C. F. Chang, "An R2R-DAC-Based Architecture for Equalization-Equipped Voltage-Mode PAM-4 Wireline Transmitter Design," *IEEE Trans. Very Large Scale Integration (VLSI) Systems*, vol. 25, no. 11, pp. 3260–3264, 2017.

- [11] Z. Liang, B. Li, M. Huang, H. Ye, K. Xu, Y. Liu, and Y. Lu, "A fourband TD-LTE transmitter with wide dynamic range and LPF bandwidth calibration," in *Int. Symp. VLSI Design, Automation Test (VLSI-DAT)*. IEEE, 2017, pp. 1–4.

- [12] L. Duncan, B. Dupaix, J. McCue, B. Mathieu, M. LaRue, M. Teshome, M.-J. Choe, and W. Khalil, "A 10b DC-to-20GHz multiple-return-tozero DAC with; 48dB SFDR," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*), 2017, pp. 286–287.

- [13] D. E. Bellasi and L. Benini, "Smart Energy-Efficient Clock Synthesizer for Duty-Cycled Sensor SoCs in 65 nm/28nm CMOS," *IEEE Trans. Circuits Systems I: Regular Papers*, vol. 64, no. 9, pp. 2322–2333, 2017.

- [14] D. Marche and Y. Savaria, "Modeling R-2R Segmented-Ladder DACs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 1, pp. 31–43, 2010.

- [15] P. E. Dodd and L. W. Massengill, "Basic mechanisms and modeling of single-event upset in digital microelectronics," *IEEE Transactions on Nuclear Science*, vol. 50, no. 3, pp. 583–602, 2003.

- [16] G. W. McIver, J. R. Marum, and J. B. Cho, "Triple redundant faulttolerant register," 1991, US Patent 5,031,180.

- [17] T. E. Becker, A. J. Lanot, G. S. Cardoso, and T. R. Balen, "Single event transient effects on charge redistribution SAR ADCs," *Microelectronics Reliability*, vol. 73, pp. 22–35, 2017.

- [18] Z. Qin et al., "0.5-V 70-nW Rail-to-Rail Operational Amplifier Using a Cross-Coupled Output Stage," *IEEE Trans. Circuits Systems II: Express Briefs*, vol. 63, no. 11, pp. 1009–1013, 2016.

- [19] C. W. Lu, "A Rail-To-Rail Class-AB Amplifier With an Offset Cancellation for LCD Drivers," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 2, pp. 525–537, 2009.

- [20] M. D. Pardoen and M. G. Degrauwe, "A rail-to-rail input/output CMOS power amplifier," *IEEE Journal of Solid-State Circuits*, vol. 25, no. 2, pp. 501–504, 1990.

- [21] H. Heidari, E. Bonizzoni, U. Gatti, and F. Maloberti, "A CMOS Current-Mode Magnetic Hall Sensor With Integrated Front-End," *IEEE Trans. Circuits Systems I: Regular Papers*, vol. 62, no. 5, pp. 1270–1278, 2015.

- [22] A. B. Tripura Sundari and A. Srinivasulu and T. N. Bhagirath, "Two Rail-To-Rail Class-AB CMOS Buffers with High Performance Slew Rate and Delay," *Int. Conf. Devices, Circuits Communications (ICD-CCom)*, pp. 1–6, 2014.

- [23] Analog Devices DAC8412, "Quad, 12-Bit DAC Voltage Output with Readback," www.analog.com.

- [24] Analog Devices AD7837, "LC2MOS Complete, Dual 12-Bit MDACs," www.analog.com.

- [25] Analog Devices AD8522, "+5 Volt, Serial Input, Dual 12-Bit DAC," www.analog.com.

Hua Fan (M'16) was born in Ziyang, Sichuan, China, in 1981. She received the B.S. degree in communications engineering and the M.S. degree in Computer science and technology, both from Southwest Jiaotong University, Chengdu, China, in 2003 and 2006, respectively. She received the Ph.D. degree from Tsinghua University, BeiJing, in July 2013.

From September 2013 to June 2016, she was an assistant professor of University of Electronic Science and Technology of China, from July 2016 to

present, she is an associate professor of University of Electronic Science and Technology of China, Chengdu, China. Her research interests include lowpower, high-speed and high-resolution A/D converter designs. From March 2015 to March 2016, she joined the Integrated Microsystem (IMS) research group in the department of electrical computer and biomedical engineering at University of Pavia in Italy as a post-doc under the supervision of Professor Franco Maloberti.

Quanyuan Feng (M'06–SM'08) received the M.S. degree in microelectronics and solid electronics from the University of Electronic Science and Technology of China, Chengdu, China, in 1991, and the Ph.D. degree in electromagnetic field and microwave technology from Southwest Jiaotong University, Chengdu, in 2000. He is currently the Head of the Institute of Microelectronics, Southwest Jiaotong University.

In recent five years, he has authored more than 500 papers such as the IEEE TRANSACTIONS

ON ANTENNAS AND PROPAGATION, the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, and the IEEE ANTENNAS AND WIRELESS PROPAGATION LETTERS, among which more than 300 were registered by SCI and EL His current research interests include integrated circuits design, RFID technology, embedded system, wireless communications, antennas and propagation, microwave and millimeter-wave technology, smart information processing, electromagnetic compatibility, and RF/microwave devices and materials.

Dr. Feng has been honoured as the "Excellent Expert" and the "Leader of Science and Technology" of Sichuan Province owing to his outstanding contribution.

**Dagang Li** was born in Suqian, Jiangsu, China, in 1977. He received the B.S.degree from University of Electronic Science and Technology of China, Chengdu, China, in 2000.

From July 2000, he works in Chengdu Sino Microelectronic Science and Technology co.,ltd. His research interests include high-resolution high speed A/D and D/A converter and power management designs.

Kelin Zhang was born in Mishan, Heilongjiang, China, in 1978. He received the B.S. degree in microelectronics from Jilin University, Changchun, China, in 2001. And he obtained the M.S. degree in Microelectronics and Solid State Physics at the University of Electronic Science and Technology of China, Chengdu, China, in 2009.

From 2001 to 2012, he worked in CSMSC as an engineer, project manager and vice president of research and development. From 2012 to 2014, he worked at INFOSYS as Senior Account Manager.

From 2014 to 2015, he worked as a back-end manager in Shanghai, Onbright. From 2016 to this year, he worked at CSMSC, as a Vice Minister of analog research and development. He focuses on the research and development of high speed and high precision ADC and DAC, high speed operation and amplifier, high power DC-DC, AC-DC, LDO.

in Department of Electronic Engineering, Tsinghua University, China. He received his PhD degree from Tsinghua University, China, in 2006, and received his bachelor degree from Lanzhou University, China, in 2000, respectively. His research interests include energy-efficient integrated perception systems for intelligent robots, and algorithm/hardware co-design for moving robots. He patented more than 30 inventions and published around 90 paper.

Fe Qiao (M'06) is currently an associate professor

Hadi Heidari (M'15–SM'17) is a Lecturer (Assistant Professor) in the School of Engineering at the University of Glasgow, UK. He received his PhD in Microelectronics from the University of Pavia (Italy) in 2015. He has authored over 70 articles in peer reviewed journals (e.g. IEEE Solid-State Circuits Journal, Trans. Circuits and Systems I and IEEE Trans. Electron Devices) and in international conferences. He has been the recipient of a number of awards including the IEEE CASS Scholarship (NGCAS'17 conference), Silk Road Award from the

Solid-State Circuits Conference (ISSCC'16), Best Paper Award from the IEEE ISCAS'14 conference, Gold Leaf Award from the IEEE PRIME'14 Conference and Rewards for Excellence prize from the University of Glasgow (2018). He involves in the organising committees of the IEEE PRIME'15, SENSORS'16, '17, IEEE NGCAS'17, BioCAS'18, ISCAS'20,'23 conferences and chairing three special sessions at ISCAS'16,'17,'18. He is an IEEE Senior Member, an Editor for the Elsevier Microelectronics Journal and lead Guest Editor for four journal special issues. He is member of the IEEE Circuits and Systems Society Board of Governors (BoG), IEEE Sensors Council Administrative Committee (AdCom).

**Yuanjun Cen** was born in Daqing, Heilongjiang, China, in 1977. He received the B.S. degree in microelectronics from Jilin University, Changchun, China, in 2000. And he obtained the M.S. degree in Microelectronics and Solid State Physics at the University of Electronic Science and Technology of China, Chengdu, China, in 2009.

From 2000 to this year, he worked in CSMSC, as an engineer, project manager, analog research and development minister, deputy chief engineer, chief engineer, also as a simulation research and

development department minister. He specializes in high-speed and highprecision ADC and DAC, high-speed op amp, high-power DC-DC, AC-DC, LDO, CPLD and other fields of research and development.