University of Paderborn System and Circuit Technology

# A Eightweight Hook

**NOVA Packet Processing Platform** Prof. Dr.-Ing. Ulrich Rückert C. Sauer<sup>1</sup>, M. Gries<sup>1</sup>, S. Dirk<sup>1</sup>, J.-C. Niemann<sup>2</sup>, M. Porrmann<sup>2</sup>, U. Rückert<sup>2</sup>

<sup>1</sup> Infineon Technologies, Access Communications, Munich <sup>2</sup> Heinz Nixdorf Institute, Paderborn

## **Motivation & Goal**

## Modular platform construction kit to investigate design criteria, such as flexibility, programmability, area, and performance

- Reuse of of-the-shelf components (e.g., programmable embedded cores) and deployment tools where possible

- Refinements (instruction set, co-processors, etc.) where needed as determined by profiling of reference applications

- Synergy: Hardware platform directly supports message passing semantics of application; NoC is a natural choice

# **Application Domain**

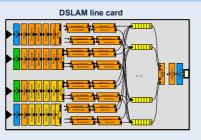

Packet processing in access networks

cluster

N-Core & multi-

on-chip network

- Data-flow driven processing

- Message passing semantics between computational kernels

- Subject to tight constraints on costs and performance

- Flexibility required to support broad variety of protocols and customer requirements

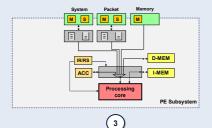

# **Network-Optimized Versatile Architecture (NOVA) Platform: Concepts**

Systematic development of platform building blocks Profiling of embedded general-purpose cores (and their

general purpose cores are flexible and have mature compilers

compilers) and specialized packet processing engines

Packet processing engines provide high performance;

> Provides a first estimate of required parallelism

# Modular platform

- Number and type of processing cores

- Number and type of co-processors

- Number and type of I/O interfaces

- Heterogeneous memory hierarchy

- Communication architecture

# I/O If CoP Mem Memory

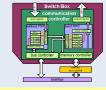

### GigaNoC - hierarchical Network-on-chip

- Bus-based network for small clusters (< 10 components)</li>

- Switch boxes for connecting clusters

### **Efficient implementation** Two NoC interfaces, buffering 16 64B messages each, need less than 1/3 of the CPU subsystem area

### **NoC** principles

- Message passing interface with priorities: computation can continue while message is transmitted to destination

- Incorporation of flow control by backpressure signaling to avoid overload and loss

- Lightweight one-word header, which contains destination, message type, and context ID for fast flow-through processing

| SoC main components                                            | Area [mm²]                    |           | Frequency [MHz] |      |

|----------------------------------------------------------------|-------------------------------|-----------|-----------------|------|

|                                                                | 130nm                         | 90nm      | 130nm           | 90nm |

| 32 Cores [N-Core]                                              | 32 x 0.16                     | 32 x 0.12 | 205             | 285  |

| 8 switch-boxes [with 5 ports]                                  | 8 x 1.129                     | 8 x 0.53  | 560             | 650  |

| 32 local RAMs, (32 KB)<br>+ 8 local packet buffers (2 x 16 KB) | 32 x 0.875<br>+ 8 x 2 x 0.466 |           |                 | 450  |

| 8 local on-chip busses                                         | 8 x 0.05                      | 8 x 0.02  | 211             | 290  |

| Total                                                          | 50.01                         | 43.7      | 205             | 285  |

## **NOVA Socket concept**

- Homogeneous interface

- Separation of IP-specific interfaces from interconnect and memory interfaces

# **Status/Next Steps**

(4)

- Verification of approach and concepts

- Currently implementing initial NOVA platform prototype comprising approx. 20 message passing clients

- Application-driven analysis using system-level benchmark

- Mapping IP-DSLAM reference application to the platform

- Enables detailed quantitative exploration of design trade-offs

- Demonstrator at CeBIT 2006 trade fair

- Evaluation of GigaNoC for larger systems [2]

# Partners/Funding

### Infineon Technologies

- Communications, Access System Engineering (COM AC SE NP)

- 81726 Munich, Germany

- E-mail: Christian.Sauer@infineon.com

### **Heinz Nixdorf Institute**

- University of Paderborn, System and Circuit Technology

- Fürstenallee 11, 33102 Paderborn, Germany

- E-mail: niemann@hni.upb.de

This project is supported, in parts, by the research grants GigaNetIC and PlaNetS of the German government (BMBF).