# STUDY OF LOW POWER, LOW VOLTAGE ANALOG REALIZATION OF PROGRAMMABLE CELLULAR NEURAL NETWORKS

$\mathcal{B}y$

NASIR ALI KANT

Department of Electronics and Instrumentation

Technology,

University of Kashmir,

Hazratbal, Srinagar,

190006

January 2014

A Dissertation submitted to the Faculty of Applied Sciences and Technology in partial fulfilment of the requirement for the Degree of Master of Philosophy in Electronics.

# Certificate

This is to certify that *Mr. Nasir Ali Kant* has worked under my supervision for the dissertation entitled, "*Study of Low Power, Low Voltage Analog Realization of Programmable Cellular Neural Networks*" and the work is truly commendable of consideration for the award of the degree of Masters of Philosophy in Electronics.

### It is further certified that

- (i) The dissertation embodies the work of the candidate.

- (ii) The candidate worked under my supervision for the period required under statues.

- (iii) The candidate has put in the required attendance in the Department.

- (iv) The conduct of the candidate remained very good during the period of the research.

(Prof. N. A. Shah) (Prof. G. M. Bhat)

Supervisor Head of Department,

Dept. of Electronics and

Department of Electronics and

Instrumentation Technology Instrumentation Technology

University of Kashmir University of Kashmir

Srinagar-190006 Srinagar-190006

Dated: Dated:

### Candidate's Declaration

I hereby declare that the work presented in this dissertation "Study of Low Power, Low Voltage Analog Realization of Programmable Cellular Neural Networks" in partial fulfilment of the requirements for the degree of Masters of Philosophy and submitted in the Department of Electronics and Instrumentation Technology, Faculty of Applied Sciences and Technology, University of Kashmir, Srinagar, has entirely been done by me under the supervision of Prof. N. A. Shah.

I, further, declare that the work contained in the dissertation is the original research work conducted by me and has not been submitted in part or full, to any other University or Institute for the award of any degree.

(Nasir Ali Kant)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(Prof. N. A. Shah)

Supervisor

Department of Electronics and Instrumentation Technology

University of Kashmir Srinagar-190006

Dagaarah Cahalar

The Viva-voce examination of Mr. Nasir Ali Kant, Research Scholar,

has been held on.....

Supervisor

Head of the Department

**External Examiner**

## Acknowledgements

I am thankful to Almighty Allah for guiding me to the right path & for giving me the strength to undertake this work....

Words are often too less to reveal one's deep regards, I take the opportunity to express my deep sense of gratitude and respect to all those who helped me in this work.

This work would not have been possible without the encouragement and able guidance of my supervisor, Prof. N. A. Shah. His enthusiasm and optimism made this experience really enjoyable. I would like to express my deep sense of gratitude towards Prof. G. M. Bhat, Professor and Head, Department of Electronics and Instrumentation Technology, University of Kashmir for his support, guidance & encouragement and for providing necessary facilities in the Department. Further, I wish to express my appreciation to Dr. Farooq Ah. Khanday Asst. Professor Dept. of Electronics & I.T. University of Kashmir for his support & constant encouragement. Special thanks to faculty members of the Department of Electronics, University of Kashmir: Dr. M. Tariq Banday, Dr. Shabir Ahmad Parah, Dr. Javaid Ahmed Sheikh and others who directly or indirectly helped me in the work. Very special thanks to all the technical and non-teaching staff of the department for their valuable encouragement and support. I would take opportunity to thank the research scholars of the Department of Electronics, University of Kashmir: Mr. M. Rafiq Beigh, Mr. Imran Yaseen, Mr. Zubair Ahmad Bangi, Mr Javeed Iqbal and others for their assistance, encouragement and discussions. I would also like to thank all my friends and relatives for their valuable suggestions and support. I am highly indebted to my Family, my Sister and her family for their unconditional support and love.

### Abstract

"Neural network" is the term used to refer to a circuit of neurons that perform information processing. They are highly complex, nonlinear systems (with huge degree of freedom) which employ different principles of information processing than those of the conventional algorithmic computation of modern computer systems. The basic computational units of neural networks are neurons which are simulated mathematically on a computational substrate (e.g. a standard computer, an electronic circuit, etc.).

Cellular Neural Network (CNN) being the derivative of Artificial Neural Network (ANN) is also a parallel computing paradigm with the difference that communication is allowed between neighbouring units only. CNNs are characterized by simplicity of operation. The network consists of a large number of nonlinear processing units (cells) that are equally spread in the space. Each cell has a simple function that takes an element of a topographic map and then interacts with all cells within a specified sphere of interest through direct connections. CNNs have attracted the attention of a wide variety of scientists, due to their intrinsic parallel computing power. They find their use in different fields e.g., the fields of image and video processing, robotics.

A variety of problems can be solved with neural networks in the areas of Image Processing, Control Systems etc. and most of them have been demonstrated by employing their software based designs. While designing the software based solutions, many special features of neural networks does not persist as the employed machines perform many of their processes in a sequential manner. Therefore to fully utilize the application potential of ANNs, they need to be designed in hardware. Despite many years of studies involving neural networks, it is only due

to advancement in programmable hardware that actual implementation for study and their applications have become practical. There are many examples of neural network codes running on von Neumann computers, but as per the published reports, there is still unavailability of commercial Neural Networks (NNs) implemented in hardware.

In the hardware implementation of neural network, it is important to consider flexibility and power consumption in order to satisfy a wide range of applications. So designers focus on circuits which consume very little power per connection allowing for a high number of connections per neuron. The hardware implementation of the neural networks can be achieved through analog or digital means. However, analog realization of the neural networks provides a fast and power efficient realization compared to the digital realization as the later employ digital processors which often work in sequential way. In addition, the flexibility in analog hardware is added by employing electronic tunablity feature.

According to data that provides information about the near future of semiconductor technology, International Technology Roadmap for Semiconductors (ITRS), in 2013-14, the supply voltage of digital circuits in 32 nm technologies will be 0.5 V. Therefore, the trend for the implementation of analog integrated circuits is the usage of low-voltage building blocks that use a compatible single low-voltage power supply.

In order to achieve all the features of contemporary hardwired neural networks, companding (compression-expansion) technique is a very promising subclass of Low-Voltage Low-Power circuit design technique. The technique has three types: the Log-Domain (LD), the Square-Root Domain (SRD) and the Sinh-Domain (SD). The basic operation in all the three types is same i.e. the input current is first

converted into a compressed voltage, the compressed voltage is then processed by the companding core and finally the output compressed voltage is converted into a linear current. The companding technique provides the features of: resistor less designs, electronic tunability and capability of operation low-voltage environment which are the primary requirements of the contemporary Very Large Scale Integration (VLSI) design. Among the three companding techniques, the inherent class-AB operation of SD technique offers the capability for handling signals greater than the bias current, leading to a further power saving.

Therefore, the present investigation was primarily concerned with the study and design of low-voltage and low-power companding ANNs. The work includes the study about: the building blocks required in implementing low-voltage and low-power Sinh-Domain Companding ANNs; the implementation of various analog activation functions for ANNs.

The low-voltage design of three Activation Functions (AFs), Tanh, Unipolar Sigmoidal, and Bipolar Sigmoidal, using SD technique were designed. The SD blocks have been implemented using MOS transistors in weak inversion which ensures the reduction of supply voltage operation of the circuits in addition to that provided by the companding technique itself. The AFs are subsequently used to design the neural network which have been trained in MATLAB environment to perform AND, OR, NOT, NAND, NOR, and XOR logic functions.

The investigations on these designs are based on the SPICE simulations using model parameters of the BSIM 0.35µm CMOS process MOS transistors. The performance of each circuit has been validated by comparing the characteristics obtained using simulation with the results present in the open literature.

The proposed designs could not be realized in silicon due to non-availability of foundry facility at the place of study.

# Table of Contents

| Certif | icate                                                            | ii   |

|--------|------------------------------------------------------------------|------|

| Candi  | date's Declaration                                               | iii  |

| Ackno  | owledgements                                                     | iv   |

| Abstra | act                                                              | v    |

| Table  | of Contents                                                      | ix   |

|        | f Figures                                                        |      |

|        | f Tables                                                         | xiii |

| Chapt  |                                                                  |      |

| 1.1    | Introduction                                                     |      |

| 1.2    | Outline of the dissertation                                      | 4    |

| Chapt  |                                                                  |      |

| 2.1    | Neural Networks                                                  |      |

| 2.2    | The Biological Inspiration for Artificial Neural Networks (ANNs) |      |

| 2.3    | The Biological Neural Networks                                   |      |

| 2.4    | Artificial Neural Networks                                       |      |

| 2.5    | Cellular Neural Networks (CNNs)                                  |      |

| 2.5    | 5.1 Standard CNN Architecture                                    | 15   |

| 2.5    | S.2 Sphere of Influence (Neighbourhood)                          | 15   |

| 2.5    | 5.3 Standard CNN Equations                                       | 16   |

| 2.5    | 5.4 Cloning Template                                             | 20   |

| 2.5    | 5.5 Boundary Conditions                                          | 22   |

| 2.6    | Discrete-Time (DT) CNN                                           | 25   |

| 2.7    | Full Signal Range CNN                                            | 28   |

| 2.8    | Time-Derivative CNN                                              | 29   |

| 2.9    | Application of ANNs                                              | 29   |

| 2.10   | Conclusion                                                       | 31   |

| Chapt  | er 3                                                             |      |

| 3.1    | Introduction                                                     | 32   |

| 3.2    | Hardware implementation Artificial Neural Networks               | 33   |

| 3.2    | 2.1 Analogue Artificial Neural Networks                          | 33   |

| 3.2    | 2.2 Digital Artificial Neural Networks                           | 33   |

| 3.2    | 2.3 Hybrid Artificial Neural Networks                            | 34   |

| 3.3    | Hardware Implementations of CNN                                  | 34   |

| 3.4        | Conclusion                                                     | 42          |

|------------|----------------------------------------------------------------|-------------|

| Chapt      | ter 4                                                          |             |

| 4.1        | Introduction                                                   | 43          |

| 4.2        | Companding Techniques                                          | 46          |

| 4.3        | Types of Companding                                            | 46          |

| 4.4        | Sinh-Domain (SD) Companding                                    | 48          |

| 4.4        | 4.1 Sinh-Cosh (SC) transconductor cells                        | 48          |

| 4.4        | 4.2 Low-Voltage Two-Quadrant SD Divider                        | 52          |

| 4.4        | 4.3 SD Summation/Subtraction Block                             | 53          |

| 4.4        | 4.4 SD Integrators                                             | 54          |

| 4.5        | Conclusion                                                     | 55          |

| Chapt      | ter 5                                                          |             |

| 5.1        | Introduction                                                   | 57          |

| 5.2        | Neural Network Design                                          | 58          |

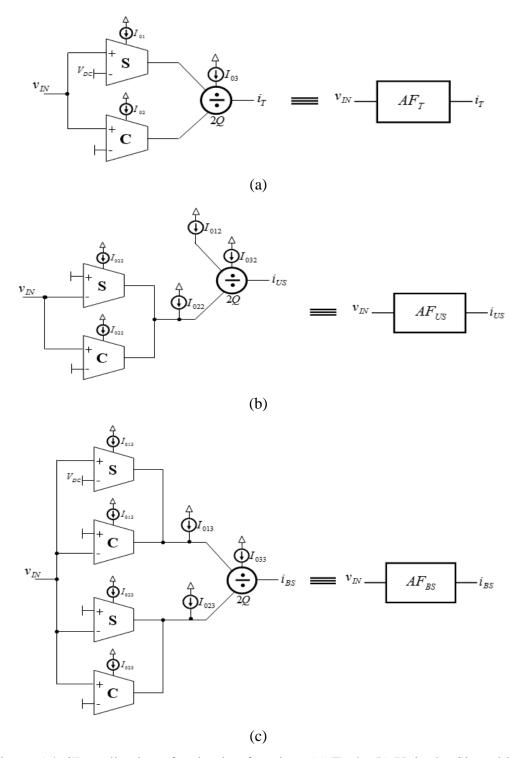

| 5.3        | SD design of activation function and multi-layer perceptron    | 60          |

| 5.3        | 3.1 SD Building Blocks                                         | 60          |

| 5.3        | 3.2 SD Realization of Activation Functions                     | 62          |

| 5.3        | 3.3 SD Realization of Single Neuron Network and Multi-Layer Po | erceptron63 |

| 5.4        | Simulation Results                                             | 65          |

| 5.5        | Conclusion                                                     | 72          |

| Chapt      | ter 6                                                          |             |

| 6.1        | Conclusion                                                     | 74          |

| 6.2        | Suggestions for Future Work                                    | 76          |

| Appe       | endix                                                          |             |

| A:         | List of Publications                                           | 77          |

| <i>B</i> : | Bibliography                                                   | 78          |

| C·         | Nomenclature                                                   | 115         |

# Table of Figures

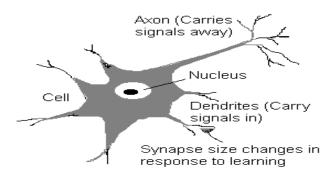

| Figure 2.1: A simple Neuron                                                               | 7  |

|-------------------------------------------------------------------------------------------|----|

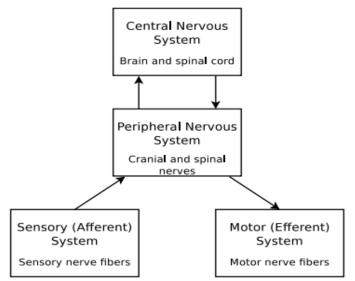

| Figure 2.2: Simplified structure of the nervous system in vertebrate animals              | 10 |

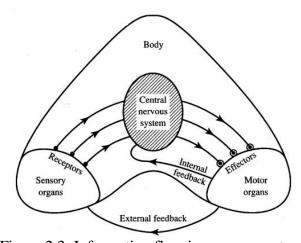

| Figure 2.3: Information flow in nervous system                                            | 11 |

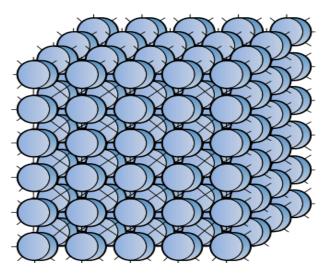

| Figure 2.4: CNN, where the globes represent cells and the links represent direct coupling | 15 |

| Figure 2.5: Different r-neighbourhoods for the centre cell (black circle)                 | 16 |

| Figure 2.6: (a) Sigmoid function and (b) piece-wise linear function                       | 18 |

| Figure 2.7: When $r = 1$ , boundary cells coincide with edge cells (a) but for            |    |

| 1 boundary cells (light grey) are not located on the edges only (b)                       | 23 |

| Figure 2.8: In periodic boundary condition the CNN is joined onto itself                  | 24 |

| Figure 2.9: Block diagram of a CT CNN cell circuitry based on Chua-Yang's model           | 25 |

| Figure 2.10: A schematic diagram illustrating a DT-CNN cell                               | 27 |

| Figure 2.11: (a) Block diagram of CNN cell circuitry using the FSR model,                 |    |

| (b) Integrator with saturation                                                            | 28 |

| Figure 3.1: Alternative models of CNN cell:                                               |    |

| (a) Chua & Yang's model, with bias represented as voltage instead of current              | 37 |

| (b) dual model with weighting at the output                                               | 37 |

| Figure 3.2: Cruz & Chua's CNN cell                                                        | 38 |

| Figure 3.3: Equivalent inner circuit structures                                           | 39 |

| Figure 3.4: Balanced inner circuit structure                                              | 39 |

| Figure 3.5: Balanced variable conductance block                                           | 39 |

| Figure 3.6: (a) lossy integrator; (b) half-clock delay in current mode                    | 40 |

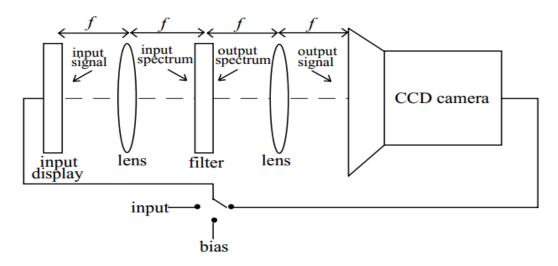

| Figure 3.7: Optical realization of a DT-CNN                                               | 42 |

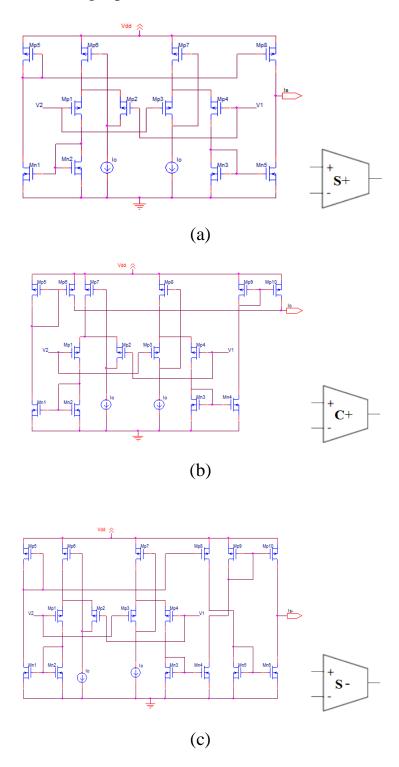

| Figure 4.1: (a) Positive Sinh                                                             | 49 |

| (b) Positive Cosh                                                                         | 49 |

| (c) Negative Sinh                                                                         | 49 |

| (d) Negative Cosh transconductor cell                                                     | 50 |

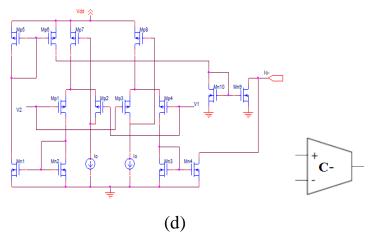

| Figure 4.2: Realization of the SD operators: (a) SINH-1 and (b) SINH                      | 51 |

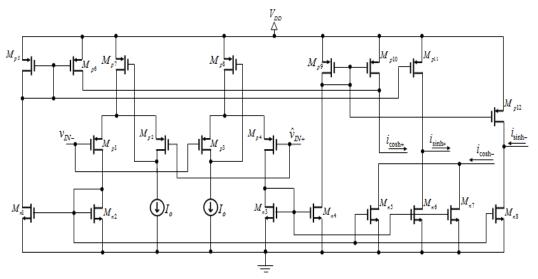

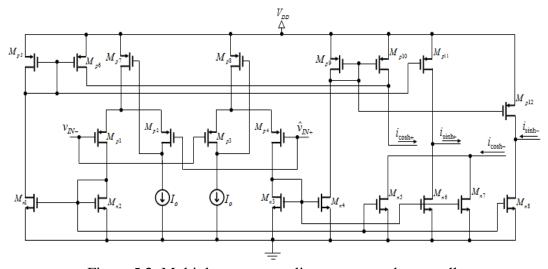

| Figure 4.3: Multiple output non-linear transconductor cell                                | 52 |

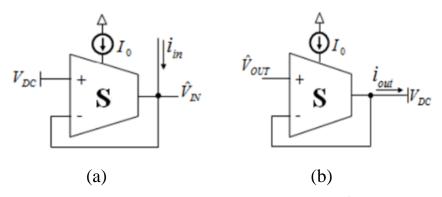

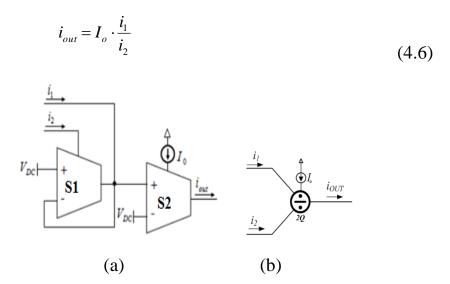

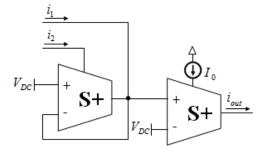

| Figure 4.4: (a) Two-quadrant multiplier/divider and (b) associated symbol                 | 53 |

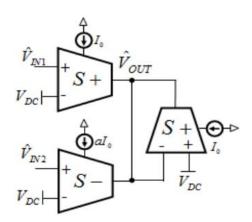

| Figure 4.5: SD algebraic summation/subtraction block with weighted input                  | 53 |

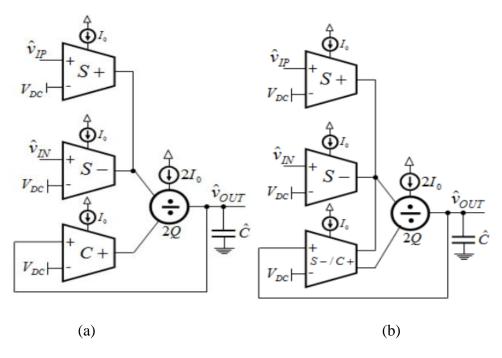

| Figure 4.6: SD Integrators. (a) Two-input SD lossless integrator                          | 55 |

| (b)Two input SD lossy integrator                                                          | 55 |

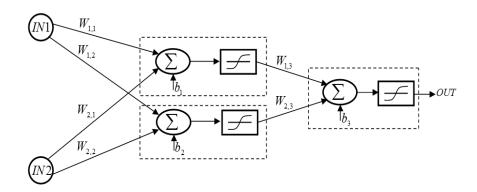

| Figure 5.1: A Multilayer Perceptron                                                       | 58 |

| Figure 5.2: Multiple output non-linear transconductor cell                                | 61 |

| Figure 5.3: Two-quadrant multiplier/divider                                               | 61 |

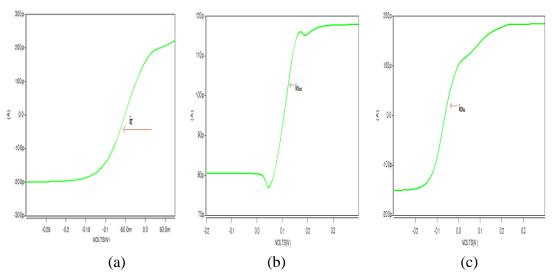

| Figure 5.4: SD realization of activation functions:                                       |    |

| (a) Taul                                                                                  | (0 |

| (b) Unipolar Sigmoidal                                                                                             |

|--------------------------------------------------------------------------------------------------------------------|

| (c) Bipolar Sigmoidal                                                                                              |

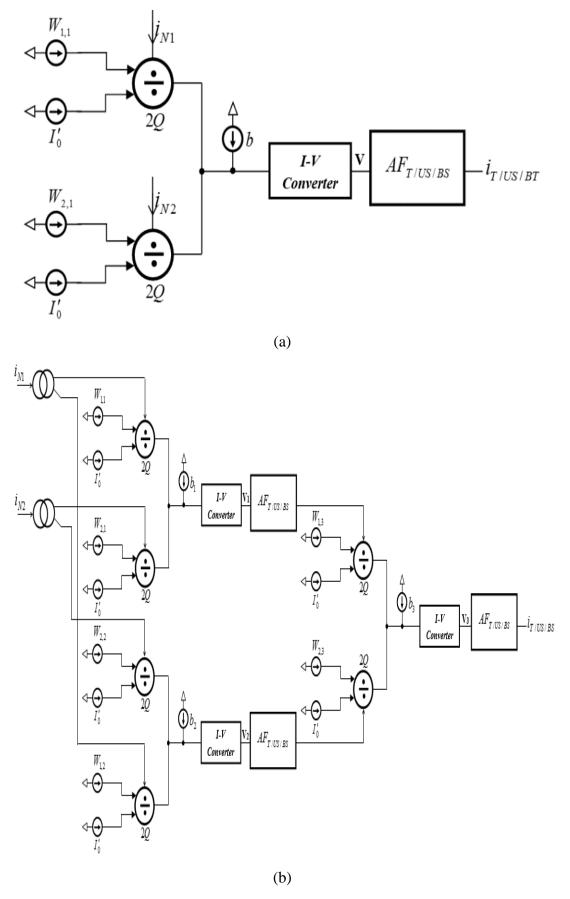

| Figure 5.5: SD realization of:                                                                                     |

| (a) Single neuron Network                                                                                          |

| (b) Multi-layer perceptron                                                                                         |

| Figure 5.6: Input/output characteristics of activation functions                                                   |

| (a) Tanh (b) Unipolar Sigmoidal (c) Bipolar Sigmoidal 66                                                           |

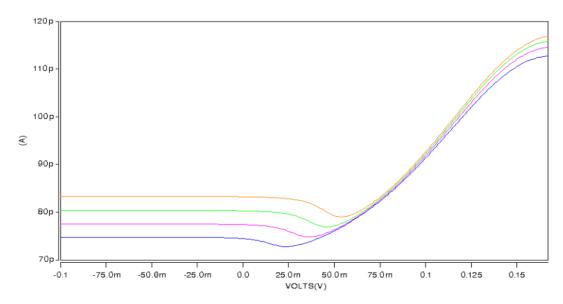

| Figure 5.7: Demonstration of electronic tunability of saturation limits for Unipolar Sigmoidal Activation Function |

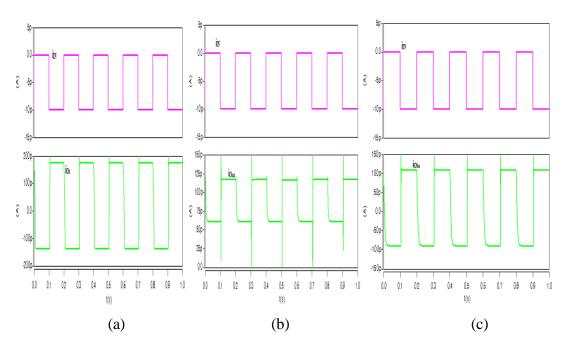

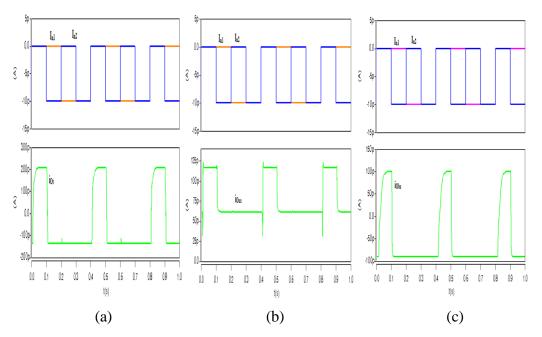

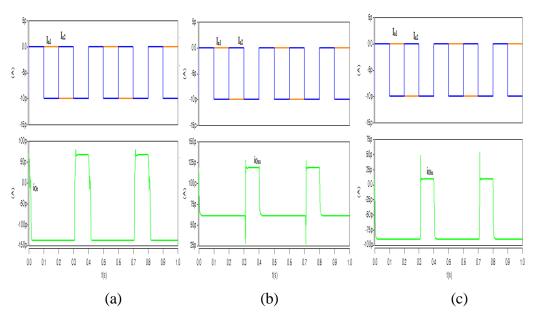

| Figure 5.8: Simulation results of trained single neuron network for NOT function                                   |

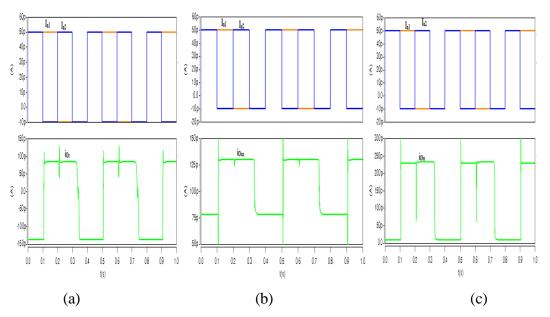

| (a) Tanh function (b) Sigmoidal function (c) Bipolar Sigmoidal function67                                          |

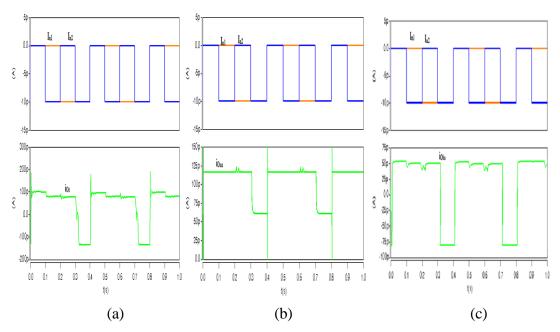

| Figure 5.9: Simulation results of trained single neuron network for AND function                                   |

| (a)Tanh function (b) Sigmoidal function (c) Bipolar Sigmoidal function                                             |

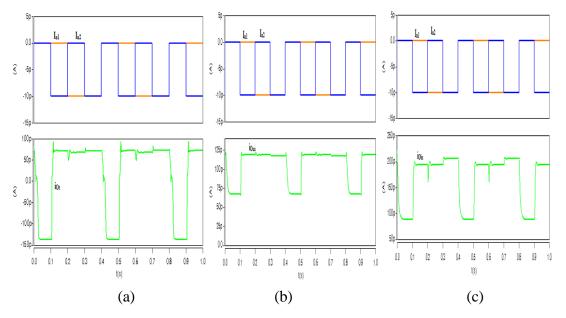

| Figure 5.10: Simulation results of trained single neuron network for OR function                                   |

| (a)Tanh function (b) Sigmoidal function (c) Bipolar Sigmoidal function                                             |

| Figure 5.11: Simulation results of trained single neuron network for NAND function                                 |

| (a) Tanh function (b) Sigmoidal function (c) Bipolar Sigmoidal function69                                          |

| Figure 5.12: Simulation results of trained single neuron network for NOR function                                  |

| (a) Tanh function (b) Sigmoidal function (c) Bipolar Sigmoidal function69                                          |

| Figure 5.13: Simulation results of trained single neuron network for XOR function                                  |

| (a) Tanh function (b) Sigmoidal function (c) Bipolar Sigmoidal function70                                          |

# Table of Tables

| Table 5.1: Bias scheme for the circuits.                                                        | 71  |

|-------------------------------------------------------------------------------------------------|-----|

| Table 5.2: The aspect ratio of MOS transistors employed of the non-linear transconductor        | 71  |

| Table 5.3: Weights and bias for different activation functions for:                             |     |

| (a) NOT                                                                                         | 71  |

| (b) AND, OR, NAND and NOR                                                                       | 71  |

| (c) XOR                                                                                         | .72 |

| Table 5.4: Total power dissipation of the SD neural network trained for various logic functions |     |

| employing the three activation functions                                                        | 72  |

### 1.1 Introduction

In spite of the fact that different aspects of computational complexity have given rise to different complex computer architectures, the concept of scientific computing has not changed during the last sixseven decades. A computer is still built with stored programmability, i.e. with the algorithm as the underlying mechanism [1]. When Alan Turing introduced his abstract machine in 1936 it was meant to consist of a tape of symbols, a header to read/write the symbols, a state register and finally an action table that tells the machine what to do next. About ten years later, the foundation established by Turing was adopted in von Neumann's computer architecture. In general, a von Neumann machine stores both the program and the data in a memory that can be unified as in a Princeton architecture or separate as in Harvard architecture. A control unit features a program counter that keeps track of how instructions are executed on the arithmetic and logic unit. The program is executed sequentially in line with human thinking, which is the main reason for von Neumann machine to gain worldwide acceptance and to quickly become the fundament of future digital computing devices [2]. But being sequential, architectures based on von Neumann machine are characterized by low utilization of the computational components. As the execution of each instruction is divided into a number of stages, only the components belonging to the current stage are active while all other units in the architecture remain idle. Furthermore, we know nowadays engineering tasks are characterized by the high complexity of the underlying algorithms. Here, large amounts of information are handled in real-time hence conventional digital computation methods have run into a serious speed bottleneck due to their serial nature.

Also due to the Sensor revolution which means that cheap sensor and Micro-Electro-Mechanical System (MEMS) arrays are proliferating in almost all the conceivable forms. Thousands and millions of generically analog signals are produced waiting for processing. A new computing paradigm is needed. The cited technology assessment reads:

"The long-term consequence of the coming sensor revolution may be the emergence of a newer analog computing industry in which digital technology plays a mere supporting role, or in some instances plays no role at all [3].

For processing analog array signals, the revolutionary Analogic (generic terms for analog and logic) cellular computer paradigm is a major candidate. The core of this computer is a nonlinear cellular neural network (CNN), an array of analog dynamic processors or cells (called neurons). The key features of neural networks are asynchronous parallel processing, continuous-time dynamics, and global interaction of network elements [4]. At the same time, Analogic CNN computers mimic the anatomy and physiology of many sensory and processing organs with an additional capability of stored programmability.

CNNs were, originally proposed by Chua and Yang in 1988 [5], and since then they have been the object of a great deal of research work, concerning both theoretical studies and application-oriented circuit implementations. CNNs are well suited for high-speed image processing tasks; their reported applications cover a much wider range of activities, such as motion detection, classification and recognition of objects, associative memory, solution of partial differential equations, statistical and non-linear filtering, etc. [6]. Recent studies on optical and nano-scale implementations open up new horizons on the atomic and molecular levels. Unlike cellular automata, CNN host processors

accepting and generating analog signals, the time is continuous, and the interaction values are also real values. Moreover, CNN becomes a rigorous framework for complex systems exhibiting emergent behaviour and the various forms of emergent computations. This allows not only modelling but also engineering of complex systems.

networks without However. neural learning rather are uninteresting. If the weights of a network were fixed from the beginning and were not to change, neural networks could be implemented using any programming language in conventional computers. But the main objective of building special hardware is to provide a platform for efficient adaptive systems, capable of updating their parameters in the course of time. Furthermore hardware neural networks are much faster compared to their software counterparts owing to the fact that the feature of full parallelism is captured by means of hardware realizations only. CNNs are particularly well suited for an analog VLSI implementation. The recent extension towards the definition of a programmable analogic array computer, the CNN Universal Machine, has opened many new application fields which can be handled through spatial and temporal task sequencing controlled by a stored program [6]. A key feature of CNNs is their potential for high operation speed in the processing of array signals.

Typical CNN chips may contain up to about 200 transistors per pixel (including sensory and processing devices) [7], [8]. On the other hand, practical applications require large enough grid sizes; around 100×100. Thus, CNN designers must confront a large level of complexity. To achieve an acceptable resolution with standard design procedures, a large cell-grid size is required, which results in

considerable area occupation, low production yield and high-power consumption [9].

As more and more complex systems are being integrated on the same chip, area minimization is becoming of primary importance. As the size of batteries is now becoming the limiting factor, it is not sufficient to reduce the size of bulky components by integrating them, the reduction of the power dissipation is also very important. As a consequence, the key point is to develop, simultaneously, both low-voltage and low-power operating integrated circuits in order to reduce the battery size and chip area.

In this research program I have tried to achieve the Low-Voltage Low-Power analog CNN design and in this respect Low-Voltage Lowpower implementation of various analog activation functions were designed in Sinh-Domain (SD) technique.

# 1.2 Outline of the dissertation

In this dissertation issues relating to the hardware implementation of an ANN in low power and low voltage design regimes are discussed. The aim is to present a potential solution to the problem of realizing artificial neurons in hardware since most work is currently conducted via software synthesis and modelling.

The outline of the dissertation structure is consequently presented below.

A general overview about neural networks is given in Chapter 2. The biological inspiration for designing ANNs is also presented. Besides CNNs are discussed in details and different types of CNNs is also presented in the chapter. Furthermore the importance of ANNs is also given at the end of the chapter.

The need for the hardware implementation of ANNs is discussed in Chapter 3. Besides different types of hardware implementation of ANNs and the complications in hardware implementation are also mentioned. Furthermore the special emphasis is lead on the hardware implementation of CNNs along with the different approaches of achieving its hardware.

Chapter 4 introduces to Low-Voltage Low-Power Analog Design techniques along with a brief discussion on companding techniques i.e. Log-Domain (LD), Square-Root-Domain (SRD) and Sinh-Domain (SD). Towards the end, the operators and building blocks required to design SD classification are discussed in detail.

Chapter 5 includes the designing of analog activation functions (unipolar, bipolar sigmoidal and Tanh) utilizing SD companding technique. Besides this the designed activation functions are used in designing single-layer and two-layer perceptron whose weights are trained in such a manner that the network implements various logic gate functions.

### 2.1 Neural Networks

"Neural network" is the term used to refer to a circuit of neurons that performs information processing. They are highly complex, nonlinear systems (with huge degree of freedom) which employ different principles of information processing than those of the conventional algorithmic computation of modern computer systems. The basic computational units of neural networks are neurons which are simulated mathematically on a computational substrate (e.g. a standard computer, an analogue circuit, etc.).

# 2.2 The Biological Inspiration for Artificial Neural Networks (ANNs)

The roots and inspiration for ANNs are drawn from biological nervous system. Such biological system or wetware consists of a multitude of simple processing elements which are connected together in a massively parallel architecture.

The human brain is indeed a triumph of nature as it consists of many neurons of different varieties but the general format remains almost the same and is illustrated in Figure 2.1. Neurons are cells that send and receive electro-chemical signals to and from the brain and nervous system. The neuron consists of a cell body (or soma) with branching dendrites (signal receivers) and a projection called an axon, which conduct the nerve signal. The terminating points of the divided axon form transmitting connections to the dendrites of other neurons or connect directly to the neurons via synaptic junctions or synapses. The axon terminals transmit the electro-chemical signal through synapse.

Figure 2.1: A simple Neuron.

A complex chemical process is involved in signalling from one neuron to another with chemicals released from the sending side of the synapse. The effect of these chemical releases is to alter the electrical potential within the cell body. If the cell potential reaches certain given level, the neuron is activated releasing a fixed strength and duration signal along the axon to other neurons. A recovery period follows before the neuron is able to fire again once it is fired. Individual cells can achieve limited task, but the collective behaviour of these structures of biological formations performs a useful task in the embodying organism. Conservatively, it has been estimated that there are at least 10<sup>11</sup> neurons in the human brain with 10<sup>14</sup> interconnections.

Also an important point about neural networks (NNs) which needs to be mentioned here is that they are not a static i.e., the strengths of inter connections vary with time, new ones are formed and old ones may decay away. Due to the large quantity of parallelism there is redundancy built in to the system and a level of fault tolerance is available. Rather than being explicitly programmed, a NN evolves to perform an action by learning and adaption. Thus, given that the network changes through damage or the network has to increase its functionality, it is able to adapt to the new situation.

Given the above rudimentary description of a neuron's behaviour two main approaches can be adopted for the study and development of ANNs. One approach is to study, model and possibly build analogous devices as accurately as possible. The second is to draw upon ideas from actual systems and develop simple processing element exemplar with in a massively parallel architecture. The former approach is normally adopted by biologists and psychologists in order to determine the functioning of the brain and nervous system. The latter approach is usually followed by engineers in pursuit of a system which will perform a computationally useful task.

### But few important questions:

- ➤ Why study and develop Artificial Neural Networks at all?

- ➤ What task or tasks could they be used to perform?

- ➤ What benefit can they offer beyond a traditional von Neumann architecture machine?

By answering the latter two questions, hopefully a more complete reason for the study of ANNs will become apparent. Within a traditional computer, a failure in a processing section is catastrophic in terms of system performance; this is not necessarily the case with a NNs. Benefits of ANN are their potential robustness and only a gradual degradation in performance, but not the network stops working, if an area of the network becomes damaged. Furthermore, certainly for rapid exact algorithmic or mathematical operations a traditional computer is excellent but this is not the case for noisy, inexact information processing. Also as it has been stated that much of the interest and power of NNs is the ability they have to adapt and learn from the data presented to them. So the ANN designed will not need to be reprogrammed once it is trained which is not the case with simple computer. The ANN has recently been applied in process control,

identification, diagnostics, character recognition, sensory prediction, robot vision, and forecasting [10-16] etc.

## 2.3 The Biological Neural Networks

The networks formed by biological neurons which are connected to carry out the functionalities typical of the nervous system in biological life forms are referred as biological neural networks However, not all multicellular life forms on the earth have a nervous system. For example, sponges are very old life forms comprising colonies of cells which do not have a nervous system to allow electrical communication between the various parts of the body [17]. In particular the presence and the complexity of the nervous system have evolved during the various historical eras.

In the evolutionary scale, with regard to the nervous system, after the sponges it is possible to find the "Radiata" branch: life forms which have a radial symmetry. In these life forms it is possible to identify a "top" and a "bottom", but not "left" and "right" sides; jellyfish are an example of this class. These life forms have a simple nerve net which allows reactions to external [18].

Life forms having the most complex neural system belong to the "Bilateria" branch. These are the life forms which are (approximately) symmetric with respect to a longitudinal axis, and for which it is possible to define a "left" and a "right" side in addition to a "top" and a "bottom". This branch includes the human race which has the most complex nervous system known in nature [19], [20].

More generally, in the "Bilateria" branch, the "Vertebrate" subphylum occurs. In individuals of this subphylum, the nervous system can be divided into two interconnected halves [21]: the peripheral nervous system and the central nervous system. However, these two

parts differ only from an anatomical point of view as depicted in Figure 2.2.

Figure 2.2: Simplified structure of the nervous system in vertebrate animals.

Considering the human nervous system, human brain consists of  $10^{11}$ computing elements approximately called neurons. communicate through a connection network of axons and synapses having a density of approximately 10<sup>4</sup> synapses per neuron. The hypothesis regarding the modelling of the natural nervous system is that neurons communicate with each other by means of electrical impulses [22]. The neurons operate in a chemical environment that is even more important in terms of actual brain behaviour. The brain thus can be considered to be a densely connected electrical switching network conditioned largely by the biochemical processes. The vast NN has an elaborate structure with very complex interconnections. The input to the network is provided by sensory receptors. Receptors deliver stimuli both from within the body, as well as from sense organs when the stimuli originate in the external world. The stimuli are in the form of electrical impulses that convey the information into the network of neurons. As a

result of information processing in the central nervous systems, the effectors are controlled and give human responses in the form of diverse actions. We thus have a three-stage system, consisting of receptors, neural network, and effectors, in control of the organism and its actions.

A lucid, although rather approximate idea, about the information links in the nervous system is shown in Figure 2.3. As we can see from the figure, the information is processed, evaluated, and compared with the stored information in the central nervous system. The necessary commands are generated there and transmitted to the motor organs. Notice that motor organs are monitored in the central nervous system by feedback links that verify their action. The implementation of commands is controlled with the help of both internal and external feedbacks. As can be seen, the overall nervous system structure has many of the characteristics of a closed-loop control system.

Figure 2.3: Information flow in nervous system.

### 2.4 Artificial Neural Networks

The simplest definition of a neural network, more properly referred to as an 'artificial' neural network (ANN), is provided by the inventor of one of the first neuro-computers, *Dr. Robert Hecht-Nielsen* [23]. He defines a neural network as:

"...a computing system made up of a number of simple, highly interconnected processing elements, which process information by their dynamic state response to external inputs."

There are a number of different answers possible to the question of how to define artificial neural networks. At one extreme, the answer could be that these are simply a class of mathematical algorithms, since a network can be regarded essentially as a graphic notation for a large class of algorithms. Such algorithms produce solutions to a number of specific problems. At the other end, the reply may be that these are synthetic networks that emulate the biological neural networks found in living organisms. In light of today's limited knowledge of biological neural networks and organisms, the more plausible answer seems to be closer to the algorithmic one. Thus we can say ANNs are the result of academic investigation that uses mathematical formulations to model nervous system operation. They are circuits made by the interconnection of artificial neurons, which mimic the behaviour of biological neurons. The circuits or simulators comprise hardware (analogue or digital) or software (digital) components which compute mathematical models of biological neurons and biological synapses.

Our knowledge about actual brain functions is still limited, and no model has been successful in duplicating the performance of the human brain. Despite ANNs have undoubtedly been biologically inspired, but the close correspondence between the biologic neural systems and ANN is still weak. Vast discrepancies exist between both the architectures and capabilities of natural and artificial neural networks. Therefore, the brain has been and still is only a metaphor for a wide variety of neural network configurations that have been developed [24].

Talking about the designing of ANNs, different approaches have been adopted resulting in different architectures like Perceptron, Madaline, and Hopfield Networks etc. One class of architectures that are designed taking the inspiration from the neural networks with the difference that communication is allowed between neighbouring units only is called as Cellular Neural Networks (CNNs). They are the class of neural networks whose concept was first introduced by Chua and Yang, in 1988, to efficiently perform large time-consuming tasks in real-time by using an array of simple, nonlinearly coupled dynamic circuits [5].

### 2.5 Cellular Neural Networks (CNNs)

Cellular Neural Network (CNN) is novel class of information-processing systems. The concept of CNN rests on two major sources of inspiration. The architecture possesses some of the key features of NNs [25], such as continuous time dynamics and global interaction of the network elements, which allows for real-time signal processing. On the other hand, it inherits the feature of local interconnectivity from the world of Cellular Automata [26], which makes it suitable for VLSI implementations.

Cellular Neural Networks are characterized by simplicity of operation. The network consists of a large number of nonlinear processing units; called cells; that are equally spread in the space. Each cell has a simple function that takes an element of a topographic map and then interacts with all cells within a specified sphere of interest through direct connections. Due to their intrinsic parallel computing power, CNNs have attracted the attention of a wide variety of scientists in, e.g., the fields of image and video processing, robotics and higher brain functions [27–29].

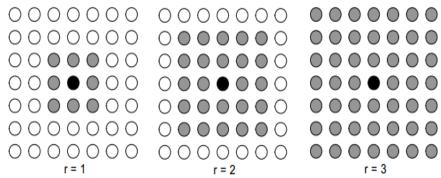

Since its inception, cellular network has been thoroughly investigated. Two-dimensional networks in which each cell is connected physically only to its eight nearest neighbours are studied in great detail in the literature, although cells in cellular network can be arranged in several spatial configurations. The radius of effect or the radius of neighbourhood  $r_N$  determines how a particular cell is affected by the neighbouring cells. For example, for  $r_N = 1$  the neighbourhood includes the cell itself and its eight adjacent cells which directly affect it; for  $r_N = 2$  the neighbourhood includes the cells mentioned for  $r_N = 1$  plus 16 additional cells which indirectly affect the central cell; for  $r_N = 3$  the neighbourhood includes the cells mentioned for  $r_N = 2$  plus 24 additional cells which again indirectly affect the central cell; and so on. In other words,  $r_N = 1$ , 2, and 3 neighbourhoods can be respectively called as 3×3, 5×5 and 7×7 neighbourhoods. Each cell has its own input, state, and output. Depending on the nature of these variables (e.g. continuous vs. discrete) and the way in which the dynamics of each cell is defined, the cellular network receives different names in the scientific literature (continuous and discrete-time Chua-Yang CNN [5], full signal range CNN [30], time-derivative CNN [31]).

In upcoming section, the network structure is introduced, as it eases the understanding of CNNs basic equations, and is followed by a brief description of CNN models: Chua and Yang model that is also referred to as Continuous-Time CNN (CT-CNN) and the counterpart Discrete-Time CNN (DT-CNN), Full Signal Range CNN and Time-derivative CNN. The aim is to give an intuitive understanding of the concept, rather than discussing the theory in detail.

### 2.5.1 Standard CNN Architecture

A massive aggregate of regularly spaced processing units, called cells, forms the CNN architecture. Similar to Cellular Automata [26], any cell in the network is connected only to its neighbour cells, where direct interaction only occurs among adjacent cells. However, other cells are indirectly affected due the propagation effect of the continuous-time dynamics. Furthermore, a CNN of any dimension can be defined theoretically, as illustrated in Figure 2.4, which allows a CNN to handle spatial relations such as topographic maps. The discussion here will be however restricted to the 2-dimensional case.

Figure 2.4: CNN, where the globes represent cells and the links represent direct coupling.

# 2.5.2 Sphere of Influence (Neighbourhood)

In the case of 2-dimensional finite-size CNN, cells are arranged in M rows and N columns, each cell C(i, j) is indexed according to row i and column j and each cell communicates directly with its sphere of influence  $S_r(i, j)$  of radius r, also called r-neighbourhood. Equation 2.1 gives the relation for such a neighbourhood and is defined as the set of cells within a certain distance r to C(i, j), where  $r \ge 0$ .

$$S_r(i,j) = \{C(k,l) | \max(|k-i|,|l-j|) \le r; 1 \le k \le M, 1 \le j \le N\}$$

(2.1)

For instance, we have a  $3\times3$  neighbourhood when r=1 as we obtain a  $3\times3$  matrix in this case as can be seen in Figure 2.5. For r=2,  $5\times5$  neighbourhood and so on. In general, a neighbourhood of size  $(2r+1)^2$  is obtained for certain  $r\geq0$ . Figure 2.5 shows different neighbourhood examples, with r=1, 2 and 3. Observe that when r>N/2, and M=N, a fully connected CNN is obtained, i.e.  $S_r(i,j)$  is the entire network.

Figure 2.5: Different r-neighbourhoods for the centre cell (black circle). To avoid clutter all interconnections are dropped.

### 2.5.3 Standard CNN Equations

Considering a case of a cell with no coupling to any other cell in the grid, such a cell, called an isolated cell, is associated with four variables: input  $u_{ij} \in R^u$ , threshold  $z_{ij} \in R^z$ , state  $x_{ij} \in R^x$ , and output  $y_{ij} \in R^y$ , which are generally the functions of the continuous time t. The cell output value depends on the current state of the cell and also on the input value and the threshold. If the given input is  $u_{ij}(t_0)$  at  $t = t_0$ , an initial state is  $x_{ij}(t_0)$  and a threshold is  $z_{ij}(t_0)$  the state  $x_{ij}(t)$  evolves via the state equation given in Equation 2.2 where the "dot" denotes the time derivate and F is an ordinary nonlinear differential function.

$$\dot{x}_{ij} = F[x_{ij}(t), z_{ij}(t), u_{ij}(t)] \tag{2.2}$$

Now as we know that if the  $n^{th}$  derivative of an unknown function  $H: R \to R$  with respect to a variable h is a function of the lower-order derivatives, i.e.  $F(h,H,H',H'',H''',.....H^{(n-1)})=H^{(n)}$  then the function H is an ordinary differential. Furthermore, if the differential function is not dependent on the variable h, it is then considered autonomous. Equation 2.2, in this sense, is simply a non-autonomous system of ordinary differential equations [32]. In general, different non-linear functions can be used for different cells, but in almost all known applications the cells are identical and therefore employ the same function.

The operative description of a cell is concluded by the determination of the output  $y_{ij}(t)$  by means of a nonlinear function. In most literature, this function is assumed to depend only on the state of the cell, as depicted in Equation 2.3 but it may depend on  $x_{ij}(t)$ ,  $z_{ij}(t)$  and  $y_{ij}(t)$ .

$$y_{ij}(t) = g(x_{ij}(t)) \tag{2.3}$$

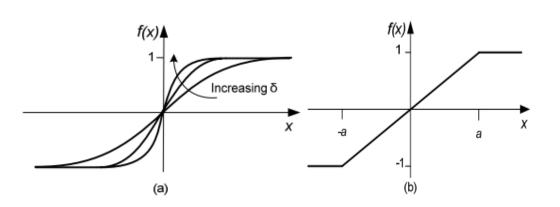

For the quality of the obtained output and the speed achieved, the choice of function g is crucial. There are different functions that can be used but three different types of nonlinear functions are frequently used [33]: (a) threshold, (b) hyperbolic tangent and (c) piece-wise linear functions. The threshold function, commonly referred to as hard-limiter (or Heaviside) function, is binary-valued only and performs a binary decision. The hyperbolic tangent function is generally defined as a strictly increasing continuous s-shaped function and is a special case of the sigmoid function. Figure 2.6(a) shows the nature of this function and Equation 2.4 is used to describe it mathematically. By varying  $\delta$  (the slope parameter), different sigmoid functions are obtained. As the slope parameter approaches infinity, in the case of Equation 2.4, the sigmoid

function simply becomes a threshold function. Finally, the piecewise linear function can be defined as the one that is totally linear with positive slope within a certain interval [-a, a] and saturates outside this interval as illustrated in Figure 2.6(b). The function is mathematically described in Equation 2.5.

$$f(x) = \tanh(\delta x)$$

$$f(x) = \begin{cases} 1, & x \ge a \\ \delta x, & |x| < a \\ -1, & x \le -a \end{cases}$$

$$(2.4)$$

(2.5)

Figure 2.6: Sigmoid function (a) and piece-wise linear function (b).

The State equation standard isolated CNN cell is given in Equation 2.6, which is the most widely used in the literature. Coefficients  $a_{ij}$  and  $b_{ij}$  are the two weightings coefficients whose value define the contributions of state and input variables while as the threshold is simply assumed to be a scalar quantity of constant magnitude [32].  $a_{ij}$  and  $b_{ij}$  are called feed-back and control coefficients respectively as  $a_{ij}$  mirrors the effect of the previous output value, while  $b_{ij}$  scales the current input value. A threshold  $z_{ij}$  is used to adjust the obtained state value into a desired range. The output is usually obtained

by using the piece-wise linear function introduced in Equation 2.5 with the interval [-1, 1] and slope  $\delta$ =1 resulting in Equation 2.7. Assuming all coefficients are linear, the dynamics of the isolated CNN cell are due to the nonlinear output function only.

$$\dot{x}_{ij} = -x_{ij} + a_{ij}y_{ij} + b_{ij}u_{ij} + z_{ij}$$

(2.6)

$$y_{ij} = f(x_{ij}) = \frac{1}{2} (|x_{ij} + 1| - |x_{ij} - 1|) = \begin{cases} 1, & x_{ij} \ge 1 \\ x_{ij}, & |x_{ij}| < 1 \\ -1, & x_{ij} \le -1 \end{cases}$$

$$(2.7)$$

Equation 2.6 is also commonly referred to as 'cell dynamics' as it explains how the state of the cell evolves over time. These dynamics depends upon two constraints: initial condition constraint where the state variable is assumed to be equal to a certain value upon start, and input constraint where input value  $u \in [-1,+1]$ .

In CNN architecture, generally, each cell is directly coupled to all other cells within the sphere of influence  $(S_r)$ . The new output is produced by the consumption of both input  $u_{kl}$  and output  $y_{kl}$  of all available neighbouring cells. Inputs and outputs from cells belonging to  $S_r$  of the cell are weighted as  $b_{kl}$  and  $a_{kl}$  respectively, similar to that of an isolated cell. The state equation of a standard CNN cell can be obtained by simply summing the contributions of all cells in the sphere of influence, and can be written as in Equation 2.8. The output value is still obtained according to Equation 2.7.

$$\dot{x}_{ij} = -x_{ij} + \sum_{kl \in S_r(i,j)} a_{kl} y_{kl}(t) + \sum_{kl \in S_r(i,j)} b_{kl} u_{kl}(t) + z_{ij}$$

(2.8)

$$i = 1,2,3....N$$

;  $j = 1,2,3....N$

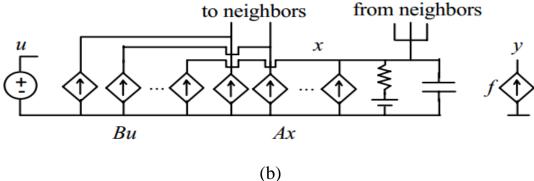

For solving ordinary differential equation systems, almost all theorems and numerical techniques are formulated in vector form [30]. Hence, it is desirable to express the state equation given in Equation 2.8 in vector form. The vector form of the state equation is given in Equation 2.9. The matrices A and B are  $n \times n$  matrices whose nonzero entries are the feed-back coefficient  $a_{kl}$  and control coefficient  $b_{kl}$ .

$$\dot{x} = -x + Ay + Bu + z \tag{2.9}$$

One may conclude that in the mesh, each CNN cell is a dynamic system whose state evolves according to a prescribed state equation. The cell dynamics are coupled to the cells lying within the sphere of influence with the centre that is located at the position of the cell itself. However, the cell dynamics boundary cells have a great effect on the behaviour of the entire CNN. This will be discussed in boundary conditions. But first, a concise form of the state equation is introduced in the following section.

## 2.5.4 Cloning Template

Generally, all feedback and control coefficients of Equation 2.8 can be represented by time-dependent nonlinear operators of the coupled values. For simplification we consider them to be time-invariant and real-valued scalars. Furthermore, in the grid these coefficients are identical for all cells. The state Equation 2.8 is written in a more compact form by using the two-dimensional convolution operator defined in [5], in order to simplify the notation and is re-introduction below.

For any  $3\times 3$  matrix M, the convolution operator  $\otimes$  is defined by Equation 2.10, where M(m,n) denotes the entry in the m<sup>th</sup> row and the n<sup>th</sup> column of the matrix, and  $m,n \in \{-1,0,+1\}$ .

$$M \otimes v_{ij} = \sum_{kl \in S_r(i,j)} M(k-i,l-j)v_{kl}$$

(2.10)

$$\dot{x} = -x_{ii} + A \otimes y_{ii} + B \otimes u_{ii} + z \tag{2.11}$$

Equation 2.11 gives the compact form of the state equation which resulted as the weighting coefficients can be grouped in two square matrices: which holds all feedback coefficients and is accordingly called feedback template (A), and the control template (B). Together with the real-valued threshold (also known as bias), they constitutes a so-called cloning template  $\Gamma$ = (A, B, z). The latter term is commonly used to emphasize the property of space-invariance [34]. It is now obvious that in addition to given input and the initial conditions the cloning template  $\Gamma$  also participate in completely determining the dynamic behaviour of the cell.

The matrices in Equation 2.12 show the common notation of feedback and control templates respectively, for the case of 1-neighbourhood.

$$A = \begin{bmatrix} a_{-1,-1} & a_{-1,0} & a_{-1,1} \\ a_{0,-1} & a_{0,0} & a_{0,1} \\ a_{1,-1} & a_{1,0} & a_{1,1} \end{bmatrix} , B = \begin{bmatrix} b_{-1,-1} & b_{-1,0} & b_{-1,1} \\ b_{0,-1} & b_{0,0} & b_{0,1} \\ b_{1,-1} & b_{1,0} & b_{1,1} \end{bmatrix}$$

(2.12)

The self-feedback entry i.e. the central entry of the feedback template is of significant importance for the stability of operation of a CNN. In this sense, in many cases, it is desired to decompose the A template in Equation 2.12 as shown in Equation 2.13. Matrices  $\hat{A}$  and  $\overline{A}$  are called centre and surround feedback template respectively [35].

$$A = \hat{A} + \overline{A} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & a_{0,0} & 0 \\ 0 & 0 & 0 \end{bmatrix} + \begin{bmatrix} a_{-1,-1} & a_{-1,0} & a_{-1,1} \\ a_{0,-1} & 0 & a_{0,1} \\ a_{1,-1} & a_{1,0} & a_{1,1} \end{bmatrix}$$

(2.14)

The neighbourhood determines the number of the real-valued template coefficient. Three simple classes of special importance and are worth mentioning [17]. These classes are briefly introduced below.

➤ Zero-feedback template: in this case all the feedback coefficients are zero. Equation 2.15 describes the dynamics of each cell of a zero-feedback CNN.

$$\dot{x} = -x_{ii} + B \otimes u_{ii} + z \tag{2.15}$$

➤ Zero-input template: Zero-input CNNs are also termed as autonomous CNNs. In the case of Zero-input CNNs all control coefficients are zero. The dynamics of each cell of a zero-input CNN is described by Equation 2.16.

$$\dot{x} = -x_{ij} + A \otimes y_{ij} + z \tag{2.16}$$

➤ Un-coupled template: The dynamics of each cell of uncoupled CNN is described by a scalar nonlinear ordinary differential equation as shown in Equation 2.17. In the case of uncoupled CNN all surround control coefficients are zero, i.e.  $A = \hat{A}$ .

$$\dot{x} = -x_{ii} + a_{0.0} f(x_{ii}) + B \otimes u_{ii} + z \tag{2.17}$$

# 2.5.5 Boundary Conditions

So far no restrictions have been imposed on the size of the CNN grid. Actually, the conceptual discussion carried out till now is valid for infinite CNN grids, but when CNNs of finite size are considered it suffers from a number of complications.

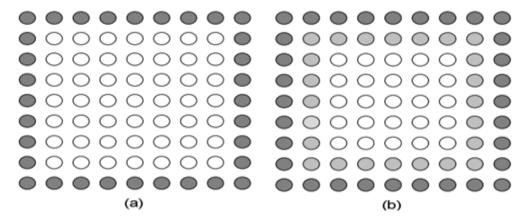

Equations 2.8 and 2.10 are not completely defined in the case of cells whose sphere of interest  $S_r(i,j)$  extends outside of the boundary of the grid. Thus we can divide CNN cells into two different categories: regular cells and boundary cells. A regular cell can be defined as the one for which for a certain neighbourhood "r" it has  $(2r+1)^2$  neighbour cells. All the other cells with less than  $(2r+1)^2$  neighbours belong to the category of boundary cells. Also it is to be noted that all boundary cells are not edge cells, if r > 1 (Figure 2.7). Edge cells lie on the perimeter, i.e. they are the outermost boundary cells.

Figure 2.7: When r = 1, boundary cells coincide with edge cells (a) but for 1 boundary cells (light grey) are not located on the edges only (b).

Furthermore, due to the nature of indirect propagation, the absence of neighbouring cells doesn't affect the boundary cells only, but it has a great impact on the dynamic behaviour of the entire network. Thus a different interpretation of boundary cell is required. Traditionally, virtual CNN cells are introducing around the grid for remedying the boundary cell problem. The virtual cells complete the sphere of influence of all boundary cells and each virtual cell is associated with a virtual state, a virtual input, a virtual output and a virtual threshold [35]. These virtual parameters are specified via various boundary conditions. Three of the most commonly used boundary

conditions for 1-neighborhood, as described in [34], and are rephrased as under:

- ➤ Fixed (Dirichlet) boundary condition: predefined constant values are assigned for virtual state and input of each virtual cell or in other words we can say that the boundaries of the network are tied to fixed values.

- $\triangleright$  Zero-flux (Neumann) boundary condition: usually, this condition applies to CNNs with no input, i.e.  $u_{ij}=0$ . In this case virtual cells are considered to have the same state and input values as their direct neighbouring boundary cells.

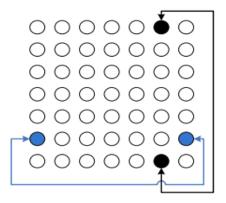

- ➤ Periodic (Toroidal) boundary condition: Here the first and last rows of the network are identical and the top the bottom column are identical as shown in Figure 2.8. Thus, the CNN behaves as if it is joined onto itself forming a torus.

Figure 2.8: In periodic boundary condition the CNN is joined onto itself.

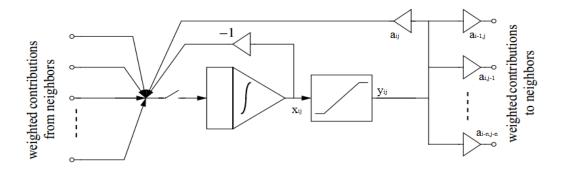

Figure 2.9 shows a block diagram of a CNN cell based on Chua-Yang's model. Each cell receives/generates a weighted contribution from/for each cell in its neighbourhood. Incoming contributions are added directly at the input of the cell and integrated. The output of the integrator represents the state variable  $x_{ij}$ , which is feedback to the input

with a scaling factor -1 that represents a normalization factor for the rest of the weights. A nonlinear block is then used to generate the output  $y_{ij}$ , which is replicated and scaled to generate the out-coming contributions for the cells in the neighbourhood. The implementation of the control and the offset terms is not shown in the figure. Variables  $x_{ij}$  and  $y_{ij}$  in Figure 2.9 are identical while the cell is within its linear region. Otherwise  $y_{ij}$ , saturates at  $\pm 1$  (after normalization), while  $x_{ij}$  goes beyond these limits. This means that the output signal range of the integrator must be wide enough as the circuit implementation must provide room for these larger variations of the state variable.

Figure 2.9: Block diagram of a CT CNN cell circuitry based on Chua-Yang's model. Control template and offset-term implementation are not shown.

### 2.6 Discrete-Time (DT) CNN

A DT-CNN poses a regular grid of locally connected cells that can theoretically, have any dimension, but again the focus here will be on the 2-dimensional case only for simplicity. The DT-CNN is a clocked system which is in contrary to CT-CNNs. The dynamics of DT-CNN are described by a set of discrete equations. This enforces the introduction of slightly different notations, so for that reason notations used in [1] are used. Furthermore, it is important to emphasize that the space invariance feature is assumed here as well and the size of the grid is assumed to be finite, unless it is explicitly stated otherwise.

The coordinate of the position of the cell in the grid, i.e. row  $c_i$  and column  $c_j$  helps in identifying the cell c. The cell communicates directly with all the neighbour cells belonging to the r-neighbourhood. A slight modification is made to the definition of r-neighbourhood given in Equation 2.1 to reflect the new notation of the cell but as depicted in Equation 2.18 the relation remains unchanged. The character d represents any cell belonging to the neighbourhood of cell c, including c itself.

$$N_r(c) = \left\{ d \in \mathbb{Z}^2 \middle| \max \left( |d_i - c_i|, |d_j - c_j| \right) \le r \right\}$$

(2.18)

The state  $x^c$ , of a cell c, mainly depends on the contribution of the time-independent input  $u^d$  and the time-variant output  $y^d$ . These dependencies at a discrete time k are depicted in Equation 2.19.

$$x^{c}(k) = \sum_{d \in N_{r}(c)} a_{d}^{c} y^{d}(k) + \sum_{d \in N_{r}(c)} b_{d}^{c} u^{d} + i^{c}$$

(2.19)

The real-valued coefficients, the feedback coefficients, the control coefficients and the threshold/bias values are represented by  $a_d^c$ ,  $b_d^c$  and  $i^c$  respectively. While  $a_d^c$  reflect the contribution from the output of all cells in the neighbourhood,  $b_d^c$  describe the dependency on the inputs of the neighbours and  $i^c$  is added to adjust a cell's threshold. For DT-CNN, coefficients are commonly expressed in a compact form by means of matrices, as was also seen in the case of CT-CNN. The cloning template  $\Gamma = \langle A, B, i \rangle$  that is often thought of as an elementary DT-CNN program or DT-CNN instruction [1] is thus used to specify the spatially invariant DT-CNNs.

A compact state equation is, in Equation 2.20, by substituting Equation 2.10 into Equation 2.19. Equation 2.20 is obviously equivalent

to Equation 2.11. All cells in the DT-CNN have identical functionality, because of that cell subscripts can be omitted as shown in Equation 2.21.

$$x^{c}(k) = A \otimes y^{d}(k) + B \otimes u^{d} + i \tag{2.20}$$

$$x(k) = A \otimes y(k) + B \otimes u + i \tag{2.21}$$

An initial output  $y^c(0)$  is of crucial importance for the dynamic behaviour of the network (compare with the initial condition constraint in section 2.5.3) in the case of non-zero feedback coefficients. On the other hand the output of the system remains constant after the first time step if all feedback coefficients are equal to zero.

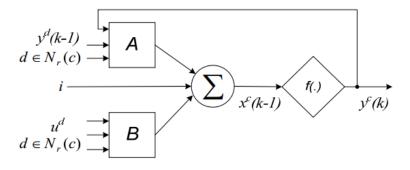

The functionality of the system in accordance to CT-CNN is defined by the cloning template  $\Gamma$ . The dynamic behaviour of a DT-CNN is completely determined by cloning template together with the activation pattern u and the initial output  $y^c(0)$ . Figure 2.10 illustrates the functionality of a cell, explains schematically the influence of all involved parameters [1]. The data comes in over the  $u^d$  input and is modified through the control template B, while the interaction with the neighbouring cells is gathered through the  $y^d$  input and modified through the feedback template A. All modified input values are summed and discriminated after application of the bias i.

Figure 2.10: A schematic diagram illustrating a DT-CNN cell. [23]

### 2.7 Full Signal Range CNN

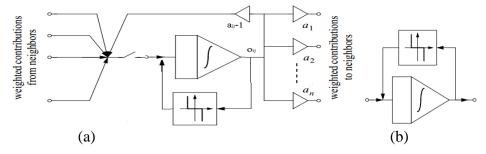

As we have seen in CT-CNN (of Figure 2.9) that the output signal range of the integrator must be wide enough which increases the circuit complexity. This reason motivates searching for alternative models, and resulted in Full Signal Range CNN (FSR-CNN). Again considering CT-CNN model (Figure 2.9) it appears from a functional point of view, that  $x_{ii}$  may be restricted to the unitary interval as well and that the state and output variables may be merged into a single one with no influence on the functionality. This is actually the idea behind the FSR model, whose block diagram is depicted in Figure 2.11(a). The main modification centres on the integrator, which in Figure 2.9 is designed with sufficient output signal range to avoid its saturation during the dynamic evolution of the cell, while in Figure 2.11(a), it is designed to have saturation limits equal to those of the output variable. Thus, this block responds to the usual integral law while its output  $o_{ij}$  (modified state variable) is within its saturation limits (after normalization). Whenever the state variable reaches +1 (alternatively-1), it remains clamped to this value as long as the input of the integrator is non-negative (alternatively nonpositive), without modifying its value. As soon as the integrator input becomes negative (alternatively positive), the modified state variable will enter the linear region again. Figure 2.11(b) shows a conceptual block diagram to realize the integrator.

Figure 2.11: (a) Block diagram of CNN cell circuitry using the FSR model, (b) Integrator with saturation. [30]

### 2.8 Time-Derivative CNN

Time-derivative CNN (TDCNN) [37] extends the original CNN description in [5] by adding derivative connections between cells. A time-derivative linear CNN is described by

$$\frac{dx(i,j,t)}{dt} = \sum_{m,n=-r}^{r} A(m,n)x(i+m,j+n,t) + \sum_{m,n=-r}^{r} B(m,n)u(i+m,j+n,t)

+ \sum_{q \in 1...D} \left[ \sum_{m,n=-r}^{r} A_q(m,n) \frac{dx^q(i+m,j+n,t)}{dt^q} \right]$$

(2.22)

The first two terms on the right hand side of (2.22) are the same as in the case of original CNN equation, A and B are feedback and feed-forward cloning templates, u is input and x denotes the state and output of the linear network.  $A_q$  and  $B_q$  are defined as  $q^{th}$  derivative of feedback and feed-forward templates, respectively, and r denotes the neighbourhood of the CNN. It has been shown that by adding first order derivatives of the outputs of the neighbouring cells to the original CNN equation, bandpass spatiotemporal filters can be realized [20, 37]. For these first derivative TDCNNs, Equation 2.22 becomes

$$\frac{dx(i,j,t)}{dt} = \sum_{m,n=-r}^{r} A(m,n)x(i+m,j+n,t) + \sum_{m,n=-r}^{r} B(m,n)u(i+m,j+n,t) + \sum_{m,n=-r}^{r} A_1(m,n)\frac{dx(i+m,j+n,t)}{dt}$$

(2.23)

# 2.9 Application of ANNs

ANNs are powerful tools for modelling, especially when the underlying data relationship is unknown. Besides ANNs can identify and learn correlated patterns between input data sets and corresponding target values. They have seen an explosion of interest over the last few decades, as they perform "intelligent" tasks similar to those performed

by the human brain, and are being successfully applied across an extraordinary range of problem domain, in the areas as diverse as medicine, engineering, biology, physics and finance. From a statistical perspective NNs are interesting because of their potential use in prediction and classification problems. ANNs acquires knowledge through learning and after training, ANNs can be used to predict the outcome of new independent input data.

ANNs imitate the learning process of the human brain and can process problems involving non-linear and complex data even if the data are imprecise and noisy. A very important feature of these networks is their adaptive nature, where "programing" is replaced by "learning by example" in solving problems. This feature makes such computational models very appealing in application domains where training data is readily available but one has little or incomplete understanding of the problem to be solved.

The applications of ANNs are limitless. They have been used in classification problems, such as identifying underwater sonar currents, recognizing speech, and predicting the secondary structure of globular proteins. In time-series applications, ANNs have been used in predicting stock market performance. Besides they have been applied within the medical domain for clinical diagnosis [38], image analysis and interpretation [39], signal analysis and interpretation, drug development [40] and to design and discover new drugs in pharmacology [41]. Furthermore, their application also covers activities such as motion detection, classification and recognition of objects, associative memory, and solution of partial differential equations, statistical and non-linear filtering and much more.

# 2.10 Conclusion

Neural networks are discussed in brief along with the biological inspiration for the implementation of ANNs. Besides this an introduction about CNNs is given in this chapter along with its various types. Few of the applications of ANNs are mentioned in the end of the chapter.

#### 3.1 Introduction

Implementation of neural networks can be achieved either by software simulation in conventional computers or by a special hardware solution. Most of the Neural Network architectures and algorithms exist only as mathematical models or are implemented as a software solution upon a standard von Neumann style architecture machine, and despite the high speed of modern computer platforms for the simulation of ANNs, the platforms are not fast enough for very large networks or realtime applications. The hardwired neural network is capable of dramatically decreasing execution time as the feature of full parallelism is captured by means of hardware realizations only. Furthermore, the main objective of building special hardware is to provide a platform for efficient adaptive systems, capable of updating their parameters in the course of time as the main problem is the time required for the learning process, which can increase exponentially with the size of the network. Neural networks without learning, however, are rather uninteresting and if the weights of a network were fixed from the beginning and were not change, neural networks could be implemented using any programming language in conventional computers.

The first modelling of neurons was devised by Pitts and McCulloch in 1943. In their view a neuron, which they called a formal neuron, is a logical gate with two possible internal states, active and silent. A neuron has a few entries provided by the outputs of other neurons. The entries are summed up and the state of the neuron is determined by the value of the resulting signal with respect to a certain

threshold, if the signal is larger than the threshold the neuron is active otherwise it is silent.

### 3.2 Hardware implementation Artificial Neural Networks

Hardware implementation of neural networks can be achieved in different ways. They can be Analog, Digital or Hybrid depending upon the way signals is processed. A brief introduction of these is given in the next sections.

### 3.2.1 Analogue Artificial Neural Networks

In the analog implementation of neural networks, a coding method is used in which signals are represented by currents or voltages. This allows us to think of these systems as operating with real numbers during the neural network simulation. The basic operation of an ANN processing element can be summarized as

$$out = F\left[\sum(\Pi)\right] \tag{3.1}$$

Therefore three operations of multiplication, summation  $\Sigma$  and activation function are to be performed within analogue hardware. Graf and Jackal [42] and Foo et al [43] provide a general introduction into analogue implementations, while Mead [44] provides a greater depth and more specialized viewpoint for using analogue circuits.

### 3.2.2 Digital Artificial Neural Networks

In a digital implementation of an ANN it is obviously necessary to perform the same operations as with an analogue approach. A number of approaches can be taken: one is to form all the components of a neuron separately using digital technology, second is to generate digital architectures and processors tailored towards ANN implementation and application, i.e. to design neuro-computer devices/accelerator boards and the third is to make use of existing high performance parallel

computers and devices to construct purpose built machines, for example using transputers, or parallel DSP devices [45, 46]. Atlas and Suziki in [47] have provided a general introduction to digital NN systems.

Yet another approach using digital circuits is to use pulse coded computation as exemplified by Murray et al [48], Tomlinson et al [49] and Leaver [50].

### 3.2.3 Hybrid Artificial Neural Networks

Analogue and digital techniques for the hardware implementation of ANNs could be combined to provide a hybrid solution. This could lead to the best of both disciplines being combined.

In a hybrid system actual computation could be performed using analogue processing circuits as this often provides the smaller, faster circuits while as weight storage and update can be performed digitally since this provides a more stable method than their analogue counterparts. Inter-element communication could be a mixture of digital and analogue. Analogue communication links could be used internally within an individual neural chip

Alternatively, pseudo analogue systems could be realized using digital signals by means of pulse encoding.

### 3.3 Hardware Implementations of CNN

Fabrication of Fully connected analogue neural networks is a very difficult task as they suffer because of number of connections and the distance that these connections need to propagate. CNNs in contrary to simple neural networks are characterized by local connectivity. The adoption of the concept of nearest neighbour interactions found in cellular automata [51] allows for the arrangement of the cells which are equidistant in regular grid. The routing and layout problems usually

faced in traditional analogue circuits are then easily tackled in analogue CNN VLSI implementations. A cell is designed and replicated to form a regular network that is placed and routed rapidly. The first VLSI implementation of a CNN [52] has, naturally, been based on the analogue model of the standard cell as presented by Chua [5].

Fabrication usually has its issues as most of the fabricated circuits come with parasitic capacitances and resistances, which in many cases leads to undesired behaviour. In order to reduce the sensitivity of the cell to such fabrication deviations, the dynamics of the cell are dominated by large state capacitor. Furthermore, the state capacitors affect the initialization procedure. A single row of state capacitors (cells) is loaded at a time as all cells cannot be loaded with initial states simultaneously. Also while initialized, the state capacitors have to be disconnected from the remainder of the cells in order to prevent their voltages from dropping to such a level that it may affect the processing.

Another issue has to do with the degree of adaptability. High flexibility is difficult to achieve, as one can tell by the experience gained from neural network VLSI implementations. Hence, the CNN array is very difficult to be 'programmed', so the array is designed to perform one or a related set of processing functions using fixed coefficients. Complex tasks are proposed to be solved by cascading or paralleling multiple CNN VLSI devices. This is, apparently, not practical and removes most of the attraction of the CNN VLSI implementation as time and cost are then much higher in comparison to other established systems. Next, due to fabrication and the available VLSI technology issues, only small CNN chips  $(20 \times 20)$  were realized. But with the advancement in hardware technology a wide range of concepts, models and architectures were proposed.

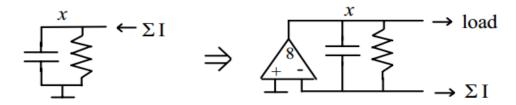

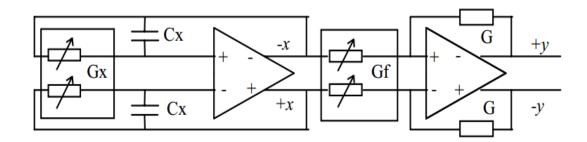

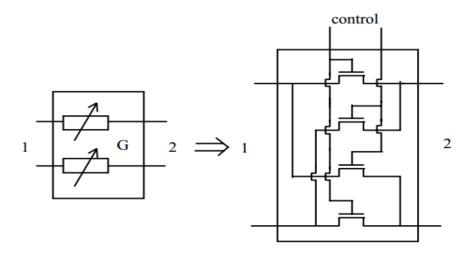

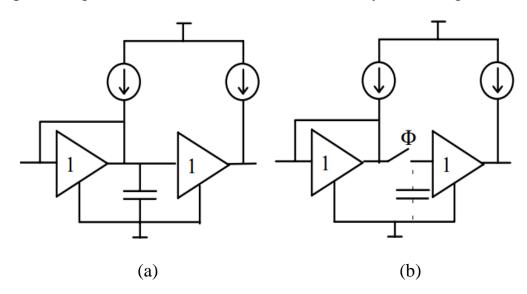

The first attempt toward a VLSI implementation of a CNN was presented by Yang and Chua [5]. Meanwhile, a hardware accelerator board (CNN-HAC), mainly for hardware simulation was developed by Roska et al. [53]. Chua and Roska in 1992 introduced first algorithmically programmable analogue array computer having real time and super-computer power on a single chip [54] called as the CNN Universal Machine (CNN-UM). A key feature in the CNN-UM is the "dual computing" paradigm. Logic operations that only involve the symbolic variables YES/NO are combined with analogue array processing; therefore denoted analogic computing. All signals and operators are either analogue or logic, which in principle removes the need for Analog to Digital and Digital to Analog conversions.