# Realization of Integrable Low-Voltage Companding Filters for Portable System Applications

## **THESIS**

Submitted to

**University of Kashmir**

In partial fulfillment of the requirements for the award of the degree of

## **DOCTOR OF PHILOSOPHY**

In

## **ELECTRONICS**

By

FAROOQ AHMAD KHANDAY

Under the Supervision of

Prof. N. A. SHAH

March 2013

Postgraduate Department of Electronics and

**Instrumentation Technology**

**University of Kashmir**

#### Abstract

Undoubtedly, today's integrated electronic systems owe their remarkable performance primarily to the rapid advancements of digital technology since 1970s. The various important advantages of digital circuits are: its abstraction from the physical details of the actual circuit implementation, its comparative insensitiveness to variations in the manufacturing process, and the operating conditions besides allowing functional complexity that would not be possible using analog technology. As a result, digital circuits usually offer a more robust behaviour than their analog counterparts, though often with area, power and speed drawbacks. Due to these and other benefits, analog functionality has increasingly been replaced by digital implementations.

In spite of the advantages discussed above, analog components are far from obsolete and continue to be key components of modern electronic systems. There is a definite trend toward persistent and ubiquitous use of analog electronic circuits in day-to-day life. Portable electronic gadgets, wireless communications and the widespread application of RF tags are just a few examples of contemporary developments. While all of these electronic systems are based on digital circuitry, they heavily rely on analog components as interfaces to the real world. In fact, many modern designs combine powerful digital systems and complementary analog components on a single chip for cost and reliability reasons. Unfortunately, the design of such systems-on-chip (SOC) suffers from the vastly different design styles of analog and digital components. While mature synthesis tools are readily available for digital designs, there is hardly any such support for analog designers apart from well-established PSPICE-like circuit simulators. Consequently, though the analog part usually occupies only a small fraction of the entire die area of an SOC, but its design often constitutes a major bottleneck within the entire development process.

Integrated continuous-time active filters are the class of continuous-time or analog circuits which are used in various applications like channel selection in radios, anti-aliasing before sampling, and hearing aids etc. One of the figures of merit of a filter is the dynamic range; this is the ratio of the largest to the smallest signal that can be applied at the input of the filter while maintaining certain specified performance. The dynamic range required in the filter varies with the application and is decided by the variation in strength of the desired signal as well as that of unwanted signals that

are to be rejected by the filter. It is well known that the power dissipation and the capacitor area of an integrated active filter increases in proportion to its dynamic range. This situation is incompatible with the needs of integrated systems, especially battery operated ones. In addition to this fundamental dependence of power dissipation on dynamic range, the design of integrated active filters is further complicated by the reduction of supply voltage of integrated circuits imposed by the scaling down of technologies to attain twin objective of higher speed and lower power consumption in digital circuits. The reduction in power consumption with decreasing supply voltage does not apply to analog circuits. In fact, considerable innovation is required with a reduced supply voltage even to avoid increasing power consumption for a given signal to noise ratio (S/N). These aspects pose a great hurdle to the active filter designer.

A technique which has attracted the attention of circuit designers as a possible route to filters with higher dynamic range per unit power consumption is "companding". Companding (compression-expansion) filters are a very promising subclass of continuous-time analog filters, where the input (linear) signal is initially compressed before it will be handled by the core (non-linear) system. In order to preserve the linear operation of the whole system, the non-linear signal produced by the core system is converted back to a linear output signal by employing an appropriate output stage. The required compression and expansion operations are performed by employing bipolar transistors in active region or MOS transistors in weak inversion; the systems thus derived are known as logarithmic-domain (log-domain) systems. In case MOS transistors operated in saturation region are employed, the derived structures are known as Square-root domain systems. Finally, the third class of companding filters can also be obtained by employing bipolar transistors in active region or MOS transistors in weak inversion; the derived systems are known as Sinh-domain systems.

During the last several years, a significant research effort has been already carried out in the area of companding circuits. This is due to the fact that their main advantages are the capability for operation in low-voltage environment and large dynamic range originated from their companding nature, electronic tunability of the frequency characteristics, absence of resistors and the potential for operations in varied frequency regions.

Thus, it is obvious that companding filters can be employed for implementing high-performance analog signal processing in diverse frequency ranges. For example, companding filters could be used for realizing subsystems in: xDSL modems, disk drive read channels, biomedical electronics, Bluetooth/ZigBee applications, phase-locked loops, FM stereo demodulator, touch-tone telephone tone decoder and crossover network used in a three-way high-fidelity loudspeaker etc.

A number of design methods for companding filters and their building blocks have been introduced in the literature. Most of the proposed filter structures operate either above 1.5V or under symmetrical (±1.5V) power supplies. According to data that provides information about the near future of semiconductor technology, International Technology Roadmap for Semiconductors (ITRS), in 2013, the supply voltage of digital circuits in 32 nm technology will be 0.5 V. Therefore, the trend for the implementation of analog integrated circuits is the usage of low-voltage building blocks that use a single 0.5-1.5V power supply.

Therefore, the present investigation was primarily concerned with the study and design of low voltage and low power Companding filters. The work includes the study about: the building blocks required in implementing low voltage and low power Companding filters; the techniques used to realize low voltage and low power Companding filters and their various areas of application.

Various novel low voltage and low power Companding filter designs have been developed and studied for their characteristics to be applied in a particular portable area of application. The developed designs include the N-th order universal Companding filter designs, which have been reported first time in the open literature. Further, an endeavor has been made to design Companding filters with orthogonal tuning of performance parameters so that the designs can be simultaneously used for various features. The salient features of each of the developed circuit are described. Electronic tunability is one of the major features of all of the designs. Use of grounded capacitors and resistorless designs in all the cases makes the designs suitable for IC technology. All the designs operate in a low-voltage and low-power environment essential for portable system applications.

Unless specified otherwise, all the investigations on these designs are based on the PSPICE simulations using model parameters of the NR100N bipolar transistors and

BSIM  $0.35\mu m/TSMC$   $0.25\mu m$  /TSMC  $0.18\mu m$  CMOS process MOS transistors. The performance of each circuit has been validated by comparing the characteristics obtained using simulation with the results present in the open literature.

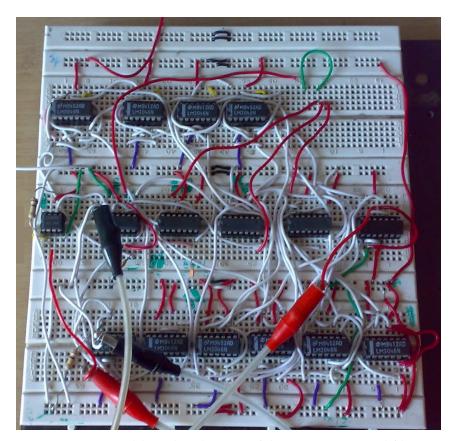

The proposed designs could not be realized in silicon due to non-availability of foundry facility at the place of study. An effort has already been started to realize some of the designs in silicon and check their applicability in practical circuits. At the basic level, one of the proposed Companding filter designs was implemented using the commercially available transistor array ICs (LM3046N) and was found to verify the theoretical predictions obtained from the simulation results.

Dedicated

To my Parents

#### **CERTIFICATE**

This is to certify that Mr. FAROOQ AHMAD KHANDAY has worked under my supervision for the Thesis entitled, "Realization of Integrable Low-Voltage Companding Filters for Portable System Applications" and the work is truly commendable of consideration for the award of the degree of Doctor of Philosophy in Electronics.

It is further certified that

- (i). The Thesis embodies the work of the candidate.

- (ii). The candidate worked under my supervision for the period required under statues.

- (iii). The candidate has put in the required attendance in the Department.

- (iv). The conduct of the candidate remained very good during the period of the research.

(Prof. N. A. Shah)

Supervisor

Department of Electronics and Instrumentation Technology University of Kashmir Srinagar-190006

#### CANDIDATE'S DECLARATION

I hereby declare that the work presented in this Thesis "Realization of Integrable Low-Voltage Companding Filters for Portable System Applications" in partial fulfillment of the requirements for the degree of **Doctor of Philosophy** and submitted in the Department of Electronics and Instrumentation Technology, Faculty of Applied Sciences and Technology, University of Kashmir, Srinagar, has entirely been done by me under the supervision of **Prof. N. A. Shah**.

I, further, declare that the work contained in the thesis is the original research work conducted by me and has not been submitted in part or full, to any other University or Institute for the award of any degree.

(FAROOQ AHMAD KHANDAY)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(Prof. N. A. Shah)

#### **Supervisor**

Department of Electronics and Instrumentation Technology University of Kashmir Srinagar-190006

The Ph. D. Viva-voce examination of Mr. Farooq Ahmad Khanday, Research Scholar, has been held on.....

Supervisor Head of the Department External Examiner

Acknowledgements

I would like to start by thanking God for giving me the strength to overcome the many

difficulties that life has thrown at me, and for making possible many things that

seemed at first to be impossible. Next, there are no words to express what I feel

towards my family. My father, mother, and sisters have always been there to offer me

their love and my brothers have always encouraged and supported me. In addition, I

would like to acknowledge people who have contributed to this work and helped me

during the whole period of study and research.

The first person I want to thank is my guide, Professor Nisar A. Shah. I want to

thank him not only because of his broad knowledge and his profound insights, but also

because of his decent, warm, sensitive and caring personality. He gave me a promising

and significant research area, strong encouragement and full support. I would like to

thank him for his trust and confidence in me and his appreciation of my work.

I wish to present special thanks to Prof. C. Psychalinos, Associate Professor,

Patras University, Greece, who gave me a lot of support during the course of my

research work. He spent an enormous amount of time to help me to solve the testing

problems and work on the circuits.

I wish to thank Prof. M. Mustafa, Dr. M. T. Banday, Mr. S. A. Parah, Dr. J. A.

Sheikh, Er. Mueed Hafiz, Er. Rouf-Ul-Alam Bhat, Mr Javeed Iqbal and other faculty

members and research scholars for their valuable discussions during the course of the

work. Finally, I also thank technicians of the Departmental Laboratories for supporting

the work.

(FAROOQ AHMAD KHANDAY)

KU, March 2013

viii

## **CONTENTS**

| ABSTRAC    | T                                                         | i        |

|------------|-----------------------------------------------------------|----------|

| DEDICAT    | ION                                                       | v        |

| CERTIFIC   | ATE                                                       | vi       |

| DECLARA    | ATION                                                     | vii      |

| ACKNOW     | LEDGEMENTS                                                | viii     |

| TABLE OF   | FCONTENTS                                                 | ix       |

| LIST OF F  | IGURES                                                    | xiii     |

| LIST OF T  |                                                           | xix      |

|            |                                                           |          |

| NOMENC     | LATURE                                                    | XXI      |

|            |                                                           |          |

| TABLE O    | F CONTENTS                                                | Page No. |

| Chapter 1: | Introduction                                              | 1        |

| 1.1.       | State-of-the-Art Low-Voltage Low-Power Analog Design      | . 1      |

|            | and its Applications                                      |          |

| 1.2.       | Active Filter Design: An Introduction                     | 3        |

| 1. 2. 1.   | Filter Classification                                     | 5        |

| 1. 3.      | Background and Motivation                                 | 8        |

| 1.4.       | History and state of the art of Companding-filters        | 10       |

| 1.5.       | Companding filter design for portable system applications | 12       |

| 1.6.       | Thesis Outline                                            | 13       |

| Chapter 2: | Companding Filters                                        | 14       |

| 2.1.       | Introduction                                              | 14       |

| 2.2.       | Companding techniques                                     | 14       |

| 2.2.1.     | Translinear Principle                                     | 15       |

| 2.3.       | Companding Filter Techniques                              | 19       |

| 2.3.1.     | Log-Domain (LD) Filtering                                 | 21       |

| 2311       | All NPN Transistor Exponential Transconductor Cells       | 2.1      |

| TABLE OF       | CONTENTS                                                   | Page No. |

|----------------|------------------------------------------------------------|----------|

| 2.3.1.2.       | LOG and EXP Operators                                      | 22       |

| 2.3.1.3.       | LD Integrators                                             | 23       |

| 2.3.1.4.       | LD Summation/Subtraction Blocks                            | 25       |

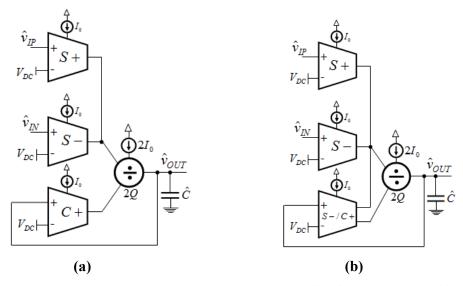

| 2.3.2.         | Square-Root-Domain (SRD) Filtering                         | 26       |

| 2.3.2.1.       | SRD Operators                                              | 26       |

| 2.3.2.2.       | SRD Integrators                                            | 27       |

| 2.3.2.3.       | SRD Summation/Subtraction Blocks                           | 29       |

| 2.3.3.         | Sinh-Domain (SD) Filtering                                 | 31       |

| 2.3.3.1.       | Weak Inversion MOSFET (WIMOSFET) based SD Filter           | 31       |

|                | Design                                                     |          |

| 2.3.3.1.1.     | WIMOSFET based SD operators                                | 31       |

| 2.3.3.1.2.     | WIMOSFET SD Integrators                                    | 34       |

| 2.3.3.1.3.     | WIMOSFET SD Summation/Subtraction Block                    | 35       |

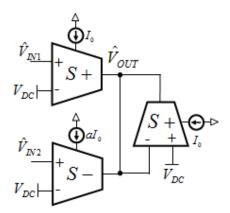

| 2.3.3.2.       | BiCMOS based SD Filter Design                              | 36       |

| 2.3.3.2.1.     | BiCMOS SD operators                                        | 36       |

| 2.3.3.2.2.     | BiCMOS based SD integrators                                | 37       |

| 2.3.3.2.3.     | BiCMOS SD Summation/Subtraction Block                      | 39       |

| 2.4.           | Summary                                                    | 40       |

| Chapter 3: S   | ynthesis Methods of Companding Filters                     | 41       |

| 3.1.           | Introduction                                               | 41       |

| 3.1.1.         | Functional Block Diagram (FBD) Synthesis Method of         | f 42     |

|                | Companding Filter Design                                   |          |

| 3.1.1.1.       | Indirect Method                                            | 42       |

| 3.1.1.1.1.     | Design Example                                             | 43       |

| 3.1.1.2.       | Direct Method                                              | 45       |

| 3.1.1.2.1.     | Proposed MIMO universal filter [J2]                        | 45       |

| 3.1.1.2.1.1.   | Simulation and Experimental Results                        | 47       |

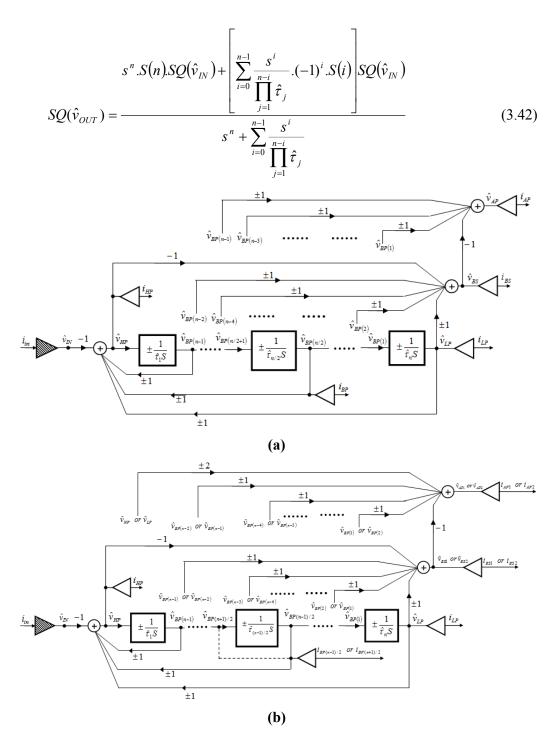

| 3.1.1.2.2.     | Proposed Universal Arbitrary-Order Filter Topologies [J5]- | 53       |

|                | [J8], [J11]                                                |          |

| 3.1.1.2.2.1.   | Single Input Multiple Output (SIMO) Universal Filters      | 53       |

| 3.1.1.2.2.1.1. | All-pole filters                                           | 53       |

| 3.1.1.2.2.1.2. | Filters with finite transmission zeros                     | 55       |

| 3.1.1.2.2.2.   | Multiple Input Single Output (MISO) Universal Filter       | 59       |

| 3.1.1.2.2.3.   | LD design [J5]-[J7]                                        | 60       |

| TABLE OF       | CONTENTS                                                    | Page No. |

|----------------|-------------------------------------------------------------|----------|

| 3.1.1.2.2.3.1. | Simulation Results                                          | 60       |

| 3.1.1.2.2.3.2. | Comparison                                                  | 65       |

| 3.1.1.2.2.4.   | SRD design [J8], [J11]                                      | 69       |

| 3.1.1.2.2.4.1. | Simulation Results                                          | 71       |

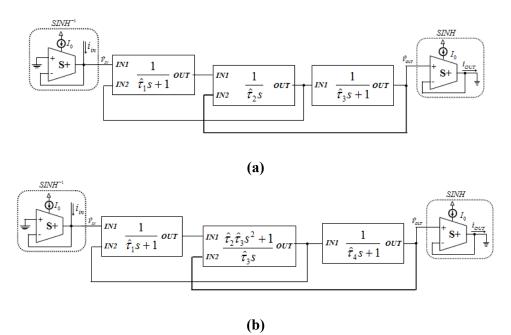

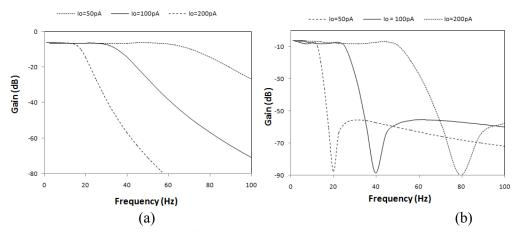

| 3.1.1.2.3.     | A low voltage and low power SD universal biquadratic filter | 87       |

|                | for low frequency applications [J4]                         |          |

| 3.1.1.2.3.1.   | Design Procedure of SD Universal Biquadratic Filter         | 87       |

| 3.1.1.2.3.2.   | Simulation Results                                          | 88       |

| 3.1.2.         | Linear Gm-C Filter Transposition Synthesis Method of        | 94       |

|                | Companding Filters                                          |          |

| 3.1.2.1.       | Synthesis of SIFO Electronically Tunable Log-Domain multi-  | 94       |

|                | function Biquad [J9]                                        |          |

| 3.1.2.1.1.     | Design of Log-Domain multi-function Biquad                  | 94       |

| 3.1.2.1.1.1.   | Method                                                      | 94       |

| 3.1.2.1.1.1.   | LP filtering function                                       | 95       |

| 3.1.2.1.1.1.2. | BP filtering function                                       | 96       |

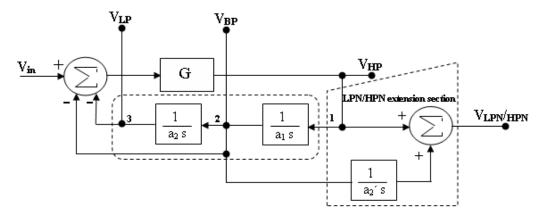

| 3.1.2.1.1.1.3. | LPN/HPN filtering function                                  | 96       |

| 3.1.2.1.1.3.   | Simulation Results                                          | 98       |

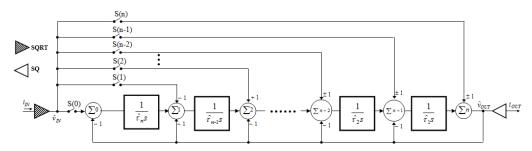

| 3.1.3.         | Exponential State-Space Synthesis Method of Companding      | 104      |

|                | Filters                                                     |          |

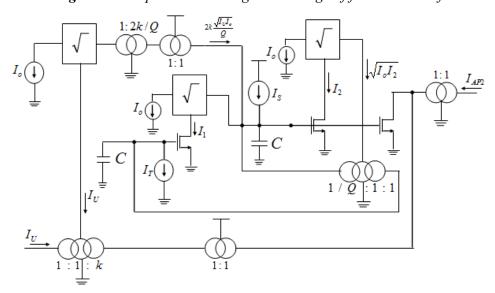

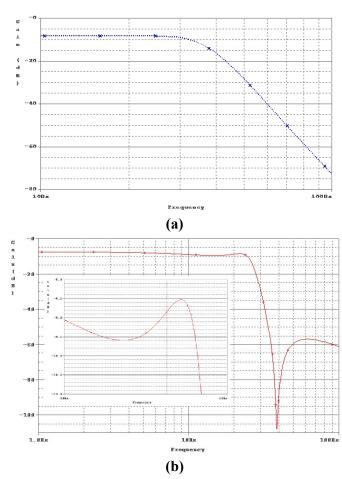

| 3.1.3.1.       | Synthesis of High-order Allpass filters using Novel Low-    | 104      |

|                | Voltage Current-Mode Square-Root-Domain low-order Allpass   |          |

|                | Filters [J15]                                               |          |

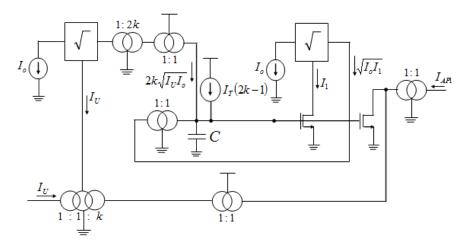

| 3.1.3.1.1.     | Proposed Low-Voltage Current-Mode Square-Root Domain        | 104      |

|                | AP filter Design                                            |          |

| 3.1.3.1.1.1.   | First-Order AP Filter                                       | 104      |

| 3.1.3.1.1.2.   | Second-Order AP Filter                                      | 106      |

| 3.1.3.1.1.3.   | Simulation results                                          | 107      |

| 3.1.4.         | Linear Transformation Synthesis Method of Companding        | 112      |

|                | Filters                                                     |          |

| 3.1.4.1.       | Sinh-Domain (SD) Linear Transformation (LT) filters [J1]    | 112      |

| 3.1.4.2.       | Realization of the Proposed SD LT Equivalents               | 114      |

| 3.1.4.3.       | Simulation Results                                          | 114      |

| 3.2.           | Summary                                                     | 118      |

| TABLE OF CONTENTS |                                                | Page No. |  |

|-------------------|------------------------------------------------|----------|--|

| Chapter 4         | 2: Conclusions and Suggestions for Future work | 120      |  |

| 4.1.              | Conclusions                                    | 120      |  |

| 4.2.              | Suggestions for the future work                | 120      |  |

| Appendix          | res                                            |          |  |

| <i>A</i> :        | <b>Publications and Accepted Papers</b>        | 122      |  |

| <b>B</b> :        | Bibliography                                   | 125      |  |

| Fig. 1.1:  | The operating frequency ranges of filter for various applications.  | 6  |

|------------|---------------------------------------------------------------------|----|

| Fig. 1.2:  | Classifications of Integrated Filters.                              | 6  |

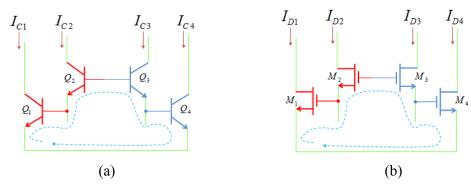

| Fig. 2.1:  | Translinear Loops: (a) BTL and (b) MTL.                             | 19 |

| Fig. 2.2:  | Translinear Loops implementing useful functions of                  | 19 |

|            | Squarer/Divider/Multiplier.                                         |    |

| Fig. 2.3:  | Response of three compression operators corresponding to a shifted  | 20 |

|            | sinusoidal waveform.                                                |    |

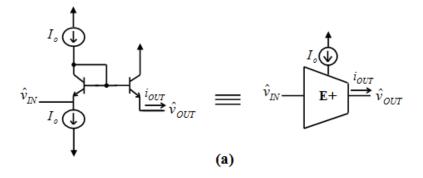

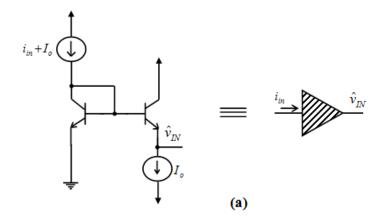

| Fig. 2.4:  | All NPN transistorized representation of transconductance cells and | 22 |

|            | the symbols used in the Thesis: (a) Positive transconductance cell. |    |

|            | (b) Negative transconductance cell.                                 |    |

| Fig. 2.5:  | Realization of the LD operators (a) LOG operator and (b) EXP        | 23 |

|            | operator.                                                           |    |

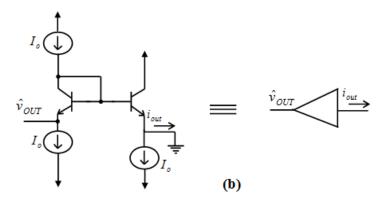

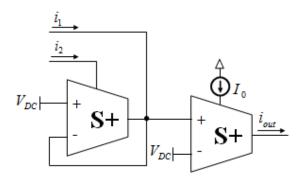

| Fig. 2.6:  | Exponential transconductor cell representation of: a) two-input     | 24 |

|            | lossless integrator. b) two-input damped (lossy) integrator.        |    |

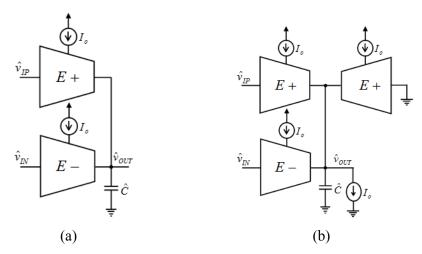

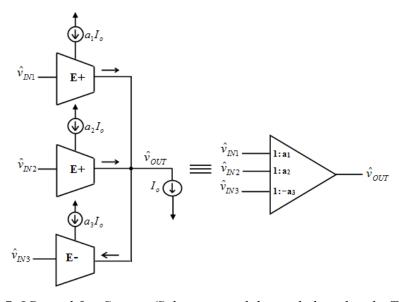

| Fig. 2.7:  | Log-domain amplifier-Summer/Subtractor and the symbol used in       | 25 |

|            | the Thesis.                                                         |    |

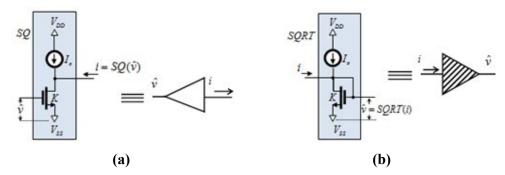

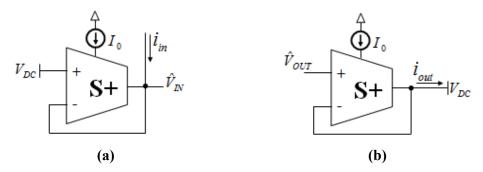

| Fig. 2.8:  | Realization of the SRD operators. (a) SQ operator (b) SQRT          | 27 |

|            | operator.                                                           |    |

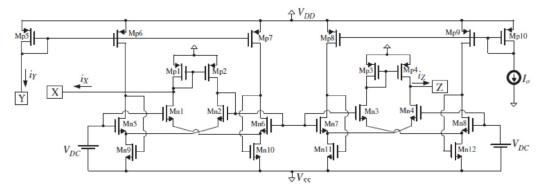

| Fig. 2.9:  | Square root divider cell [144, 145].                                | 28 |

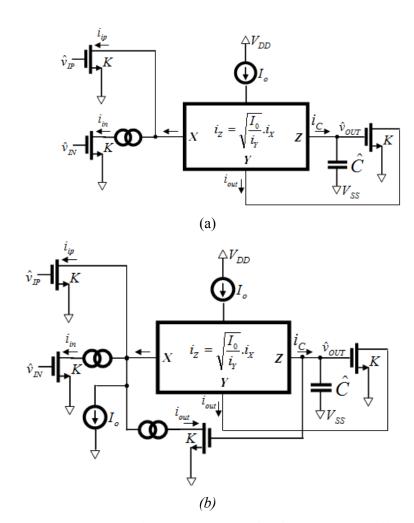

| Fig. 2.10: | SRD Integrators. (a) Two-input SRD lossless integrator. (b)Two-     | 30 |

|            | input SRD lossy integrator.                                         |    |

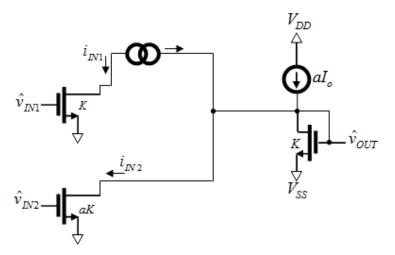

| Fig. 2.11: | SRD algebraic summation block with weighted input.                  | 30 |

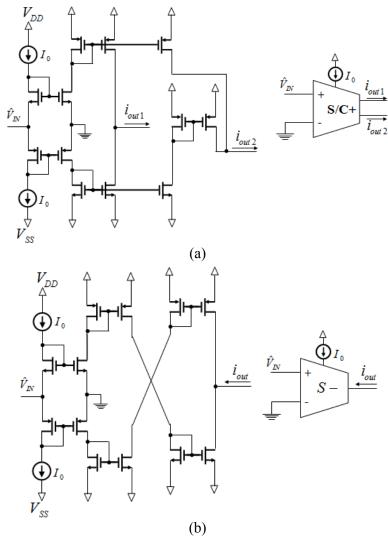

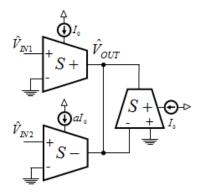

| Fig. 2.12: | WIMOSFET SC transconductors: (a) positive SC transconductor         | 33 |

|            | cell; (b) Employed Symbol of positive SC transconductor cell (c)    |    |

|            | negative SC transconductor cell; and (d) Employed Symbol of         |    |

|            | negative SC transconductor cell.                                    |    |

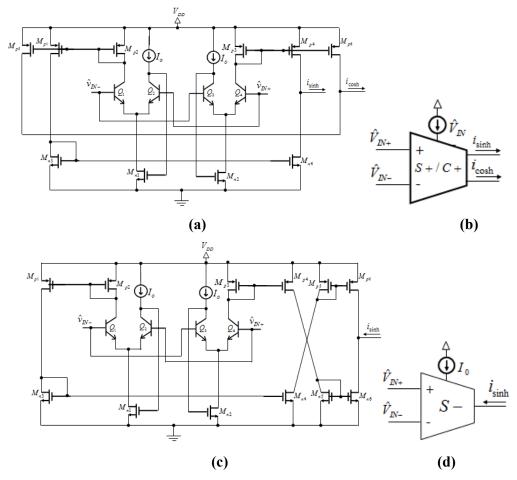

| Fig. 2.13: | Realization of the WIMOSFET SD operators: (a) $SINH^{-1}$ and (b)   | 33 |

|            | SINH.                                                               |    |

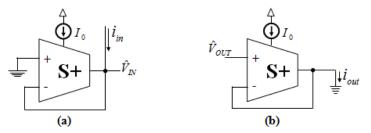

| Fig. 2.14: | WIMOSFET Two-quadrant multiplier/divider: (a) Conceptual            | 34 |

|            | representation; (b) Employed Symbol; and (c) Topology.              |    |

| Fig. 2.15: | WIMOSFET SD Integrators. (a) Two-input SD lossless integrator.      | 36 |

|            | (b)Two-input SD lossy integrator.                                   |    |

| Fig. 2.16: | WIMOSFET SD algebraic summation/subtraction block with                       | 36 |

|------------|------------------------------------------------------------------------------|----|

|            | weighted input.                                                              |    |

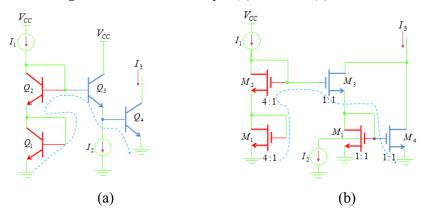

| Fig. 2.17: | BiCMOS SC transconductors: (a) positive SC transconductor cell;              | 38 |

|            | (b) Employed symbol of positive SC transconductor cell (c) negative          |    |

|            | SC transconductor cell; and (d) Employed symbol of negative SC               |    |

|            | transconductor cell.                                                         |    |

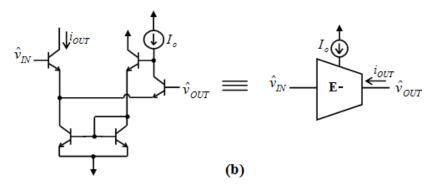

| Fig. 2.18: | Realization of the BiCMOS SD operators: (a) SINH-1 and (b)                   | 38 |

|            | SINH.                                                                        |    |

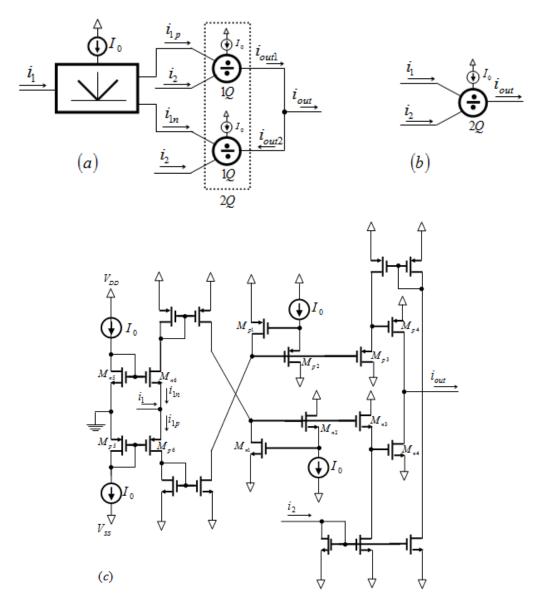

| Fig. 2.19: | BiCMOS Two-quadrant multiplier/divider.                                      | 39 |

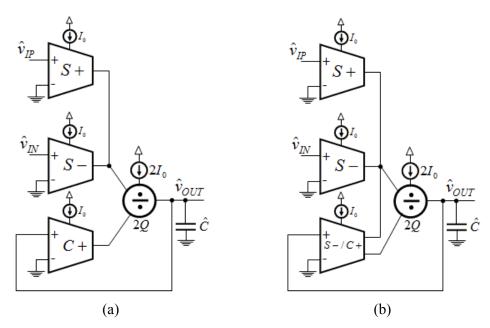

| Fig. 2.20: | BiCMOS SD Integrators. (a) Two-input SD lossless integrator.                 | 39 |

|            | (b)Two-input SD lossy integrator.                                            |    |

| Fig. 2.21: | BiCMOS SD algebraic summation/subtraction block with weighted                | 40 |

|            | input.                                                                       |    |

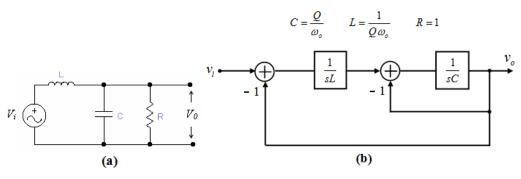

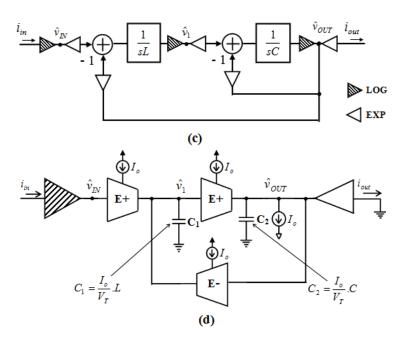

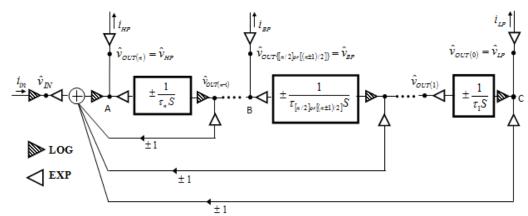

| Fig. 3.1:  | Synthesis of lowpass log-domain biquad: (a) Passive prototype (b)            | 44 |

|            | the linear SFG (c) the corresponding log-domain SFG, and (d) the             |    |

|            | final log-domain filter.                                                     |    |

| Fig. 3.2:  | Simulation Results of: (a) Passive prototype of Fig. 3.1(a). (b) log-        | 44 |

|            | domain filter of Fig. 3.1(d).                                                |    |

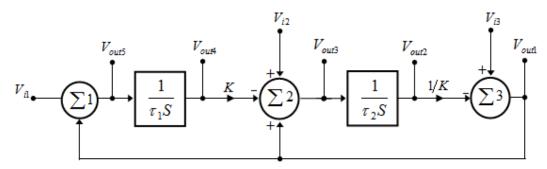

| Fig. 3.3:  | FBD of the proposed MIMO universal filter                                    | 46 |

| Fig. 3.4:  | Transposed log-domain FBD of the proposed MIMO universal filter              | 46 |

|            | of Fig. 3.3.                                                                 |    |

| Fig. 3.5:  | Proposed log-domain MIMO universal filter.                                   | 48 |

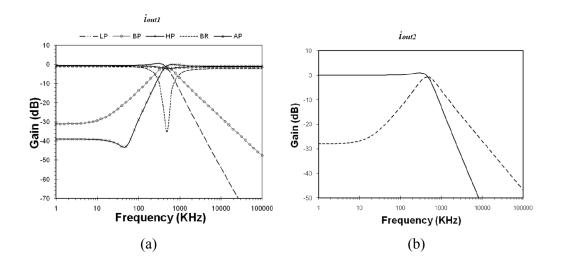

| Fig. 3.6:  | Simulated magnitude responses of standard filter functions of                | 49 |

|            | proposed MIMO universal filter in Fig. 3.5. (a) iout1, (b) iout2, (c) iout3, |    |

|            | (d) iout4, (e) iout5.                                                        |    |

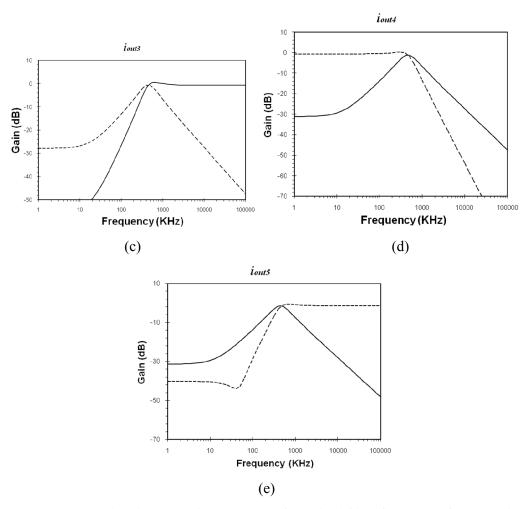

| Fig. 3.7:  | Demonstration of the electronic tunability of frequency                      | 50 |

|            | characteristics of the proposed MIMO filter.                                 |    |

| Fig. 3.8:  | Demonstration of the electronic tunability of gain characteristics of        | 51 |

|            | the proposed MIMO filter.                                                    |    |

| Fig. 3.9:  | Demonstration of the independent adjustment of $\omega_0$ and $Q$ of the     | 51 |

|            | filter.                                                                      |    |

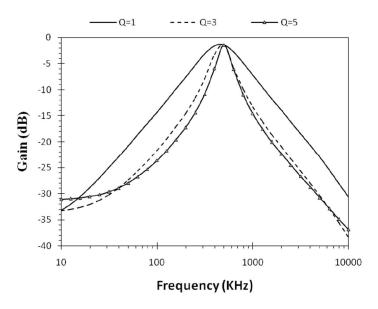

| Fig 3 10.  | Linear performance of the LP filter function (inva) of MIMO                  | 52 |

|            | universal filter.                                                             |    |

|------------|-------------------------------------------------------------------------------|----|

| Fig. 3.11: | Bread-board realization of the MIMO universal filter.                         | 52 |

| Fig. 3.12: | Measured frequency response of the MIMO universal filter for a 50             | 53 |

|            | μΑ (peak value) input signal.                                                 |    |

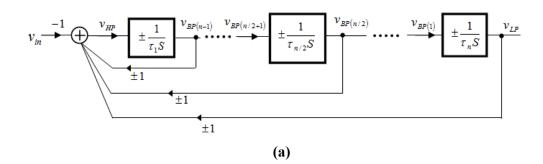

| Fig. 3.13: | FBDs of the Generic SIMO all-pole FLF filter topologies: (a) Even             | 55 |

|            | Order and (b) Odd Order.                                                      |    |

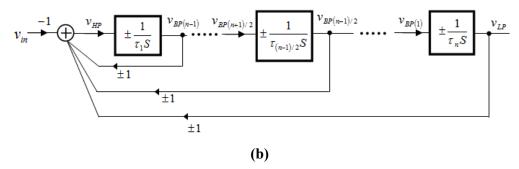

| Fig. 3.14: | FBDs of the Generic SIMO all-pole FLF filter topologies with finite           | 57 |

|            | transmission zeros: (a) Even Order and (b) Odd Order.                         |    |

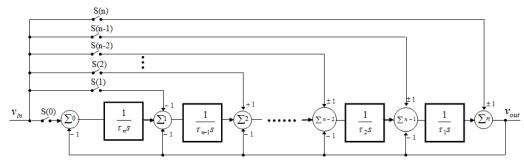

| Fig. 3.15: | FBD of the MISO Universal filter topology.                                    | 59 |

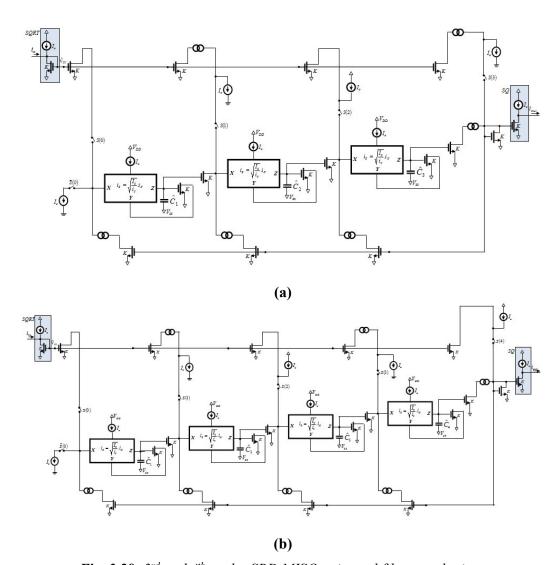

| Fig. 3.16: | Transposed topology of the filter in Fig. 3.13 into Log-Domain.               | 61 |

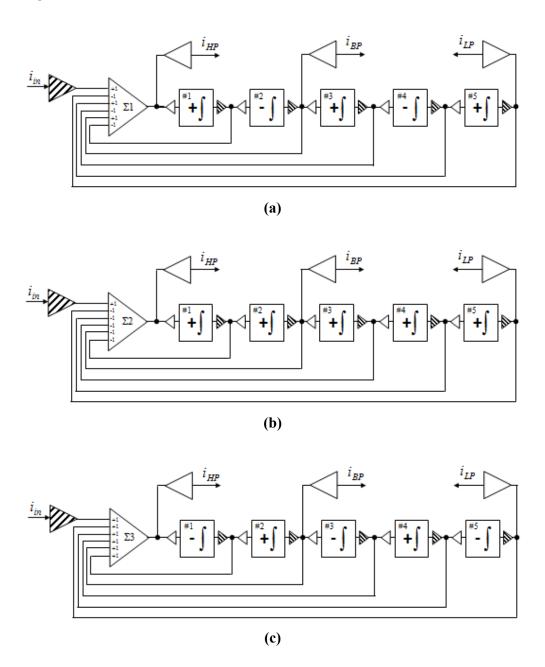

| Fig. 3.17: | Topologies of the 5 <sup>th</sup> -order generic Log-Domain MFF of Fig. 3.16. | 63 |

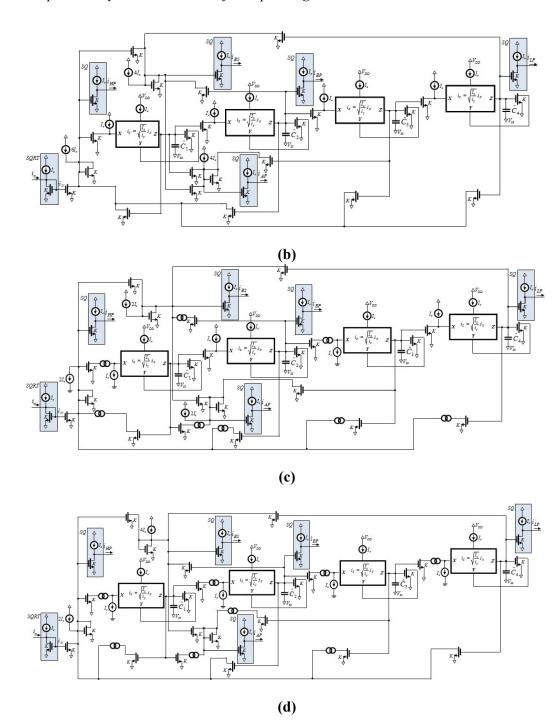

|            | (a) MFF1 (b) MFF2 (c) MFF3 (d) MFF4.                                          |    |

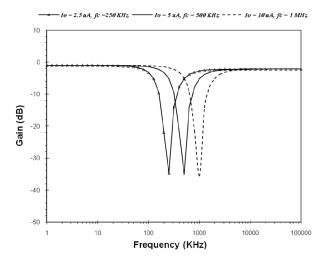

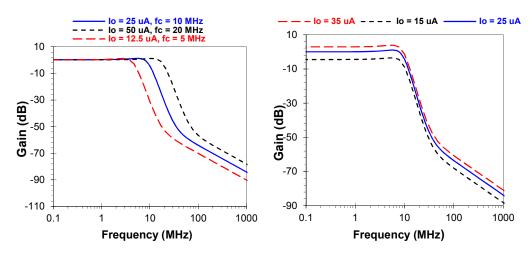

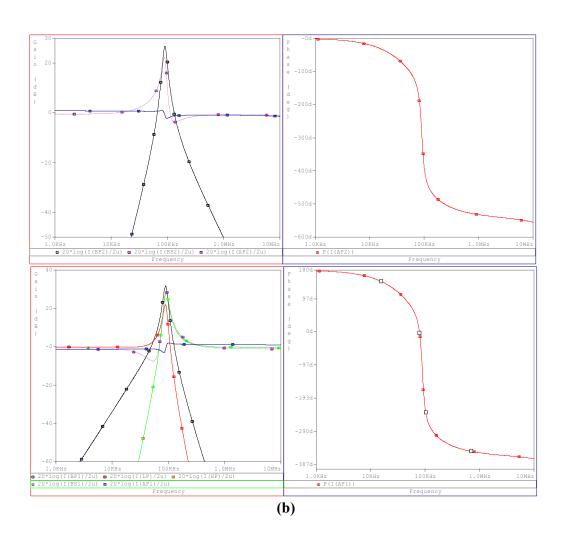

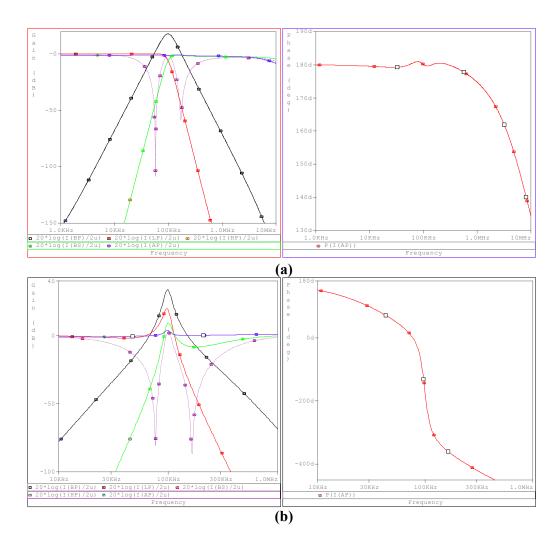

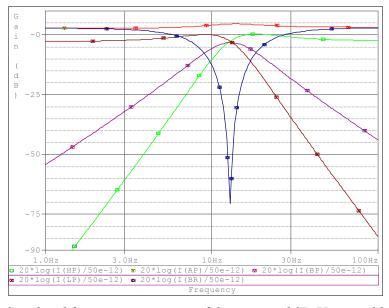

| Fig. 3.18: | Simulated magnitude responses of standard filter functions of MFFs            | 63 |

|            | of Fig. 3.17. (a) MFF1 (b) MFF2 (c) MFF3 (d) MFF4.                            |    |

| Fig. 3.19: | Demonstration of electronic tunability of cut-off frequency and gain          | 64 |

|            | of MFFs.                                                                      |    |

| Fig. 3.20: | Linear performance of the LP filter functions of 5th-order log-               | 65 |

|            | domain MFFs of Fig. 3.17.                                                     |    |

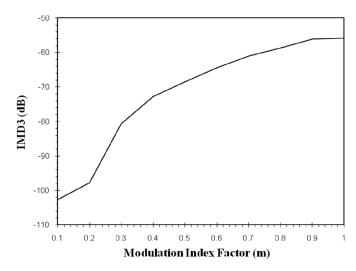

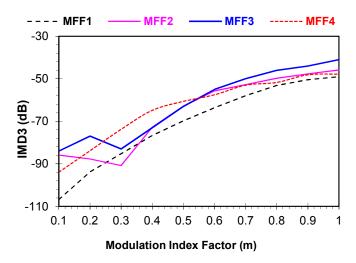

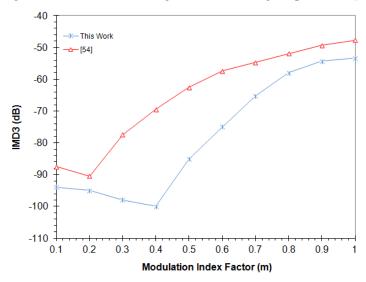

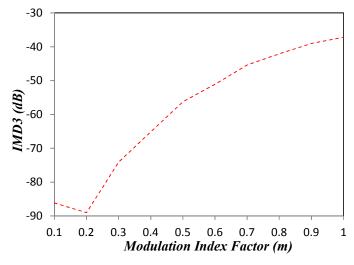

| Fig. 3.21: | Third-order intermodulation distortion (IMD3) versus modulation               | 66 |

|            | index factor response of biquads of proposed topology and                     |    |

|            | Reference [54].                                                               |    |

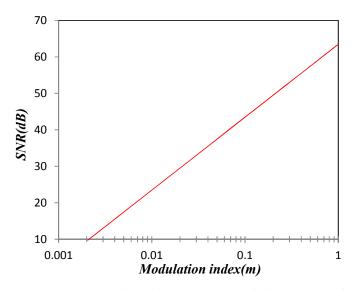

| Fig. 3.22: | SNR versus modulation index factor of biquads of proposed design              | 67 |

|            | and Reference [54].                                                           |    |

| Fig. 3.23: | Sensitivity of log-domain filters on integrating capacitor and bias           | 67 |

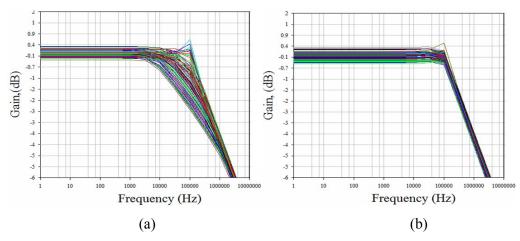

|            | current variations. (a) Reference [54] design. (b) Proposed design.           |    |

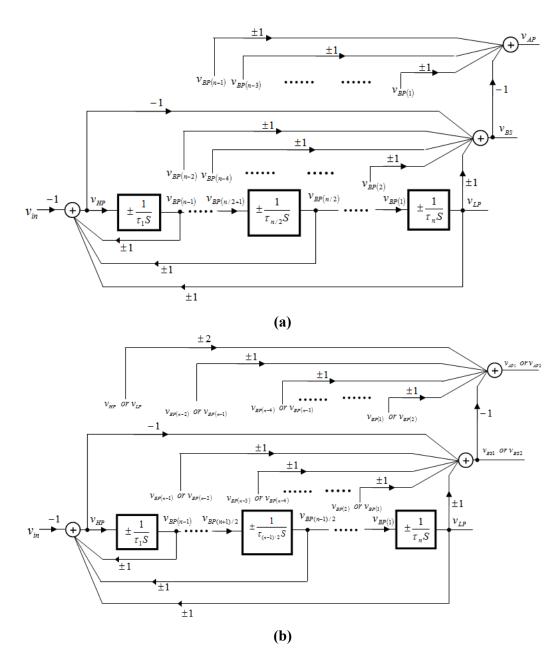

| Fig. 3.24: | Transposed topologies of the Generic SIMO all-pole FLF filter                 | 70 |

|            | topologies with finite transmission zeros of Fig. 3.14 into Square-           |    |

|            | Root-Domain: (a) Even Order and (b) Odd Order.                                |    |

| Fig. 3.25: | Transposed topology of MISO Universal filter topology of Fig. 3.15            | 71 |

|            | into Square-Root-Domain.                                                      |    |

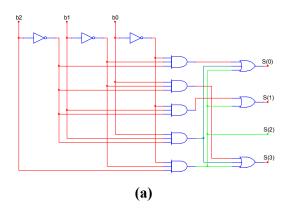

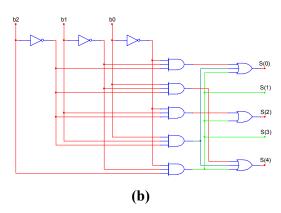

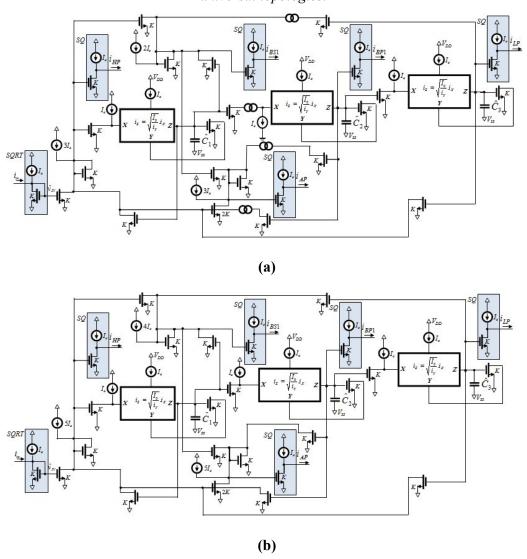

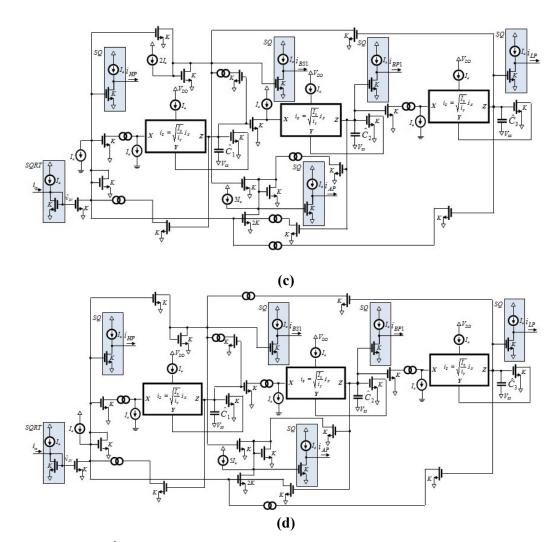

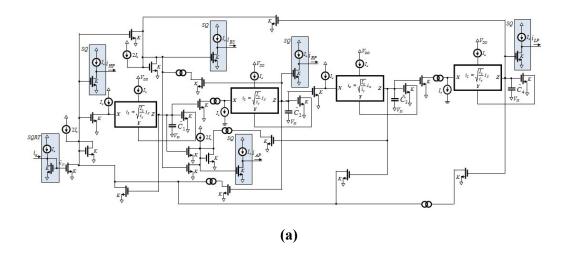

| Fig. 3.26: | Circuit schemes for filter function selection in 3rd and 4th-order            | 74 |

|            | MISO universal filter topologies.                                             |    |

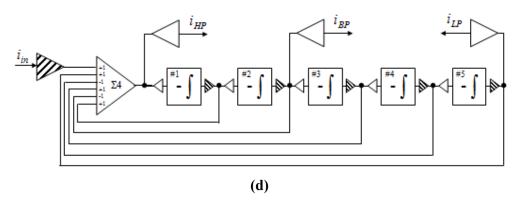

| Fig. 3.27: | 3rd-order SRD SIMO universal filter topologies: (a) FT 1, (b) FT 2,                         | 75 |

|------------|---------------------------------------------------------------------------------------------|----|

|            | (c) FT 3, and (d) FT 4.                                                                     |    |

| Fig. 3.28: | 4th-order SRD SIMO universal filter topologies: (a) FT 1, (b) FT 2, (c) FT 3, and (d) FT 4. | 76 |

| Fig. 3.29: | 3rd and 4th–order SRD MISO universal filter topologies.                                     | 77 |

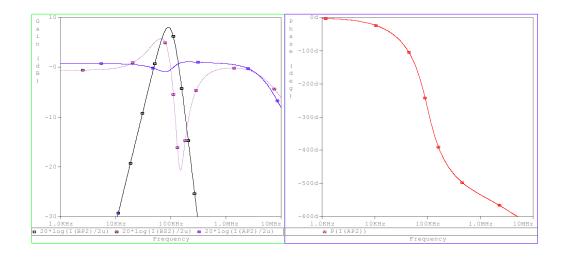

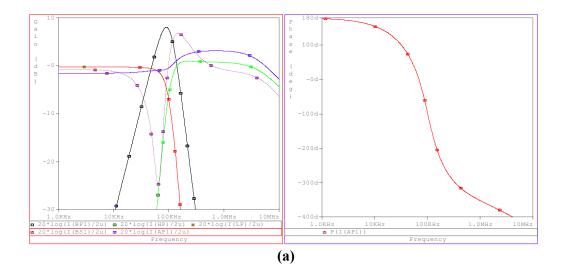

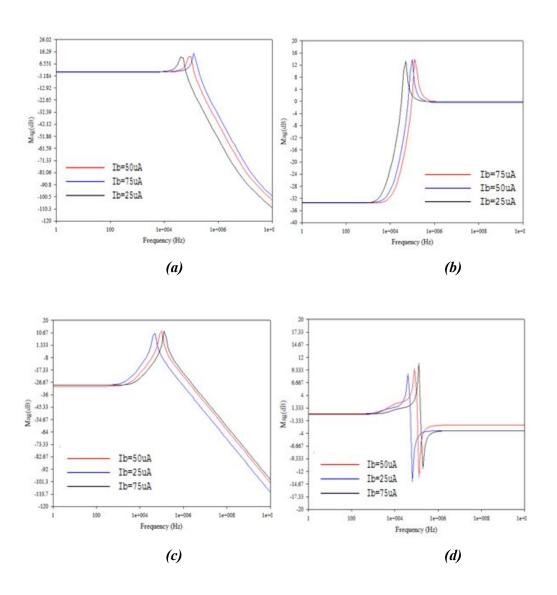

| Fig. 3.30: | Simulated magnitude and phase responses of the 3rd-order SIMO                               | 80 |

|            | universal filter topologies. (a) FT 1, (b) FT 2, (c) FT 3, and (d) FT 4.                    |    |

| Fig. 3.31: | Simulated magnitude and phase responses of the 4th–order SIMO                               | 81 |

|            | universal filter topologies. (a) FT 1, (b) FT 2, (c) FT 3, and (d) FT                       |    |

|            | 4.                                                                                          |    |

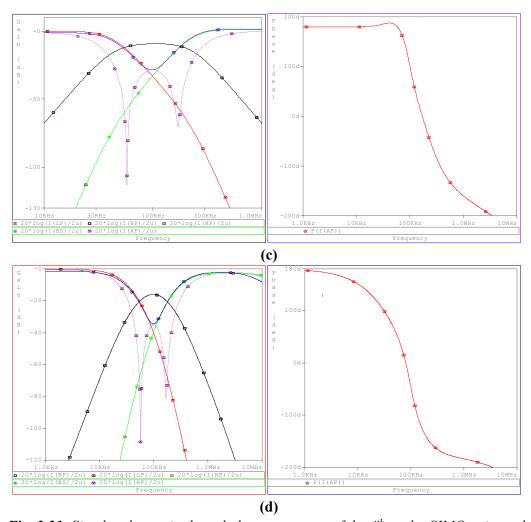

| Fig. 3.32: | Simulated magnitude and phase responses of the MISO universal                               | 82 |

|            | filter topologies. (a) 3rd-order; and (b) 4th-order.                                        |    |

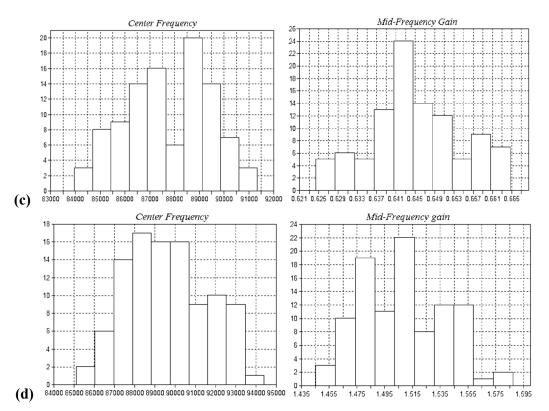

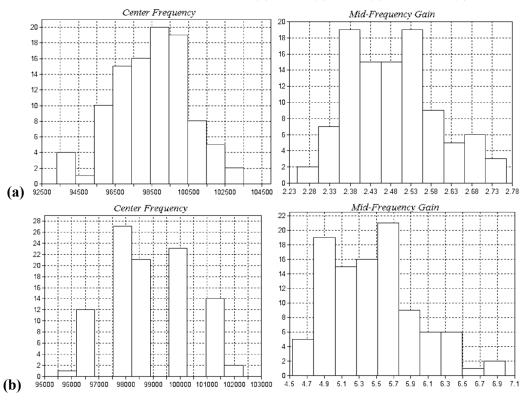

| Fig. 3.33: | Sensitivity of the 3rd-order SIMO universal filter topologies with                          | 83 |

|            | capacitor Transistor and bias current variations. (a) FT 1, (b) FT 2,                       |    |

|            | (c) FT 3, and (d) FT 4.                                                                     |    |

| Fig. 3.34: | Sensitivity of the 4th-order SIMO universal filter topologies with                          | 84 |

|            | capacitor Transistor and bias current variations. (a) FT 1, (b) FT 2,                       |    |

|            | (c) FT 3, and (d) FT 4.                                                                     |    |

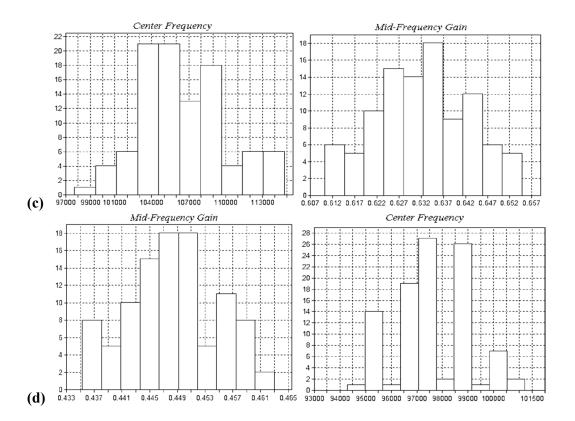

| Fig. 3.35: | Sensitivity of the MISO universal filter topology with capacitor                            | 85 |

|            | Transistor and bias current variations. (a) 3rd-order; and (b) 4th-order.                   |    |

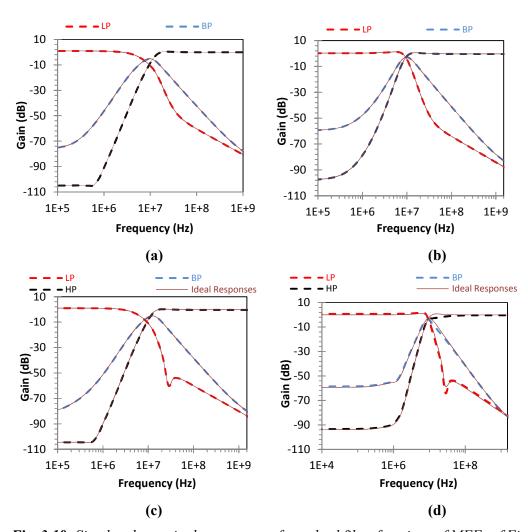

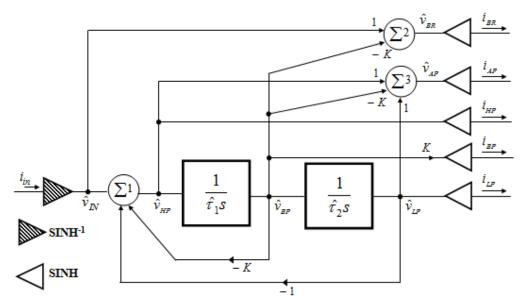

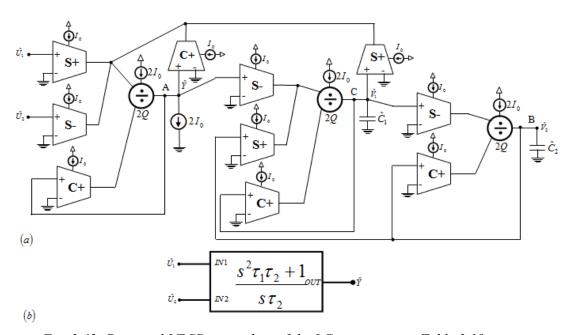

| Fig. 3.36: | FBD of the proposed SD Universal biquadratic filter.                                        | 88 |

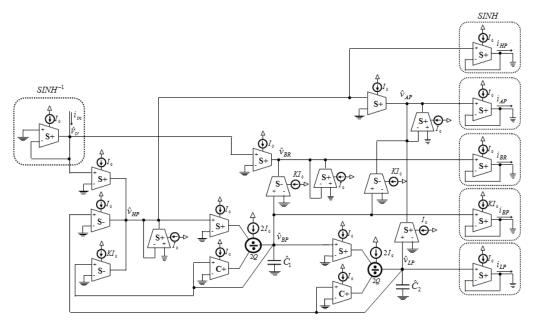

| Fig. 3.37: | Topology of the proposed SD Universal Biquadratic filter.                                   | 88 |

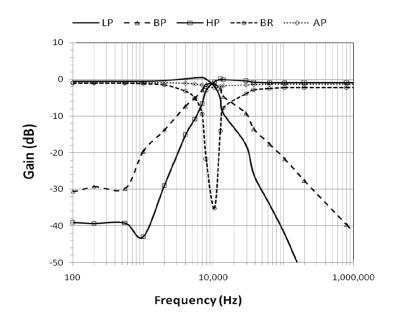

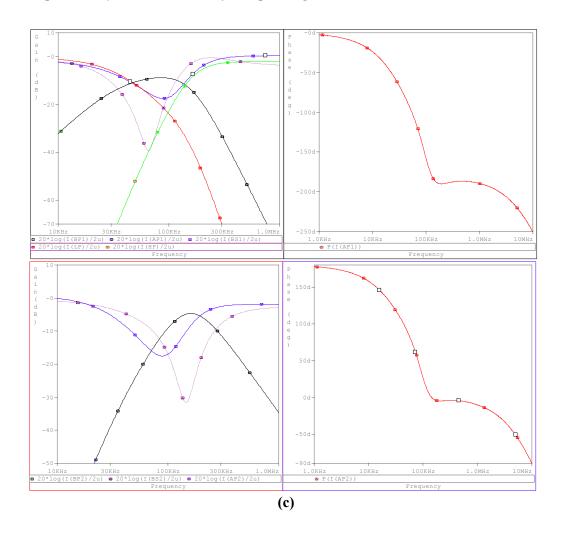

| Fig. 3.38: | Simulated frequency responses of the proposed SD Universal                                  | 90 |

|            | biquadratic filter of Fig. 3.37.                                                            |    |

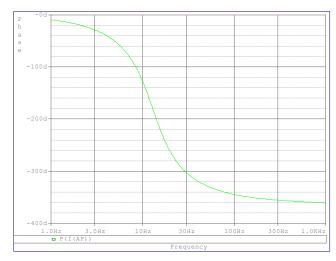

| Fig. 3.39: | AP Phase response of the filter of Fig. 3.37.                                               | 91 |

| Fig. 3.40: | Time-domain responses of the input and AP output of the filter of                           | 91 |

|            | Fig. 3.37.                                                                                  |    |

| Fig. 3.41: | Demonstration of the electronic tunability of frequency                                     | 91 |

|            | characteristics.                                                                            |    |

| Fig. 3.42: | Demonstration of the independent tunability of pole frequency $(\omega_0)$                  | 92 |

|            | and the Quality factor $(Q)$ .                                      |     |

|------------|---------------------------------------------------------------------|-----|

| Fig. 3.43: | Nonlinear performance of the proposed SD universal biquadratic      | 92  |

|            | filter of Fig. 3.37.                                                |     |

| Fig. 3.44: | Simulated SNR versus modulation index factor.                       | 93  |

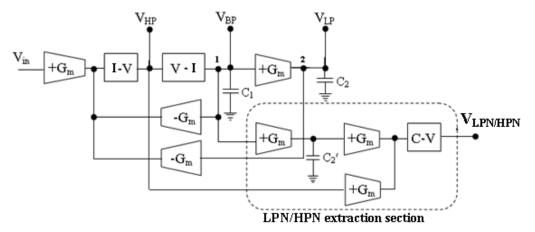

| Fig. 3.45: | FBD representation of proposed multi-function biquadratic filter.   | 95  |

| Fig. 3.46: | Gm-C representation of proposed multi-function biquad.              | 98  |

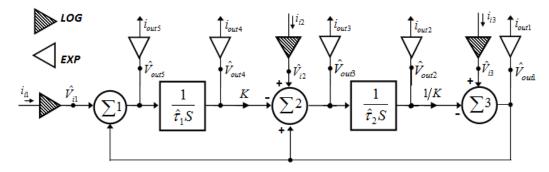

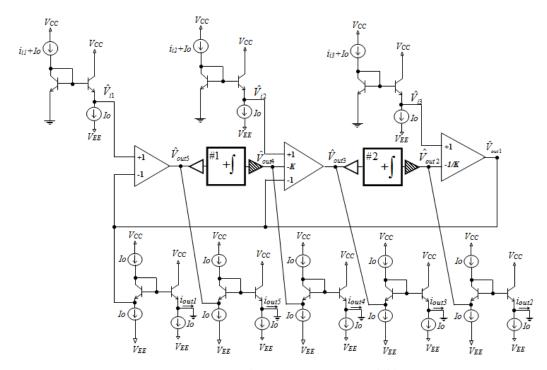

| Fig. 3.47: | LD representation of proposed multi-function biquad.                | 99  |

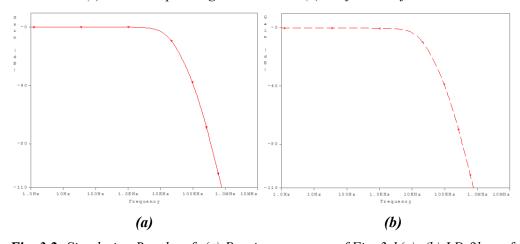

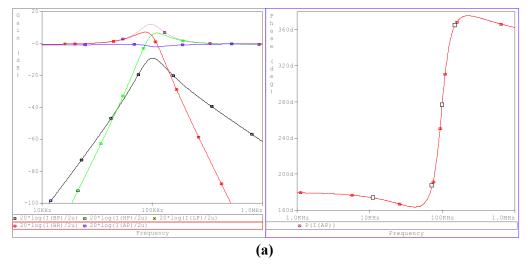

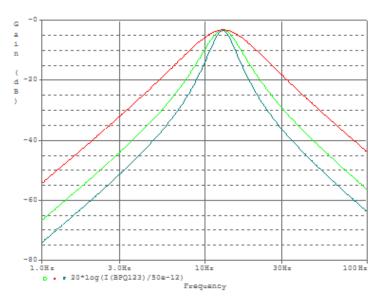

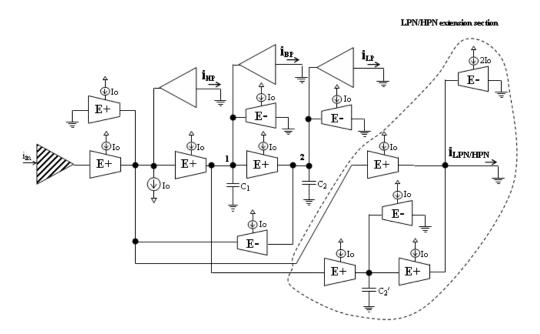

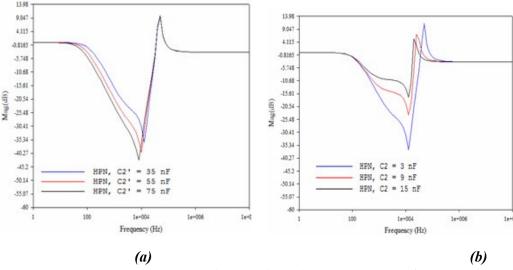

| Fig. 3.48: | Magnitude response of proposed LD multi-function biquad (a) Using   | 100 |

|            | ideal transistors (b) Using practical transistors.                  |     |

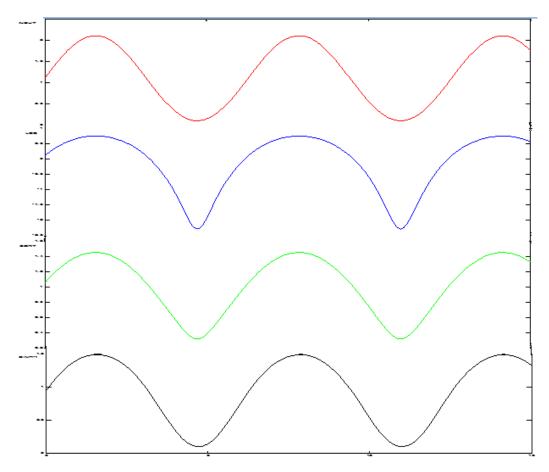

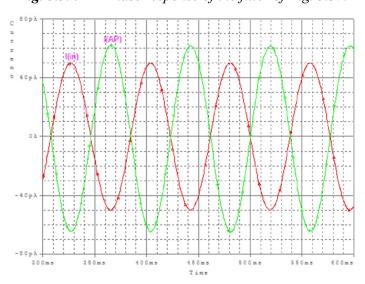

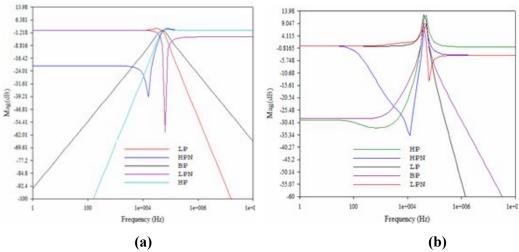

| Fig. 3.49: | Simulated input-output current waveforms of proposed LD multi-      | 100 |

|            | function biquad.                                                    |     |

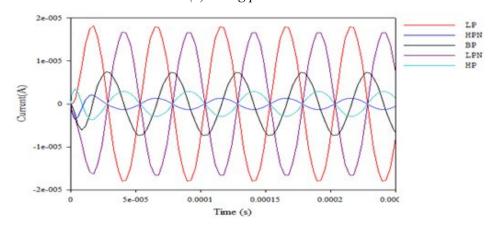

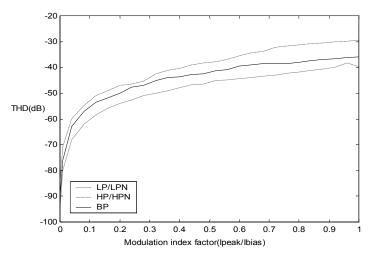

| Fig. 3.50: | Total harmonic distortion (THD) versus modulation index factor      | 100 |

|            | (Ipeak/Ibias).                                                      |     |

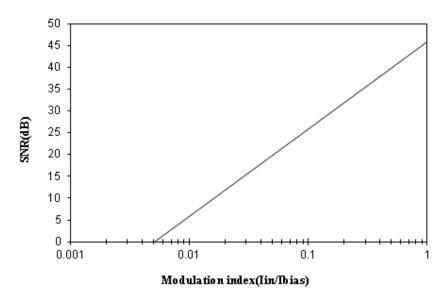

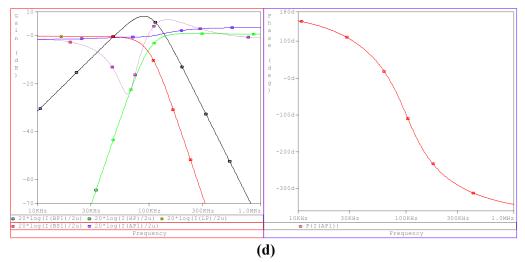

| Fig. 3.51: | Signal to noise ratio (SNR) versus modulation index factor (m).     | 101 |

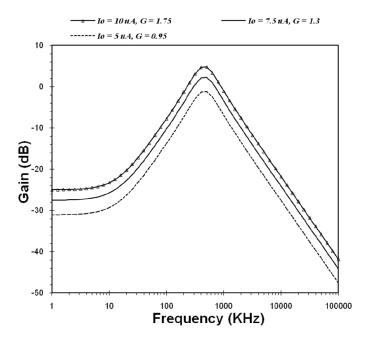

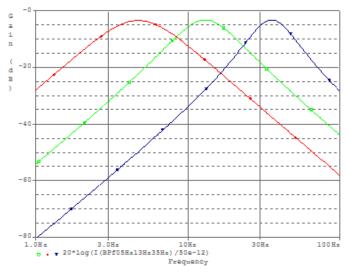

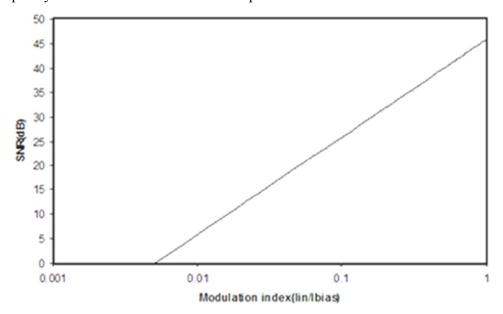

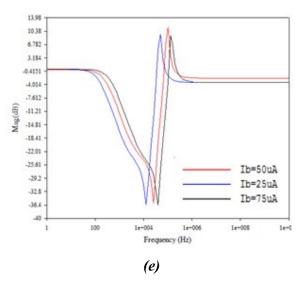

| Fig. 3.52: | Magnitude responses showing the electronic tunability of the        | 103 |

|            | proposed LD multi-function biquad. (a) LP (b) HP (c) BP (d) LPN (e) |     |

|            | HPN.                                                                |     |

| Fig. 3.53: | Magnitude responses showing the independent tuning of notch and     | 103 |

|            | cut-off/centre frequency (a) Fixed cut-off/centre frequency and     |     |

|            | varying notch frequency. (b) Fixed notch frequency and varying cut- |     |

|            | off/centre frequency.                                               |     |

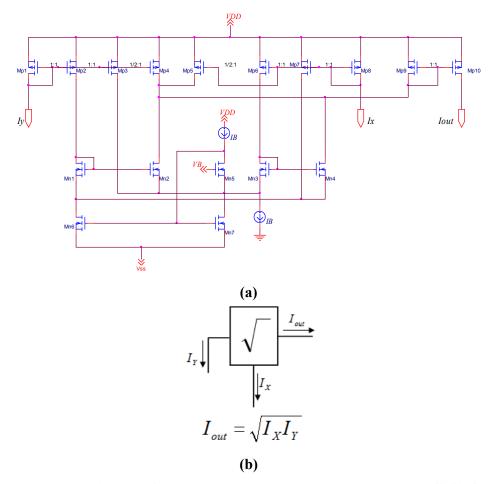

| Fig. 3.54: | (a) Low-voltage current square-root (geometric-mean) cell (b) the   | 107 |

|            | employed symbol.                                                    |     |

| Fig. 3.55: | Proposed low-voltage square-root-domain design of first-order AP    | 108 |

|            | filter.                                                             |     |

| Fig. 3.56: | Proposed low-voltage square-root-domain design of second-order      | 108 |

|            | AP filter.                                                          |     |

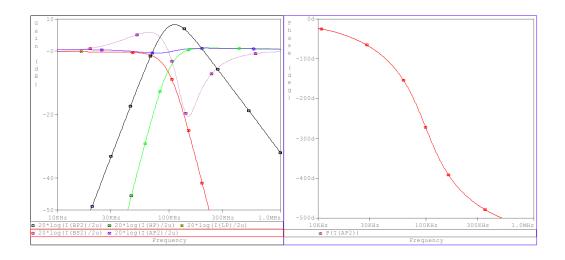

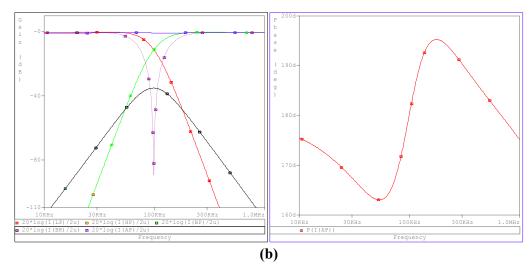

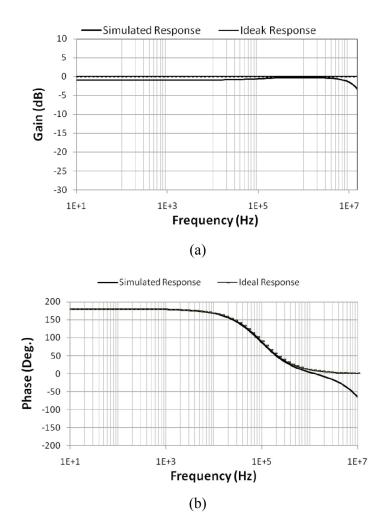

| Fig. 3.57: | Simulated Responses of first-order AP filter (a) Magnitude Response | 109 |

|            | (b) Phase Response.                                                 |     |

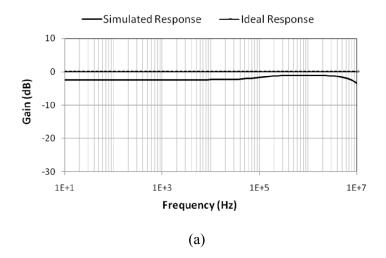

| Fig. 3.58: | Simulated Responses of second-order AP filter (a) Magnitude         | 110 |

|            | Response (b) Phase Response.                                        |     |

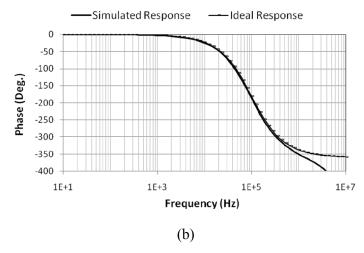

| Fig. 3.59: | Simulated Magnitude Responses of first-order LP filter and second-  | 110 |

|            | order BP filter.                                                        |     |

|------------|-------------------------------------------------------------------------|-----|

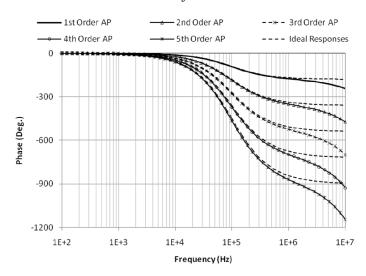

| Fig. 3.60: | Simulated Phase Responses of High-order AP filters.                     | 110 |

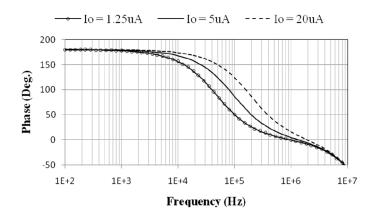

| Fig. 3.61: | Demonstration of electronic tunability of the proposed AP designs.      | 111 |

| Fig. 3.62: | Proposed LT Sinh-Domain equivalent of the LC resonators in Table        | 115 |

|            | 3.18.                                                                   |     |

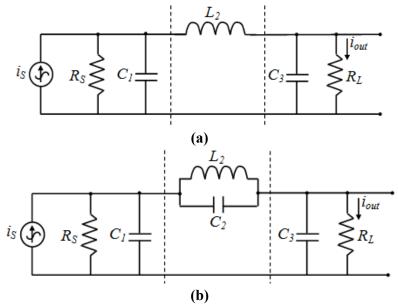

| Fig. 3.63: | 3rd-order LC ladder lowpass filters, (a) All-pole, and (b) Elliptic.    | 116 |

| Fig. 3.64: | 3rd-order Sinh-Domain LT filter topologies derived according to         | 116 |

|            | Table 3.18, (a) All-pole, and (b) Elliptic.                             |     |

| Fig. 3.65: | Simulated frequency responses of the filters in Fig. 3.63. (a) All-pole | 117 |

|            | (b) Elliptic.                                                           |     |

| Fig. 3.66: | Demonstration of electronic tunability, (a) All-pole, and (b) Elliptic  | 118 |

## LIST OF TABLES

| Table 3.1:         | The model parameters of NR100N NPN transistor used for                                 | 44  |

|--------------------|----------------------------------------------------------------------------------------|-----|

|                    | PSPICE simulations.                                                                    |     |

| <i>Table 3.2:</i>  | Standard 2 <sup>nd</sup> -order filter functions obtained for five outputs by          | 47  |

|                    | carefully selecting the input currents $i_{i1}$ , $i_{i2}$ and $i_{i3}$ .              |     |

| <i>Table 3.3:</i>  | Signs (Non-Inverting or Inverting) of the filter functions (HP is                      | 55  |

|                    | Inverting in all Configuration). (NA: Not Applicable, I:                               |     |

|                    | Inverting, NI: Non-Inverting, BP1: $BP_{(n/2)}$ , BP2: $BP_{(n+1)/2}$ , BP3:           |     |

|                    | $BP_{(n-1)/2}$ ).                                                                      |     |

| Table 3.4:         | Table demonstrating that the four configurations presented are                         | 56  |

|                    | the only stable ones.                                                                  |     |

| <i>Table 3.5:</i>  | Comparison of nonlinearity, component count and power                                  | 64  |

|                    | dissipation of MFFs of Fig. 3.17.                                                      |     |

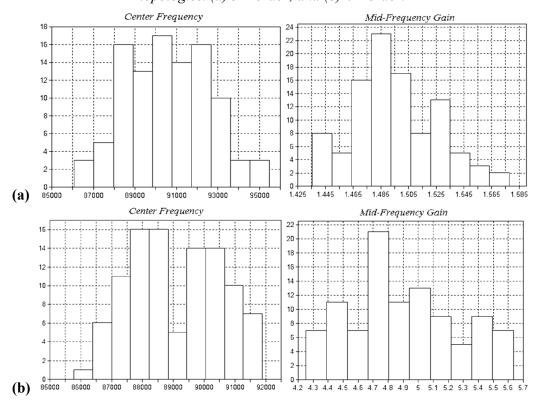

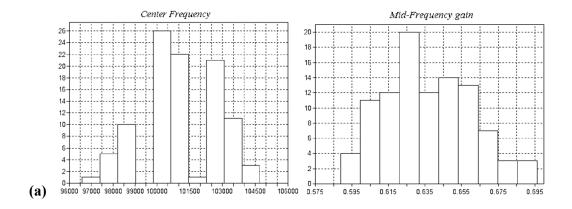

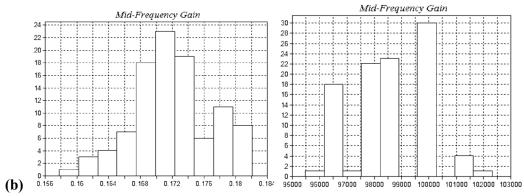

| <i>Table 3.6:</i>  | Statistical simulation results about the frequency behaviour of                        | 64  |

|                    | the LP filter functions of log-domain MFFs of Fig. 3.17.                               |     |

| <i>Table 3.7:</i>  | Comparison of non-linearity between the proposed design and                            | 67  |

|                    | Reference [54].                                                                        |     |

| <i>Table 3.8:</i>  | Comparison of component count and power dissipation between                            | 68  |

|                    | the proposed design and Reference [54].                                                |     |

| <i>Table 3.9:</i>  | Switch status condition for 3 <sup>rd</sup> and 4 <sup>th</sup> -MISO universal filter | 85  |

|                    | topologies.                                                                            |     |

| <i>Table 3.10:</i> | Aspect ratio of the MOS transistors of the geometric-mean block                        | 85  |

|                    | in Fig. 2.8.                                                                           |     |

| <i>Table 3.11:</i> | Performance comparison results for the proposed universal filter                       | 86  |

|                    | topologies (a) SIMO and (b) MISO.                                                      |     |

| <i>Table 3.12:</i> | Comparison results with the already published companding                               | 86  |

|                    | topologies.                                                                            |     |

| <i>Table 3.13:</i> | Brain waves classification [150].                                                      | 90  |

| <i>Table 3.14:</i> | Performance comparison results for the proposed Sinh-domain                            | 93  |

|                    | biquadratic filter.                                                                    |     |

| <i>Table 3.15:</i> | Simulated values of input current at $1\%$ THD, THD at $m=1$ and                       | 102 |

|                    | dynamic range for each of the three outputs.                                           |     |

| <i>Table 3.16:</i> | Aspect ratio of the MOS transistors of the geometric Mean                              | 111 |

## LIST OF TABLES

| DI |     | 7   |

|----|-----|-----|

| Вl | oc. | KS. |

| <i>Table 3.17:</i> | Results of performance factors for the proposed AP filters.       | 111 |

|--------------------|-------------------------------------------------------------------|-----|

| <i>Table 3.18:</i> | Proposed substitution scheme for the derivation of SD LT filters. | 113 |

AC Alternating Current

A/D Analog to Digital

AIC Analog Integrated Circuit

ANN Artificial Neural Networks

AP Allpass

BE Base Emitter

BiCMOS Bipolar Complementary Metal Oxide Semiconductor

BJT Bipolar Junction Transistor

BP Band Pass

BS/BR Band Stop/Band Reject

BSIM Berkeley Short-Channel IGFET Model

BTL Bipolar Translinear Loop

BW Bandwidth

C Capacitance

CCII Current Conveyor Second Generation

CW Clockwise

CCW Counter-clockwise

CFA Current Feedback Amplifier

CM Current Mode

CMOS Complementary Metal Oxide

CNN Cellular Neural Network

D/A Digital to Analog

dB Decibel

DC Direct Current

DR Dynamic Range

DSP Digital Signal Processing

E Cell Exponential Transconductance Cell

E+ Cell Positive Exponential Transconductance Cell

E- Cell Negative Exponential Transconductance Cell

EEG Electro-Encephalography

ELIN Externally Linear and Internally Nonlinear

EXP Exponential operator

FBD Function Block Diagram

FDM Frequency Domain Multiplexing

FLF Follow-The-Ladder-Feedback

FM Frequency Modulation

FOM Figure of Merit FT Filter Topology

FTFN Four Terminal Floating Nullor

GHz Gigahertz (10<sup>9</sup>)

GM Geometric-Mean

Gm-C Transconductance capacitance

GTL Generalized Translinear Loop

HP High Pass

HPN High Pass Notch<br/>IC Integrated Circuit

IF Intermediate-Frequency

IMD3 Third Order Intermodulation Distortion

ITRS International Technology Roadmap for Semiconductors

Is Saturation Current

I-V Current to Voltage

K Boltzman's Constant

KCL Kirchoff's Current Law

kHz Kilo Hertz

KVL Kirchoff's Voltage Law

L Inductance

LC Inductance Capacitance

LCR Inductance Capacitance Resistance

LD Log Domain

LOG Logarithmic operator

LP Low Pass

LPN Low Pass Notch

LT Linear Transformation

LTI Linear and Time-Invariant

LV Low Voltage

m Modulation Index

MFB Multifunction Biquad

MFF Multi-Function Filter

MHz Megahertz (10<sup>6</sup>)

MIMO Multiple-Input-Multiple-Output

MISO Multiple-Input-Single-Output

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOSFET-C Metal Oxide Semiconductor Field Effect Transistor-Capacitance

MTL MOS Translinear Loop

MV Mean Variance

mV Millivolt mW MilliWatt

nA Nano-Ampere nW Nano-Watt

OA Operational Amplifier

OTA Operational Transconductance Amplifier

P Power Dissipation

pF Pico-Farad

PSPICE Personal Simulation Computer Programme with Integrated Circuits

**Emphasis**

Q Quality factor q Electron Charge

R Resistance

RC Resistance Capacitance

RF Radio Frequency

RL Resistance Inductance

RLC Resistance Inductance Capacitance

SC Sinh-Cosh

SD Sinh-Domain

S/D Squarer/Divider

SFG Signal Flow Graph

Si Silicon

SIFO Single-Input-Four-Output

SIMO Single-Input-Multiple-Output

SINH Hyperbolic Sin operator

SINH<sup>-1</sup> Inverse Hyperbolic Sin operator

S/N or SNR Signal to Noise Ratio

SOC Systems-On-Chip

SQ Square operator

SRD Square-Root-Domain

SQRT Square-Root operator

SQRD Square-Root-Divider

STD Standard Deviation

T Temperature

TAM Trans-Admittance Mode

TDCNN Temporal-Derivative-Cellular-Neural-Network

TDM Time Domain Multiplexing

THD Total Harmonic Distortion

TIM Trans-Impedance Mode

TL Translinear loop

TSMC Taiwan Semiconductor Manufacturing Company

$V_{\text{BE}}$ Base emitter voltage  $V_{\text{CC}}/V_{\text{DD}}$ Positive Supply Voltage  $V_{CE}$ Collector Emitter Voltage  $V_{DS}$ Drain Source Voltage  $V_{EE}/V_{SS}$ Negative Supply Voltage Gate Source Voltage  $V_{GS}$ V-I Voltage to Current VMVoltage Mode

VOA Voltage Operational Amplifier

$V_T$  Thermal Voltage  $V_{TH}$  Threshold Voltage

VLSI Very Large Scale Integration

WIMOSFET Weak Inversion Metal Oxide Semiconductor Field Effect

Transistor

W/L Aspect Ratio of MOSFET

xDSL Digital Subscriber Line (of any type)

$\omega_0$  Resonant/Pole frequency

<sup>0</sup>C Degree Celcius

μ Mobility

μA Micro-Ampere μm Micro-Meter

#### INTRODUCTION

# 1. 1. State-of-the-Art Low-Voltage Low-Power Analog Design and its Applications

Indoubtedly, the remarkable performance of contemporary integrated electronic systems is attributed to the rapid advancements achieved in digital technology. The main advantage of digital circuit design is its abstraction from the physical details of the actual circuit implementations. Furthermore, digital circuitry is comparatively insensitive to the variations in the manufacturing process and the operating conditions. Consequently, digital circuits frequently offer a more robust behaviour than their analog counterparts, albeit often with area, power and speed drawbacks. Last but not the least, digital designs allow functional complexity that may not be possible in analog technology based circuits. Due to these and other benefits, analog functionality has been increasingly replaced by digital implementations.

In spite of the trends discussed above, analog components are far from obsolete. In fact, a closer look reveals that they are key components of modern electronic systems. There is a definite trend toward pervasive and ubiquitous use of electronic circuits in everyday life. In fact, analog circuits are needed in many VLSI systems such as filters, D/A and A/D converters, voltage comparators, current and voltage amplifiers, etc. Moreover, new applications continue to appear where new analog topologies have to be designed to ensure the trade-off between speed and power requirements. Wearable and Biomedical Electronics, wireless communications and the widespread application of RF tags are just some examples of current developments. While all of these electronic systems are based on digital circuitry, but they heavily rely on analog components as interfaces to the "real", i.e. analog world. In fact, many modern designs combine powerful digital systems and complementary analog systems on a single chip for cost and reliability reasons.

Further, the rapid improvement of circuit functionality has only been possible due to dramatic increase in the achievable integration densities. The corresponding permanent shrinkage of realizable circuit structures, however, is a mixed blessing. While it is desirable from the integration point of view, but it promotes more and more nonlinear physical phenomena which have only had minor impact so far. Therefore, many simplifying assumptions no longer hold, which complicates the

design of electronic circuits. In fact, not only the analog domain is affected, but digital design is also increasingly becoming aware of physical effects.

Therefore, the development of monolithic VLSI technology, has led to renewed interest in analog circuit design, especially concerning integrated circuits. The main aim of analog integrated circuits (AICs) is to satisfy circuit specifications through circuit architectures with the required performance. Thus, the Low-voltage (LV) low-power (LP) AICs design has been the focus of the contemporary research, especially in the areas of portable systems where a low voltage single-cell battery with longer lifetime has to be used. Portable and miniaturized system-on-chip applications exhibit an increasing demand in the microelectronics market and, particularly, in the biomedical field with products such as hearing aids, pacemakers or implantable sensors. System portability usually requires battery supply, except in some special cases such as RF-powered telemetry systems. Unfortunately, battery technologies do not evolve as fast as applications demand, so the combination of battery supply and miniaturization often turns into a low-voltage and/or low-current circuit design problem. In particular, these restrictions affect more drastically the analog part of the whole mixed system-on-chip. As a result, specific analog circuit techniques are needed to cope with such power supply limitations.

A short description of the specific circuit approaches for low-voltage operation is listed below:

<u>Rail-to-Rail</u> includes all strategies oriented to extend the signal voltage range up to the available room between supply rails. Most of them are mainly based on the redesign of the input and output stages in order to increase their linear range [1-5].

<u>Multistage</u> stands for multiple but simple cascaded stages instead of single cascoded structures. Efforts are then focused on their frequency stabilization with nested compensating loops [6, 7].

<u>Bulk-Driven</u> strategies make use of the MOSFET local substrate as an active signal terminal to obtain lower equivalent threshold voltages [8, 9].

<u>Supply Multipliers</u> bypass the low-voltage restriction by performing a step-up conversion of supply voltage through charge pumps [10-17], typically from 1.5V to 3V.

The said low-voltage techniques have the following drawbacks:

- ✓ All the low-voltage strategies except those using supply multipliers are actually partial solutions since they are addressed mainly to the design of operational amplifiers only.

- ✓ The bulk-driven option is also in opposition to general anti-latch-up rules of any standard CMOS process.

- ✓ Although supply multipliers are the only global and perhaps the most used solution for very low-voltage operation, they need large capacitive components, take an important Si area overhead and exhibit high extra current consumption, which make them not suitable for small package and low-current applications.

In a similar way, the main circuit techniques for low-current consumption applications are enumerated as follows:

Adaptive Biasing is based on non-static current bias to optimize consumption according to signal demands. Bias dynamics are defined either by local positive feedback [18, 19] or by feedforward [20, 21] controls.

<u>Subthreshold Biasing</u> of classic topologies by operating their MOS transistors in the weak inversion region at very low-current levels [22].

In addition to the techniques mentioned above, LV LP AICs have been achieved by substituting traditional voltage-mode techniques by the current-mode techniques, which have the recognized advantage to overcome the gain-bandwidth product limitation. Therefore, many current-mode techniques came into existence and Companding-mode design is one such technique for AICs.

#### 1.2. Active Filter Design: An Introduction

An electric filter is a two port frequency selective network that shapes the spectrum of the input signal in such a manner that desired frequency content is achieved in the output signal. It is used to separate, pass or suppress a group of signals from a mixture of signals. The applications of filters are to eliminate contamination such as noise in communication systems and to separate relevant frequency components from irrelevant frequency components. Filters are also used to detect and demodulate signals in radio and television. Another important application is to band-limit signals before sampling and to convert discrete time signals into

continuous time signals. Filters are also employed for improving quality of audio equipment, conversion of time-domain multiplexed (TDM) signals into frequency domain multiplexed (FDM), speech synthesis, equalization of transmission lines and cables, and numerous other applications.

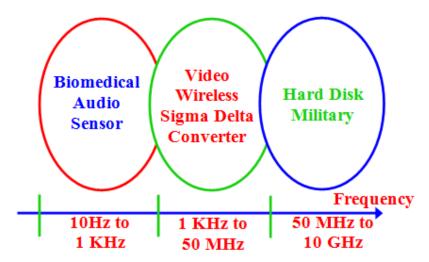

In the systems that interface with real word, the processed signal would be measured with unwanted noise. A filter is usually used to get rid of the unwanted noise and to reject the surrounding interface. Thus, filters are important blocks for specified frequency of signals and are essential for many applications. They can be used to band-limit signals in wireline and wireless communication systems. These filters operate on continuous-time fashion because the systems interface with real analog world. Fig. 1.1 shows the operating frequency ranges of the filter for various applications.

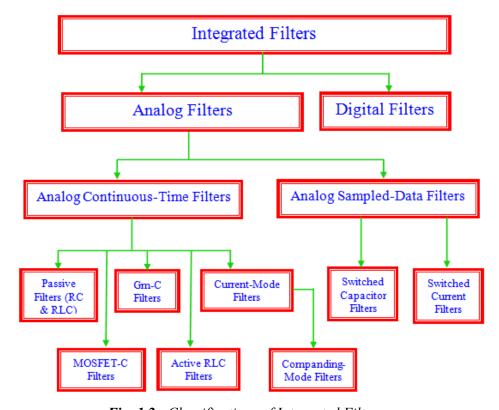

Integrated filters can in general be classified into two types: Analog and Digital, which in turn can be classified into various types as depicted in Fig. 1.2. The analog filters process the continuous data rather than the digital data for digital filters. The analog filters can be further divided into passive and active filters. The elements of a passive filter are passive which includes resistors, capacitors, inductors, and transformers. Other passive elements like distributed RC components and quartz crystals are also used. On the contrary, active filters include active devices with or without lumped passive components. The active devices can range from single transistors to integrated controlled sources such as Operational Amplifier (OA), and more exotic devices, such as the Operational Transconductance Amplifier (OTA), Current Conveyor (CC) and its variants, Current Feedback Amplifier (CFA), Four Terminal Floating Nullor (FTFN) etc. A large area is required for the construction of passive filter, while active filters are more suited for CMOS technology.

The Active-RC and Switched-Capacitor filters are suitable only for low to medium frequency applications. For high frequencies, the settling problem of amplifiers would affect the filter performance since very wide bandwidth and high unity-gain frequency are hard to achieve. For systems in the GHz range, LC filters are a better choice since the required values of L and C are small. However, Q enhancement is needed for LC filters because of low inductor quality factors. The Gm-C filters, which operate on open loop topology, would be sufficient for low to high frequency range. Thus, the Gm-C architecture can be implemented for various

applications. However, the performance of Gm-C filter is highly dependent on the performance of the transconductor. Another issue is the automatic tuning of circuit pertinent performance factors. The frequency response and the quality factor should be maintained owing to process, supply voltage and temperature variations. Thus, a high performance automatic tuning circuit is required for continuous-time active filters.

#### 1.2.1. Filter Classification

Depending upon the type of separation, filters are classified as Low Pass (LP), High Pass (HP), Band Pass (BP), Band Stop (BS), and Allpass (AP).

Depending upon the "roll off" of magnitude response in the transition band, filters are classified as first order, second order and High-order. The order of a filter is an integer number, which defines the complexity of the filter. In filters, the order of the filter is the highest power of s in denominator of its transfer function. The order of the filter can be estimated from the number of reactive elements it contains. Depending upon the type of filter approximations, filters are classified as Butterworth, Chebyshev-1, Chebyshev-2, Elliptic etc.

Depending upon the nature of input and output signals, filters are classified as Voltage-Mode (VM), Current-Mode (CM), Trans-Impedance Mode (TIM) and Trans-Admittance Mode (TAM).

In order to increase the speed of circuits for analog signal processing and to decrease the supply voltages of integrated circuits, designers devote their attention to the so-called current mode. It means-simply speaking – that the individual circuit elements should interact by means of currents not voltages [23]. In this mode of circuit description the input and output are both taken in the current form rather than in voltage form. CM signal processing can be defined as the processing of current signals in an environment where voltage signals are irrelevant in determining circuit performance. This may be the case in which circuits are designed to operate with low impedance nodes such that the voltage swings are small and time constants are short. Choosing low impedance levels, sufficiently small voltages can be achieved with the aim to eliminate the influence of Miller's capacitance and other non-idealities. In CM circuit, current is used as the active variable in preference to voltage, either throughout the whole circuit or only in certain critical areas.

Fig. 1.1: The operating frequency ranges of filter for various applications.

Fig. 1.2: Classifications of Integrated Filters.

For many years, electronic engineers seem to have been subconsciously persuaded that the world is voltage dominated; that amps are somehow subservient to volts. In electronic circuit design this is somewhat surprising, since both bipolar and field effect transistors are essentially devices exhibiting controlled output currents. The idea of voltage domination is reinforced by the fact that manufacturers produce a

wide range of integrated amplifiers whose aim is to reproduce a controlled voltage output from a voltage input. Circuits marketed for the purpose of controlling current are much less useful vis-à-vis the performance of a typical integrated transconductance amplifier not withstanding early introduction of 741 OA. This lapse is unfortunate, since experience has shown that current mode circuits synthesized from standard voltage operational amplifiers (VOAs) can produce better system performance than the original VOAs used in an equivalent voltage mode operation.

Recent advances in integrated circuit technologies aimed at state-of-the-art analog IC design are now able to explore the potential of current-mode analog signal processing, providing attractive and elegant solutions for many circuit and system problems. In addition to current conveyors themselves, such circuits range from voltage-to- current converters through translinear circuits and current-mode rectifiers to neural computation and many new amplifier topologies. For many of the applications, current-mode approach enables achievement of superior performance, even in cases where circuits have been synthesized from voltage-mode components due to the lack of suitable alternatives.

The current-mode circuits possess the following potential advantages compared with voltage-mode ones:

- **A. Higher bandwidth capability:** bipolar junction transistors and field effect transistors are both current output devices. A key performance feature of the current-mode processing is inherent wide bandwidth and as current amplifier the transistor is useful almost up to its bandwidth f<sub>T</sub>. The stray capacitances can be usefully employed as gain element at higher frequencies [24], whereas they limit the bandwidth in voltage-mode circuits.

- **B. Higher operating speed:** the shrinking dimensions of integrated circuit techniques lead to circuits whose parasitics are predominately capacitive. Current-mode circuit can achieve high speed signaling at low impedance internal nodes and low voltage swing due to minimal capacitive charging and discharging.

- C. Low circuit complexity for analog arithmetic computations: in the current domain, computations like addition and subtraction can be performed directly by joining the terminals at a single node. With the current mirror structure, the basic functions of inversion, scaling and summation can be implemented conveniently. In contrast to the voltage-mode counterpart, this needs an operational amplifier for

- realizing the same functions. It is clear that current-mode realization possesses low circuit complexity and the possibility of low power consumption.

- **D.** Greater operating dynamic range: as the shrinking device feature size of integrated technology, the supply voltage has to be reduced in order to ensure device reliability. The reduced voltage supply levels result in reduced dynamic range. An attempt to overcome this problem is simply to change the signal representation from a voltage to current. In this way the signal range is no longer directly restricted by the supply voltage but dependent on the impedance level chosen by the designer [25].

#### 1. 3. Background and Motivation

Frequency filtering networks are among the most important and widely used electronic devices, with numerous applications in analog, digital, and mixed-signal consumer products. Filters generally fall into three broad categories: fully digital, sampled-data and continuous-time. Digital filters are suited for lower frequency applications and are becoming more and more popular, as they can be easily incorporated inside the DSP core of an integrated circuit. Sampled-data filters use sampling techniques to realize analog filtering. This technique is ideally beneficial for data converters. Sample-data filters usually use MOS technology which allows them to be integrated on the same chip as the digital circuit. Continuous-time filters play an important role in filter design; no other type of filter can be used when dealing with high-frequency, low-voltage systems. Consequently, analog filters have become the most popular choice for the wireless industry.

Integrated continuous-time active filters are the class of continuous-time or analog circuits which are used in various applications like channel selection in radios, anti-aliasing before sampling, and hearing aids etc. One of the figures of merit of a filter is the dynamic range; this is the ratio of the largest to the smallest signal that can be applied at the input of the filter while maintaining certain specified performance. The dynamic range required in the filter varies with the application and is decided by the variation in strength of the desired signal as well as that of unwanted signals that are to be rejected by the filter. It is well known that the power dissipation and the capacitor area of an integrated active filter increases in proportion to its dynamic range [26]. This situation is incompatible with the needs of integrated systems,

especially battery operated ones. In addition to this fundamental dependence of power dissipation on dynamic range, the design of integrated active filters is further complicated by the reduction of supply voltage of integrated circuits imposed by the scaling down of technologies to attain twin objective of higher speed and lower power consumption in digital circuits. The reduction in power consumption with decreasing supply voltage does not apply to analog circuits. In fact, considerable innovation is required with a reduced supply voltage even to avoid increasing power consumption for a given signal to noise ratio (S/N). These aspects pose a great hurdle to the active filter designer.

A technique which has attracted attention as a possible route to filters with higher dynamic range per unit power consumption is *companding* [27, 28]. Traditionally companding has been applied to memoryless systems with a dynamic range limited channel (e.g. in telephony). The key idea is to ensure that the signal in the channel stays sufficiently above noise. To ensure this, pre-amplification is applied. However, it is necessary to avoid overloading the channel as well and for this reason, large signals are pre-amplified by much smaller amounts than small signals. Thus the entire dynamic range of input signals is amplified by appropriate amounts depending on their strength so that they are near the top of the channel's dynamic range. To restore the output of the channel to the original input levels, the opposite, i.e. small gain for small signals and large gain for large signals is applied. Depending on whether the gain is made to depend on the instantaneous value or the average value of the signal, the companding can be called "Instantaneous" or "Syllabic" respectively [29].

Merely substituting a filter in place of the channel with either type of input and output amplifiers described above results in a system that is not linear and time-invariant between its input and output. This general problem of applying companding to filters while maintaining input-output linearity and time-invariance has been solved earlier [28, 30-32]. Several practical implementations have been published as well. While some of them have significantly improved dynamic range per unit power consumption compared to traditional active filters, it is thought that companding can do much better. It is in fact hoped that companding filters can be realized with lower power consumption per dynamic range than *passive RC/RLC* filters which are

assumed to be operating at the fundamental lower limit [26] of power consumption for a given dynamic range.

### 1.4. History and state of the art of Companding filters

Instantaneous companding has been studied in detail during the last three decades. The earliest form of externally linear and internally nonlinear (ELIN) instantaneous companding filters, dubbed "Log-Domain (LD)" filters due to their use of logarithmic nonlinearity of diodes date back to 1978 [33]. The motivation was not companding, but wide tuneability of filter parameters. [31] presented a compact realization of first-order LD filters using translinear loops [34, 35] and through the use of class-AB circuits for high dynamic range, connected them to the concept of companding filters introduced in [27]. To date, LD filters have been the most thoroughly investigated species of companding filters. LD filters received a systematic treatment in [32] in which they were shown to be synthesizable using exponential mappings of state variables in the state equations of linear filter prototypes. Since then, several papers dealing with their analysis and synthesis based on the LC ladder simulation [36, 37], one-one substitution or use of new cells [38, 39] or analysis of translinear circuits [40] have been published. A state space formulation for class-AB LD filters, which are a class of filters capable of large dynamic range, was presented in [41]. [42] presented a LD filter with syllabic companding. This was however still based on the formulation of [43]. [44] presented a technique for syllabic companding using dynamic biasing that is unique to LD filters and is much simpler to implement than [42]. The potential increase in the dynamic range of syllabicallycompanding filters was illustrated in [45]. [46] presented a class-AB LD filter in BiCMOS technology which outperformed most published filters in terms of dynamic range per unit power consumption by a large factor. [47] deals with programmable LD filters. The critical issues related with the design of LD filters such transistor Nonidealities and DC stability, are addressed in [48-52]. The above are a few examples of the published works in the area of LD filters. LD filters at very high frequencies of hundreds of MHz to a GHz are explored in [51, 52]. The field of LD multifunction or universal filter design is almost untouched and is one of the present research trends in the LD design. In [53] a 1<sup>st</sup>-order LD multifunction filter is given. In [54], the micropower LD universal biquad is discussed. Both methods mentioned above for the realization of LD multifunction filters cannot be extended to high-order multifunction filters as their cascade leads to single-function filters. In [55] a systematic approach is given which can be extended to high-order LD multi-function filter design. In [56] a MISO LD multifunction filter is given. Besides this, steadfast endeavour is carried out on the realization of high-order LD filters [57, 58], high-order multifunctional filter design and improved building blocks [59, 60]. In [61-63] high-order multifunctional filter design is given.

The concept of "LD filtering" has been extended to the MOS transistors in weak-inversion, due the fact that a similar I-V exponential relationship holds. A number of LD filter realizations using MOS transistors have been presented in the literature. This is achieved by a direct transformation of the corresponding implementations based on bipolar transistors, into MOS transistors realizations using component-to-component substitution [64]. The main drawbacks of these topologies are the increased effect of transistor mismatches and the limited speed of operation, both originated from the operation mode of the MOS transistor. In order to overcome the above imperfections a new subclass of translinear filters, named "Square-Root-Domain (SRD) filters," was introduced. In this case, the main concept is based on the well-known quadratic I-V relationship for the MOS transistor operated in saturation and on the MOS translinear principle. A number of SRD circuits, including integrators, oscillators, etc., were presented in the literature [65]–[71]. Second-order SRD lowpass and/or bandpass filter topologies have been already published in the open literature [70, 72–76]. Besides, a novel n-th order follow-the-leader feedback (FLF) SRD filter topology is introduced in [77].

The final class of instantaneous companding filters is called Sinh-Domain (SD) filter obtained through the inverse of the hyperbolic sine function realized by translinear loops formed by bipolar transistors in active region or MOS transistors in weak inversion. SD filtering is an important technique for realizing analog filters with inherent class-AB nature. This is originated from the fact that the required current splitting is simultaneously realized with the compression of the linear input current and its conversion into a non-liner voltage. This is not the case in the LD filters, where a pseudo class-AB operation is realized by establishing two identical class-AB signal paths and employing a current splitter at the input of the whole filter. The produced intermediate output currents are then subtracted in order to derive the final

output of the filter. Besides, SD filtering offers the benefits of companding circuits like electronic adjustment of their frequency characteristics because the realized time-constants are controlled by a dc current and capability of operation under a low-voltage environment. Compared with their corresponding LD and SRD counterparts, SD offer more power efficient filter realizations but price that may be paid is an increased circuit complexity [32, 78-85].

#### 1.5. Companding filter design for portable system applications

With the inception of companding filters, researchers continuously worked on their applications and the endeavor is still in vogue. Since from the last two decades, there is an incredible attraction towards portable system applications, the companding filters were driven by the same force and a number of companding filter applications for the portable systems came into existence. The companding filters work on the compression-expansion principle and the compression/expansion operators are Log/Exponential or Square-root/Square or Sinh-1/Sinh provided by either the BJTs operating in active region or MOSFETs operating in weak inversion or saturation regions. So, the exactness of the companding filters is restricted to that of the compression-expansion operators. Unfortunately, the I-V relationships corresponding to the compression-expansion operators of the mentioned devices remain valid for low (SRD/SD) to high (LD/SD) frequencies only. However, the companding filters found many applications in the said frequency range. Towards this end, the companding filters were effectively used in the Biomedical and low frequency applications [86-92]. Mentioning few of them, companding filters were used to: design Cardiac Sense Amplifier for Pacemakers [93], circuit which mimics the oscillations observed during the biochemical process of glycolysis due to the phosphor fructokinase enzyme [94], gain control circuits and filters for Hearing aids and Cochlear Implant Channels [83, 95-98]. In addition, companding filters were used to design circuits for: Passive Telemetry [99], Electret Microphones [100], Audio Filter [101] and DECT cordless transmit path applications [102]. Moreover, companding filters were used in telecommunication applications to reject the undesired image signals, caused by the down-conversion operation in low Intermediate-Frequency (IF) radio transceiver architectures [103, 104].

Furthermore, during the last three decades, owing to large application area, a significant amount of research has been carried in the artificial neural networks

(ANNs) and Cellular Neural Networks (CNNs). The key features of neural networks are asynchronous parallel processing, continuous-time dynamics, and global interaction of network elements. Unfortunately, most of these features are not met by their software designs. Therefore, there has been considerable interest in the hardware based designs of ANNs and CNNs [105, 106]. Towards this end, companding filters were used to give the LV LP designs of Neuron models [107-110]. Last but not the least, companding filters have been used to design complex Temporal-Derivative-Cellular-Neural-Networks (TDCNNs). TDCNN initiates time derivative 'diffusion' between CNN cells for non-separable spatiotemporal filtering applications, where the input to the CNN is an image that changes over time [111].

#### 1.6. Thesis Outline

This thesis will describe the synthesis of low-voltage low-power companding filters and their possible applications in the portable systems. The contents of this work have been organized as follows:

Chapter 1 presents an overview of the low-voltage low-power analog integrated circuits and their applications, context of the work and its motivations.