| Title                          | Integrable bias solution for avalanche photodiodes                                                                                                                                                                                                                                                |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)                      | Deng, Shijie; Morrison, Alan P.                                                                                                                                                                                                                                                                   |

| Publication date               | 2011-02-24                                                                                                                                                                                                                                                                                        |

| Original citation              | Deng, S. and Morrison, A. P. (2011) 'Integrable bias solution for<br>avalanche photodiodes', Electronics Letters, 47(4), pp. 240-241,<br>http://digital-library.theiet.org/content/journals/10.1049/el.2010.3270.                                                                                 |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                           |

| Link to publisher's<br>version | http://digital-library.theiet.org/content/journals/10.1049/el.2010.3270<br>http://dx.doi.org/10.1049/el.2010.3270<br>Access to the full text of the published version may require a<br>subscription.                                                                                              |

| Rights                         | © The Institution of Engineering and Technology. This paper is a<br>postprint of a paper submitted to and accepted for publication in<br>Electronics Letters and is subject to Institution of Engineering and<br>Technology Copyright. The copy of record is available at IET<br>Digital Library. |

| Item downloaded<br>from        | http://hdl.handle.net/10468/6385                                                                                                                                                                                                                                                                  |

Downloaded on 2019-01-07T06:02:53Z

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

## An integrable bias solution for avalanche photodiodes

S. Deng and A. P. Morrison

A bias circuit for avalanche photodiodes (APDs) based on a dual-rail charge pump configuration operating from a 5 V supply that is capable of supplying a bias voltage in excess of 50 V is presented. For shallow-junction planar APDs that operate between 25 V and 45 V this circuit is capable of delivering more that 50 mW of power, allowing avalanche currents in the mA range. The circuit design requires only 2 external load capacitors, while the rest of the circuit can be implemented as an application specific integrated circuit (ASIC) which makes the circuit highly integrable. The bias voltage can be accurately controlled and easily adjusted by the end user using the shunt regulator incorporated for voltage control.

Introduction: Avalanche photodiodes are used in wide range of low-light sensing applications such as astronomy, DNA sequencing, quantum key distribution, LIDAR and medical sensing. Planar APDs have been developed over a number of years by many organisations for low-light sensing applications requiring both linear, multiplicative and Geiger-mode operation [1], [2]. Typically these APDs are designed with a breakdown voltage less than 30 V. The difficulty that remains is the requirement to bias these devices at voltages in excess of the voltage requirements for the rest of the sensing system. Existing APD-based sensing solutions use external high-voltage supplies or a DC-DC converter chip with significant additional external circuits to bias the APD. There are also some commercially available chips on the market specifically designed for biasing APDs, such as [3], [4]. These chips, however, require several external discrete components to function correctly, thereby limiting their usefulness in compact or integrated applications.

This paper describes an adjustable bias circuit that is capable of delivering more than 50 V with more than 50 mW output power in the bias range from 25 V to 45 V. The circuit uses a dual-rail charge pump (positive and negative charge pump) to generate the high bias voltage and includes shunt regulators to control the magnitude of the voltage. The circuit is designed using standard CMOS process design rules and requires only two external load capacitors. The combination of ASIC, APD and external capacitors can all be hybridly integrated in a single package to operate seamlessly from a 5 V supply, thereby taking the additional responsibility for biasing the APD from the end-user.

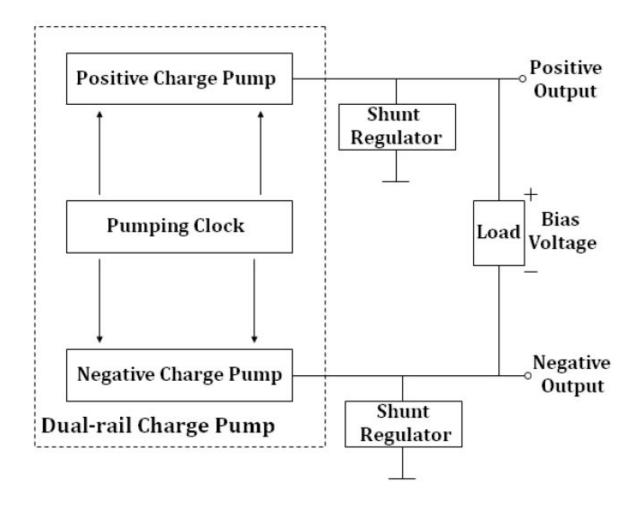

*Circuit Description:* An overview of the bias voltage circuit is shown in Fig. 1 and consists of two main parts: (i) A dual-rail charge pump which provides the high bias voltage for the load. (ii) Two shunt regulators which are used to control the output voltage for the positive and negative nodes of the load.

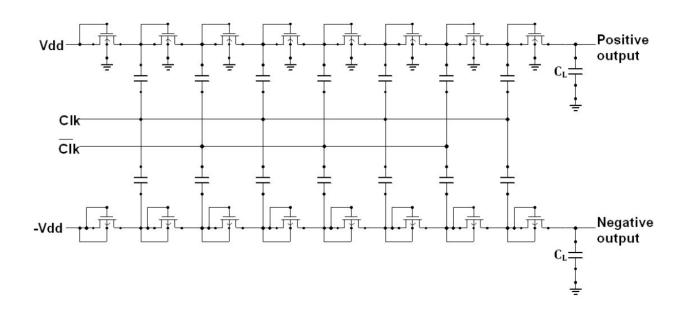

Fig. 2 shows the schematic of the dual-rail charge pump. The positive and negative charge pumps used in Fig. 2 are Dickson pump circuits [5]. The MOS transistors in the circuit are connected in diode fashion. The neighbouring pumping capacitors are connected to two inverse pumping clocks. NMOS is used for the positive charge pump to transfer the positive charge. PMOS is used for the negative charge pump to transfer the negative charge [6]. The charge is sourced from the system power supply,  $V_{dd}$  or  $-V_{dd}$ . Through every stage, the output voltage is increased or decreased by the pumping clock. At the output, a higher potential exceeding the magnitude of the system supply is obtained.

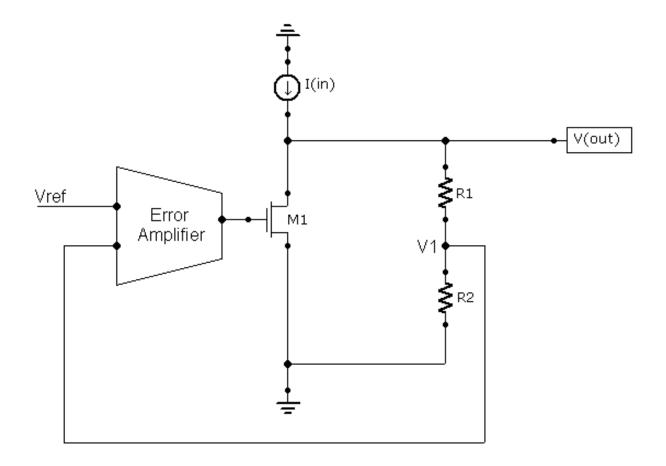

For maximizing output current, shunt regulators are needed to control the output of the charge pump. With the shunt regulator, the charge pump operates continuously. Fig. 3 shows the schematic of the shunt regulator. This regulator uses a MOS transistor (NMOS for positive output and PMOS for negative output) in parallel with the load and behaves functionally like a variable current divider to obtain load voltage regulation [7]. R1 and R2 are used to decrease the output voltage to a comparable level V<sub>1</sub>. A two-stage op amp is used as the error amplifier. A power supply of V<sub>dd</sub> and GND are used for amplifying the positive error, a power supply of GND and -V<sub>dd</sub> is used for amplifying the negative error. If V<sub>1</sub> exceeds the regulation level V<sub>ref</sub>, the error amplifier generates an output voltage proportional to the difference between V<sub>ref</sub> and V<sub>1</sub> and the MOS transistor will be biased to divide the output current. If the output falls below the regulation level, the MOS transistor will be turned off, and the output can be continuously charged up. In this way, V<sub>1</sub> can be set equal to V<sub>ref</sub>. By setting the reference voltage V<sub>ref</sub>, the output voltage can be altered.

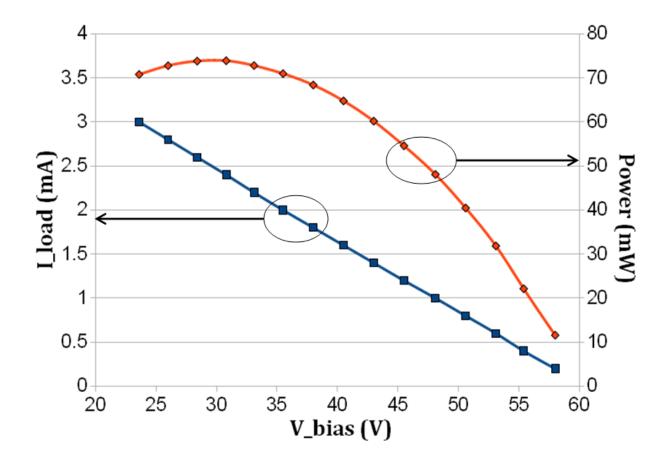

*Simulations:* A 7-stage dual-rail charge pump with shunt regulators was designed. The pumping capacitors are 20 pF. The two load capacitors are 3 nF each and are the only external components required for this design. The simulations were completed using Austria Microsystem's 0.35  $\mu$ m CMOS process running in the Cadence design environment. The clock frequency is 50 MHz with V<sub>dd</sub> = V<sub>clk</sub> = 5 V. Simulation results show that the bias voltage can be regulated accurately with a peak-peak ripple of 25 mV. Fig. 4 shows the maximum load current and output power for different bias voltages. From the simulations it is clear that the circuit is capable of meeting load current demands in excess of 1 mA at bias voltages up to 45 V.

*Conclusions:* This paper describes an adjustable bias circuit which can provide in excess of 50 V for biasing planar APDs. Simulations show the output bias voltage can be adjusted precisely and can sustain mA current output when operating

between 25 V and 45 V. This circuit can be hybrid integrated with the APD and 2 surface mount external capacitors in a single package (TO-can or Dual-in-line) which is very attractive for applications requiring a compact integrated APD device solution. *Acknowledgments:* This work was supported by Science Foundation Ireland under Grant 07/SRC/I1173.

## References

- J. C. Jackson, J. Donnelly, B. O'Neill, A-M. Kelleher, G. Healy, A. P. Morrison, and A. Mathewson. 'An integrated bulk/SOI APD sensor: bulk substrate inspection with Geiger-mode avalanche photodiodes', IET Electronics Letters, Vol. 39, No. 9, pp. 735-736, May 2003.

- 2 A. M. Moloney, A. P. Morrison, J. C. Jackson, A. Mathewson, J. Donnelly, B. O'Neill, A-M. Kelleher, G. Healy, and P. J. Murphy. "Monolithically integrated avalanche photodiode and transimpedance amplifier in a hybrid bulk/SOI CMOS process", IET Electronics Letters, Vol. 39, No. 4, pp. 391-392, February 2003.

- 3 http://www.maxim-ic.com/app-notes/index.mvp/id/1831

- 4 http://cds.linear.com/docs/Datasheet/3571fa.pdf

- 5 J. F. Dickson: 'On-chip high voltage generation in MNOS integrated circuits using an improved voltage multiplier technique', Vol. SC-11, No. 3, pp. 374-378, 1976.

- Feng Pan and Tapan Samaddar: 'Charge Pump Circuit Design', ISBN:

9780071491426, McGraw-Hill Professional, 2006.

- Jiann-Jong Chen, Ming-Shian Lin, Che-Min Kung and Yuh-Shyan Hwang:

'Low-Quiescent-Current Fast-Response Current-Feedback Shunt Regulator',

IEEE Asia Pacific Conference on Circuits and Systems, Page(s): 530-533,

December 2008.

## Authors' affiliations:

S. Deng and A. P. Morrison (Department of Electrical and Electronic Engineering, University College Cork, College Road, Cork, Ireland and Photonics Centre,Tyndall National Institute, Dyke Parade, Cork, Ireland)

E-mail: a.morrison@ucc.ie

## Figure captions:

Fig. 1 Block-diagram of overall bias circuit solution

Fig. 2 Schematic of Dual-rail Charge Pump

Fig. 3 Schematic of Shunt Regulator

Fig. 4 Simulation results of maximum load current and output power for different bias voltages

Figure 1