## UNIVERSITAT POLITÈCNICA DE CATALUNYA

MASTER THESIS

# On the Impact of Heterogeneous NoC Bandwidth Allocation in the WCET of Applications

*Author:* Jordi Cardona Nadal Supervisors: Dr. Carles HERNANDEZ LUZ Dr. Jaume ABELLA FERRER Dr. Francisco J CAZORLA ALMEDIA

*A thesis submitted in fulfillment of the requirements for the degree of Master in Innovation and Research*

in the

Facultat d'Informàtica de Barcelona (FIB) Departament d'Arquitectura de Computadors (DAC)

and the

Computer Arquitecture and Operating Systems (CAOS) Barcelona Supercomputing Center (BSC-CNS)

April 16, 2018

## **Declaration of Authorship**

I, Jordi CARDONA NADAL, declare that this master thesis titled, "On the Impact of Heterogeneous NoC Bandwidth Allocation in the WCET of Applications" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a master degree at Universitat Politècnica de Catalunya .

- Where any part of this thesis has previously been submitted for a degree or any other qualification at Universitat Politècnica de Catalunya or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

## Abstract

Achieving high performance and time predictability in current manycore systems is still a challenge these days as the number of cores in manycore systems keeps increasing every day. Even though the memory speed has improved in the last decades, the speed gap between cores and memory is still relevant since part of the time that cores are stalled is due to waiting for data coming from memory. This performance bottleneck gets even worse when we increase the core count as we have more and more cores competing for the same memory bandwidth and for the same interconnection network to reach memory.

In order to mitigate this issue, in the last few years Networks-on-Chip (NoCs) such as meshes and trees, have been introduced in high-performance manycore processors due to their physical scalability and low cost. In general, these NoCs lead to heterogeneous latencies across cores to reach memory due to core location, which determines the distance between the core and the memory accessed (i.e. number of routers in between), the arbitration policy and the routing algorithm used, and the contention caused by other cores in the NoC. Furthermore, in the context of parallel applications running simultaneously in multiple cores, performance is determined by the slowest thread, which may change across different thread-to-core allocations.

In the context of Critical Real-Time Embedded Systems (CRTES), the use of manycores deploying wormhole NoCs complicates the analysis of application's timing behavior. In particular, in order to assess whether applications will run within their allocated time budget, we need to estimate their Worst-Case Execution Time (WCET) which, in turn, depends on the Worst Contention Delay (WCD) that each packet can experience to reach memory. In this thesis, we study the influence of core allocation on WCD and WCET for tree and mesh NoCs, and how specific modifications of the arbitration algorithm allow reducing the WCET by homogeneizing the memory latency across cores.

# Acknowledgements

First of all I would like to deeply thank my master thesis advisors Carles Hernández, Jaume Abella and Francisco J Cazorla for their guidance, mentoring and for giving me the opportunity to undertake this master thesis in the Computer Architecture and Operating Systems' group (CAOS) at Barcelona Supercomputing Center (BSC-CNS). I also want to thank the rest of the members of the CAOS group as they have always been available to provide feedback on my work and give me advices to improve it.

Furthermore, I would like to acknowledge the BSC institution for financially support my master studies and these two others institutions as this work has been partially funded by the Spanish Ministry of Science and Innovation under grant TIN2015-65316-P and the HiPEAC Network of Excellence.

Finally, I would not forget to thank my entire family and specially my parents, my sister and my closest friends for their unconditional support during all these years, without you this master thesis would not be possible. My most heartfelt thanks for the great confidence you have shown in me.

# Contents

| D  | eclara | ation of Authorship                      | i   |

|----|--------|------------------------------------------|-----|

| Al | ostrad | ct                                       | ii  |

| A  | cknow  | wledgements                              | iii |

| 1  | Intr   | oduction                                 | 1   |

|    | 1.1    | Motivation                               | 2   |

|    | 1.2    | Contribution                             | 3   |

|    | 1.3    | Structure of the Thesis                  | 5   |

| 2  | Bac    | kground                                  | 6   |

|    | 2.1    | Timing Analysis                          | 6   |

|    | 2.2    | NoCs                                     | 8   |

|    |        | 2.2.1 Data organization and transmission | 9   |

|    |        | 2.2.2 Network structure                  | 11  |

|    |        | 2.2.3 NoC concepts for CRTES             | 13  |

|    | 2.3    | Parallel Applications                    | 15  |

| 3  | Rela   | ated Work                                | 17  |

| 4  | Eva    | luation Framework                        | 19  |

|    | 4.1    | Simulation Platforms                     | 19  |

|    |        | 4.1.1 Processor details                  | 19  |

|    |        | 4.1.2 Network-on-chip Simulator          | 20  |

|    | 4.2    | Workload                                 | 21  |

|    |        | 4.2.1 Synthetic Traffic                  | 21  |

|    |        | 4.2.2 Real Traffic                       | 21  |

|   |     |          | 4.2.2.1    | Resource Stressing Kernels                              | 21 |

|---|-----|----------|------------|---------------------------------------------------------|----|

|   |     |          | 4.2.2.2    | Spinlock benchmarks properties                          | 22 |

| 5 | Con | trolling | g Bandwi   | dth Allocation in NoCs                                  | 23 |

|   | 5.1 | Arbite   | er Design  |                                                         | 25 |

|   |     | 5.1.1    | Implem     | entation cost of a weighted round-robin (WRR) arbiter . | 28 |

|   |     | 5.1.2    | Adaptin    | g arbitration weights                                   | 30 |

|   | 5.2 | On-Cl    | hip Interc | onnection Architectures                                 | 32 |

|   |     | 5.2.1    | Tree       |                                                         | 32 |

|   |     | 5.2.2    | Meshes     |                                                         | 33 |

|   | 5.3 | A mo     | del for co | mputing worst-case delay (WCD) from the allocated       |    |

|   |     | bandv    | vidth      |                                                         | 38 |

|   |     | 5.3.1    | Baseline   | NoC                                                     | 38 |

|   |     | 5.3.2    | Account    | ting for the Impact of Bandwidth Allocation in WCD      | 39 |

|   | 5.4 | Comp     | outing WC  | CET in NoC-based processors                             | 41 |

| 6 | Eva | luation  | Results    |                                                         | 42 |

|   | 6.1 | Perfor   | mance ch   | aracterization of workloads                             | 42 |

|   |     | 6.1.1    | Executio   | on time in Isolation                                    | 42 |

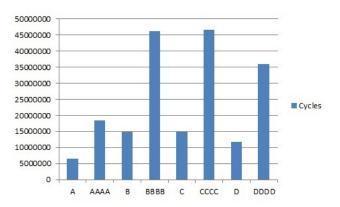

|   |     | 6.1.2    | Homoge     | eneous executions                                       | 43 |

|   |     | 6.1.3    | Heterog    | eneous executions                                       | 44 |

|   | 6.2 | Tree-N   | NoC arbiti | ration and bandwidth allocation analysis                | 46 |

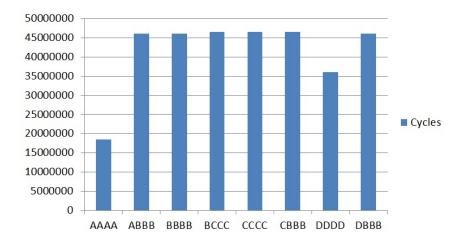

|   | 6.3 | WRR      | arbitratio | n analysis                                              | 50 |

|   | 6.4 | WCET     | Г analysis | in RR and WRR NoCs                                      | 55 |

| 7 | Con | clusion  | ns and Fu  | ture Work                                               | 58 |

# **List of Figures**

| 1.1  | Schematic of the problem where this thesis contributes             | 4  |

|------|--------------------------------------------------------------------|----|

| 2.1  | Packet format                                                      | 10 |

| 2.2  | Pipelined router                                                   | 12 |

| 5.1  | Binary Tree NoC structure                                          | 25 |

| 5.2  | 2x2 Mesh representation in tree                                    | 27 |

| 5.3  | Window arbitration implementation                                  | 30 |

| 5.4  | 3x3 mesh weight using XY routing and WRR arbitration               | 31 |

| 5.5  | Binary tree with RR arbiter                                        | 32 |

| 5.6  | 3x3 mesh flows using XY routing algorithm                          | 33 |

| 5.7  | 3x3 mesh weights using XY routing and RR arbitration               | 34 |

| 5.8  | Messages sent per NIC in a 3x3mesh XY routing and RR arbitration   | 34 |

| 5.9  | Messages latency                                                   | 35 |

| 5.10 | Messages sent per core in a RR 3x3Mesh varying the IR              | 36 |

| 5.11 | Messages latency per core in a RR 3x3Mesh varying IR               | 37 |

| 5.12 | 2x2 Mesh with 4 cores                                              | 40 |

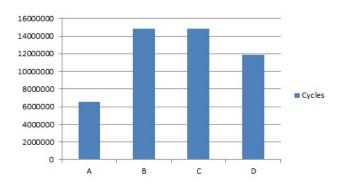

| 6.1  | Tree isolation benchmarks results                                  | 42 |

| 6.2  | Comparison between multicore homogeneous and isolation bench-      |    |

|      | marks results                                                      | 43 |

| 6.3  | Heterogeneous benchmarks results                                   | 44 |

| 6.4  | Comparison between multicore heterogeneous and homogeneous bench-  |    |

|      | marks results                                                      | 45 |

| 6.5  | Messages sent per NIC with 1.0 of IR and RR arbitration            | 46 |

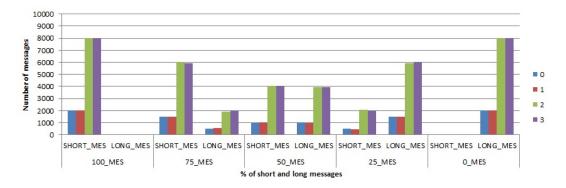

| 6.6  | Number of short and long messages sent per NIC with 1.0 of IR with |    |

|      | RR arbitration                                                     | 47 |

| 6.7  | Binary tree with WRR arbiter                                      | 48 |

|------|-------------------------------------------------------------------|----|

| 6.8  | Messages sent per NIC with 1.0 of IR with WRR arbitration         | 48 |

| 6.9  | Number of short and long messages sent per NIC with 1.0 of IR and |    |

|      | WRR arbitration                                                   | 49 |

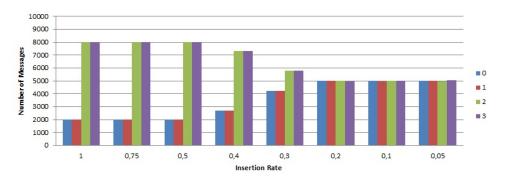

| 6.10 | WRR arbitration impact varying the tree NoC IR                    | 49 |

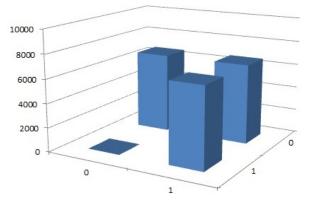

| 6.11 | Messages sent per NIC in a 2x2mesh XY routing 1.0 IR and WRR ar-  |    |

|      | bitration                                                         | 50 |

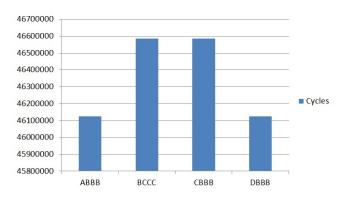

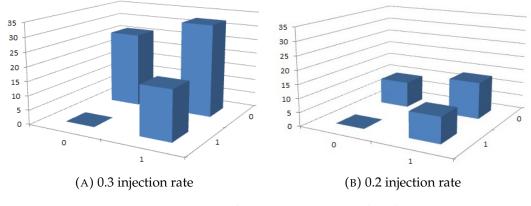

| 6.12 | Latency evolution in a 2x2 2D Mesh reducing IR                    | 51 |

| 6.13 | BW distribution in a 4x4 2D mesh with 1 FLIT messages             | 51 |

| 6.14 | BW distribution in a 4x4 2D mesh with 5 FLIT messages             | 53 |

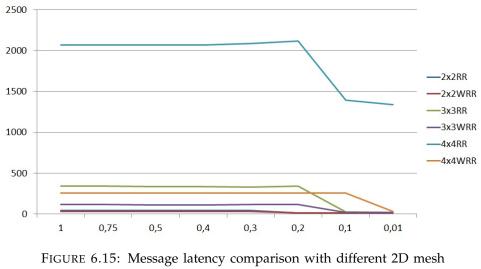

| 6.15 | Message latency comparison with different 2D mesh sizes           | 53 |

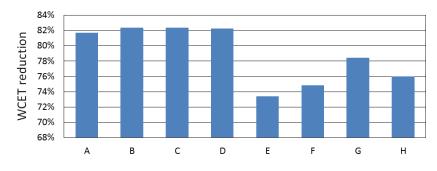

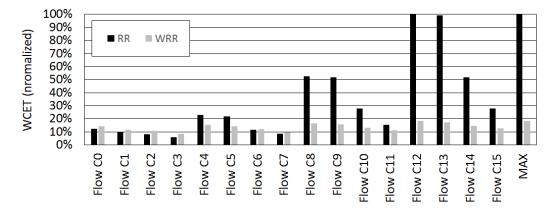

| 6.16 | WCET reduction along all the benchmarks                           | 56 |

| 6.17 | WCET normalized in a 4x4 mesh of benchmark A                      | 57 |

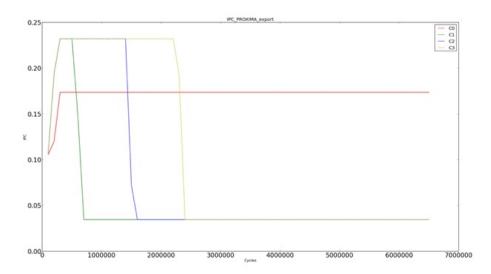

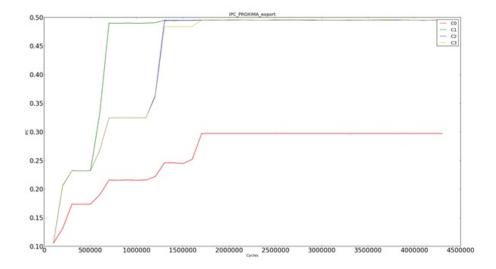

| 7.1  | IPC evolution along time results                                  | 60 |

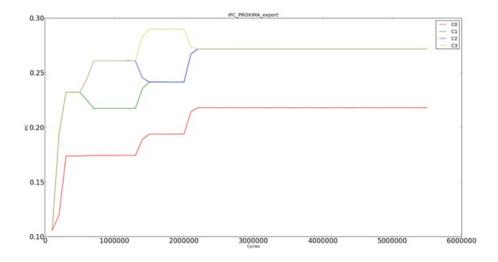

| 7.2  | IPC evolution along time with spinlock reduction of x10           |    |

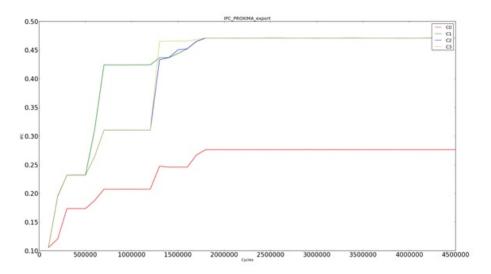

| 7.3  | IPC evolution along time with spinlock reduction of x100          |    |

| 7.4  | IPC evolution along time with spinlock reduction of x1000         |    |

| 7.5  | Messages sent per NIC in a 3x3mesh XY routing 1.0 IR and WRR ar-  |    |

|      | bitration                                                         | 64 |

| 7.6  | Arbitration windows in $R_2$                                      |    |

| 7.7  | Messages sent per NIC in a 3x3mesh XY routing 1.0 IR with Fig-    |    |

|      | ure 7.6b arbitration window                                       | 66 |

| 7.8  | Arbiter effectiveness lost due to window alignment                |    |

| 1.0  | The first check to be true to white on angument                   | 00 |

# List of Tables

| 4.1 | Processor Configuration                                         | 20 |

|-----|-----------------------------------------------------------------|----|

| 4.2 | Single-threaded benchmarks                                      | 22 |

| 4.3 | Spinlock Benchmarks Properties                                  | 22 |

| 5.1 | Weights per input port direction for a 3x3 Mesh with WRR        | 31 |

| 5.2 | WCD values for L-flit packets, where the maximum allowed packet |    |

|     | size is L                                                       | 41 |

| 6.1 | Growth between isolation and homogeneous execution              | 44 |

| 6.2 | WCET of applications running in a 4x4 2D Mesh                   | 56 |

## Chapter 1

## Introduction

Computing systems require functional correctness, so that the outputs provided correspond to the system specification. A subset of the computing systems, known as real-time systems, also needs *timing correctness*. Timing correctness refers to the execution of the corresponding functionalities before specific deadlines. For instance, the braking system of a car needs to stop the car within limited time bounds. Analogously, video players need to process frames at a given speed.

Some real-time systems may afford missing some deadlines with certain frequency, since those *timing failures* only produce a lower quality output, which may not even be perceived if the deadline miss rate is sufficiently low. For instance, this is the case of many systems related to entertainment (e.g. music and video players). However, some other systems are intended not to miss any deadline, since a failure of those systems could lead to catastrophic consequences (e.g. the navigation system of a plane or the braking system of a car). These systems, often referred to as critical real-time embedded systems (CRTES), require a careful functional and timing verification to prove – qualitatively and quantitatively – that the risk of failure can be regarded as residual. In other words, the validation and verification (V&V) process provides evidence that all relevant scenarios have been considered and safety measures have been put in place to mitigate risks.

CRTES can be critical because of many reasons. For instance, safety-critical systems are those whose failure could cause casualties, injuries or severe damages to objects (including the system itself). Instead, mission-critical systems are those whose failure may typically cause economical losses such as, for instance, systems controlling measurement instruments in a satellite. Even if those systems do not compromise the integrity of the satellite itself, they may lead to a failure of accomplishing the mission, which ultimately is a severe consequence. In this work, we target the design and timing verification of CRTES, regardless of their type of criticality.

Until recently, CRTES built upon relatively-simple software running on relatively low-performance (and low-complexity) hardware. For instance, many avionics systems still today build upon single-core processors with in-order execution and without cache memories. The advantage of those systems is that timing verification is relatively simple, since execution time variability is low. Hence, the Worst-Case Execution Time (WCET) can be estimated with affordable costs either by using timing models of the system or by collecting measurements and adding a safety margin over the highest execution time observed.

However, the increasing automation of systems first, and the trend towards fullyautonomous systems later, pushes CRTES industry for adopting hardware platforms delivering much higher performance to respond to the performance demands of complex functionalities. Multicore and manycore processors are one such type of hardware platform. They consist of a number of cores capable of executing software simultaneously, as well as an interconnection network to communicate cores among them and with neighbor devices (e.g. main memory).

#### 1.1 Motivation

Multicore and manycore processors have already been considered for the execution of critical real-time software in experimental environments [24, 34, 39, 17, 3, 13] – although they have not been deployed yet. While communication buses have been proven effective for small multicores [33], they have been proven not to scale well to larger multicores and manycores (e.g.  $\geq$  8 cores) [37]. Hence, more complex Networks-on-Chip (NoCs) are used for the interconnection of the cores, as well as to reach any other device. Different types of NoCs have been considered to satisfy the communication requirements of multi/manycores. We classify those works into two different categories: ad-hoc and commercial designs. The former category consists of those NoCs that are particularly designed to provide time predictability, so that the WCET of tasks can be easily estimated. In general, these designs trade average performance for guaranteed performance (WCET), which is against efficiency. Therefore, chip manufacturers are unlikely to adopt them. The latter category of NoC designs corresponds to Commercial Off-The-Shelf (COTS) designs [25, 9, 40]. In other words, it corresponds to those designs that can already be found in commercial processors (e.g. meshes, torus, etcetera). However, those designs often provide very high average performance at the expense of offering poor timing guarantees. Hence, they are not suitable, in general, for CRTES. Recently, this has been addressed and small modifications have been proposed on COTS NoC designs to make them amenable to (tight) WCET estimation while preserving high average performance [24].

Those multi/manycore processors equipped with powerful NoCs have been proven efficient for the execution of independent tasks in the different cores, or by running some simple deployments of parallel applications [24]. Also, it has been shown that almost-homogeneous bandwidth can be allocated to the different cores with appropriate hardware support on COTS NoCs, thus making core allocation irrelevant for WCET estimation, since all cores experience similar worst-case communication delays [22]. These NoCs are referred to as weighted NoCs. By using locally-unfair arbitration, those NoCs achieve globally-fair bandwidth allocation across cores. However, the benefits of weighted NoCs (and in particular meshes) for different degrees of traffic and application types have not been assessed. Also, the performance of NoCs for different types of parallel applications has not been assessed.

#### 1.2 Contribution

This thesis studies whether it is possible (and to what extent) configuring powerful NoCs in multi/manycores to reduce the WCET of critical real-time parallel applications.

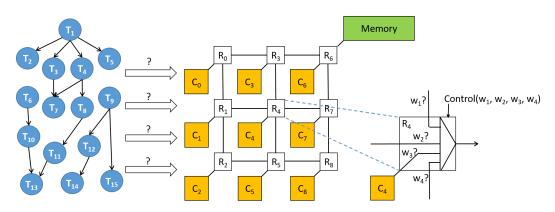

FIGURE 1.1: Schematic of the problem where this thesis contributes.

The magnitude of the problem is illustrated in Figure 1.1. As shown, mapping parallel applications to a multi/manycore where bandwidth per link can be adjusted is a very complex problem since both, thread mapping and weight allocated to each link, are not independent. In this thesis we aim at investigating the tradeoffs involved. Note that solving this problem is a complex research challenge much beyond the scope of this thesis. Instead, this thesis focuses on characterizing the problem and understand the tradeoffs involved.

In particular, the contributions of this work are as follows:

- We verify and adapt a NoC simulator to provide WCET bounds for requests.

- We implement a weighted mesh on that simulator where the bandwidth allocated to each core and flow can be flexibly adjusted. In this process, we define a number of parameters left open in the original description of the mechanism implemented.

- We assess quantitatively the potential gains that thread-to-core allocation and weight allocation can obtain by running experiments on a processor performance simulator where the NoC simulator is integrated. For the sake of this analysis, ad-hoc benchmarks have been developed, thus providing us with controllability on the experiments and a-priori knowledge of the behavior of applications. This is key for the verification of the design.

#### **1.3** Structure of the Thesis

The rest of this document is organized as follows. Chapter 2 provides background on timing analysis for CRTES, NoC design and application imbalance. Chapter 3 provides some related work on NoC designs for CRTES. Chapter 4 introduces the evaluation framework used in this work. Chapter 5 presents weighted meshes including their implementation, WCD modelling and characterization. Chapter 6 provides the result of our analysis for parallel applications. Finally, Chapter 7 draws some conclusions and presents some future work.

### Chapter 2

## Background

#### 2.1 Timing Analysis

Critical real-time tasks must complete their execution by a given deadline. In order to assess whether this will be the case during operation, a process called *timing anal-ysis* is performed as part of the verification of the system to estimate the WCET of those tasks. This step is mandatory to schedule tasks such that they can complete their execution before a given deadline.

Two main timing analysis strands have been pursued in industry and academia: static timing analysis (STA) and measurement-based timing analysis (MBTA) [42].

STA builds a timing model of the hardware and on which it performs an abstract interpretation of the program under analysis, modelling the potential hardware states that can occur. Ideally, STA models all possible state transitions, thus obtaining each potential state of the hardware at each step (i.e. after each instruction or after each execution cycle). Finally, when all instructions of the program have been analyzed, the final state with a higher execution time determines the WCET. However, the number of potential states exploits exponentially due to potential outcomes of branches, uncertainty on the addresses accessed (and so on the hit/miss outcome of cache memories and the resulting cache state), and limitations of the timing model. The way STA addresses this is by reducing the number of states modelled making pessimistic assumptions. For instance, cache accesses that could hit or miss, may be assumed to miss, or some data that could reside in cache at some point, is assumed not to be in cache to allow merging several states. Overall, STA is highly demanding on the amount of information needed to derive tight WCET estimates and it has been shown only suitable for simple programs running on simple hardware [4].

MBTA, instead, builds upon execution time measurements of the program collected on top of the target platform. This removes the need for a timing model and for any type of abstract interpretation. However, the challenge for MBTA resides in relating the scenarios evaluated during the test campaign with those that can occur during operation. Moreover, a number of features such as memory placement of objects (and so cache placement), contention in shared resources and values operated in variable-latency units are, often, beyond the control of the end user. Hence, the limited controllability together with the difficulties to assess the coverage of the analysis tests with respect to the scenarios during operation pose uncertainty on the WCET estimates obtained with MBTA. In fact, MBTA usually uses the maximum observed execution time (MOET) plus a safety margin (e.g. 20% in single-core processors [41]) as the WCET estimate. However, the confidence provided by the safety margin is unknown. Hence, MBTA is convenient when users are highly familiar with the software analyzed and the hardware platform, so that they can create relevant test cases and set appropriate safety margins [4].

Some hybrid timing analysis approaches exist that attempt to combine the advantages of both, STA and MBTA, by, for instance, collecting measurements at finer granularity than end-to-end program runs and applying some form of abstract analysis to estimate the execution time for paths that have not been measured [4]. While conceptually those methods may bring tighter estimates than STA and less uncertainty than MBTA, their tightness and confidence cannot be proven better than those of STA and MBTA.

Overall, different timing analysis families bring their pros and cons. In general, each approach is suitable for some specific systems, but all of them have been used even for systems with the highest criticality. In general, MBTA is the most used approach since it does not provide WCET estimates duly pessimistic, and its application is less cumbersome than that of STA. In this thesis, we use specific models to estimate the worst latency needed to traverse the NoC, as such latency can be obtained analytically, and MBTA to measure the execution time of the program and to estimate the WCET. In particular, the WCET is obtained by measuring execution time in a contention-free scenario in the NoC, and then adding the Worst Contention Delay (WCD) to each memory request to account for the potential contention that packets could experience upon integration of the application with other software that, potentially, could cause such worst-case contention. This methodology introduces time composability as when we integrate for instance a new application in our system, we do not need to reverify the timing correctness of all the applications that are running but the new one. Time composability property is a highly sought property as it allows industry to optimize the V&V process (e.i. it can be done in an incremental manner) reducing the cost of the timing V&V part.

#### 2.2 NoCs

The need for multicores and the fact that cores may need to communicate between them and with other devices (e.g. main memory, shared caches) imposes the need of setting up an interconnect network among cores and other devices. On small multicores, classic monolithic solutions such as buses have been shown to be effective [33]. However, as the number of cores in the processor grows, buses become easily a bottleneck. The main reason is that their latency increases due to their increased capacity and long distance, which can only be partially mitigated pipelining the bus. However, in general, the bus cannot serve more than one transfer simultaneously due to its monolithic nature. Hence, given that its latency grows with the number of cores, the relative bus occupancy per core increases, and the number of cores willing to use it also increases, thus making the bus being a potential bottleneck even with a few cores (e.g. > 4 cores).

To tackle this problem, NoCs have been proposed as the most convenient interconnection solution to connect cores and other devices in multicores [10]. NoCs rely on setting up point-to-point connections inside the chip to keep all components connected by means of switches and links. Hence, in a NoC one may not be able to reach each device directly, but messages can be routed through those links and switches to destination. Given that NoCs build upon many individual connections, they can afford transmitting multiple messages simultaneously as long as they can be managed not to clash in the same resources. For instance, routing messages appropriately may avoid conflicts or, alternatively, setting up buffers may allow stalling messages when the resource required is busy.

The most common NoC topologies used in multicores include rings [31], trees [37] and meshes [33, 10]. For instance, some commercial processors build upon those networks. The Intel Nehalem [25] implements a bidirectional ring network. The Kalray MPPA-256 implements a tree network [6, 9]. Finally, several processors, such as the Tilera 100-core chip [40], the Polaris prototype [16] and the Single-chip Cloud Computing (SCC) prototype [30], implement a 2D mesh network.

#### 2.2.1 Data organization and transmission

When two or more networked devices try to read from each other's memory, the unit of information sent or received is called *message*. The device that sends the petition, first has to compound this message and send it in the form of a *request*. This request contains inter alia, the address where the receiver will found the requested data. Then, after processing the request, the receiver will be able to send back a *reply* message containing the data also known as *payload*. Alternatively, a networked device may send a message containing data to a receiver, thus containing already the payload. The receiver, upon data reception may or may not send a reply message (without payload) to acknowledge the reception of the data, depending on the actual data management policy of the network implemented.

Usually, *network interfaces* together with some *direct memory access* (*DMA*) engines and link drivers are in charge of composing and processing messages before sending and receiving information. In some networks, there is a fixed amount of information that can be transferred so that network buffers can be sized appropriately. Messages longer than the maximum transfer unit are divided into smaller units, called *packets*. These packets are reassembled into messages at the destination end node before delivery to the application.

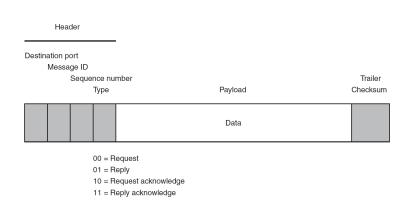

Packets normally contain, in addition to the payload, a header and a tail part. In Figure 2.1 it can be seen a representation of a possible packet format. Usually, the packet header contains the destination port, the message ID of the packet it belongs

FIGURE 2.1: Packet format

to, a packet sequence number to enable reordering of the entire message in the destination device and packet type (request, reply, acknowledge,...). Each packet also uses to contain a checksum field that is used to check if the packet received has no corruption (re-calculating the checksum value in the receiver device and comparing it with the checksum field received in the tail part of the packet).

Packets may have sizes larger than the transmission bandwidth (links). For instance, messages may be divided into packets of up to 512 bits, and links to communicate networked interfaces may be of up to 128 bits. Hence, messages cannot be transmitted at once and may need to be divided into smaller network units called *flow control units (FLITS)*. FLITS, are the smallest data entity inside networks and they can be transmitted atomically. The set of FLITS forming a message is known as *flow*. All FLITS of a flow are transmitted atomically across several cycles between two nodes, so only the first flit needs to include information about the destination, whereas all FLITS contain a flow ID to determine when a packet has been completely received and hence, a different packet can be sent.

Once a packet is ready to be sent at its source, it is injected into the network by the network interface. The speed of the packet transmission will depend strongly on the media, distance and the form factor used. In order to ensure reliable delivery of packets, two main assumptions have to be taken into account: (1) The sender cannot send packets at a faster rate than they can be processed by the receiver, and (2) packets are correctly received (neither lost nor corrupted in transit). The most used strategy is called *flow control*, where the receiver notifies the sender to stop sending packets until the receiver has enough space in its input buffer or an emptiness threshold has been reached. The basic implementation consists of using a simple *handshaking* protocol between the sender and the receiver. Two main different strategies exist to implement flow control:

- *Stop & Go*: The receiver notifies the sender to stop or to resume sending packets once high or low buffer occupancy levels are reached respectively.

- *Credit-based*: Every time a packet is transmitted, the sender decrements the credit counter. When the receiver processes it, it increments the sender's credit counter. The sender can send a new packet as long as its credit is above a given threshold.

The most spread policy is the Stop&Go one as it introduces lower traffic in the network (flow control messages are only sent when buffer capacity bounds are reached) than the Credit-based strategy (flow control messages are sent every time that a packet is processed by the receiver).

#### 2.2.2 Network structure

A NoC consists of a number of physical components, including switches, links, network interfaces, etc. Network interfaces connect end nodes to switches (also referred to as routers). Then, routers are connected among them by means of links. Packet's flow is determined by routers, which implement a number of policies for switching, routing and arbitration in general. Instead, links are passive components, and network interfaces inject/eject packets with specific source and destination, but without influencing when and how those packets will traverse the NoC.

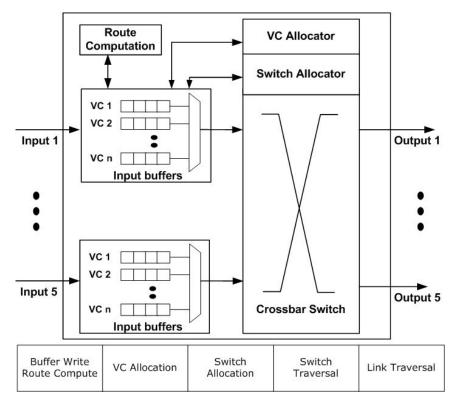

Figure 2.2 depicts a typical pipelined router. First, a set of input buffers for each port are used to store incoming packets. Second, a routing algorithm determines the next router where those packets need to be sent (or the network interface at destination). Third, an arbiter determines which input ports buffers grants access to each output port. Finally, a switch allocator matches the corresponding input port buffers with the output ports ones for the packets' transfer. Eventually, whenever input buffers are available at the destination router, packets leave the current router and are stored in the input buffers of the next router.

Input buffers for a given input port can be organized into multiple queues (virtual channels) to allow multiple flows being processed in parallel. This requires

FIGURE 2.2: Pipelined router

additional queues per input port and a virtual channel allocator. On the other hand, however, virtual channels typically increase the average throughput of routers.

In many NoCs, multiple routes exist to forward a packet from its source to its destination. Different routing policies have been proposed to accomplish this goal, with some common goals, namely: (1) trying to minimize the number of hops from source to destination, (2) avoiding deadlocks and (3) avoiding livelocks. In particular, minimizing the number of hops is desired for efficiency reasons, and only some policies consider alternative routes to go around broken links or overly congested NoC regions. Deadlocks in NoCs occur whenever a set of packets use multiple resources (e.g. buffers) such that no packet can make forward progress because the resources needed are busy, and no resource can be released because packets cannot make any forward progress. Finally, livelocks occur when routing decisions may potentially make a packet not to reach its destination despite it may keep moving in the NoC (e.g. looping in a subset of routers). Routing policies implementing those goals may be dynamic or static, either taking routing decisions based on dynamic conditions or having predetermined routes. In the case of critical real-time tasks, static policies are normally used since they allow guaranteeing efficient routes, as well as

deadlock and livelock avoidance. Among those, the most popular routing policy is XY, where packets are forwarded in the X direction until they reach the Y-coordinate of their destination, and then they are forwarded in the Y direction until the destination node. Once a packet is forwarded in the Y direction, it cannot be further routed in the X direction. Such policy guarantees, by construction, minimal distance routes as well as deadlock/livelock avoidance. Moreover, it allows deriving tight bounds to the worst delay to forward a packet from any node to its destination. In critical real-time tasks we can also use other static routing policies that also belong to the dimension-order routing where it belongs XY routing (e.g. YX (2D) or XYZ and e-cube in 3D NoCs).

Switching algorithms determine how a packet is transferred from source to destination. The two most popular switching policies are *cut-through* and *wormhole*. The former does not allow a packet make any forward progress until enough resources for the full packet cannot be allocated in the following router. Wormhole, instead, allows individual FLITS moving forward, but once a flit has been sent, only subsequent FLITS of the same packet are accepted in the destination buffer, thus avoiding the interleaving of packets in a single buffer.

Wormhole NoCs are regarded as more efficient than cut-through ones since they allow some forward progress even if resources at the destination router cannot store the full packet, and also allows arbitrarily long packets, as opposed to cut-through, which may need large buffers if long packets may be communicated. Hence, in the rest of this work we rely on wormhole switching, which has been proven to be the preferred choice for CRTES [23].

#### 2.2.3 NoC concepts for CRTES

In the context of CRTES, the most critical parameter for timing analysis (and so for WCET estimation) is the amount of time a request can be delayed in the NoC due to contention. In particular, the delay a request (packet) takes to traverse the NoC consists of the minimum intrinsic delay to reach the destination in a congestion-free scenario, also known as *zero load latency* (*zll* for short), plus the delay due to contention. Since contention during operation cannot be forecasted tightly until late

design stages, but WCET estimates are needed much earlier in the design process, worst-case assumptions need to be made in terms of congestion.

Two main approaches have been devised to account for such worst-case congestion: Worst-Case Traversal Time (WCTT) and Worst Contention Delay (WCD). The former [28, 19, 27, 8] accounts for the worst individual delay each request may suffer. However, adding such delay to each request for WCET estimation has been shown to be overly pessimistic because a large fraction of such delay can be overlapped for several requests being processed in parallel [23]. Hence, some authors propose using WCD instead, which only accounts for the additional delay caused by another request, discounting the delay that has already been accounted to other requests. This delivers reliable but much tighter WCET estimates.

Since worst-case assumptions need to be made to account for worst-case contention delay, it has been shown that several choices, despite not being the most efficient ones for average performance, deliver the lowest WCET estimates. Amongst those we build on the following ones [23]:

- **Packetization**. Since a request may have to wait for requests in the other ports to be processed first, and those requests (packets) could be arbitrarily long, packetization has been proposed, where all packets are made to have a single flit. Hence, each flit of the task under analysis has to compete with single flit packets from other flows. Otherwise, each packet, regardless its length (e.g. 4 FLITS), would have to compete against maximum-size packets (e.g. 16 FLITS) from other contenders, whose relative contention delay can be much higher (e.g. 4x that of single-flit packets).

- Single Virtual Channel. The existence of multiple virtual channels, while effective in the average case, has a multiplicative effect on the number of contenders that packets of the task under analysis will have to compete with in every router. Hence, given *N* virtual channels, worst-case contention grows by a factor of *N* w.r.t. a single virtual channel. Therefore, the best choice for CRTES is using NoCs with a single virtual channel.

Finally, performance guarantees have been shown to vary drastically across cores in meshes (one of the most commonly used NoC architectures) due to the varying bandwidth effectively allocated to each core and diverse latencies caused by nonhomogeneous distances from cores to their target node (e.g. the one where main memory is attached) [22]. Heterogeneous bandwidth and latency is, in general, unwanted due to the fact that tasks running in some cores – those with lower bandwidth and higher latencies – can be severely penalized. This challenge has been addressed with the use of weighted meshes, where heterogeneous bandwidth allocation across links is given in the routers so that overall bandwidth can be homogenized across cores and, to some extent, performance across cores is homogenized [22]. Later in this thesis, we provide details on weighted meshes, as they are a key NoC design studied in the context of parallel applications as part of our work.

#### 2.3 Parallel Applications

Most research on NoCs for CRTES has considered single-threaded applications, since they are current practice in the domain. However, parallel applications are needed for computing intensive tasks such as those related to autonomous driving and unmanned navigation. Hence, NoC design and analysis cannot focus on the behavior of each core in isolation only, but it also needs to account for the implications on parallel applications.

Existing work has only considered default NoCs devised for single-threaded applications with just one exception: the parMERASA architecture [26, 24]. In the context of parMERASA (an already finished FP7 programme project), investigation was done on how to map parallel applications to cores for an efficient use of resources building on some NoC designs including meshes. However, bandwidth and latency heterogeneity was not tackled and thread allocation was applied on those default architectures, which have been shown to offer highly unbalanced bandwidth and latency across cores.

High imbalance across cores may lead to scenarios where, despite smart threadto-core mapping algorithms are used, threads experience highly diverse execution times. In the context of single-threaded applications this can be mitigated by allocating additional tasks to the fastest cores. However, in the context of parallel applications, the slowest thread determines the full application execution time. Therefore, high imbalance penalizes performance (and consequently WCET) severely.

Therefore, weighted meshes offer a great opportunity to optimize weight allocation and thread-to-core mapping, either independently or coordinately, to optimize the performance of parallel applications in CRTES.

## **Chapter 3**

# **Related Work**

While there have been several proposals for real-time aware NoC designs, exploring to which extent high-performance (COTS) NoC designs can be used in the real-time domain is of paramount importance:

On the one hand, it is well accepted that the CRTES domain is a relatively small market in comparison with other domains such as mobile. Hence, customized NoCs specifically designed for real-time systems (e.g. time-triggered ones and those based on time division and multiplexed access (TDMA)), which may require high non-recurrent costs, are unlikely to be adopted in the context of industrial CRTES [39].

On the other hand, the big majority of the proposed manycore designs across all computing domains use high-performance wormhole NoCs (wNoCs) to perform the interconnection of cores and shared resources within the chip. This makes wNoCs accessible (at low cost) by the CRTES since they are implemented in a vast set of chips. In this paper we have focused on improving the performance guarantees achieved by wNoCs in terms of bandwidth and latency.

Several real-time specific NoCs have been proposed based on TDMA such as [34] and [12]. While TDMA-based NoCs deal with contention at transaction level (e.g. read and write memory operations), time-triggered architectures [21] increase the abstraction level by introducing a self-contained computational unit. In time-triggered architectures micro-components exchange messages in contention-free slots. However, event-triggered transactions, such as cache misses that access main memory through the NoC, may suffer contention delay which must be upper bounded. We refer to NoC designs with real-time guarantees and time-composable behavior as Guaranteed Service (GS) NoCs. Nostrum [20] and Aethereal [12] NoCs provide

GS using time-division multiplexing, and hence, time composable bounds.

Many studies have also been carried out with the purpose of providing realistic and feasible latency bounds for best-effort wNoC. Using prioritization on a per-virtual channel basis has proven being an effective means to achieve tight latency bounds in wNoCs [35]. However, the use of per-virtual channel prioritization becomes impractical when a significant number of flows exist in the network. To overcome this issue the impact of virtual channel sharing has been analyzed in [36] and [29]. However, while these approaches effectively reduce the number of virtual channels required, the timing guarantees obtained build upon a detailed knowledge of the characteristics of the software (applications and/or tasks) that will execute in the deployed system and hence, do not meet incremental qualification requirements. The work in [18] has similar pros and cons, since the proposed solution guarantees specific bandwidth allocation for GS connections per port, by splitting the bandwidth of output ports among best effort and guaranteed service connections.

Authors in [19] made one of the first studies that provided reliable contention bounds for wNoCs without building upon flit-level virtual channel preemption. Later, this analysis has been improved in [28] where tighter bounds are presented. The model in [28], as those mentioned above, also requires detailed information on all communication flows that will be finally deployed in the system to estimate reliable upperbounds. In other words, latency bounds provided in [28] are not timecomposable. Some recent works that build upon wNoCs propose interference-free NoC designs [5, 14]. The solution in [5] has been proven to cause lower degradation on best-effort traffic than the one in [14]. The former achieves its goal by using specific ways to multiplex virtual channels. However, despite its improved performance, the performance degradation caused on best-effort traffic is still large.

Recently, as explained before, authors in [22] have proposed an alternative approach to meet CRTES requirements. In particular, that work proposes specific ways to derive time-composable worst contention delay bounds without sacrificing average performance and by allocating weights to arbiters so that fair bandwidth allocation is achieved across cores. In our work we analyze the use of wNoCs for parallel applications and the impact of using weighted meshes in that context.

## **Chapter 4**

# **Evaluation Framework**

In this section we describe the details of the evaluation framework we have used in this thesis. In particular, we provide details about both the simulation platform and the type of benchmarks/workloads we have employed.

#### 4.1 Simulation Platforms

Our simulation platform is based on an enhanced version of the SoClib simulator [38] that has been developed at the CAOS group of the Barcelona Supercomputing Center. This simulator platform models with high detail (cycle accurate) the pipeline of the processors and the cache hierarchy. This simulator has been validated against real boards showing that performance deviations of this simulation platform are below 3% when modeling the NGMP multicore processor [7].

#### 4.1.1 Processor details

We use Soclib to model a multicore/manycore processor. Cores used the PowerPC architecture [15] since this architecture is one of the most interesting ones for avionics platforms. Cores employed in these architecture are simple to ease its timing analyzable. In particular, we use in-order cores with 5-stage pipeline, single issue, and floating-point support. Cores also comprise separate data and instruction L1 caches. Data caches employ write-back write policy to reduce the amount of requests to the shared resources. The exact details of the core are given in Table 4.1.

|          | Core Features          |  |  |  |

|----------|------------------------|--|--|--|

|          | 32 bit Sparc PowerPC   |  |  |  |

| Pipeline | In-order, single-issue |  |  |  |

| I ipenne | 5-stage pipeline       |  |  |  |

|          | FPU                    |  |  |  |

|          | L1private              |  |  |  |

|          | 4-way 16KB Instruction |  |  |  |

| Cache    | 4-way 16KB Data        |  |  |  |

|          | LRU replacement        |  |  |  |

|          | Modulo placement       |  |  |  |

TABLE 4.1: Processor Configuration

#### 4.1.2 Network-on-chip Simulator

To model the behavior of NoCs we have attached the gNoCsim simulator to the So-Clib platform [2]. The gNoCsim simulator is a cycle accurate simulator of wormhole networks developed by Universitat Politècnica de València under the scope of the FP7 NanoC project. The gNoCsim simulator supports several topologies like tree, mesh, and torus and several different deterministic routing algorithms like XY, dimension order routing, and logic-based distributed routing. In this thesis, we only use the mesh with XY routing and the tree configurations. In a similar way, even gNoCsim implements different flow control algorithms, in this thesis we only use Stop&Go already explained in the Background section. Meshes in gNoCsim can be configured to support different router architectures while trees do only support the router architecture presented in [37]. In this thesis, for meshes we have chosen the canonical router architecture while we have used the default router architecture provided for the trees.

The gNoCsim simulator can work in both master and slave modes. In slave mode gNoCsim simulator simulates the requests produced by the SoClib simulator that go through the network. Typically, these are the core to memory petitions and the corresponding memory responses. However, gNoCsim simulator can also work in master mode using different synthetic traffic patterns to characterize the network behavior under different stressing situations. In this thesis, we have used both simulation modes provided by the gNoCsim simulator.

#### 4.2 Workload

#### 4.2.1 Synthetic Traffic

In order to analyze the behavior of the different network configurations analyzed, namely trees and meshes, using round-robin (RR) or weighted round-robin (WRR) arbitration, we have used synthetic traffic generation in gNoCsim simulator. The gNoCsim simulator by itself offers the possibility to generate different types of traffic in the NoC configuring some parameters such as:

- Size of short and long messages.

- Size of the links, packets, input link buffers.

- Percentage of short and long messages.

- Insertion rate in each core of the NoC.

Since the focus of this thesis is analyzing the worst-case impact of network contention, we have focused on the all-to-one traffic pattern since it is the one creating the worst-contention in a specific target, and allows modeling the case where all cores attempt to access a shared memory.

#### 4.2.2 Real Traffic

#### 4.2.2.1 Resource Stressing Kernels

As benchmarks we have used and created specific resource stressing kernels using C language and PowerPC assembly. The idea was to create workloads for which we can specify the exact fraction of instructions of each type and distribute them randomly. Additionally, for these benchmarks we can control at very fine granularity the number of requests going to memory by enforcing a specific number of hits and misses for the load and store instructions in each kernel.

For each of the stressing benchmarks generated, we execute 1 million instructions. Table 4.2 summarizes the properties of the different benchmarks employed in the evaluation.

Note that we have not used real applications because we want to have exact control of the amount of traffic generated by each benchmark since this is the most relevant parameter in the context of the worst-case network performance. Real applications are required to accurately characterize average performance. However, resource stressing kernels are the preferred solution to characterize the impact of contention on the different processor shared resources.

| Benchmarks | A  | В  | C  | D  | Ε   | F    | G    | Н  |

|------------|----|----|----|----|-----|------|------|----|

| % Local Op | 80 | 50 | 50 | 60 | 95  | 87.5 | 87.5 | 90 |

| % LD Op    | 10 | 10 | 40 | 20 | 2.5 | 2.5  | 10   | 5  |

| % ST Op    | 10 | 40 | 10 | 20 | 2.5 | 10   | 2.5  | 5  |

TABLE 4.2: Single-threaded benchmarks

#### 4.2.2.2 Spinlock benchmarks properties

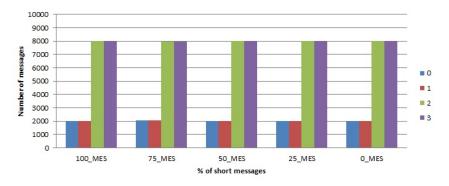

In order to analyze the spinlock effect, we have created 4 different benchmarks all of them with 5% of memory instructions and 95% of integer instructions but with different number of instructions each one, as shown in Table 4.3. These benchmarks are intended to evaluate the impact of spinlocks for synchronization purposes whenever some threads of a parallel application finish their execution and others still run.

| Spinlock benchmarks | Bench0    | Bench1  | Bench2  | Bench3  |

|---------------------|-----------|---------|---------|---------|

| % INT Op            | 95        | 95      | 95      | 95      |

| % LD Op             | 5         | 0       | 0       | 0       |

| % ST Op             | 0         | 5       | 5       | 5       |

| # instructions      | 1.100.000 | 100.000 | 300.000 | 500.000 |

**TABLE 4.3: Spinlock Benchmarks Properties**

## Chapter 5

# Controlling Bandwidth Allocation in NoCs

In this thesis we analyze the potential of using a Flexible Bandwidth Allocation (FBA) scheme to improve WCET estimates. In particular, we explore how assigning each core with a given fraction of the available shared resources bandwidth impacts the execution time of parallel applications. The idea behind FBA is that by allowing a fine-grain allocation of bandwidth, we can better exploit the computing resources of manycore systems by enabling a balanced execution time of the different tasks executing on the processor. The goal of the FBA is maximizing the overall performance guarantees of the system.

Applications parallelization is a well known topic in the high performance computing domain. In CRTES domain, parallelization of the application also has to preserve timing guarantees. This introduces an additional set of challenges: *(i)* timepredictable parallel software patterns and algorithms in order to facilitate the parallelization of legacy code as well as the development of new applications, *(ii)* timepredictable low-level synchronization primitives and *(iii)* hardware support for "fair load balancing". It is in this last aspect in which we focus our attention.

In parallel programming, a significant effort is devoted to balancing the workload of application threads i.e. sizing the computation chunk of each thread evenly. However, regardless of the programmer's effort, load imbalance can occur, either *intrinsic* (e.g. due to a specific input set) or *extrinsic* (due to, from an application perspective, external factors such as the hardware or the operating system). We focus on the hardware part.

Non-uniform memory access (NUMA) architectures are commonly employed in systems with a high number of cores. Processors including a high number of cores are typically interconnected using a NoC that interconnects the cores, memory resources, and processor peripherals using a given topology (e.g. mesh, torus, tree, etc.) that determines the latency in the communication flows (e.g. from cores to memory). On NUMA systems, the latency which a given task experiences to access memory depends on the actual location where this task is mapped to. While this uneven latency distribution affects the task's execution time, its impact is in general reduced since, in terms of average performance, caches help to minimize the number of accesses to the different shared resources and this makes at the same time the contention experienced by the requests to be low. However, since in general, deriving WCET estimates requires accounting for the worst potential contention, the impact of NUMA is not negligible in this case. In fact, to calculate the WCET in a correct way, we need to be conservative and assume the worst-case scenario in every core-memory request. That means that for every core request, we need to assume the highest contention from the other cores (the core request will be the last one to receive the arbitration grant in the routers in its path).

A FBA scheme can be implemented at the different shared resources arbiters in the processor. However, in this thesis we focus on the impact of bandwidth allocation in the interconnection architecture i.e. the connection between the cores and the shared memories or caches. For instance, in a multicore that uses an on-chip bus to connect the cores to a shared memory controller, FBA requires modifying the arbiter to allow distributing the bandwidth from cores to memory. Assuming a N-core system, a plain bandwidth allocation scheme assigns 1/N of the bandwidth to each of the cores, whereas FBA assigns each core the fraction of the bandwidth that maximizes **guaranteed performance**, where such fraction may not be homogeneous across cores.

#### 5.1 Arbiter Design

We implement FBA by leveraging a weighted arbitration. The proposed weighed arbitration is implemented on top of a round-robin arbiter and is based on using weights for the different communication flows to allocate the available bandwidth to the different cores on a flexible manner.

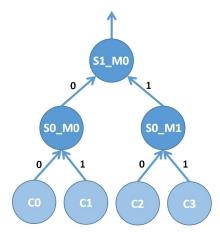

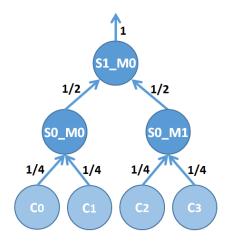

We base our design on a binary tree comparator structure [1] that easily extends to every other NoC topology. In a binary tree comparator, the global arbitration decision is split into multiple simpler arbitration decisions where each decision involves two contenders at most (see Figure 5.1). This kind of structures provides a fast response, but they are not suitable when the number of bits for encoding the priority increases [43].

FIGURE 5.1: Binary Tree NoC structure

Each 2to1 arbiter has to make a decision between two contenders. The winner is forwarded to the next 2to1 arbiter until no competitors exist. In a 2to1 arbiter, only those inputs with an active request can be forwarded. When both inputs request the output port, that input with higher bandwidth allocated – weight – wins. If both inputs have the same bandwidth allocated, a fair round-robin (RR) policy is implemented.

We can have different implementations of the weighted round-robin (WRR) policy. The one explained before is one of the more straightforward ones (i.e. the implementation does not take into account which was the port that won the arbitration the previous times). This means that, for similar weights, we can have a good arbitration alternation on the input ports that compete for an output port (both applications can make progress alternatively). However, whenever we have very different counters, we will have the case where one of the ports always wins the arbitration until the counters equalize. For instance, if port 0 has 5 time slots and port 1 has only 2, the first 3 arbitrations will be granted to port 0 (decreasing the corresponding counter on every arbitration). Then, both counters will indicate 2 time slots for each port, so RR arbitration will occur. Overall, the sequence of arbitration grants will be either 0000101 or 0001010.

Hereafter, we propose two possible implementations of the WRR arbiter policy:

• Weight counters' implementation: the first solution is the implementation explained in the 2to1 arbiter. So as to implement this option, each router input port has to store for each output port its current weight and the maximum weight that can have. The arbitration policy grants the arbitration to the input port that has the highest weight that contend for the same output port. When an input port wins the arbitration, its current weight is decreased by one unit. When both input ports that contend for the same output port have their current weights equal to zero, all the input weights are set again to the maximum weight they can have. If the prioritized input port to win the arbitration does not have a ready petition, the arbitration will give the priority to the next input port that has higher current weight counter (e.i the other input port). The maximum weight values are set at boot time and re-set when all input port weights are equal to zero.

Make notice that every time that weights are set to their maximum value, the order in which the arbitration policy grants the arbitration to input ports can potentially vary not only because of the RR part when all input ports have the same weight value, but also if one input port does not have a petition ready to be sent.

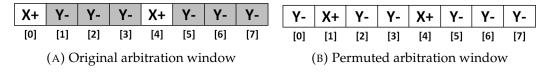

• Arbitration window implementation: the second option is to explicitly specify the arbitration window that we want the arbitration to follow per each router output port. This solution incurs in higher hardware overhead for the implementation part (we need to identify each input port, a pointer to traverse the arbitration window,...) but allows to have precise control on the arbitration that each output port is using. Every time that the window is traversed the same pattern is followed. We can also set at boot time the arbitration windows and all the values we need. In this case the port that has priority is the one pointed by the window arbitration pointer. If this port has a ready petition it wins the arbitration, otherwise we advance the pointer and we look for the next input port that has a petition. We can implement the arbitration window as a circular buffer and whenever the pointer reaches the last window slot, it is automatically set to the first arbitration window position again.

As said before, the binary tree implementations can easily be extended to a generic topology since, in the end, every NoC topology can be described as a tree structure for a given target node, in which each tree node has as many leaves as the total number of incoming links each router has.

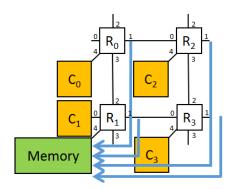

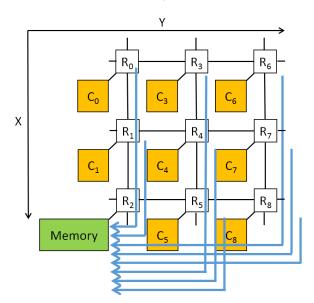

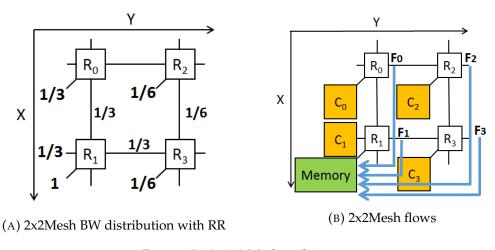

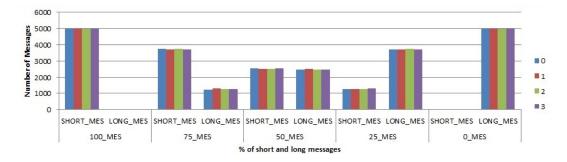

(A) 2x2Mesh example with traffic flows (B) 2x2Mesh tree representation of flows

FIGURE 5.2: 2x2 Mesh representation in tree

In Figure 5.2a we can observe a 2x2 Mesh with 4 routers represented as  $R_0$  to  $R_3$  and 4 cores represented as  $C_0$  to  $C_3$ . We can also appreciate that all the routers of the mesh have 5 ports in spite of some of them are not being traversed by the traffic flows shown in the image. All the flows of the figure have as a source point one of the cores and as a target the memory placed at port 4 of  $R_1$ . As previously mentioned, every NoC topology can be represented as a tree structure. Figure 5.2b shows how the mesh topology shown in Figure 5.2a can be interpreted as a tree. The tree structure only shows the input and output ports that are traversed by a given set of flows even though we can have potentially a (P - 1)ary tree where *P* is the number of ports that each router has (e.g. we can only have 4 contenders to the same output port as the same output port cannot be competing as an input port).

#### 5.1.1 Implementation cost of a weighted round-robin (WRR) arbiter

In order to assess the cost of achieving a programmable arbitration in the NoC routers, we analyze the cost of the two main alternative implementations explained in the previous section. In this section we account for implementation costs of WRR as the heterogeneous BW distribution to achieve homogeneous BW allocation and we also commend how to be extended to any type of FBA.

Weight counters' implementation. For each output port, we will need 1 counter and 1 register per input port (with similar cost). The counter tracks the pending arbitrations (weight) that decreases along the execution and the register keeps the maximum value to set as initial value whenever all counters in the port reach zero. That means that for a router with  $P_{ports}$  for each potential output port ( $P_{ports}$ ) we need as many counters as potential input ports for each output port ( $P_{ports} - 1$ ) per output port multiplied by 2 (the counter and the register). So, for each of the  $P_{ports}$ per router in each of the  $R_{routers}$  in the NoC we will need  $2 \cdot (P_{ports} - 1)$  weights. Each such weight has as many bits as needed to codify one flow for each core in the system  $\lceil log_2(C_{cores}) \rceil$ .

$$ArbCost_{imp1} = R_{routers} \cdot P_{ports} \cdot 2 \cdot (P_{ports} - 1) \cdot \lceil log_2(C_{cores}) \rceil$$

(5.1)

For instance, for Figure 5.1, the cost of implementing weight counters would be  $3 \cdot 1 \cdot 2 \cdot 2 = 24$  bits, so 3 bytes only. That is, we have 3 routers and in each router has 1 potential output port and 2 potential input ports per this output port. Each potential input port has to keep information about the current counter (counter) and the maximum value that the counter will have when it will be set (register).

The previous formula easily extends for other topologies like meshes. In the case of meshes,  $R_{routers} = (NxM)$  where N and M are the X and Y dimensions of the mesh respectively. For example, for a 4x4 2D mesh with 16 cores, the cost of the implementation would be  $16 \cdot 5 \cdot 2 \cdot 4 \cdot 4 = 2560$  bits, so 320 bytes for the whole NoC (20 bytes per router). That is, for each router (16) we have 5 potential output ports and 4 potential input ports for each of this potential output ports. Each potential input port has to keep information about the current counter (counter) and the maximum value that the counter will have when it will be set (register). The

more cores in the mesh we have, the more bits we need to codify the weights to achieve homogeneous BW allocation (e.i number of cores in the mesh grows).

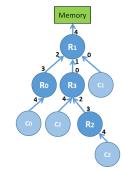

Arbitration Window implementation: we need an arbitration window for all potential output ports ( $P_{ports}$ ) that each router has. Each arbitration window needs to have as many entries as number of cores in the NoC ( $C_{cores}$ ) to allow homogeneous BW allocation in all NoC cores. In each of the entries of the arbitration window, we need to codify the potential values of input ports per each output port that we can have ( $P_{ports} - 1$ ). Thus, we need  $\lceil \log_2(P_{port} - 1) \rceil$ . This values can be X+,X-,Y+,Y- and Processor/Memory Element (PME) indicating the input port incoming direction. This design is sketched in Figure 5.3). Then, each arbitra also needs a  $\lceil log_2(C_{cores}) \rceil$  bit counter pointing to the next entry in the window along with an incrementer for that counter. Alternatively, one could use shift registers with wrap-up for the window and use always the value at a given position (e.g. first position) to determine what port is granted access next.

$$ArbCost_{imp2} = R_{routers} \cdot P_{ports} \cdot \left(C_{cores} \cdot \lceil log_2(P_{ports} - 1) \rceil + \lceil log_2(C_{cores}) \rceil\right)$$

(5.2)

For instance, for Figure 5.1 binary tree, the cost of implementing the window arbiter would be  $3 \cdot 1 \cdot (4 \cdot 1 + 2) = 18$  bits, so 2, 25 bytes only. Or for example, for a 4x4 2D mesh with 16 cores, the cost of the implementation would be  $16 \cdot 5 \cdot (16 \cdot 2 + 4) = 2880$  bits, so 360 bytes for the whole NoC (22,5 bytes per router).

If we want to implement FBA not only to homogenize the BW allocation in all the interconnect, the implementation will be more costly. When applying WRR arbitration to homogenize BW it is enough to have counters of  $\lceil log_2(C_{cores})) \rceil$  bits or arbitration windows of  $C_{core}$  size. However, if we want a desired BW distribution (not following the RR and homogenizing WRR), we will have to change the  $C_{core}$  value for the *maximum weight value*.

Some NoC implementations favor efficiency in front of flexibility and arbitration choices are hardwired. Adapting such a NoC to implement the weighted arbitration would require, at most, hardwiring different choices in the arbitration windows, thus not increasing the hardware cost.

FIGURE 5.3: Window arbitration implementation.

Overall, hardware modifications would have limited impact on the overall cost of the NoC, which is mostly dominated by the buffering required at input ports.

#### 5.1.2 Adapting arbitration weights

In weighted round-robin arbitration (WRR) to achieve homogeneous core BW allocation, weights can be used to determine the frequency at which a given master gets access to a given shared resource. In a NoC router with  $N_{IP_{contenders}}$  input ports contending for the access to a output port (OP) different arbitration weights can be employed for each of the input ports ( $IP_{weight}$ ) provided that the following conditions are meet:

$$OP_{BW} = \sum IP_{weight} / N_{IP_{contenders}}$$

(5.3)

The equation above, simply illustrates formally that the total bandwidth (BW) of the output port has to be shared by the different input ports. For instance, for a plain round-robin arbitration, the weights are all 1 since all input ports are allocated the same bandwidth. However, round-robin arbitration does not distribute the bandwidth fairly in the context of NUMA-based network topologies like the mesh. Weighted arbitration can be employed to homogeneously allocate the BW. To do so, weights can be computed using the following expression:

$$w(I_{dir}, O_{dir}) = I_{dir} / O_{dir}$$

(5.4)

where  $I_{dir}$  represents the number of communication flows traversing the  $dir_i$  input port of a given router being dir any of the possible mesh router port directions. Similarly,  $O_{dir}$  is the number of flows traversing the dir output port of the same router.

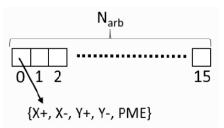

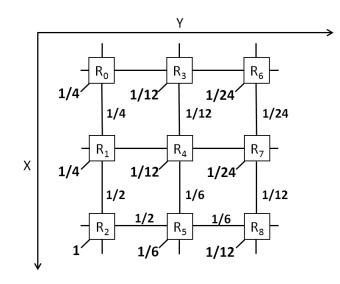

FIGURE 5.4: 3x3 mesh weight using XY routing and WRR arbitration

We can configure our mesh input ports' weight for each output port as we show in Figure 5.4, which in practice means:

- In both WRR arbiter implementations, we can set in  $R_2$  for the memory output port, the weights 1 and 3 for ports that come from  $R_1$  (X+) and  $R_5$  (Y-) respectively and weight 0 to all other input ports. Analogously for  $R_5$ , having as an output port the port that goes to  $R_2$ , we can assign the weights 1, 3 and 2 to input ports that come from  $C_5$  mapped in  $R_5$  as a Processor/Memory Element (PME),  $R_8$  (Y-) and  $R_4$  (X+) respectively.

- In the particular case of the arbitration window implementation, in the memory output port of *R*<sub>2</sub> we can use the window *X*+, *Y*-, *Y*-, *Y* being *X*+ the input port that comes from *R*<sub>1</sub> and *Y* the input port that comes from *R*<sub>5</sub>. Analogously, for the output port that goes to *R*<sub>2</sub> router in *R*<sub>5</sub>, we can set as arbitration window the combination *PME*, *Y*-, *X*+, *Y*-, *X*+, *Y* being *PME* the input port that comes from *C*<sub>5</sub> mapped in *R*<sub>5</sub>, and *Y* and *X*+ the input ports that come from *R*<sub>8</sub> and *R*<sub>4</sub> respectively.

| Router id  | X+ | Х- | Y+ | Y- | PME | Router id | X+ | <b>X-</b> | Y+ | Y- | PME |

|------------|----|----|----|----|-----|-----------|----|-----------|----|----|-----|

| R0         | 0  | 0  | 0  | 0  | 1   | R5        | 2  | 0         | 0  | 3  | 1   |

| <i>R</i> 1 | 1  | 0  | 0  | 0  | 1   | R6        | 0  | 0         | 0  | 0  | 1   |

| R2         | 1  | 0  | 0  | 3  | 0   | R7        | 1  | 0         | 0  | 0  | 1   |

| R3         | 0  | 0  | 0  | 0  | 1   | R8        | 2  | 0         | 0  | 0  | 1   |

| <i>R</i> 4 | 1  | 0  | 0  | 0  | 1   | -         | -  | -         | -  | -  | -   |

TABLE 5.1: Weights per input port direction for a 3x3 Mesh with WRR

#### 5.2 On-Chip Interconnection Architectures

We apply the FBA scheme to two of the common NoCs topologies implemented in current multicore processors like the tree and the mesh. For each topology, we analyze its particular behavior and propose solutions on how to take advantage of using a FBA scheme.

#### 5.2.1 Tree

We consider a tree NoC topology as the one proposed in [32]. This topology is also implemented in real processors like the P2012 [6] and it can serve as the basis to efficiently implement crossbar topologies as shown in [32]. In tree NoC topologies all the cores are at the same distance from the memory. Thus, we have intrinsically unified memory access (UMA) in all the cores. Having UMA in the NoC, allows basic RR arbitration to homogeneously allocate BW across all the cores.

FIGURE 5.5: Binary tree with RR arbiter

When we apply homogeneous BW distribution in each router (i.e. using RR arbitration), we observe homogeneous BW allocation as shown in Figure 5.5. In each one of the routers, the RR arbitration policy divides by two the output BW to the input ports that are contending for this output port. Applying this BW distribution recursively, we end up with the weights shown in Figure 5.5. In this case, as we have 4 cores, each core receives 1/4 of the available BW. We can generalize this BW distribution in UMA NoCs in the following way: if we have *N* cores, when we follow the RR policy to distribute the BW along the tree, we end up with 1/N of the initial BW per core.

#### 5.2.2 Meshes

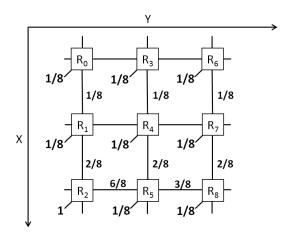

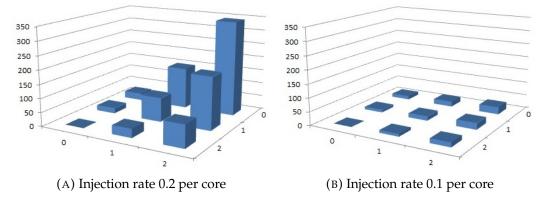

In this section we analyze the mesh topology. Meshes, unlike trees, have intrinsically a non-unified memory access (NUMA) since, depending on the core location in the mesh, it takes more or less time to access memory. On the one hand, we have different latencies, which translates to different execution times from the same application depending in which core we run the application even in isolation (i.e. the execution time of the application does not depend on other contenders). On the other hand, in the presence of contention, the fact that RR arbitration is applied in every router along the path from source to destination, causes an uneven distribution of bandwidth. This phenomena is illustrated in Figures 5.6 (flows) and 5.7 (weights).

FIGURE 5.6: 3x3 mesh flows using XY routing algorithm

In Figure 5.6, we can see which are the traffic flows when each core injects messages to the 3x3 mesh targeting the memory controller located in  $R_2$ . We show how flows are mapped in the mesh following XY routing algorithm which, as we have already explained in section 2.2.2, is one of the most used routing algorithms since it is easy to implement in hardware and it has deadlock/livelock free properties.

As said before, when we apply homogeneous BW distribution in each mesh router (i.e. using RR arbitration), we observe globally heterogeneous BW allocation. We can observe this phenomena in Figure 5.7. Note that the example we propose in this figure shows a 3x3 mesh NoC with 8 cores as we connect a memory module in  $R_2$  instead of  $C_2$ . With this RR BW distribution, we have  $C_0$  and  $C_1$  with 1/4 of

FIGURE 5.7: 3x3 mesh weights using XY routing and RR arbitration

the BW,  $C_5$  with 1/6,  $C_3$ ,  $C_4$  and  $C_8$  with 1/12, and  $C_6$  and  $C_7$  with 1/24 of the BW. As we can notice, this BW distribution is highly related with the distance from each core to the memory (placed in this case in  $R_2$ ) as the farther cores from memory ( $C_6$ and  $C_7$ ) tend to have less BW, even though it does not follow this trend perfectly ( $C_6$ and  $C_7$  receive the same amount of BW but  $C_6$  is farther away in number of hops from memory as it has 4 hops whereas  $C_7$  it has 3).

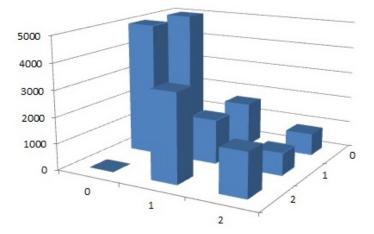

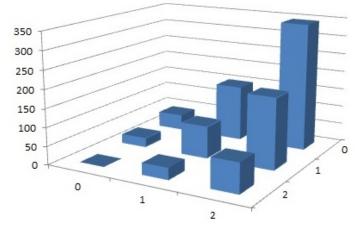

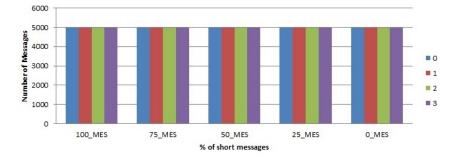

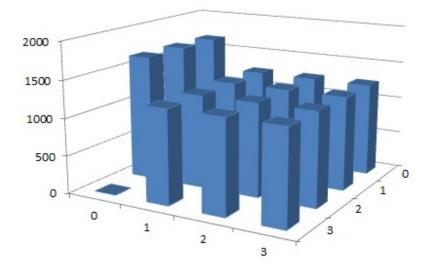

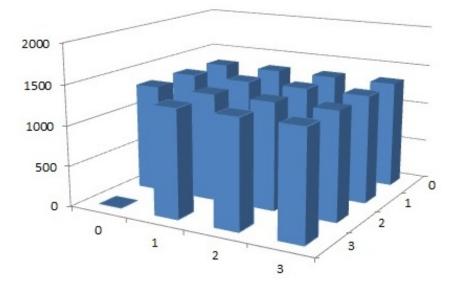

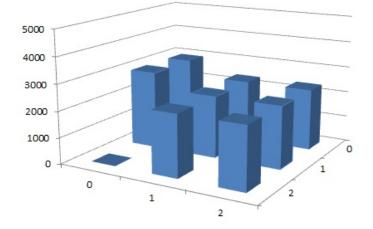

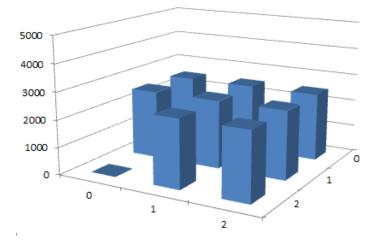

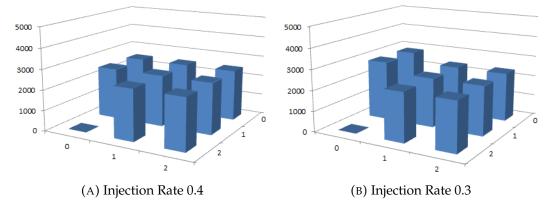

FIGURE 5.8: Messages sent per NIC in a 3x3mesh XY routing and RR arbitration

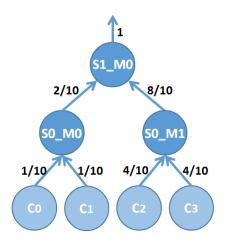

In Figure 5.8, we can observe the imbalance between messages sent per core which is strongly related to the imbalance that the mesh topology brings intrinsically when using RR arbitration. As we have explained, cores that are closer to the memory location have higher BW (i.e.  $C_0$  and  $C_1$ ) than the ones that are farther away (i.e.

$C_6$ ), which allows them to be granted more arbitration rounds than the others. This plot also shows that, when we send 20000 messages along the mesh,  $C_0$  and  $C_1$  are able to send 5000 messages each (25% of the BW), $C_3$  3333 messages (33% of the BW),  $C_3$ ,  $C_4$  and  $C_8$  1667 messages (8,33% of the BW) and  $C_6$  and  $C_7$  833 messages (4,1% of the BW), which matches perfectly with the heterogeneous distribution showed in Figure 5.7.

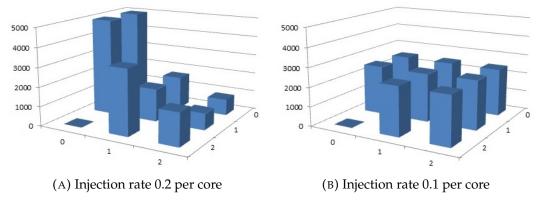

When we deal with a 2D mesh as a NoC, we have also to take into account the real latency distribution, since messages sent from cores farther away from memory will take more time to arrive to memory than the messages sent from the closer cores. In Figure 5.9 we show the latency (time between a message is being sent and it arrives to the memory) that messages have experienced depending on from which core have been sent.

FIGURE 5.9: Messages latency